Power Network Distribution ChungKuan Cheng CSE Dept University

Power Network Distribution Chung-Kuan Cheng CSE Dept. University of California, San Diego

Power Distribution Network Overview Background: power distribution networks (PDN’s) Analysis: worst-case PDN noise prediction – Target Impedance – Worst Current Loads – Rogue Wave Conclusions and future work Page 2

Research on Power Distribution Networks Analysis – Stimulus, Noise Margin, Simulation Synthesis – VRM, Decap, ESR, Topology Integration – Sensors, Prediction, Stability, Robustness Page 3

Agenda Background: power distribution networks (PDN’s) Analysis: worst-case PDN noise prediction – Motivation – Problem formulation – Proposed Algorithm – Case study Conclusions and future work Page 4

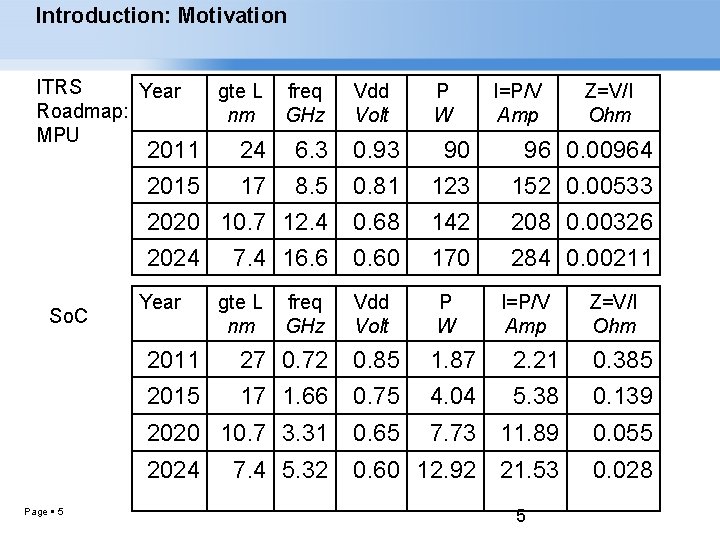

Introduction: Motivation ITRS Year Roadmap: MPU gte L nm Year gte L nm freq GHz 2011 24 6. 3 2015 17 8. 5 2020 10. 7 12. 4 2024 7. 4 16. 6 So. C Page 5 freq GHz Vdd Volt P W I=P/V Amp Z=V/I Ohm 0. 93 0. 81 0. 68 0. 60 90 123 142 170 96 152 208 284 0. 00964 0. 00533 0. 00326 0. 00211 Vdd Volt P W I=P/V Amp Z=V/I Ohm 2011 27 0. 72 0. 85 1. 87 2. 21 0. 385 2015 17 1. 66 0. 75 4. 04 5. 38 0. 139 2020 10. 7 3. 31 0. 65 7. 73 11. 89 0. 055 2024 0. 60 12. 92 21. 53 0. 028 7. 4 5. 32 5

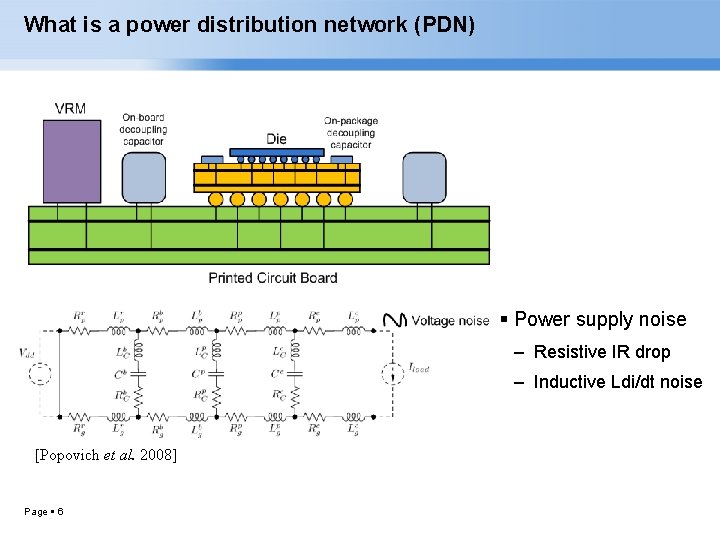

What is a power distribution network (PDN) Power supply noise – Resistive IR drop – Inductive Ldi/dt noise [Popovich et al. 2008] Page 6

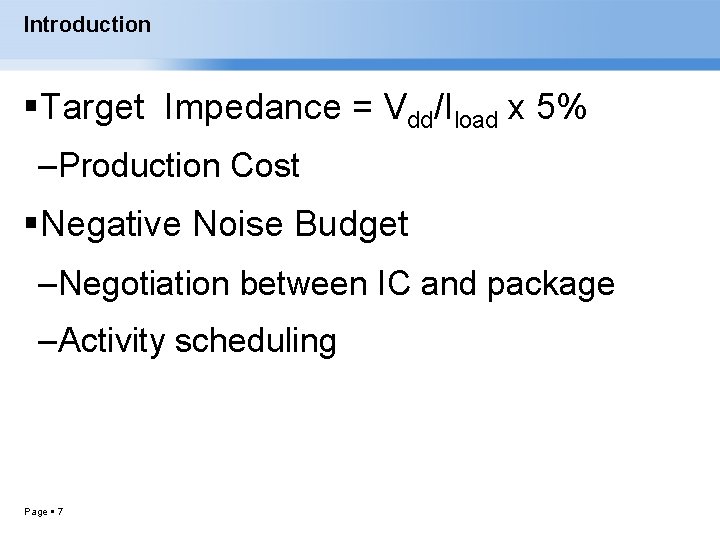

Introduction Target Impedance = Vdd/Iload x 5% – Production Cost Negative Noise Budget – Negotiation between IC and package – Activity scheduling Page 7

Agenda Background: power distribution networks (PDN’s) Analysis: worst-case PDN noise prediction – Motivation – Formulation – Algorithms – Case study Conclusions and future work Page 8

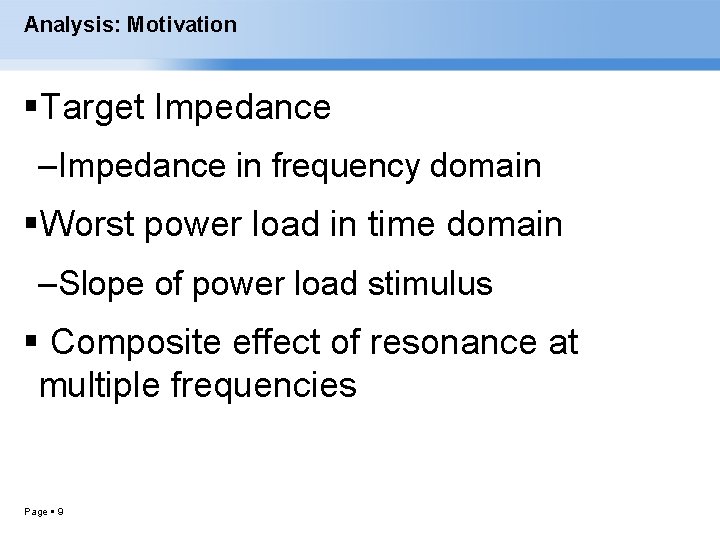

Analysis: Motivation Target Impedance – Impedance in frequency domain Worst power load in time domain – Slope of power load stimulus Composite effect of resonance at multiple frequencies Page 9

Target Impedance PDN design – Objective: low power supply noise – Popular methodology: “target impedance” [Smith ’ 99] Implication: if the target impedance is small, then the noise will also be small Page 10

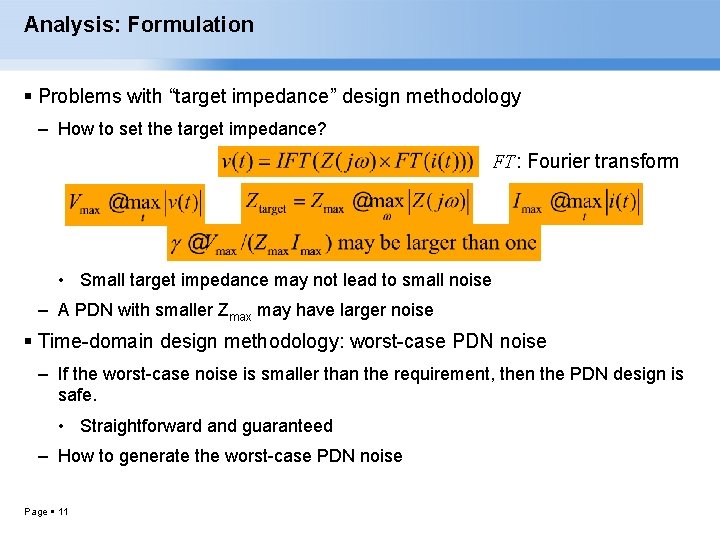

Analysis: Formulation Problems with “target impedance” design methodology – How to set the target impedance? FT: Fourier transform • Small target impedance may not lead to small noise – A PDN with smaller Zmax may have larger noise Time-domain design methodology: worst-case PDN noise – If the worst-case noise is smaller than the requirement, then the PDN design is safe. • Straightforward and guaranteed – How to generate the worst-case PDN noise Page 11

![Analysis: Related Work At final design stages [Evmorfopoulos ’ 06] – Circuit design is Analysis: Related Work At final design stages [Evmorfopoulos ’ 06] – Circuit design is](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-12.jpg)

Analysis: Related Work At final design stages [Evmorfopoulos ’ 06] – Circuit design is fully or almost complete – Realistic current waveforms can be obtained by simulation – Problem: countless input patterns lead to countless current waveforms • Sample the excitation space • Statistically project the sample’s own worst-case excitations to their expected position in the excitation space At early design stages [Najm ’ 03 ’ 05 ’ 07 ’ 08 ’ 09] – Real current information is not available – “Current constraint” concept – Vectorless approach: no simulation needed – Problem: assume ideal current with zero transition time Page 12

![Analysis: Formulation Problem formulation I PDN noise: Worst-case current [Xiang ’ 09]: Zero current Analysis: Formulation Problem formulation I PDN noise: Worst-case current [Xiang ’ 09]: Zero current](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-13.jpg)

Analysis: Formulation Problem formulation I PDN noise: Worst-case current [Xiang ’ 09]: Zero current transition time. Unrealistic! Page 13

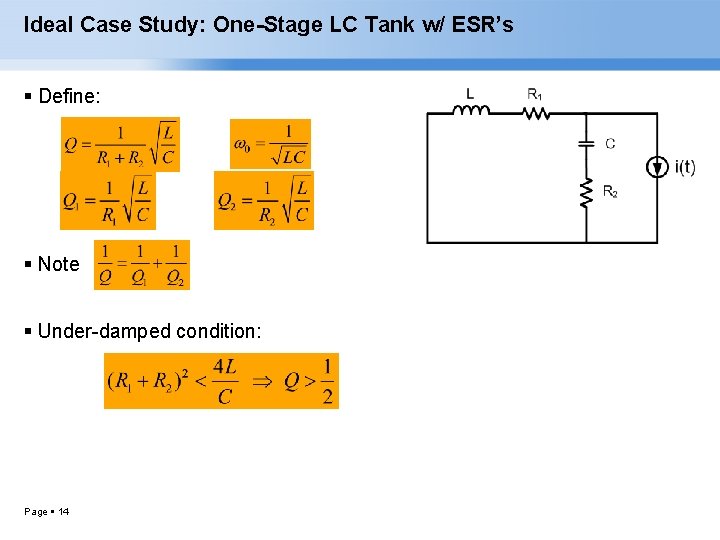

Ideal Case Study: One-Stage LC Tank w/ ESR’s Define: Note Under-damped condition: Page 14

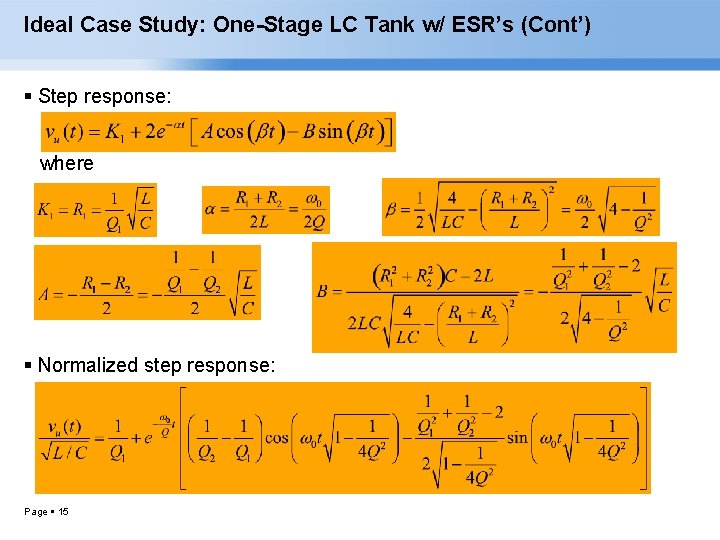

Ideal Case Study: One-Stage LC Tank w/ ESR’s (Cont’) Step response: where Normalized step response: Page 15

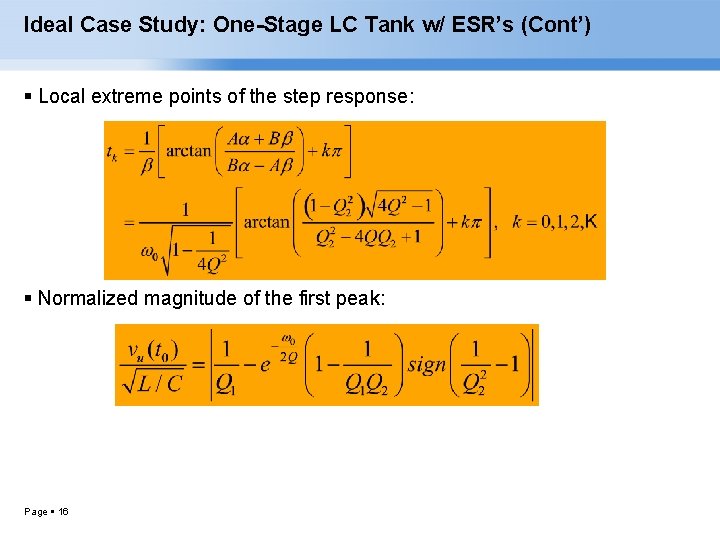

Ideal Case Study: One-Stage LC Tank w/ ESR’s (Cont’) Local extreme points of the step response: Normalized magnitude of the first peak: Page 16

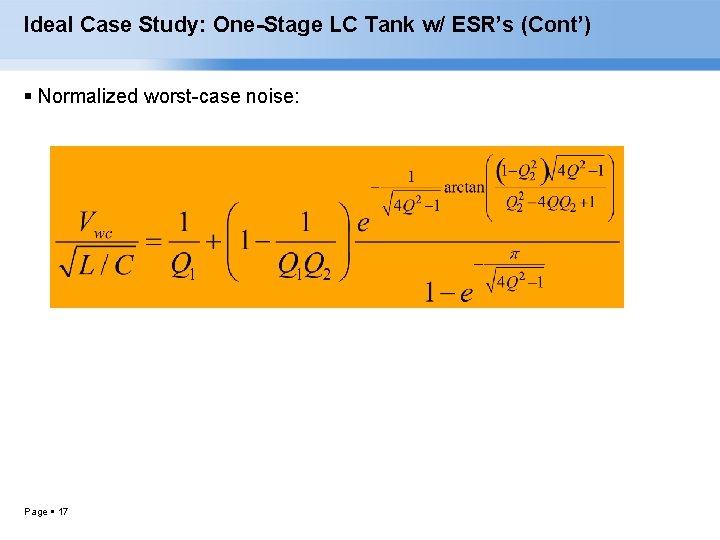

Ideal Case Study: One-Stage LC Tank w/ ESR’s (Cont’) Normalized worst-case noise: Page 17

![Ideal Case Study: One-Stage LC Tank w/ ESR’s (Cont’) Impedance: When [Mikhail 08] Normalized Ideal Case Study: One-Stage LC Tank w/ ESR’s (Cont’) Impedance: When [Mikhail 08] Normalized](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-18.jpg)

Ideal Case Study: One-Stage LC Tank w/ ESR’s (Cont’) Impedance: When [Mikhail 08] Normalized peak impedance: Page 18

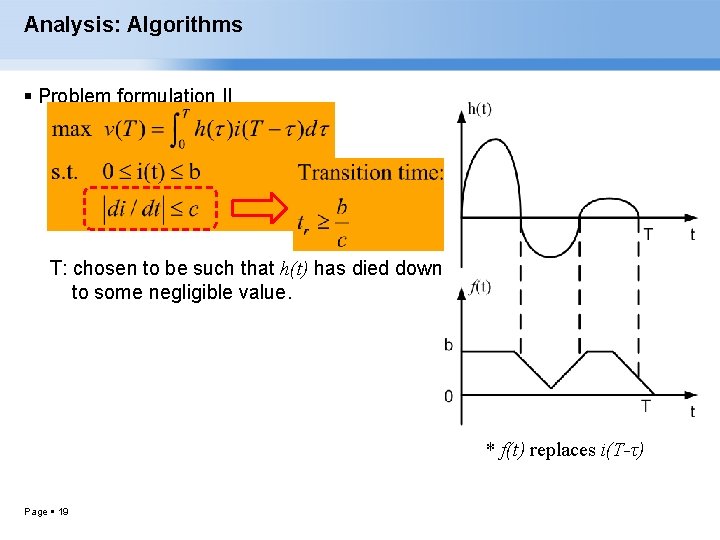

Analysis: Algorithms Problem formulation II T: chosen to be such that h(t) has died down to some negligible value. * f(t) replaces i(T-τ) Page 19

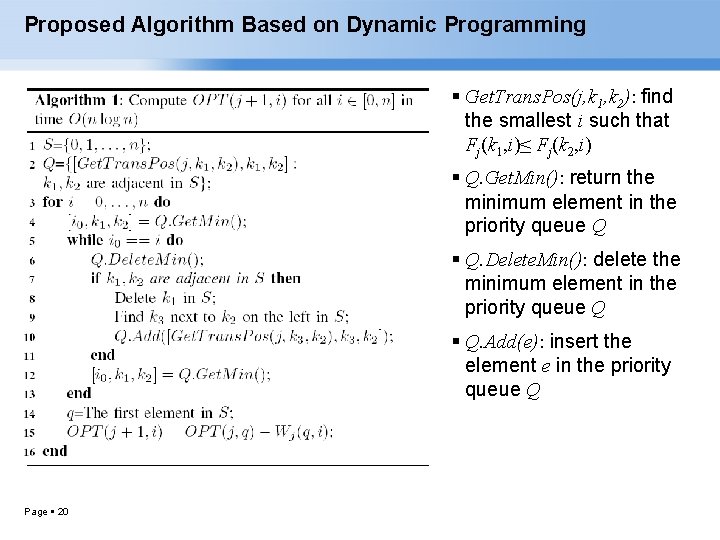

Proposed Algorithm Based on Dynamic Programming Get. Trans. Pos(j, k 1, k 2): find the smallest i such that Fj(k 1, i)≤ Fj(k 2, i) Q. Get. Min(): return the minimum element in the priority queue Q Q. Delete. Min(): delete the minimum element in the priority queue Q Q. Add(e): insert the element e in the priority queue Q Page 20

![Proposed Algorithm: Initial Setup Divide the time range [0, T] into m intervals [t Proposed Algorithm: Initial Setup Divide the time range [0, T] into m intervals [t](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-21.jpg)

Proposed Algorithm: Initial Setup Divide the time range [0, T] into m intervals [t 0=0, t 1], [t 1, t 2], …, [tm-1, tm=T]. h(ti) = 0, i=1, 2, …, m-1 u 0 = 0, u 1, u 2, …, un = b are a set of n+1 values within [0, b]. The value of f(t) is chosen from those values. A larger n gives more accurate results. h(t) Page 21

![Proposed Algorithm: f(t) within a time interval [tj, tj+1] Theorem 1: The worst-case f(t) Proposed Algorithm: f(t) within a time interval [tj, tj+1] Theorem 1: The worst-case f(t)](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-22.jpg)

Proposed Algorithm: f(t) within a time interval [tj, tj+1] Theorem 1: The worst-case f(t) can be constructed by determining the values at the zerocrossing points of the h(t) Ij(k, i): worst-case f(t) starting with uk at time tj and ending with ui at time tj+1 Page 22 h(t)

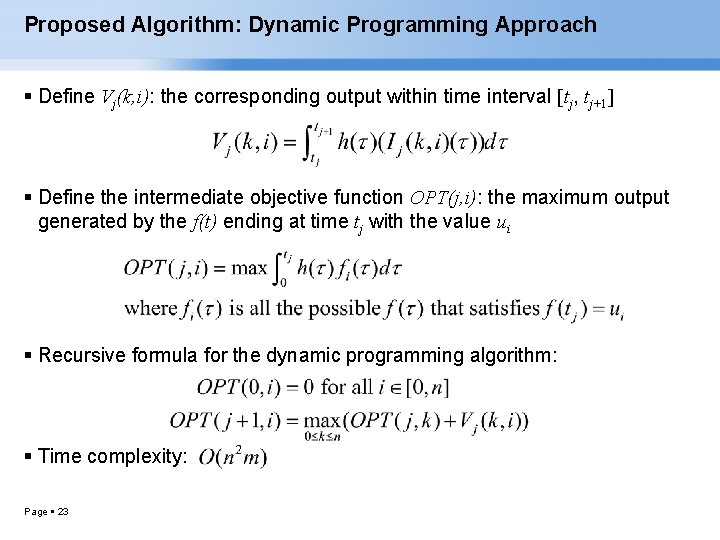

Proposed Algorithm: Dynamic Programming Approach Define Vj(k, i): the corresponding output within time interval [tj, tj+1] Define the intermediate objective function OPT(j, i): the maximum output generated by the f(t) ending at time tj with the value ui Recursive formula for the dynamic programming algorithm: Time complexity: Page 23

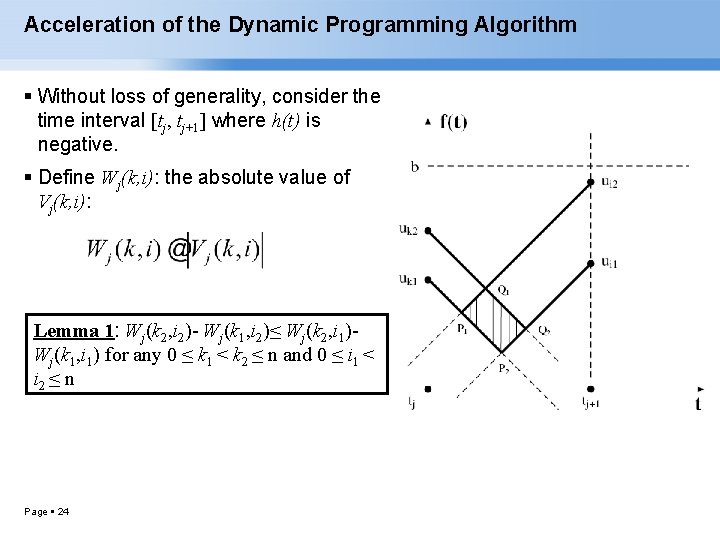

Acceleration of the Dynamic Programming Algorithm Without loss of generality, consider the time interval [tj, tj+1] where h(t) is negative. Define Wj(k, i): the absolute value of Vj(k, i): Lemma 1: Wj(k 2, i 2)- Wj(k 1, i 2)≤ Wj(k 2, i 1)Wj(k 1, i 1) for any 0 ≤ k 1 < k 2 ≤ n and 0 ≤ i 1 < i 2 ≤ n Page 24

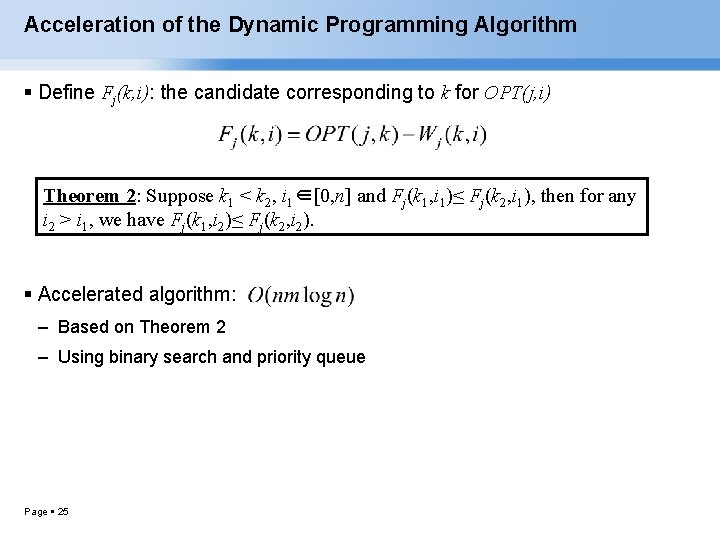

Acceleration of the Dynamic Programming Algorithm Define Fj(k, i): the candidate corresponding to k for OPT(j, i) Theorem 2: Suppose k 1 < k 2, i 1∈[0, n] and Fj(k 1, i 1)≤ Fj(k 2, i 1), then for any i 2 > i 1, we have Fj(k 1, i 2)≤ Fj(k 2, i 2). Accelerated algorithm: – Based on Theorem 2 – Using binary search and priority queue Page 25

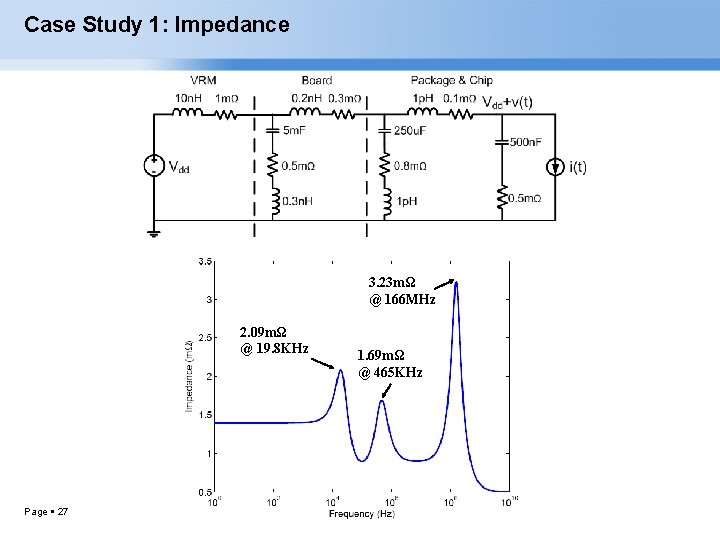

Analysis: Case Study Case 1: Impedance => Voltage drop – Transition Time Case 2: Impedances vs Worst Cases Case 3: Voltage drop due to resonance at multiple frequencies. Page 26

Case Study 1: Impedance 3. 23 mΩ @ 166 MHz 2. 09 mΩ @ 19. 8 KHz Page 27 1. 69 mΩ @ 465 KHz

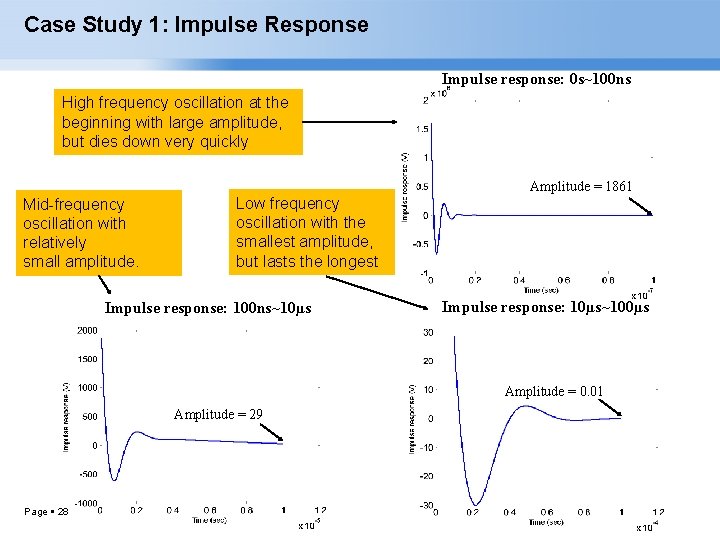

Case Study 1: Impulse Response Impulse response: 0 s~100 ns High frequency oscillation at the beginning with large amplitude, but dies down very quickly Amplitude = 1861 Mid-frequency oscillation with relatively small amplitude. Low frequency oscillation with the smallest amplitude, but lasts the longest Impulse response: 100 ns~10µs Impulse response: 10µs~100µs Amplitude = 0. 01 Amplitude = 29 Page 28

Case Study 1: Worst-Case Current constraints: Zoom in The worst-case current also oscillates with the three resonant frequencies which matches the impulse response. Saw-tooth-like current waveform at large transition times Page 29

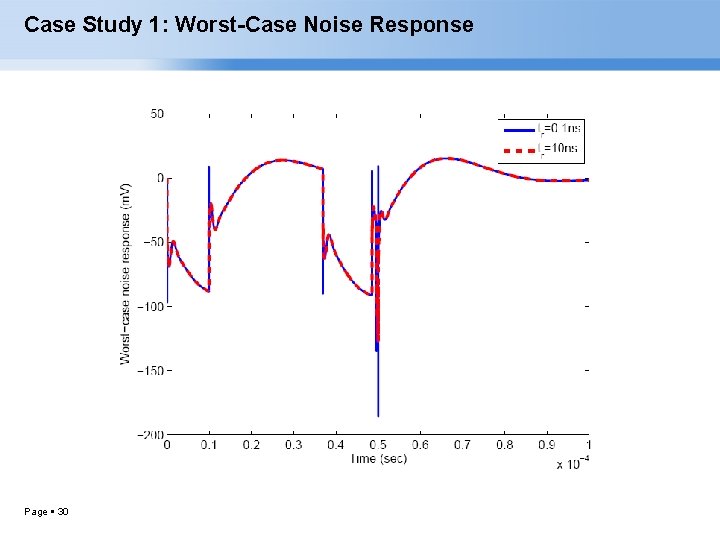

Case Study 1: Worst-Case Noise Response Page 30

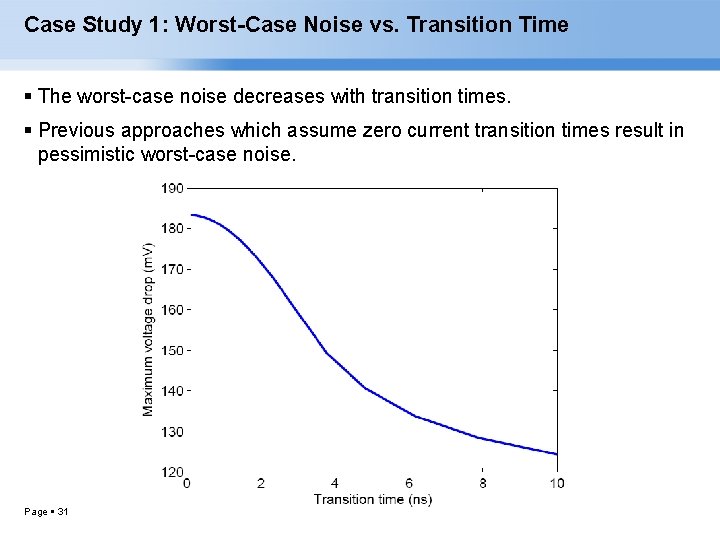

Case Study 1: Worst-Case Noise vs. Transition Time The worst-case noise decreases with transition times. Previous approaches which assume zero current transition times result in pessimistic worst-case noise. Page 31

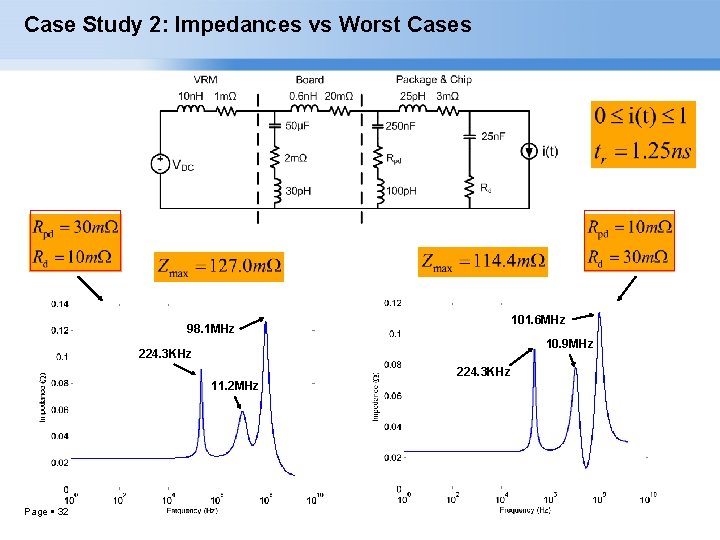

Case Study 2: Impedances vs Worst Cases 101. 6 MHz 98. 1 MHz 10. 9 MHz 224. 3 KHz 11. 2 MHz Page 32

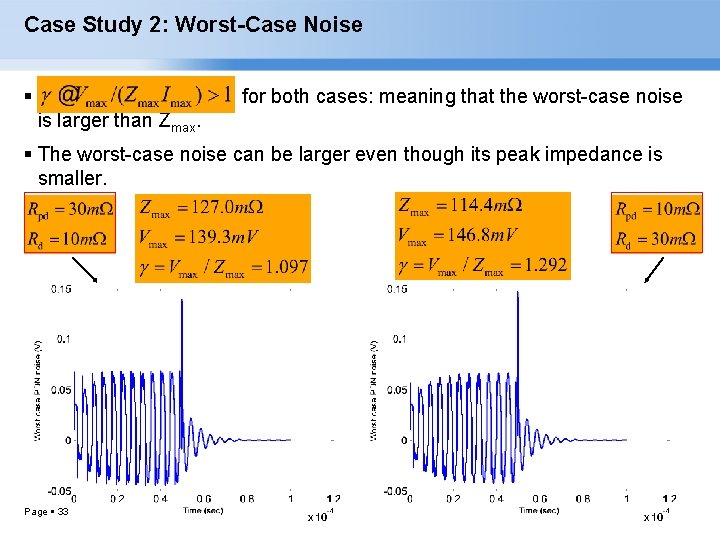

Case Study 2: Worst-Case Noise for both cases: meaning that the worst-case noise is larger than Zmax. The worst-case noise can be larger even though its peak impedance is smaller. Page 33

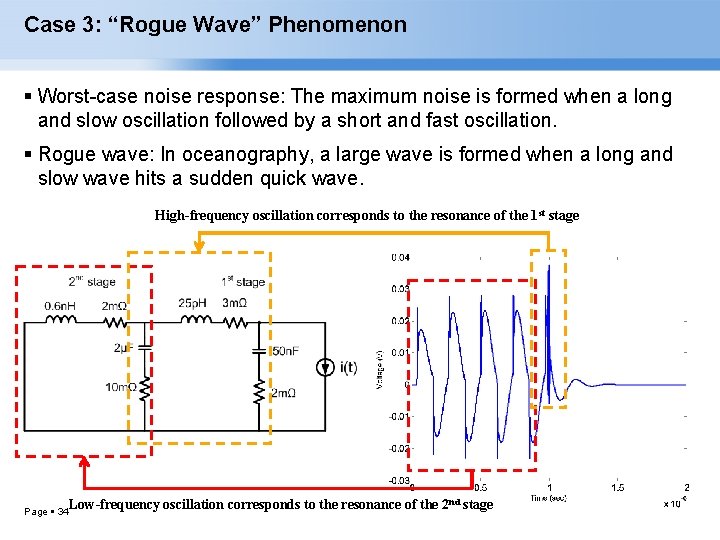

Case 3: “Rogue Wave” Phenomenon Worst-case noise response: The maximum noise is formed when a long and slow oscillation followed by a short and fast oscillation. Rogue wave: In oceanography, a large wave is formed when a long and slow wave hits a sudden quick wave. High-frequency oscillation corresponds to the resonance of the 1 st stage Page 34 Low-frequency oscillation corresponds to the resonance of the 2 nd stage

Case 3: “Rogue Wave” Phenomenon (Cont’) Equivalent input impedance of the 2 nd stage at high frequency Page 35

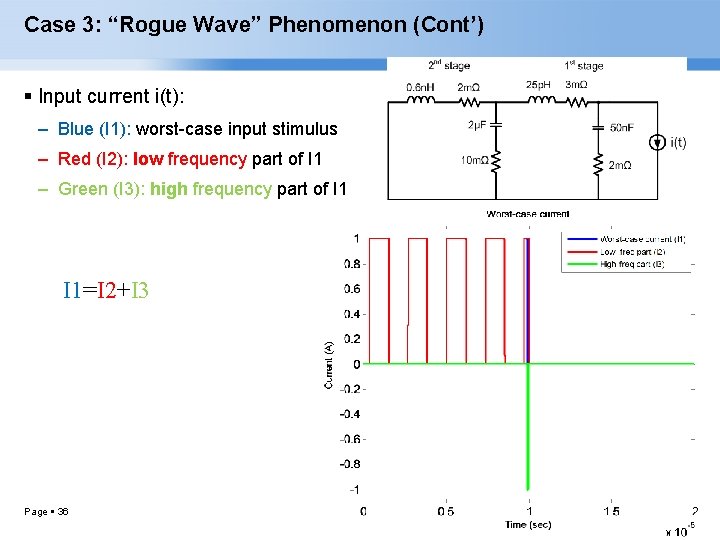

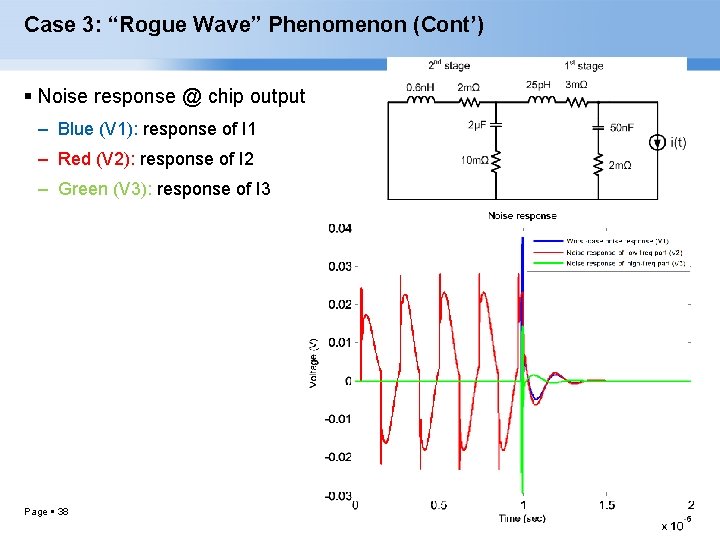

Case 3: “Rogue Wave” Phenomenon (Cont’) Input current i(t): – Blue (I 1): worst-case input stimulus – Red (I 2): low frequency part of I 1 – Green (I 3): high frequency part of I 1=I 2+I 3 Page 36

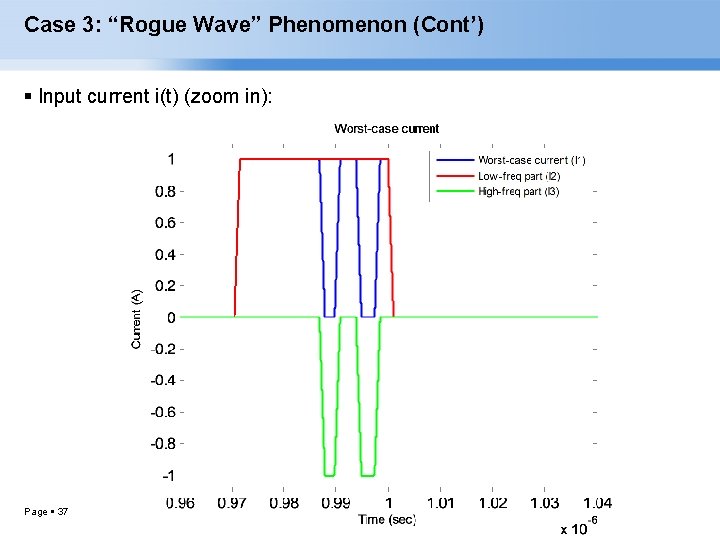

Case 3: “Rogue Wave” Phenomenon (Cont’) Input current i(t) (zoom in): Page 37

Case 3: “Rogue Wave” Phenomenon (Cont’) Noise response @ chip output – Blue (V 1): response of I 1 – Red (V 2): response of I 2 – Green (V 3): response of I 3 Page 38

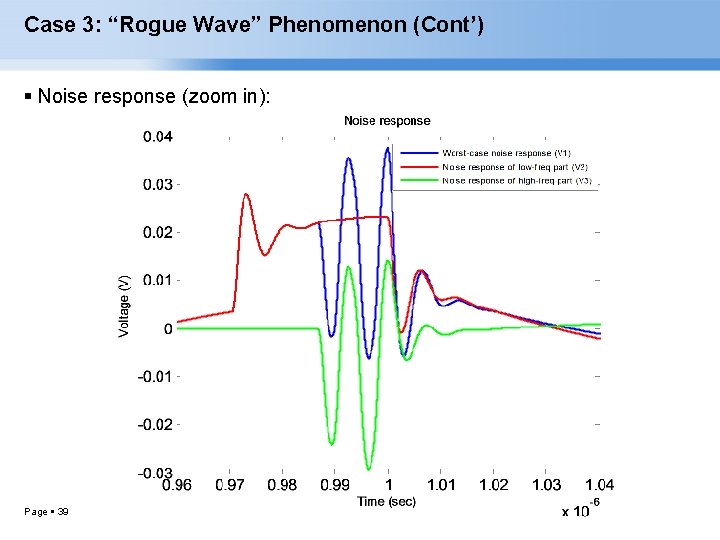

Case 3: “Rogue Wave” Phenomenon (Cont’) Noise response (zoom in): Page 39

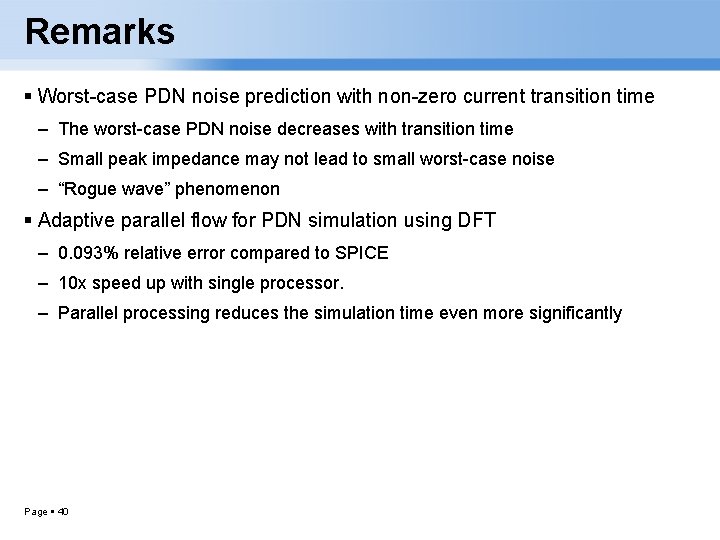

Remarks Worst-case PDN noise prediction with non-zero current transition time – The worst-case PDN noise decreases with transition time – Small peak impedance may not lead to small worst-case noise – “Rogue wave” phenomenon Adaptive parallel flow for PDN simulation using DFT – 0. 093% relative error compared to SPICE – 10 x speed up with single processor. – Parallel processing reduces the simulation time even more significantly Page 40

Summary 1. Throughput/power (instruction/energy) 2. Throughput 2/power (f x instruction/energy) Power Distribution Network – VRMs, Switches, Decaps, ESRs, Topology, Analysis – Stimulus, Noise Tolerance, Simulation Control (smart grid) – High efficiency, Real time analysis, Stability, Reliability, Rapid recovery, and Self healing Page 41

Page 42

![Publication List • Power Distribution Network Simulation and Analysis [1] W. Zhang and C. Publication List • Power Distribution Network Simulation and Analysis [1] W. Zhang and C.](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-43.jpg)

Publication List • Power Distribution Network Simulation and Analysis [1] W. Zhang and C. K. Cheng, "Incremental Power Impedance Optimization Using Vector Fitting Modeling, “ IEEE Int. Symp. on Circuits and Systems, pp. 2439 -2442, 2007. [2] W. Zhang, W. Yu, L. Zhang, R. Shi, H. Peng, Z. Zhu, L. Chua-Eoan, R. Murgai, T. Shibuya, N. Ito, and C. K. Cheng, "Efficient Power Network Analysis Considering Multi-Domain Clock Gating, “ IEEE Trans on CAD, pp. 1348 -1358, Sept. 2009. [3] W. P. Zhang, L. Zhang, R. Shi, H. Peng, Z. Zhu, L. Chua-Eoan, R. Murgai, T. Shibuya, N. Ito, and C. K. Cheng, "Fast Power Network Analysis with Multiple Clock Domains, “ IEEE Int. Conf. on Computer Design, pp. 456 -463, 2007. [4] W. P. Zhang, Y. Zhu, W. Yu, R. Shi, H. Peng, L. Chua-Eoan, R. Murgai, T. Shibuya, N. Ito, and C. K. Cheng, "Finding the Worst Case of Voltage Violation in Multi-Domain Clock Gated Power Network with an Optimization Method“ IEEE DATE, pp. 540 -547, 2008. [5] X. Hu, W. Zhao, P. Du, A. Shayan, C. K. Cheng, “An Adaptive Parallel Flow for Power Distribution Network Simulation Using Discrete Fourier Transform, ” IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC), 2010. [6] C. K. Cheng, P. Du, A. B. Kahng, G. K. H. Pang, Y. Wang, and N. Wong, "More Realistic Power Grid Verification Based on Hierarchical Current and Power Constraints, “ ACM Int. Symp. on Physical Design, pp. 159 -166, 2011. Page 43

![Publication List • Power Distribution Network Analysis and Synthesis [7] W. Zhang, Y. Zhu, Publication List • Power Distribution Network Analysis and Synthesis [7] W. Zhang, Y. Zhu,](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-44.jpg)

Publication List • Power Distribution Network Analysis and Synthesis [7] W. Zhang, Y. Zhu, W. Yu, A. Shayan, R. Wang, Z. Zhu, C. K. Cheng, "Noise Minimization During Power-Up Stage for a Multi-Domain Power Network, “ IEEE Asia and South Pacific Design Automation Conf. , pp. 391 -396, 2009. [8] W. Zhang, L. Zhang, A. Shayan, W. Yu, X. Hu, Z. Zhu, E. Engin, and C. K. Cheng, "On-Chip Power Network Optimization with Decoupling Capacitors and Controlled-ESRs, “Asia and South Pacific Design Automation Conference, 2010. [9] X. Hu, W. Zhao, Y. Zhang, A. Shayan, C. Pan, A. E. Engin, and C. K. Cheng, “On the Bound of Time-Domain Power Supply Noise Based on Frequency-Domain Target Impedance, ” System Level Interconnect Prediction Workshop (SLIP), July 2009. [10] A. Shayan, X. Hu, H. Peng, W. Zhang, and C. K. Cheng, “Parallel Flow to Analyze the Impact of the Voltage Regulator Model in Nanoscale Power Distribution Network, ” In. Symp. on Quality Electronic Design (ISQED), Mar. 2009. [11] X. Hu, P. Du, and C. K. Cheng, "Exploring the Rogue Wave Phenomenon in 3 D Power Distribution Networks, “ IEEE Electrical Performance of Electronic Packaging and Systems, pp. 5760, 2010. [12] C. K. Cheng, A. B. Kahng, K. Samadi, and A. Shayan, "Worst-Case Performance Prediction Under Supply Voltage and Temperature Variation, “ ACM/IEEE Int. Workshop on System Level Interconnect Prediction, pp. 91 -96, 2010. Page 44

![Publication List (Cont’) • 3 D Power Distribution Networks [13] A. Shayan, X. Hu, Publication List (Cont’) • 3 D Power Distribution Networks [13] A. Shayan, X. Hu,](http://slidetodoc.com/presentation_image_h/09f315ce44607ecf1db50599403a34b0/image-45.jpg)

Publication List (Cont’) • 3 D Power Distribution Networks [13] A. Shayan, X. Hu, “Power Distribution Design for 3 D Integration”, Jacob School of Engineering Research Expo, 2009 [Best Poster Award] [14] A. Shayan, X. Hu, M. l Popovich, A. E. Engin, C. K. Cheng, “Reliable 3 D Stacked Power Distribution Considering Substrate Coupling”, in International Conference on Computre Design (ICCD), 2009. [15] A. Shayan, X. Hu, C. K. Cheng, “Reliability Aware Through Silicon Via Planning for Nanoscale 3 D Stacked ICs, ” in Design, Automation & Test in Europe Conference (DATE), 2009. [16] A. Shayan, X. g Hu, H. Peng, W. Zhang, C. K. Cheng, M. Popovich, and X. Chen, “ 3 D Power Distribution Network Co-design for Nanoscale Stacked Silicon IC, ” in 17 th Conference on Electrical Performance of Electronic Packaging (EPEP), Oct. 2008. [5] [17] W. Zhang, W. Yu, X. Hu, A. i Shayan, E. Engin, C. K. Cheng, "Predicting the Worst-Case Voltage Violation in a 3 D Power Network", Proceeding of IEEE/ACM International Workshop on System Level Interconnect Prediction (SLIP), 2009. [18] X. Hu, P. Du, and C. K. Cheng, "Exploring the Rogue Wave Phenomenon in 3 D Power Distribution Networks, “ IEEE Electrical Performance of Electronic Packaging and Systems, pp. 5760, 2010. Page 45

- Slides: 45