Structure des Systmes Informatiques n Oprations des Systmes

- Slides: 30

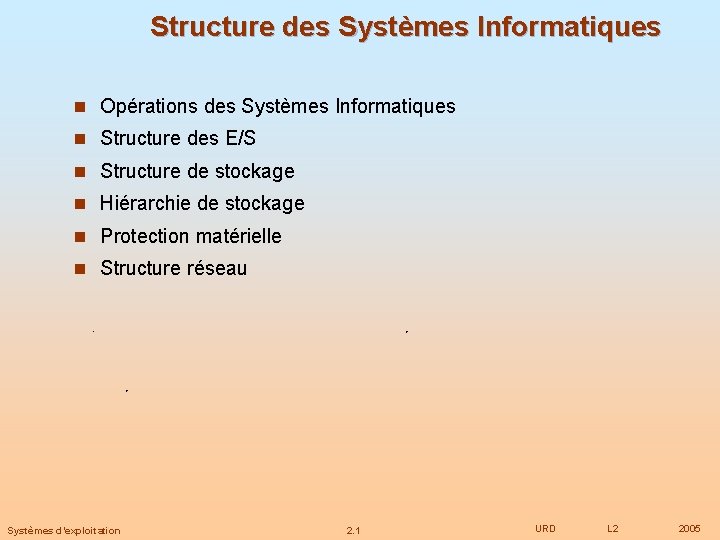

Structure des Systèmes Informatiques n Opérations des Systèmes Informatiques n Structure des E/S n Structure de stockage n Hiérarchie de stockage n Protection matérielle n Structure réseau Systèmes d’exploitation 2. 1 URD L 2 2005

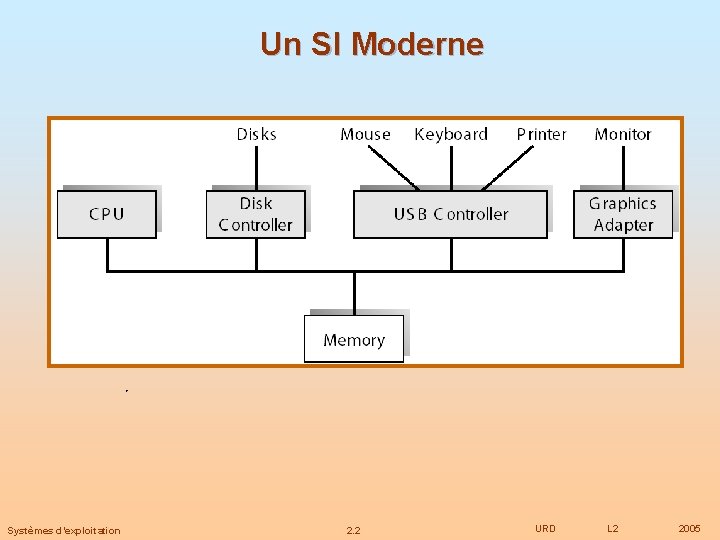

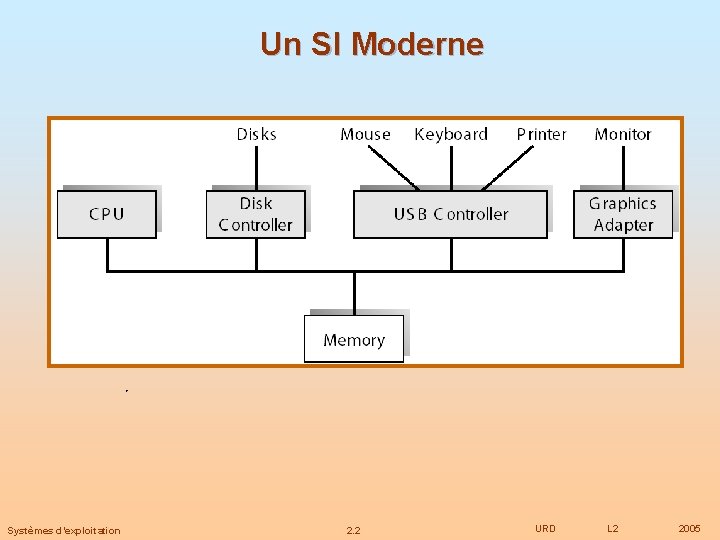

Un SI Moderne Systèmes d’exploitation 2. 2 URD L 2 2005

Opérations des SI n Périphériques d’E/S et la CPU peuvent s’exécuter simultanément n Chaque contrôleur de périphérique est en charge d’un type particulier de périphériques n Chaque contrôleur de périphérique a un tampon local n CPU transfère les données de/à la mémoire centrale au/du tampon local n E/S se fait du périphérique au tampon local du contrôleur n Le contrôleur de périphérique informe la CPU qu’il a fini l’opération en générant une interruption Systèmes d’exploitation 2. 3 URD L 2 2005

Fonctions Communes des Interruptions n Une interruption transfère le contrôle à une fonction de service de l’interruption à travers le vecteur d’interruption qui contient les adresses de tous les services n L’adresse de l’instruction interrompue doit être sauvegardée n Les interruptions sont désactivées tant qu’une interruption est en cours de traîtement pour ne pas avoir une interruption perdue n Une “trap” est un interruption logicielle causée par une erreur ou une requête utilisateur n Les OSs modernes sont dirigés par les interruptions Systèmes d’exploitation 2. 4 URD L 2 2005

Traîtement des Interruptions n L’OS sauvegarde l’état de la CPU (registre, compteur de programme) n Détermine quelle interruption a eu lieu: l polling l Vecteur d’interruption n Différentes fonctions du noyau correspondent aux traîtement rattachés à chaque interruption Systèmes d’exploitation 2. 5 URD L 2 2005

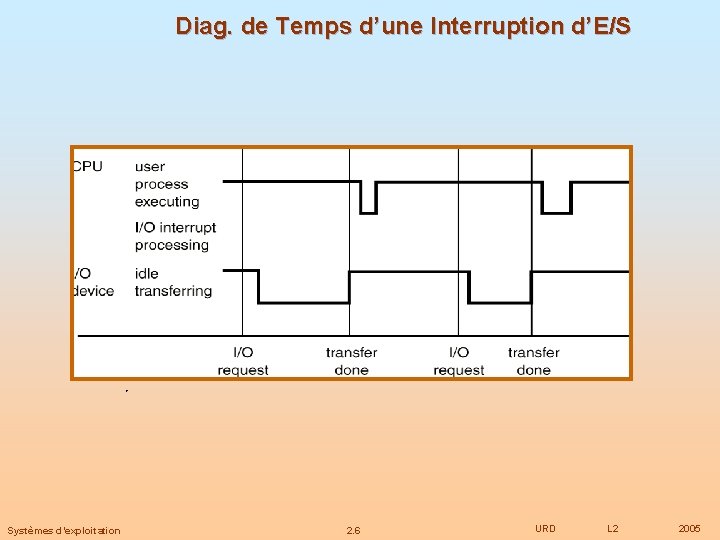

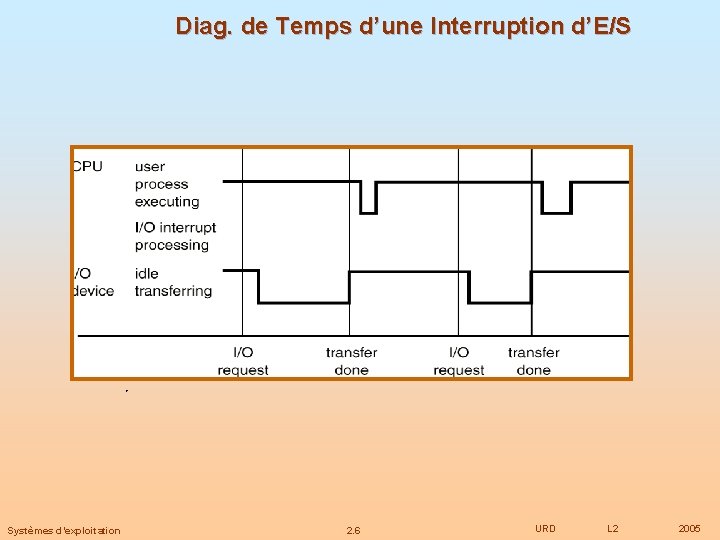

Diag. de Temps d’une Interruption d’E/S Systèmes d’exploitation 2. 6 URD L 2 2005

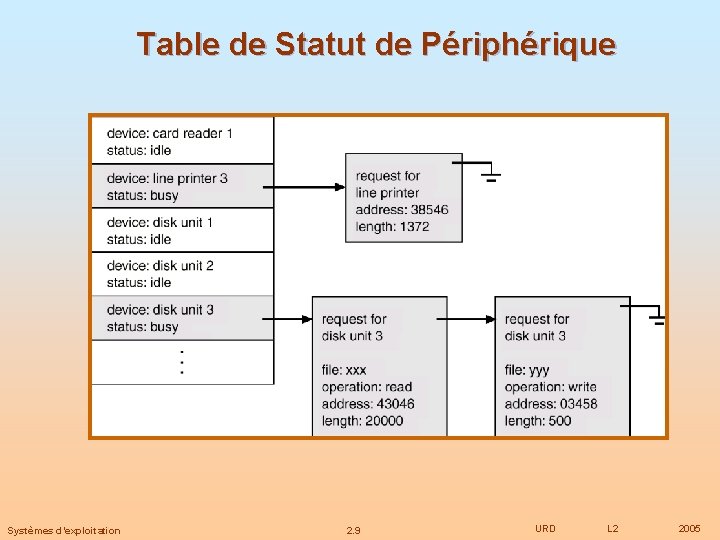

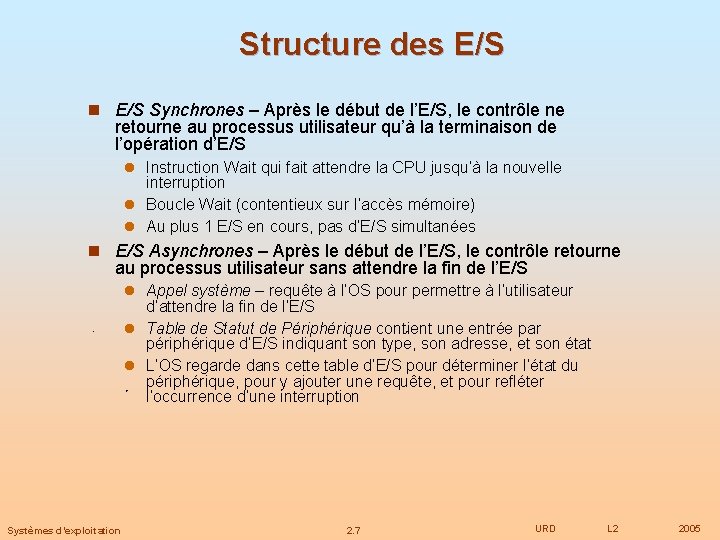

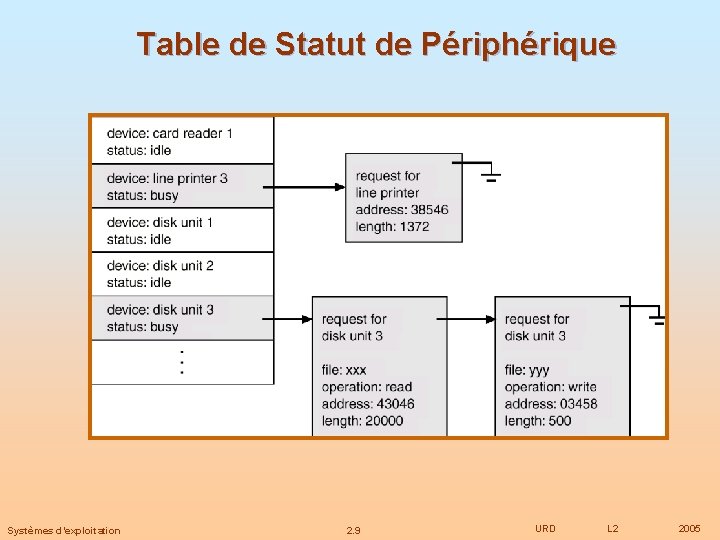

Structure des E/S n E/S Synchrones – Après le début de l’E/S, le contrôle ne retourne au processus utilisateur qu’à la terminaison de l’opération d’E/S l Instruction Wait qui fait attendre la CPU jusqu’à la nouvelle interruption l Boucle Wait (contentieux sur l’accès mémoire) l Au plus 1 E/S en cours, pas d’E/S simultanées n E/S Asynchrones – Après le début de l’E/S, le contrôle retourne au processus utilisateur sans attendre la fin de l’E/S l Appel système – requête à l’OS pour permettre à l’utilisateur d’attendre la fin de l’E/S l Table de Statut de Périphérique contient une entrée par périphérique d’E/S indiquant son type, son adresse, et son état l L’OS regarde dans cette table d’E/S pour déterminer l’état du périphérique, pour y ajouter une requête, et pour refléter l’occurrence d’une interruption Systèmes d’exploitation 2. 7 URD L 2 2005

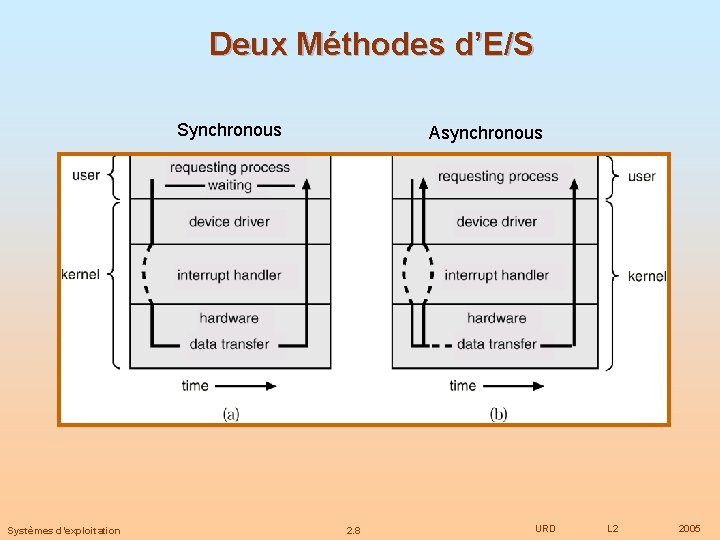

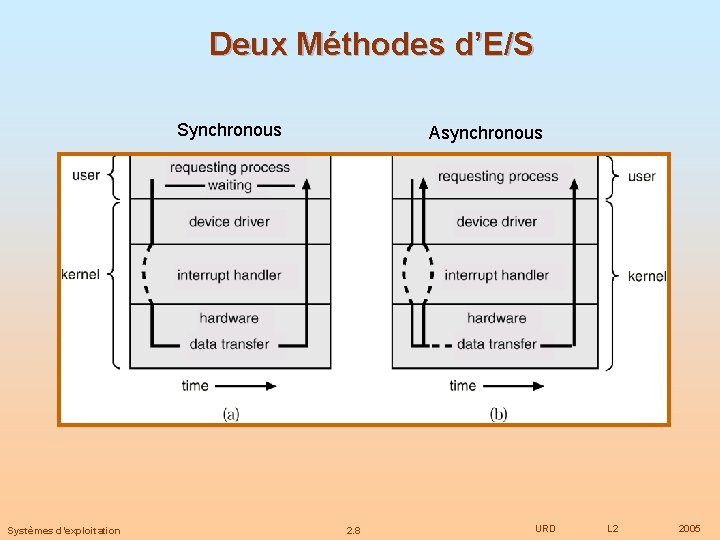

Deux Méthodes d’E/S Synchronous Systèmes d’exploitation Asynchronous 2. 8 URD L 2 2005

Table de Statut de Périphérique Systèmes d’exploitation 2. 9 URD L 2 2005

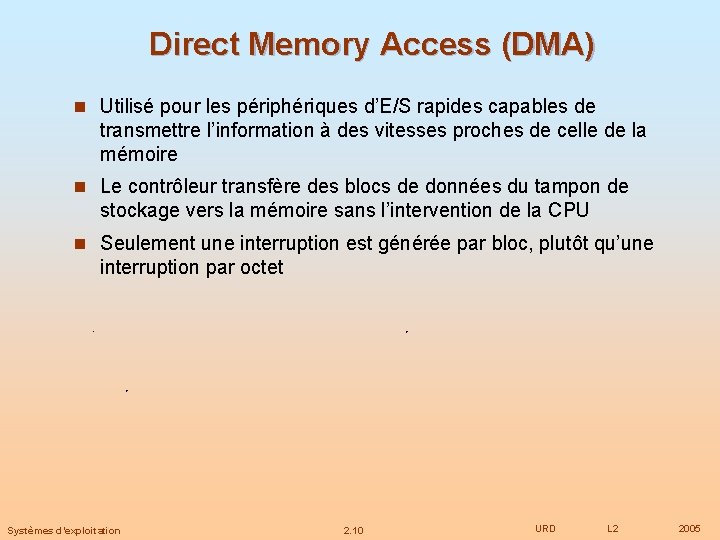

Direct Memory Access (DMA) n Utilisé pour les périphériques d’E/S rapides capables de transmettre l’information à des vitesses proches de celle de la mémoire n Le contrôleur transfère des blocs de données du tampon de stockage vers la mémoire sans l’intervention de la CPU n Seulement une interruption est générée par bloc, plutôt qu’une interruption par octet Systèmes d’exploitation 2. 10 URD L 2 2005

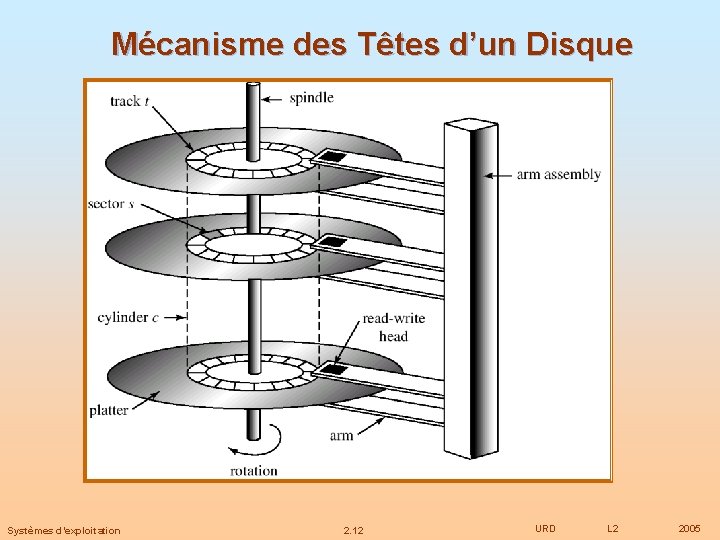

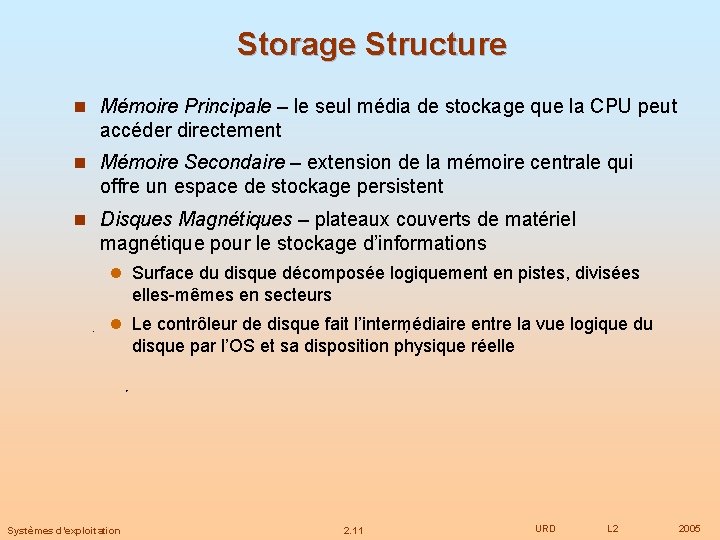

Storage Structure n Mémoire Principale – le seul média de stockage que la CPU peut accéder directement n Mémoire Secondaire – extension de la mémoire centrale qui offre un espace de stockage persistent n Disques Magnétiques – plateaux couverts de matériel magnétique pour le stockage d’informations l Surface du disque décomposée logiquement en pistes, divisées elles-mêmes en secteurs l Le contrôleur de disque fait l’intermédiaire entre la vue logique du disque par l’OS et sa disposition physique réelle Systèmes d’exploitation 2. 11 URD L 2 2005

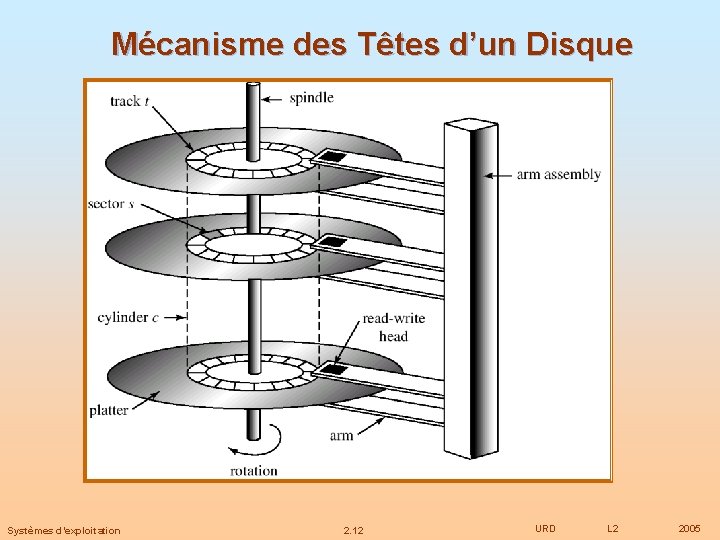

Mécanisme des Têtes d’un Disque Systèmes d’exploitation 2. 12 URD L 2 2005

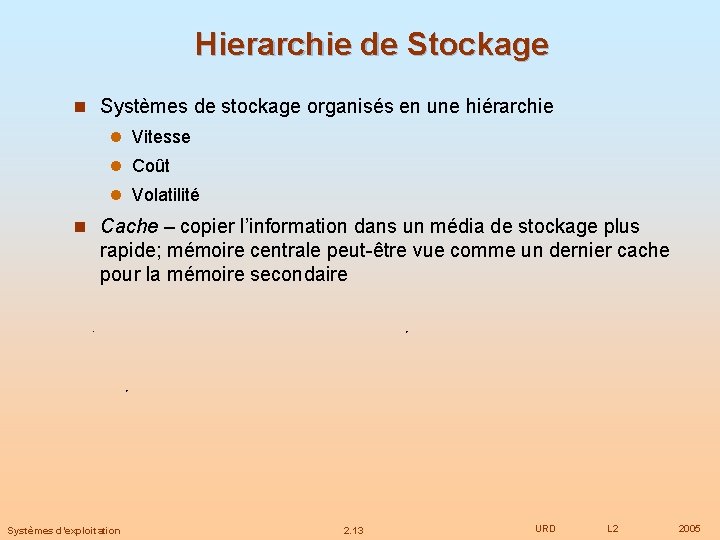

Hierarchie de Stockage n Systèmes de stockage organisés en une hiérarchie l Vitesse l Coût l Volatilité n Cache – copier l’information dans un média de stockage plus rapide; mémoire centrale peut-être vue comme un dernier cache pour la mémoire secondaire Systèmes d’exploitation 2. 13 URD L 2 2005

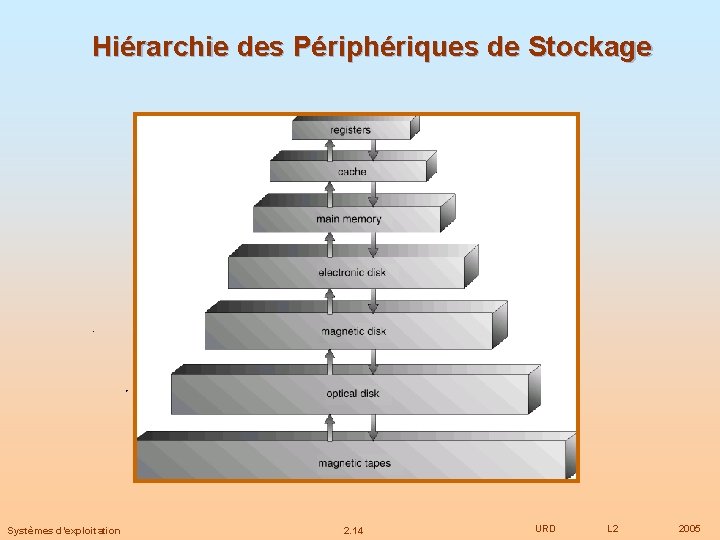

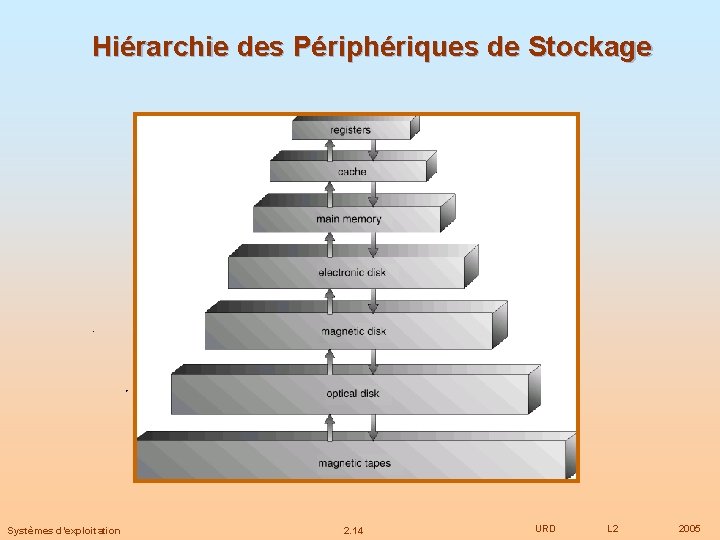

Hiérarchie des Périphériques de Stockage Systèmes d’exploitation 2. 14 URD L 2 2005

Cache n Utilisation d’une mémoire très rapide d’accès pour maintenir des informations dernièrement accédées n Besoin d’une polititque de gestion de cache n Le cache introduit un autre niveau de stockage l Besoin que les données stockées à plusieurs niveaux soient cohérents Systèmes d’exploitation 2. 15 URD L 2 2005

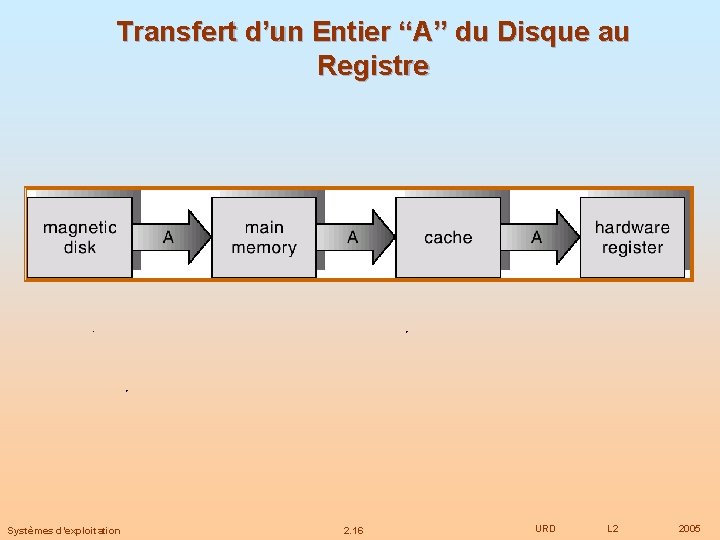

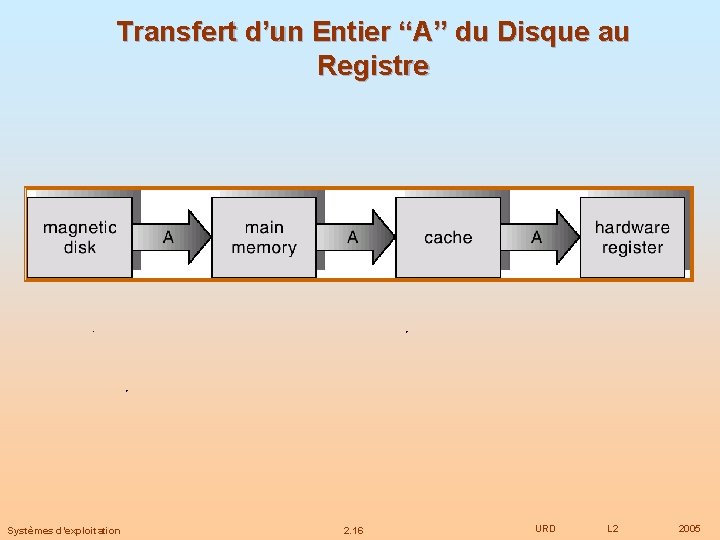

Transfert d’un Entier “A” du Disque au Registre Systèmes d’exploitation 2. 16 URD L 2 2005

Protection Matérielle n Opération en Mode Double n Protection E/S n Protection de la Mémoire n Protection CPU Systèmes d’exploitation 2. 17 URD L 2 2005

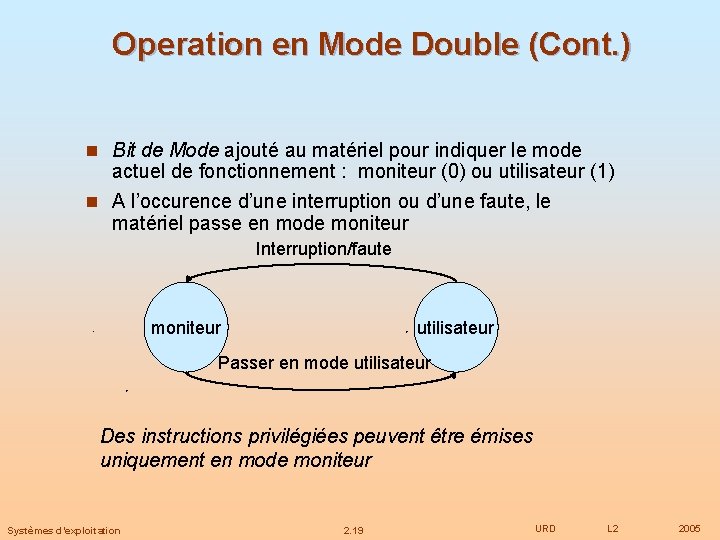

Operation en Mode Double n Le partage des ressources requiert que l’OS assure qu’un processus incorrect ou qu’un utilisateur se comportant mal ne puisse pas compromettre l’exécution des autres processus n Le système doit fournir un support matériel pour différencier au moins 2 modes d’opération 1. Mode Utilisateur – exécution en tant qu’utilisateur 2. Mode Moniteur (aussi Mode Noyau ou Mode Système) – exécution en tant qu’OS Systèmes d’exploitation 2. 18 URD L 2 2005

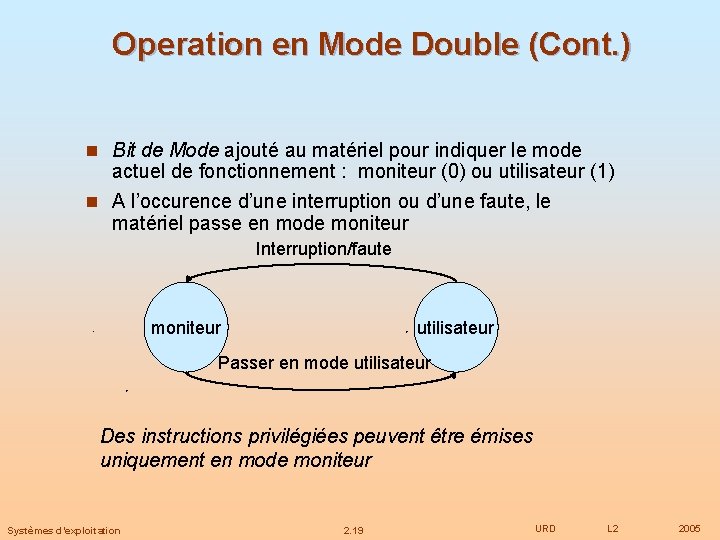

Operation en Mode Double (Cont. ) n Bit de Mode ajouté au matériel pour indiquer le mode actuel de fonctionnement : moniteur (0) ou utilisateur (1) n A l’occurence d’une interruption ou d’une faute, le matériel passe en mode moniteur Interruption/faute moniteur utilisateur Passer en mode utilisateur Des instructions privilégiées peuvent être émises uniquement en mode moniteur Systèmes d’exploitation 2. 19 URD L 2 2005

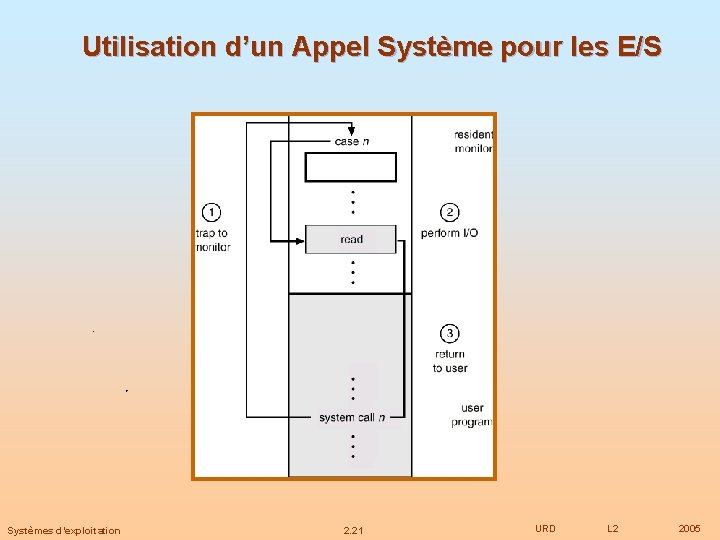

Protection E/S n Les instructions d’E/S sont des instructions privilégiées n Doit assurer qu’un processus utilisateur ne peut pas prendre le contrôle du système en mode moniteur (I. e. , un processus utilisateur qui essaye de placer dans le vecteur d’interruption l’adresse d’une fonction “louche” pour la gestion d’une interruption !) Systèmes d’exploitation 2. 20 URD L 2 2005

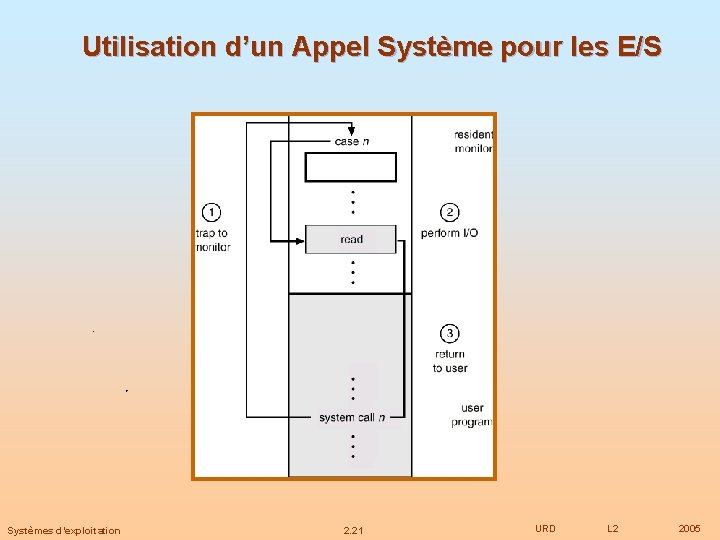

Utilisation d’un Appel Système pour les E/S Systèmes d’exploitation 2. 21 URD L 2 2005

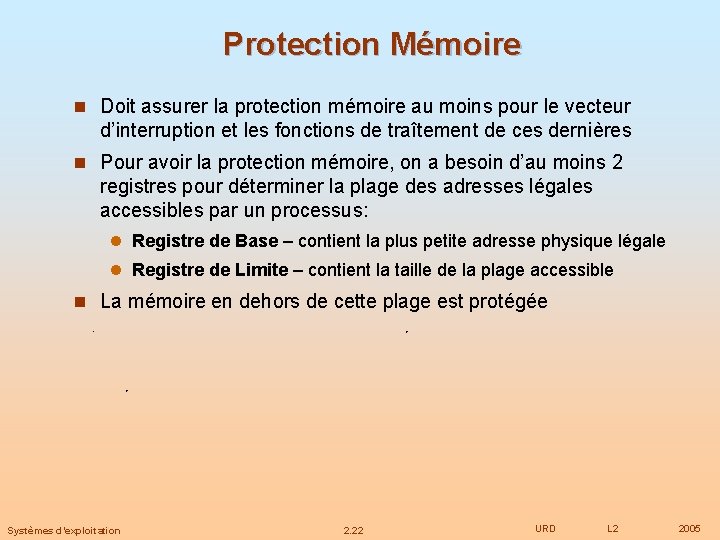

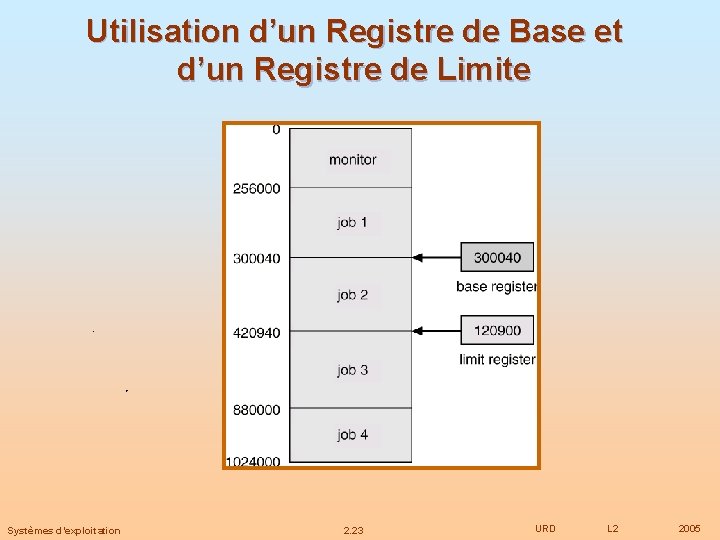

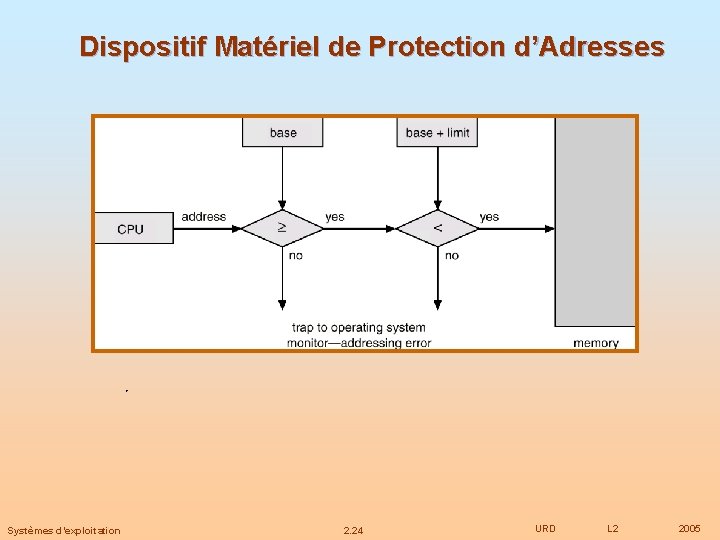

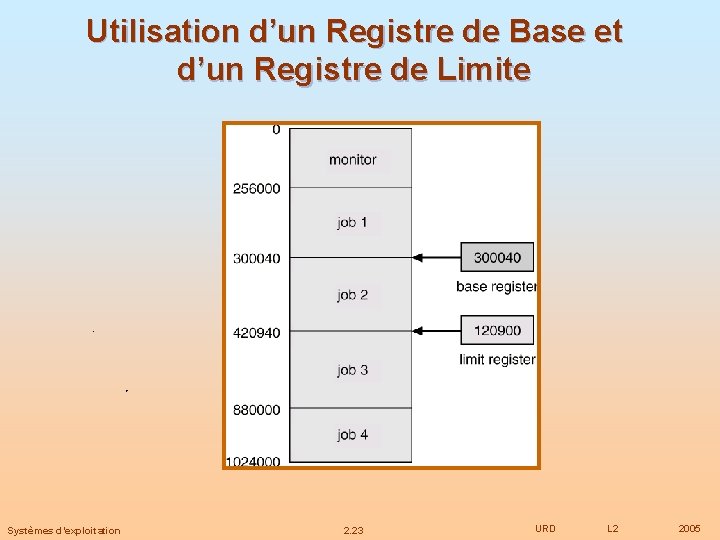

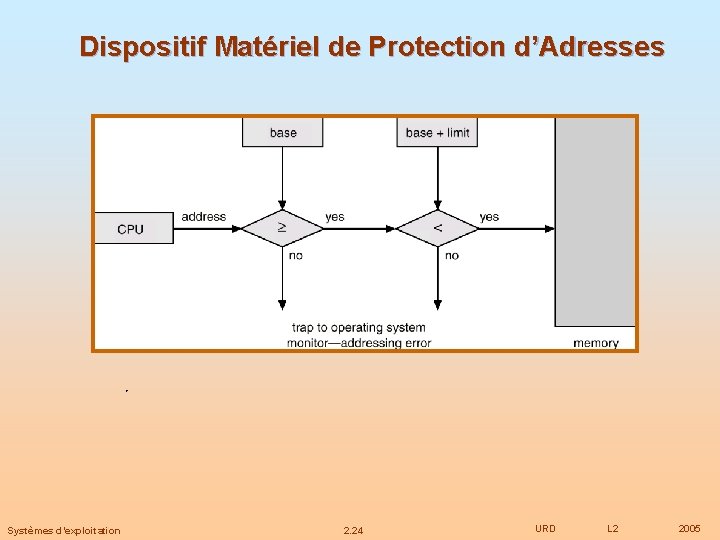

Protection Mémoire n Doit assurer la protection mémoire au moins pour le vecteur d’interruption et les fonctions de traîtement de ces dernières n Pour avoir la protection mémoire, on a besoin d’au moins 2 registres pour déterminer la plage des adresses légales accessibles par un processus: l Registre de Base – contient la plus petite adresse physique légale l Registre de Limite – contient la taille de la plage accessible n La mémoire en dehors de cette plage est protégée Systèmes d’exploitation 2. 22 URD L 2 2005

Utilisation d’un Registre de Base et d’un Registre de Limite Systèmes d’exploitation 2. 23 URD L 2 2005

Dispositif Matériel de Protection d’Adresses Systèmes d’exploitation 2. 24 URD L 2 2005

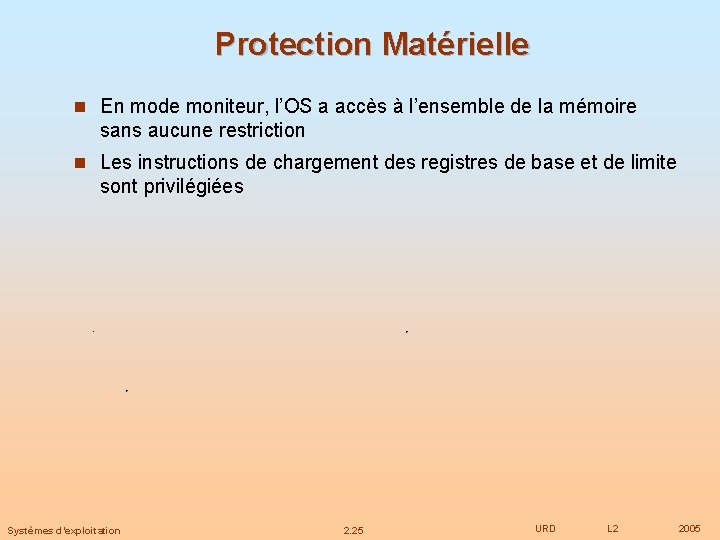

Protection Matérielle n En mode moniteur, l’OS a accès à l’ensemble de la mémoire sans aucune restriction n Les instructions de chargement des registres de base et de limite sont privilégiées Systèmes d’exploitation 2. 25 URD L 2 2005

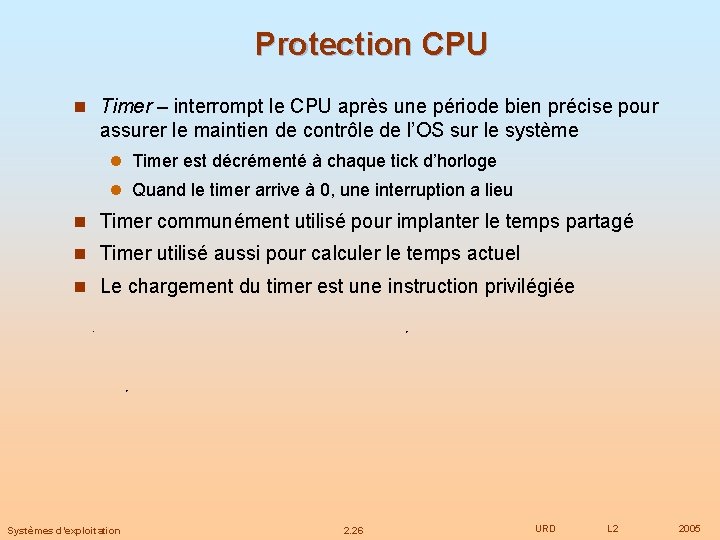

Protection CPU n Timer – interrompt le CPU après une période bien précise pour assurer le maintien de contrôle de l’OS sur le système l Timer est décrémenté à chaque tick d’horloge l Quand le timer arrive à 0, une interruption a lieu n Timer communément utilisé pour implanter le temps partagé n Timer utilisé aussi pour calculer le temps actuel n Le chargement du timer est une instruction privilégiée Systèmes d’exploitation 2. 26 URD L 2 2005

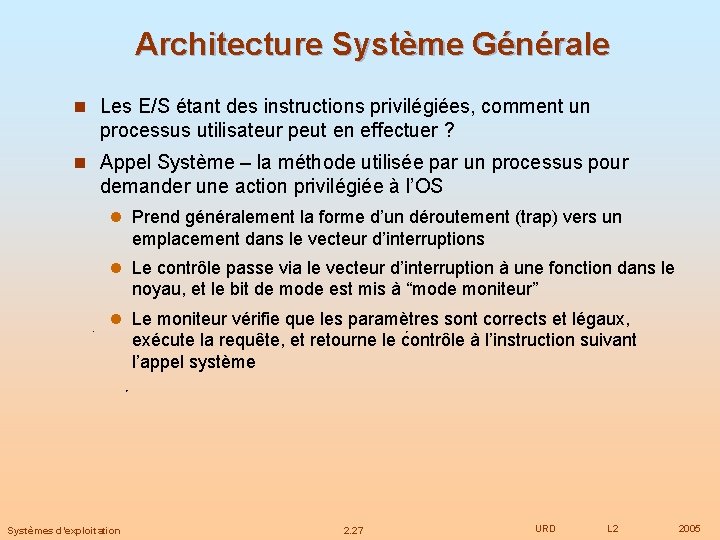

Architecture Système Générale n Les E/S étant des instructions privilégiées, comment un processus utilisateur peut en effectuer ? n Appel Système – la méthode utilisée par un processus pour demander une action privilégiée à l’OS l Prend généralement la forme d’un déroutement (trap) vers un emplacement dans le vecteur d’interruptions l Le contrôle passe via le vecteur d’interruption à une fonction dans le noyau, et le bit de mode est mis à “mode moniteur” l Le moniteur vérifie que les paramètres sont corrects et légaux, exécute la requête, et retourne le contrôle à l’instruction suivant l’appel système Systèmes d’exploitation 2. 27 URD L 2 2005

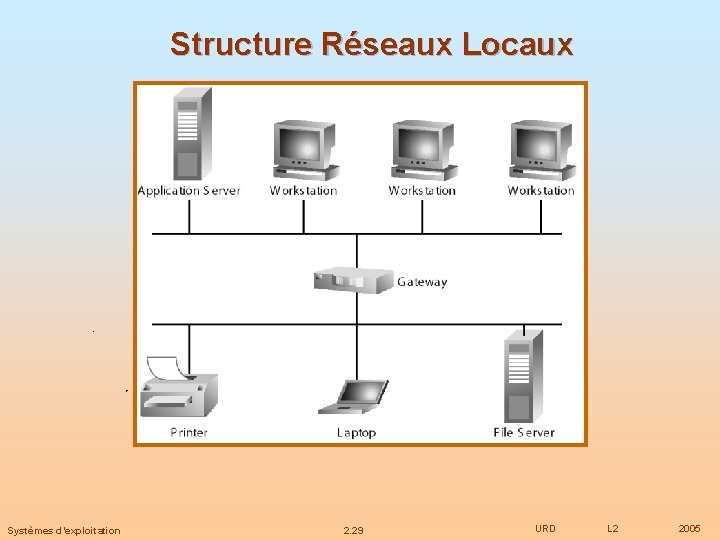

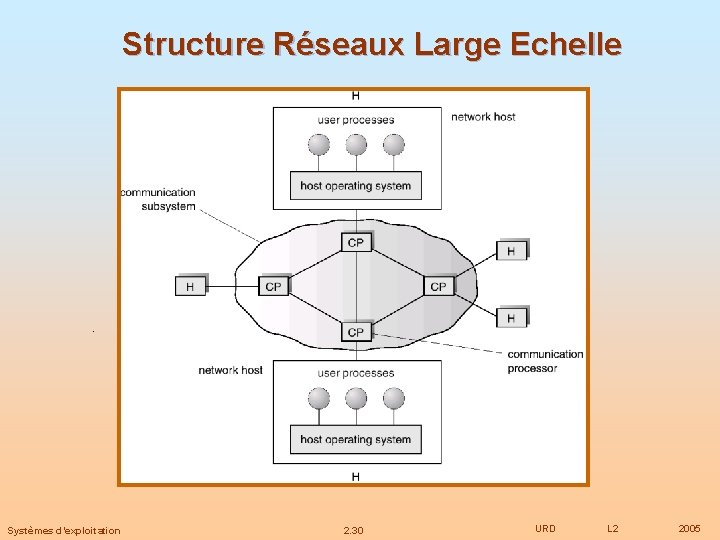

Structure Réseau n Réseau Local (LAN) n Réseau Large Echelle (WAN) Systèmes d’exploitation 2. 28 URD L 2 2005

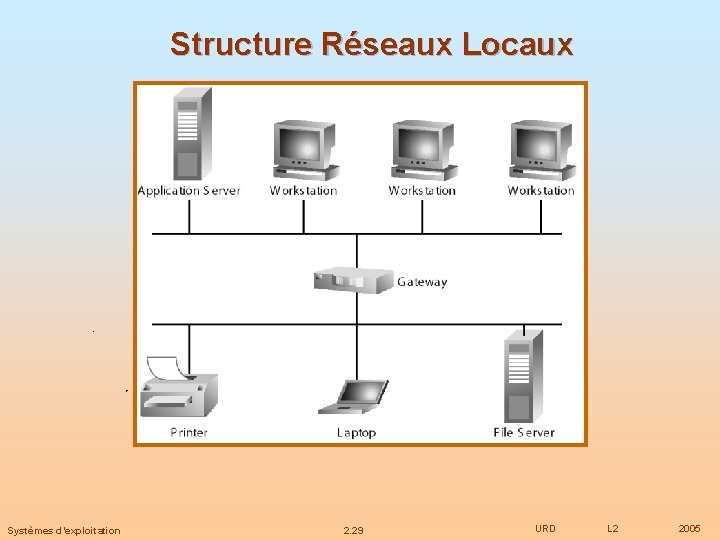

Structure Réseaux Locaux Systèmes d’exploitation 2. 29 URD L 2 2005

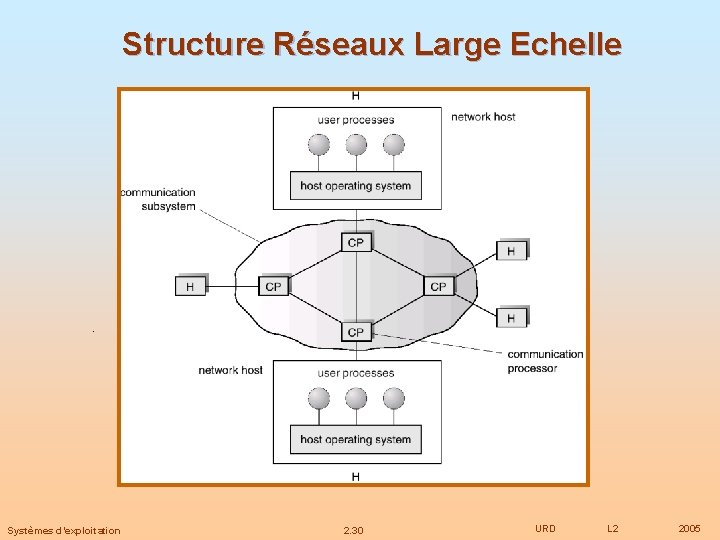

Structure Réseaux Large Echelle Systèmes d’exploitation 2. 30 URD L 2 2005