STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTIONS

- Slides: 34

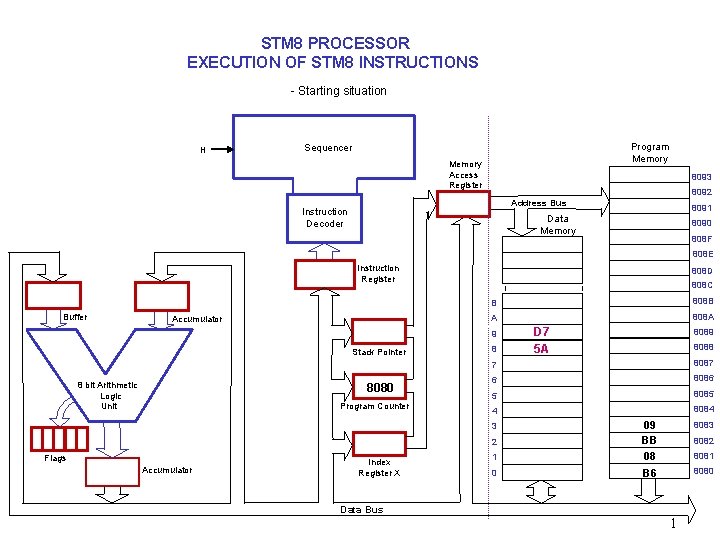

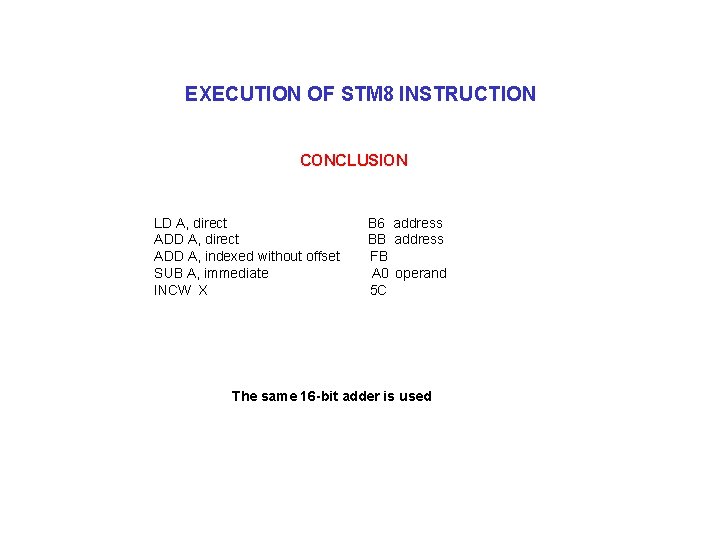

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTIONS - Starting situation H Program Memory Sequencer Memory Access Register 8093 8092 Address Bus Instruction Decoder 8091 Data Memory 8090 808 F 808 E Instruction Register Buffer Accumulator 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8 bit Arithmetic Logic Unit 8080 Program Counter 8 Accumulator 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 Data Bus 1

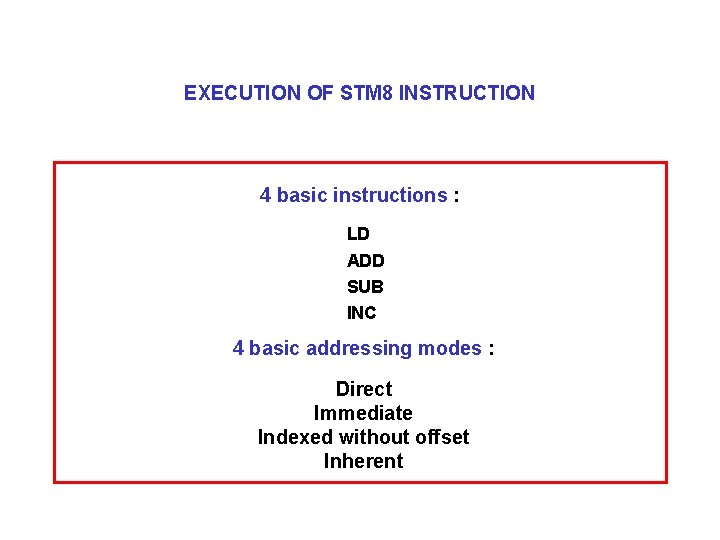

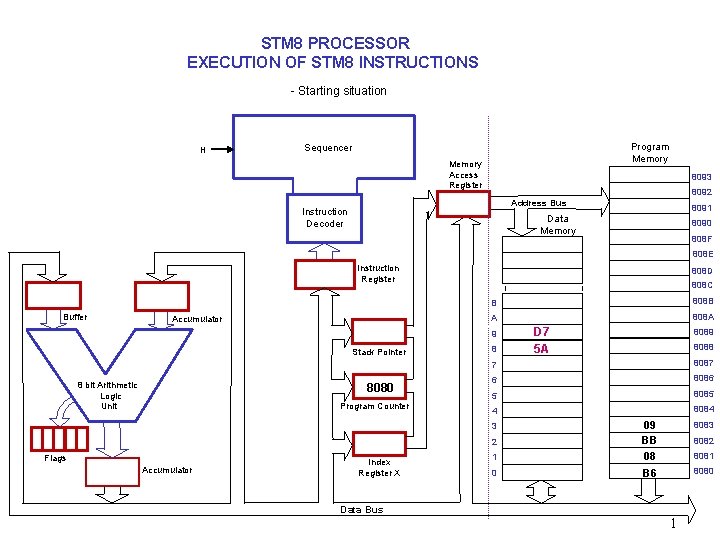

EXECUTION OF STM 8 INSTRUCTION 4 basic instructions : LD ADD SUB INC 4 basic addressing modes : Direct Immediate Indexed without offset Inherent

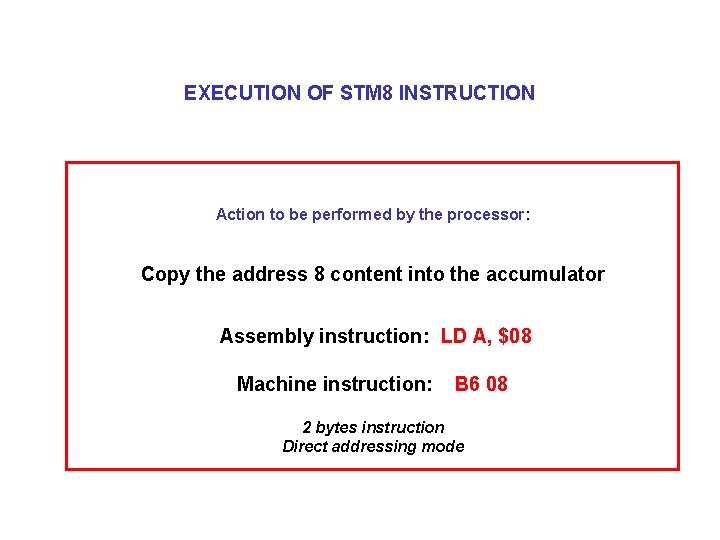

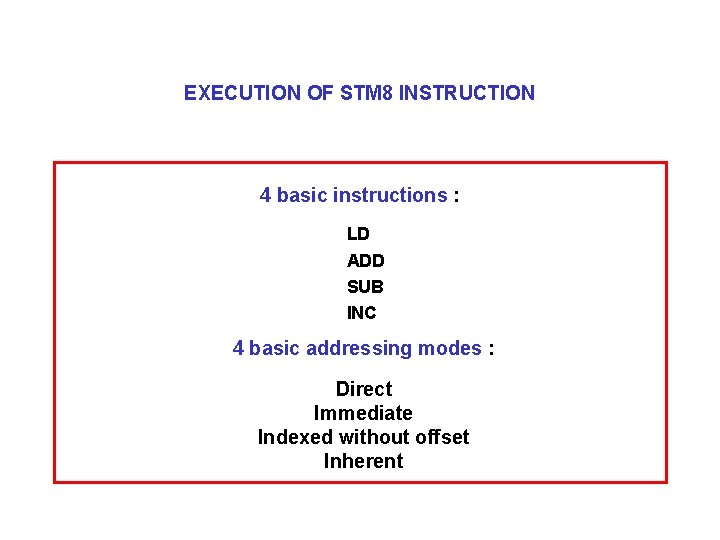

EXECUTION OF STM 8 INSTRUCTION Action to be performed by the processor: Copy the address 8 content into the accumulator Assembly instruction: LD A, $08 Machine instruction: B 6 08 2 bytes instruction Direct addressing mode

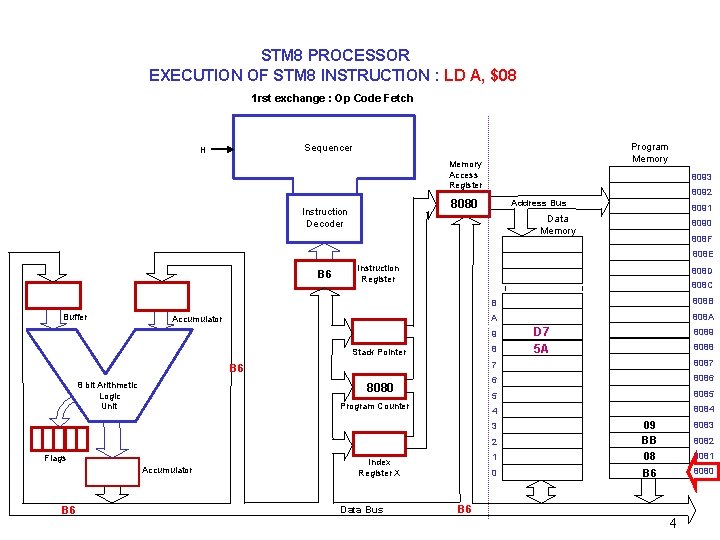

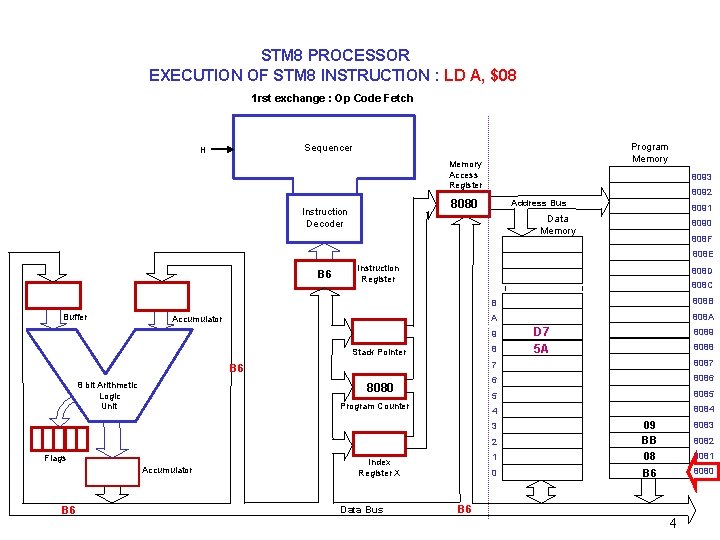

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : LD A, $08 1 rst exchange : Op Code Fetch Program Memory Sequencer H Memory Access Register 8093 8092 8080 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E B 6 Buffer Instruction Register 808 D 808 C Accumulator B 808 B A 808 A 9 8 Stack Pointer B 6 8 bit Arithmetic Logic Unit 8080 Program Counter Accumulator B 6 Data Bus B 6 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 4

C

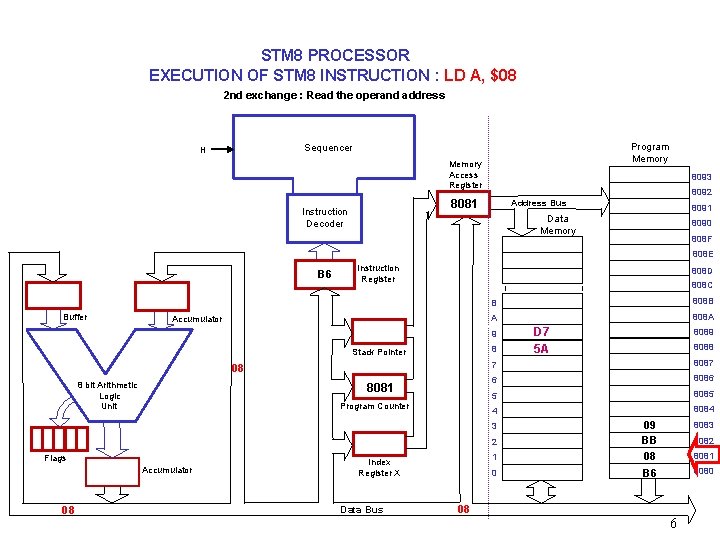

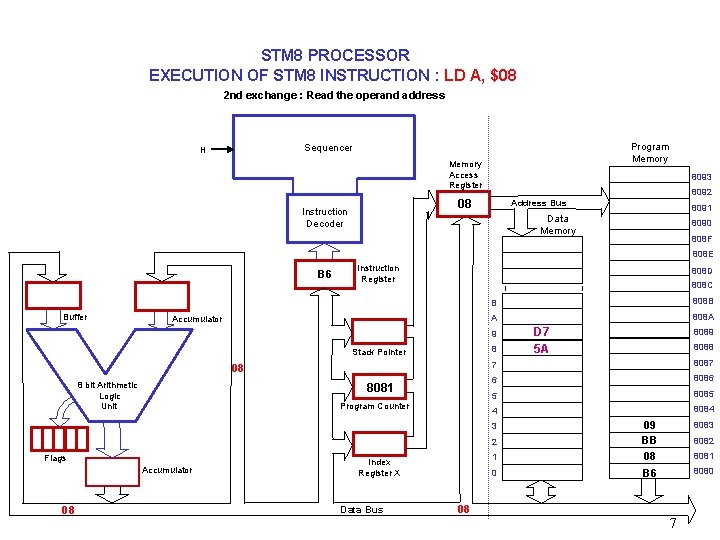

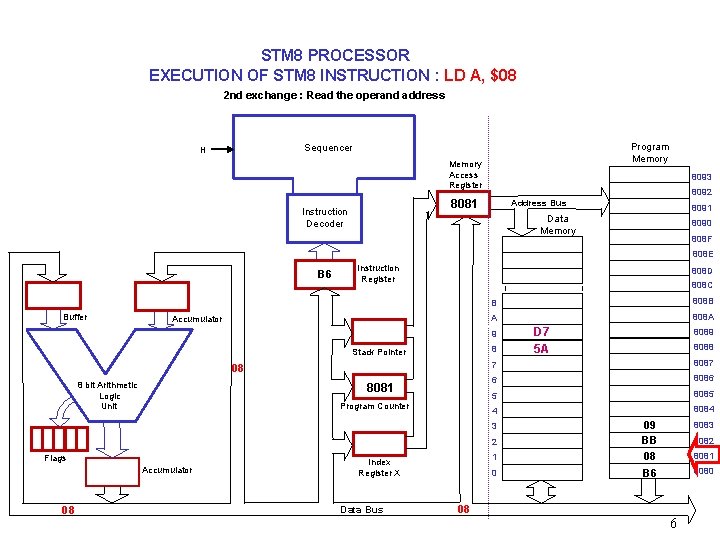

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : LD A, $08 2 nd exchange : Read the operand address Program Memory Sequencer H Memory Access Register 8093 8092 8081 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E B 6 Buffer Instruction Register 808 D 808 C Accumulator B 808 B A 808 A 9 8 Stack Pointer 08 8 bit Arithmetic Logic Unit 8081 Program Counter Accumulator 08 Data Bus 08 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 6

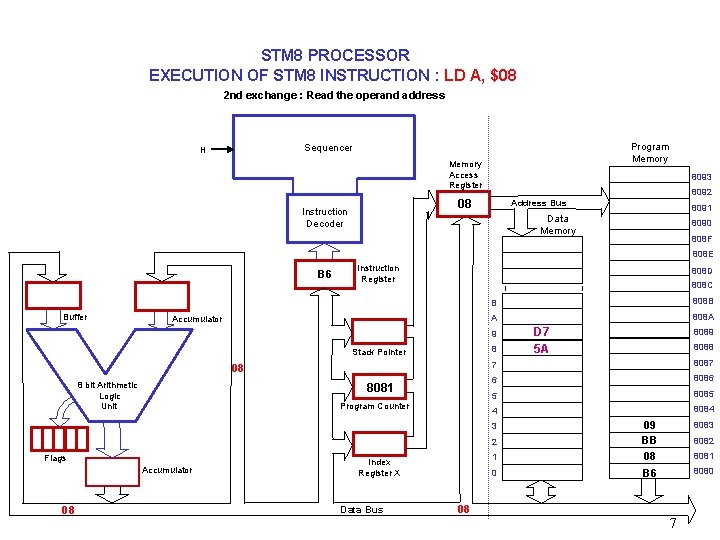

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : LD A, $08 2 nd exchange : Read the operand address Program Memory Sequencer H Memory Access Register 8093 8092 08 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E B 6 Buffer Instruction Register 808 D 808 C Accumulator B 808 B A 808 A 9 8 Stack Pointer 08 8 bit Arithmetic Logic Unit 8081 Program Counter Accumulator 08 Data Bus 08 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 7

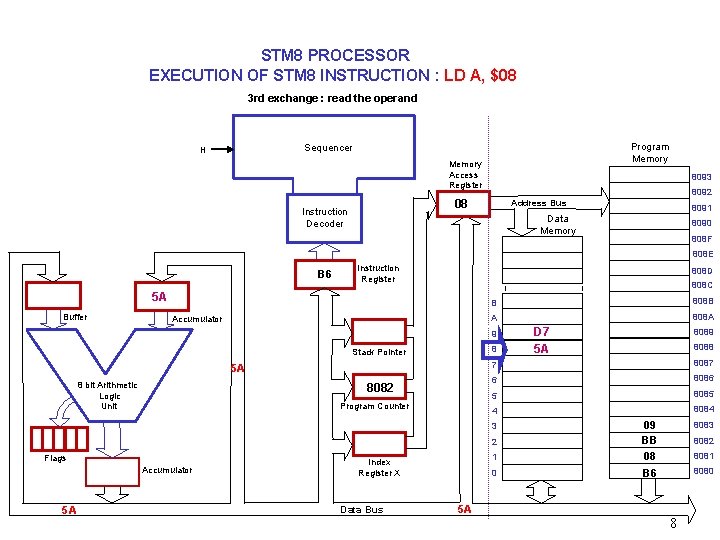

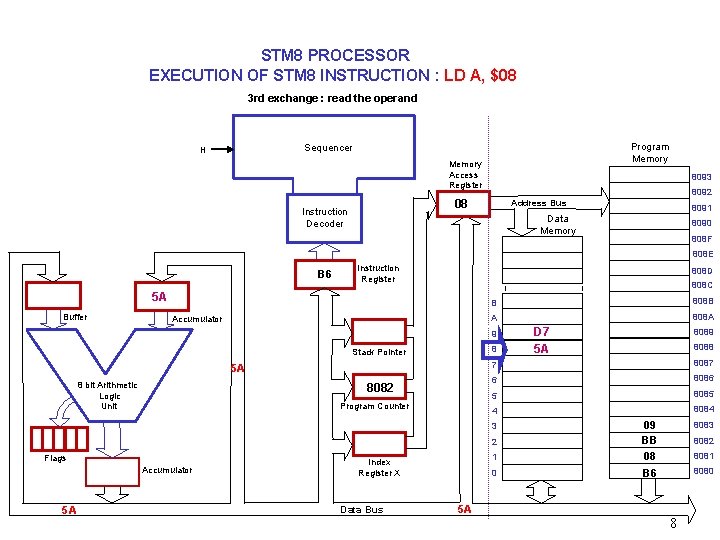

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : LD A, $08 3 rd exchange : read the operand Program Memory Sequencer H Memory Access Register 8093 8092 08 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E B 6 Instruction Register 808 D 808 C 5 A Buffer Accumulator B 808 B A 808 A 9 8 Stack Pointer 5 A 8 bit Arithmetic Logic Unit 8082 Program Counter Accumulator 5 A Data Bus 5 A 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 8

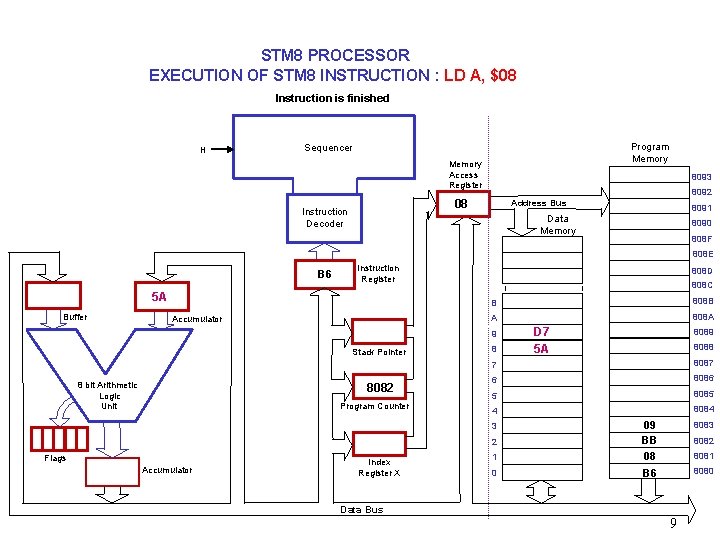

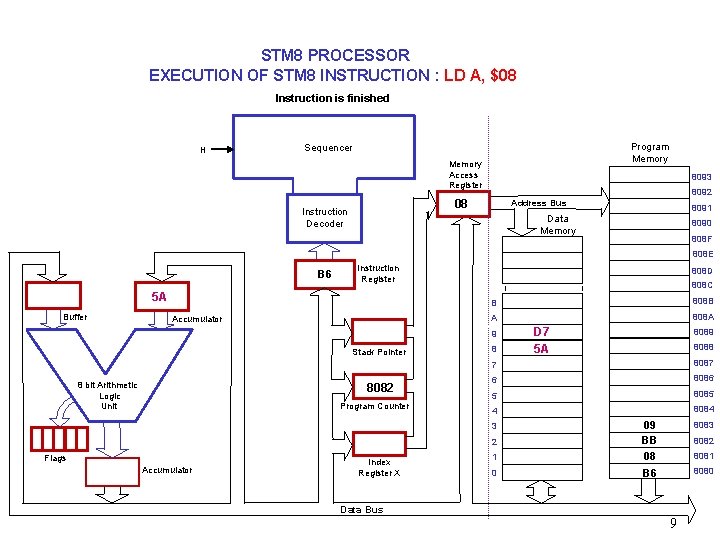

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : LD A, $08 Instruction is finished H Program Memory Sequencer Memory Access Register 8093 8092 08 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E B 6 Instruction Register 5 A Buffer Accumulator 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8 bit Arithmetic Logic Unit 8082 Program Counter 8 Accumulator 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 Data Bus 9

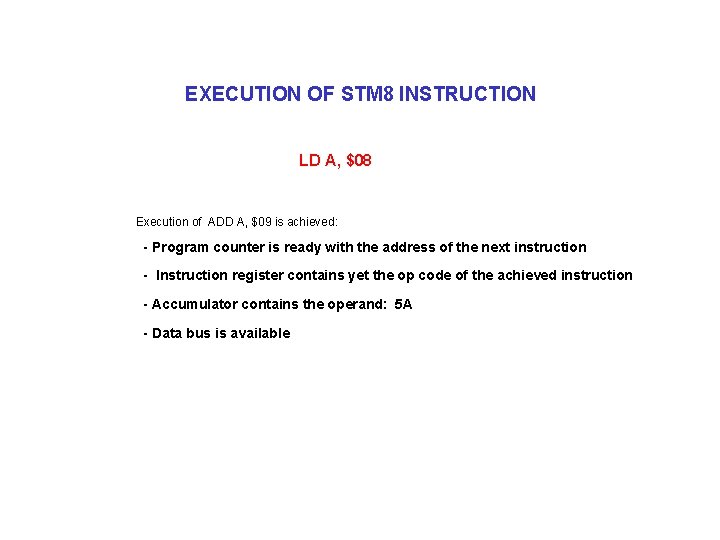

EXECUTION OF STM 8 INSTRUCTION LD A, $08 Execution of ADD A, $09 is achieved: - Program counter is ready with the address of the next instruction - Instruction register contains yet the op code of the achieved instruction - Accumulator contains the operand: 5 A - Data bus is available

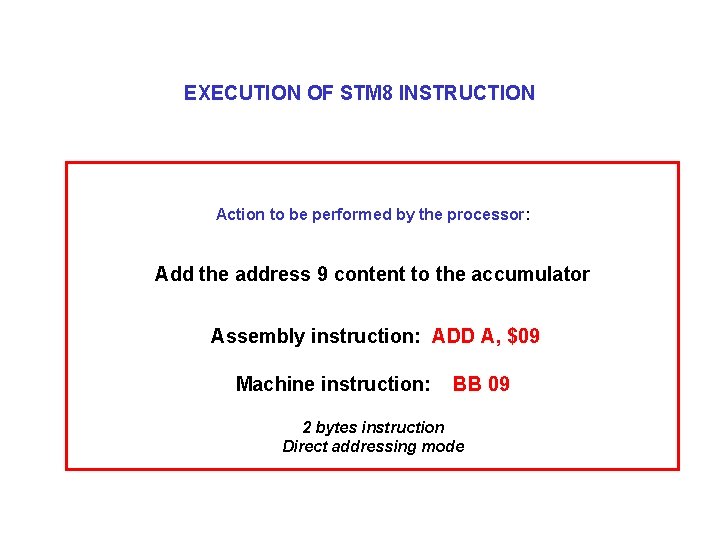

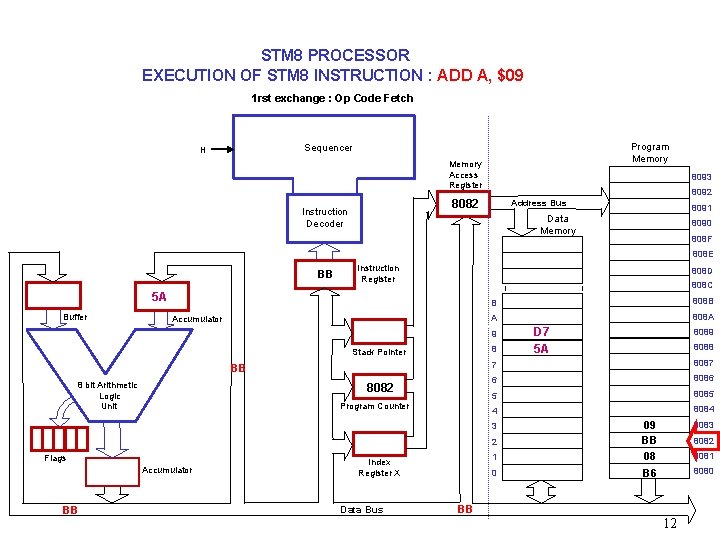

EXECUTION OF STM 8 INSTRUCTION Action to be performed by the processor: Add the address 9 content to the accumulator Assembly instruction: ADD A, $09 Machine instruction: BB 09 2 bytes instruction Direct addressing mode

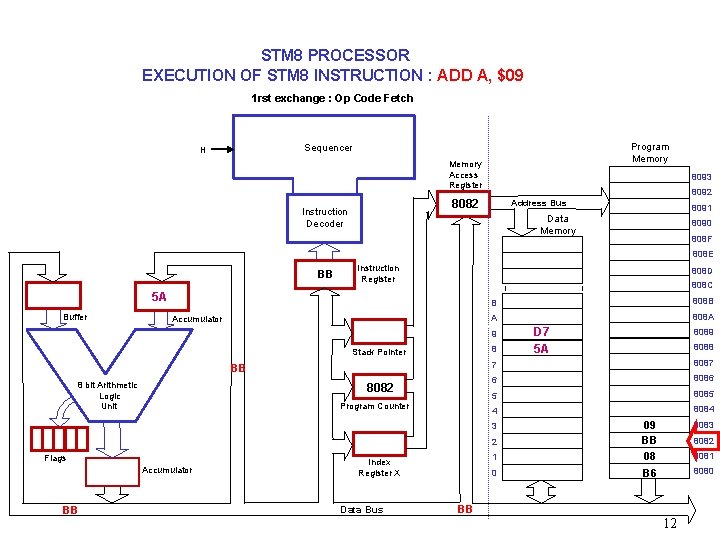

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, $09 1 rst exchange : Op Code Fetch Program Memory Sequencer H Memory Access Register 8093 8092 8082 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E BB Instruction Register 808 D 808 C 5 A Buffer Accumulator B 808 B A 808 A 9 8 Stack Pointer BB 8 bit Arithmetic Logic Unit 8082 Program Counter Accumulator BB Data Bus BB 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 12

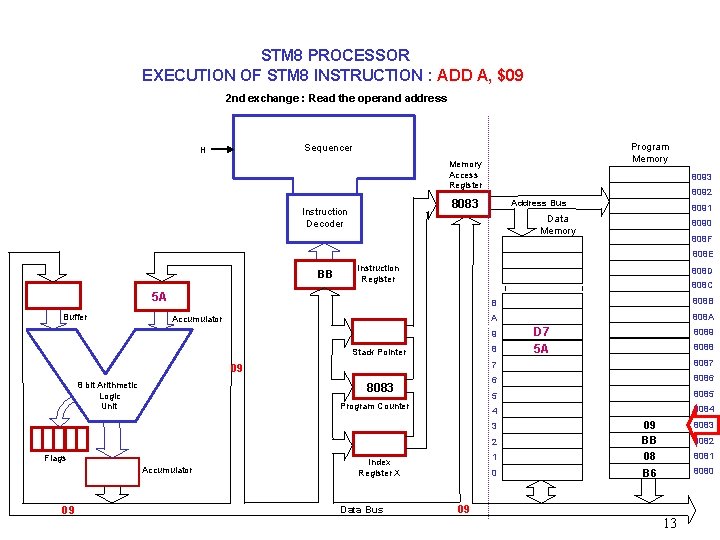

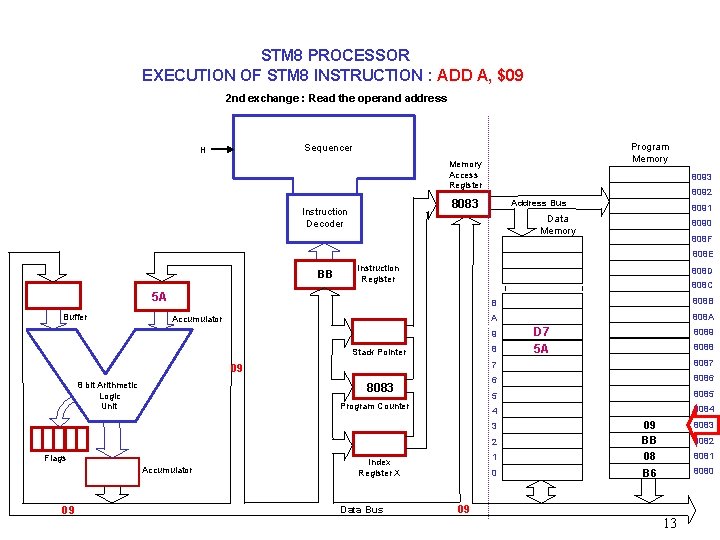

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, $09 2 nd exchange : Read the operand address Program Memory Sequencer H Memory Access Register 8093 8092 8083 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E BB Instruction Register 808 D 808 C 5 A Buffer Accumulator B 808 B A 808 A 9 8 Stack Pointer 09 8 bit Arithmetic Logic Unit 8083 Program Counter Accumulator 09 Data Bus 09 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 13

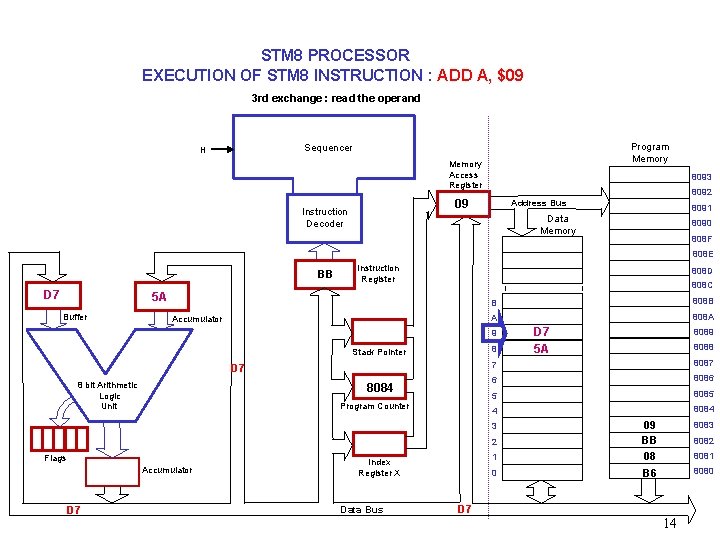

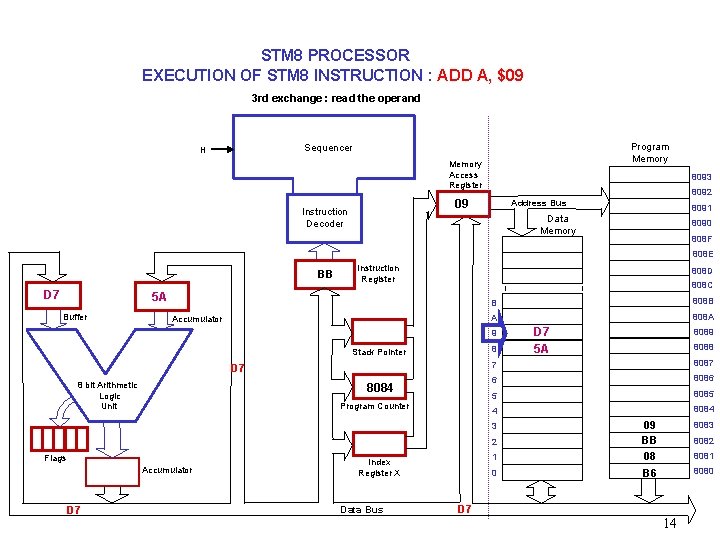

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, $09 3 rd exchange : read the operand Program Memory Sequencer H Memory Access Register 8093 8092 09 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E BB D 7 Instruction Register 808 D 808 C 5 A Buffer Accumulator B 808 B A 808 A 9 8 Stack Pointer D 7 8 bit Arithmetic Logic Unit 8084 Program Counter Accumulator D 7 Data Bus D 7 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Index Register X 8089 7 3 Flags D 7 5 A 8083 8081 14

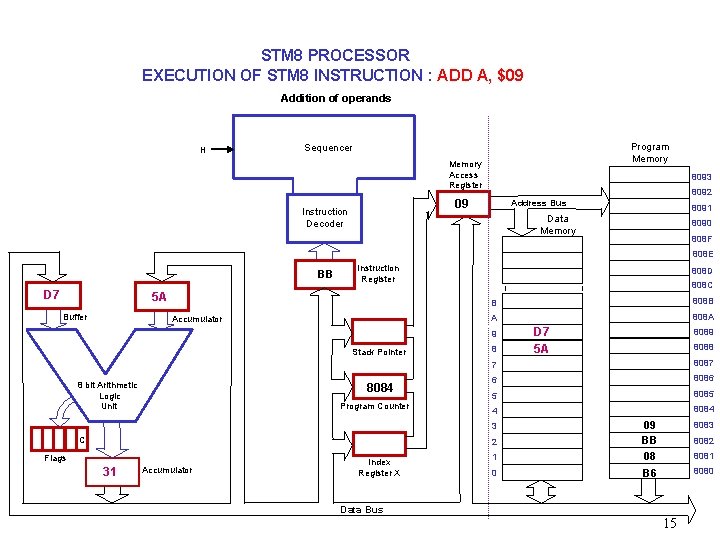

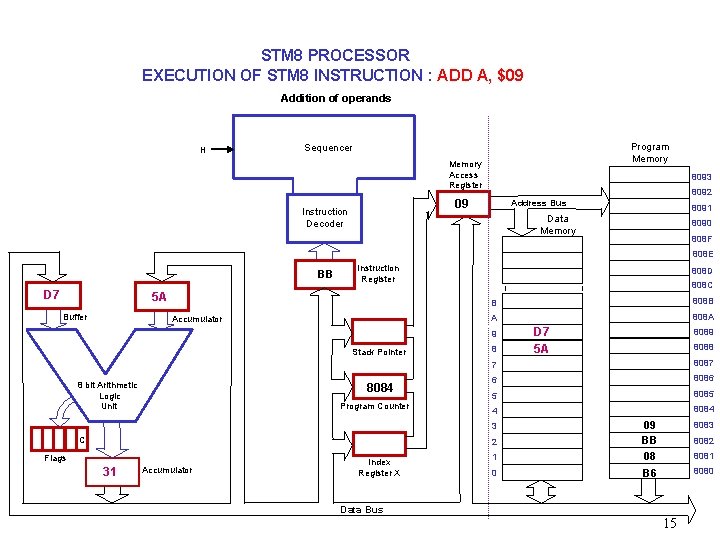

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, $09 Addition of operands H Program Memory Sequencer Memory Access Register 8093 8092 09 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E BB D 7 Instruction Register 5 A Buffer Accumulator 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8 bit Arithmetic Logic Unit 8084 Program Counter 8 31 Accumulator Index Register X 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Flags 8089 7 3 C D 7 5 A 8083 8081 Data Bus 15

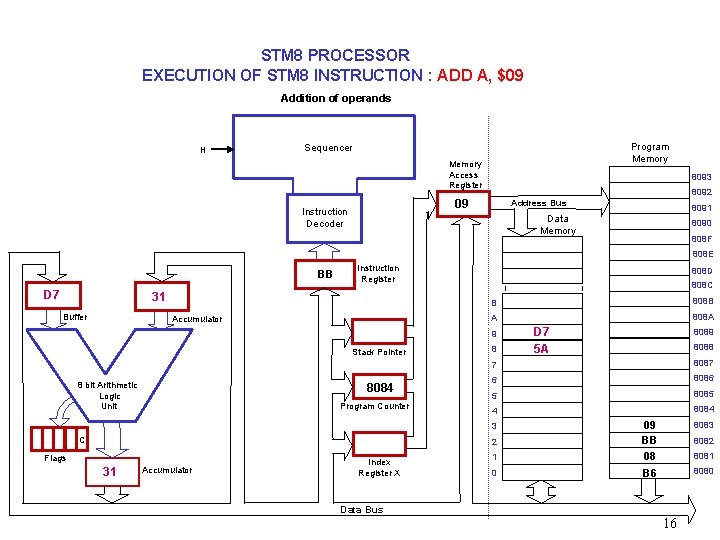

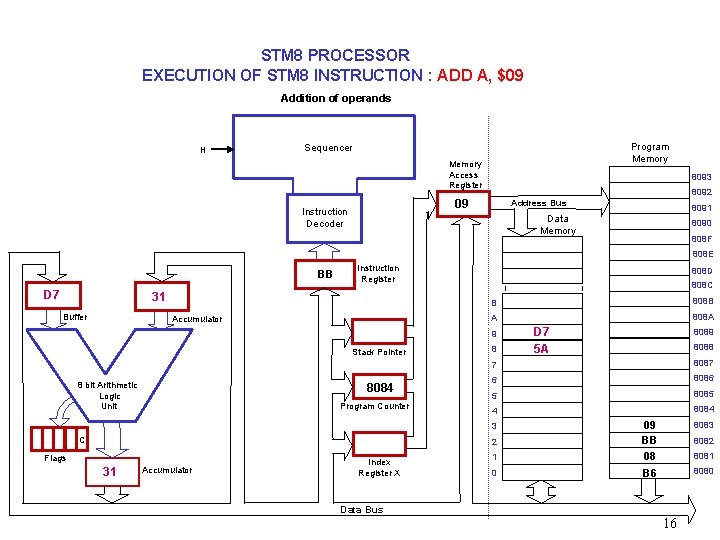

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, $09 Addition of operands H Program Memory Sequencer Memory Access Register 8093 8092 09 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E BB D 7 Instruction Register 31 Buffer Accumulator 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8 bit Arithmetic Logic Unit 8084 Program Counter 8 31 Accumulator Index Register X 8088 8087 6 8086 5 8085 4 8082 1 09 BB 08 0 B 6 8080 2 Flags 8089 7 3 C D 7 5 A 8083 8081 Data Bus 16

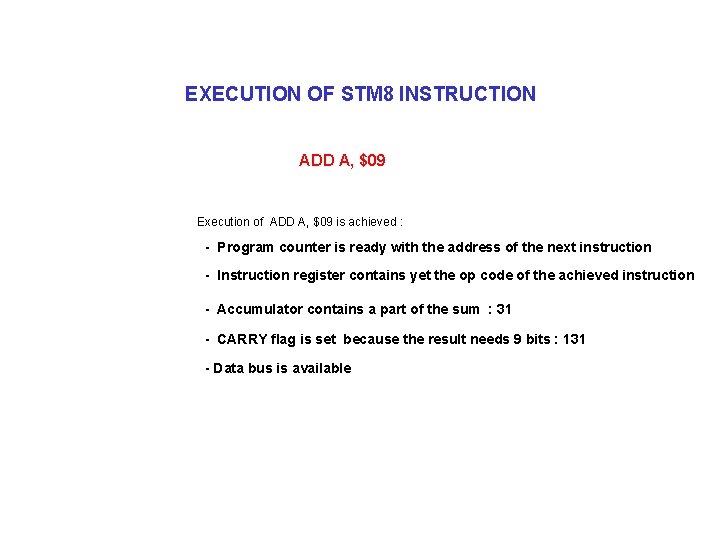

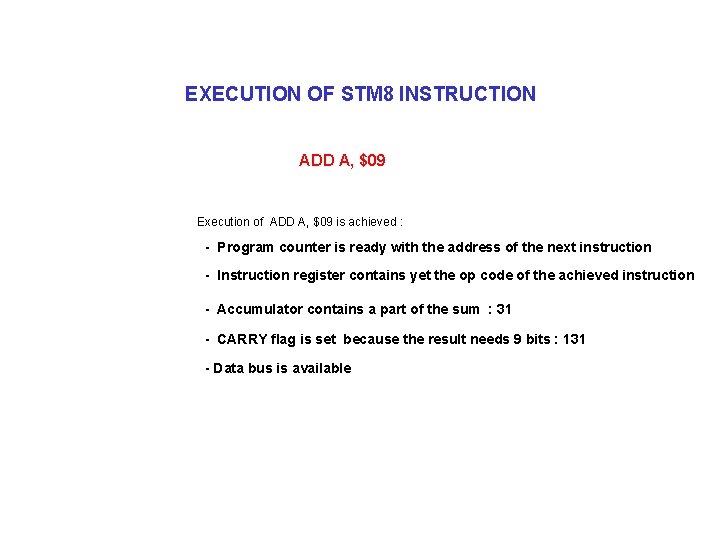

EXECUTION OF STM 8 INSTRUCTION ADD A, $09 Execution of ADD A, $09 is achieved : - Program counter is ready with the address of the next instruction - Instruction register contains yet the op code of the achieved instruction - Accumulator contains a part of the sum : 31 - CARRY flag is set because the result needs 9 bits : 131 - Data bus is available

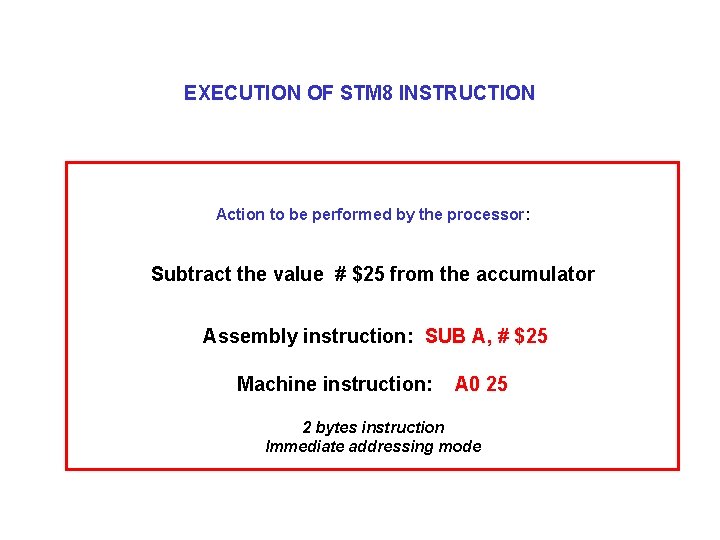

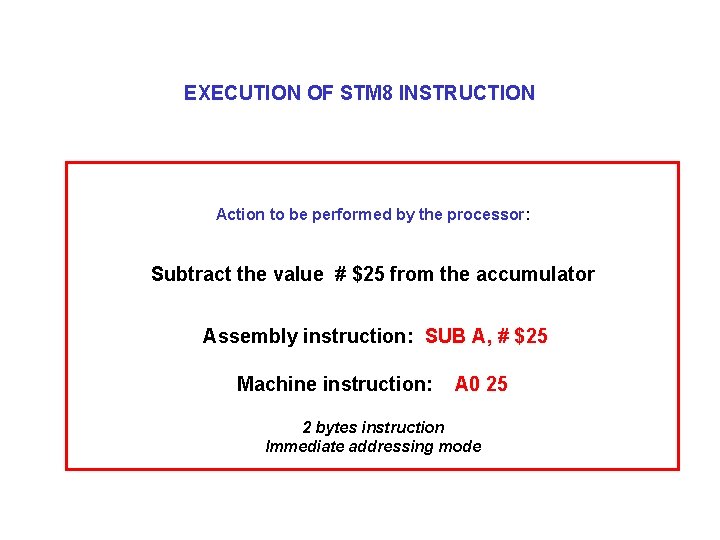

EXECUTION OF STM 8 INSTRUCTION Action to be performed by the processor: Subtract the value # $25 from the accumulator Assembly instruction: SUB A, # $25 Machine instruction: A 0 25 2 bytes instruction Immediate addressing mode

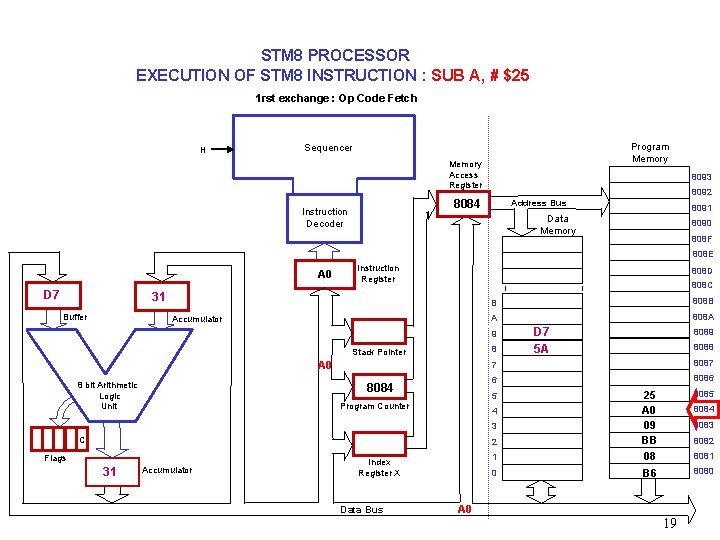

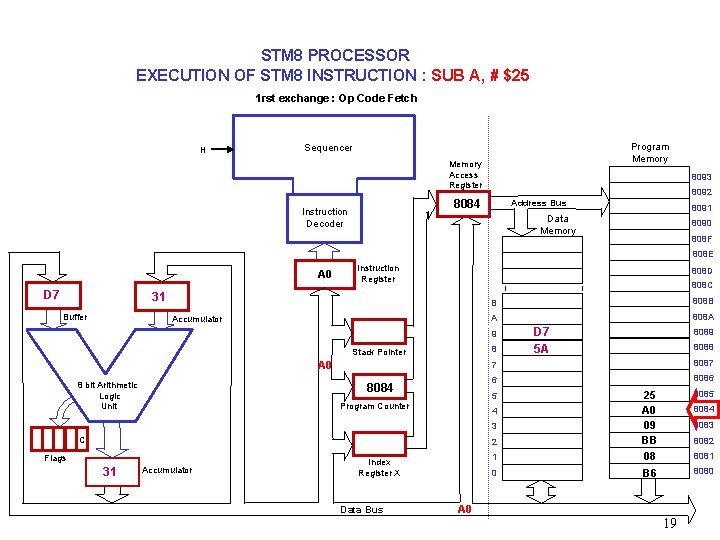

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : SUB A, # $25 1 rst exchange : Op Code Fetch H Program Memory Sequencer Memory Access Register 8093 8092 8084 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E A 0 D 7 Instruction Register 808 D 808 C 31 Buffer Accumulator B 808 B A 808 A 9 8 Stack Pointer A 0 8 bit Arithmetic Logic Unit 8084 6 8086 1 25 A 0 09 BB 08 0 B 6 3 2 Flags 31 Accumulator Index Register X Data Bus A 0 8088 8087 4 C 8089 7 5 Program Counter D 7 5 A 8085 8084 8083 8082 8081 8080 19

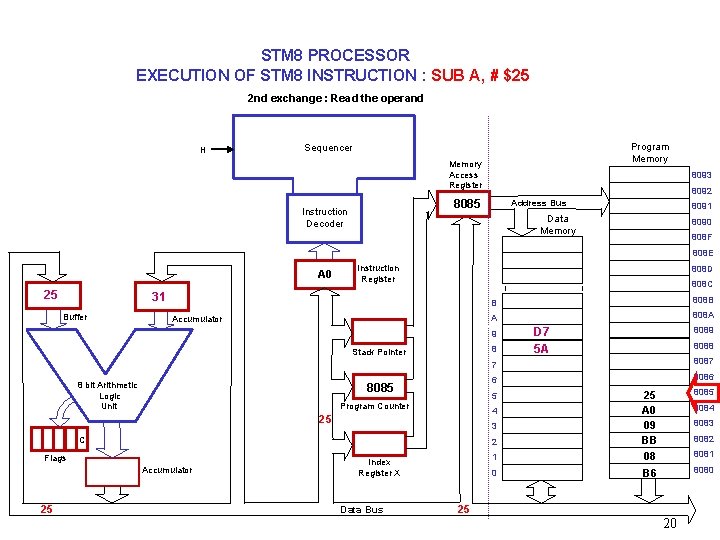

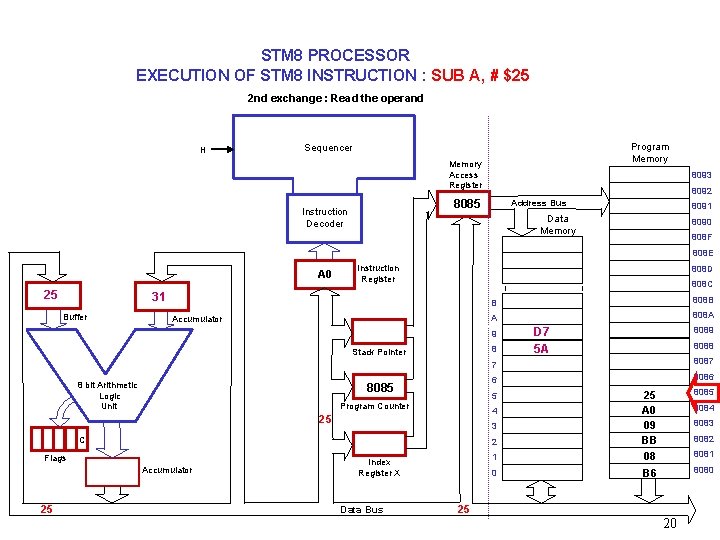

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : SUB A, # $25 2 nd exchange : Read the operand H Program Memory Sequencer Memory Access Register 8093 8092 8085 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E A 0 25 Instruction Register 808 D 808 C 31 Buffer Accumulator B 808 B A 808 A 9 8 Stack Pointer 8 bit Arithmetic Logic Unit 8085 Program Counter 6 8086 1 25 A 0 09 BB 08 0 B 6 3 2 Flags Accumulator 25 8087 4 C Index Register X Data Bus 25 8088 7 5 25 8089 D 7 5 A 8085 8084 8083 8082 8081 8080 20

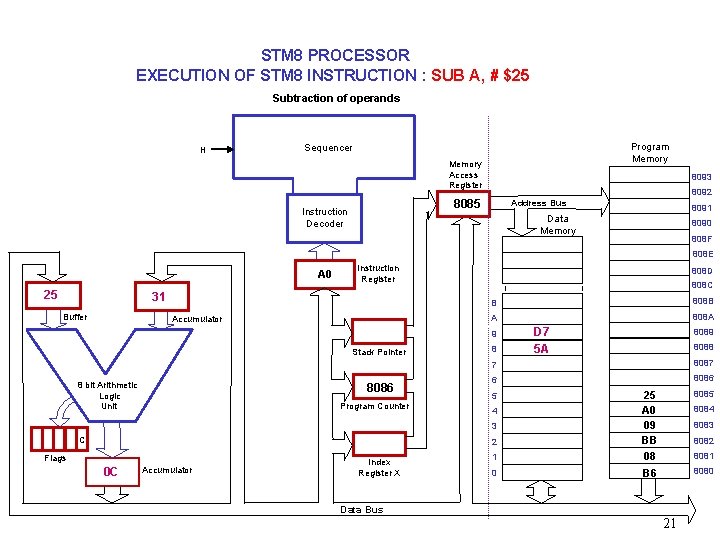

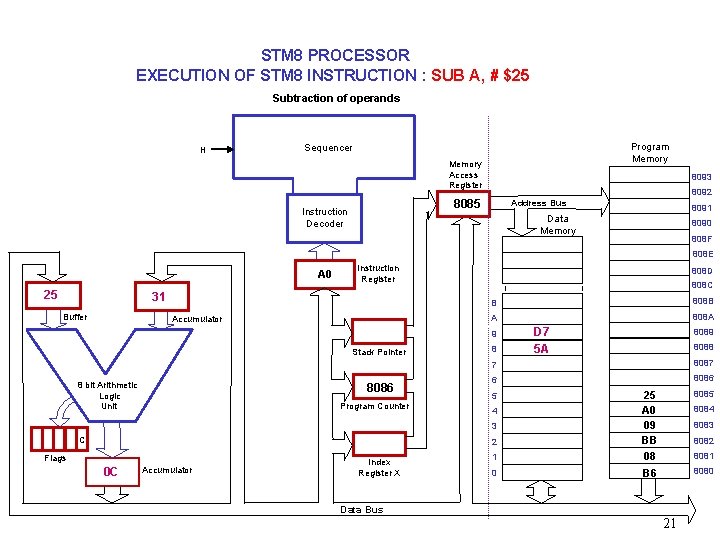

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : SUB A, # $25 Subtraction of operands H Program Memory Sequencer Memory Access Register 8093 8092 8085 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E A 0 25 Instruction Register 31 Buffer Accumulator 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8 bit Arithmetic Logic Unit 8086 Program Counter 8 0 C Accumulator Index Register X 8088 8087 6 8086 1 25 A 0 09 BB 08 0 B 6 5 4 2 Flags 8089 7 3 C D 7 5 A 8085 8084 8083 8082 8081 8080 Data Bus 21

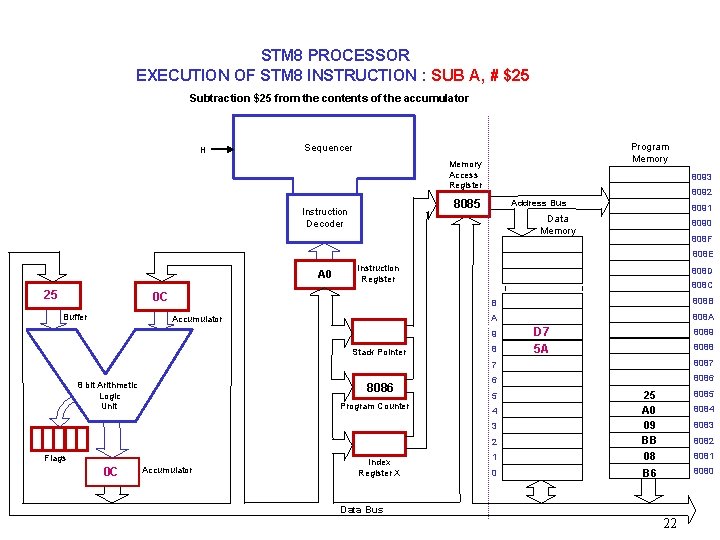

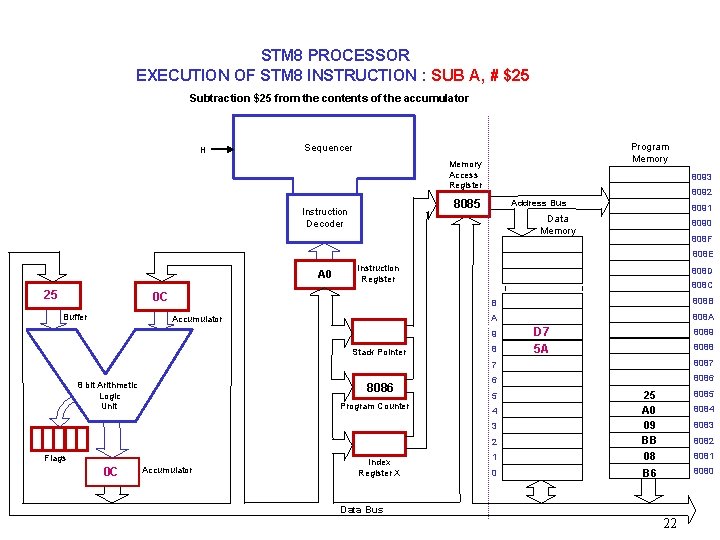

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : SUB A, # $25 Subtraction $25 from the contents of the accumulator H Program Memory Sequencer Memory Access Register 8093 8092 8085 Instruction Decoder Address Bus 8091 Data Memory 8090 808 F 808 E A 0 25 Instruction Register 0 C Buffer Accumulator 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8 bit Arithmetic Logic Unit 8086 Program Counter 8 0 C Accumulator 8088 8087 6 8086 1 25 A 0 09 BB 08 0 B 6 5 4 2 Index Register X 8089 7 3 Flags D 7 5 A 8085 8084 8083 8082 8081 8080 Data Bus 22

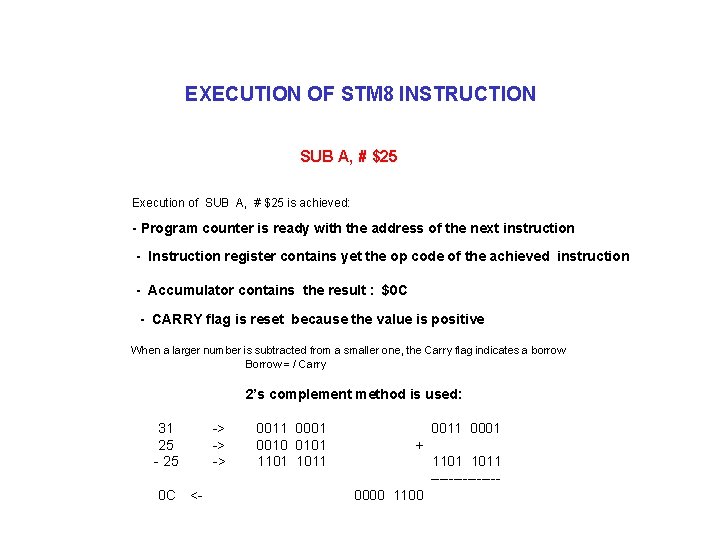

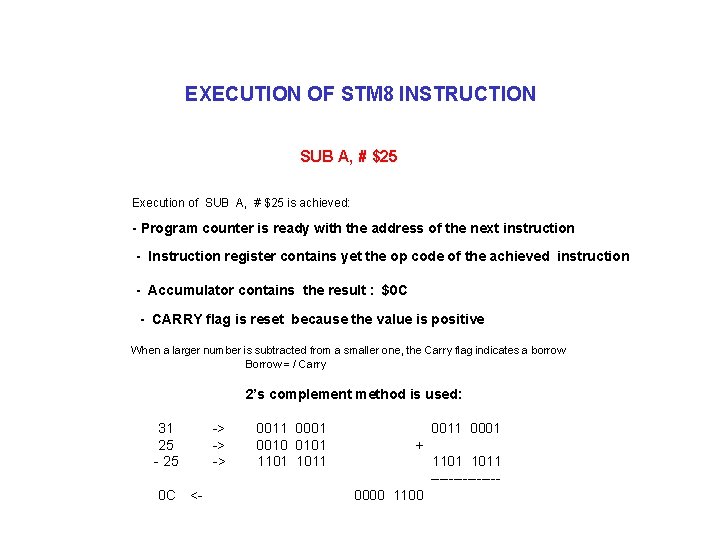

EXECUTION OF STM 8 INSTRUCTION SUB A, # $25 Execution of SUB A, # $25 is achieved: - Program counter is ready with the address of the next instruction - Instruction register contains yet the op code of the achieved instruction - Accumulator contains the result : $0 C - CARRY flag is reset because the value is positive When a larger number is subtracted from a smaller one, the Carry flag indicates a borrow Borrow = / Carry 2’s complement method is used: 31 25 - 25 0 C <- -> -> -> 0011 0001 0010 0101 1011 0001 + 1101 1011 -------0000 1100

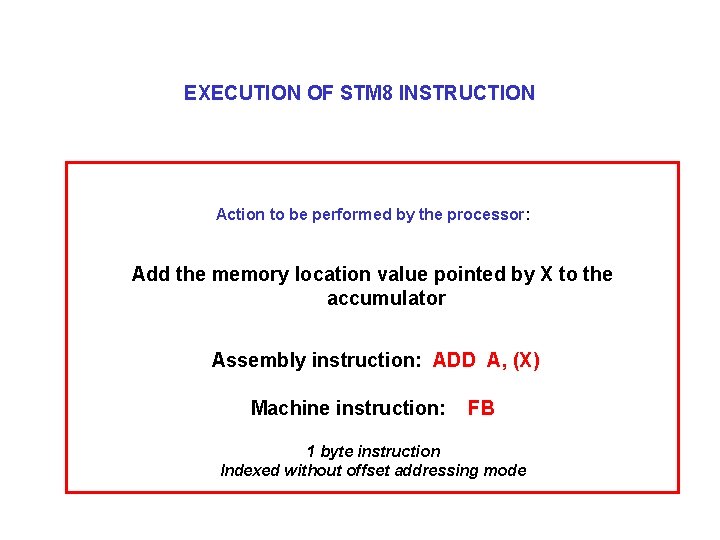

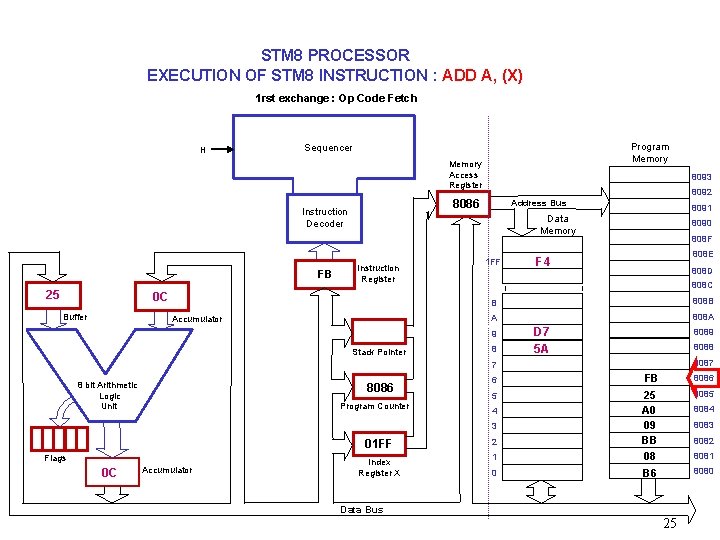

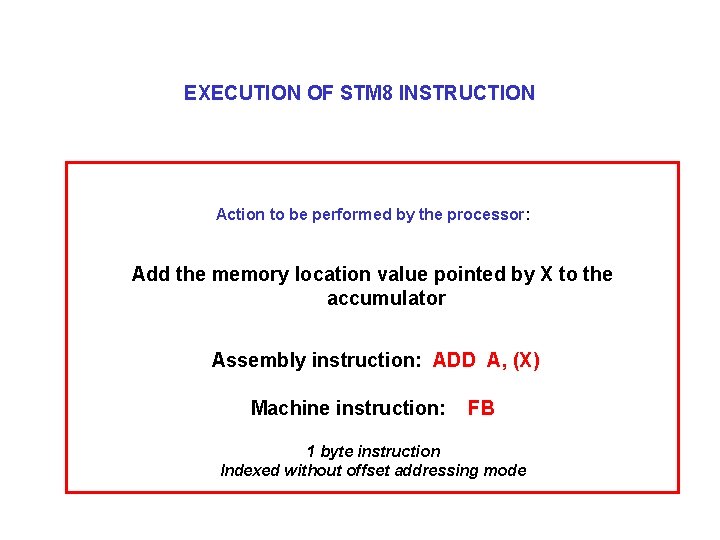

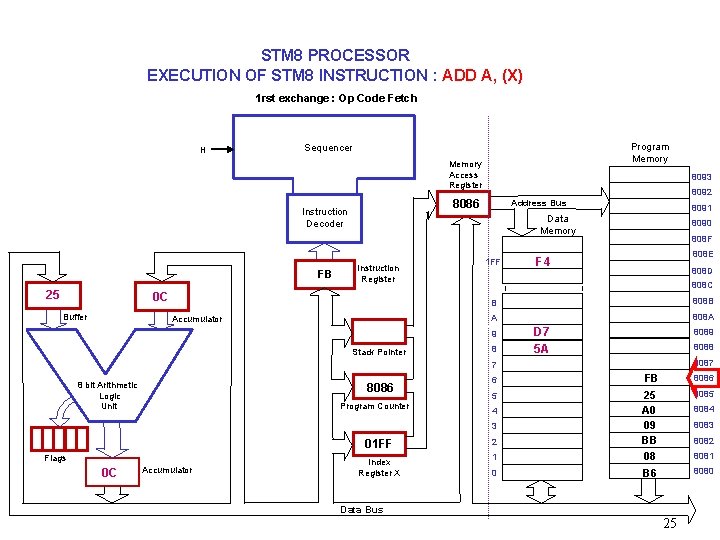

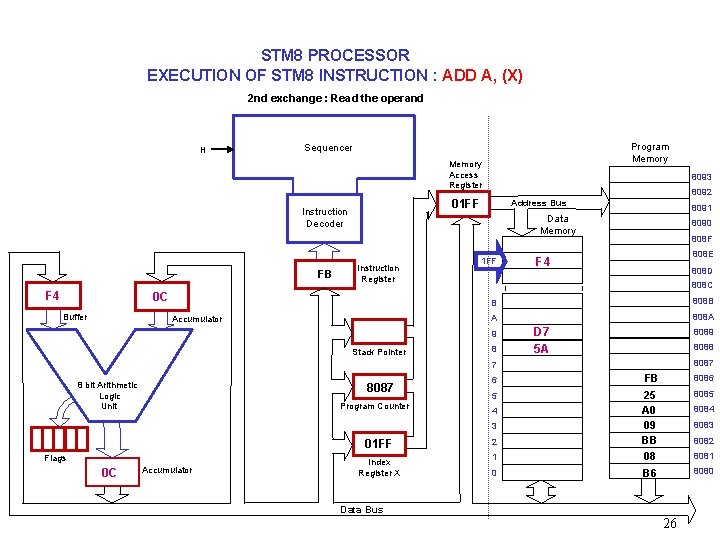

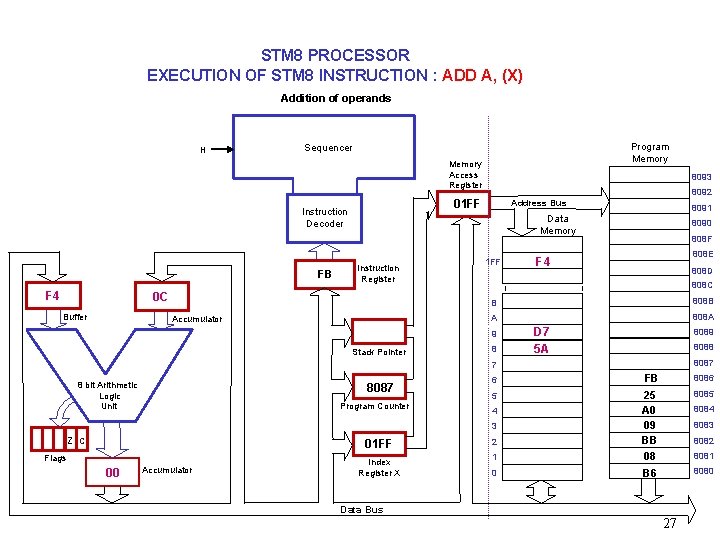

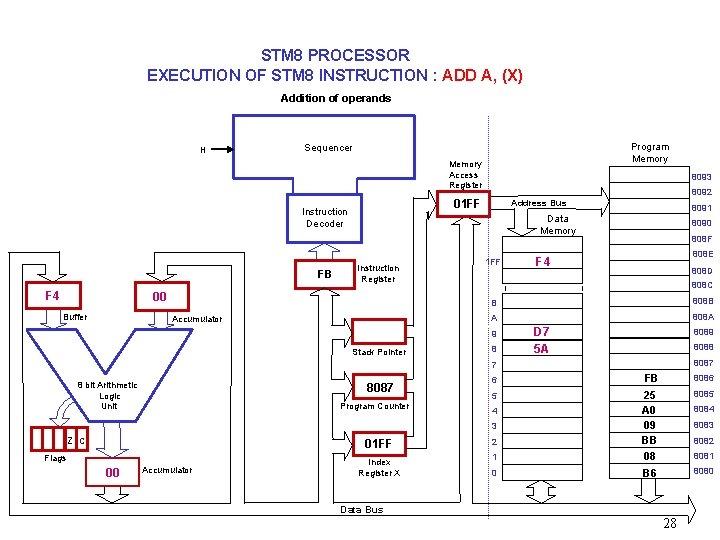

EXECUTION OF STM 8 INSTRUCTION Action to be performed by the processor: Add the memory location value pointed by X to the accumulator Assembly instruction: ADD A, (X) Machine instruction: FB 1 byte instruction Indexed without offset addressing mode

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, (X) 1 rst exchange : Op Code Fetch H Program Memory Sequencer Memory Access Register 25 Address Bus 8091 Data Memory Instruction Register 0 C Buffer 8092 8086 Instruction Decoder FB 8093 Accumulator 1 FF 808 E F 4 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8090 8 D 7 5 A 8089 8088 8087 7 8 bit Arithmetic Logic Unit 8086 Program Counter 6 FB 8086 5 8085 1 25 A 0 09 BB 08 0 B 6 4 3 01 FF Flags 0 C Accumulator Index Register X 2 8084 8083 8082 8081 8080 Data Bus 25

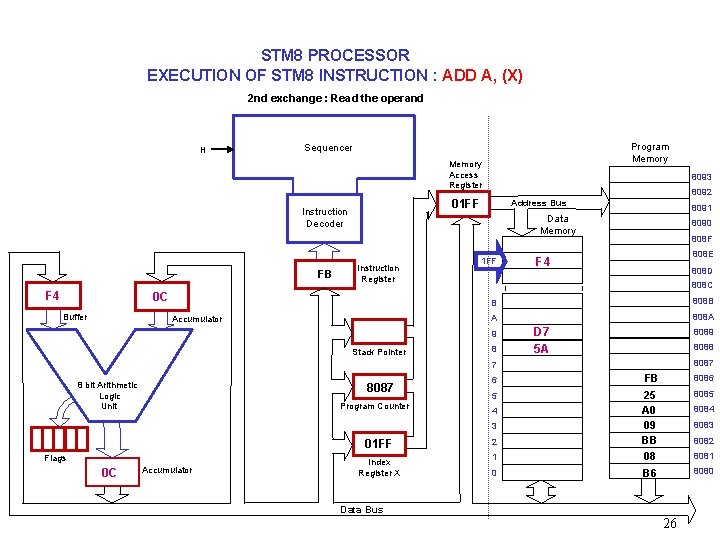

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, (X) 2 nd exchange : Read the operand H Program Memory Sequencer Memory Access Register F 4 Address Bus 8091 Data Memory Instruction Register 0 C Buffer 8092 01 FF Instruction Decoder FB 8093 Accumulator 1 FF 808 E F 4 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8090 8 D 7 5 A 8089 8088 8087 7 8 bit Arithmetic Logic Unit 8087 Program Counter 6 FB 8086 5 8085 1 25 A 0 09 BB 08 0 B 6 4 3 01 FF Flags 0 C Accumulator Index Register X 2 8084 8083 8082 8081 8080 Data Bus 26

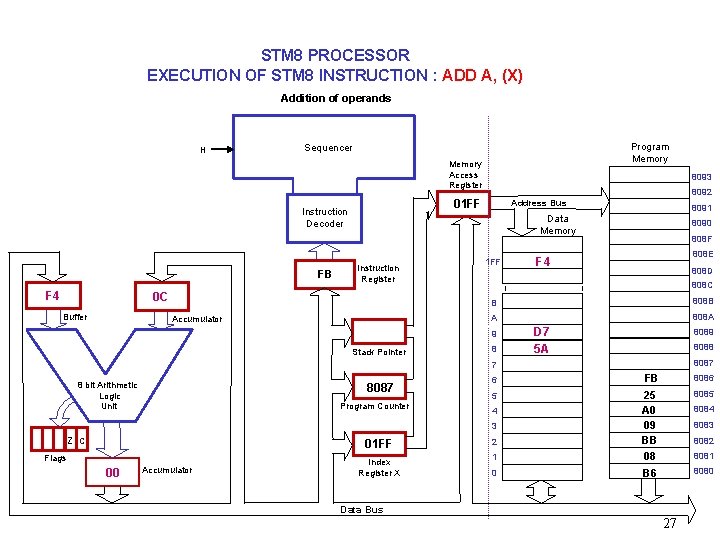

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, (X) Addition of operands H Program Memory Sequencer Memory Access Register F 4 Address Bus 8091 Data Memory Instruction Register 0 C Buffer 8092 01 FF Instruction Decoder FB 8093 Accumulator 1 FF 808 E F 4 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8090 8 D 7 5 A 8089 8088 8087 7 8 bit Arithmetic Logic Unit 8087 Program Counter 6 FB 8086 5 8085 1 25 A 0 09 BB 08 0 B 6 4 3 Z C 01 FF Flags 00 Accumulator Index Register X 2 8084 8083 8082 8081 8080 Data Bus 27

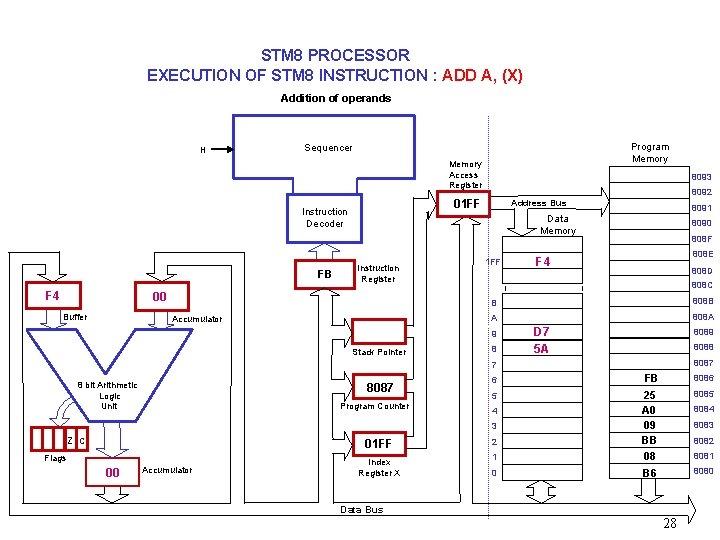

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : ADD A, (X) Addition of operands H Program Memory Sequencer Memory Access Register F 4 Address Bus 8091 Data Memory Instruction Register 00 Buffer 8092 01 FF Instruction Decoder FB 8093 Accumulator 1 FF 808 E F 4 808 D 808 C B 808 B A 808 A 9 Stack Pointer 8090 8 D 7 5 A 8089 8088 8087 7 8 bit Arithmetic Logic Unit 8087 Program Counter 6 FB 8086 5 8085 1 25 A 0 09 BB 08 0 B 6 4 3 Z C 01 FF Flags 00 Accumulator Index Register X 2 8084 8083 8082 8081 8080 Data Bus 28

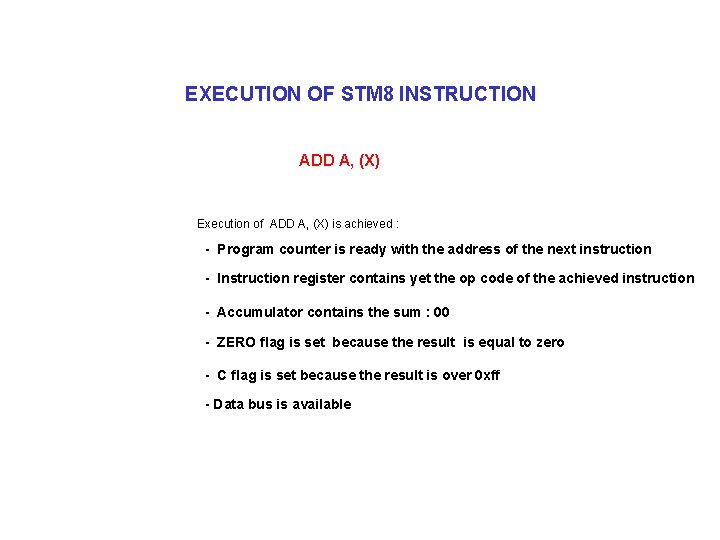

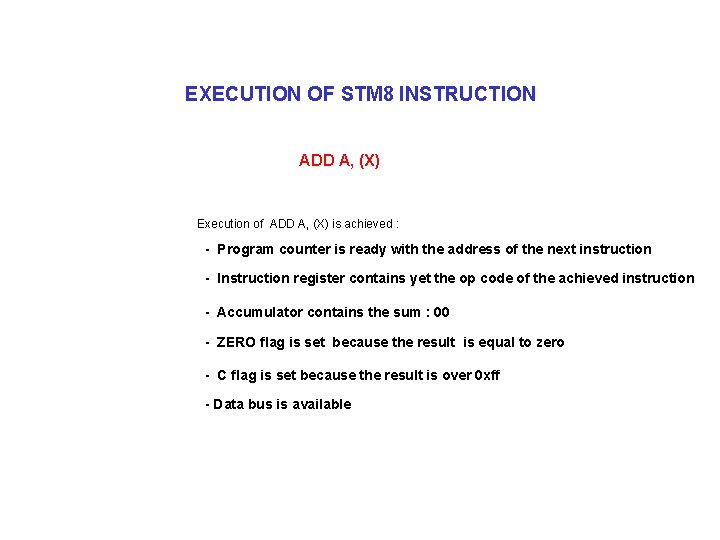

EXECUTION OF STM 8 INSTRUCTION ADD A, (X) Execution of ADD A, (X) is achieved : - Program counter is ready with the address of the next instruction - Instruction register contains yet the op code of the achieved instruction - Accumulator contains the sum : 00 - ZERO flag is set because the result is equal to zero - C flag is set because the result is over 0 xff - Data bus is available

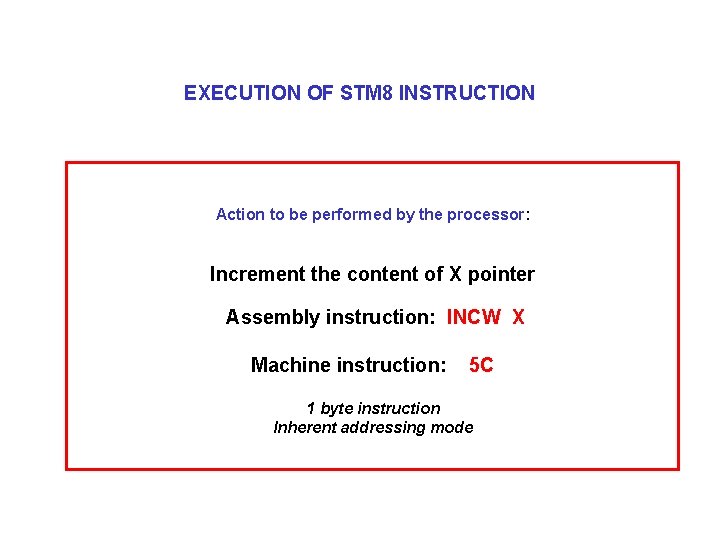

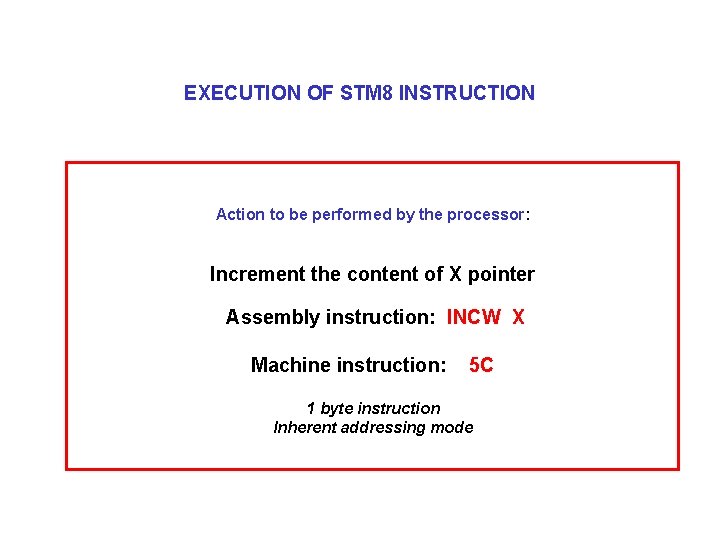

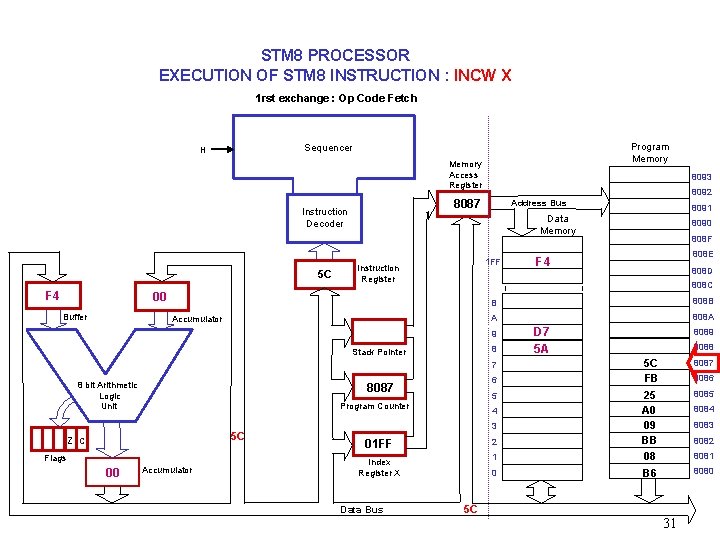

EXECUTION OF STM 8 INSTRUCTION Action to be performed by the processor: Increment the content of X pointer Assembly instruction: INCW X Machine instruction: 5 C 1 byte instruction Inherent addressing mode

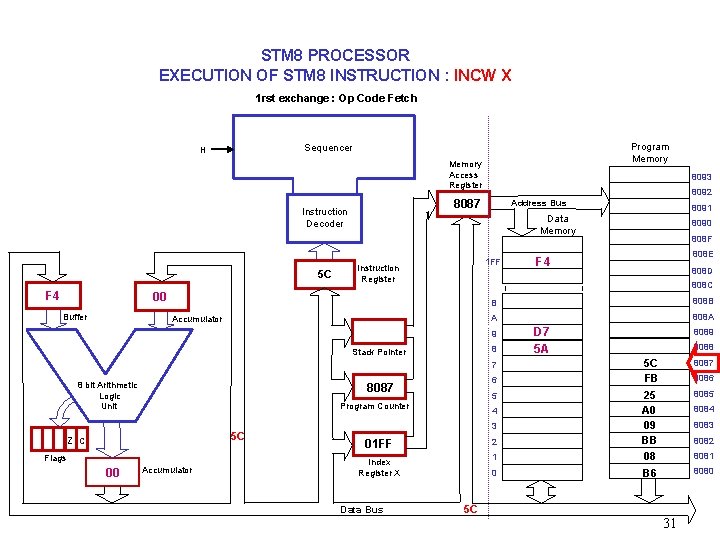

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : INCW X 1 rst exchange : Op Code Fetch Program Memory Sequencer H Memory Access Register F 4 Address Bus 1 FF Instruction Register 00 808 A 8085 1 0 B 6 3 2 Index Register X Data Bus 8088 25 A 0 09 BB 08 4 01 FF 8089 8087 5 Program Counter D 7 5 A 5 C FB 6 8087 Accumulator 808 D A 7 Flags 808 E F 4 808 B 8 Stack Pointer Z C 808 F B 9 5 C 8090 808 C Accumulator 8 bit Arithmetic Logic Unit 8091 Data Memory 00 Buffer 8092 8087 Instruction Decoder 5 C 8093 8086 8084 8083 8082 8081 8080 5 C 31

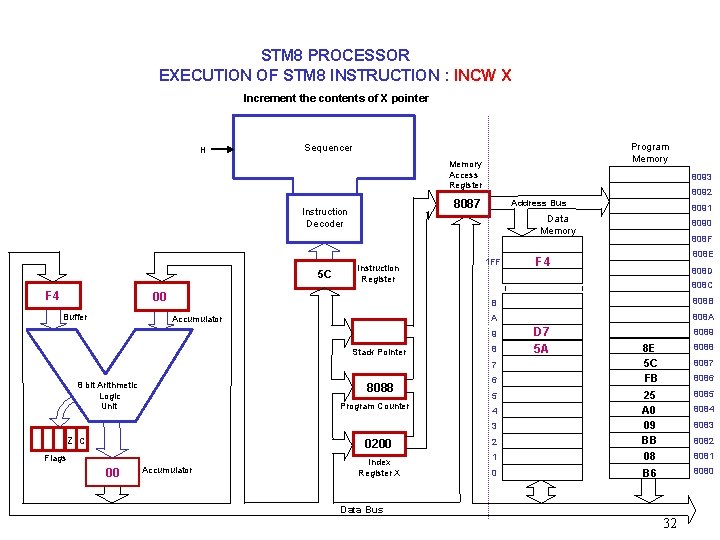

STM 8 PROCESSOR EXECUTION OF STM 8 INSTRUCTION : INCW X Increment the contents of X pointer H Program Memory Sequencer Memory Access Register F 4 Address Bus Instruction Register Accumulator 1 FF Stack Pointer Program Counter 0200 Flags 00 Accumulator Index Register X 808 E F 4 808 D 808 B A 808 A D 7 5 A 8089 8 E 5 C FB 8088 8085 1 25 A 0 09 BB 08 0 B 6 8 6 5 4 3 Z C 808 F B 7 8088 8090 808 C 9 8 bit Arithmetic Logic Unit 8091 Data Memory 00 Buffer 8092 8087 Instruction Decoder 5 C 8093 2 8087 8086 8084 8083 8082 8081 8080 Data Bus 32

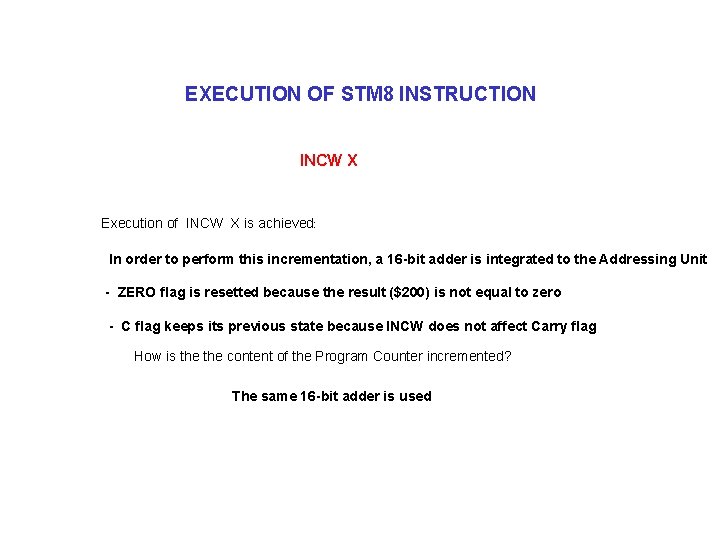

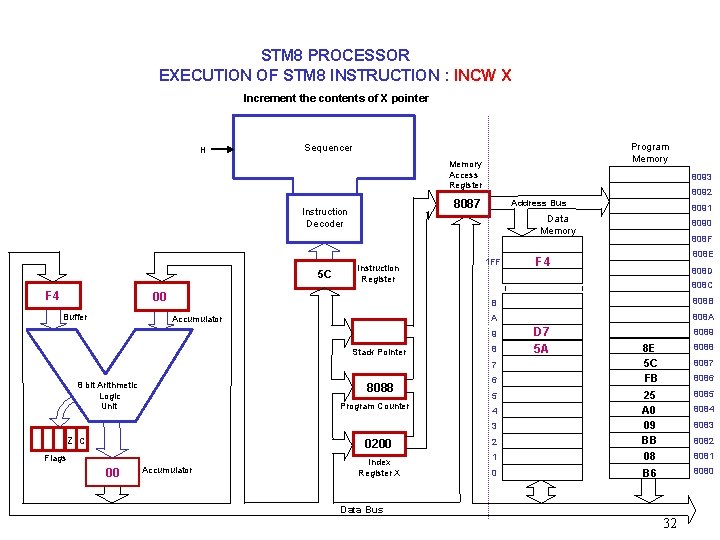

EXECUTION OF STM 8 INSTRUCTION INCW X Execution of INCW X is achieved: In order to perform this incrementation, a 16 -bit adder is integrated to the Addressing Unit - ZERO flag is resetted because the result ($200) is not equal to zero - C flag keeps its previous state because INCW does not affect Carry flag How is the content of the Program Counter incremented? The same 16 -bit adder is used

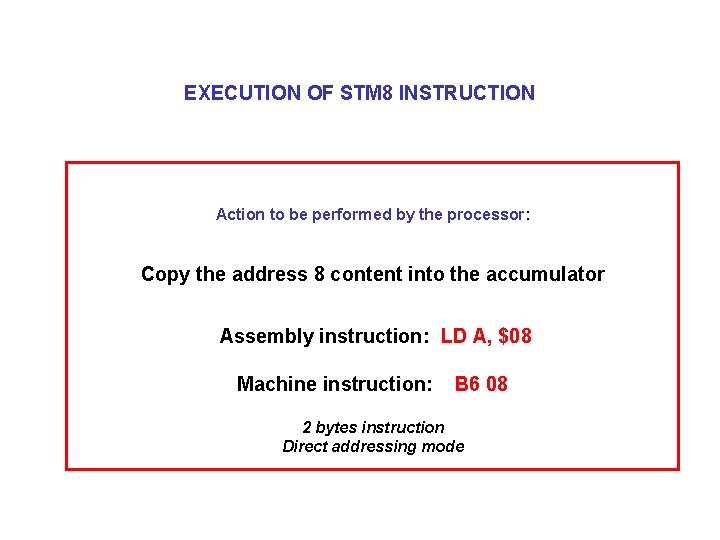

EXECUTION OF STM 8 INSTRUCTION CONCLUSION LD A, direct ADD A, indexed without offset SUB A, immediate INCW X B 6 address BB address FB A 0 operand 5 C The same 16 -bit adder is used