32 bitni mikrokontroleri i primena MS 1 BMP

32 -bitni mikrokontroleri i primena - MS 1 BMP 2016/2017 Nenad Jovičić

Organizacija kursa �Predavač: �doc. Dr Nenad Jovičić nenad@etf. rs �Web: tnt. etf. rs/~ms 1 bmp �Projekat 40% ocene �Ispit (60% ocene): �Demonstracija projekta �Diskusija o projektu �Diskusija o Cortex-u

Timeline �U ovom kursu ćemo se baviti kako praktičnom realizacijom projekata koji u sebi sadrže Cortex mikrokontroler, tako i specifičnim teorijskim aspektima ove tehnologije. �Gruba struktur kursa: �Uvod u Cortex tehnologije. �Pisanje softvera po CMSIS standardu. �Detaljno proučavanje hardverskih sklopova STM Cortex mikrokontrolera. �Specifičnosti arhitekture Cortex mikrokontrolera. �Napredne tehnike debagovanja �Cortex u DSP aplikacijama �RTOS na Cortex platformi

Projekat �Implementacija jednostavnog hardversko-softverskog sistema/uređaja na Cortex-M 3 ili Cortex-M 4 razvojnoj platformi. �Projekat ne treba da bude obiman po broju korišćenih periferija, ali treba da bude detaljan u ispitivanju mogućnosti izabranih periferija. Ide se u dubinu a ne u širinu.

Projekat - rokovi �danas - 18. 10. 2016. – Prikupljanje predloga projekata. � 18. 10. 2016. Izveštaj 1. - Idejno rešenje. � 18. 10. 2016. - 25. 10. 2016. – Definisanje spiska potrebnih komponenti. � 25. 10. 2016. Izveštaj 2. - Dizajn hardvera na nivou električne šeme, i dostavljanje spiska komponenti. � 25. 10. 2016. - 15. 11. 2016. – Nabavka komponenti. � 15. 11. 2016. - 6. 12. 2016. – Rad na prototipu. � 6. 12. 2016. Izveštaj 3. – Prototip hardvera i softvera. Minimalna konfiguracija koja potvrđuje izvodljivost projekta. � 6. 12. 2016. – 31. 12. 2016. Finalizacija projekta. �Ispitni rok januar 2016 – Finalni izveštaj.

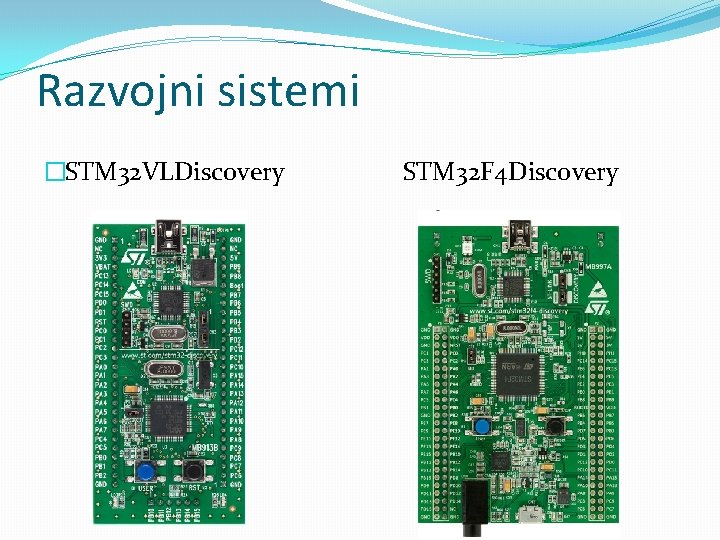

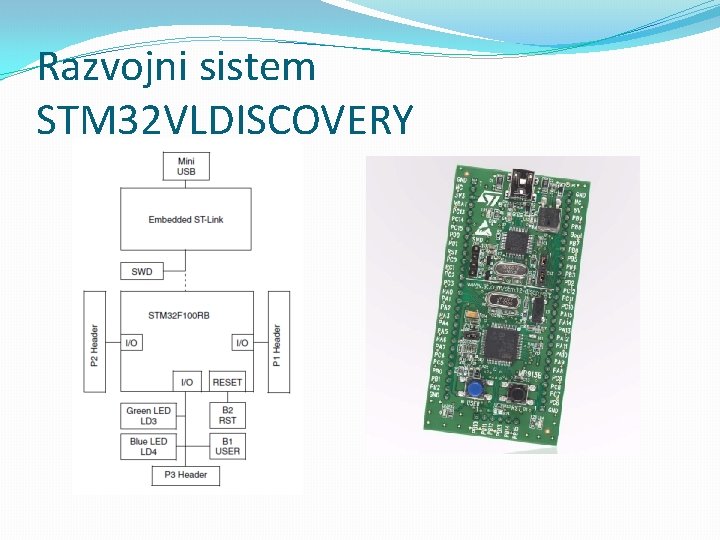

Razvojni sistemi �STM 32 VLDiscovery STM 32 F 4 Discovery

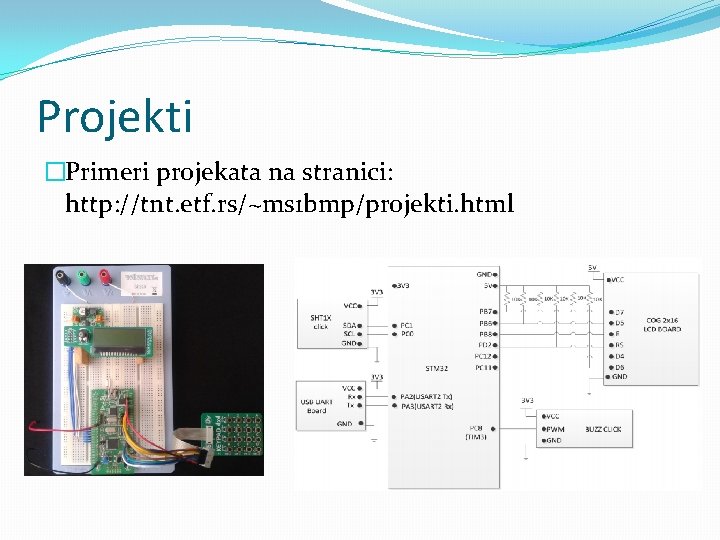

Projekti �Primeri projekata na stranici: http: //tnt. etf. rs/~ms 1 bmp/projekti. html

Komponente � Preferirani dobavljač modula je kompanija mikroelektronika. www. mikroe. com. � Najzgodnije za upotrebu su Click pločice. � Moguća je u posebnim slučajevima i nabavka nekih specijalnih komponenti iz stranih kataloga, kao na primer iz www. farnell. com.

Komponente �Povezivanje može da bude izvedeno pomoću kratkospojnika, ali može da se realizuje i preko namenski napravljene/izlemljene matične ploče. �Nabavka standardnih elektronskih/električnih komponenti se vrši u kelco-u ili mikroprincu. www. kelco. rs , www. mikroprinc. rs

Literatura - knjige �The Definitive Guide to ARM® Cortex®-M 3 and Cortex®-M 4 Processors, Joseph Yiu, Elsevier, 2013. �The Designer's Guide to the Cortex-M Processor Family, Trevor Martin, Elsevier, 2013.

Literatura – ARM-ova dokumentacija � ARMv 7 -M Architecture Reference Manual (ARM DDI 0403) � ARM Cortex-M 3 Integration and Implementation Manual (ARM DII 0240) � ARM AMBA® 3 AHB-Lite Protocol (v 1. 0) (ARM IHI 0033) � ARM AMBA™ 3 APB Protocol Specification (ARM IHI 0024) � AMBA® 3 ATB Protocol Specification (ARM IHI 0032) � ARM Core. Sight™ Components Technical Reference Manual (ARM DDI 0314) � ARM Debug Interface v 5 Architecture Specification (ARM IHI 0031) � ARM Embedded Trace Macrocell Architecture Specification (ARM IHI 0014). � IEEE Standard Test Access Port and Boundary-Scan Architecture 1149. 1 -2001 (JTAG). �. . .

Razvojni sistem STM 32 VLDISCOVERY

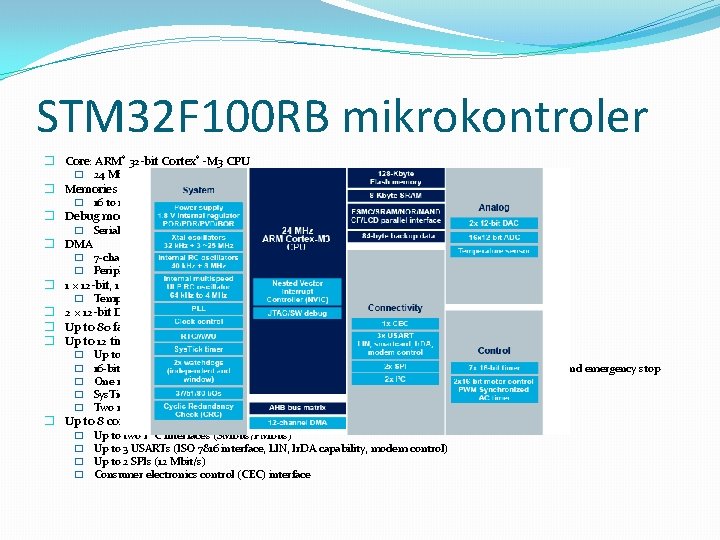

STM 32 F 100 RB mikrokontroler � Core: ARM® 32 -bit Cortex® -M 3 CPU � 24 MHz maximum frequency, 1. 25 DMIPS/MHz (Dhrystone 2. 1) performance � Memories � 16 to 128 Kbytes of Flash memory, 4 to 8 Kbytes of SRAM � Debug mode � Serial wire debug (SWD) and JTAG interfaces � DMA � 7 -channel DMA controller � Peripherals supported: timers, ADC, SPIs, I 2 Cs, USARTs and DACs � 1 × 12 -bit, 1. 2 μs A/D converter (up to 16 channels) � Temperature sensor � 2 × 12 -bit D/A converters � Up to 80 fast I/O ports, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant � Up to 12 timers � � � Up to three 16 -bit timers, each with up to 4 IC/OC/PWM or pulse counter 16 -bit, 6 -channel advanced-control timer: up to 6 channels for PWM output, dead time generation and emergency stop One 16 -bit timer, Two 16 -bit timers, 2 watchdog timers (Independent and Window) Sys. Tick timer: 24 -bit downcounter Two 16 -bit basic timers to drive the DAC � Up to 8 communications interfaces � � Up to two I 2 C interfaces (SMBus/PMBus) Up to 3 USARTs (ISO 7816 interface, LIN, Ir. DA capability, modem control) Up to 2 SPIs (12 Mbit/s) Consumer electronics control (CEC) interface

STM 32 F 100 RB mikrokontroler � Core: ARM® 32 -bit Cortex® -M 3 CPU � 24 MHz maximum frequency, 1. 25 DMIPS/MHz (Dhrystone 2. 1) performance � Memories � 16 to 128 Kbytes of Flash memory, 4 to 8 Kbytes of SRAM � Debug mode � Serial wire debug (SWD) and JTAG interfaces � DMA � 7 -channel DMA controller � Peripherals supported: timers, ADC, SPIs, I 2 Cs, USARTs and DACs � 1 × 12 -bit, 1. 2 μs A/D converter (up to 16 channels) � Temperature sensor � 2 × 12 -bit D/A converters � Up to 80 fast I/O ports, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant � Up to 12 timers � � � Up to three 16 -bit timers, each with up to 4 IC/OC/PWM or pulse counter 16 -bit, 6 -channel advanced-control timer: up to 6 channels for PWM output, dead time generation and emergency stop One 16 -bit timer, Two 16 -bit timers, 2 watchdog timers (Independent and Window) Sys. Tick timer: 24 -bit downcounter Two 16 -bit basic timers to drive the DAC � Up to 8 communications interfaces � � Up to two I 2 C interfaces (SMBus/PMBus) Up to 3 USARTs (ISO 7816 interface, LIN, Ir. DA capability, modem control) Up to 2 SPIs (12 Mbit/s) Consumer electronics control (CEC) interface

Programiranje i debagovanje �Kratkosponicima na konektoru CN 3 se određuje da li je STlink povezan na ovu pločicu ili neki spoljašnji mikrokontroler. �Više podataka o razvojnom sistemu se može naći u dokumentu UM 0919.

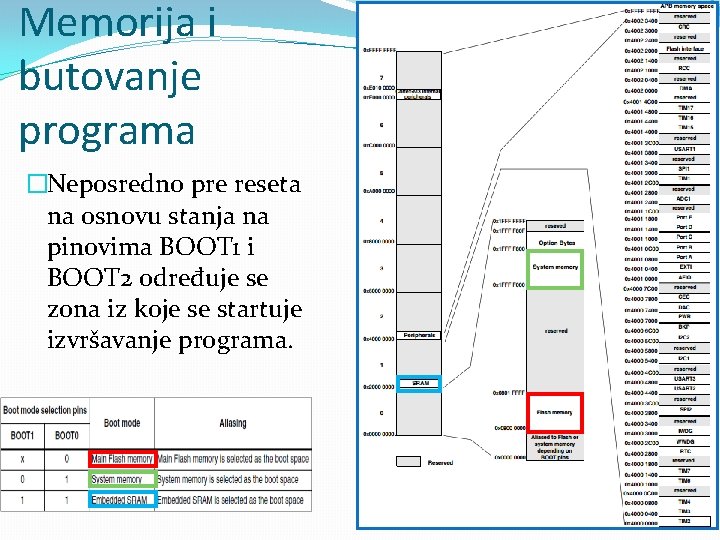

Memorija i butovanje programa �Neposredno pre reseta na osnovu stanja na pinovima BOOT 1 i BOOT 2 određuje se zona iz koje se startuje izvršavanje programa.

CMSIS - Cortex Microcontroller Software Interface Standard �Razvijen u težnji da se standardizuje pristup hervderskim resursima Cortex mikrokontrolera i obezbedi portabilnost softvera među različitim proizvođačima. �CMSIS omogućava razvoj ponovo iskoristljivih (reusable) komponenti softvera za sisteme bazirane na ARM Cortex-M. �Sistemi bazirani na ARM Cortex-M tehnologiji imaju veliki broj zajedničkih komponenti hardvera pa i Hardware Abstraction Layer (HAL) može biti veoma sličan.

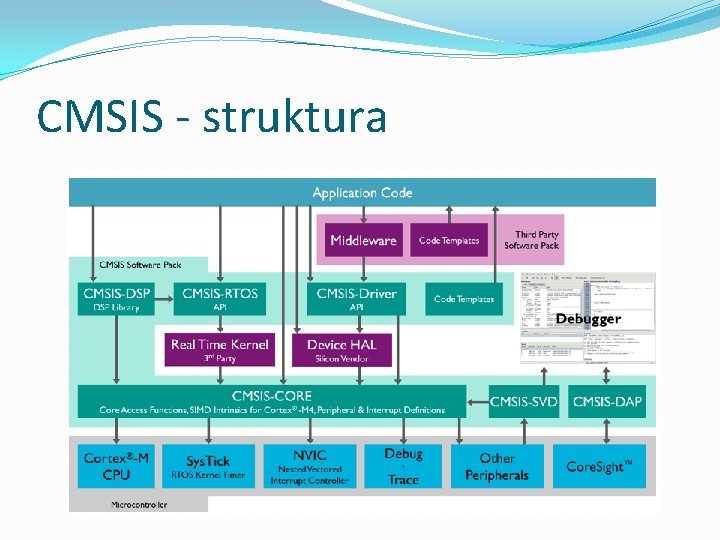

CMSIS - struktura

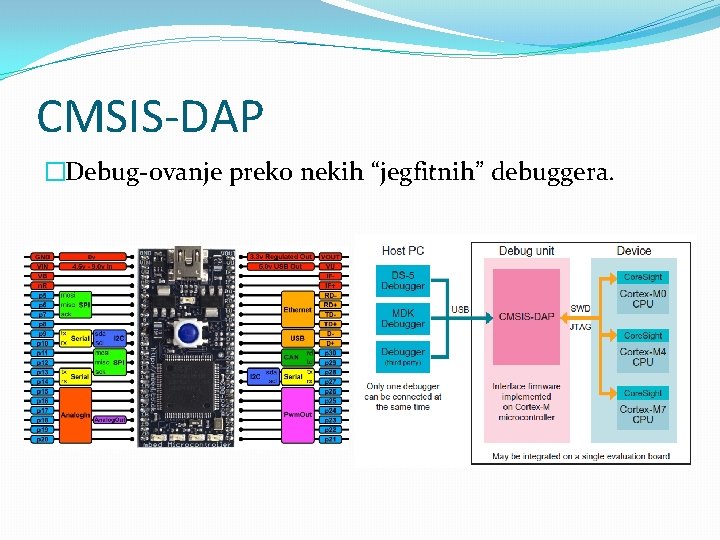

CMSIS - komponente � CMSIS-Core (Cortex-M processor support) � CMSIS-Driver – podrška za middleware komponente, tj. Drajvere poizvođača � CMSIS-DSP library – od 2010. � CMSIS-SVD e the CMSIS System View Description – set XML fajlova koje kreiraju proizvođači mikrokontrolera i preko kojih na stadardizovan način opisuju hardver. Ovo dalje mogu da koriste recimo proizvođači mikrokontrolera. � CMSIS-RTOS – univerzalna podrška za razne proizvođače operativnih sistema � CMSIS-DAP (Debug Access Port) – set funkcija koje obezbeđuju debug interfejs preko USB ili JTAG/Serial veze. Namenjen za podršku razvoju jeftinih hardveraskih debug interfejsa. � CMSIS-Pack – primeri, template-ovi i slični kodovi koji pomažu pri razvoju aplikacija.

CMSIS-DAP �Debug-ovanje preko nekih “jegfitnih” debuggera.

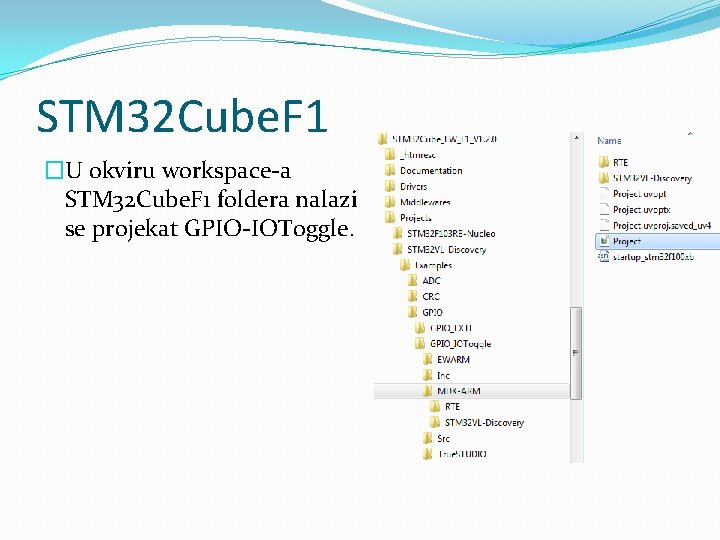

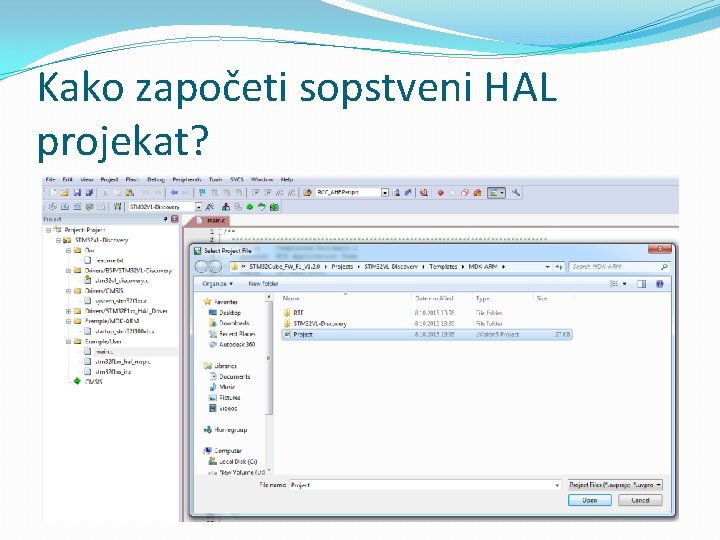

Za početak mi treba mala pomoć �Napraviti folder D: /MS 1 MBP/ �Download-ovati sledeći zip fajl: http: //www. st. com/st-webui/static/active/en/st_prod_software_internet/resource/te chnical/software/firmware/stm 32 cubef 1. zip �Raspakovati ga u taj folder tako da struktura bude sledeća: �D: /MS 1 MBP/ STM 32 Cube_FW_F 1_V 1. 2. 0/…….

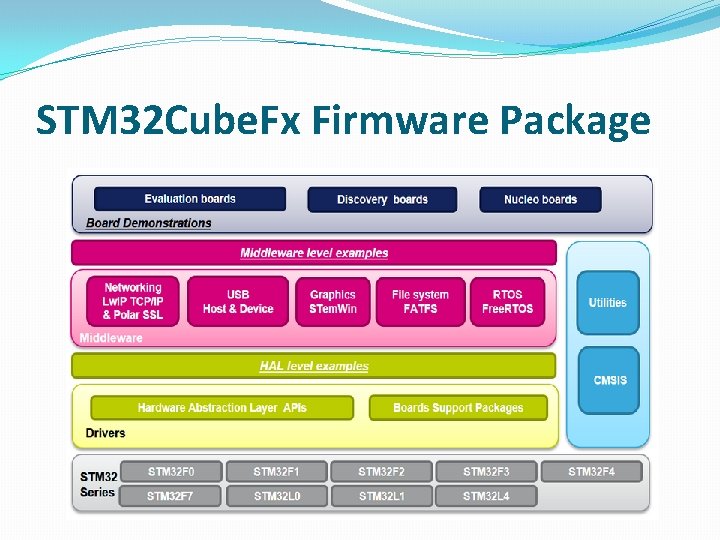

STM 32 Cube. Fx Firmware Package

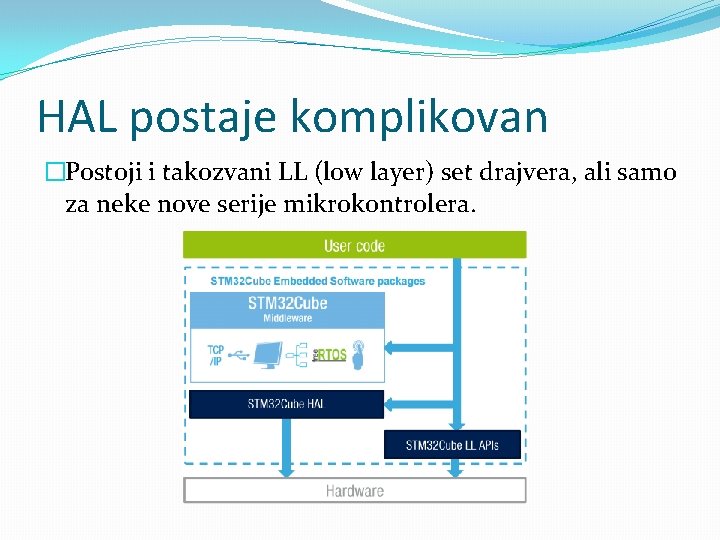

HAL postaje komplikovan �Postoji i takozvani LL (low layer) set drajvera, ali samo za neke nove serije mikrokontrolera.

STM 32 Cube. F 1 �U okviru workspace-a STM 32 Cube. F 1 foldera nalazi se projekat GPIO-IOToggle.

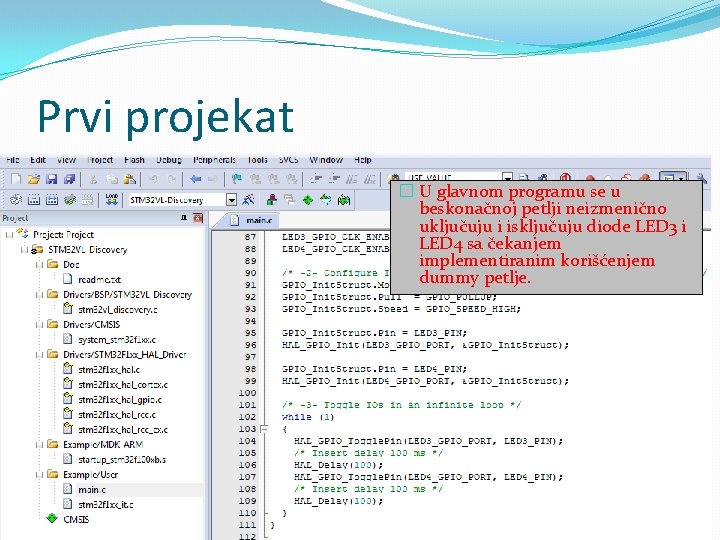

Prvi projekat � U glavnom programu se u beskonačnoj petlji neizmenično uključuju i isključuju diode LED 3 i LED 4 sa čekanjem implementiranim korišćenjem dummy petlje.

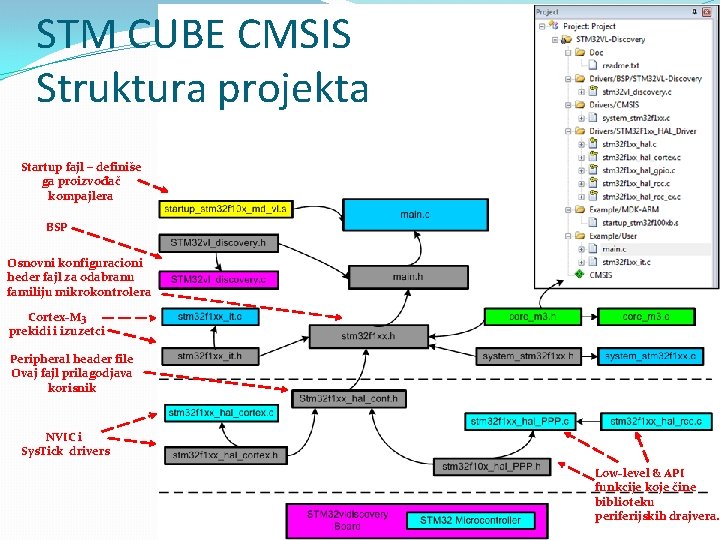

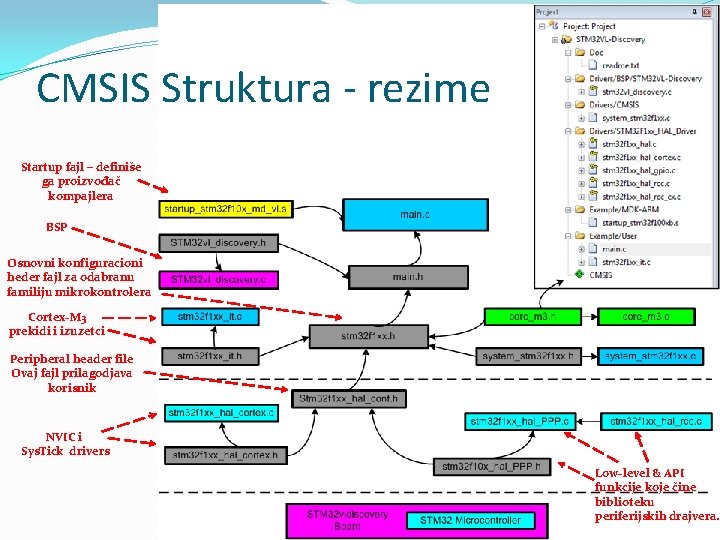

STM CUBE CMSIS Struktura projekta Startup fajl – definiše ga proizvođač kompajlera BSP Osnovni konfiguracioni heder fajl za odabranu familiju mikrokontrolera Cortex-M 3 prekidi i izuzetci Peripheral header file Ovaj fajl prilagodjava korisnik NVIC i Sys. Tick drivers Low-level & API funkcije koje čine biblioteku periferijskih drajvera.

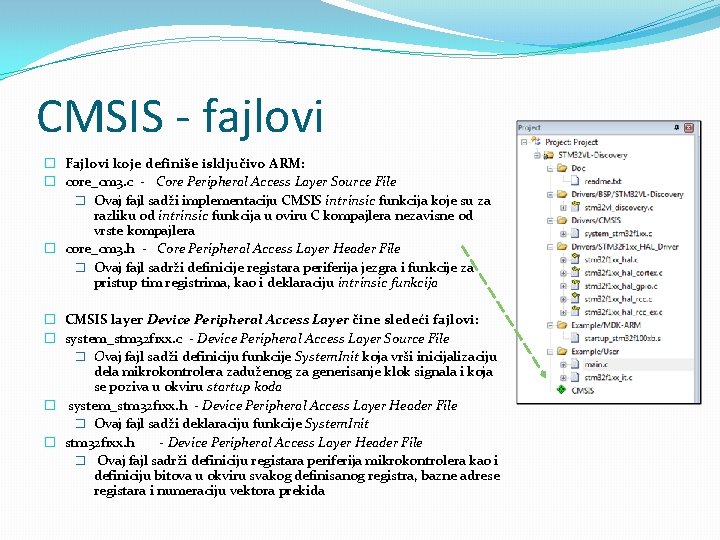

CMSIS - fajlovi � Fajlovi koje definiše isključivo ARM: � core_cm 3. c - Core Peripheral Access Layer Source File � Ovaj fajl sadži implementaciju CMSIS intrinsic funkcija koje su za razliku od intrinsic funkcija u oviru C kompajlera nezavisne od vrste kompajlera � core_cm 3. h - Core Peripheral Access Layer Header File � Ovaj fajl sadrži definicije registara periferija jezgra i funkcije za pristup tim registrima, kao i deklaraciju intrinsic funkcija � CMSIS layer Device Peripheral Access Layer čine sledeći fajlovi: � system_stm 32 f 1 xx. c - Device Peripheral Access Layer Source File � Ovaj fajl sadži definiciju funkcije System. Init koja vrši inicijalizaciju dela mikrokontrolera zaduženog za generisanje klok signala i koja se poziva u okviru startup koda � system_stm 32 f 1 xx. h - Device Peripheral Access Layer Header File � Ovaj fajl sadži deklaraciju funkcije System. Init � stm 32 f 1 xx. h - Device Peripheral Access Layer Header File � Ovaj fajl sadrži definiciju registara periferija mikrokontrolera kao i definiciju bitova u okviru svakog definisanog registra, bazne adrese registara i numeraciju vektora prekida

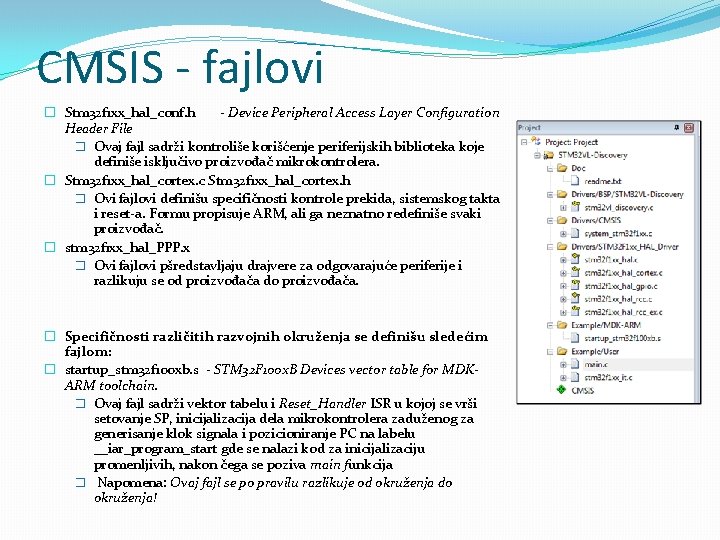

CMSIS - fajlovi � Stm 32 f 1 xx_hal_conf. h - Device Peripheral Access Layer Configuration Header File � Ovaj fajl sadrži kontroliše korišćenje periferijskih biblioteka koje definiše isključivo proizvođač mikrokontrolera. � Stm 32 f 1 xx_hal_cortex. c Stm 32 f 1 xx_hal_cortex. h � Ovi fajlovi definišu specifičnosti kontrole prekida, sistemskog takta i reset-a. Formu propisuje ARM, ali ga neznatno redefiniše svaki proizvođač. � stm 32 f 1 xx_hal_PPP. x � Ovi fajlovi pšredstavljaju drajvere za odgovarajuće periferije i razlikuju se od proizvođača do proizvođača. � Specifičnosti različitih razvojnih okruženja se definišu sledećim fajlom: � startup_stm 32 f 100 xb. s - STM 32 F 100 x. B Devices vector table for MDKARM toolchain. � Ovaj fajl sadrži vektor tabelu i Reset_Handler ISR u kojoj se vrši setovanje SP, inicijalizacija dela mikrokontrolera zaduženog za generisanje klok signala i pozicioniranje PC na labelu __iar_program_start gde se nalazi kod za inicijalizaciju promenljivih, nakon čega se poziva main funkcija � Napomena: Ovaj fajl se po pravilu razlikuje od okruženja do okruženja!

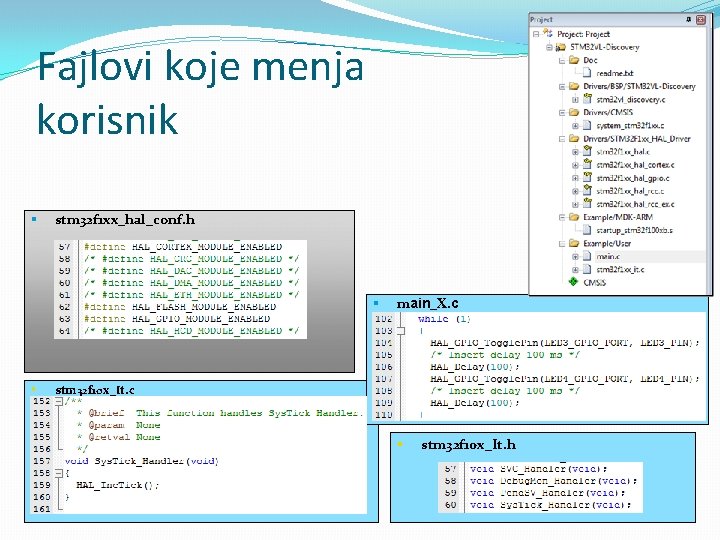

Fajlovi koje menja korisnik § stm 32 f 1 xx_hal_conf. h § § main_X. c stm 32 f 10 x_It. c § stm 32 f 10 x_It. h

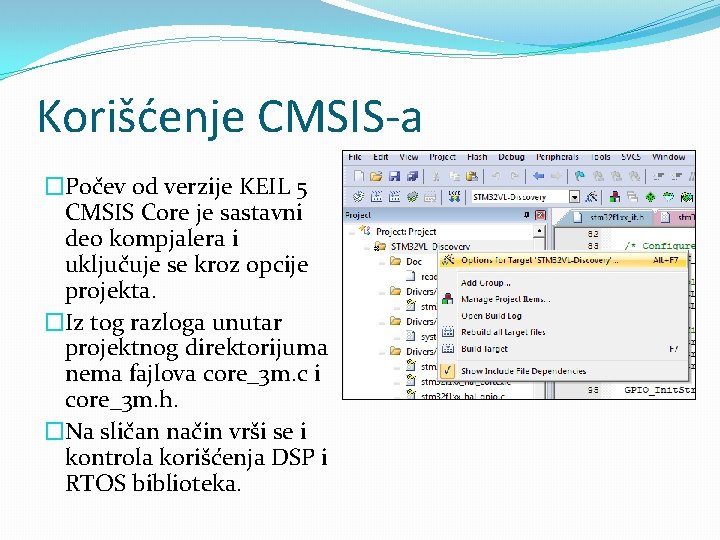

Korišćenje CMSIS-a �Počev od verzije KEIL 5 CMSIS Core je sastavni deo kompjalera i uključuje se kroz opcije projekta. �Iz tog razloga unutar projektnog direktorijuma nema fajlova core_3 m. c i core_3 m. h. �Na sličan način vrši se i kontrola korišćenja DSP i RTOS biblioteka.

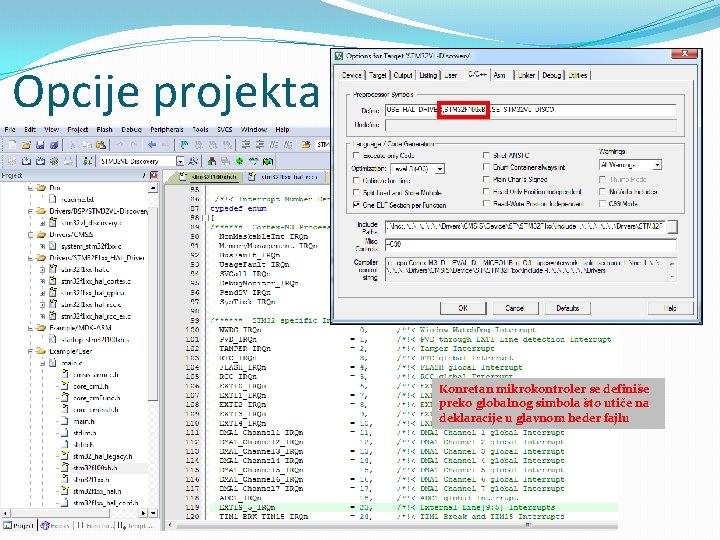

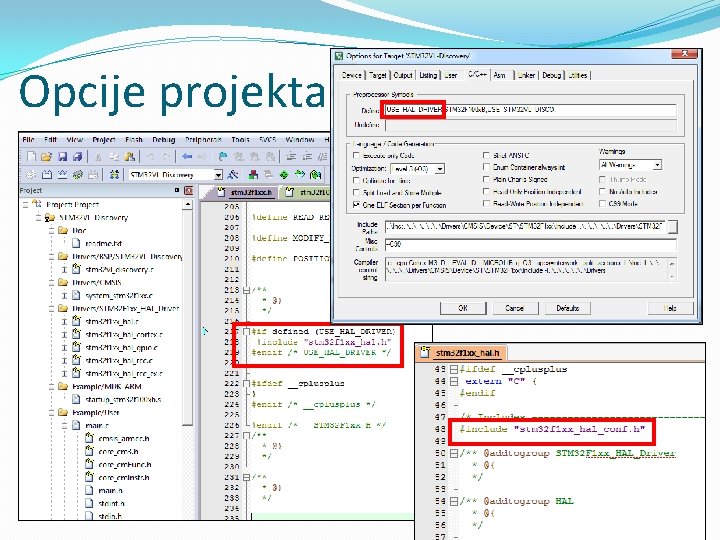

Opcije projekta Konretan mikrokontroler se definiše preko globalnog simbola što utiče na deklaracije u glavnom heder fajlu

Opcije projekta Korišćenje periferijskih biblioteka se kontroliše globalnim simbolom koji povezuje konfiguracione heder fajl.

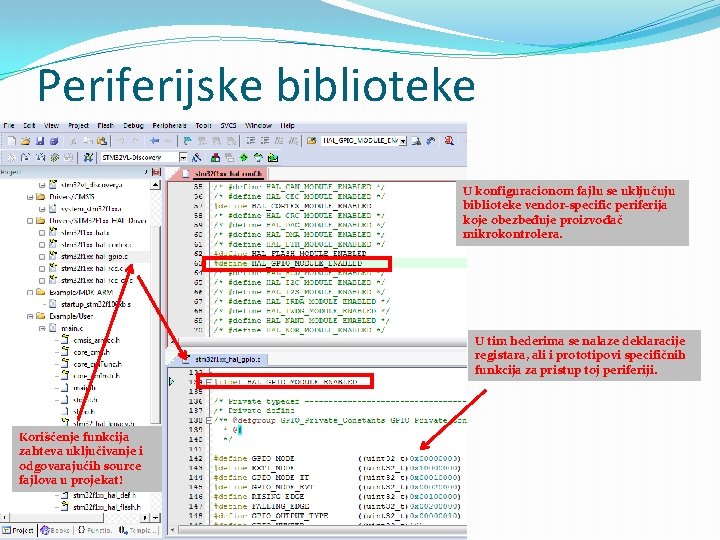

Periferijske biblioteke U konfiguracionom fajlu se uključuju biblioteke vendor-specific periferija koje obezbeđuje proizvođač mikrokontrolera. U tim hederima se nalaze deklaracije registara, ali i prototipovi specifičnih funkcija za pristup toj periferiji. Korišćenje funkcija zahteva uključivanje i odgovarajućih source fajlova u projekat!

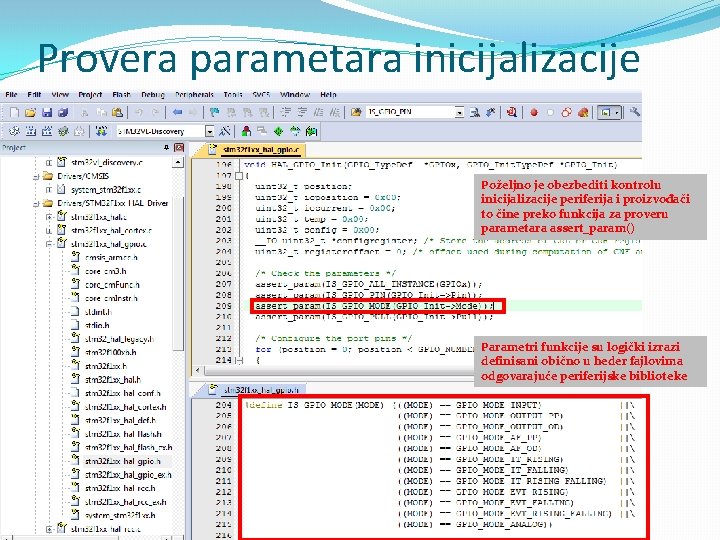

Provera parametara inicijalizacije Poželjno je obezbediti kontrolu inicijalizacije periferija i proizvođači to čine preko funkcija za proveru parametara assert_param() Parametri funkcije su logički izrazi definisani obično u heder fajlovima odgovarajuće periferijske biblioteke

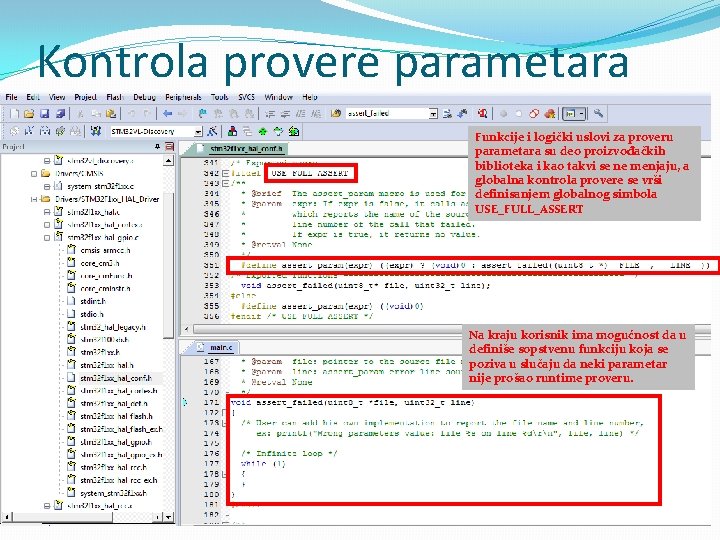

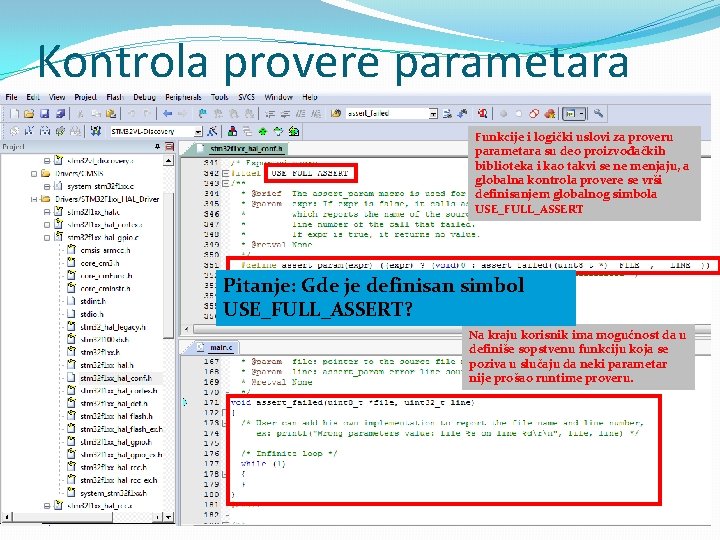

Kontrola provere parametara Funkcije i logički uslovi za proveru parametara su deo proizvođačkih biblioteka i kao takvi se ne menjaju, a globalna kontrola provere se vrši definisanjem globalnog simbola USE_FULL_ASSERT Na kraju korisnik ima mogućnost da u definiše sopstvenu funkciju koja se poziva u slučaju da neki parametar nije prošao runtime proveru.

Kontrola provere parametara Funkcije i logički uslovi za proveru parametara su deo proizvođačkih biblioteka i kao takvi se ne menjaju, a globalna kontrola provere se vrši definisanjem globalnog simbola USE_FULL_ASSERT Pitanje: Gde je definisan simbol USE_FULL_ASSERT? Na kraju korisnik ima mogućnost da u definiše sopstvenu funkciju koja se poziva u slučaju da neki parametar nije prošao runtime proveru.

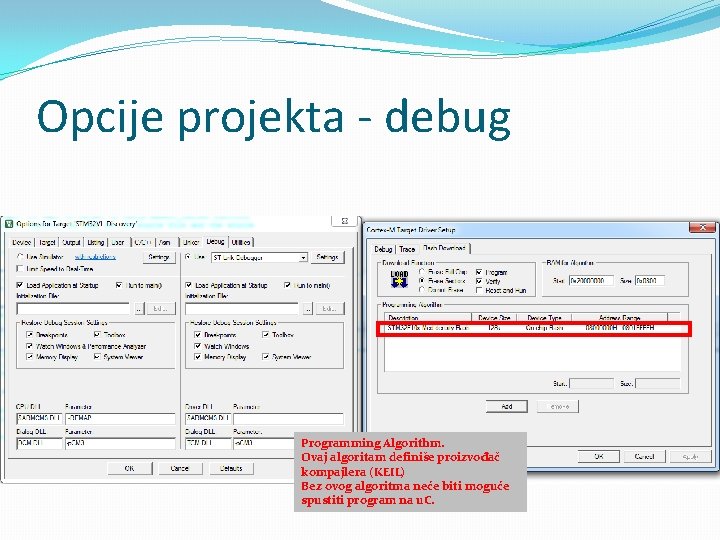

Opcije projekta - debug Programming Algorithm. Ovaj algoritam definiše proizvođač kompajlera (KEIL) Bez ovog algoritma neće biti moguće spustiti program na u. C.

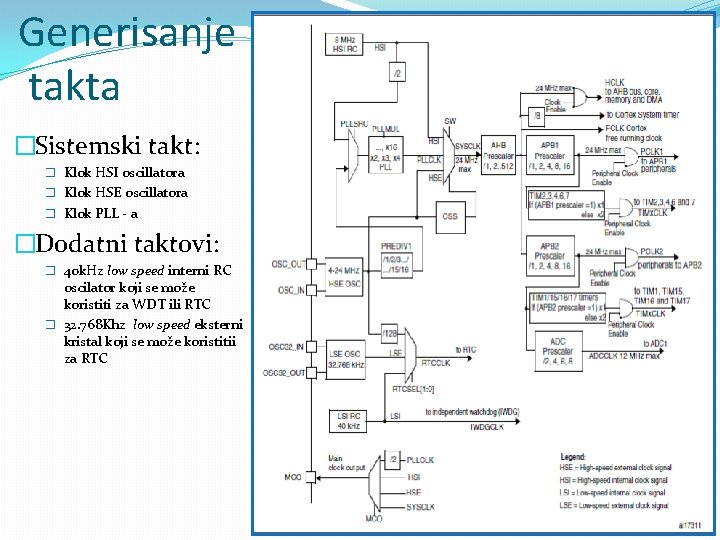

Generisanje takta �Sistemski takt: � Klok HSI oscillatora � Klok HSE oscillatora � Klok PLL - a �Dodatni taktovi: � 40 k. Hz low speed interni RC oscilator koji se može koristiti za WDT ili RTC � 32. 768 Khz low speed eksterni kristal koji se može koristitii za RTC

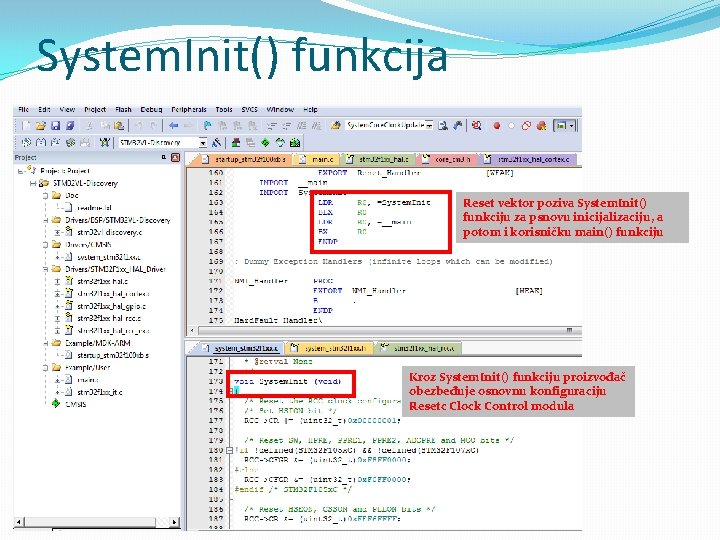

System. Init() funkcija Reset vektor poziva System. Init() funkciju za psnovu inicijalizaciju, a potom i korisničku main() funkciju Kroz System. Init() funkciju proizvođač obezbeđuje osnovnu konfiguraciju Resetc Clock Control modula

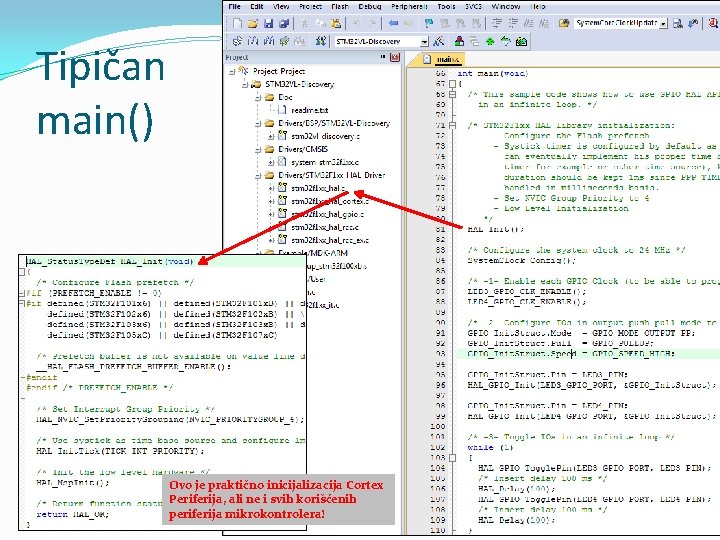

Tipičan main() Ovo je praktično inicijalizacija Cortex Periferija, ali ne i svih korišćenih periferija mikrokontrolera!

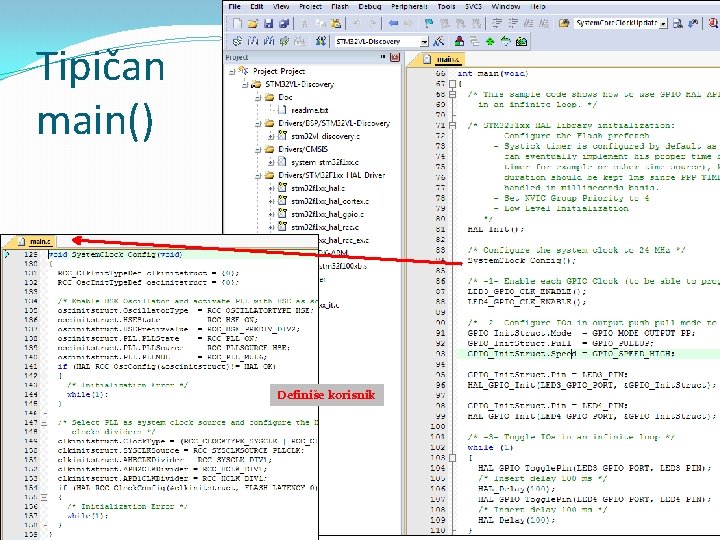

Tipičan main() Definiše korisnik

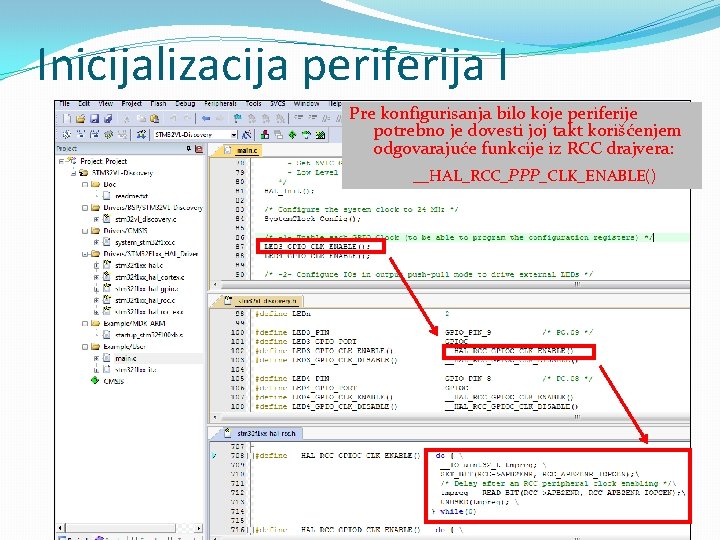

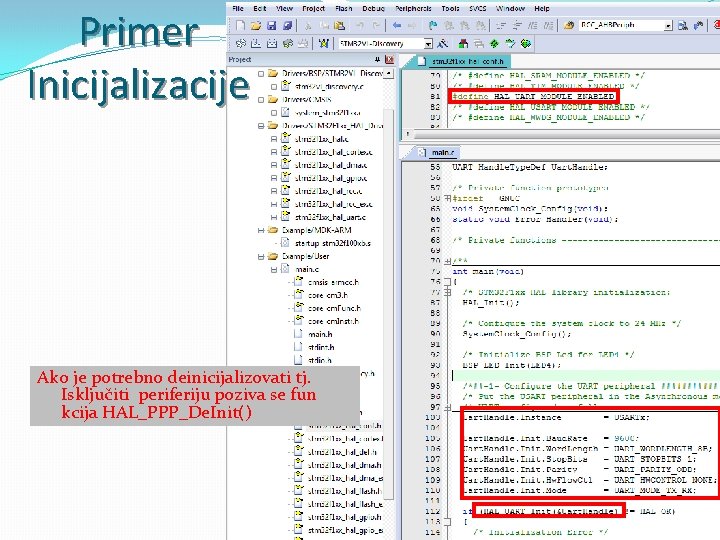

Inicijalizacija periferija I Pre konfigurisanja bilo koje periferije potrebno je dovesti joj takt korišćenjem odgovarajuće funkcije iz RCC drajvera: __HAL_RCC_PPP_CLK_ENABLE()

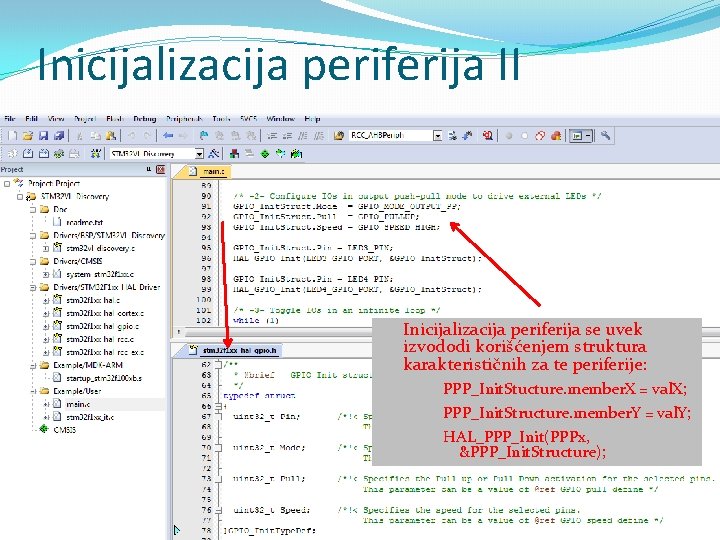

Inicijalizacija periferija II Inicijalizacija periferija se uvek izvododi korišćenjem struktura karakterističnih za te periferije: PPP_Init. Stucture. member. X = val. X; PPP_Init. Structure. member. Y = val. Y; HAL_PPP_Init(PPPx, &PPP_Init. Structure);

Primer Inicijalizacije Ako je potrebno deinicijalizovati tj. Isključiti periferiju poziva se fun kcija HAL_PPP_De. Init()

CMSIS Struktura - rezime Startup fajl – definiše ga proizvođač kompajlera BSP Osnovni konfiguracioni heder fajl za odabranu familiju mikrokontrolera Cortex-M 3 prekidi i izuzetci Peripheral header file Ovaj fajl prilagodjava korisnik NVIC i Sys. Tick drivers Low-level & API funkcije koje čine biblioteku periferijskih drajvera.

Kako započeti sopstveni HAL projekat?

- Slides: 46