32 bitni mikrokontroleri i primena MS 1 BMP

32 -bitni mikrokontroleri i primena - MS 1 BMP 2017/2018 Nenad Jovičić

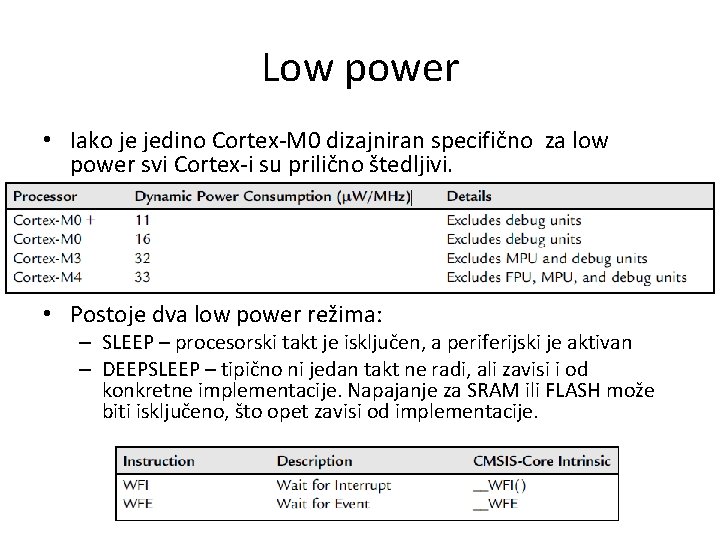

Low power • Iako je jedino Cortex-M 0 dizajniran specifično za low power svi Cortex-i su prilično štedljivi. • Postoje dva low power režima: – SLEEP – procesorski takt je isključen, a periferijski je aktivan – DEEPSLEEP – tipično ni jedan takt ne radi, ali zavisi i od konkretne implementacije. Napajanje za SRAM ili FLASH može biti isključeno, što opet zavisi od implementacije.

Low power • Iako je jedino Cortex-M 0 dizajniran specifično za low power svi Cortex-i su prilično štedljivi. • U čemu je razlika između WFI i WFE? Postoje dva low power režima: Nakon WFI čeka se prekid, i prvo što se izvršava jetakt prekidna rutina. a periferijski je aktivan – SLEEP – procesorski je isključen, WFE jednostavno se nastavlja – DEEPSLEEP –Nakon tipično ni jedan takt ne radi, ali zavisi i od izvršavanje programa. konkretne implementacije. Napajanje za SRAM ili FLASH može biti isključeno, što opet zavisi od implementacije.

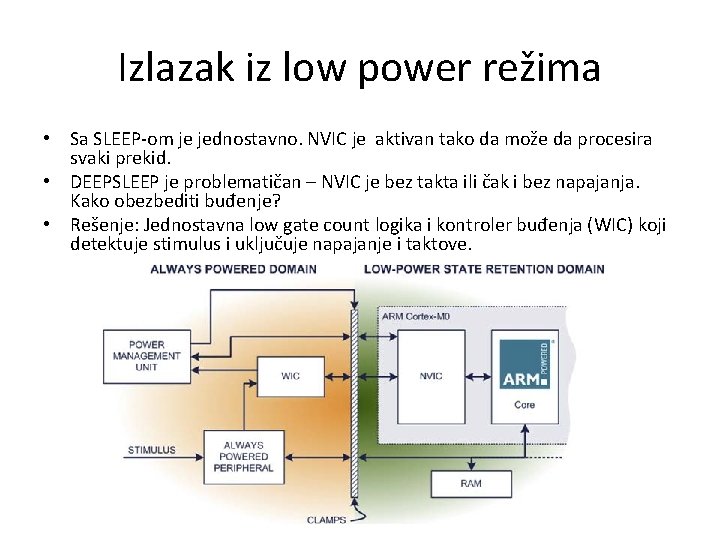

Izlazak iz low power režima • Sa SLEEP-om je jednostavno. NVIC je aktivan tako da može da procesira svaki prekid. • DEEPSLEEP je problematičan – NVIC je bez takta ili čak i bez napajanja. Kako obezbediti buđenje? • Rešenje: Jednostavna low gate count logika i kontroler buđenja (WIC) koji detektuje stimulus i uključuje napajanje i taktove.

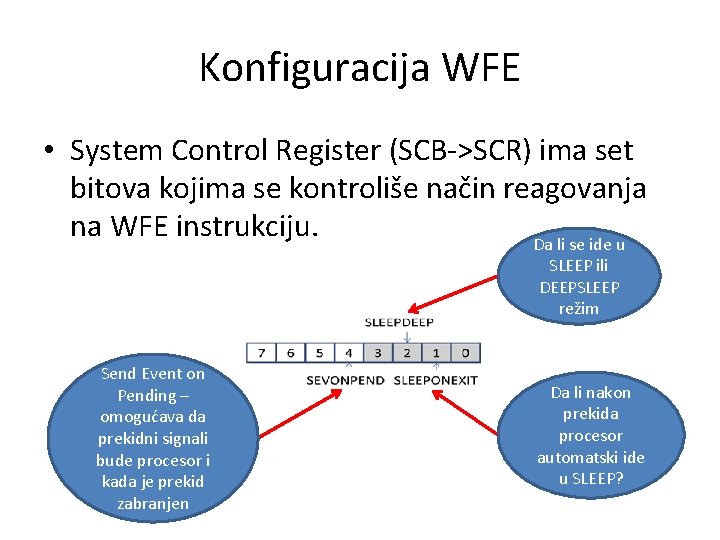

Konfiguracija WFE • System Control Register (SCB->SCR) ima set bitova kojima se kontroliše način reagovanja na WFE instrukciju. Da li se ide u SLEEP ili DEEPSLEEP režim Send Event on Pending – omogućava da prekidni signali bude procesor i kada je prekid zabranjen Da li nakon prekida procesor automatski ide u SLEEP?

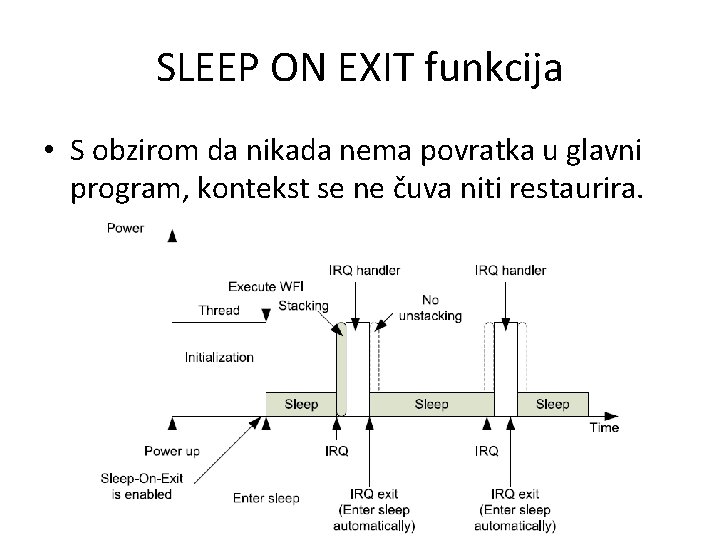

SLEEP ON EXIT funkcija • S obzirom da nikada nema povratka u glavni program, kontekst se ne čuva niti restaurira.

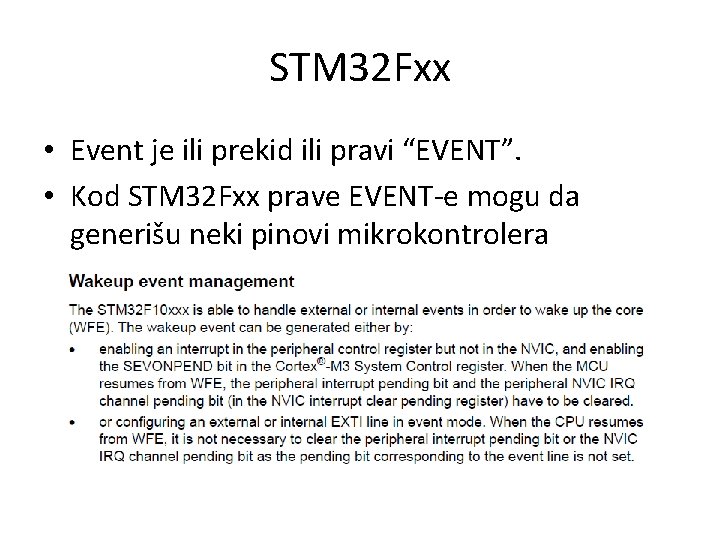

STM 32 Fxx • Event je ili prekid ili pravi “EVENT”. • Kod STM 32 Fxx prave EVENT-e mogu da generišu neki pinovi mikrokontrolera

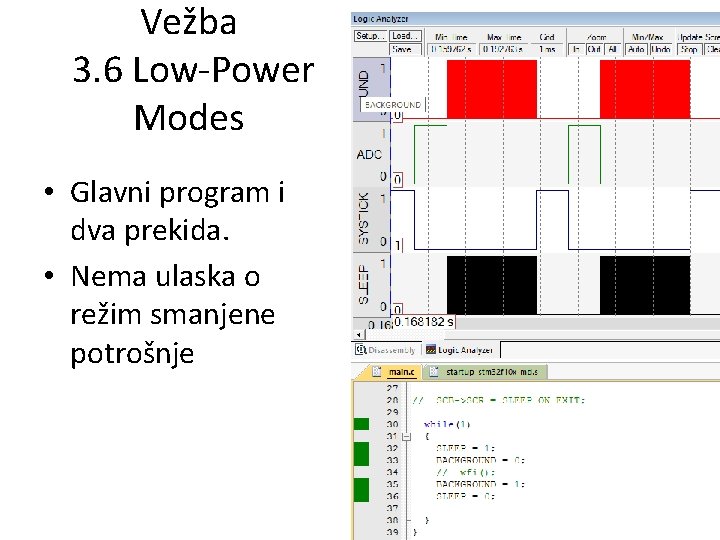

Vežba 3. 6 Low-Power Modes • Glavni program i dva prekida. • Nema ulaska o režim smanjene potrošnje

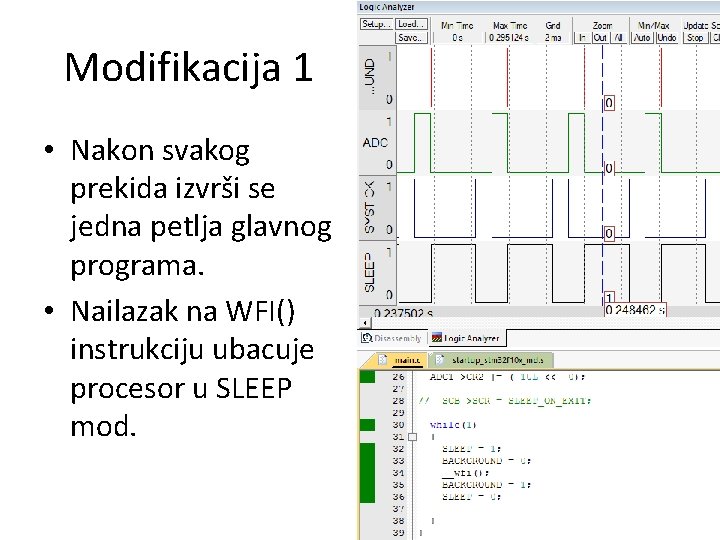

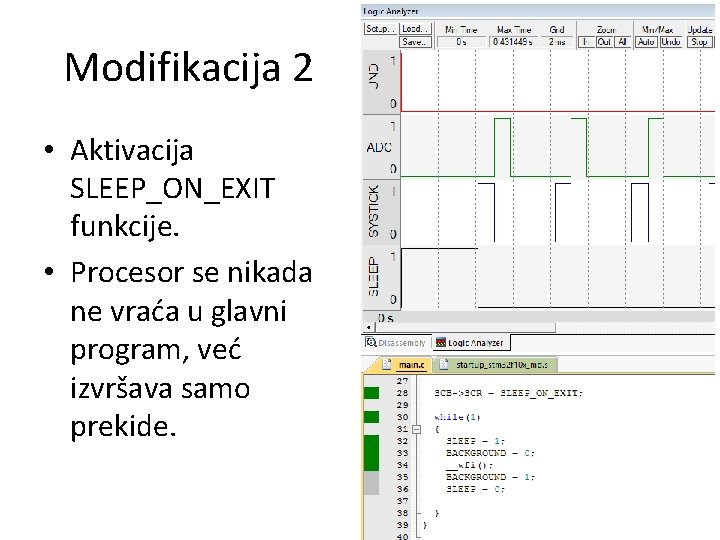

Modifikacija 1 • Nakon svakog prekida izvrši se jedna petlja glavnog programa. • Nailazak na WFI() instrukciju ubacuje procesor u SLEEP mod.

Modifikacija 2 • Aktivacija SLEEP_ON_EXIT funkcije. • Procesor se nikada ne vraća u glavni program, već izvršava samo prekide.

Cortex-M vs. ostali u. C-ovi • Cortex-M mikrokontroleri su dominantni na tržištu 32 bitnih mikrokontrolera. • 17 Vendora trenutno oproizvodi svoje varijante Cortex-M mikrokontrolera. • Prakitčno nemaju konkurenciju. • Šta održava takvo stanje? Zašto Vendori ne prave svoje miktokontrolere? • Prave ih ako imaju nešto baš specifično. Kao MSP, koji je na primer ultra low power. • Šta je dobro kod Cortex-a? Dobro je to što postoji razvijena podrška, alati, community i slično. • Čime se diferenciraju Vendori? Specijalnim periferijama, prilagođenim realizacijama i slično.

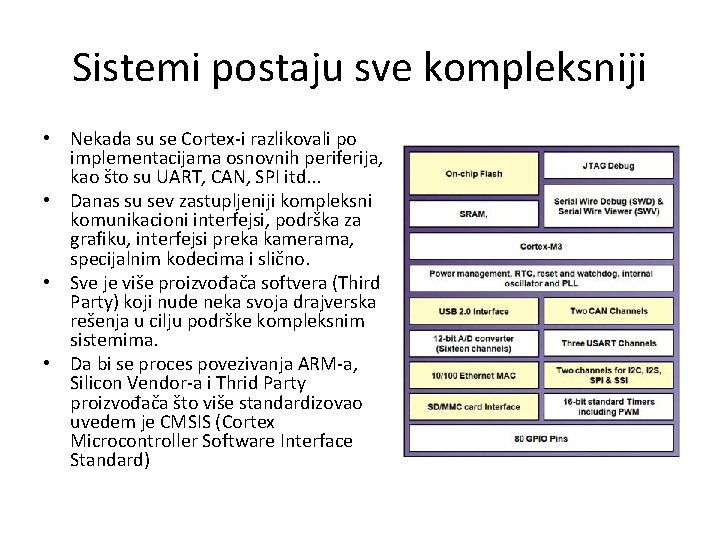

Sistemi postaju sve kompleksniji • Nekada su se Cortex-i razlikovali po implementacijama osnovnih periferija, kao što su UART, CAN, SPI itd. . . • Danas su sev zastupljeniji kompleksni komunikacioni interfejsi, podrška za grafiku, interfejsi preka kamerama, specijalnim kodecima i slično. • Sve je više proizvođača softvera (Third Party) koji nude neka svoja drajverska rešenja u cilju podrške kompleksnim sistemima. • Da bi se proces povezivanja ARM-a, Silicon Vendor-a i Thrid Party proizvođača što više standardizovao uvedem je CMSIS (Cortex Microcontroller Software Interface Standard)

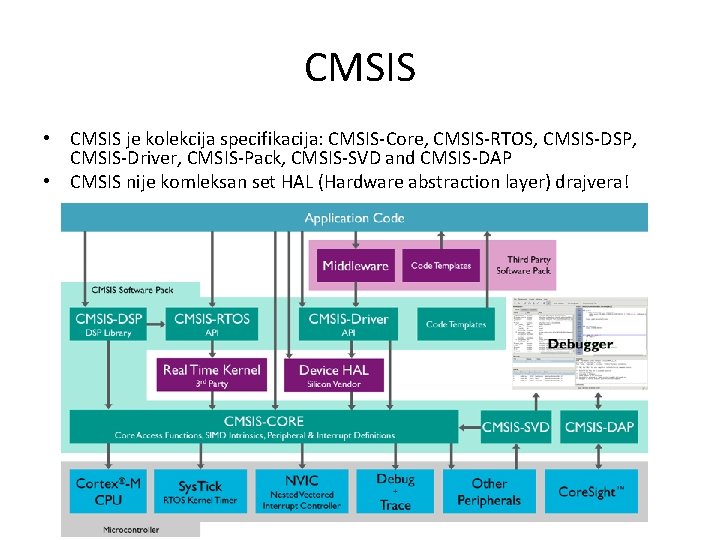

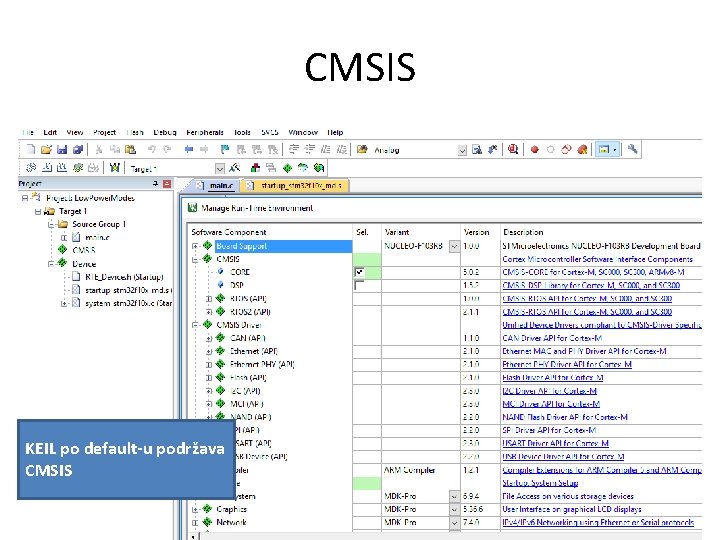

CMSIS • CMSIS je kolekcija specifikacija: CMSIS-Core, CMSIS-RTOS, CMSIS-DSP, CMSIS-Driver, CMSIS-Pack, CMSIS-SVD and CMSIS-DAP • CMSIS nije komleksan set HAL (Hardware abstraction layer) drajvera!

CMSIS KEIL po default-u podržava CMSIS

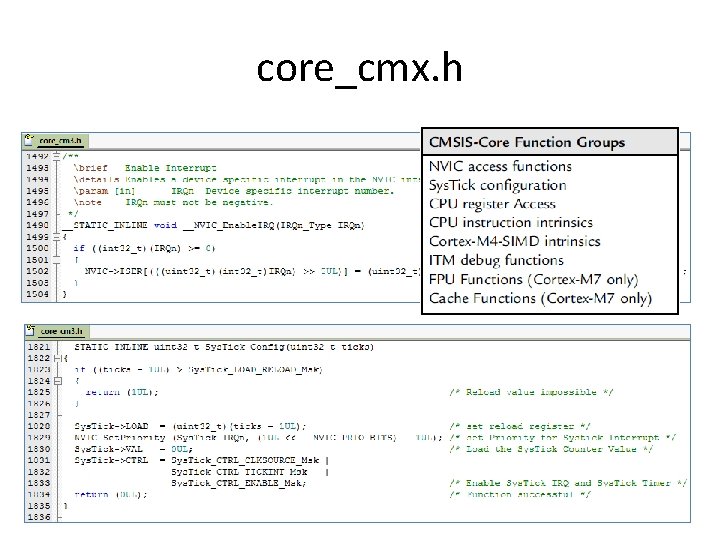

CMSIS-Core • CMSIS-Core – Set funkcija i makroa za pristup svim registrima u koje spadaju Sys. Tick, NVIC, System Control Block registers, MPU registers, FPU registers. • Definicije su u core_cmx. h fajlu. • Standardizuje se System. Init() funkcija koju prilagođava svaki Vendor i u kojoj se vrši osnovno podešavanje takta. • Standardizuje se globalna promenljiva System. Core. Clock

CMSIS-RTOS • Set funkcija koje prilagođavaju CMSIS-RTOS API na API specifičnog RTOS-a. • Prvi RTOS koji je izveden na bazi CMSIS-RTOS API-ja je KEIL-ov RTX RTOS, koji je otvoren i besplatan. • Set funkcija je definisan u cmsis_os. h fajlu. • RTX RTOS podleže Berkeley Software Distribution (BSD) licenci i može da se koristi i u komercijalne i nekomercijalne svrhe.

CMSIS-DSP • Sadrži preko 60 implementacija najčešće korišćenih matematički zahtevnih funkcija koje se koriste u digitalnoj obradi signala. • Iako su optimizovane za Cortex-M 4 i Cortex. M 7 mogu se prekompajlirati i za Cortex-M 3. • O ovome ćemo više govoriti kansije.

CMSIS-Driver • Standardni API za korišćenje najrazličitijih standardnih periferija – od jednostavnjih kao što su UART, SPI, I 2 C, do kompleksnih kao što su USB, ETHERNET, CAN. . . • Suština je obezbeđivanje podrške za pisanje drajvera.

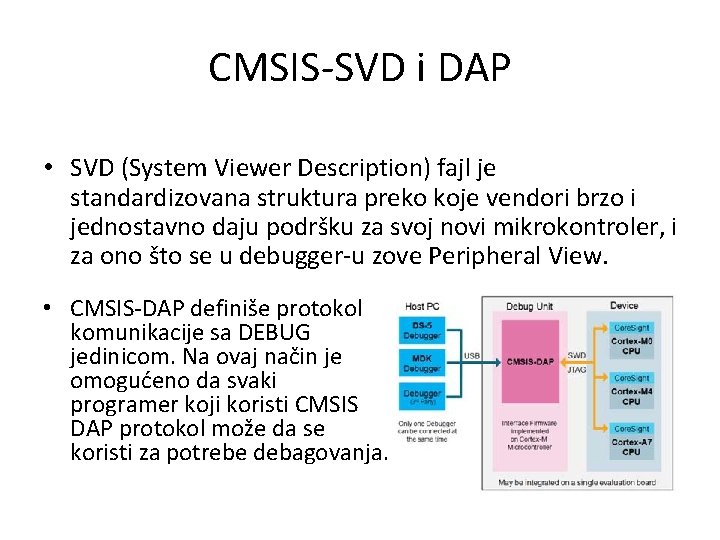

CMSIS-SVD i DAP • SVD (System Viewer Description) fajl je standardizovana struktura preko koje vendori brzo i jednostavno daju podršku za svoj novi mikrokontroler, i za ono što se u debugger-u zove Peripheral View. • CMSIS-DAP definiše protokol komunikacije sa DEBUG jedinicom. Na ovaj način je omogućeno da svaki programer koji koristi CMSIS DAP protokol može da se koristi za potrebe debagovanja.

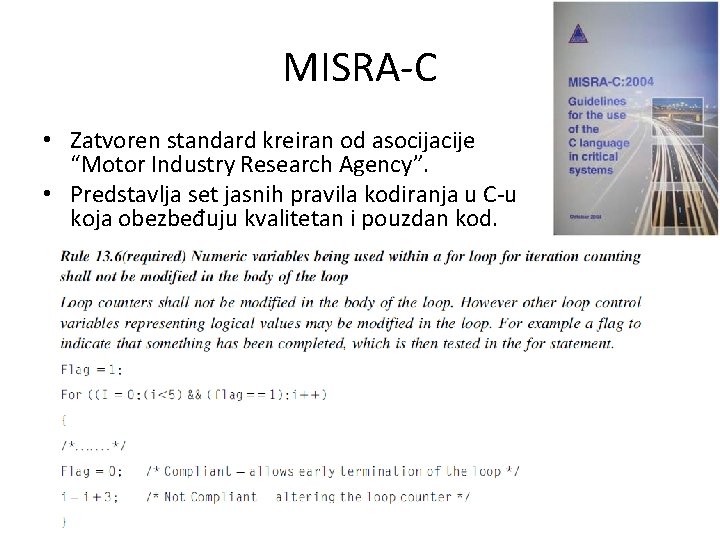

MISRA-C • Zatvoren standard kreiran od asocijacije “Motor Industry Research Agency”. • Predstavlja set jasnih pravila kodiranja u C-u koja obezbeđuju kvalitetan i pouzdan kod.

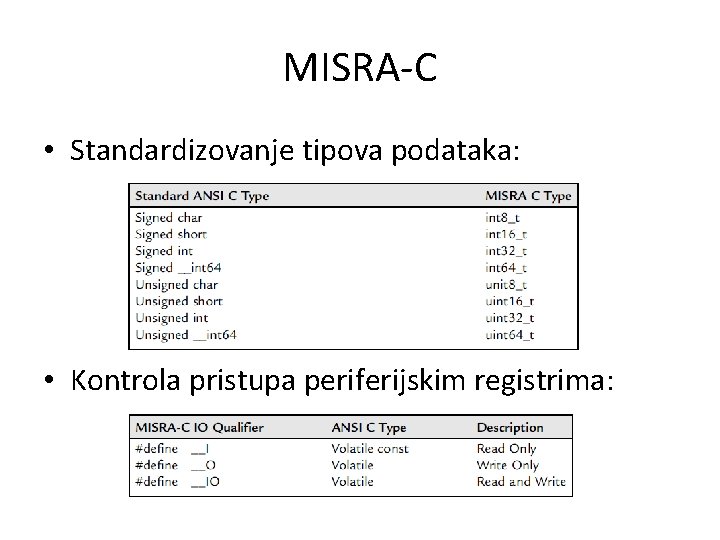

MISRA-C • Standardizovanje tipova podataka: • Kontrola pristupa periferijskim registrima:

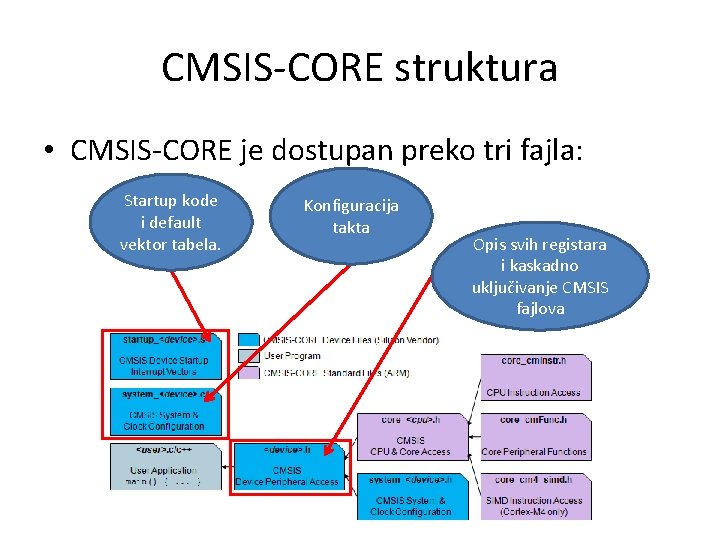

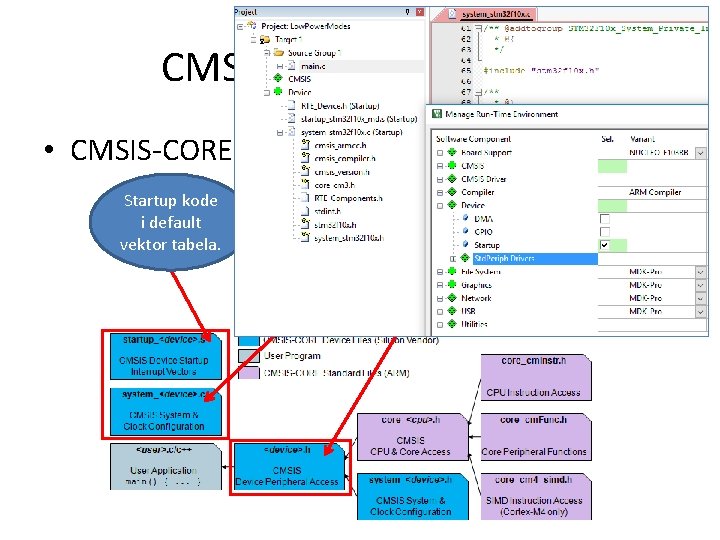

CMSIS-CORE struktura • CMSIS-CORE je dostupan preko tri fajla: Startup kode i default vektor tabela. Konfiguracija takta Opis svih registara i kaskadno uključivanje CMSIS fajlova

CMSIS-CORE struktura • CMSIS-CORE je dostupan preko tri fajla: Startup kode i default vektor tabela. Konfiguracija takta Opis svih registara i kaskadno uključivanje CMSIS fajlova

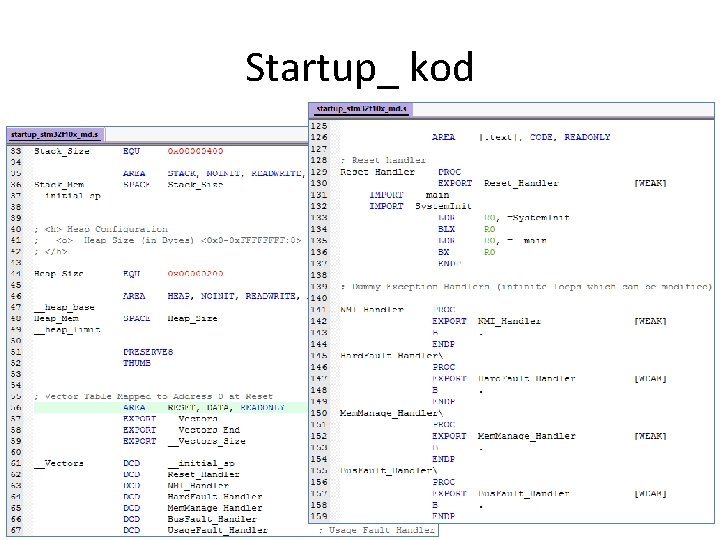

Startup_ kod • Inicijalizacija steka i tabele vektora prekida

System_ kod Svaki Vendor i svaki mikrokontroler može da ima drugačija podešavanja

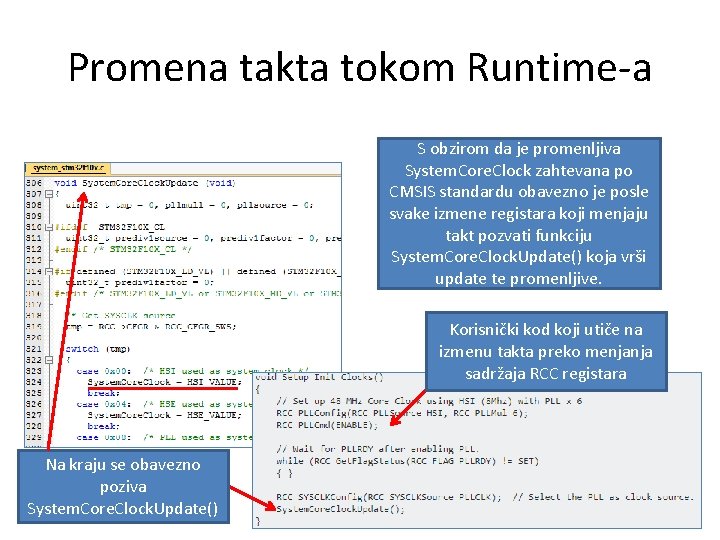

Promena takta tokom Runtime-a S obzirom da je promenljiva System. Core. Clock zahtevana po CMSIS standardu obavezno je posle svake izmene registara koji menjaju takt pozvati funkciju System. Core. Clock. Update() koja vrši update te promenljive. Korisnički kod koji utiče na izmenu takta preko menjanja sadržaja RCC registara Na kraju se obavezno poziva System. Core. Clock. Update()

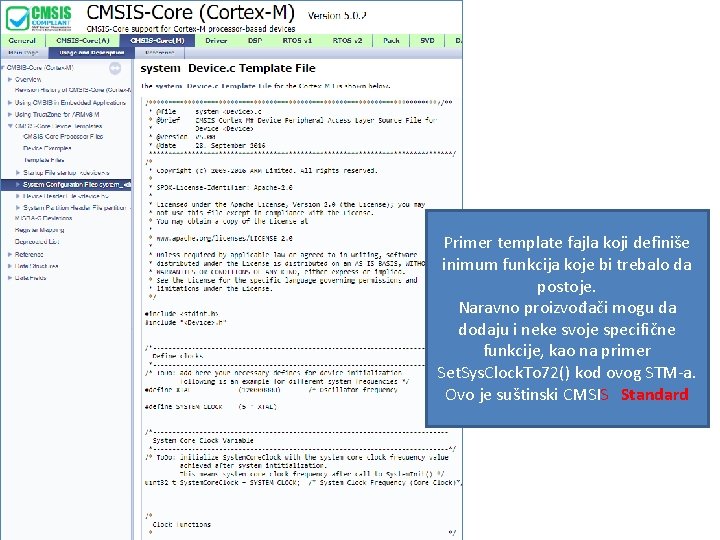

Primer template fajla koji definiše inimum funkcija koje bi trebalo da postoje. Naravno proizvođači mogu da dodaju i neke svoje specifične funkcije, kao na primer Set. Sys. Clock. To 72() kod ovog STM-a. Ovo je suštinski CMSIS Standard

<device>. h Device Header File • Definicije svih periferijskih registara

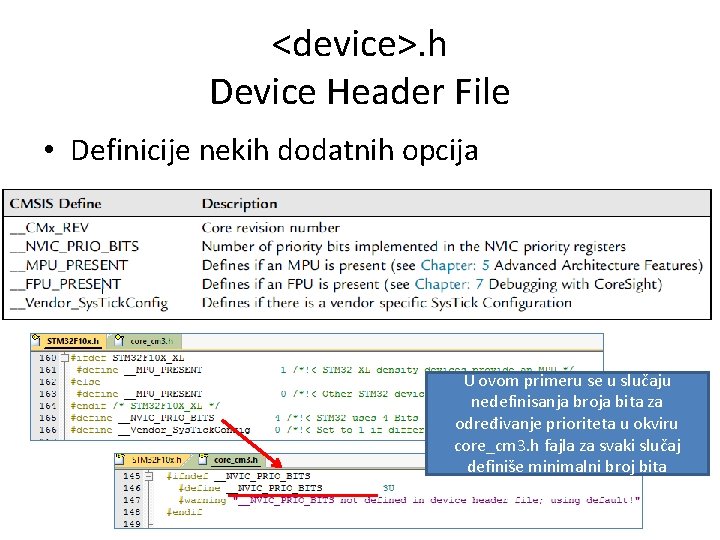

<device>. h Device Header File • Definicije nekih dodatnih opcija U ovom primeru se u slučaju nedefinisanja broja bita za određivanje prioriteta u okviru core_cm 3. h fajla za svaki slučaj definiše minimalni broj bita

core_cmx. h

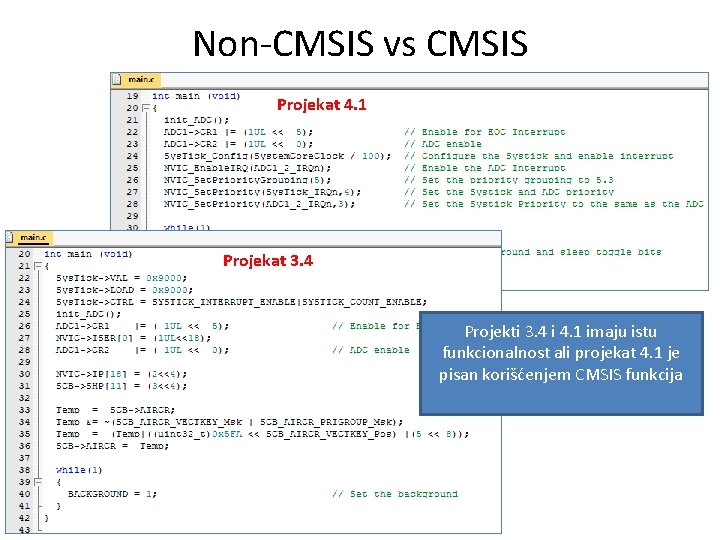

Non-CMSIS vs CMSIS Projekat 4. 1 Projekat 3. 4 Projekti 3. 4 i 4. 1 imaju istu funkcionalnost ali projekat 4. 1 je pisan korišćenjem CMSIS funkcija

Šta je još definisano u core_cmx. h? Interesantno je da je implementacija ovih funkcija nevidljiva je su ugrađene su u sam kompajler!

STM 32 L 476 RG – kopamo dublje • STM 32 L 476 xx – MCU Datasheet – Provera karakteristika pri izboru mikrokontrolera – Alternate pin function – Additional pin function • STM 32 Nucleo-64 board – User Manual – Solder bridges • STM 32 L 4 x 5 and STM 32 L 4 x 6 advanced ARM®based 32 -bit MCUs - Reference Manual – Sve što ste hteli da znate ali vas mrzi da čitate

STM Cortex-M - GPIO - Portovi • 5 V tolerantni ulazi • Kapacitet po pinu 25 m. A • 18 MHz učestanost toglovanja • Konfigurabilna izlazna brzina do 50 MHz • Do 16 analognih ulaza • Alternativne funkcije (USARTx, TIMx, I 2 Cx, SPIx, …) • Svaki pin može da generiše spoljašnji prekid • Jedan pin može da se koristi za buđenje iz STANDBY moda (PA. 00) • Jedan pin može da bude Tamper Pin (za watchdog) (PC. 13) • Pinovi grupisani u 5 16 -bitnih portova (GPIOA. . GPIOE) • Mehanizam zaključavanja konfiguracije

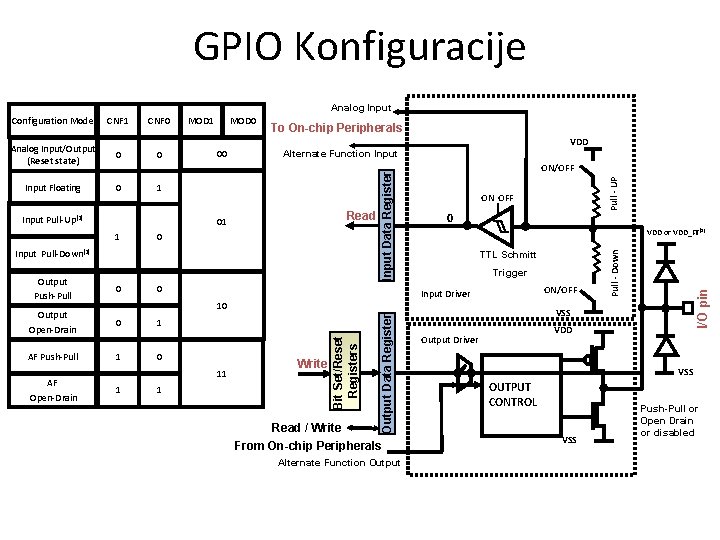

GPIO Konfiguracije Analog Input Configuration Mode CNF 1 CNF 0 Analog Input/Output (Reset state) 0 0 Input Floating 0 MOD 1 MOD 0 To On-chip Peripherals VDD Alternate Function Input 1 0 Input Pull-Down(2) Output Push-Pull 0 Output Open-Drain 0 AF Push-Pull 1 1 1 Write Output Data Register 10 0 0 VDD or VDD_FT(1) TTL Schmitt Trigger ON/OFF Input Driver Bit Set/Reset Registers AF Open-Drain 0 Read / Write From On-chip Peripherals Alternate Function Output Pull - UP Read 01 ON OFF I/O pin Input Pull-Up(2) ON/OFF Pull - Down 1 Input Data Register 00 VSS VDD Output Driver VSS OUTPUT CONTROL VSS Push-Pull or Open Drain or disabled

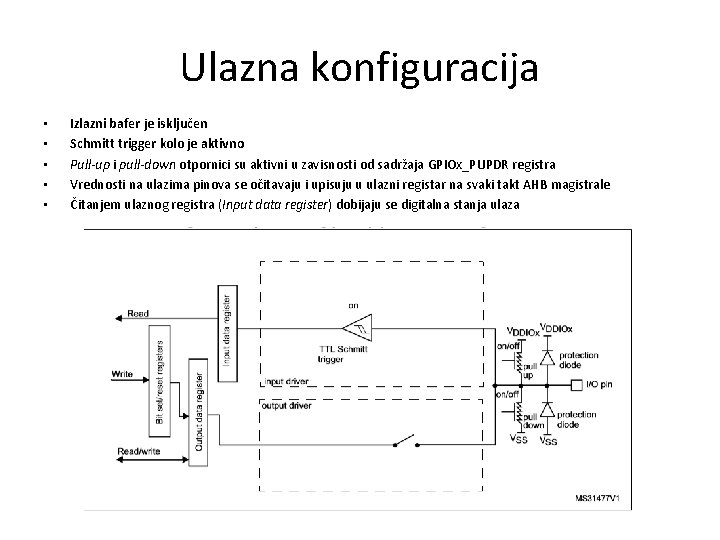

Ulazna konfiguracija • • • Izlazni bafer je isključen Schmitt trigger kolo je aktivno Pull-up i pull-down otpornici su aktivni u zavisnosti od sadržaja GPIOx_PUPDR registra Vrednosti na ulazima pinova se očitavaju i upisuju u ulazni registar na svaki takt AHB magistrale Čitanjem ulaznog registra (Input data register) dobijaju se digitalna stanja ulaza

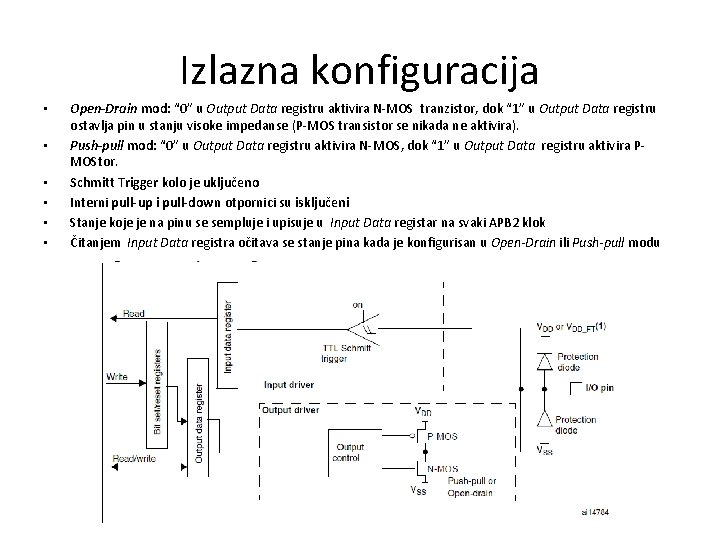

Izlazna konfiguracija • • • Open-Drain mod: “ 0” u Output Data registru aktivira N-MOS tranzistor, dok “ 1” u Output Data registru ostavlja pin u stanju visoke impedanse (P-MOS transistor se nikada ne aktivira). Push-pull mod: “ 0” u Output Data registru aktivira N-MOS, dok “ 1” u Output Data registru aktivira PMOStor. Schmitt Trigger kolo je uključeno Interni pull-up i pull-down otpornici su isključeni Stanje koje je na pinu se sempluje i upisuje u Input Data registar na svaki APB 2 klok Čitanjem Input Data registra očitava se stanje pina kada je konfigurisan u Open-Drain ili Push-pull modu

Konfiguracija alternativne funkcije • • • Izlazni dajver je u Open Drain ili Push-Pull konfiguraciji Schmitt Trigger ulaz je aktiviran Pull-up i pull-down otpornici su deaktivirani Podatak na pinu se sempluje u ulazni registar na svaku ivicu APB 2 takta Ako je izlaz u open drain modu očitavanje ulaznog registra daje stanje na pinu

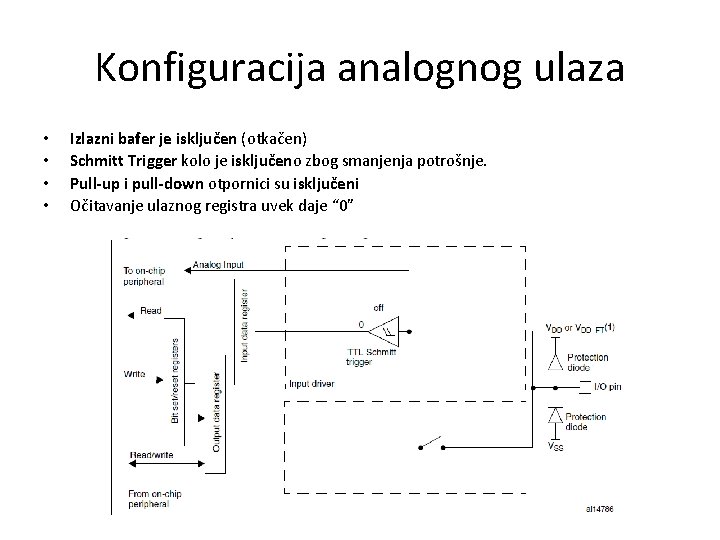

Konfiguracija analognog ulaza • • Izlazni bafer je isključen (otkačen) Schmitt Trigger kolo je isključeno zbog smanjenja potrošnje. Pull-up i pull-down otpornici su isključeni Očitavanje ulaznog registra uvek daje “ 0”

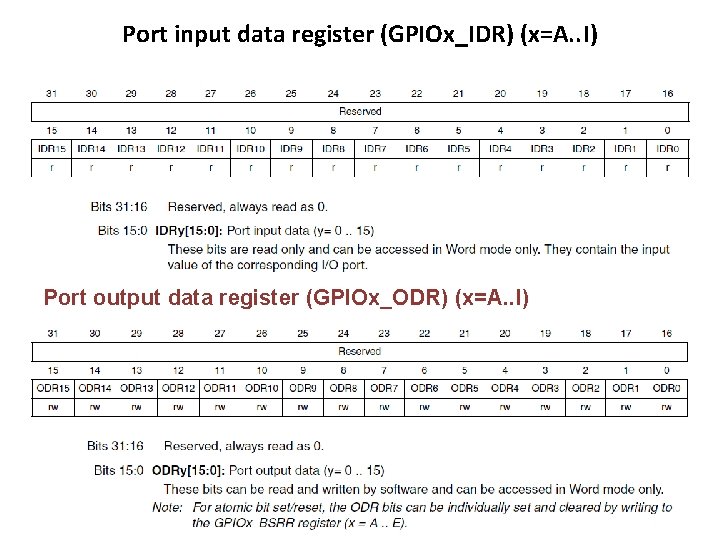

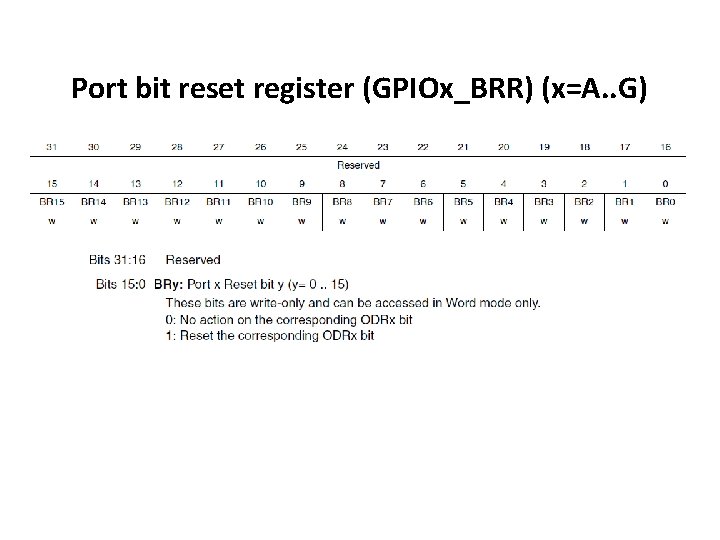

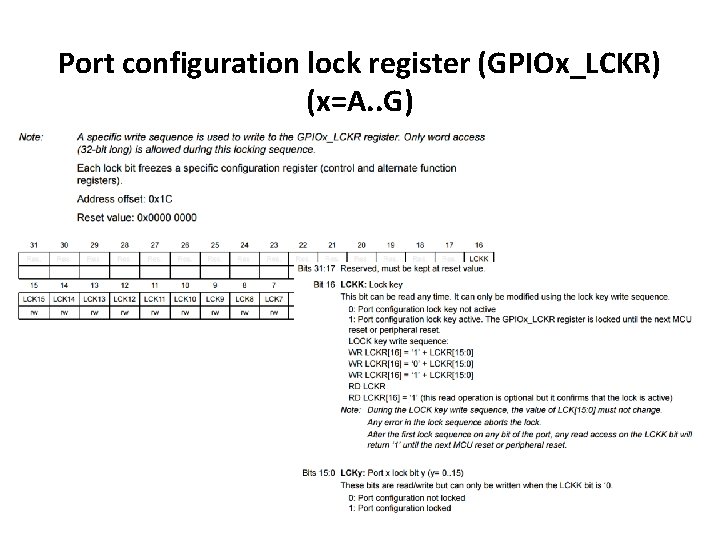

GPIO registri • Četiri 32 -bitna konfiguraciona registra (GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR, GPIOx_PUPDR) • Dva 32 -bitna data registra (GPIOx_IDR, GPIOx_ODR) • Jedan 32 -bitni set/reset registar (GPIOx_BSRR) • Jedan 16 -bitni reset registar (GPIOx_BRR) • Jedan 32 -bitni locking registar (GPIOx_LCKR) • Dva 32 -bitna alternate function selekciona registra (GPIOx_AFRH, GPIOx_AFRL)

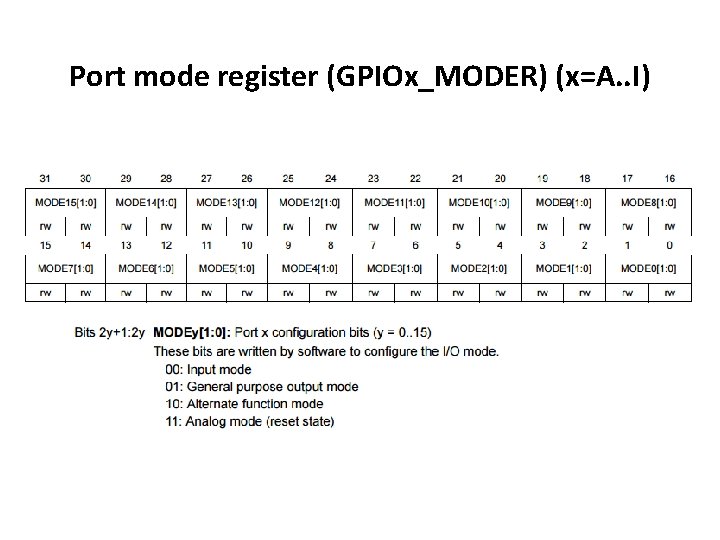

Port mode register (GPIOx_MODER) (x=A. . I)

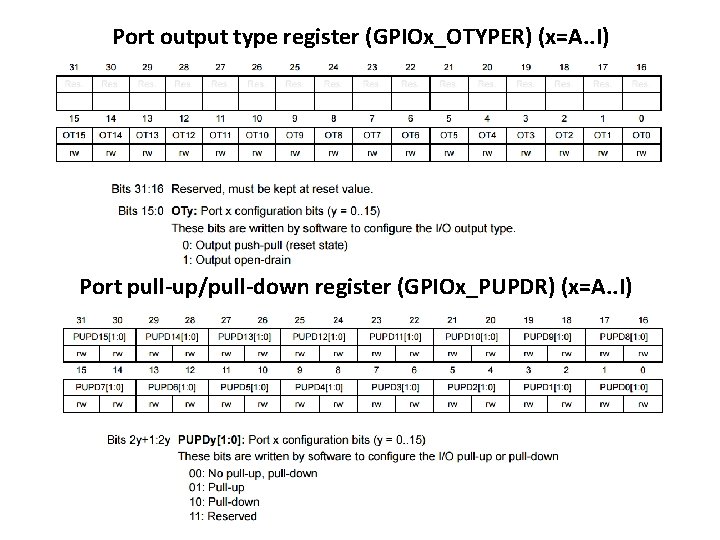

Port output type register (GPIOx_OTYPER) (x=A. . I) Port pull-up/pull-down register (GPIOx_PUPDR) (x=A. . I)

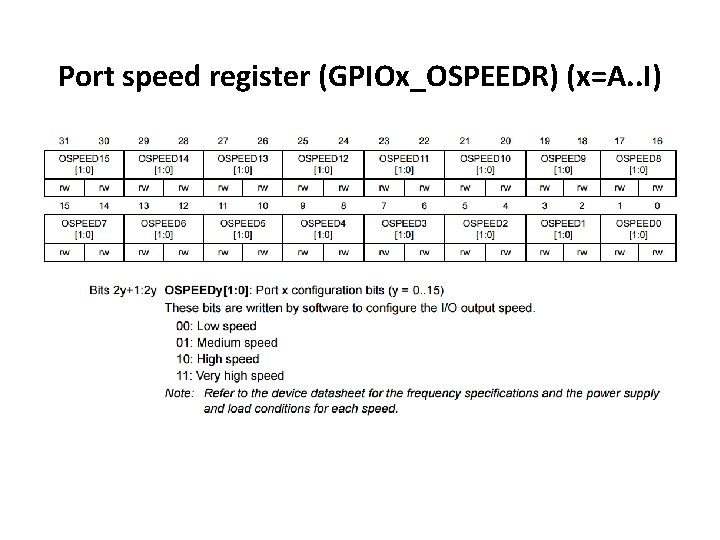

Port speed register (GPIOx_OSPEEDR) (x=A. . I)

Port input data register (GPIOx_IDR) (x=A. . I) Port output data register (GPIOx_ODR) (x=A. . I)

Port bit set/reset register (GPIOx_BSRR) (x=A. . G)

Port bit reset register (GPIOx_BRR) (x=A. . G)

Port configuration lock register (GPIOx_LCKR) (x=A. . G)

• STM 32 L 4 x 5 and STM 32 L 4 x 6 advanced ARM®-based 32 -bit MCUs

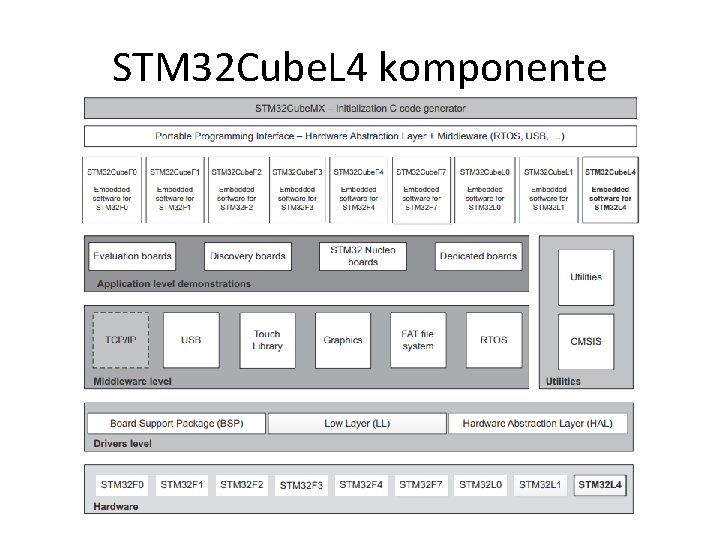

STM 32 Cube. L 4 komponente Sa adrese • tnt. etf. rs/~ms 1 bmp/stm 32 cubel 4. zip • (za F 103 RB tnt. etf. rs/~ms 1 bmp/stm 32 cubef 1. zip) skinuti. zip fajl i raspakovati ga u folder E: /MS 1 BMP

STM 32 Cube. L 4 komponente

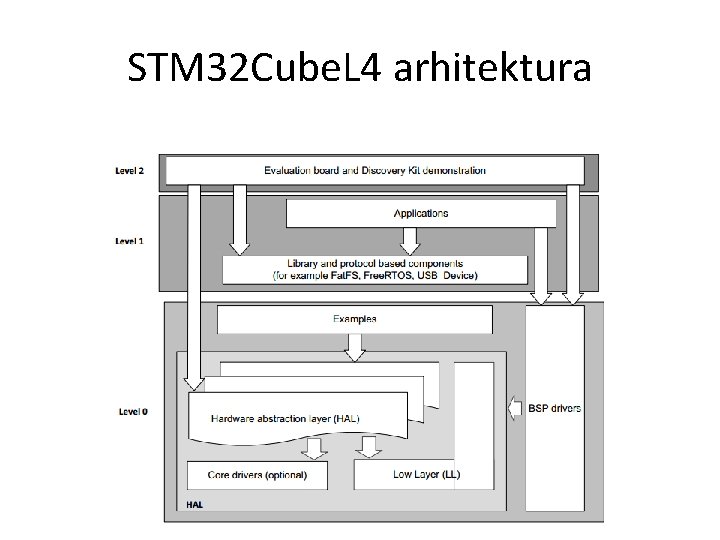

STM 32 Cube. L 4 arhitektura

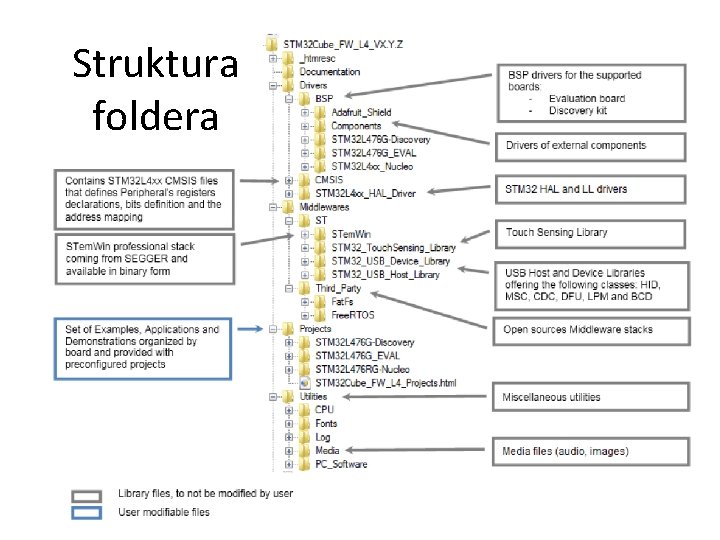

Struktura foldera

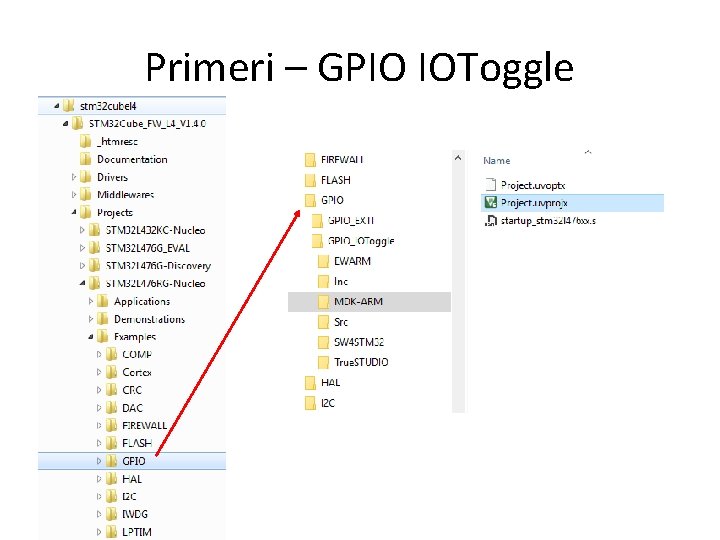

Primeri – GPIO IOToggle

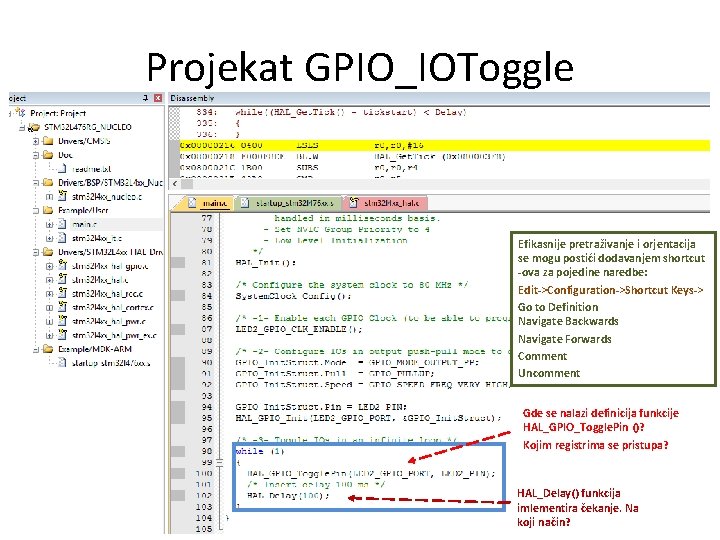

Projekat GPIO_IOToggle Efikasnije pretraživanje i orjentacija se mogu postići dodavanjem shortcut -ova za pojedine naredbe: Edit->Configuration->Shortcut Keys-> Go to Definition Navigate Backwards Navigate Forwards Comment Uncomment Gde se nalazi definicija funkcije HAL_GPIO_Toggle. Pin ()? Kojim registrima se pristupa? HAL_Delay() funkcija imlementira čekanje. Na koji način?

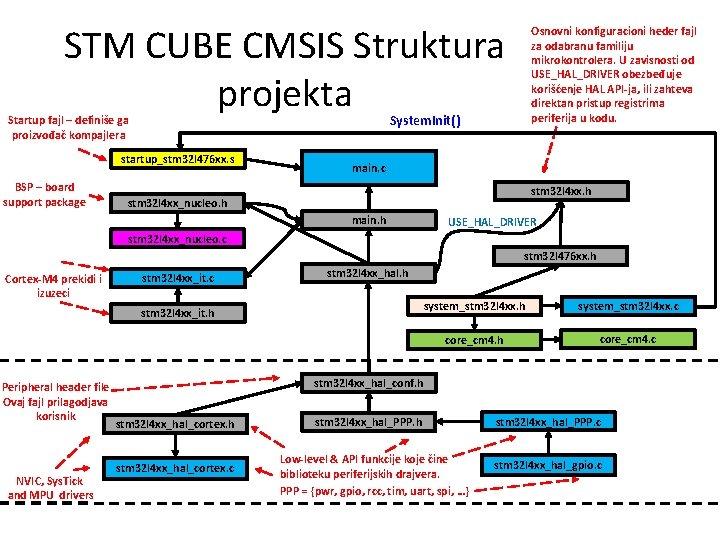

STM CUBE CMSIS Struktura projekta System. Init() Startup fajl – definiše ga proizvođač kompajlera startup_stm 32 l 476 xx. s BSP – board support package Osnovni konfiguracioni heder fajl za odabranu familiju mikrokontrolera. U zavisnosti od USE_HAL_DRIVER obezbeđuje korišćenje HAL API-ja, ili zahteva direktan pristup registrima periferija u kodu. main. c stm 32 l 4 xx. h stm 32 l 4 xx_nucleo. h main. h USE_HAL_DRIVER stm 32 l 4 xx_nucleo. c stm 32 l 476 xx. h Cortex-M 4 prekidi i izuzeci stm 32 l 4 xx_it. c stm 32 l 4 xx_hal. h stm 32 l 4 xx_it. h Peripheral header file Ovaj fajl prilagodjava korisnik NVIC, Sys. Tick and MPU drivers system_stm 32 l 4 xx. h system_stm 32 l 4 xx. c core_cm 4. h core_cm 4. c stm 32 l 4 xx_hal_conf. h stm 32 l 4 xx_hal_cortex. c stm 32 l 4 xx_hal_PPP. h Low-level & API funkcije koje čine biblioteku periferijskih drajvera. PPP = {pwr, gpio, rcc, tim, uart, spi, …} stm 32 l 4 xx_hal_PPP. c stm 32 l 4 xx_hal_gpio. c

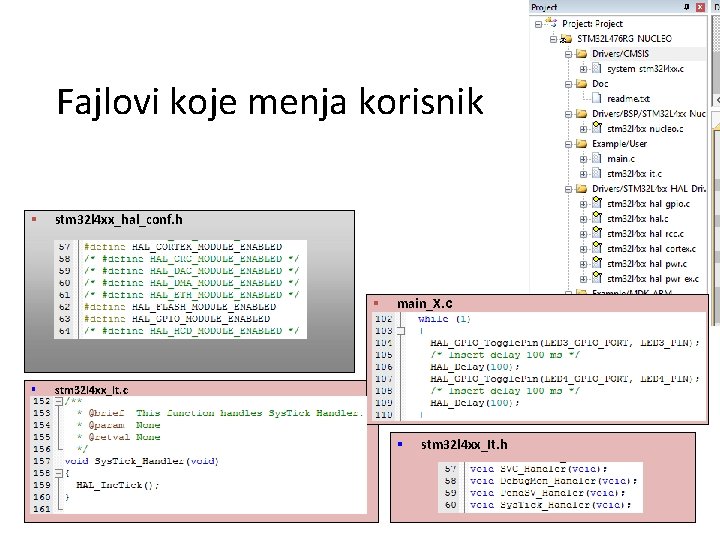

Osnovni konfiguracioni heder fajl za odabranu familiju mikrokontrolera. U zavisnosti od USE_HAL_DRIVER obezbeđuje korišćenje HAL API-ja, ili zahteva direktan pristup registrima periferija u kodu. Fajlovi koje menja korisnik System. Init() Startup fajl – definiše ga proizvođač kompajlera startup_stm 32 l 476 xx. s BSP – board support package main. c stm 32 l 4 xx. h stm 32 l 4 xx_nucleo. h main. h stm 32 l 4 xx_nucleo. c Cortex-M 4 prekidi i izuzeci stm 32 l 4 xx_it. c stm 32 l 476 xx. h stm 32 l 4 xx_hal. h stm 32 l 4 xx_it. h Peripheral header file Ovaj fajl prilagodjava korisnik NVIC, Sys. Tick and MPU drivers system_stm 32 l 4 xx. h system_stm 32 l 4 xx. c core_cm 4. h core_cm 4. c stm 32 l 4 xx_hal_conf. h stm 32 l 4 xx_hal_cortex. c stm 32 l 4 xx_hal_PPP. h Low-level & API funkcije koje čine biblioteku periferijskih drajvera. PPP = {pwr, gpio, rcc, tim, uart, spi, …} stm 32 l 4 xx_hal_PPP. c stm 32 l 4 xx_hal_gpio. c

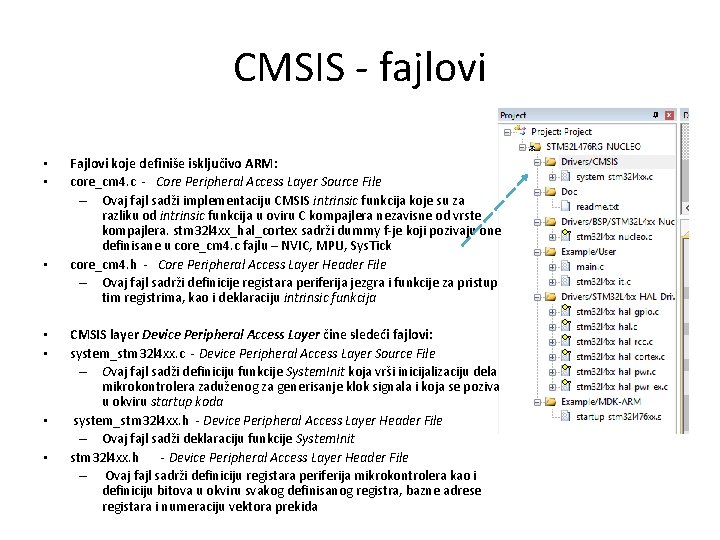

CMSIS - fajlovi • • Fajlovi koje definiše isključivo ARM: core_cm 4. c - Core Peripheral Access Layer Source File – Ovaj fajl sadži implementaciju CMSIS intrinsic funkcija koje su za razliku od intrinsic funkcija u oviru C kompajlera nezavisne od vrste kompajlera. stm 32 l 4 xx_hal_cortex sadrži dummy f-je koji pozivaju one definisane u core_cm 4. c fajlu – NVIC, MPU, Sys. Tick core_cm 4. h - Core Peripheral Access Layer Header File – Ovaj fajl sadrži definicije registara periferija jezgra i funkcije za pristup tim registrima, kao i deklaraciju intrinsic funkcija CMSIS layer Device Peripheral Access Layer čine sledeći fajlovi: system_stm 32 l 4 xx. c - Device Peripheral Access Layer Source File – Ovaj fajl sadži definiciju funkcije System. Init koja vrši inicijalizaciju dela mikrokontrolera zaduženog za generisanje klok signala i koja se poziva u okviru startup koda system_stm 32 l 4 xx. h - Device Peripheral Access Layer Header File – Ovaj fajl sadži deklaraciju funkcije System. Init stm 32 l 4 xx. h - Device Peripheral Access Layer Header File – Ovaj fajl sadrži definiciju registara periferija mikrokontrolera kao i definiciju bitova u okviru svakog definisanog registra, bazne adrese registara i numeraciju vektora prekida

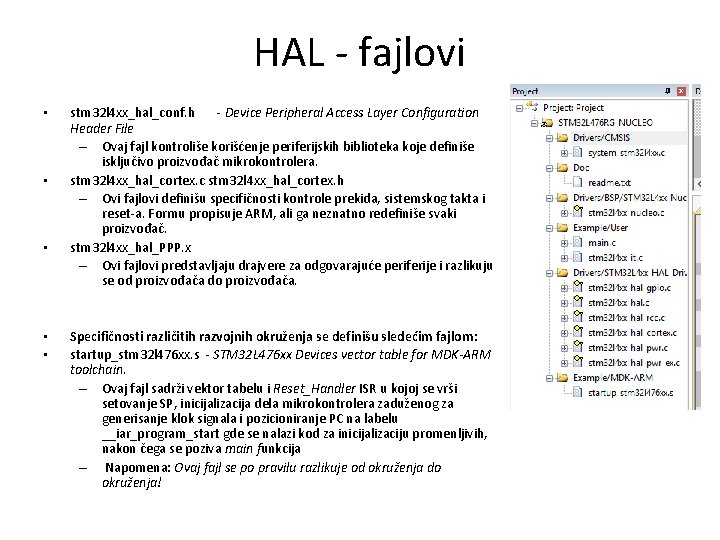

HAL - fajlovi • • • stm 32 l 4 xx_hal_conf. h - Device Peripheral Access Layer Configuration Header File – Ovaj fajl kontroliše korišćenje periferijskih biblioteka koje definiše isključivo proizvođač mikrokontrolera. stm 32 l 4 xx_hal_cortex. c stm 32 l 4 xx_hal_cortex. h – Ovi fajlovi definišu specifičnosti kontrole prekida, sistemskog takta i reset-a. Formu propisuje ARM, ali ga neznatno redefiniše svaki proizvođač. stm 32 l 4 xx_hal_PPP. x – Ovi fajlovi predstavljaju drajvere za odgovarajuće periferije i razlikuju se od proizvođača do proizvođača. Specifičnosti različitih razvojnih okruženja se definišu sledećim fajlom: startup_stm 32 l 476 xx. s - STM 32 L 476 xx Devices vector table for MDK-ARM toolchain. – Ovaj fajl sadrži vektor tabelu i Reset_Handler ISR u kojoj se vrši setovanje SP, inicijalizacija dela mikrokontrolera zaduženog za generisanje klok signala i pozicioniranje PC na labelu __iar_program_start gde se nalazi kod za inicijalizaciju promenljivih, nakon čega se poziva main funkcija – Napomena: Ovaj fajl se po pravilu razlikuje od okruženja do okruženja!

Fajlovi koje menja korisnik § stm 32 l 4 xx_hal_conf. h § § main_X. c stm 32 l 4 xx_It. c § stm 32 l 4 xx_It. h

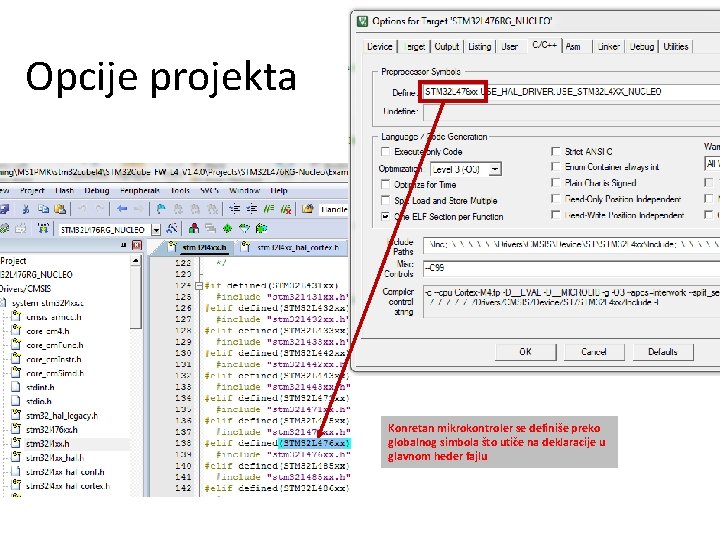

Opcije projekta Konretan mikrokontroler se definiše preko globalnog simbola što utiče na deklaracije u glavnom heder fajlu

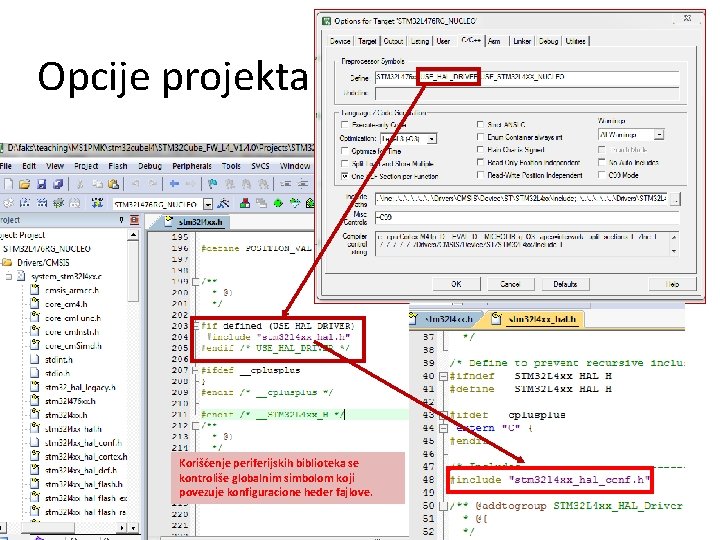

Opcije projekta Korišćenje periferijskih biblioteka se kontroliše globalnim simbolom koji povezuje konfiguracione heder fajlove.

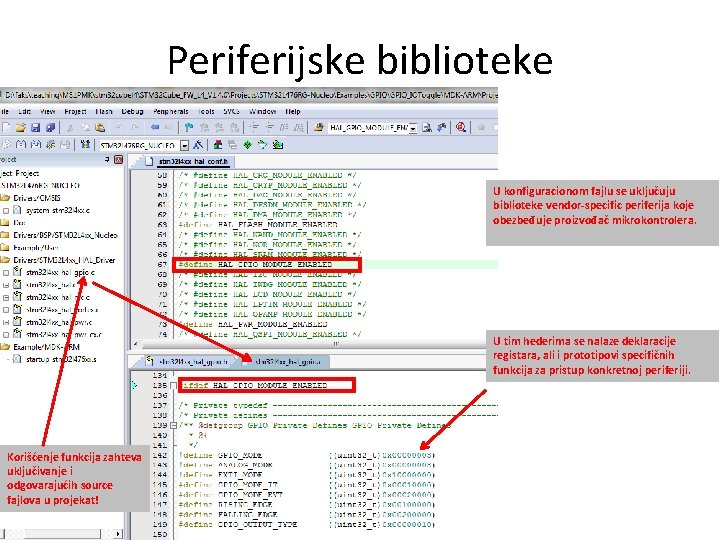

Periferijske biblioteke U konfiguracionom fajlu se uključuju biblioteke vendor-specific periferija koje obezbeđuje proizvođač mikrokontrolera. U tim hederima se nalaze deklaracije registara, ali i prototipovi specifičnih funkcija za pristup konkretnoj periferiji. Korišćenje funkcija zahteva uključivanje i odgovarajućih source fajlova u projekat!

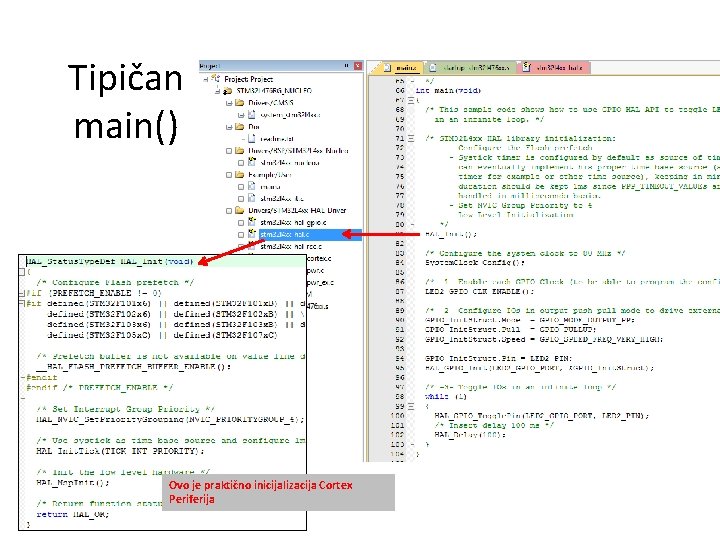

Tipičan main() Ovo je praktično inicijalizacija Cortex Periferija

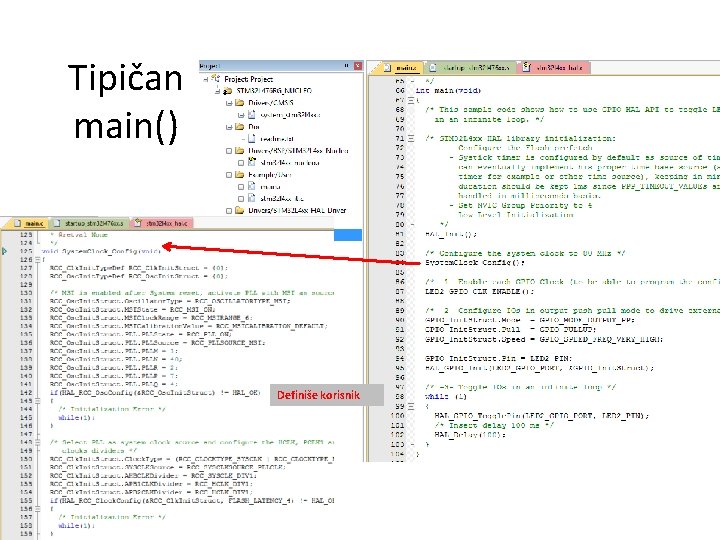

Tipičan main() Definiše korisnik

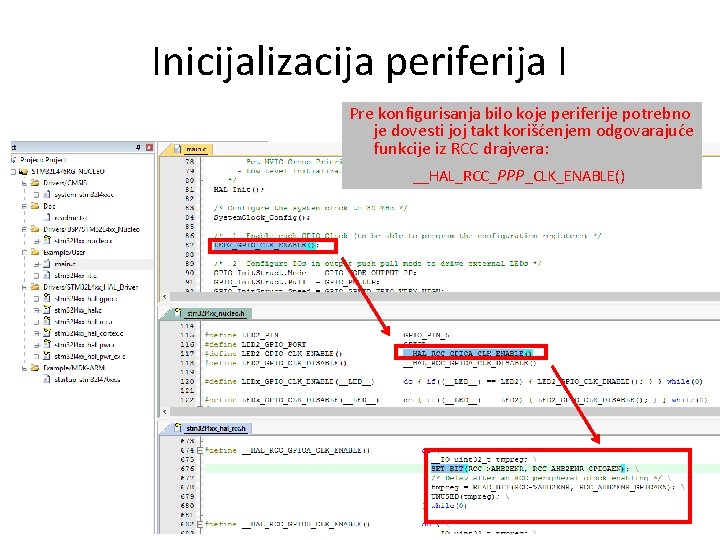

Inicijalizacija periferija I Pre konfigurisanja bilo koje periferije potrebno je dovesti joj takt korišćenjem odgovarajuće funkcije iz RCC drajvera: __HAL_RCC_PPP_CLK_ENABLE()

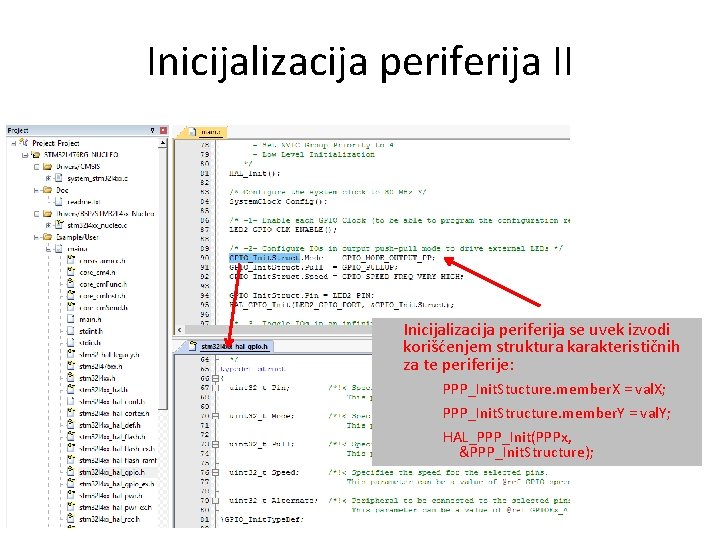

Inicijalizacija periferija II Inicijalizacija periferija se uvek izvodi korišćenjem struktura karakterističnih za te periferije: PPP_Init. Stucture. member. X = val. X; PPP_Init. Structure. member. Y = val. Y; HAL_PPP_Init(PPPx, &PPP_Init. Structure);

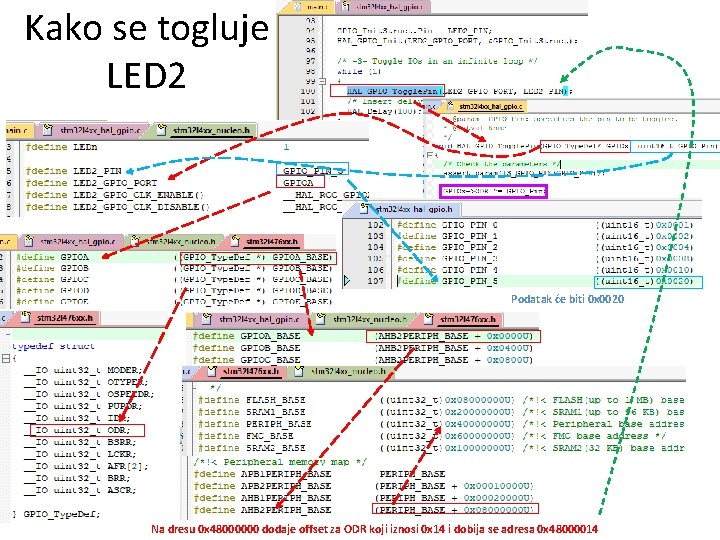

Kako se togluje LED 2 Podatak će biti 0 x 0020 Na dresu 0 x 48000000 dodaje offset za ODR koji iznosi 0 x 14 i dobija se adresa 0 x 48000014

LED Toggle - BSRR • Napisati funkciju GPIO_Toggle. Pin(GPIO_Type. Def* GPIOx, uint 16_t GPIO_Pin) koja vrši izmenu stanja izlaza pina upisujući u – BSR registar GPIO porta – BSR i BR registar GPIO porta • Testirati

- Slides: 68