SCIPP RD on the International Linear Collider Detector

![The SCIPP/UCSC ILC HARDWARE GROUP Faculty/Senior Post-Docs Alex Grillo [Gavin Nesom*] Hartmut Sadrozinski Jurgen The SCIPP/UCSC ILC HARDWARE GROUP Faculty/Senior Post-Docs Alex Grillo [Gavin Nesom*] Hartmut Sadrozinski Jurgen](https://slidetodoc.com/presentation_image_h2/b9c1d3a57baab44c5f0badae75876e6b/image-19.jpg)

- Slides: 29

SCIPP R&D on the International Linear Collider Detector SCIPP Review May 18, 2006 Presenter: Bruce Schumm

R&D Activity is increasing, with studies now on four fronts: Ø Physics and machine studies for e-e- running Ø Detector resolution standards from physics simulation Ø Reconstruction capabilities of all-silicon tracking Ø Hardware proof-of-principle of low-noise silicon strip readout Current involvements (all very much part time) 3 senior physicists, 1 post-doc (looking for a second), 8 (current) undergraduate students, 1 engineer, 2 technical staff, one bored spouse of a Silicon Valley engineer.

International Linear Collider: Activity on the e-e- Front Clem Heusch is the SCIPP participant in e-e- studies • Leading international effort in the use and application of e-e- beams at the ILC • Continuing series of workshops hosted by SCIPP; proceedings published in World Scientific • Heusch is a member of ILC Subcommittee on International Collaboration.

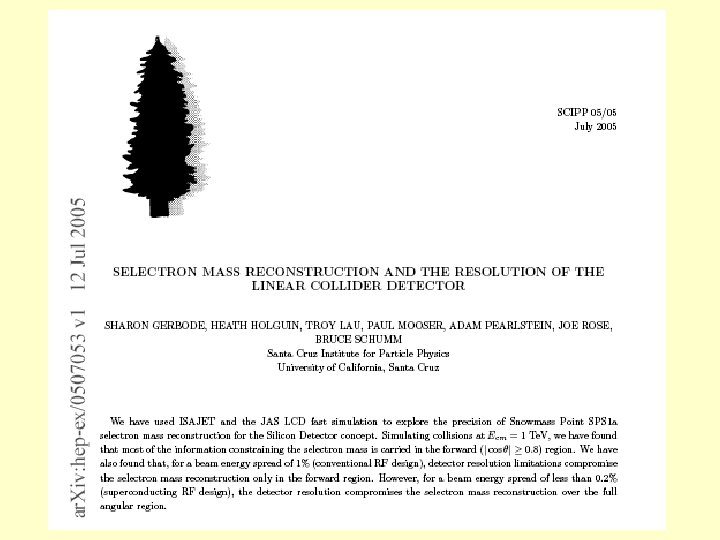

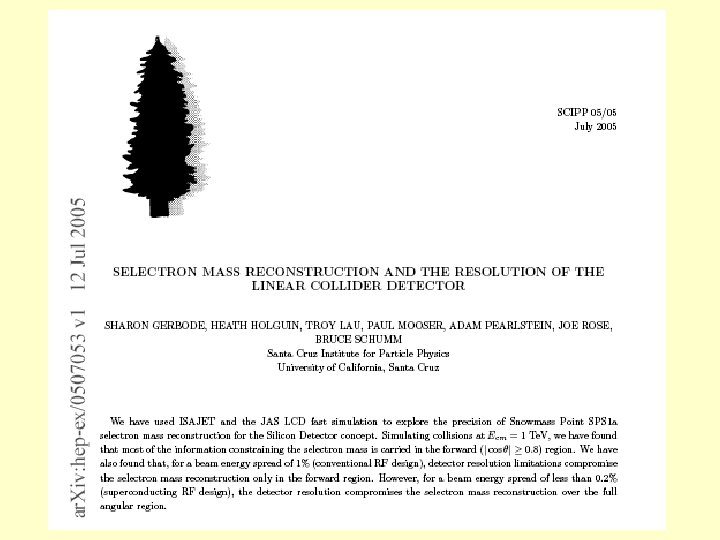

Detector Resolution Standards from Selectron Production Participants: Senior Physicist Bruce Schumm Undergraduate Thesis Students Sharon Gerbode, Heath Holguin, Troy Lau*, Paul Moser, Adam Perlstein, Joseph Rose, Matthew Vegas Community Member (on hold before Grad School) Ayelet Lorberbaum *Recipient of two Undergraduate Research Awards; grad school at U. Michigan.

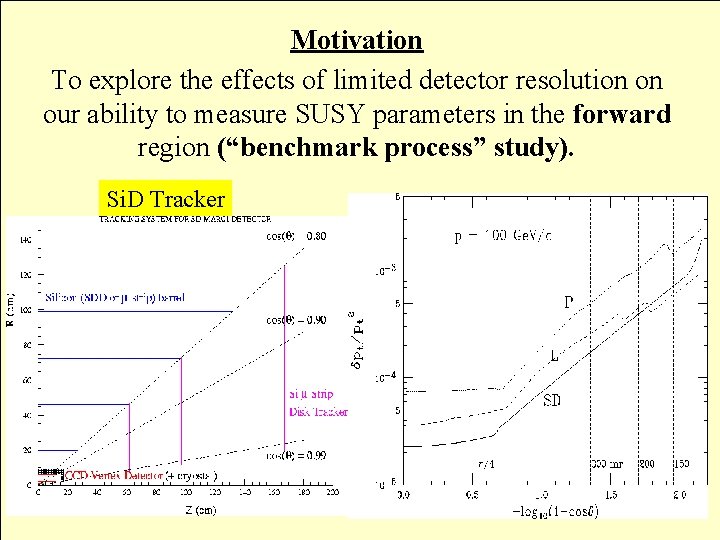

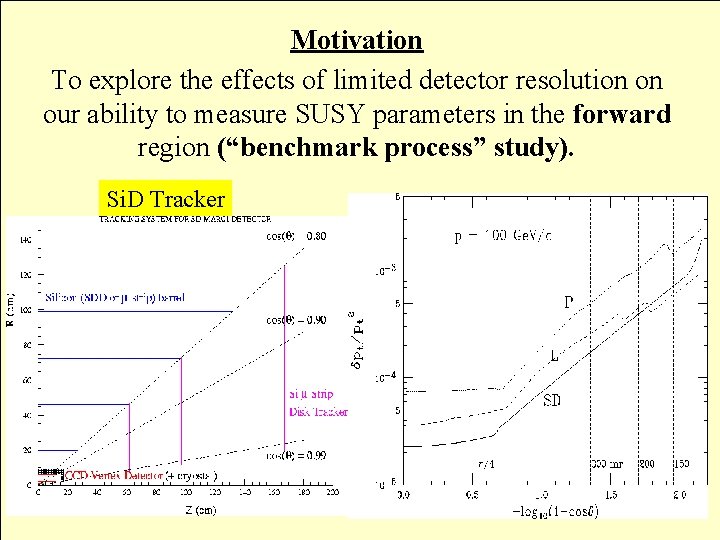

Motivation To explore the effects of limited detector resolution on our ability to measure SUSY parameters in the forward region (“benchmark process” study). Si. D Tracker

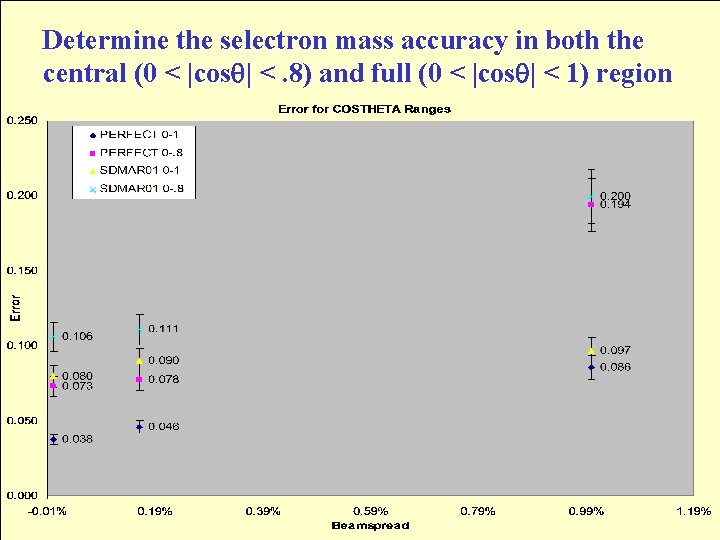

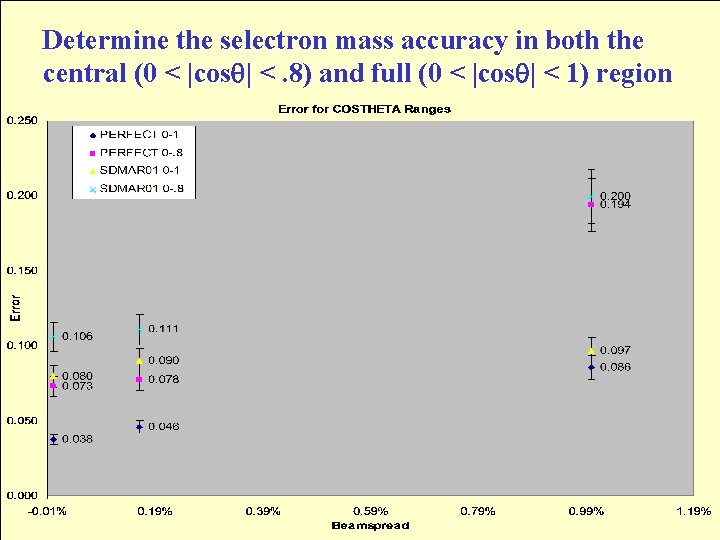

Determine the selectron mass accuracy in both the central (0 < |cos | <. 8) and full (0 < |cos | < 1) region

Simulation of Si. D Tracking System (and Si. D variants) Participants: Senior Physicist Bruce Schumm Recent Graduate Students Christian Flacco, Michael Young* Undergraduate Students John Mikelich, Tyler Rice, Lori Stevens, Eric Wallace *Supported primarily through department (TA) funds; SLAC paid for ½ of his support this summer.

Simulation of Si. D Tracking System, continued Three areas of work: Fast MC Simulation Billior-based LCDTRK. f (B. Schumm) provides covariance matrices for fast MC simulation and resolution plots. Si. D Tracking Capabilities Explore tracking performance of Si. D tracker and variants Microstrip Pulse Development Simulation Provides simulation of pulse development and amplification for designing and detector layout

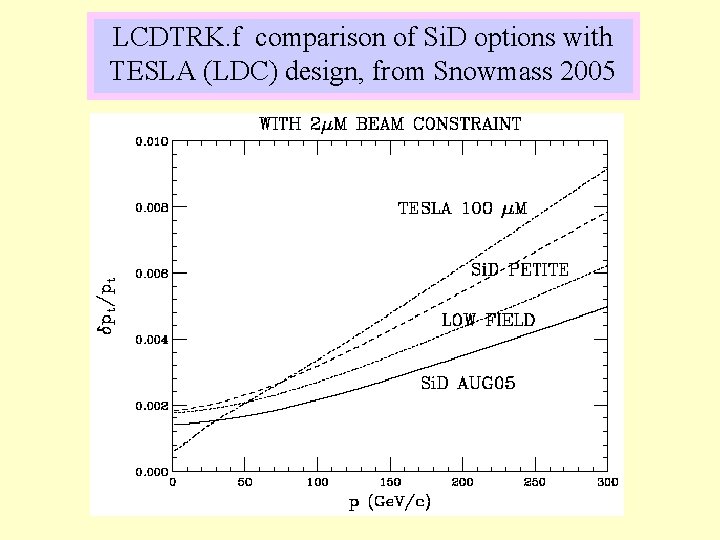

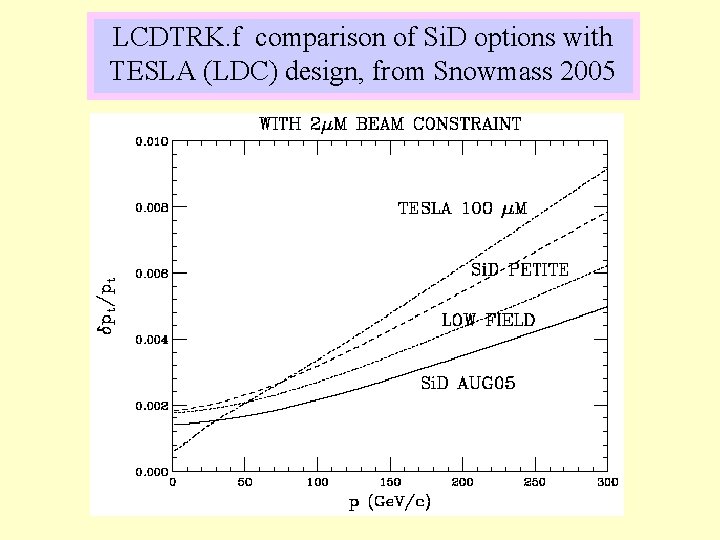

LCDTRK. f comparison of Si. D options with TESLA (LDC) design, from Snowmass 2005

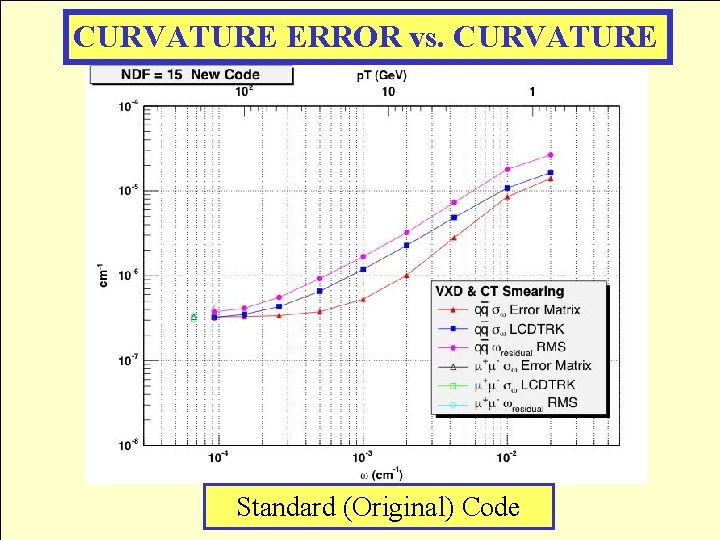

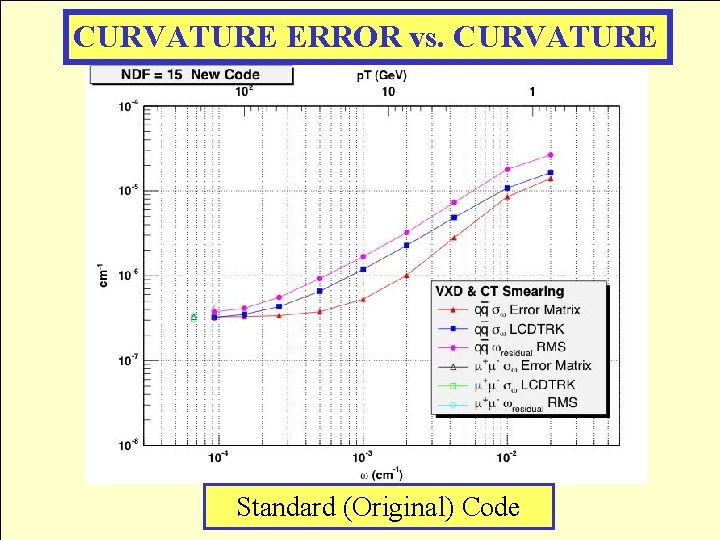

CURVATURE ERROR vs. CURVATURE Standard (Original) Code

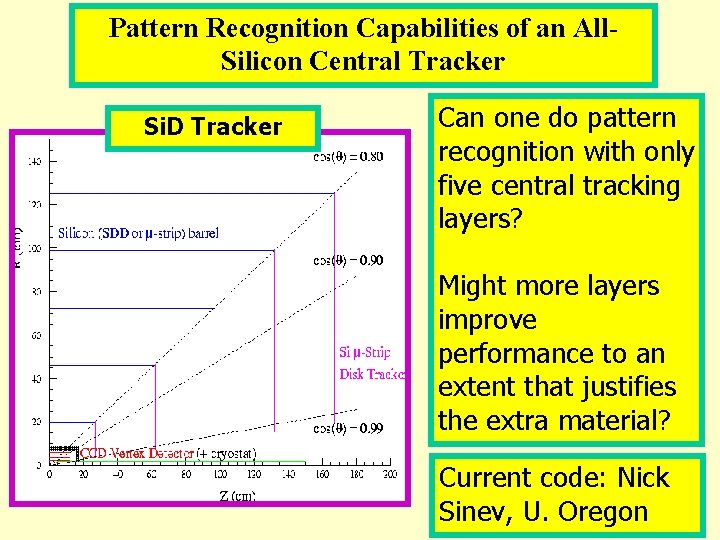

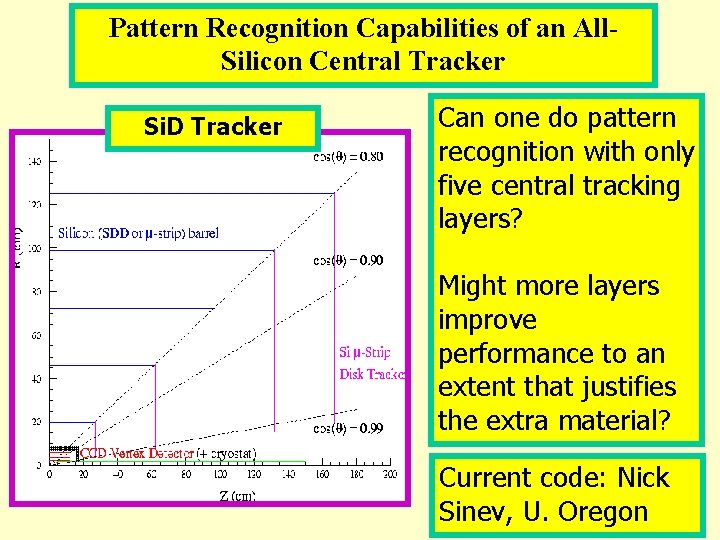

Pattern Recognition Capabilities of an All. Silicon Central Tracker Si. D Tracker Can one do pattern recognition with only five central tracking layers? Might more layers improve performance to an extent that justifies the extra material? Current code: Nick Sinev, U. Oregon

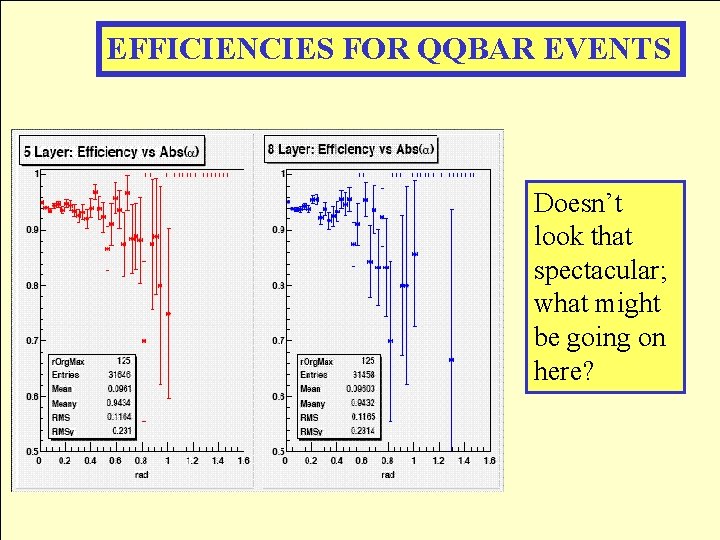

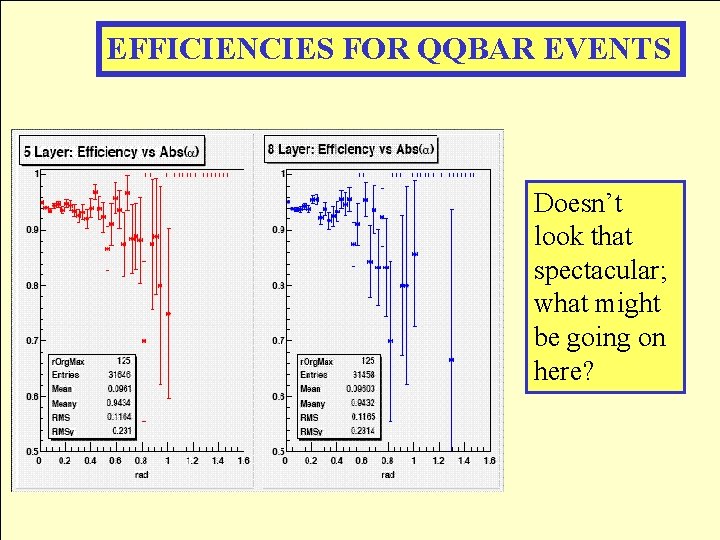

EFFICIENCIES FOR QQBAR EVENTS Doesn’t look that spectacular; what might be going on here?

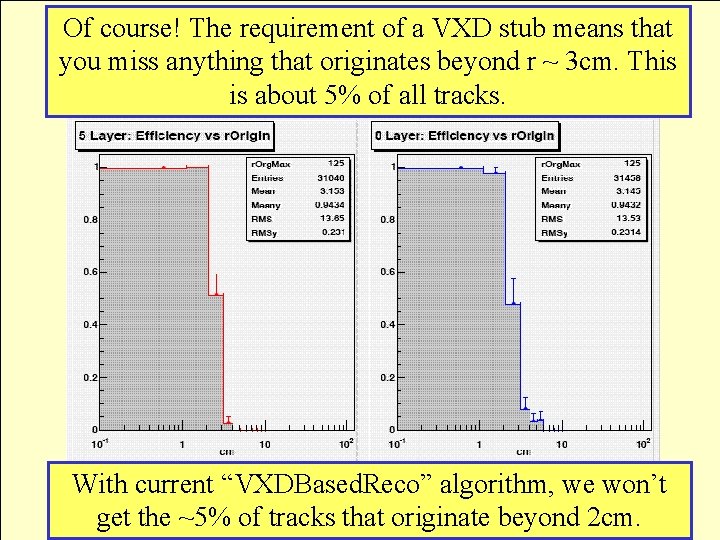

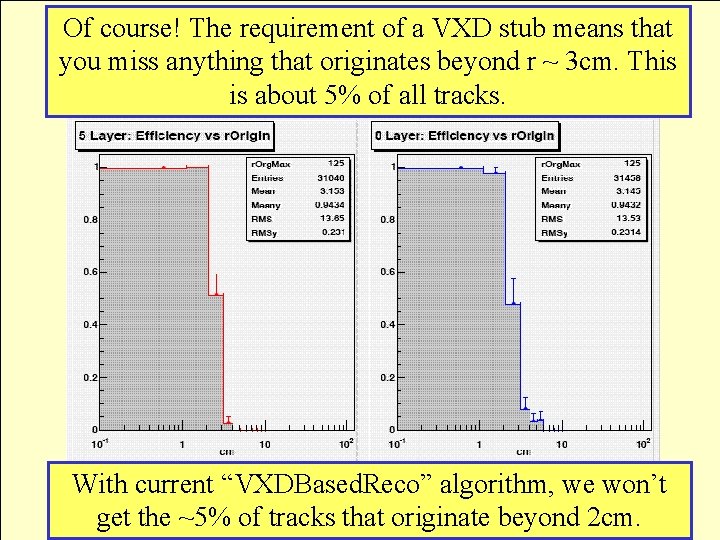

Of course! The requirement of a VXD stub means that you miss anything that originates beyond r ~ 3 cm. This is about 5% of all tracks. With current “VXDBased. Reco” algorithm, we won’t get the ~5% of tracks that originate beyond 2 cm.

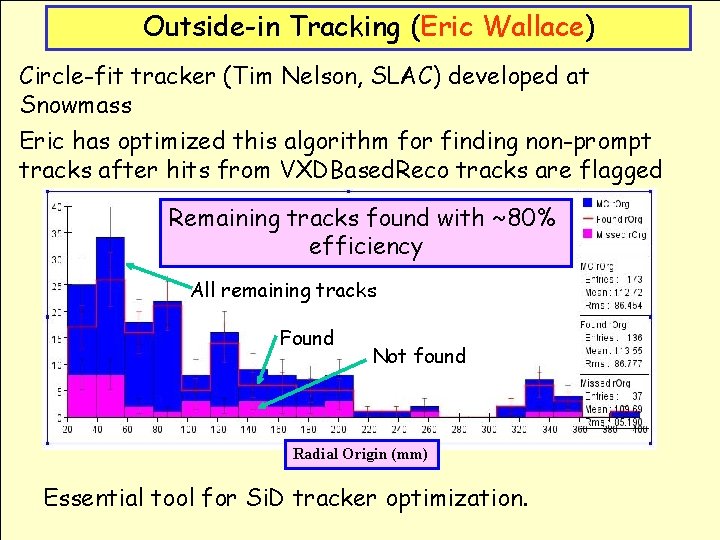

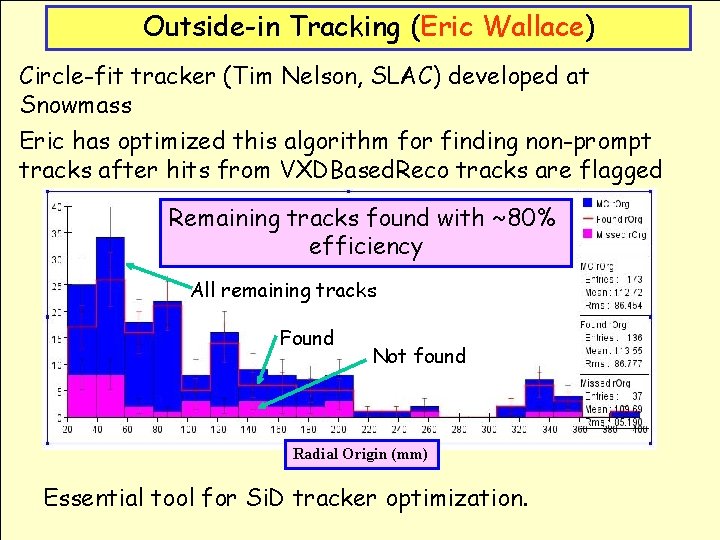

Outside-in Tracking (Eric Wallace) Circle-fit tracker (Tim Nelson, SLAC) developed at Snowmass Eric has optimized this algorithm for finding non-prompt tracks after hits from VXDBased. Reco tracks are flagged Remaining tracks found with ~80% efficiency All remaining tracks Found Not found Radial Origin (mm) Essential tool for Si. D tracker optimization.

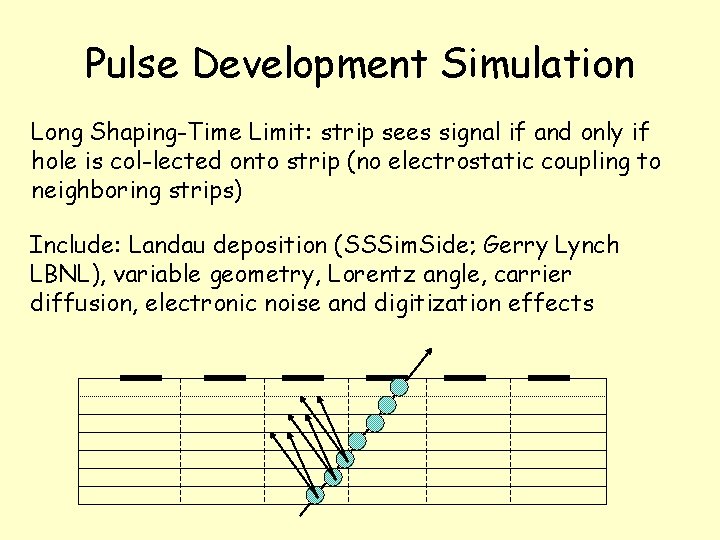

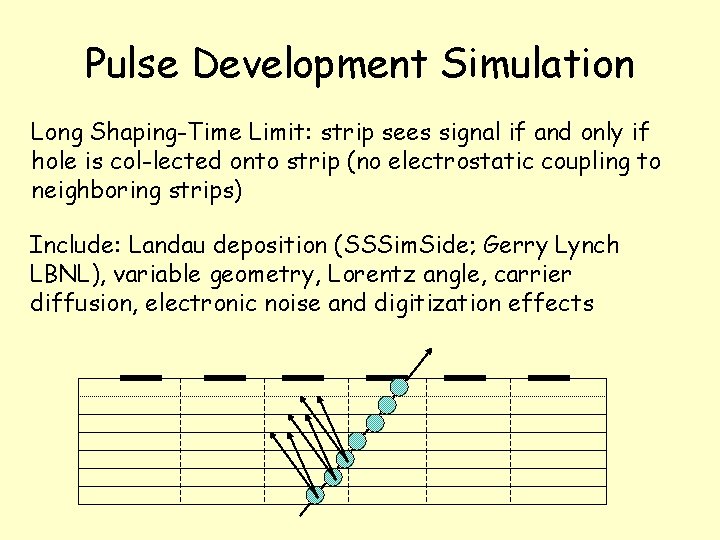

Pulse Development Simulation Long Shaping-Time Limit: strip sees signal if and only if hole is col-lected onto strip (no electrostatic coupling to neighboring strips) Include: Landau deposition (SSSim. Side; Gerry Lynch LBNL), variable geometry, Lorentz angle, carrier diffusion, electronic noise and digitization effects

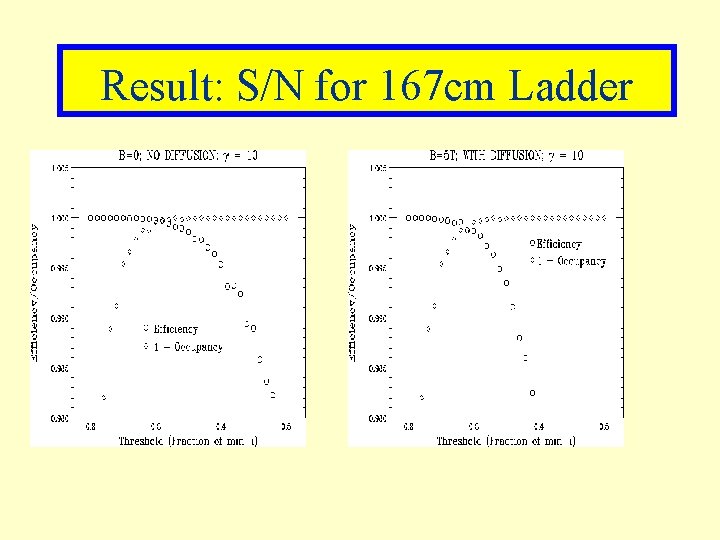

Result: S/N for 167 cm Ladder

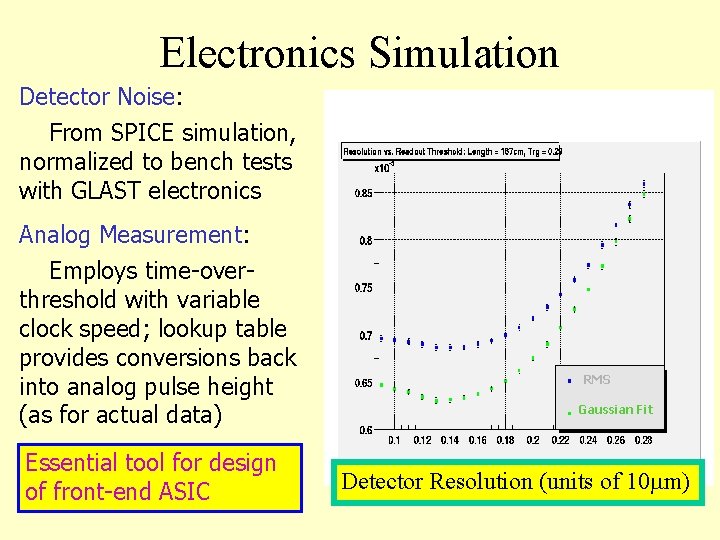

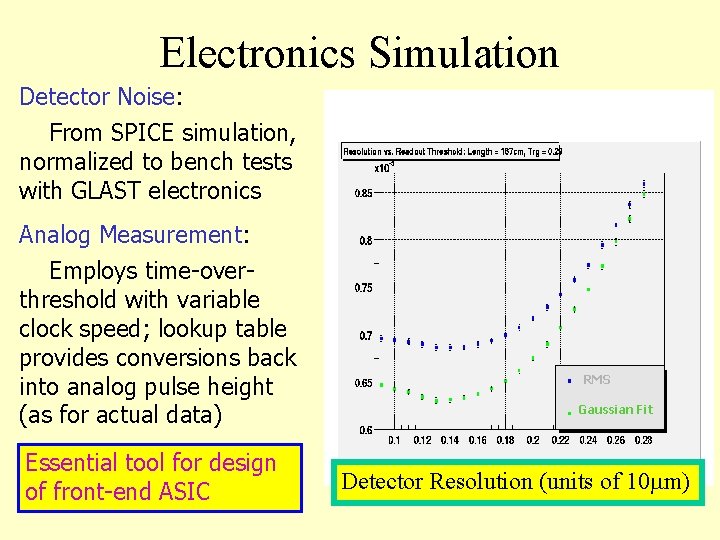

Electronics Simulation Detector Noise: From SPICE simulation, normalized to bench tests with GLAST electronics Analog Measurement: Employs time-overthreshold with variable clock speed; lookup table provides conversions back into analog pulse height (as for actual data) Essential tool for design of front-end ASIC RMS Gaussian Fit Detector Resolution (units of 10 m)

![The SCIPPUCSC ILC HARDWARE GROUP FacultySenior PostDocs Alex Grillo Gavin Nesom Hartmut Sadrozinski Jurgen The SCIPP/UCSC ILC HARDWARE GROUP Faculty/Senior Post-Docs Alex Grillo [Gavin Nesom*] Hartmut Sadrozinski Jurgen](https://slidetodoc.com/presentation_image_h2/b9c1d3a57baab44c5f0badae75876e6b/image-19.jpg)

The SCIPP/UCSC ILC HARDWARE GROUP Faculty/Senior Post-Docs Alex Grillo [Gavin Nesom*] Hartmut Sadrozinski Jurgen Bruce Schumm Kroseberg Abe Seiden Students Greg Horn Glenn Gray Bryan Matsuo (Comp. Sci. ) Lead Engineer: Ned Spencer Technical Staff: Max Wilder, Forest Martinez-Mc. Kinney *Recently lured away by the sirens of Silicon Valley

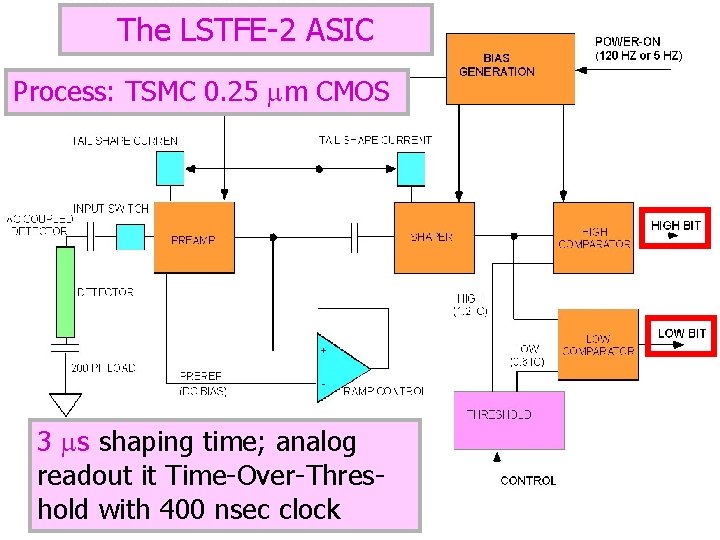

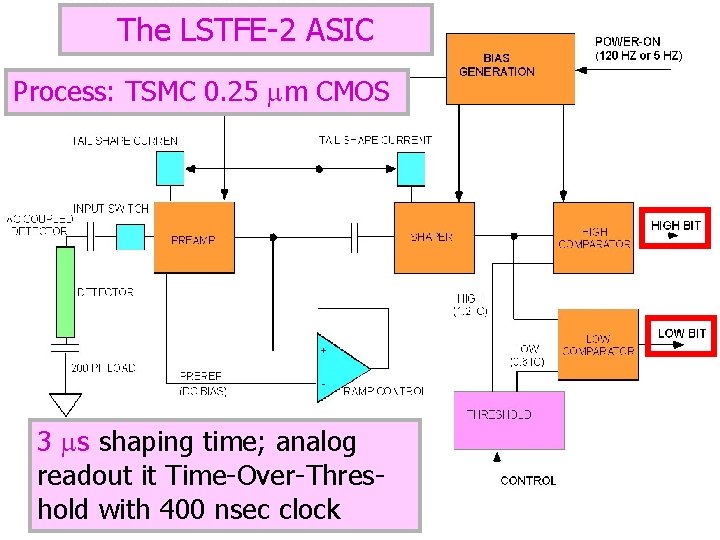

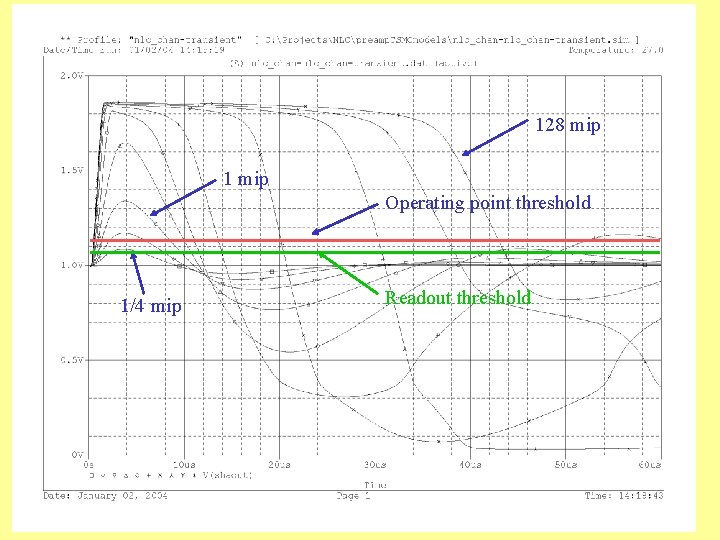

The LSTFE-2 ASIC Process: TSMC 0. 25 m CMOS 3 s shaping time; analog readout it Time-Over-Threshold with 400 nsec clock

128 mip 1 mip Operating point threshold 1/4 mip Readout threshold

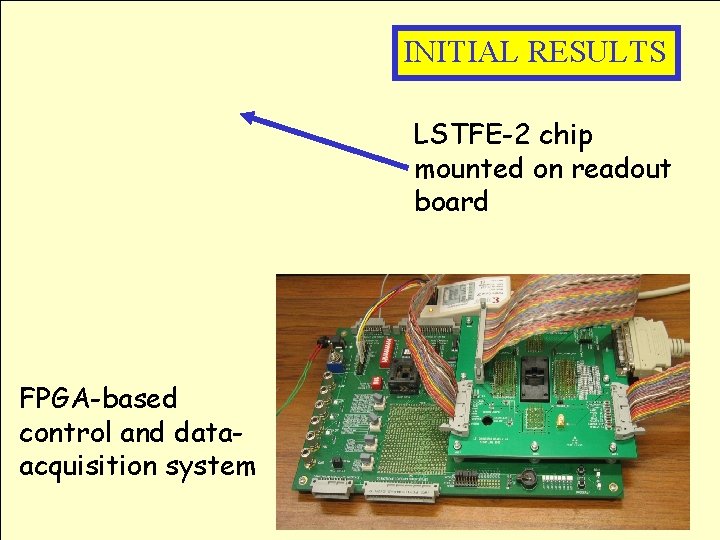

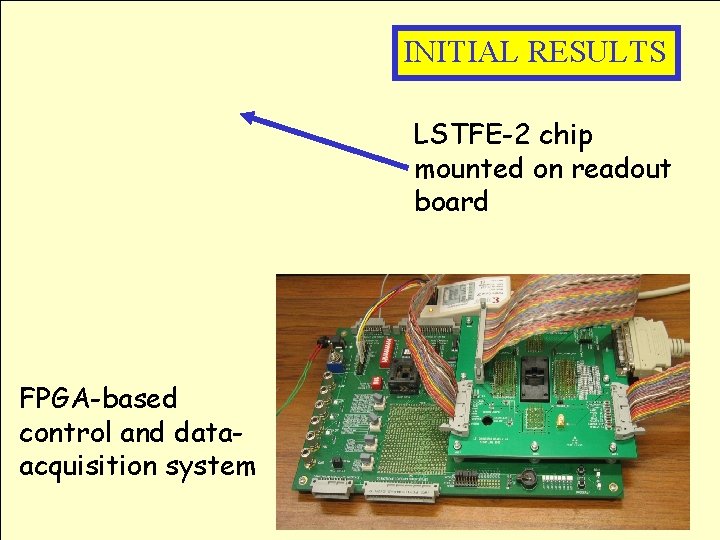

INITIAL RESULTS LSTFE-2 chip mounted on readout board FPGA-based control and dataacquisition system

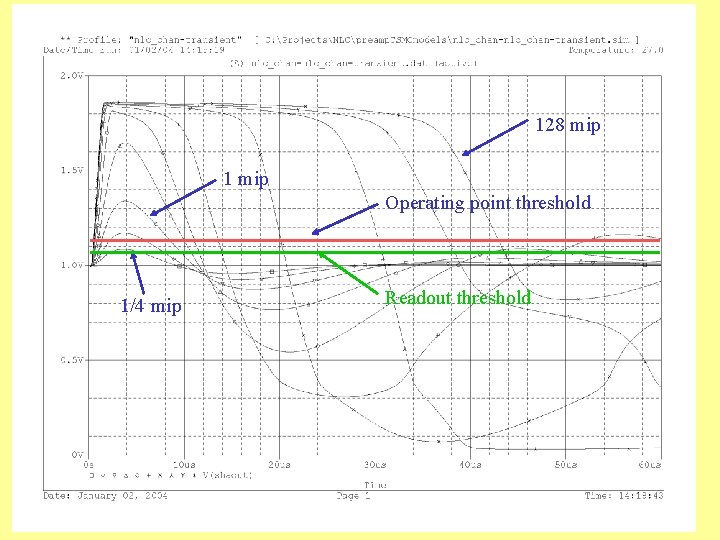

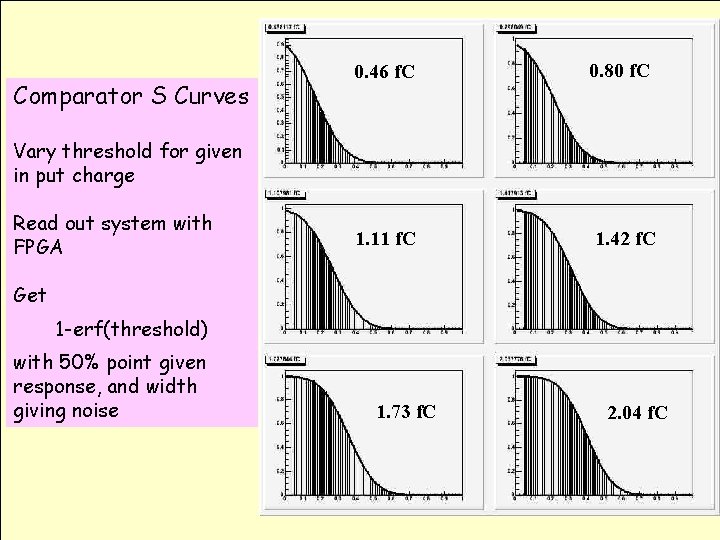

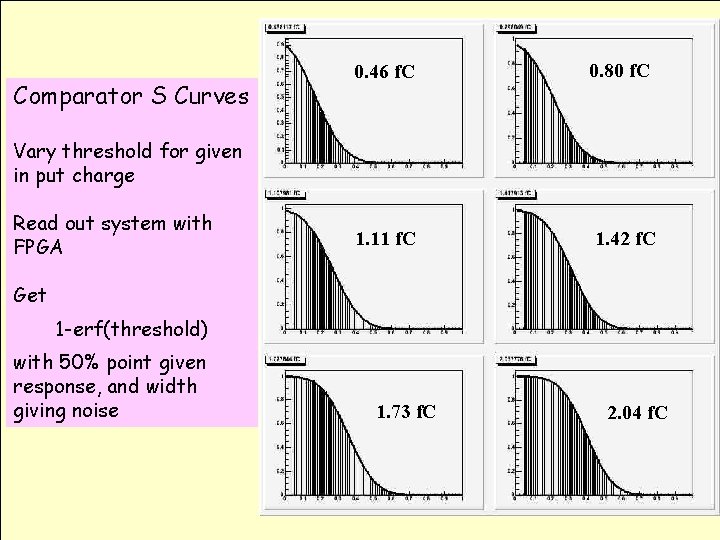

Comparator S Curves 0. 46 f. C 0. 80 f. C 1. 11 f. C 1. 42 f. C Vary threshold for given in put charge Read out system with FPGA Get 1 -erf(threshold) with 50% point given response, and width giving noise 1. 73 f. C 2. 04 f. C

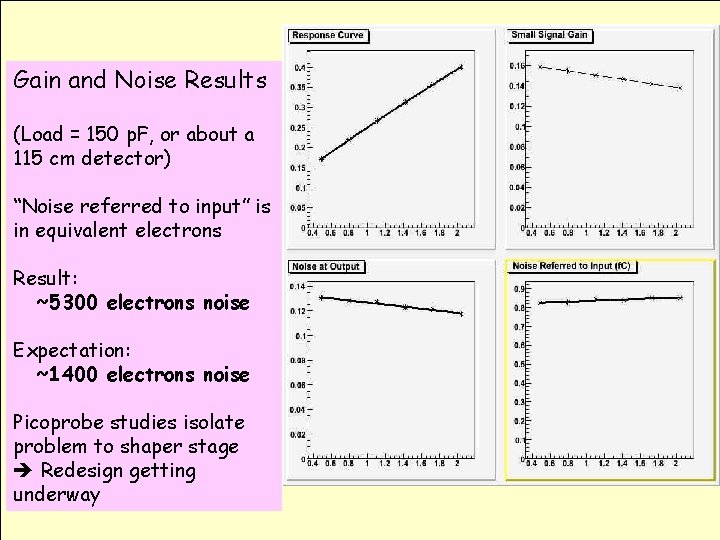

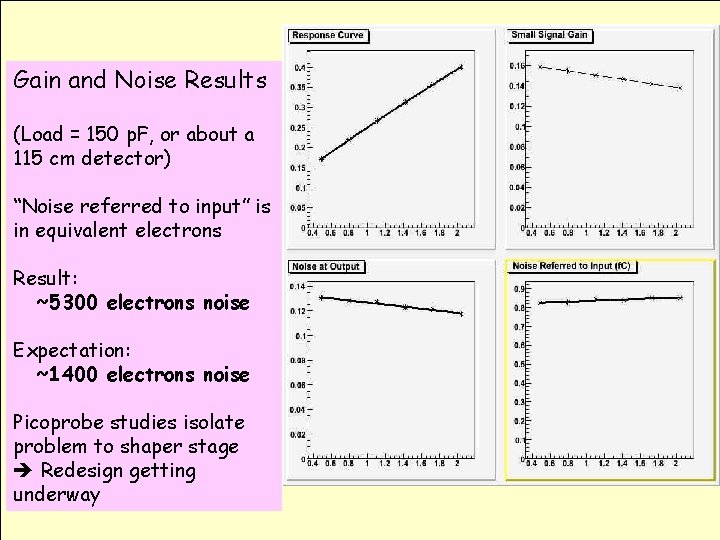

Gain and Noise Results (Load = 150 p. F, or about a 115 cm detector) “Noise referred to input” is in equivalent electrons Result: ~5300 electrons noise Expectation: ~1400 electrons noise Picoprobe studies isolate problem to shaper stage Redesign getting underway

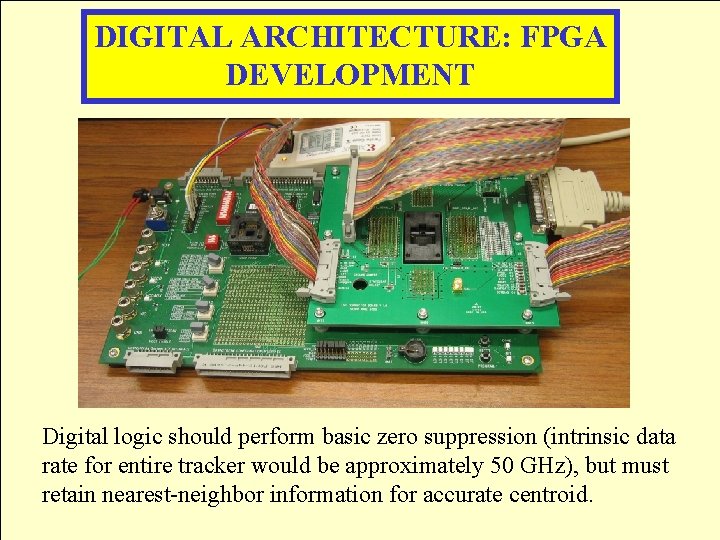

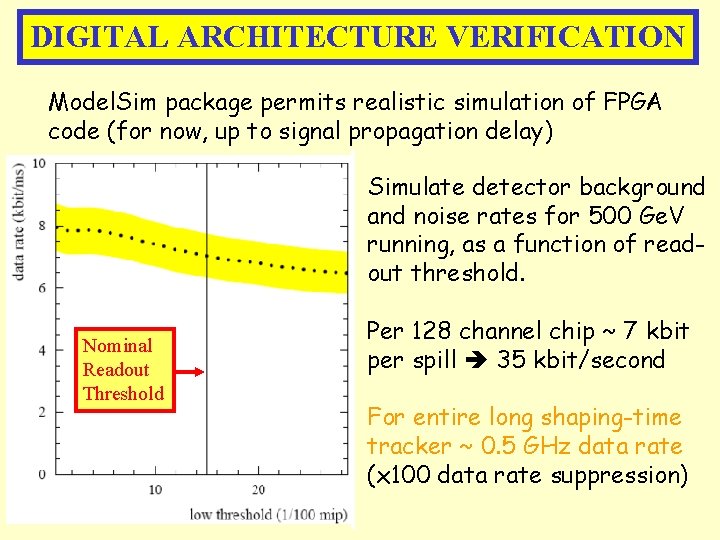

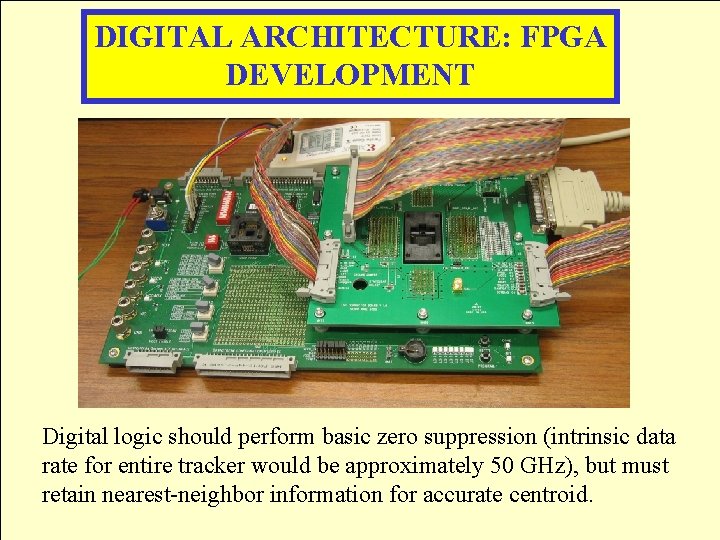

DIGITAL ARCHITECTURE: FPGA DEVELOPMENT Digital logic should perform basic zero suppression (intrinsic data rate for entire tracker would be approximately 50 GHz), but must retain nearest-neighbor information for accurate centroid.

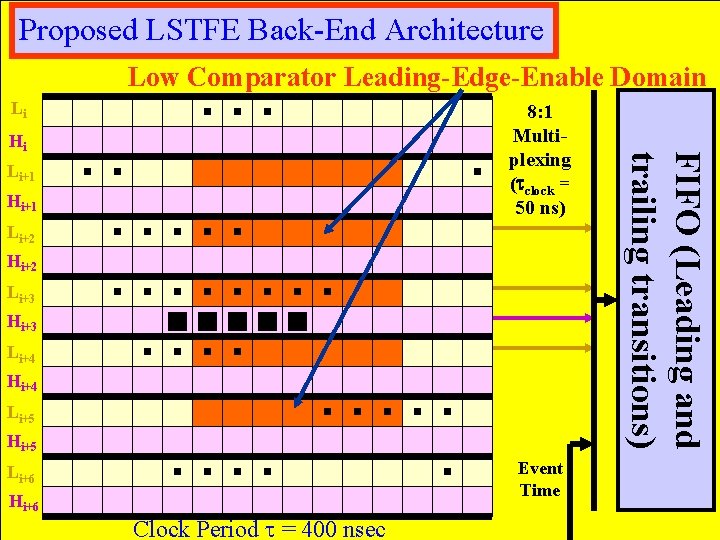

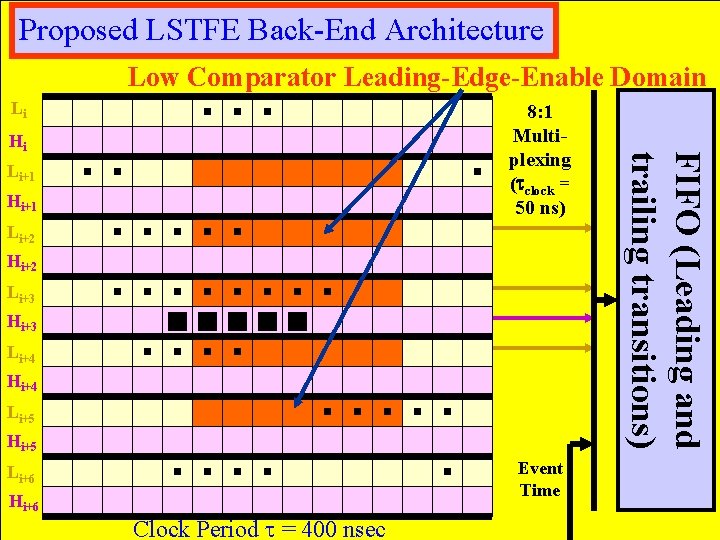

Proposed LSTFE Back-End Architecture Low Comparator Leading-Edge-Enable Domain Li Hi Li+1 Hi+1 Li+2 Hi+2 Li+3 Hi+3 Li+4 Hi+4 Li+5 Hi+5 Event Time Li+6 Hi+6 Clock Period = 400 nsec FIFO (Leading and trailing transitions) 8: 1 Multiplexing ( clock = 50 ns)

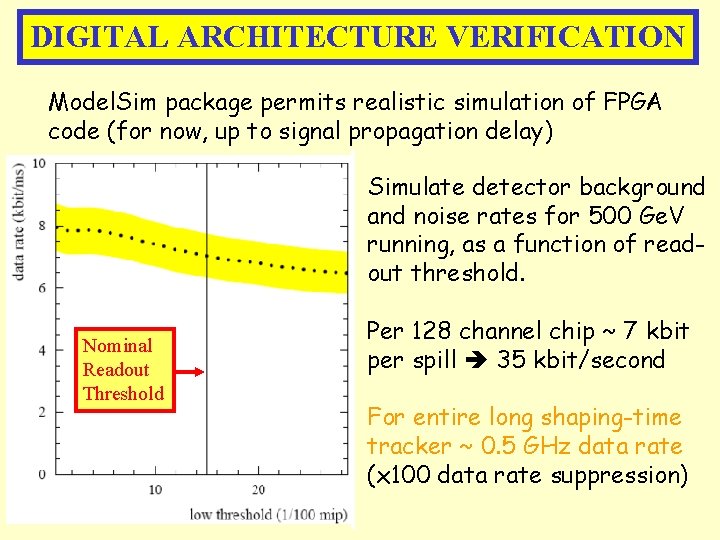

DIGITAL ARCHITECTURE VERIFICATION Model. Sim package permits realistic simulation of FPGA code (for now, up to signal propagation delay) Simulate detector background and noise rates for 500 Ge. V running, as a function of readout threshold. Nominal Readout Threshold Per 128 channel chip ~ 7 kbit per spill 35 kbit/second For entire long shaping-time tracker ~ 0. 5 GHz data rate (x 100 data rate suppression)

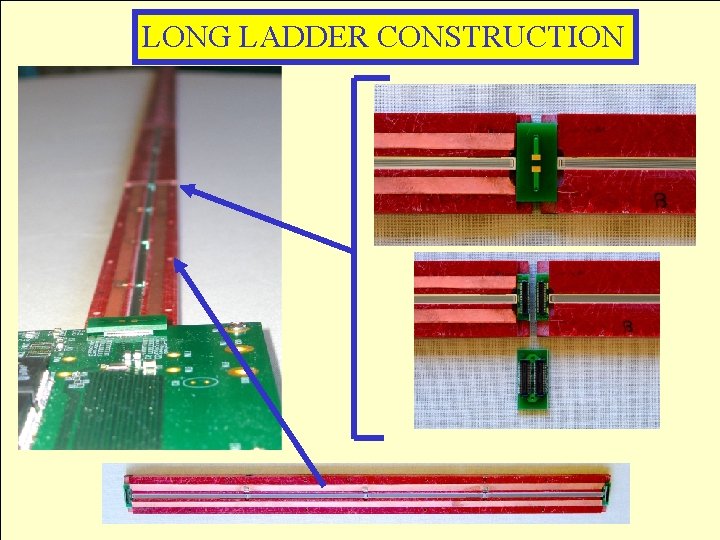

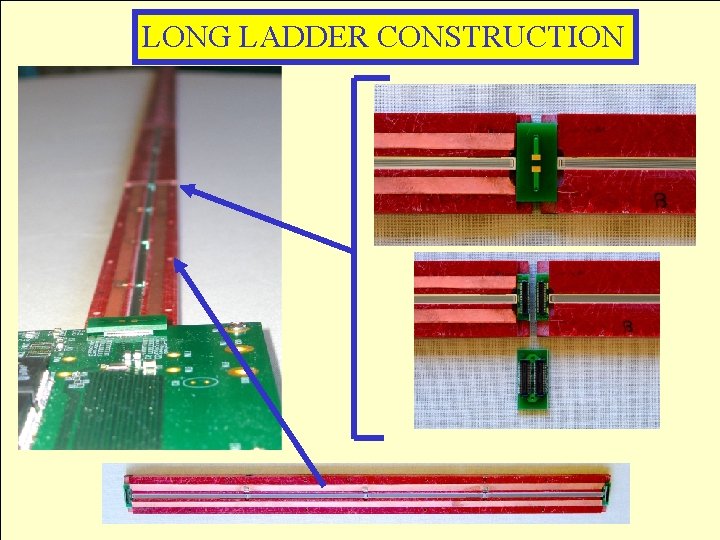

LONG LADDER CONSTRUCTION

OVERALL SUMMARY Linear Collider R&D at SCIPP is: • Directly benefiting from SCIPP expertise • Focused on central issues for the ILC • Supporting leadership roles (international cooperation, oversight of tracking RD) • Creating synergies with other SCIPP programs • Providing key educational opportunities, undergrad through postdoc, with a good placement record