Linear Collider Detector RD at Fermilab BNL FNAL

Linear Collider Detector R&D at Fermilab BNL - FNAL Exploring Possible Future Joint Avenues Slide Marcel Demarteau Fermilab BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau Brookhaven, Long Island Slide November 14, 2005

Goals and Approach • Goals: – Establish a coherent, focused ILC Detector R&D program at Fermilab – Focus on critical detector R&D areas – Tie in, and help define, future activities and strengths across the laboratory • Approach: – Identify areas of strengths at the laboratory – Identify areas of synergy between existing Fermilab projects and ILC – Identify areas unique to the laboratory – Exploit regional common interests – Form collaborative efforts where possible – When possible, keep R&D general, not detector specific • Slide 2 Documentation: – http: //ilc. fnal. gov/detector/rd/detrd. html BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau 2

World Wide Study R&D Panel • The World Wide Study Organizing Committee has established the Detector R&D Panel to promote and coordinate detector R&D for the ILC – https: //wiki. lepp. cornell. edu/wws/bin/view/Projects/Web. Home • Fermilab has nine submissions to this registry: – Vertex and Tracking detectors: • Mechanical design of vertex detector • Active Pixels – MAPS – SOI and 3 D …… …… …… • Hybrid Pixels • Beam pipe design – Calorimetry: • Particle-Flow Algorithms and Related Simulation Software …… • Digital Hadron Calorimeter with RPC’s …… – 5 T Solenoid design …… – Scintillator-Based Muon System R&D …… BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau RD 1 RD 2 RD 3 a RD 3 b RD 4 RD 5 Slide 3 RD 6 RD 7 RD 8 RD 9 3

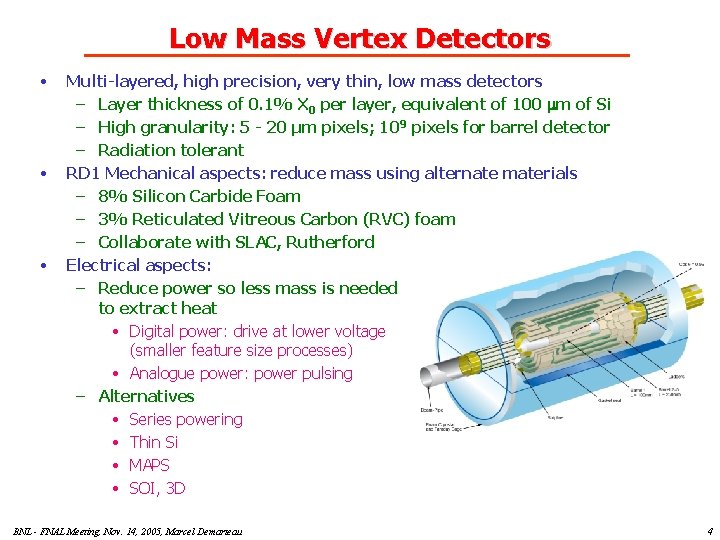

Low Mass Vertex Detectors • • • Multi-layered, high precision, very thin, low mass detectors – Layer thickness of 0. 1% X 0 per layer, equivalent of 100 mm of Si – High granularity: 5 - 20 µm pixels; 109 pixels for barrel detector – Radiation tolerant RD 1 Mechanical aspects: reduce mass using alternate materials – 8% Silicon Carbide Foam – 3% Reticulated Vitreous Carbon (RVC) foam – Collaborate with SLAC, Rutherford Electrical aspects: – Reduce power so less mass is needed to extract heat • Digital power: drive at lower voltage (smaller feature size processes) • Analogue power: power pulsing – Alternatives • Series powering • Thin Si • MAPS • SOI, 3 D BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau Slide 4 4

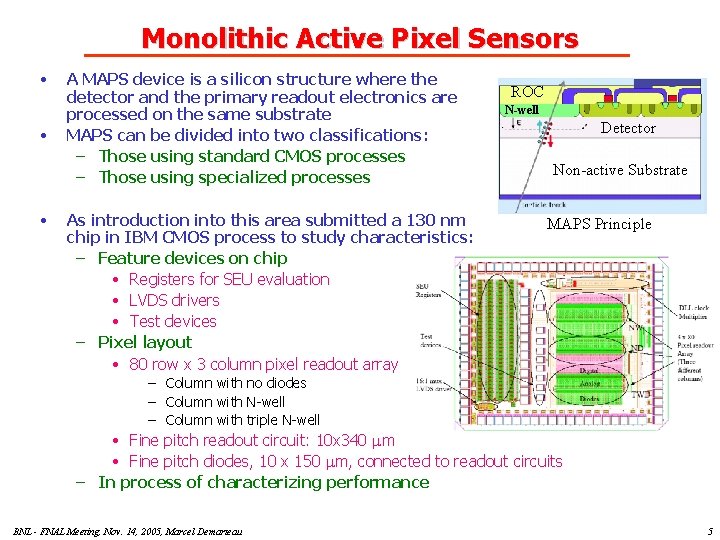

Monolithic Active Pixel Sensors • • • A MAPS device is a silicon structure where the detector and the primary readout electronics are processed on the same substrate MAPS can be divided into two classifications: – Those using standard CMOS processes – Those using specialized processes As introduction into this area submitted a 130 nm chip in IBM CMOS process to study characteristics: – Feature devices on chip • Registers for SEU evaluation • LVDS drivers • Test devices – Pixel layout • 80 row x 3 column pixel readout array ROC N-well Detector Non-active Substrate MAPS Principle Slide 5 – Column with no diodes – Column with N-well – Column with triple N-well • Fine pitch readout circuit: 10 x 340 mm • Fine pitch diodes, 10 x 150 mm, connected to readout circuits – In process of characterizing performance BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau 5

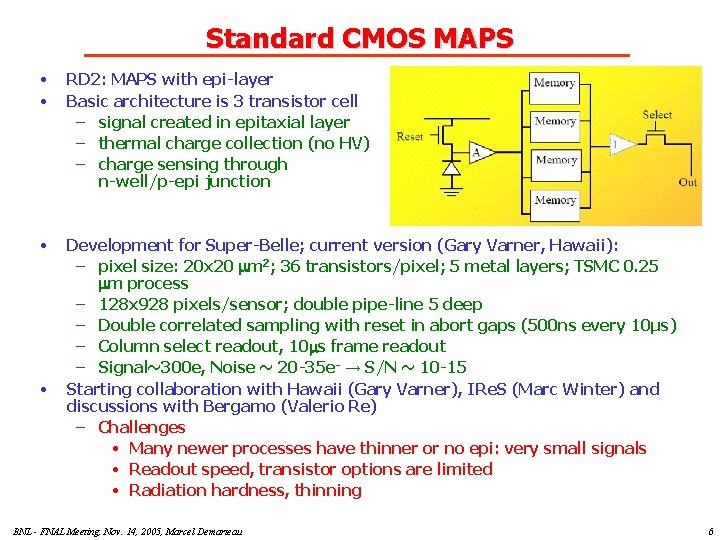

Standard CMOS MAPS • • RD 2: MAPS with epi-layer Basic architecture is 3 transistor cell – signal created in epitaxial layer – thermal charge collection (no HV) – charge sensing through n-well/p-epi junction • Development for Super-Belle; current version (Gary Varner, Hawaii): – pixel size: 20 x 20 mm 2; 36 transistors/pixel; 5 metal layers; TSMC 0. 25 mm process – 128 x 928 pixels/sensor; double pipe-line 5 deep – Double correlated sampling with reset in abort gaps (500 ns every 10µs) – Column select readout, 10 ms frame readout – Signal~300 e, Noise ~ 20 -35 e- → S/N ~ 10 -15 Starting collaboration with Hawaii (Gary Varner), IRe. S (Marc Winter) and discussions with Bergamo (Valerio Re) – Challenges • Many newer processes have thinner or no epi: very small signals • Readout speed, transistor options are limited • Radiation hardness, thinning • BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau Slide 6 6

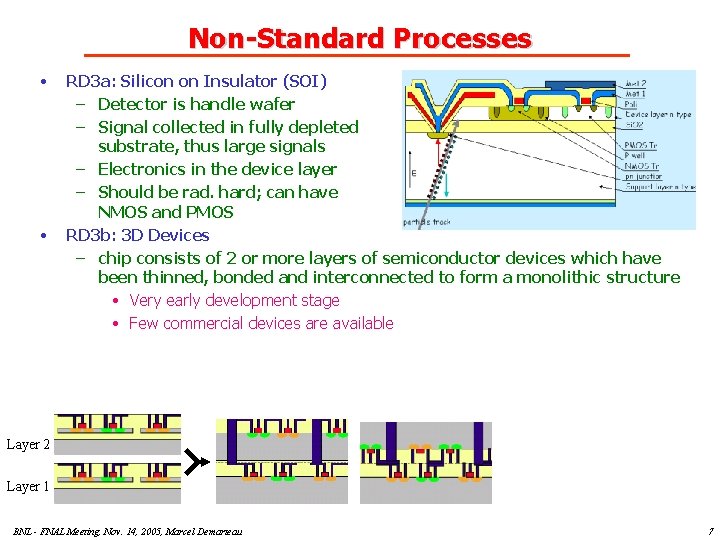

Non-Standard Processes • • RD 3 a: Silicon on Insulator (SOI) – Detector is handle wafer – Signal collected in fully depleted substrate, thus large signals – Electronics in the device layer – Should be rad. hard; can have NMOS and PMOS RD 3 b: 3 D Devices – chip consists of 2 or more layers of semiconductor devices which have been thinned, bonded and interconnected to form a monolithic structure • Very early development stage • Few commercial devices are available Slide 7 Layer 2 Layer 1 BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau 7

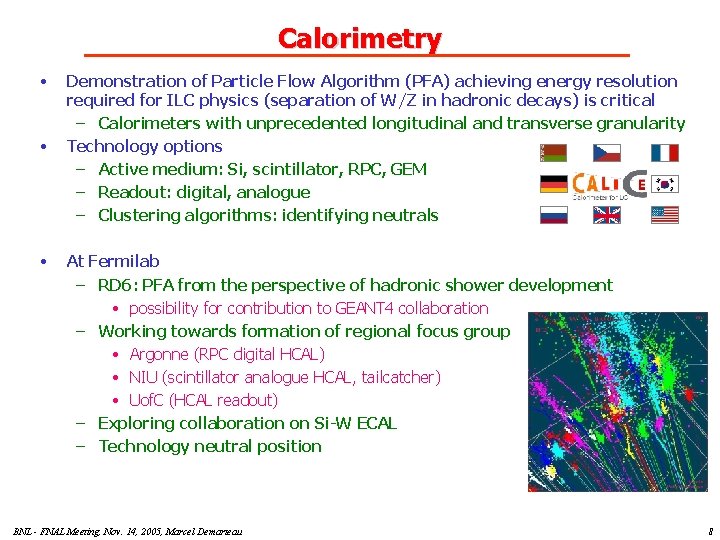

Calorimetry • • • Demonstration of Particle Flow Algorithm (PFA) achieving energy resolution required for ILC physics (separation of W/Z in hadronic decays) is critical – Calorimeters with unprecedented longitudinal and transverse granularity Technology options – Active medium: Si, scintillator, RPC, GEM – Readout: digital, analogue – Clustering algorithms: identifying neutrals At Fermilab – RD 6: PFA from the perspective of hadronic shower development • possibility for contribution to GEANT 4 collaboration – Working towards formation of regional focus group • Argonne (RPC digital HCAL) • NIU (scintillator analogue HCAL, tailcatcher) • Uof. C (HCAL readout) – Exploring collaboration on Si-W ECAL – Technology neutral position BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau Slide 8 8

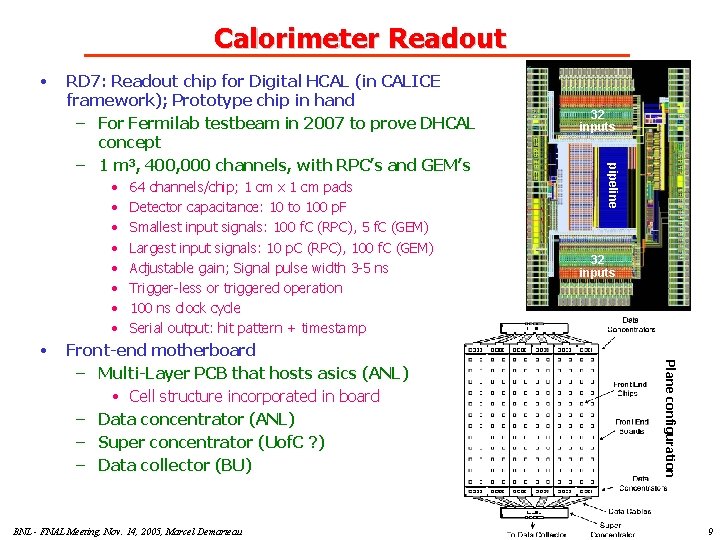

Calorimeter Readout • • • 64 channels/chip; 1 cm x 1 cm pads Detector capacitance: 10 to 100 p. F Smallest input signals: 100 f. C (RPC), 5 f. C (GEM) Largest input signals: 10 p. C (RPC), 100 f. C (GEM) Adjustable gain; Signal pulse width 3 -5 ns Trigger-less or triggered operation 100 ns clock cycle Serial output: hit pattern + timestamp BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau 32 inputs Slide 9 Plane configuration Front-end motherboard – Multi-Layer PCB that hosts asics (ANL) • Cell structure incorporated in board – Data concentrator (ANL) – Super concentrator (Uof. C ? ) – Data collector (BU) 32 inputs pipeline RD 7: Readout chip for Digital HCAL (in CALICE framework); Prototype chip in hand – For Fermilab testbeam in 2007 to prove DHCAL concept – 1 m 3, 400, 000 channels, with RPC’s and GEM’s 9

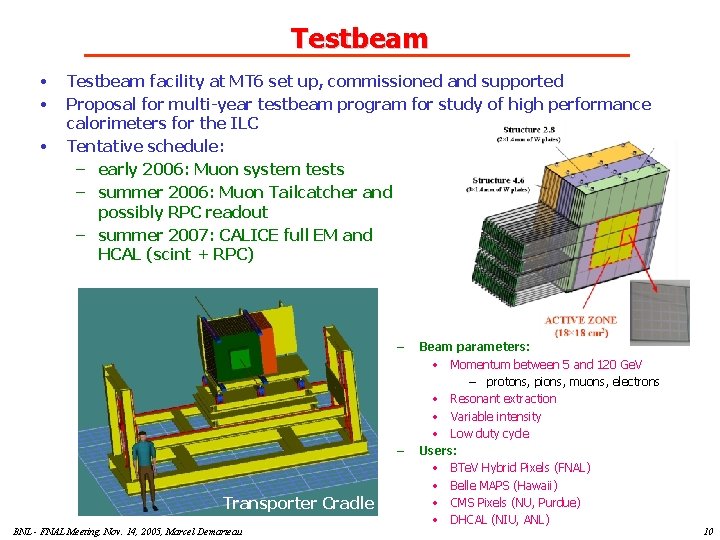

Testbeam • • • Testbeam facility at MT 6 set up, commissioned and supported Proposal for multi-year testbeam program for study of high performance calorimeters for the ILC Tentative schedule: – early 2006: Muon system tests – summer 2006: Muon Tailcatcher and possibly RPC readout – summer 2007: CALICE full EM and HCAL (scint + RPC) – – Transporter Cradle BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau Beam parameters: • Momentum between 5 and 120 Ge. V – protons, pions, muons, electrons • Resonant extraction • Variable intensity • Low duty cycle Users: • BTe. V Hybrid Pixels (FNAL) • Belle MAPS (Hawaii) • CMS Pixels (NU, Purdue) • DHCAL (NIU, ANL) Slide 10 10

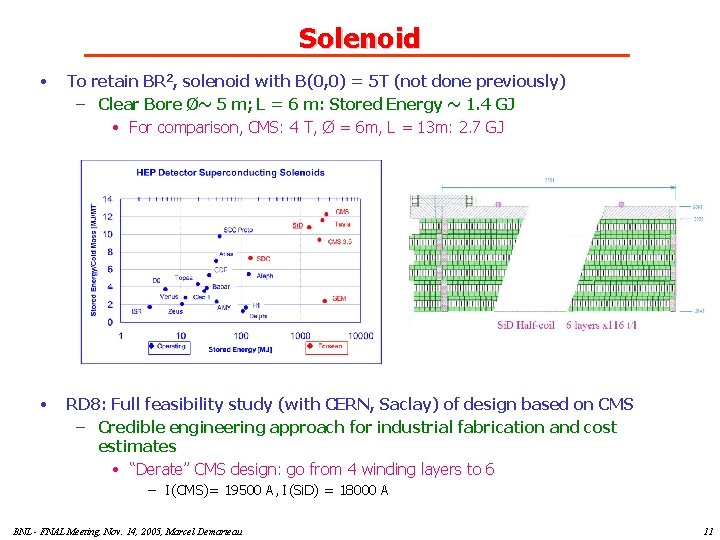

Solenoid • To retain BR 2, solenoid with B(0, 0) = 5 T (not done previously) – Clear Bore Ø~ 5 m; L = 6 m: Stored Energy ~ 1. 4 GJ • For comparison, CMS: 4 T, Ø = 6 m, L = 13 m: 2. 7 GJ Slide 11 • RD 8: Full feasibility study (with CERN, Saclay) of design based on CMS – Credible engineering approach for industrial fabrication and cost estimates • “Derate” CMS design: go from 4 winding layers to 6 – I(CMS)= 19500 A, I(Si. D) = 18000 A BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau 11

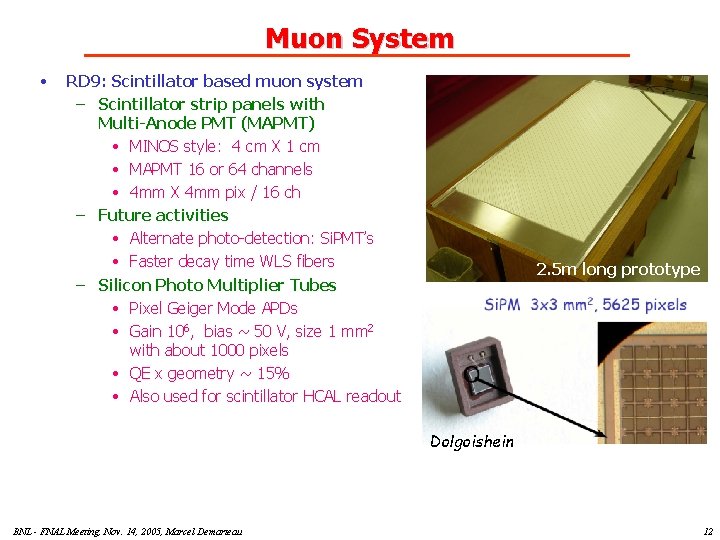

Muon System • RD 9: Scintillator based muon system – Scintillator strip panels with Multi-Anode PMT (MAPMT) • MINOS style: 4 cm X 1 cm • MAPMT 16 or 64 channels • 4 mm X 4 mm pix / 16 ch – Future activities • Alternate photo-detection: Si. PMT’s • Faster decay time WLS fibers – Silicon Photo Multiplier Tubes • Pixel Geiger Mode APDs • Gain 106, bias ~ 50 V, size 1 mm 2 with about 1000 pixels • QE x geometry ~ 15% • Also used for scintillator HCAL readout 2. 5 m long prototype Slide 12 Dolgoishein BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau 12

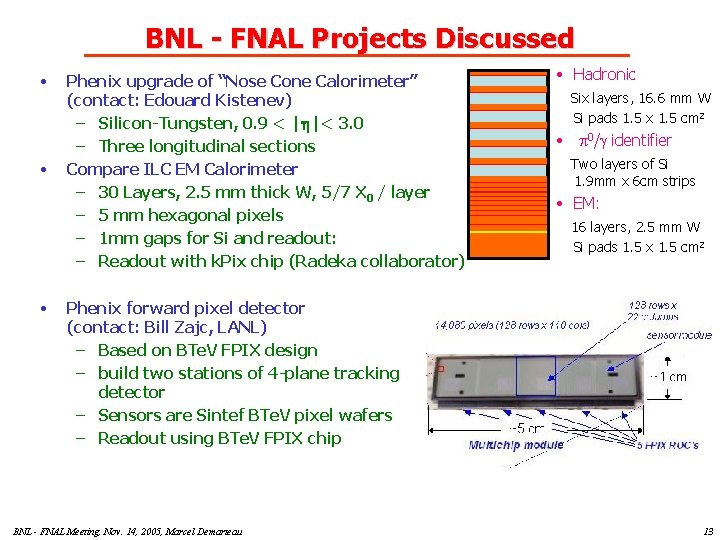

BNL - FNAL Projects Discussed • • • Phenix upgrade of “Nose Cone Calorimeter” (contact: Edouard Kistenev) – Silicon-Tungsten, 0. 9 < |h|< 3. 0 – Three longitudinal sections Compare ILC EM Calorimeter – 30 Layers, 2. 5 mm thick W, 5/7 X 0 / layer – 5 mm hexagonal pixels – 1 mm gaps for Si and readout: – Readout with k. Pix chip (Radeka collaborator) Phenix forward pixel detector (contact: Bill Zajc, LANL) – Based on BTe. V FPIX design – build two stations of 4 -plane tracking detector – Sensors are Sintef BTe. V pixel wafers – Readout using BTe. V FPIX chip BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau • Hadronic Six layers, 16. 6 mm W Si pads 1. 5 x 1. 5 cm 2 • p 0/g identifier Two layers of Si 1. 9 mm x 6 cm strips • EM: 16 layers, 2. 5 mm W Si pads 1. 5 x 1. 5 cm 2 Slide 13 13

Summary • • • ILC R&D at Fermilab becoming more mature; all activities accompanied by software simulations Focal points: – Vertex and tracking design, both mechanical and electrical – Calorimetry • PFA algorithms • Mechanics and readout of particle flow calorimeter • Complex issues; possibilities still being explored – Test beam – ILC Physics program • See possibility for collaboration of Brookhaven theorists with Fermilab theorists as well as experimentalists to optimize the detector performance to achieve Slide 14 the physics goals as well as strengthen the physics case for the ILC Obvious possibilities for collaboration between Fermilab and Brookhaven exists which would provide mutual benefits. BNL - FNAL Meeting, Nov. 14, 2005, Marcel Demarteau 14

- Slides: 14