MultiProject Reticle Design Wafer Dicing under Uncertain Demand

![Project Cloning n Motivation q q n Post-processing approach [Wu. L 05] n n Project Cloning n Motivation q q n Post-processing approach [Wu. L 05] n n](https://slidetodoc.com/presentation_image_h/83ac786ea95e170fe8c1210ce11b6a4e/image-22.jpg)

- Slides: 30

Multi-Project Reticle Design & Wafer Dicing under Uncertain Demand Andrew B Kahng, UC San Diego Ion Mandoiu, University of Connecticut Xu Xu, UC San Diego Alex Zelikovsky, Georgia State University

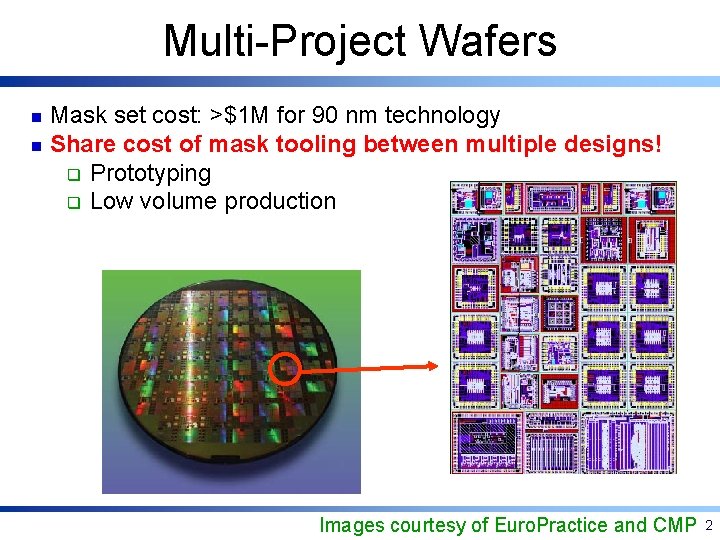

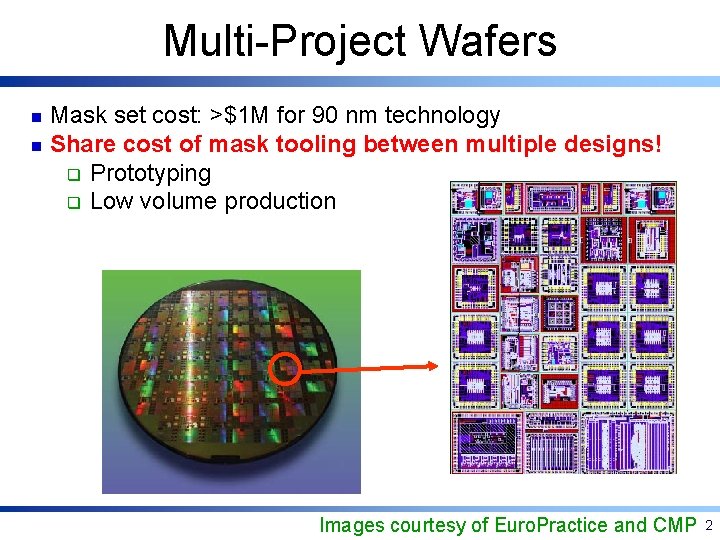

Multi-Project Wafers Mask set cost: >$1 M for 90 nm technology n Share cost of mask tooling between multiple designs! q Prototyping q Low volume production n Images courtesy of Euro. Practice and CMP 2

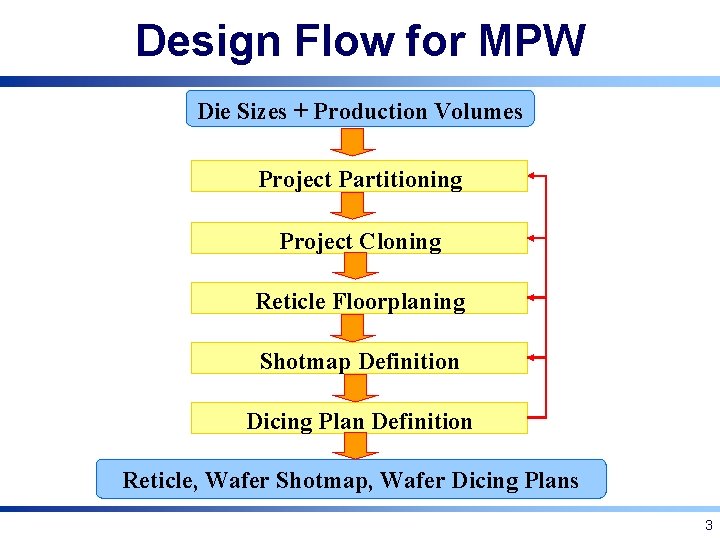

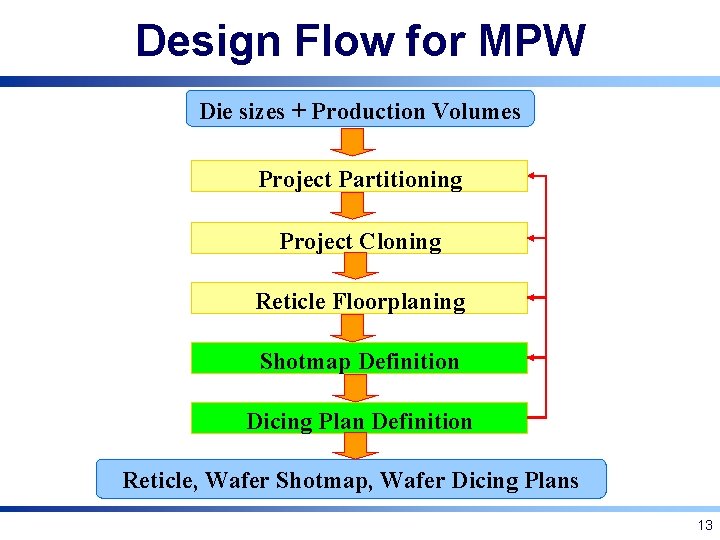

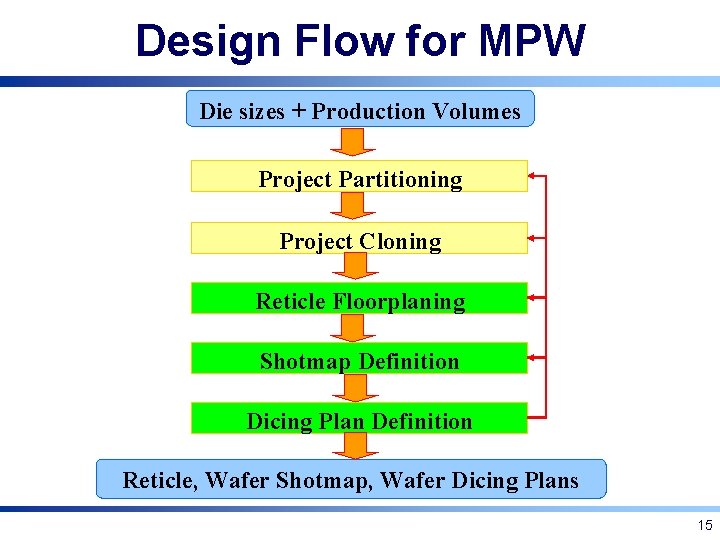

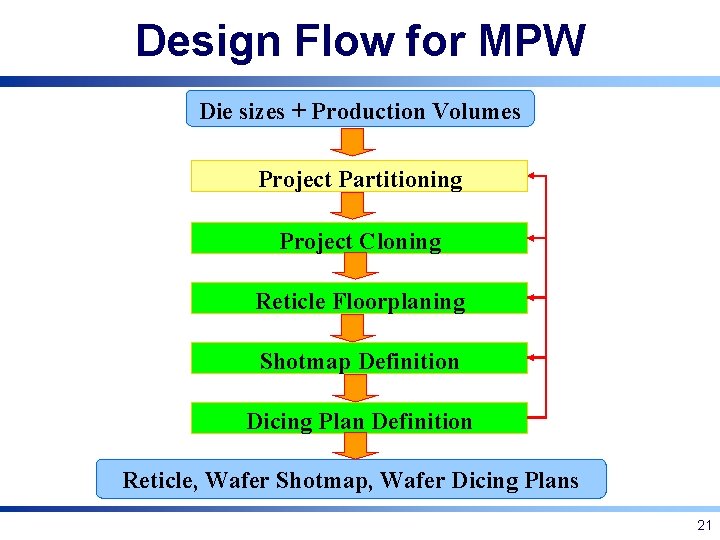

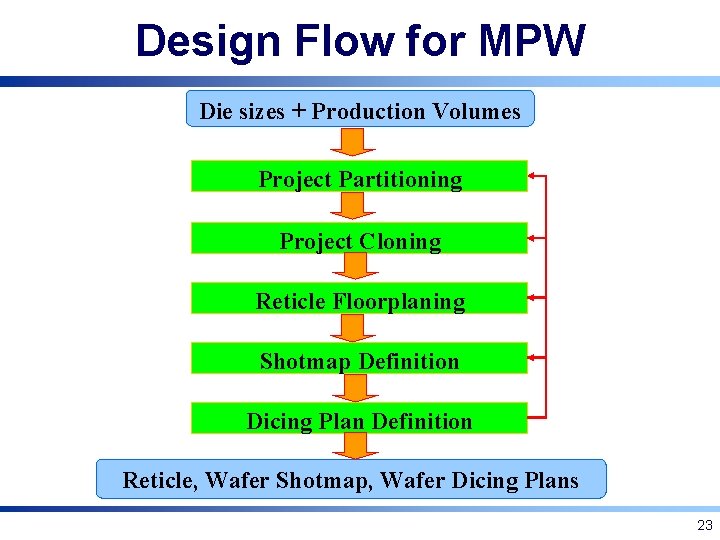

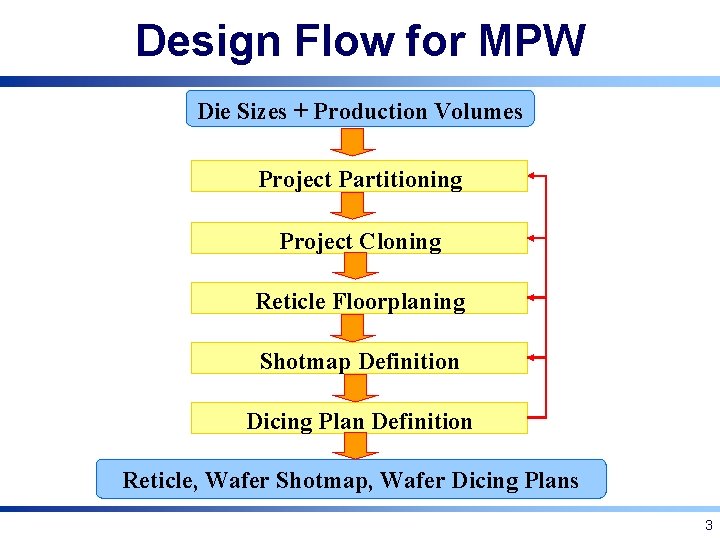

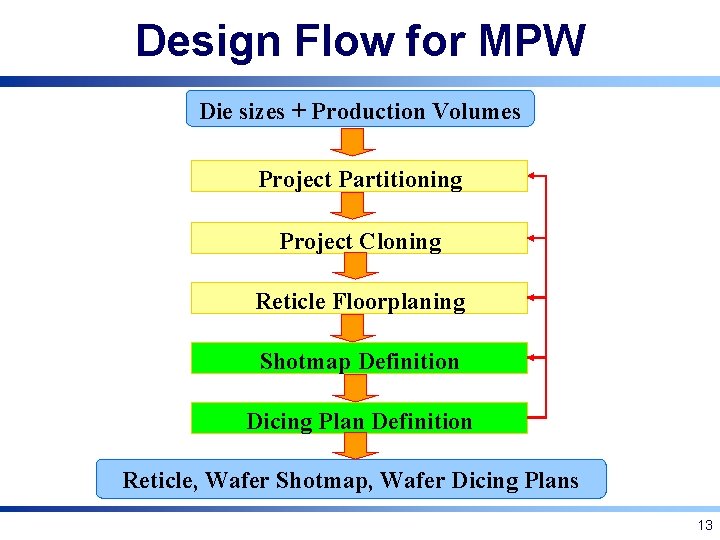

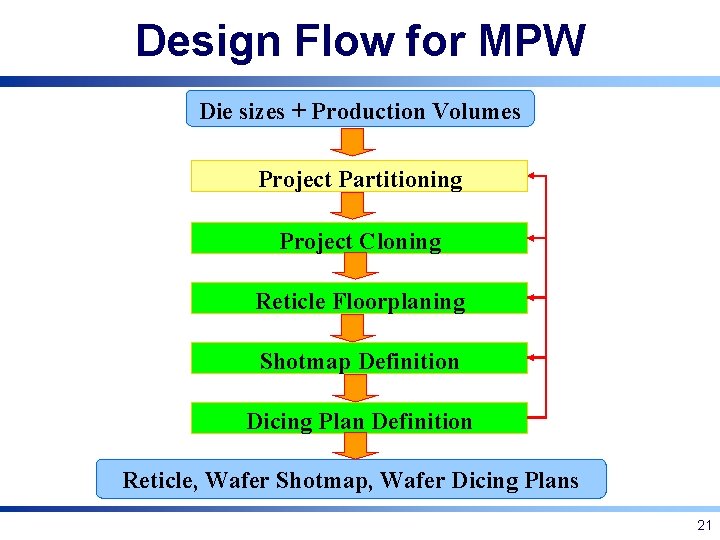

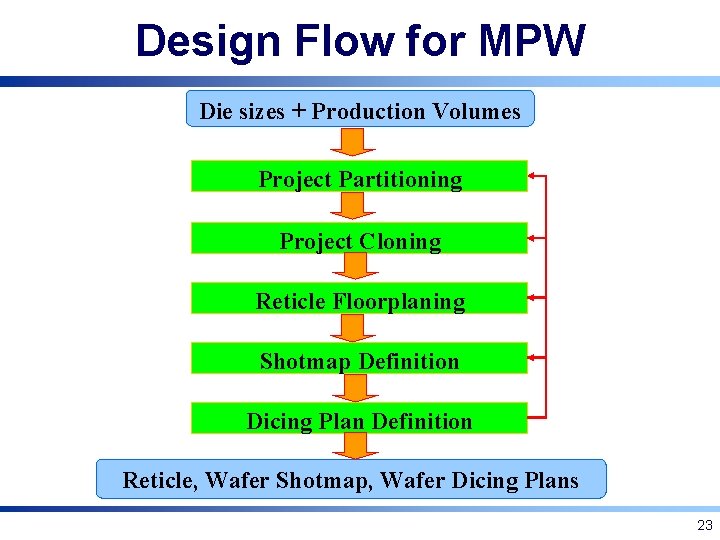

Design Flow for MPW Die Sizes + Production Volumes Project Partitioning Project Cloning Reticle Floorplaning Shotmap Definition Dicing Plan Definition Reticle, Wafer Shotmap, Wafer Dicing Plans 3

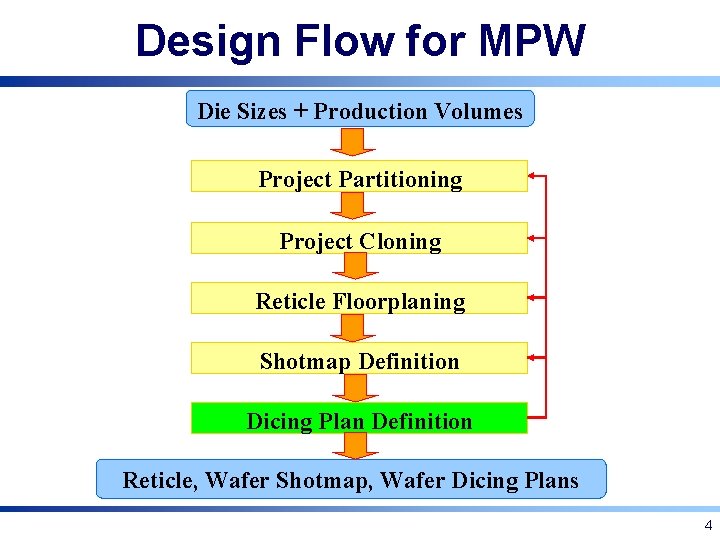

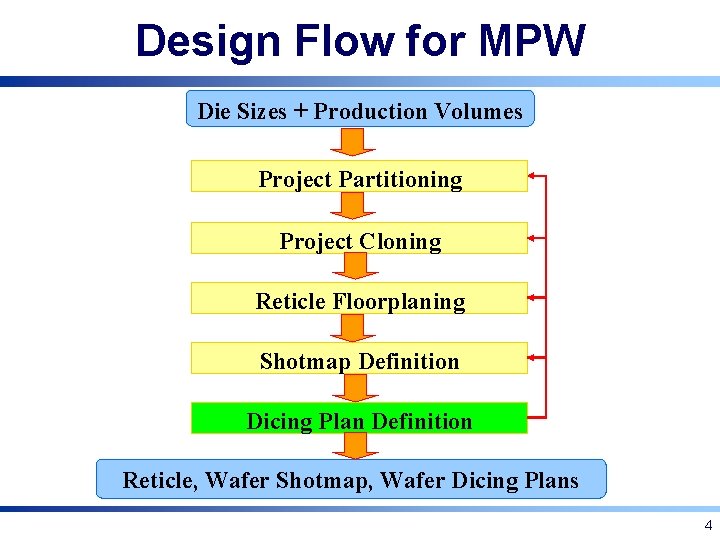

Design Flow for MPW Die Sizes + Production Volumes Project Partitioning Project Cloning Reticle Floorplaning Shotmap Definition Dicing Plan Definition Reticle, Wafer Shotmap, Wafer Dicing Plans 4

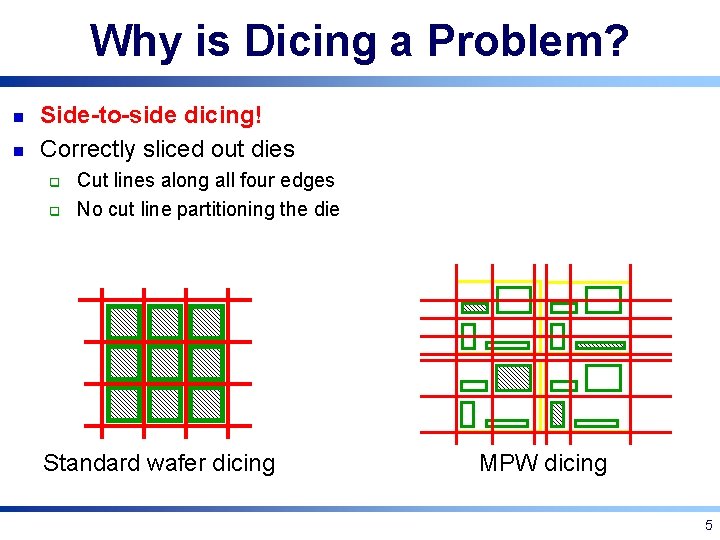

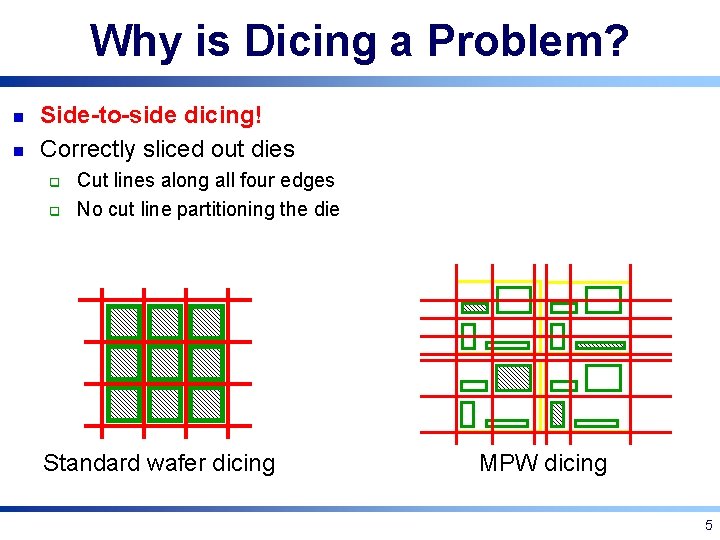

Why is Dicing a Problem? n n Side-to-side dicing! Correctly sliced out dies q q Cut lines along all four edges No cut line partitioning the die Standard wafer dicing MPW dicing 5

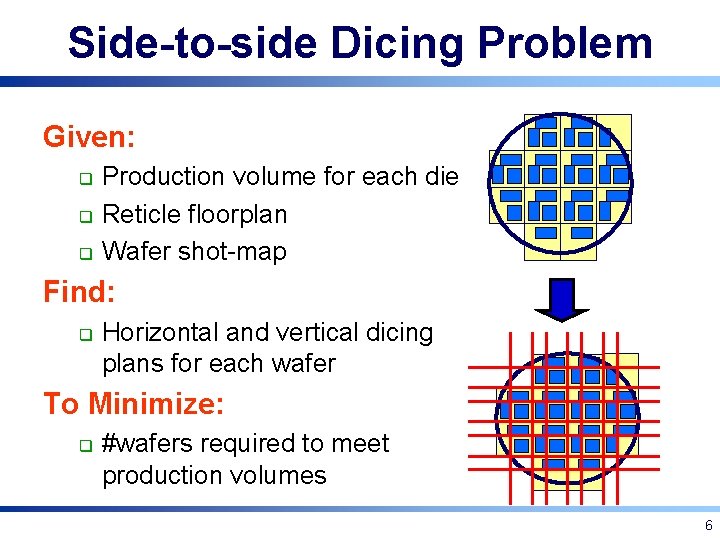

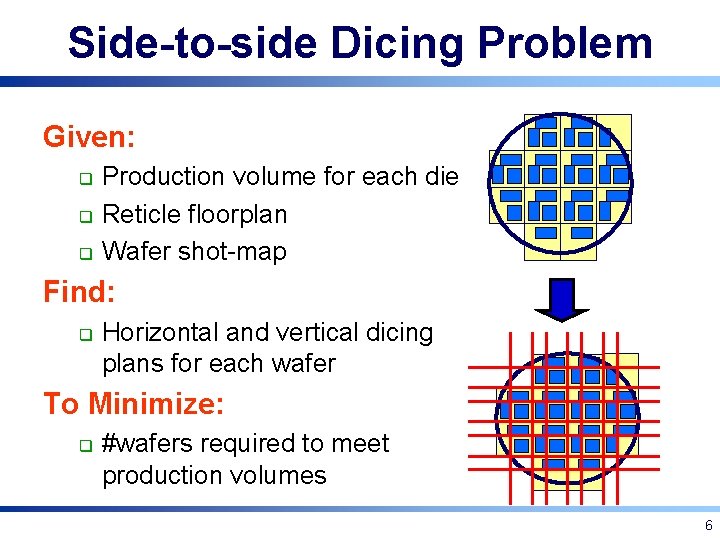

Side-to-side Dicing Problem Given: q q q Production volume for each die Reticle floorplan Wafer shot-map Find: q Horizontal and vertical dicing plans for each wafer To Minimize: q #wafers required to meet production volumes 6

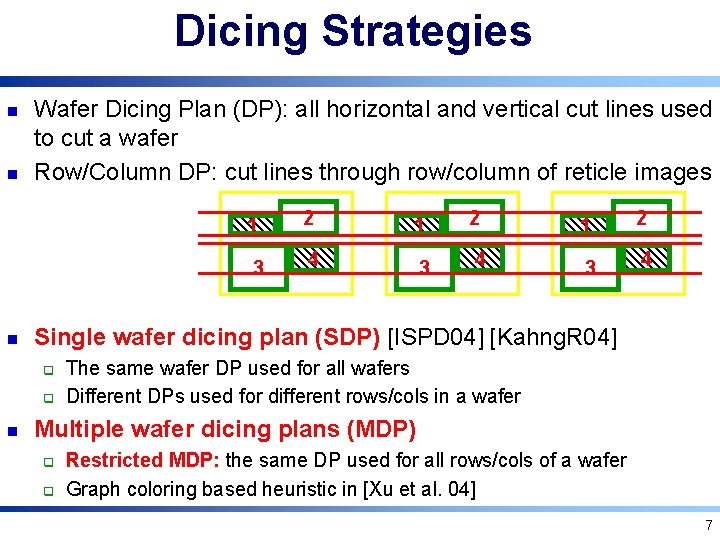

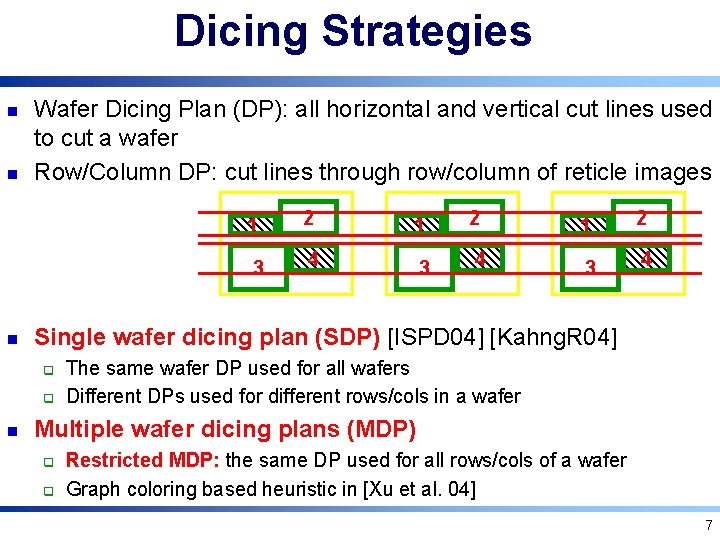

Dicing Strategies n n n Wafer Dicing Plan (DP): all horizontal and vertical cut lines used to cut a wafer Row/Column DP: cut lines through row/column of reticle images 2 1 2 3 4 3 4 Single wafer dicing plan (SDP) [ISPD 04] [Kahng. R 04] q q n 1 The same wafer DP used for all wafers Different DPs used for different rows/cols in a wafer Multiple wafer dicing plans (MDP) q q Restricted MDP: the same DP used for all rows/cols of a wafer Graph coloring based heuristic in [Xu et al. 04] 7

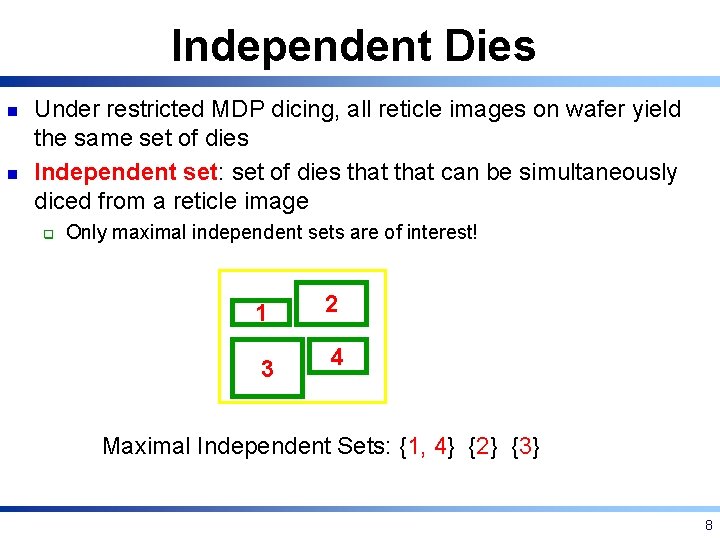

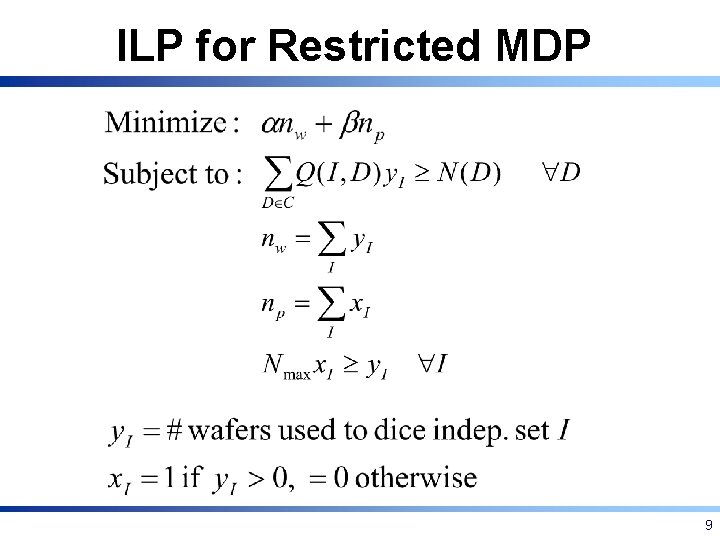

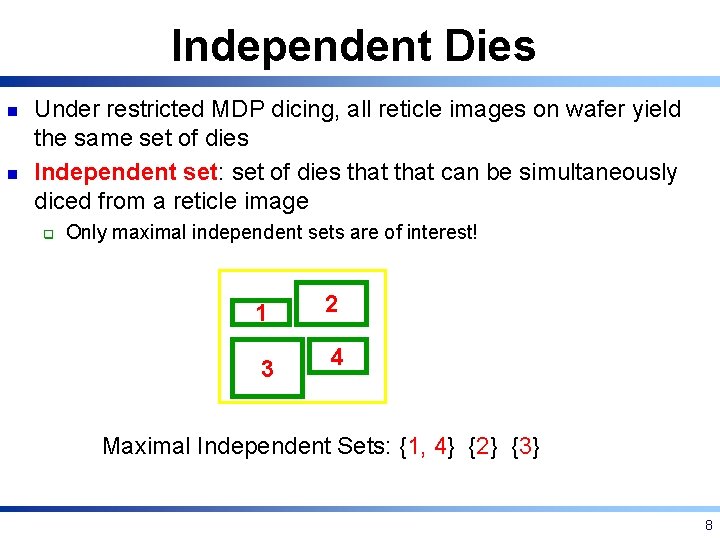

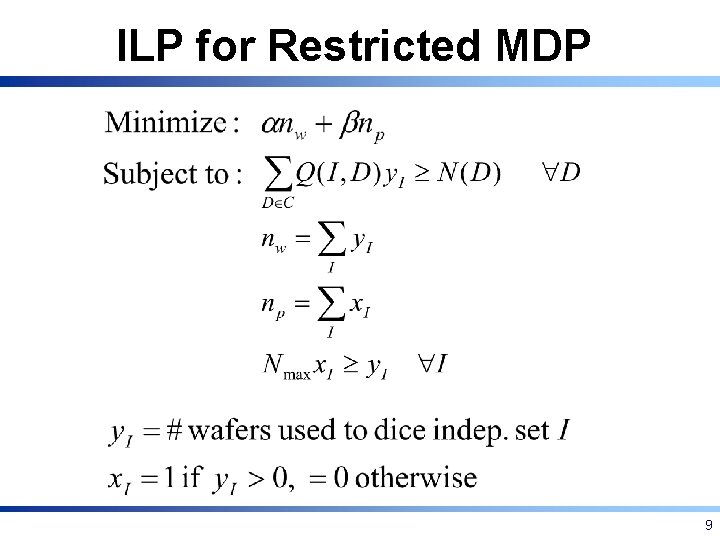

Independent Dies n n Under restricted MDP dicing, all reticle images on wafer yield the same set of dies Independent set: set of dies that can be simultaneously diced from a reticle image q Only maximal independent sets are of interest! 1 2 3 4 Maximal Independent Sets: {1, 4} {2} {3} 8

ILP for Restricted MDP 9

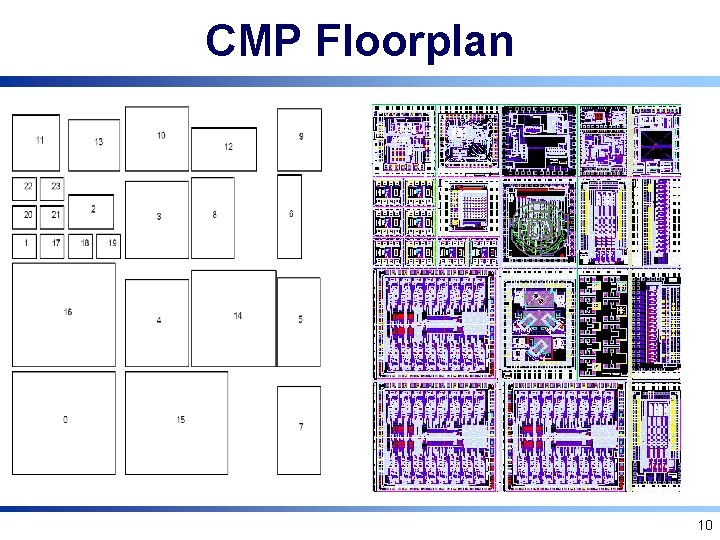

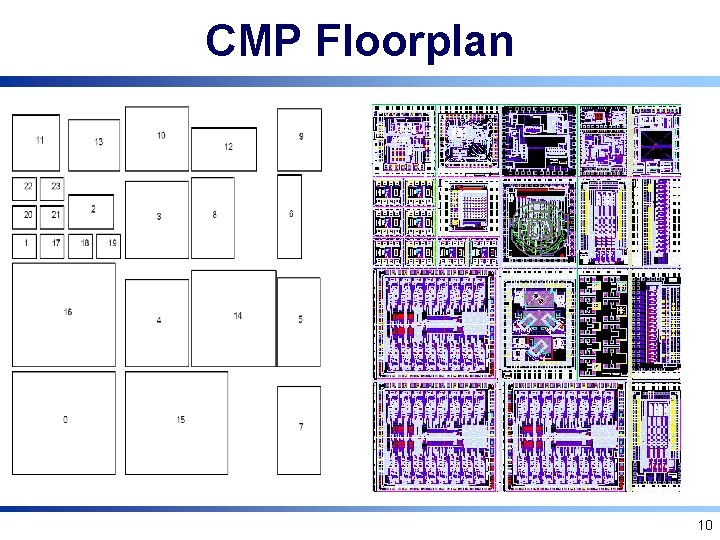

CMP Floorplan 10

SDP vs. MDP 9 wafers with SDP 5 wafers with MDP 11

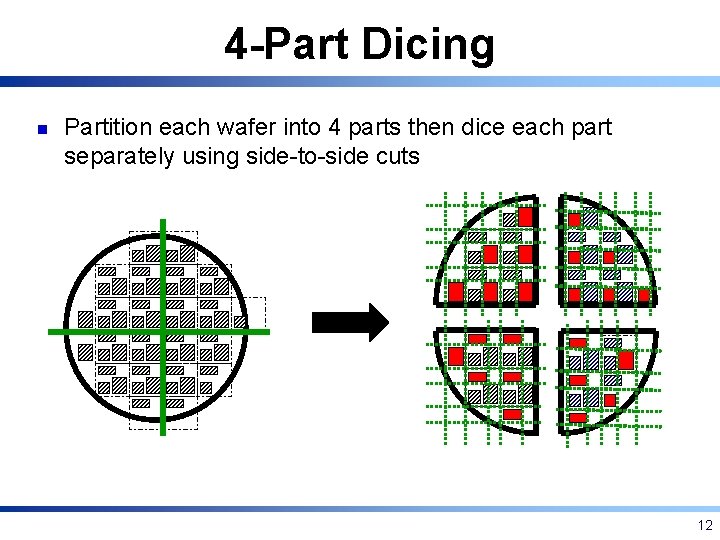

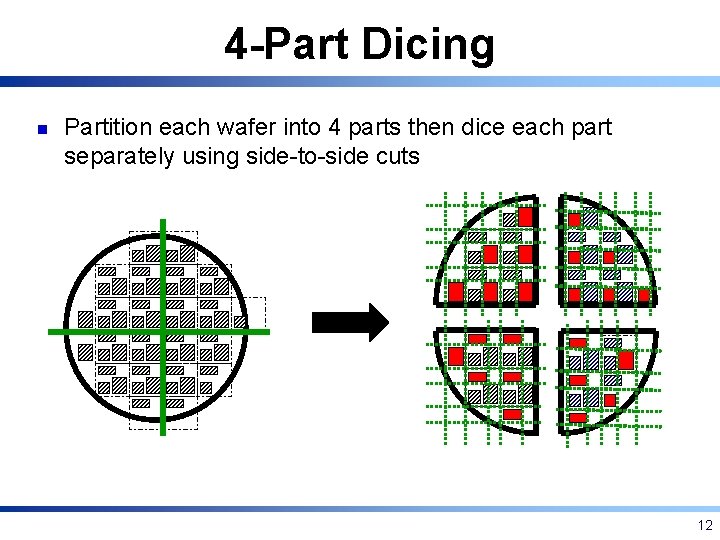

4 -Part Dicing n Partition each wafer into 4 parts then dice each part separately using side-to-side cuts 12

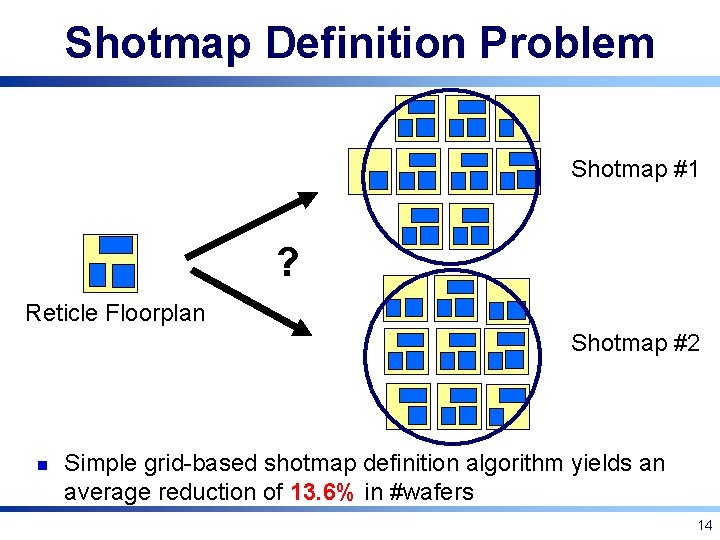

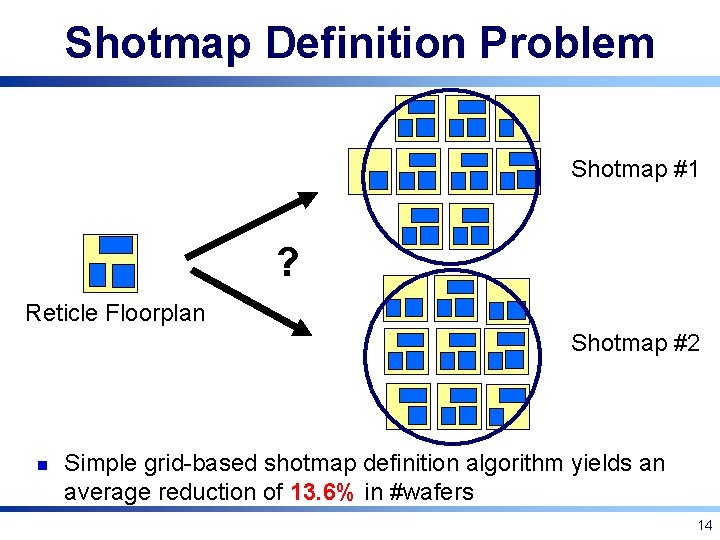

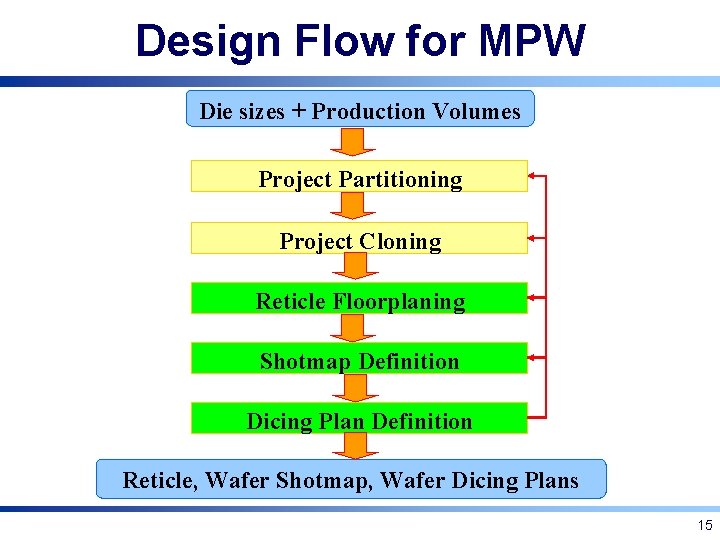

Design Flow for MPW Die sizes + Production Volumes Project Partitioning Project Cloning Reticle Floorplaning Shotmap Definition Dicing Plan Definition Reticle, Wafer Shotmap, Wafer Dicing Plans 13

Shotmap Definition Problem Shotmap #1 ? Reticle Floorplan Shotmap #2 n Simple grid-based shotmap definition algorithm yields an average reduction of 13. 6% in #wafers 14

Design Flow for MPW Die sizes + Production Volumes Project Partitioning Project Cloning Reticle Floorplaning Shotmap Definition Dicing Plan Definition Reticle, Wafer Shotmap, Wafer Dicing Plans 15

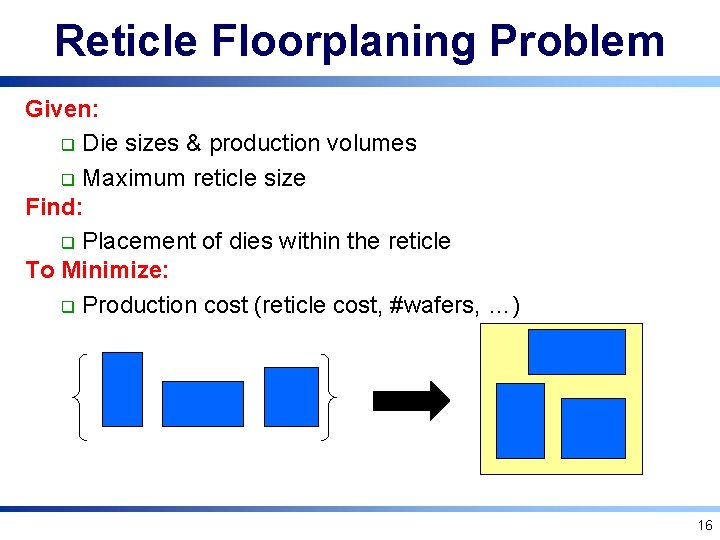

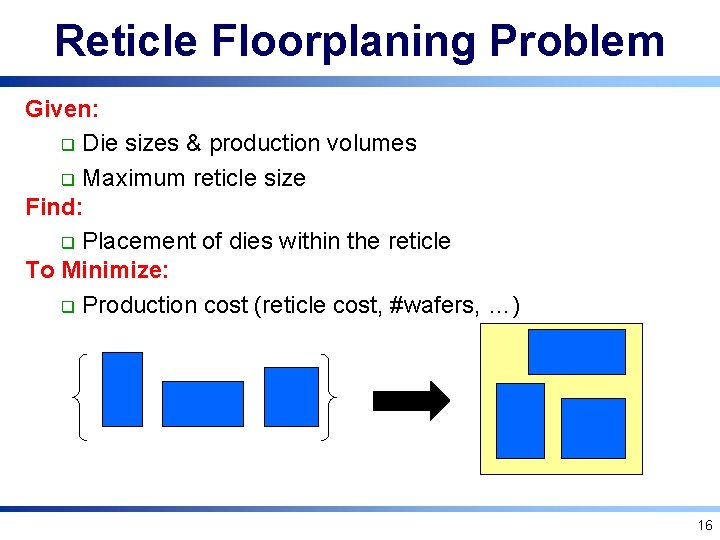

Reticle Floorplaning Problem Given: q Die sizes & production volumes q Maximum reticle size Find: q Placement of dies within the reticle To Minimize: q Production cost (reticle cost, #wafers, …) 16

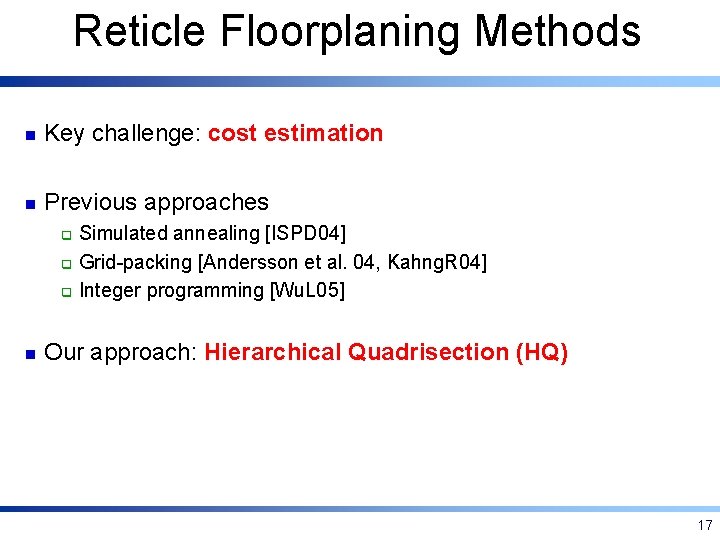

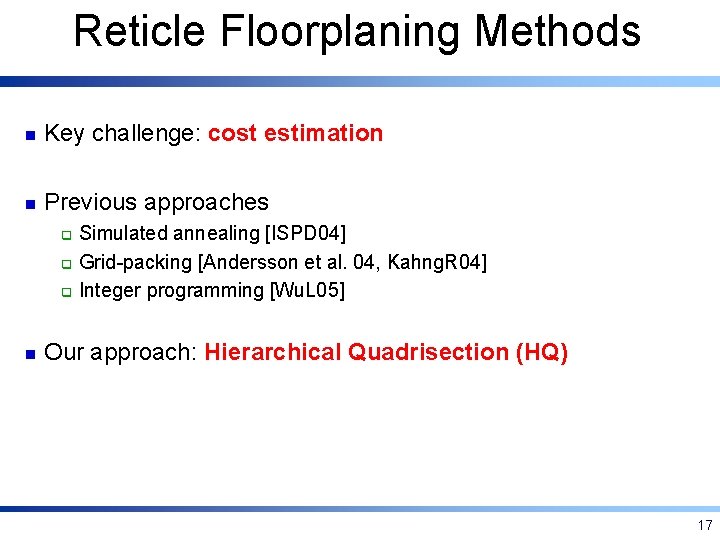

Reticle Floorplaning Methods n Key challenge: cost estimation n Previous approaches Simulated annealing [ISPD 04] q Grid-packing [Andersson et al. 04, Kahng. R 04] q Integer programming [Wu. L 05] q n Our approach: Hierarchical Quadrisection (HQ) 17

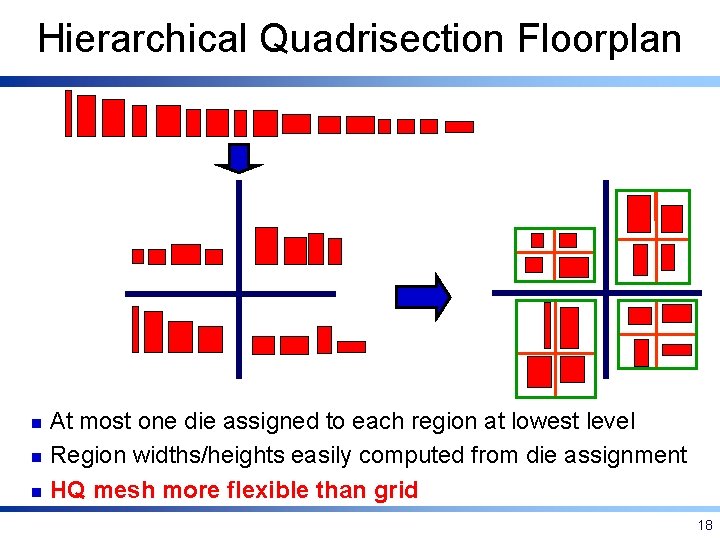

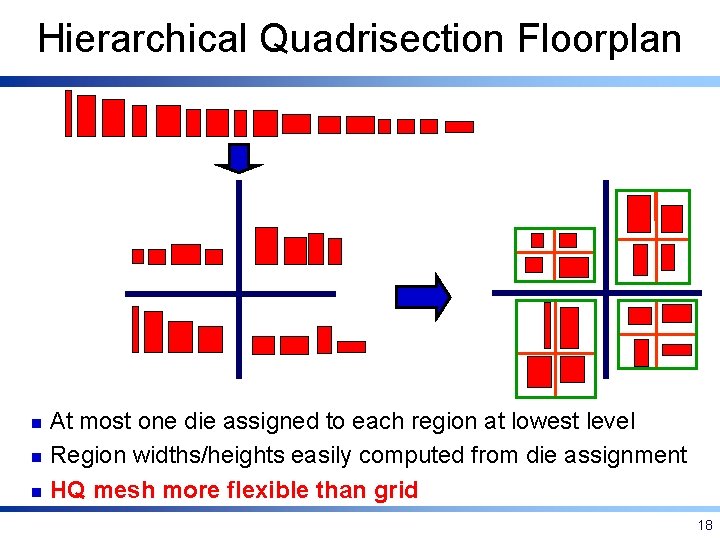

Hierarchical Quadrisection Floorplan At most one die assigned to each region at lowest level n Region widths/heights easily computed from die assignment n HQ mesh more flexible than grid n 18

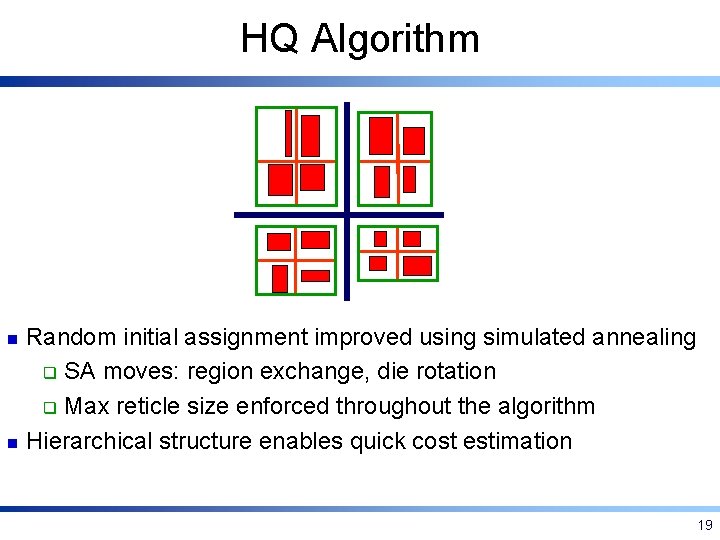

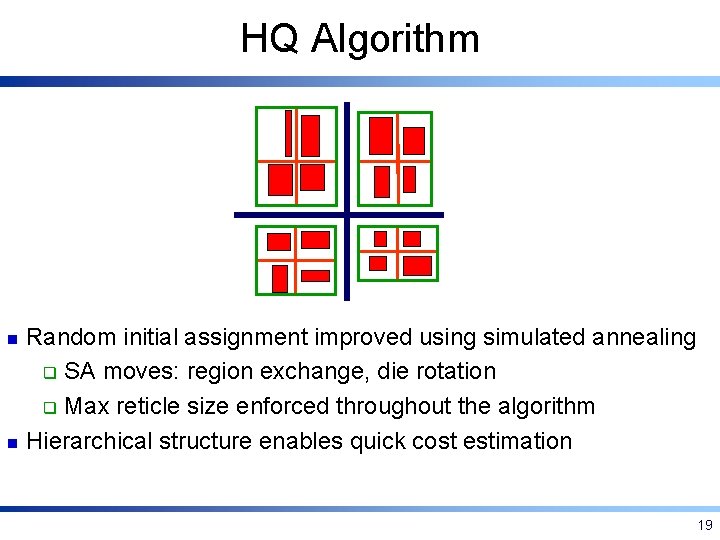

HQ Algorithm Random initial assignment improved using simulated annealing q SA moves: region exchange, die rotation q Max reticle size enforced throughout the algorithm n Hierarchical structure enables quick cost estimation n 19

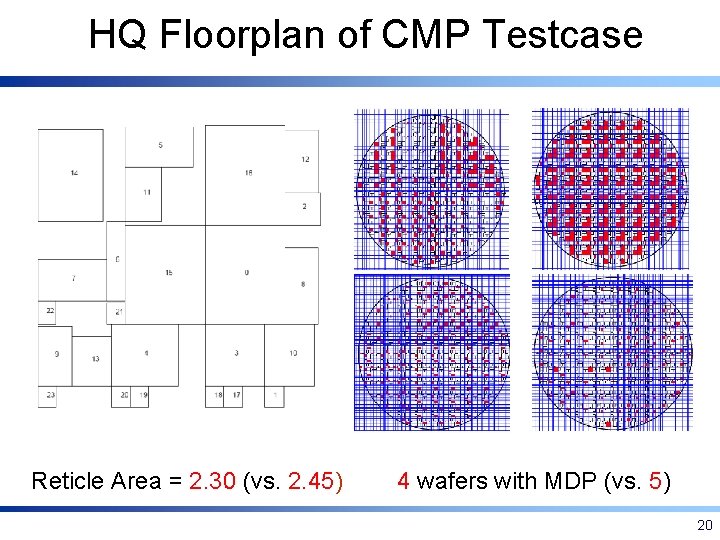

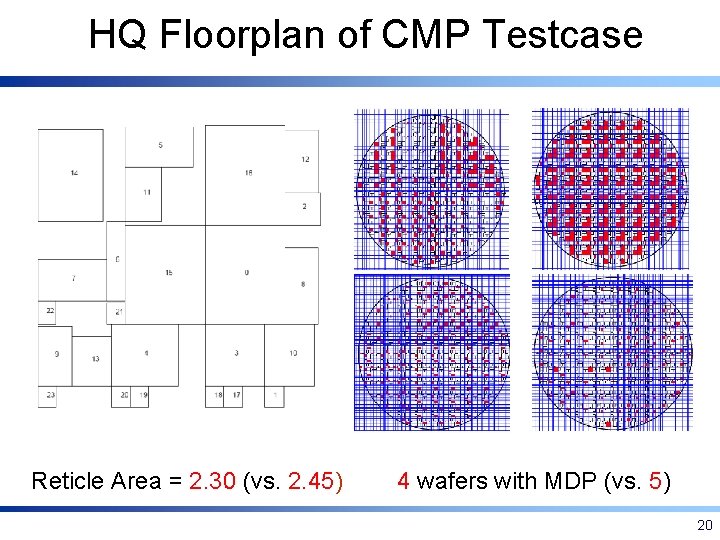

HQ Floorplan of CMP Testcase Reticle Area = 2. 30 (vs. 2. 45) 4 wafers with MDP (vs. 5) 20

Design Flow for MPW Die sizes + Production Volumes Project Partitioning Project Cloning Reticle Floorplaning Shotmap Definition Dicing Plan Definition Reticle, Wafer Shotmap, Wafer Dicing Plans 21

![Project Cloning n Motivation q q n Postprocessing approach Wu L 05 n n Project Cloning n Motivation q q n Post-processing approach [Wu. L 05] n n](https://slidetodoc.com/presentation_image_h/83ac786ea95e170fe8c1210ce11b6a4e/image-22.jpg)

Project Cloning n Motivation q q n Post-processing approach [Wu. L 05] n n Die-to-die inspection [Xu et al. ] Reduced wafer cost when there is large variation in production demands Insert clones in white space left on reticle Our approach q q q Before floorplaning: number of clones proportional to square root of production volume; clones arranged in clone arrays During floorplaning: clone arrays assigned to single cell in HQ; new SA moves: add/delete clone array row/column After floorplaning: insert additional clone array rows/columns without increasing cell size 22

Design Flow for MPW Die sizes + Production Volumes Project Partitioning Project Cloning Reticle Floorplaning Shotmap Definition Dicing Plan Definition Reticle, Wafer Shotmap, Wafer Dicing Plans 23

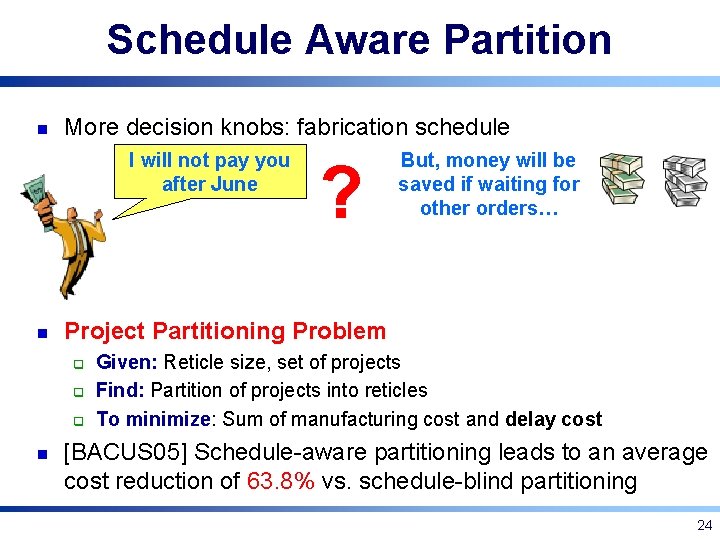

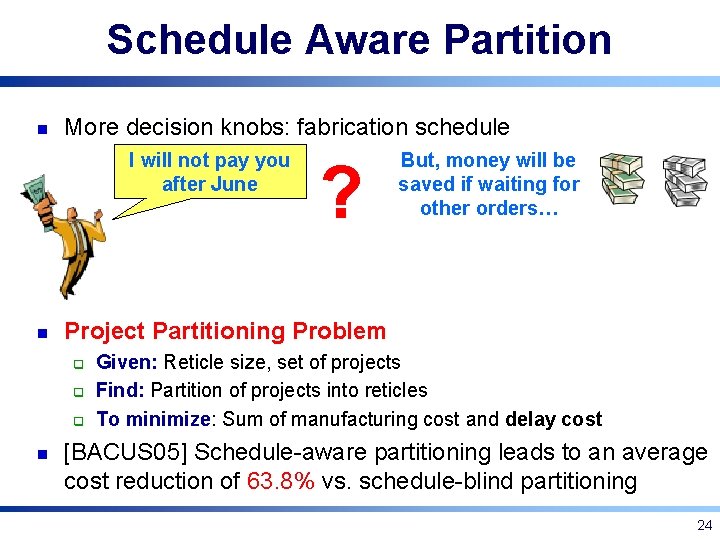

Schedule Aware Partition n More decision knobs: fabrication schedule I will not pay you after June n Project Partitioning Problem q q q n ? But, money will be saved if waiting for other orders… Given: Reticle size, set of projects Find: Partition of projects into reticles To minimize: Sum of manufacturing cost and delay cost [BACUS 05] Schedule-aware partitioning leads to an average cost reduction of 63. 8% vs. schedule-blind partitioning 24

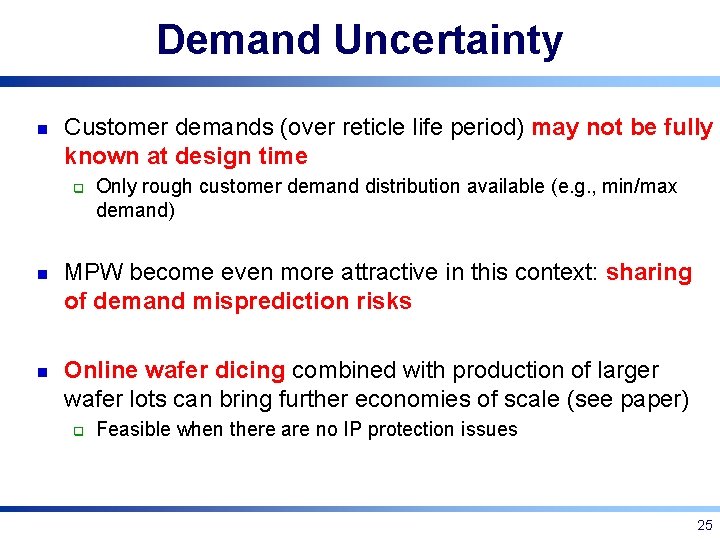

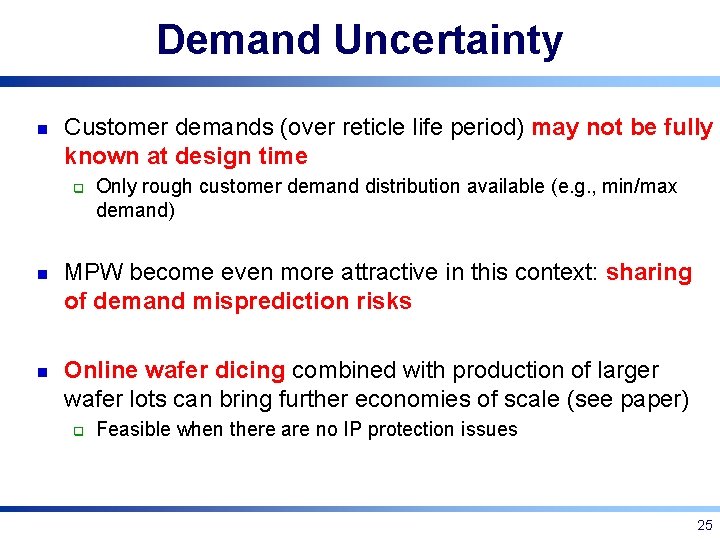

Demand Uncertainty n Customer demands (over reticle life period) may not be fully known at design time q Only rough customer demand distribution available (e. g. , min/max demand) n MPW become even more attractive in this context: sharing of demand misprediction risks n Online wafer dicing combined with production of larger wafer lots can bring further economies of scale (see paper) q Feasible when there are no IP protection issues 25

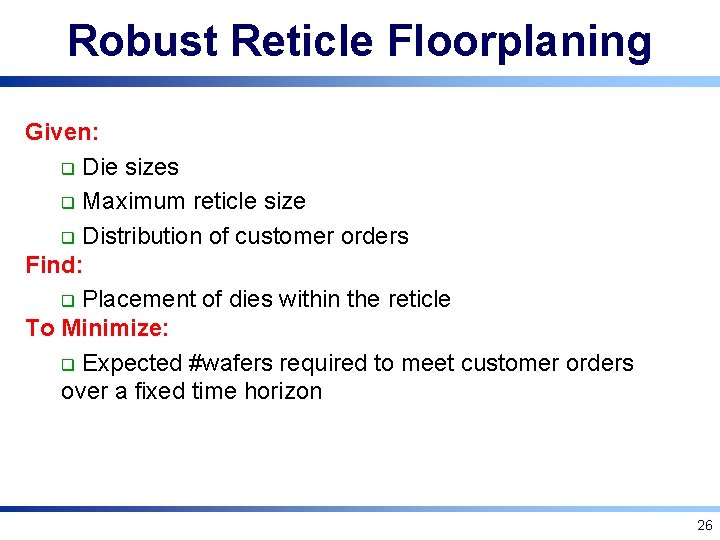

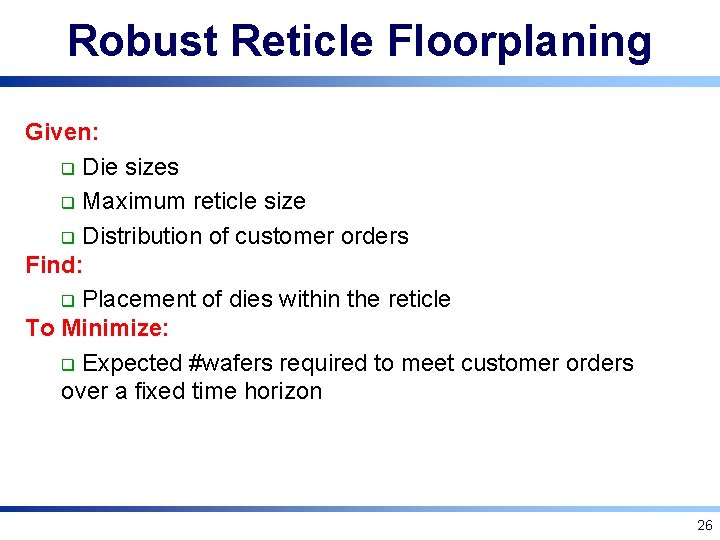

Robust Reticle Floorplaning Given: q Die sizes q Maximum reticle size q Distribution of customer orders Find: q Placement of dies within the reticle To Minimize: q Expected #wafers required to meet customer orders over a fixed time horizon 26

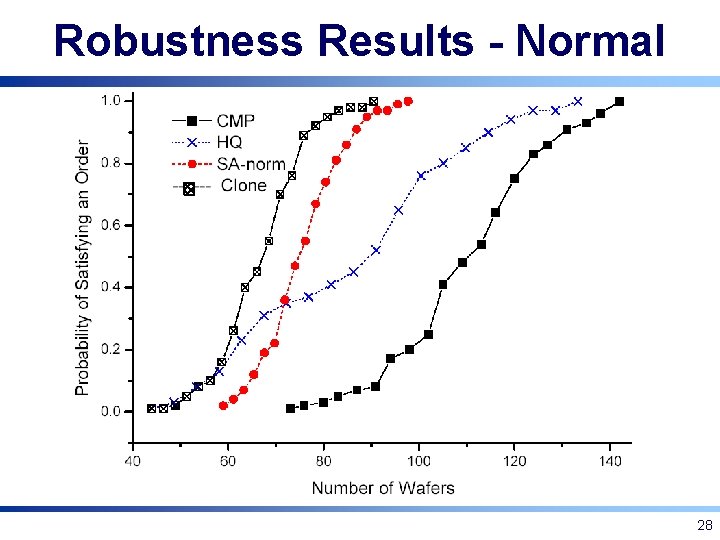

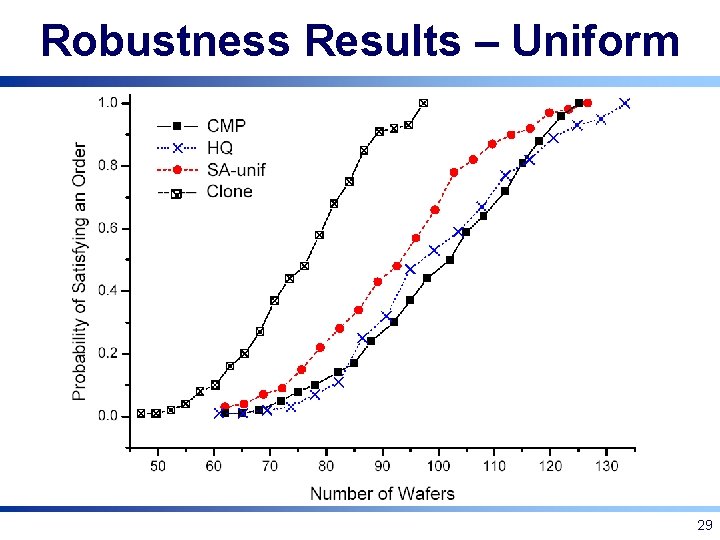

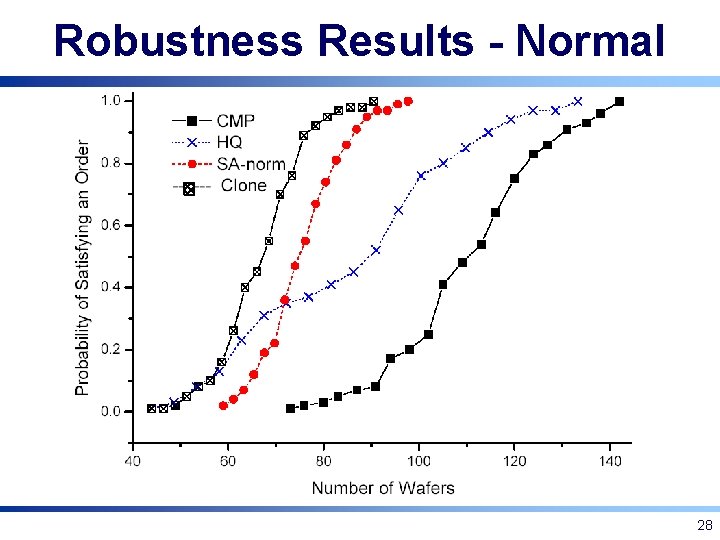

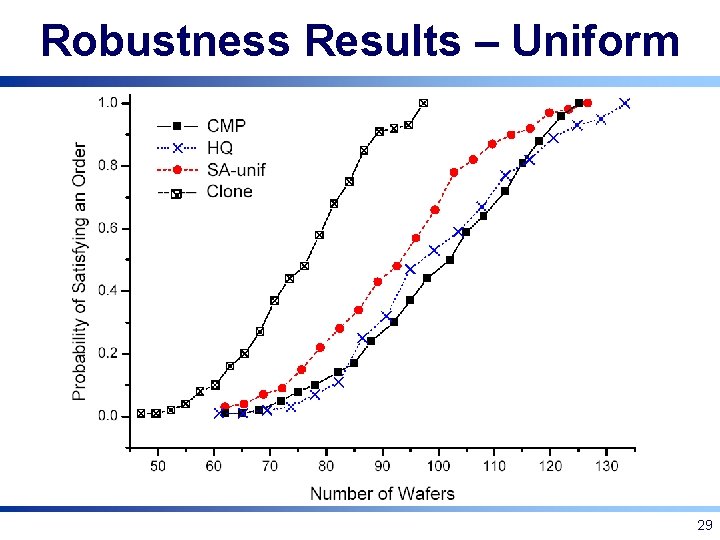

Compared Algorithms n HQ with production volume set to the expected customer demand n HQ+Cloning with production volume set to the expected customer demand n Distribution-driven simulated annealing q Use expected production cost for evaluating SA moves q Monte-Carlo simulation used to estimate expected cost 27

Robustness Results - Normal 28

Robustness Results – Uniform 29

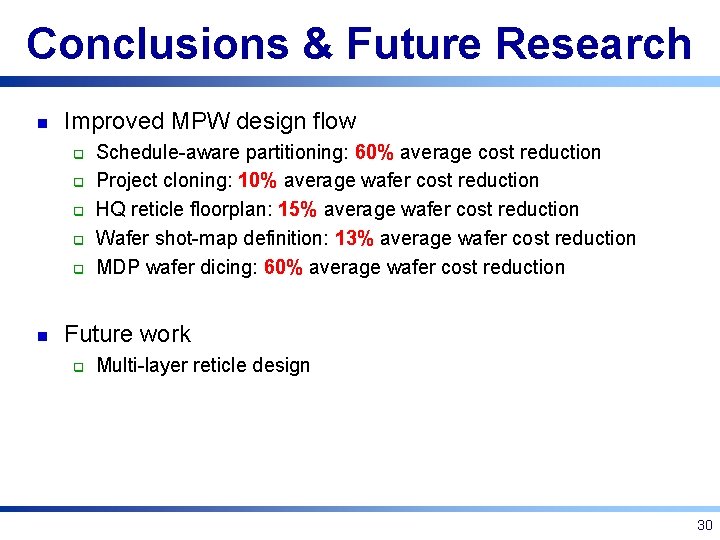

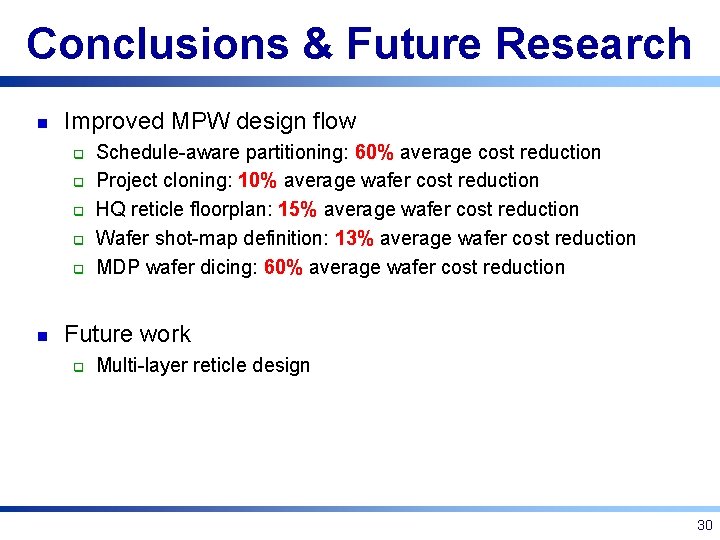

Conclusions & Future Research n Improved MPW design flow q q q n Schedule-aware partitioning: 60% average cost reduction Project cloning: 10% average wafer cost reduction HQ reticle floorplan: 15% average wafer cost reduction Wafer shot-map definition: 13% average wafer cost reduction MDP wafer dicing: 60% average wafer cost reduction Future work q Multi-layer reticle design 30