L 14 VHDL Language Elements II VHDL Language

![The Process Statement o PROCESS STATEMENT n n n o o [process_label: ] process The Process Statement o PROCESS STATEMENT n n n o o [process_label: ] process](https://slidetodoc.com/presentation_image_h/08d14d9c69a789d95fd1425c45b0fd1a/image-10.jpg)

![Loops o Form n n n n o [loop_label: ] [iteration_scheme] loop sequence_of_statements; end Loops o Form n n n n o [loop_label: ] [iteration_scheme] loop sequence_of_statements; end](https://slidetodoc.com/presentation_image_h/08d14d9c69a789d95fd1425c45b0fd1a/image-14.jpg)

- Slides: 19

L 14 – VHDL Language Elements II

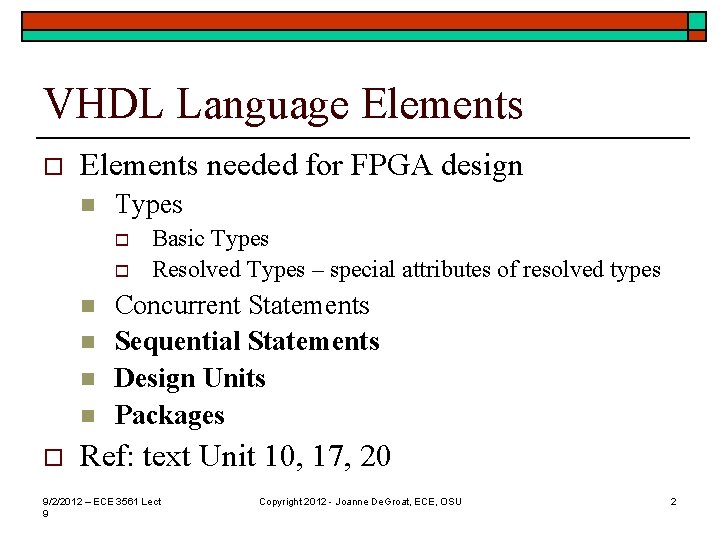

VHDL Language Elements o Elements needed for FPGA design n Types o o n n o Basic Types Resolved Types – special attributes of resolved types Concurrent Statements Sequential Statements Design Units Packages Ref: text Unit 10, 17, 20 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

Concurrent Statements o o o Concurrent statements appear between the BEGIN and END of an ARCHITECTURE So far have covered the Component Instantiation Statement BLOCK Statement – not to be convered Concurrent Procedure call – not synthesizable Concurrent Assertion Statement - for verificaiton 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 3

Used statements o Concurrent signal assignments statements n n n o X <= A and B or C; SUM <= A xor B xor C; Cout <= A and B or A and Cin or B and Cin; For synthesis typically have no need of using the AFTER to add delay to the output. n X <= A and B or C AFTER 5 ns; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 4

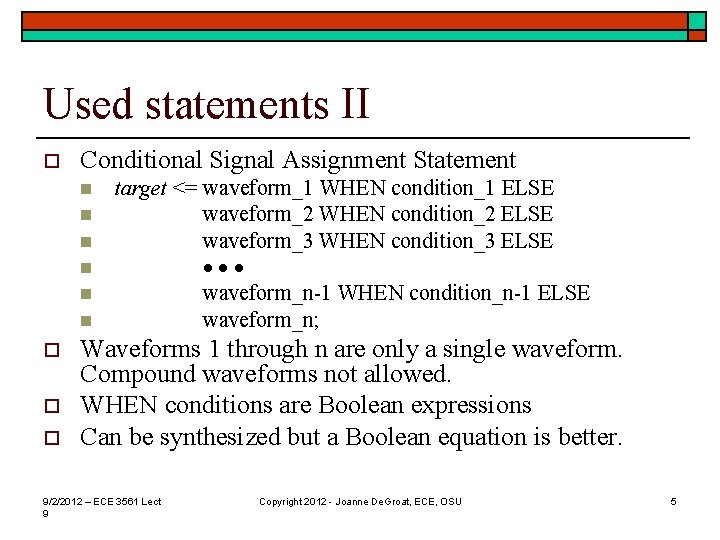

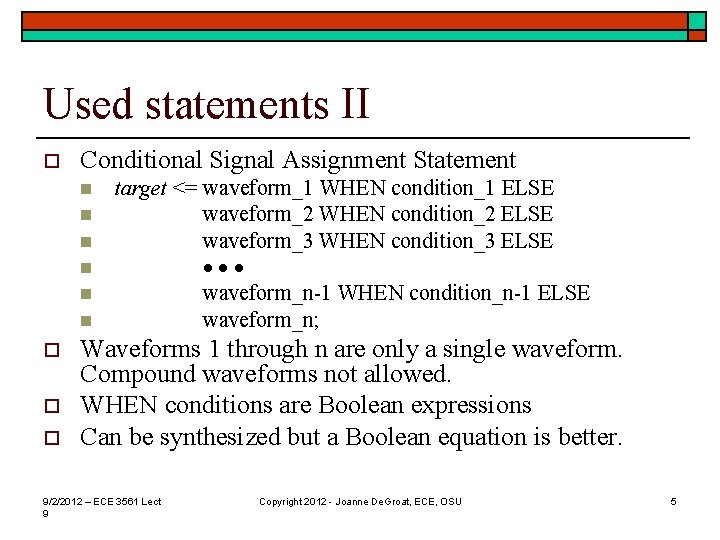

Used statements II o Conditional Signal Assignment Statement n n n o o o target <= waveform_1 WHEN condition_1 ELSE waveform_2 WHEN condition_2 ELSE waveform_3 WHEN condition_3 ELSE ··· waveform_n-1 WHEN condition_n-1 ELSE waveform_n; Waveforms 1 through n are only a single waveform. Compound waveforms not allowed. WHEN conditions are Boolean expressions Can be synthesized but a Boolean equation is better. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 5

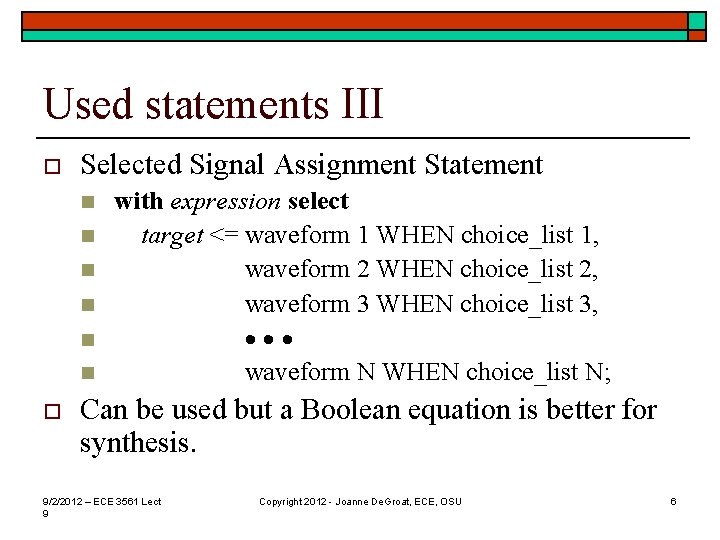

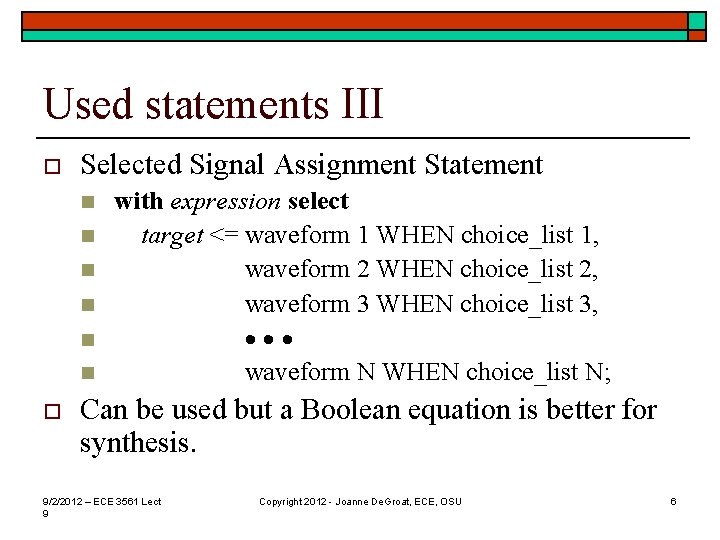

Used statements III o Selected Signal Assignment Statement n n n o with expression select target <= waveform 1 WHEN choice_list 1, waveform 2 WHEN choice_list 2, waveform 3 WHEN choice_list 3, ··· waveform N WHEN choice_list N; Can be used but a Boolean equation is better for synthesis. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 6

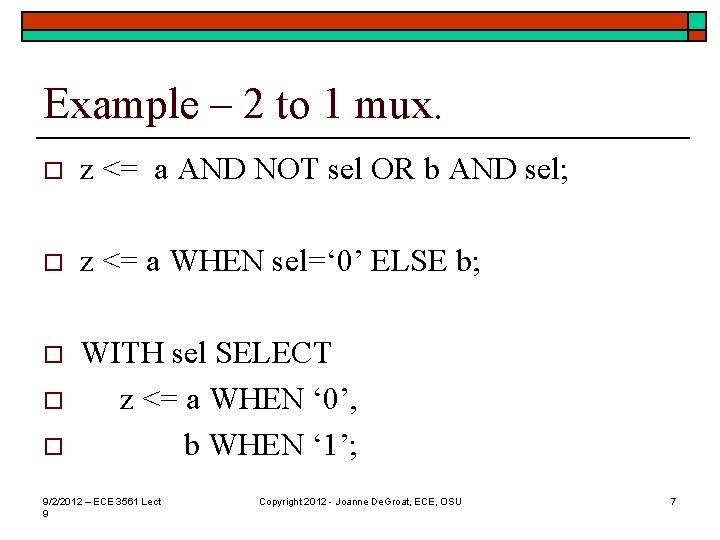

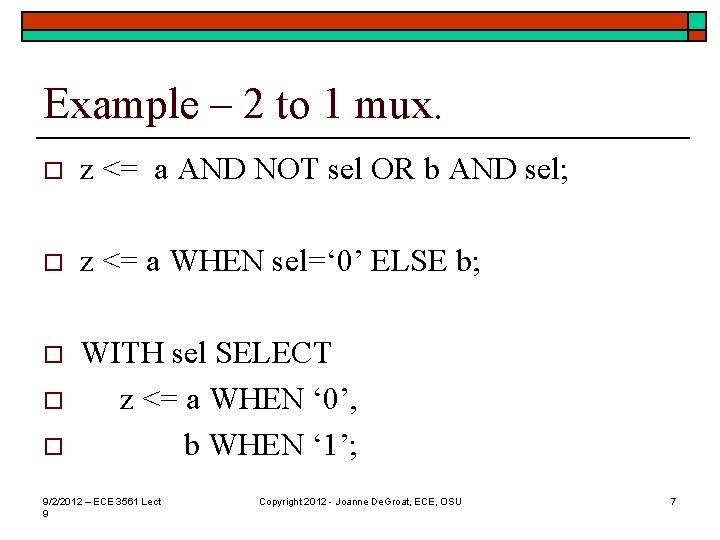

Example – 2 to 1 mux. o z <= a AND NOT sel OR b AND sel; o z <= a WHEN sel=‘ 0’ ELSE b; o WITH sel SELECT z <= a WHEN ‘ 0’, b WHEN ‘ 1’; o o 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 7

2 nd example – 1 st preferred o z <= (a AND NOT sel 1 AND NOT sel 0) OR (b AND NOT sel 1 AND sel 0) OR (c AND sel 1 AND NOT sel 0) OR (d AND sel 1 AND sel 0); o WITH sel 1&sel 0 SELECT n n o o z <= a WHEN “ 00”, b WHEN “ 01”, c WHEN “ 10”, d WHEN “ 11”; z <= a WHEN sel 1&sel 0 = “ 00” ELSE b WHEN sel 1&sel 0 = “ 01” ELSE c WHEN sel 1&sel 0 = “ 10” ELSE d; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 8

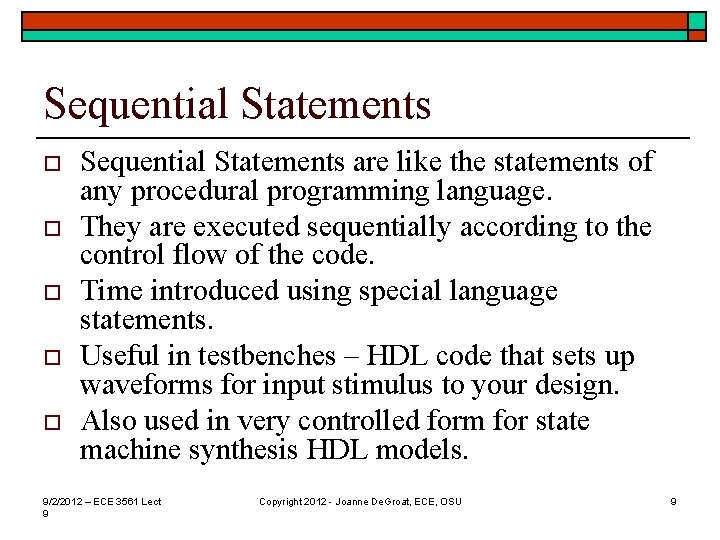

Sequential Statements o o o Sequential Statements are like the statements of any procedural programming language. They are executed sequentially according to the control flow of the code. Time introduced using special language statements. Useful in testbenches – HDL code that sets up waveforms for input stimulus to your design. Also used in very controlled form for state machine synthesis HDL models. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 9

![The Process Statement o PROCESS STATEMENT n n n o o processlabel process The Process Statement o PROCESS STATEMENT n n n o o [process_label: ] process](https://slidetodoc.com/presentation_image_h/08d14d9c69a789d95fd1425c45b0fd1a/image-10.jpg)

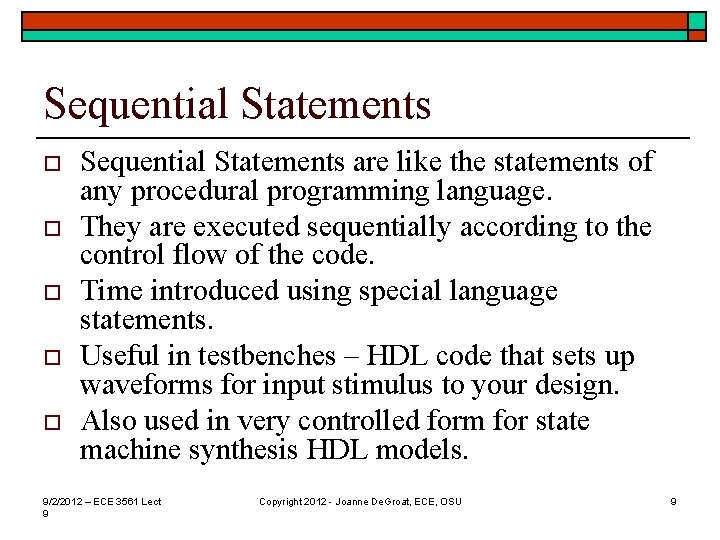

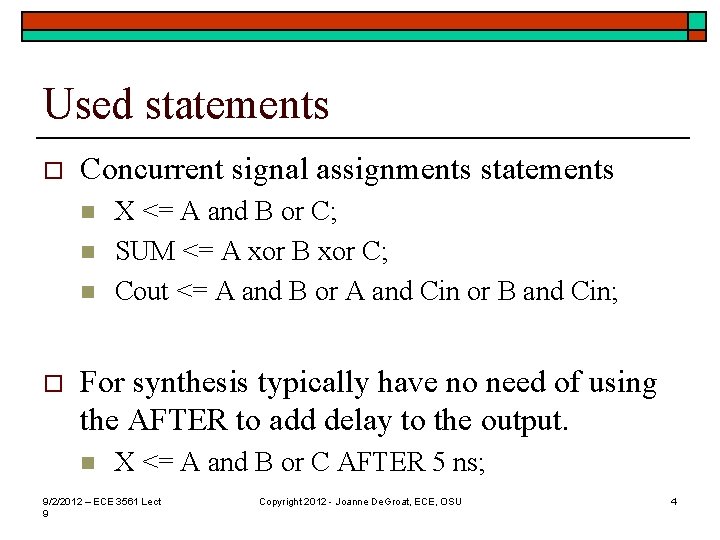

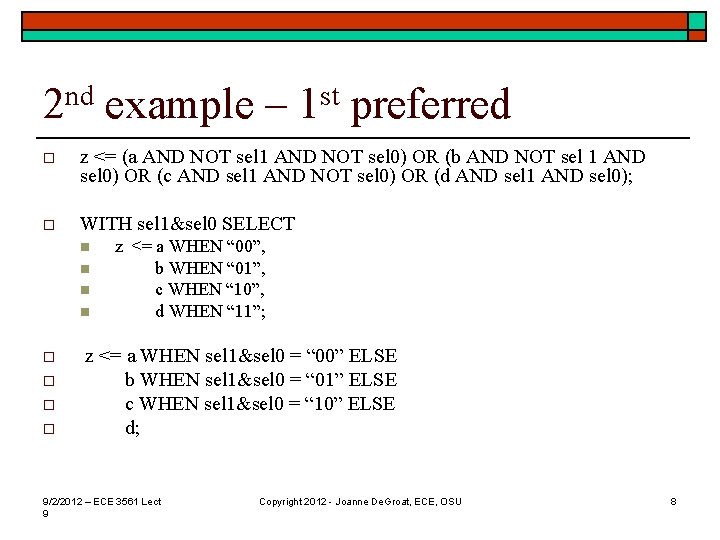

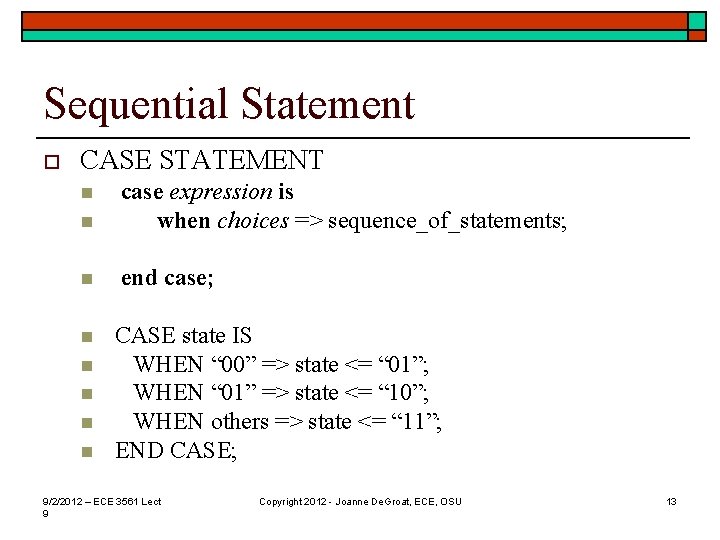

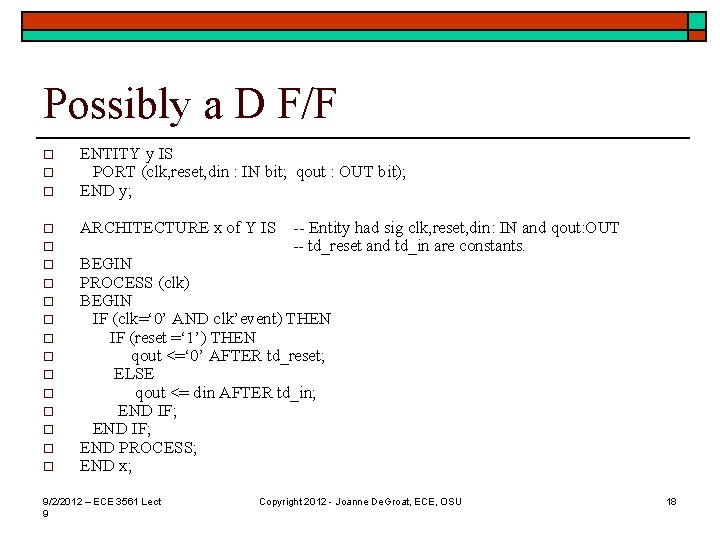

The Process Statement o PROCESS STATEMENT n n n o o [process_label: ] process [ (sensitivity_list) ] process_declarative_part begin process_statement_part -- {sequential statement} end process [process_label]; The process statement as a whole is a concurrent statement Statements between the BEGIN and END of a process are sequential – like the statements of any HLL. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 10

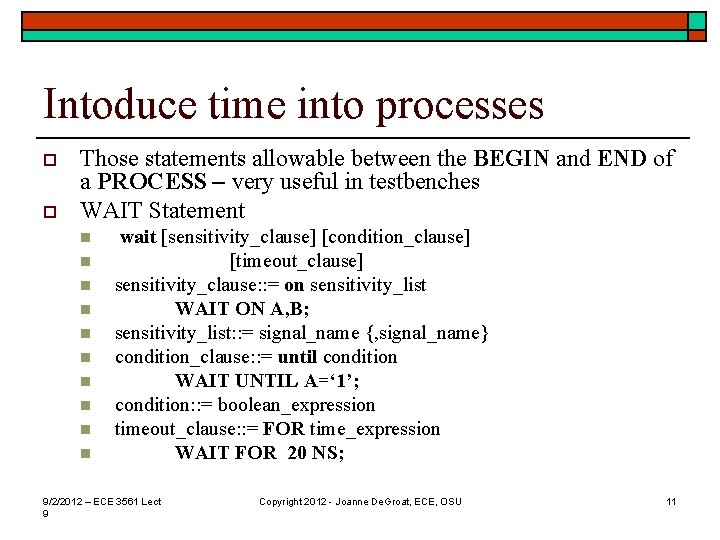

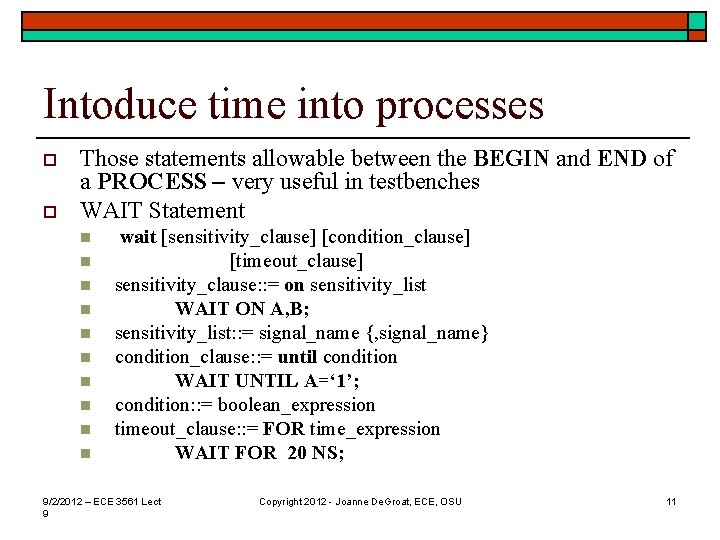

Intoduce time into processes o o Those statements allowable between the BEGIN and END of a PROCESS – very useful in testbenches WAIT Statement n n n n n wait [sensitivity_clause] [condition_clause] [timeout_clause] sensitivity_clause: : = on sensitivity_list WAIT ON A, B; sensitivity_list: : = signal_name {, signal_name} condition_clause: : = until condition WAIT UNTIL A=‘ 1’; condition: : = boolean_expression timeout_clause: : = FOR time_expression WAIT FOR 20 NS; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 11

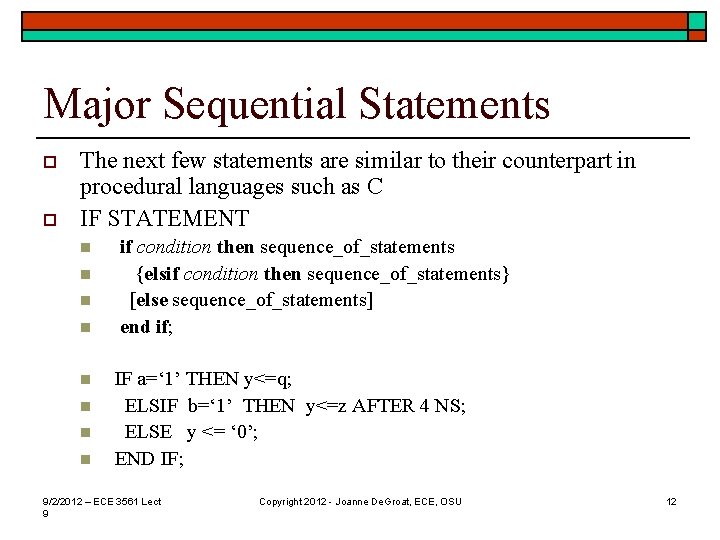

Major Sequential Statements o o The next few statements are similar to their counterpart in procedural languages such as C IF STATEMENT n n n n if condition then sequence_of_statements {elsif condition then sequence_of_statements} [else sequence_of_statements] end if; IF a=‘ 1’ THEN y<=q; ELSIF b=‘ 1’ THEN y<=z AFTER 4 NS; ELSE y <= ‘ 0’; END IF; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 12

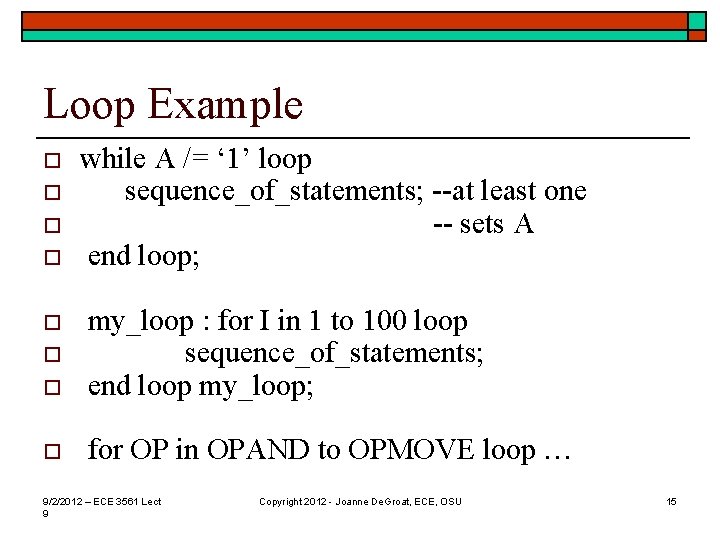

Sequential Statement o CASE STATEMENT n case expression is when choices => sequence_of_statements; n end case; n n n CASE state IS WHEN “ 00” => state <= “ 01”; WHEN “ 01” => state <= “ 10”; WHEN others => state <= “ 11”; END CASE; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 13

![Loops o Form n n n n o looplabel iterationscheme loop sequenceofstatements end Loops o Form n n n n o [loop_label: ] [iteration_scheme] loop sequence_of_statements; end](https://slidetodoc.com/presentation_image_h/08d14d9c69a789d95fd1425c45b0fd1a/image-14.jpg)

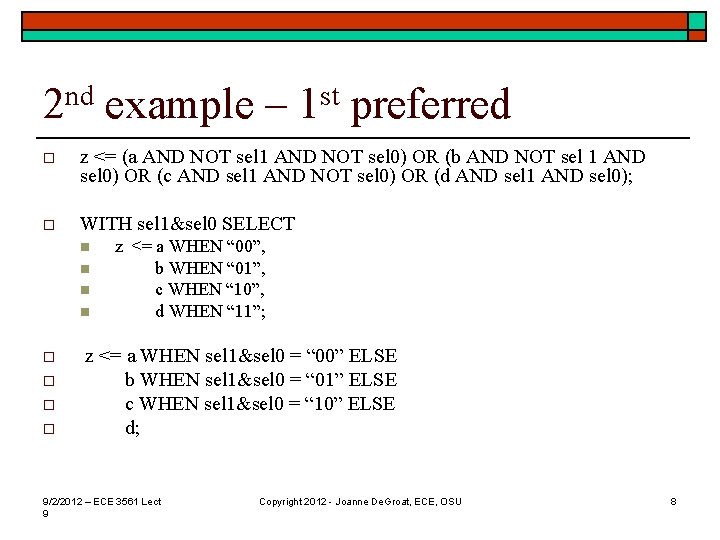

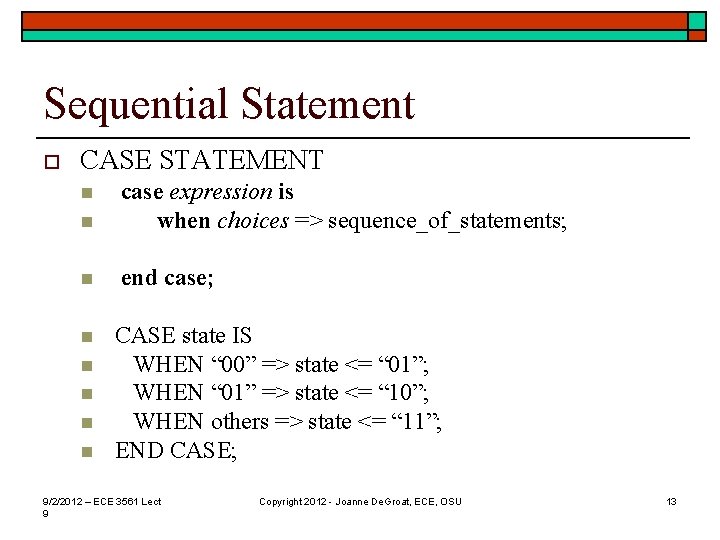

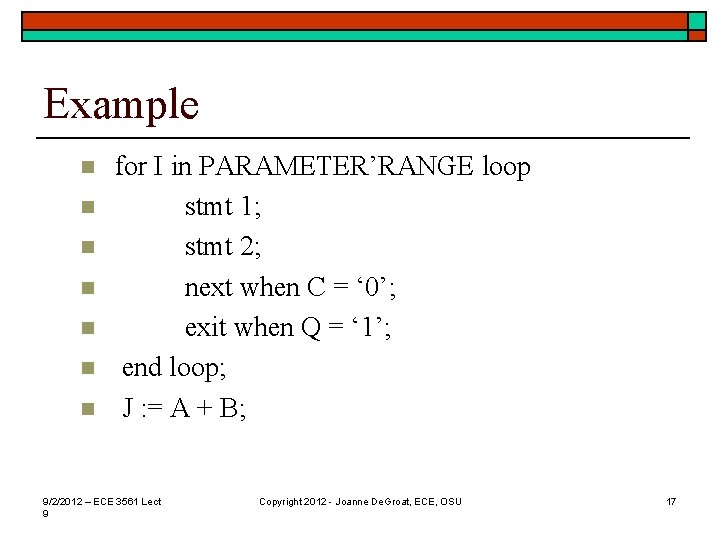

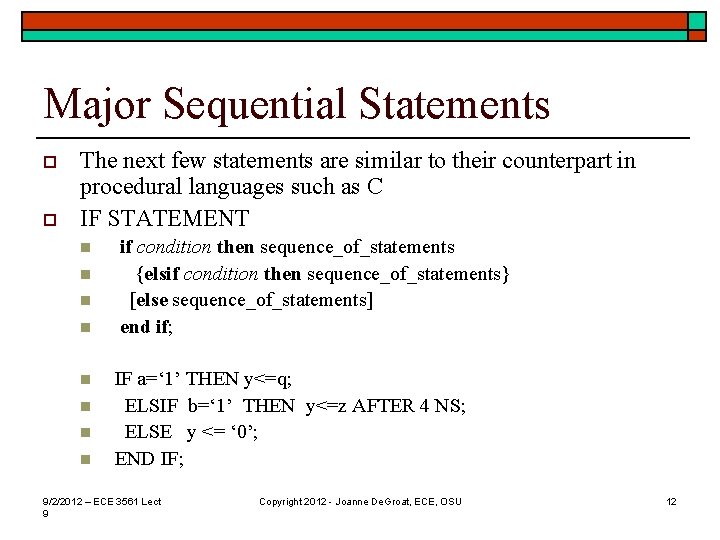

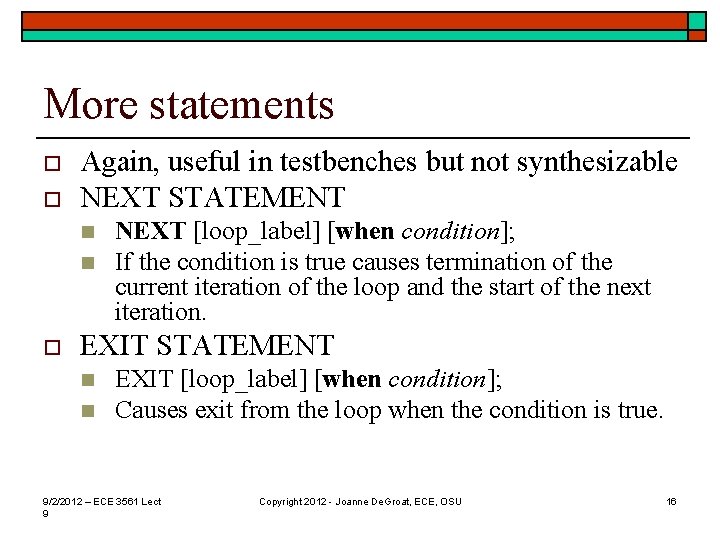

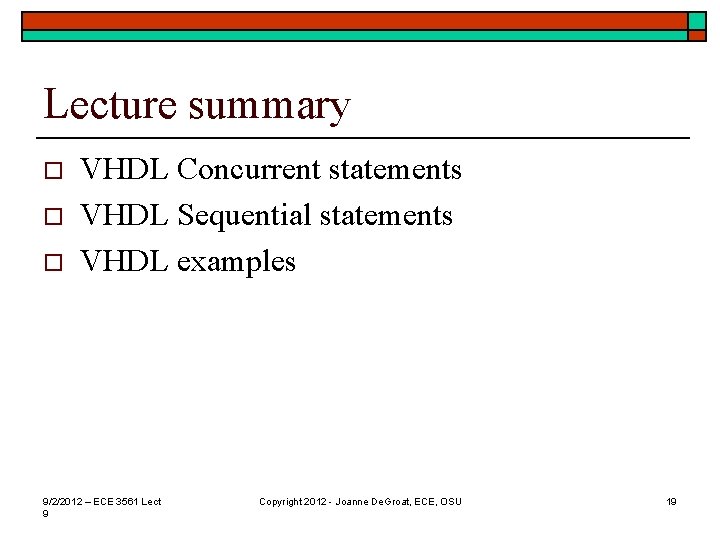

Loops o Form n n n n o [loop_label: ] [iteration_scheme] loop sequence_of_statements; end loop [loop_label]; iteration_scheme: : = while condition | for loop_parameter_specification: : = identifier in discrete_range Useful in testbenches but limited use in models to be synthesized. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 14

Loop Example o o while A /= ‘ 1’ loop sequence_of_statements; --at least one -- sets A end loop; o my_loop : for I in 1 to 100 loop sequence_of_statements; end loop my_loop; o for OP in OPAND to OPMOVE loop … o o 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 15

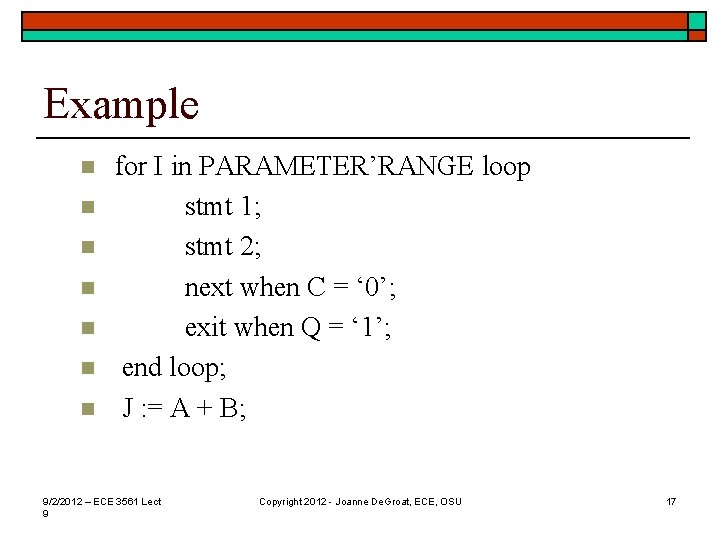

More statements o o Again, useful in testbenches but not synthesizable NEXT STATEMENT n n o NEXT [loop_label] [when condition]; If the condition is true causes termination of the current iteration of the loop and the start of the next iteration. EXIT STATEMENT n n EXIT [loop_label] [when condition]; Causes exit from the loop when the condition is true. 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 16

Example n n n n for I in PARAMETER’RANGE loop stmt 1; stmt 2; next when C = ‘ 0’; exit when Q = ‘ 1’; end loop; J : = A + B; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 17

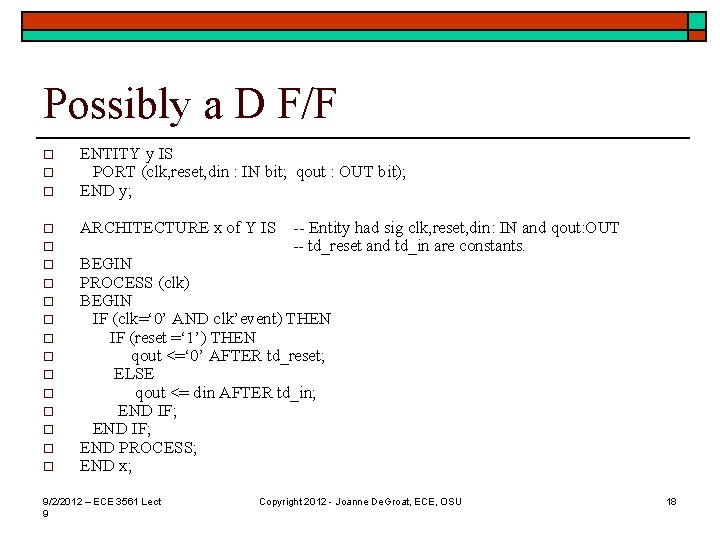

Possibly a D F/F o o o ENTITY y IS PORT (clk, reset, din : IN bit; qout : OUT bit); END y; o o o o ARCHITECTURE x of Y IS -- Entity had sig clk, reset, din: IN and qout: OUT -- td_reset and td_in are constants. BEGIN PROCESS (clk) BEGIN IF (clk=‘ 0’ AND clk’event) THEN IF (reset =‘ 1’) THEN qout <=‘ 0’ AFTER td_reset; ELSE qout <= din AFTER td_in; END IF; END PROCESS; END x; 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 18

Lecture summary o o o VHDL Concurrent statements VHDL Sequential statements VHDL examples 9/2/2012 – ECE 3561 Lect 9 Copyright 2012 - Joanne De. Groat, ECE, OSU 19