Konani automati o o o eng Finite State

- Slides: 30

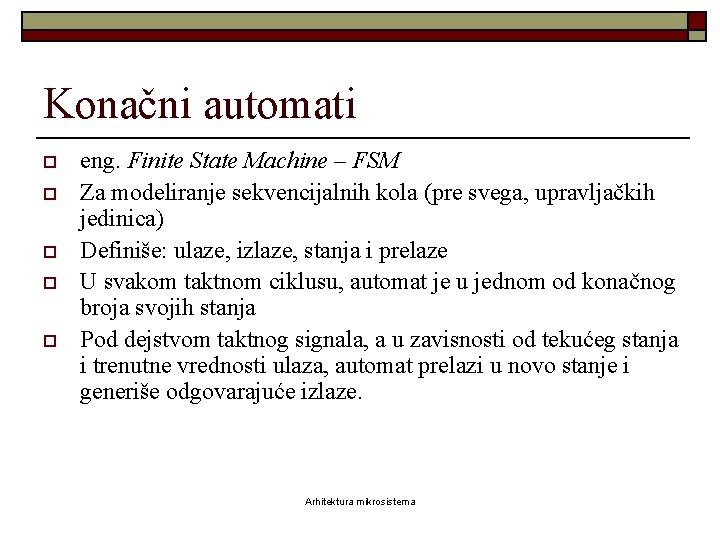

Konačni automati o o o eng. Finite State Machine – FSM Za modeliranje sekvencijalnih kola (pre svega, upravljačkih jedinica) Definiše: ulaze, izlaze, stanja i prelaze U svakom taktnom ciklusu, automat je u jednom od konačnog broja svojih stanja Pod dejstvom taktnog signala, a u zavisnosti od tekućeg stanja i trenutne vrednosti ulaza, automat prelazi u novo stanje i generiše odgovarajuće izlaze. Arhitektura mikrosistema

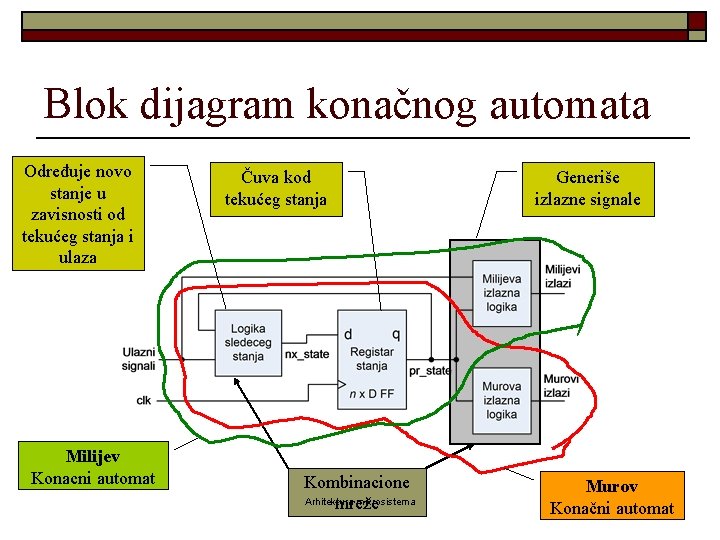

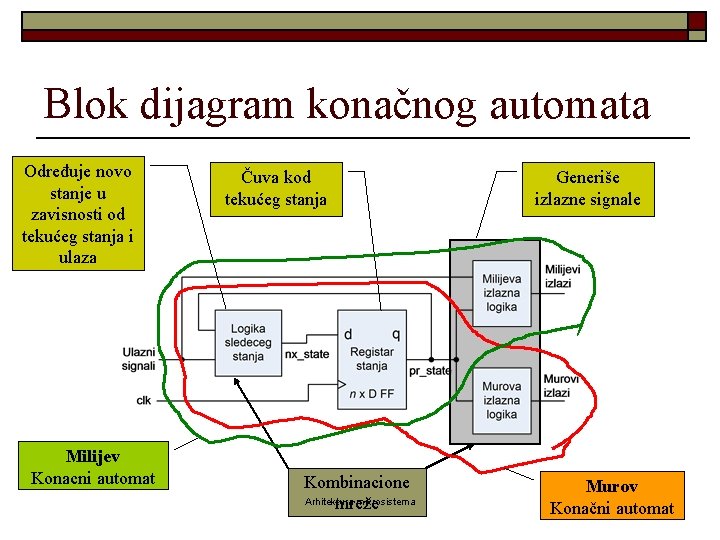

Blok dijagram konačnog automata Određuje novo stanje u zavisnosti od tekućeg stanja i ulaza Milijev Konacni automat Čuva kod tekućeg stanja Kombinacione Arhitektura mikrosistema mreže Generiše izlazne signale Murov Konačni automat

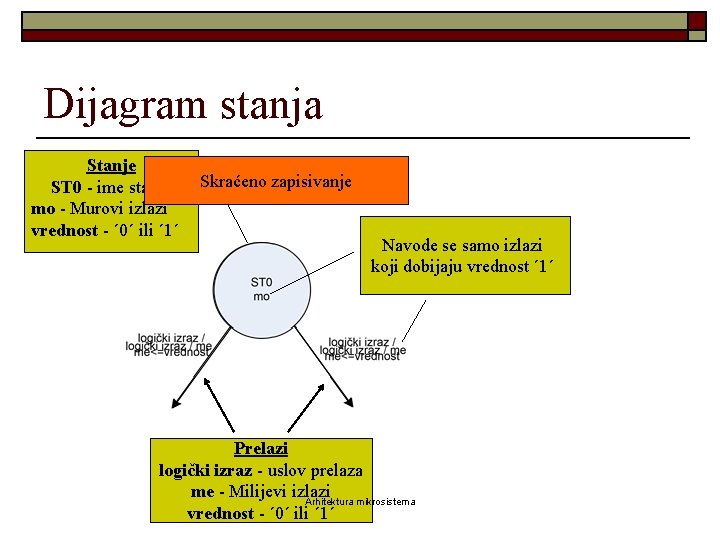

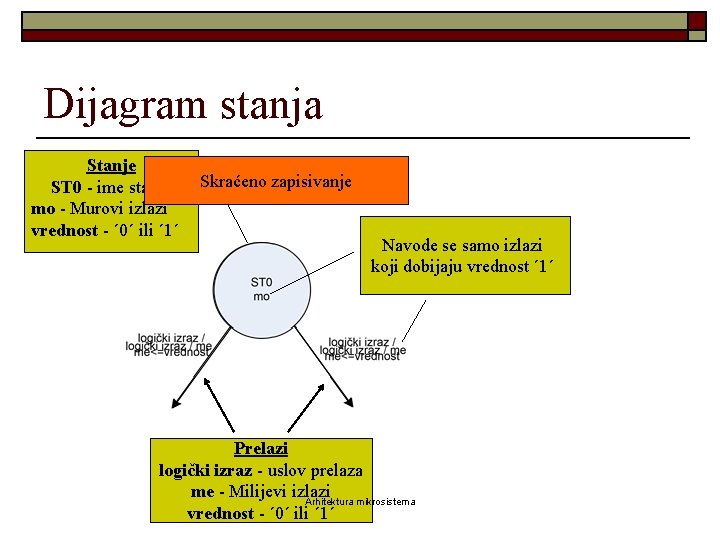

Dijagram stanja Stanje ST 0 - ime stanja mo - Murovi izlazi vrednost - ´ 0´ ili ´ 1´ Skraćeno zapisivanje Navode se samo izlazi koji dobijaju vrednost ´ 1´ Prelazi logički izraz - uslov prelaza me - Milijevi izlazi Arhitektura mikrosistema vrednost - ´ 0´ ili ´ 1´

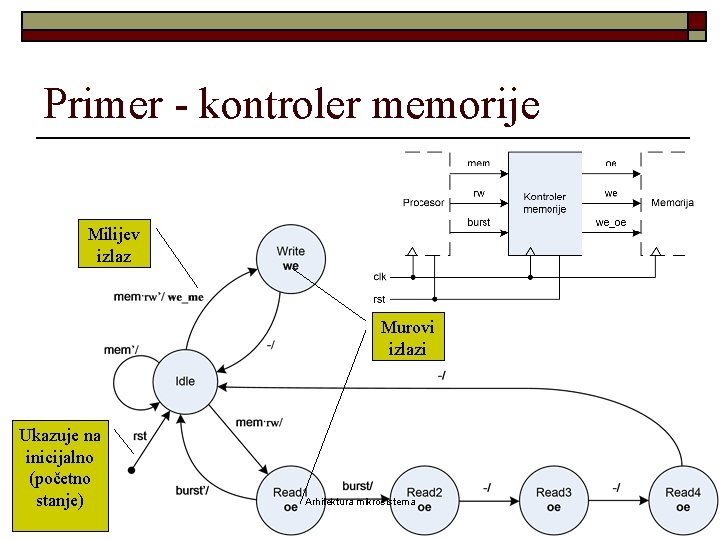

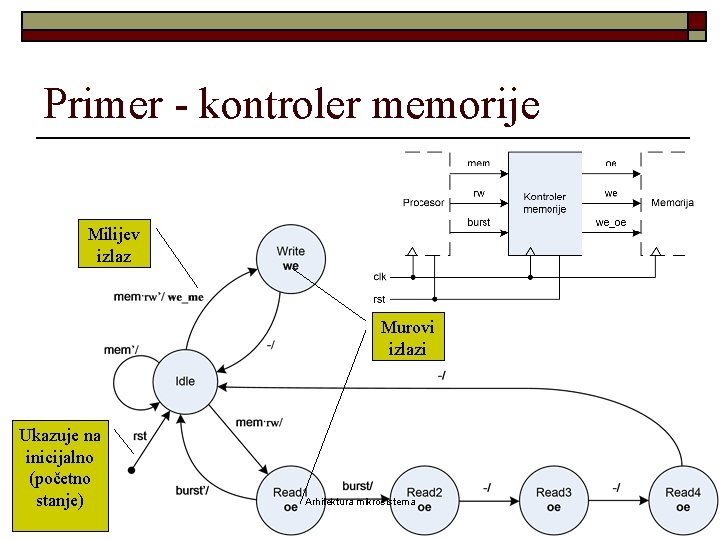

Primer - kontroler memorije Milijev izlaz Murovi izlazi Ukazuje na inicijalno (početno stanje) Arhitektura mikrosistema

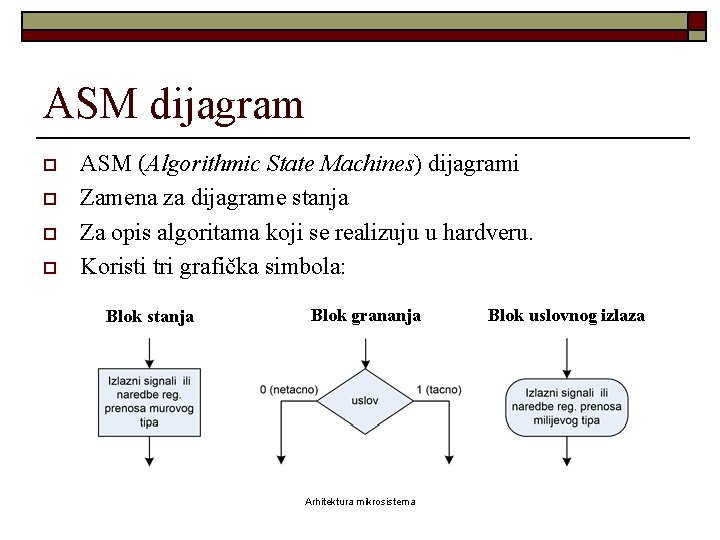

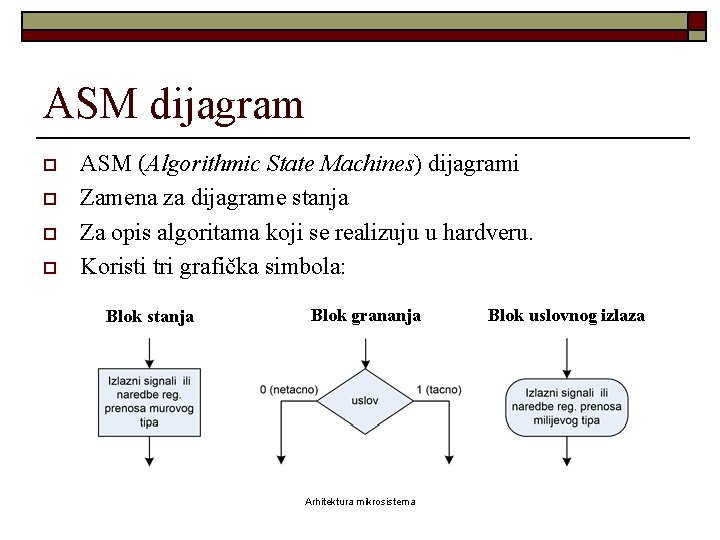

ASM dijagram o o ASM (Algorithmic State Machines) dijagrami Zamena za dijagrame stanja Za opis algoritama koji se realizuju u hardveru. Koristi tri grafička simbola: Blok stanja Blok grananja Arhitektura mikrosistema Blok uslovnog izlaza

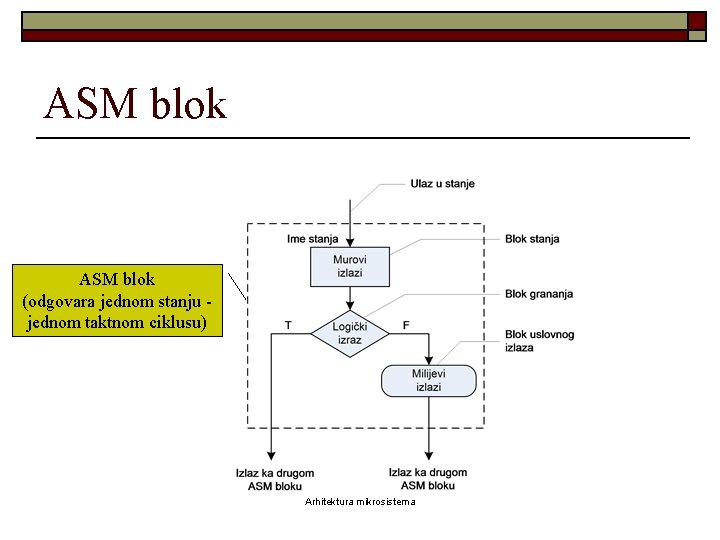

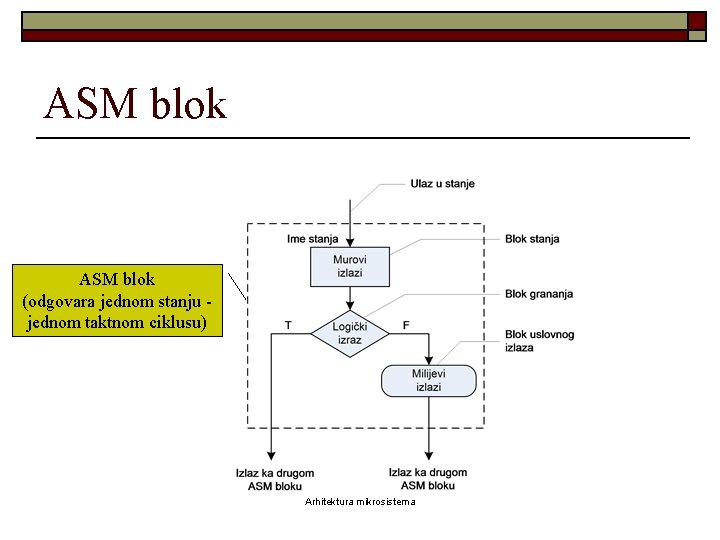

ASM blok (odgovara jednom stanju jednom taktnom ciklusu) Arhitektura mikrosistema

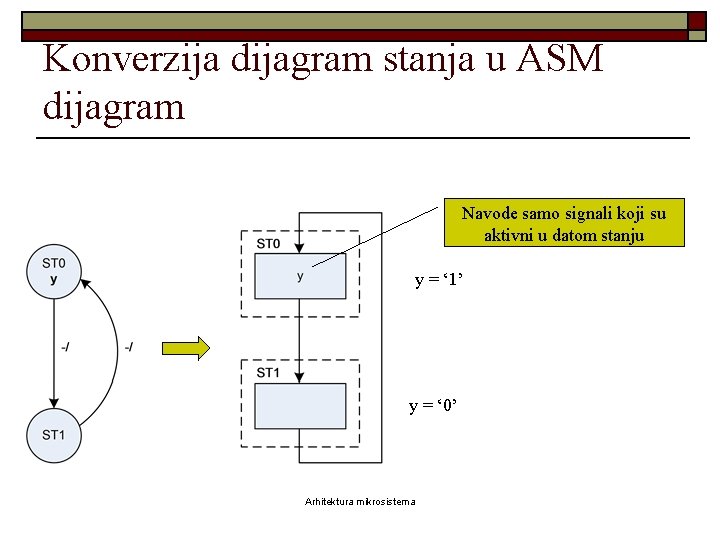

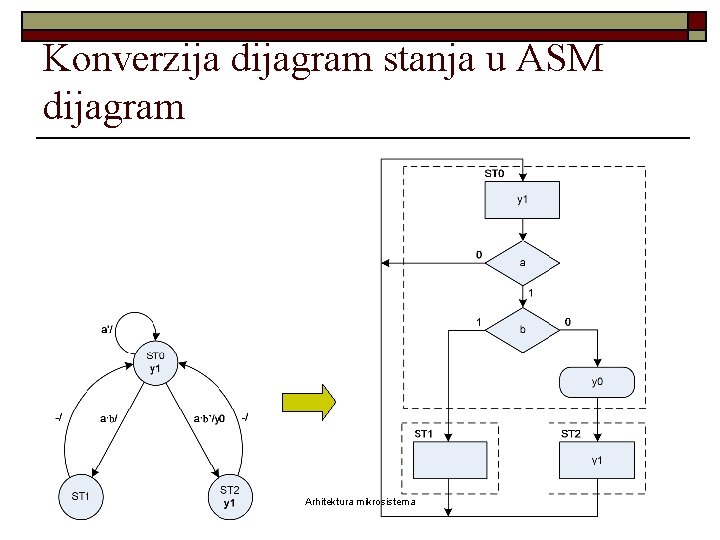

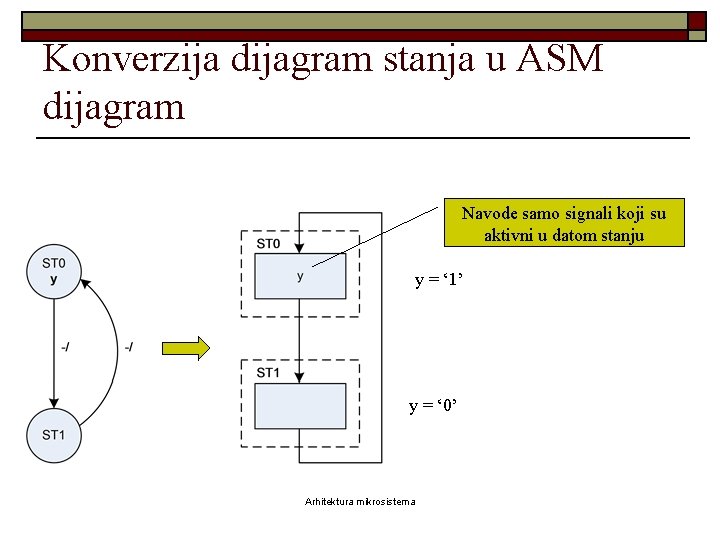

Konverzija dijagram stanja u ASM dijagram Navode samo signali koji su aktivni u datom stanju y = ‘ 1’ y = ‘ 0’ Arhitektura mikrosistema

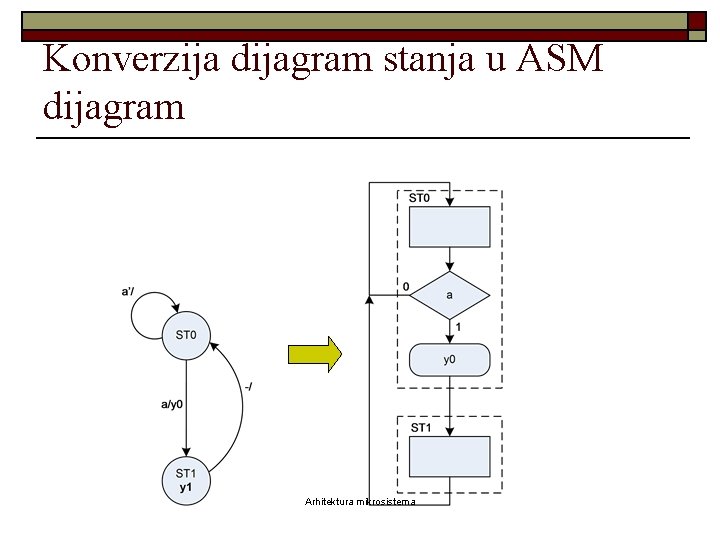

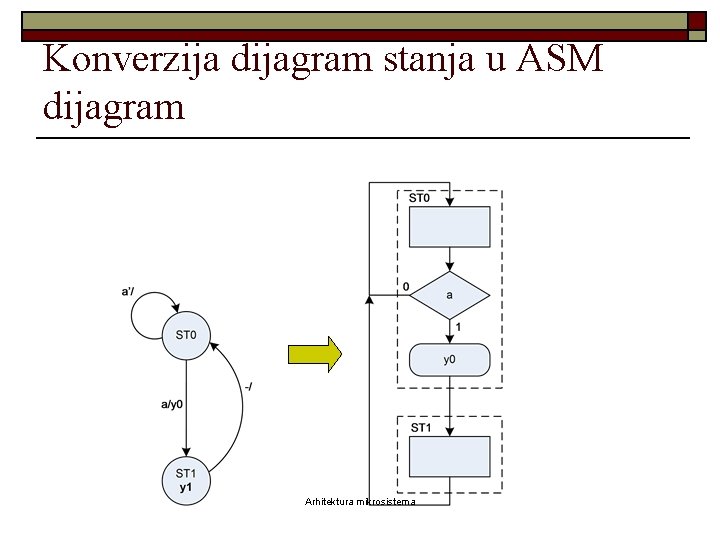

Konverzija dijagram stanja u ASM dijagram Arhitektura mikrosistema

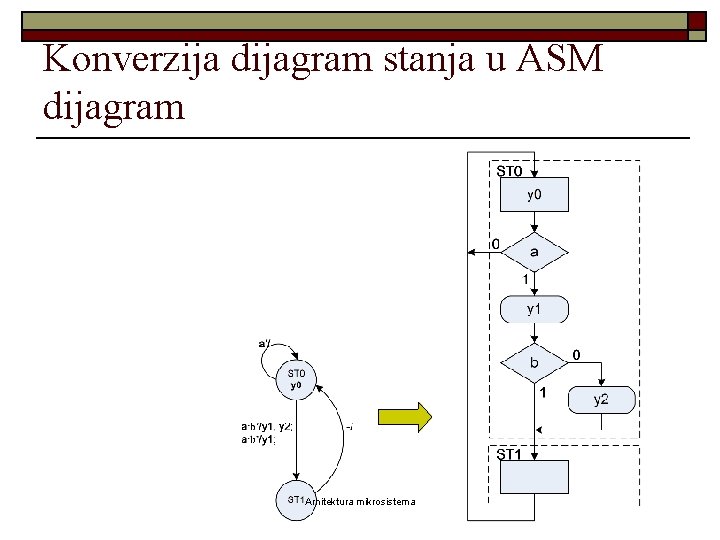

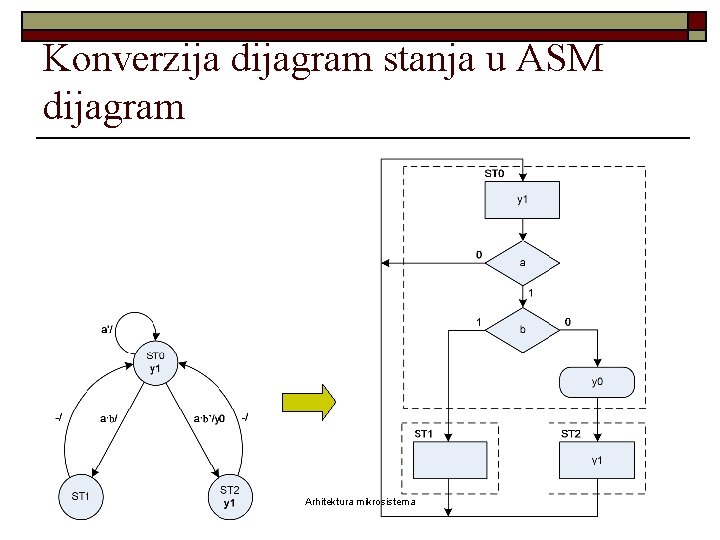

Konverzija dijagram stanja u ASM dijagram Arhitektura mikrosistema

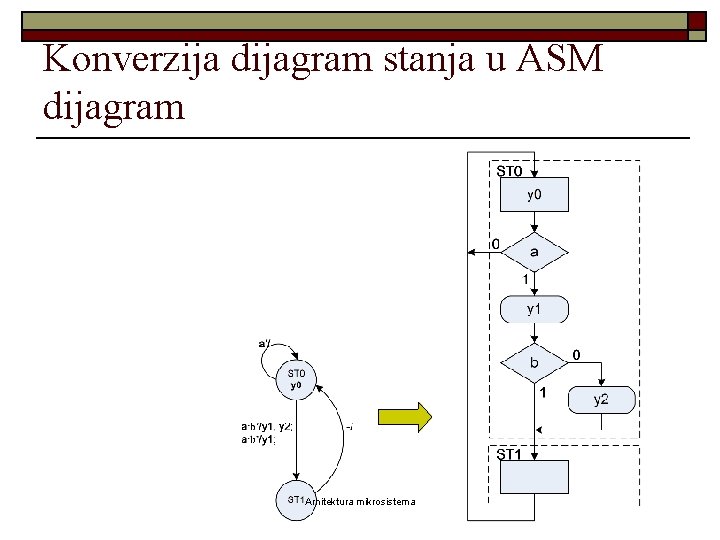

Konverzija dijagram stanja u ASM dijagram Arhitektura mikrosistema

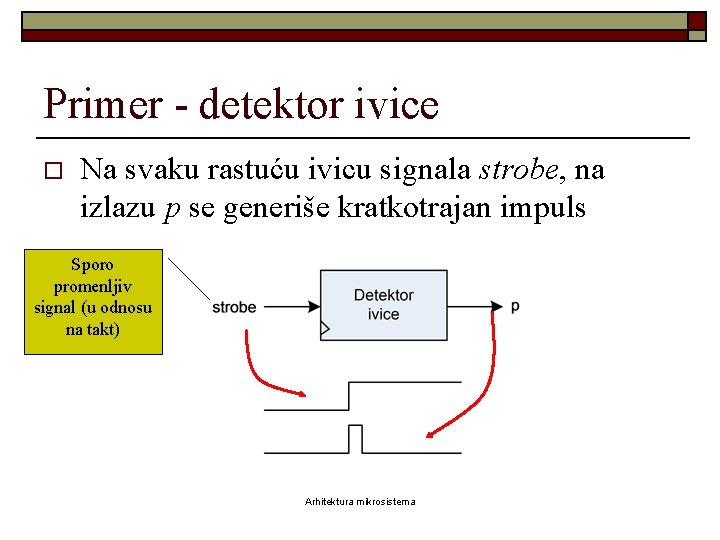

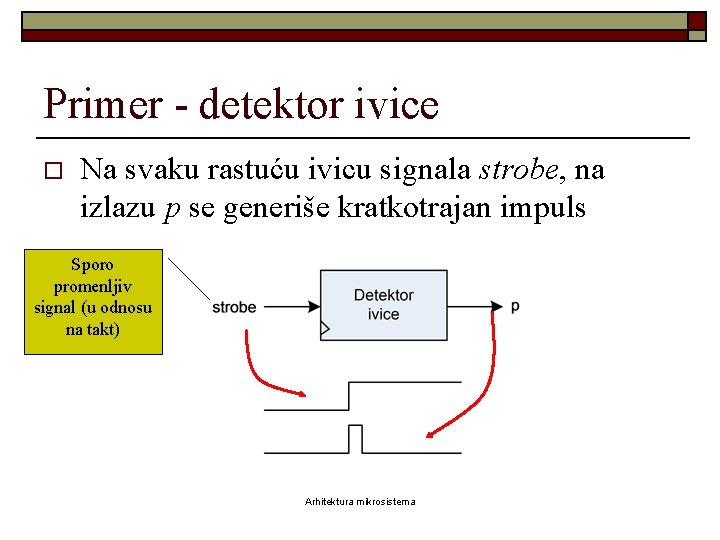

Primer - detektor ivice o Na svaku rastuću ivicu signala strobe, na izlazu p se generiše kratkotrajan impuls Sporo promenljiv signal (u odnosu na takt) Arhitektura mikrosistema

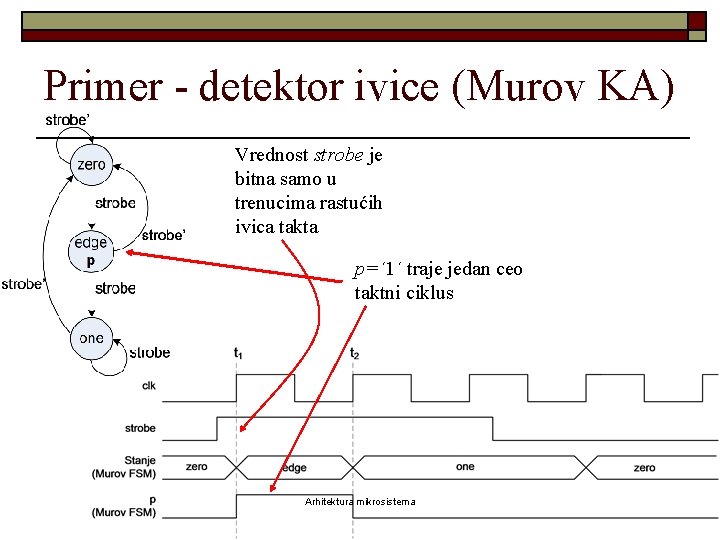

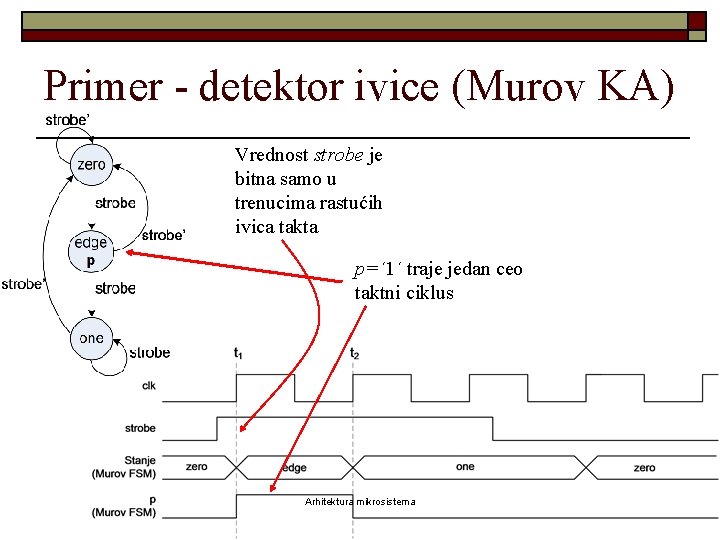

Primer - detektor ivice (Murov KA) Vrednost strobe je bitna samo u trenucima rastućih ivica takta p=´ 1´ traje jedan ceo taktni ciklus Arhitektura mikrosistema

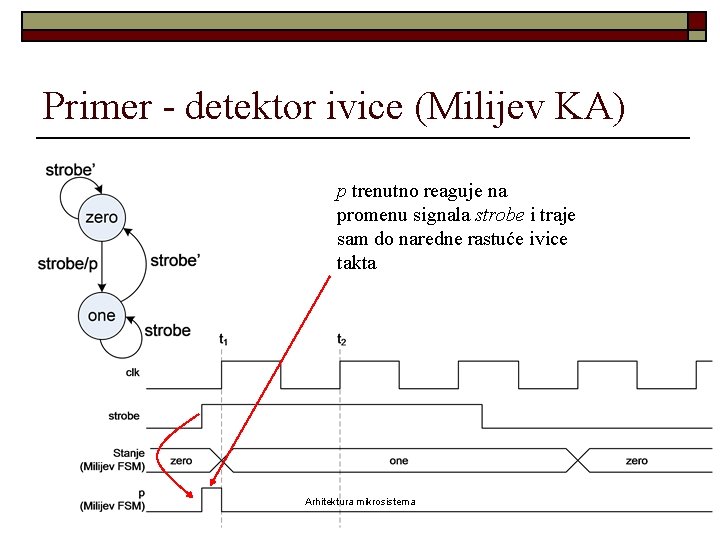

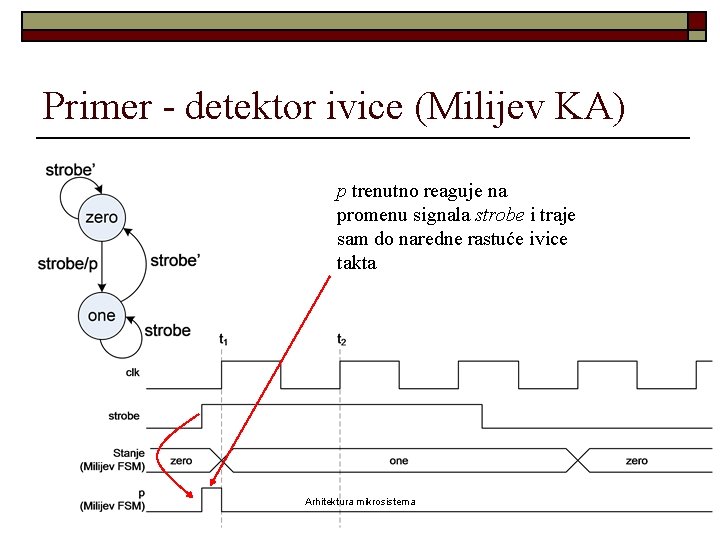

Primer - detektor ivice (Milijev KA) p trenutno reaguje na promenu signala strobe i traje sam do naredne rastuće ivice takta Arhitektura mikrosistema

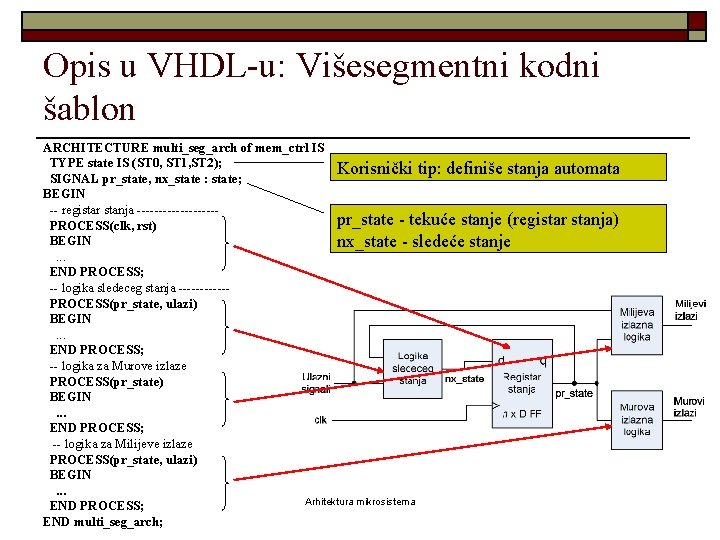

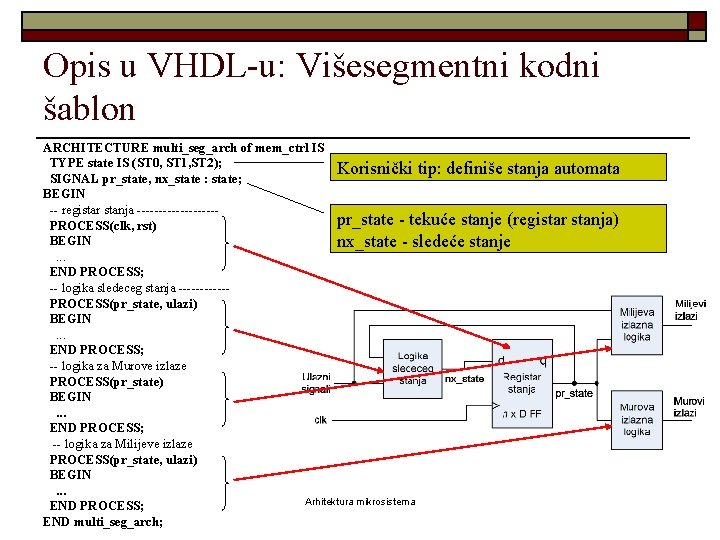

Opis u VHDL-u: Višesegmentni kodni šablon ARCHITECTURE multi_seg_arch of mem_ctrl IS TYPE state IS (ST 0, ST 1, ST 2); Korisnički tip: definiše stanja automata SIGNAL pr_state, nx_state : state; BEGIN -- registar stanja ---------pr_state - tekuće stanje (registar stanja) PROCESS(clk, rst) BEGIN nx_state - sledeće stanje. . . END PROCESS; -- logika sledeceg stanja ------PROCESS(pr_state, ulazi) BEGIN. . . END PROCESS; -- logika za Murove izlaze PROCESS(pr_state) BEGIN. . . END PROCESS; -- logika za Milijeve izlaze PROCESS(pr_state, ulazi) BEGIN. . . Arhitektura mikrosistema END PROCESS; END multi_seg_arch;

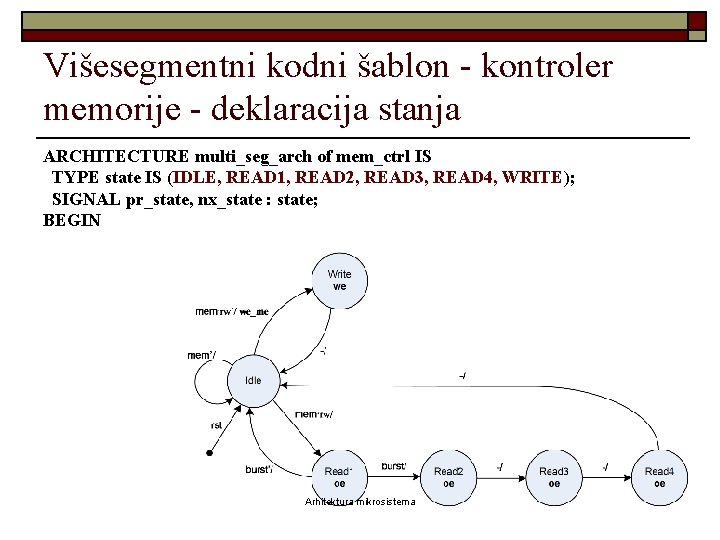

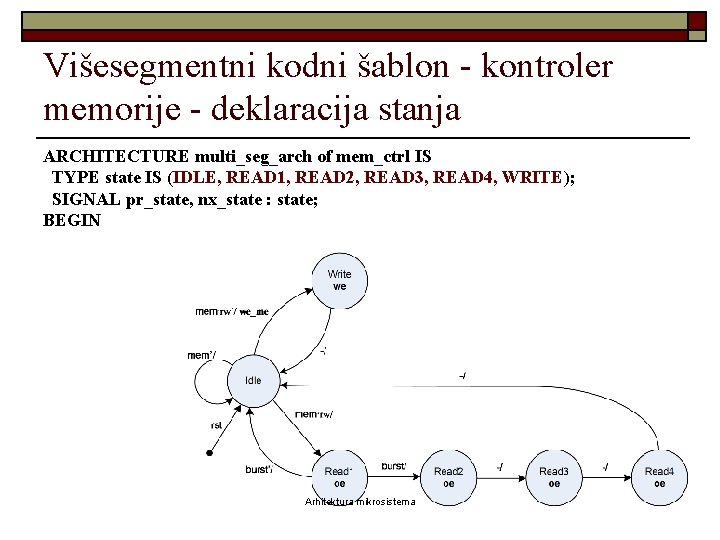

Višesegmentni kodni šablon - kontroler memorije - deklaracija stanja ARCHITECTURE multi_seg_arch of mem_ctrl IS TYPE state IS (IDLE, READ 1, READ 2, READ 3, READ 4, WRITE); SIGNAL pr_state, nx_state : state; BEGIN Arhitektura mikrosistema

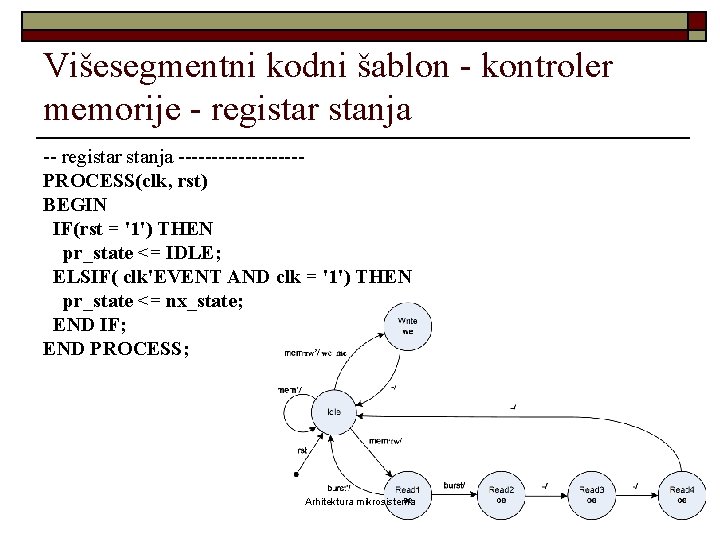

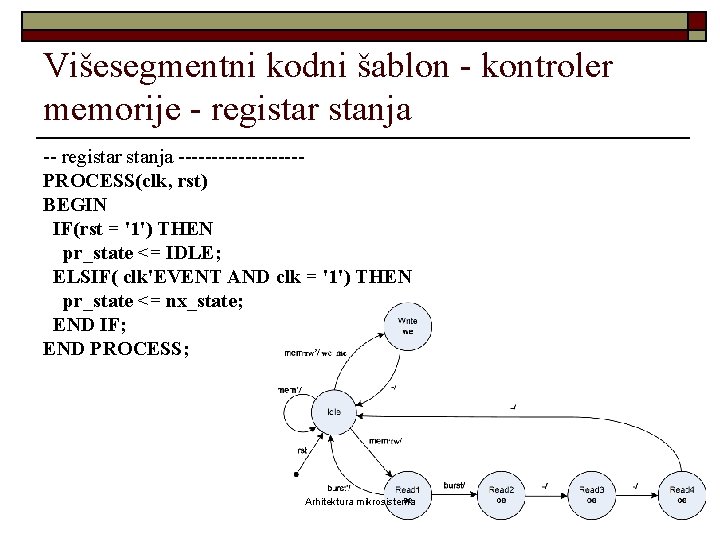

Višesegmentni kodni šablon - kontroler memorije - registar stanja ----------PROCESS(clk, rst) BEGIN IF(rst = '1') THEN pr_state <= IDLE; ELSIF( clk'EVENT AND clk = '1') THEN pr_state <= nx_state; END IF; END PROCESS; Arhitektura mikrosistema

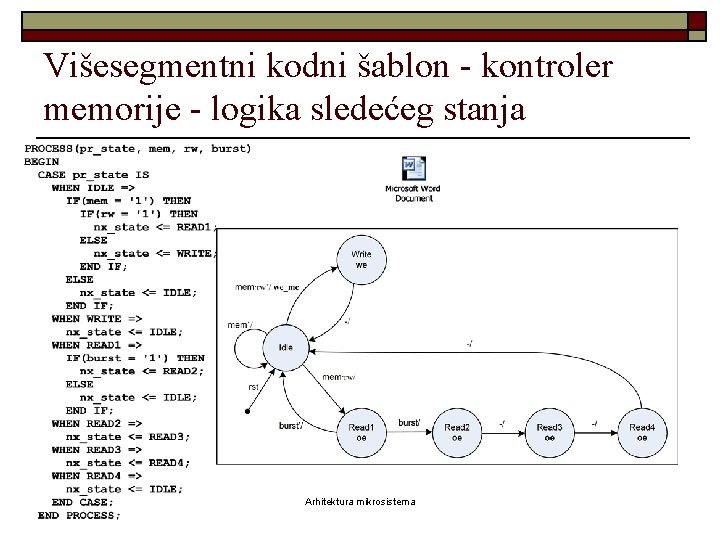

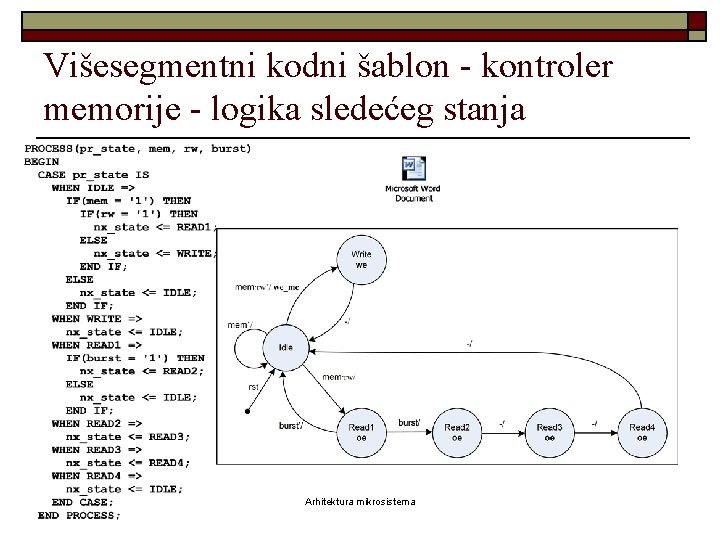

Višesegmentni kodni šablon - kontroler memorije - logika sledećeg stanja Arhitektura mikrosistema

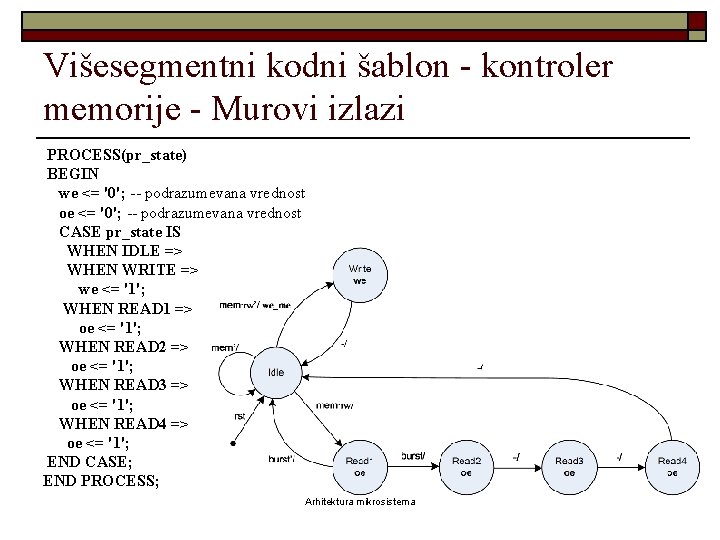

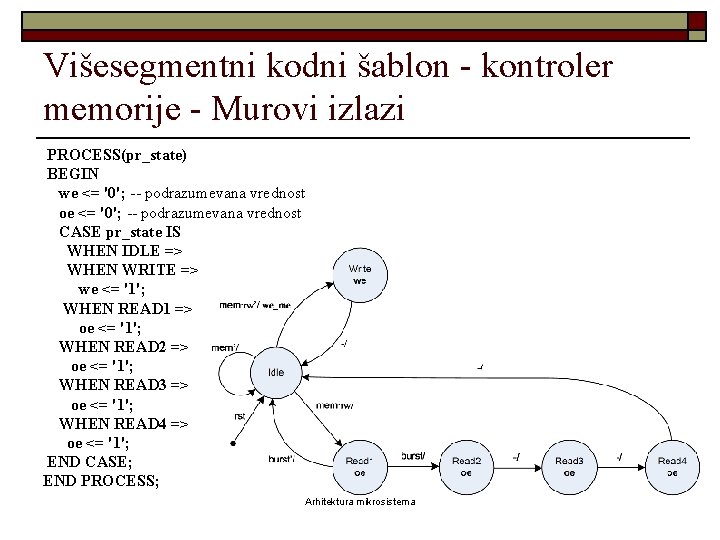

Višesegmentni kodni šablon - kontroler memorije - Murovi izlazi PROCESS(pr_state) BEGIN we <= '0'; -- podrazumevana vrednost oe <= '0'; -- podrazumevana vrednost CASE pr_state IS WHEN IDLE => WHEN WRITE => we <= '1'; WHEN READ 1 => oe <= '1'; WHEN READ 2 => oe <= '1'; WHEN READ 3 => oe <= '1'; WHEN READ 4 => oe <= '1'; END CASE; END PROCESS; Arhitektura mikrosistema

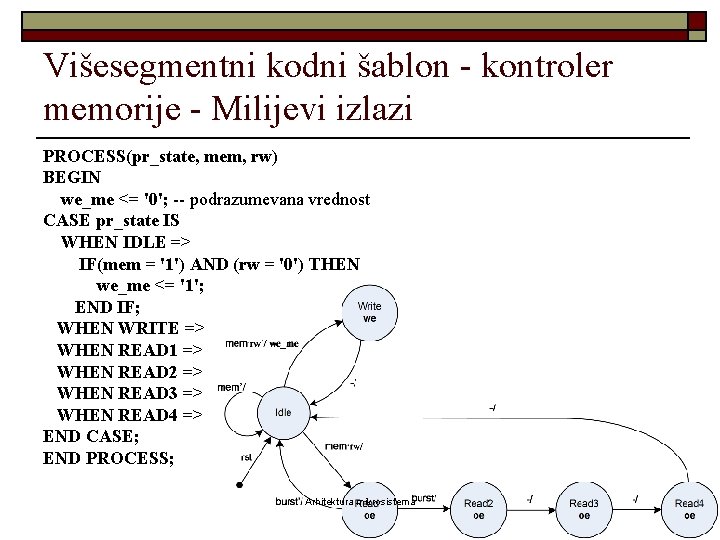

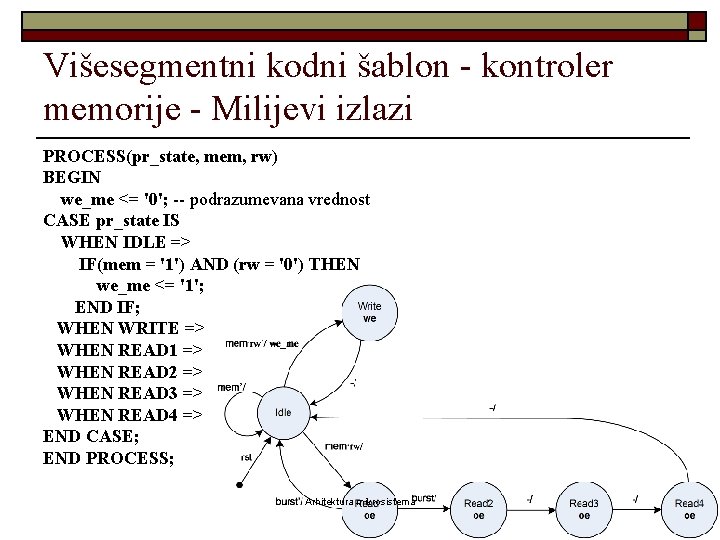

Višesegmentni kodni šablon - kontroler memorije - Milijevi izlazi PROCESS(pr_state, mem, rw) BEGIN we_me <= '0'; -- podrazumevana vrednost CASE pr_state IS WHEN IDLE => IF(mem = '1') AND (rw = '0') THEN we_me <= '1'; END IF; WHEN WRITE => WHEN READ 1 => WHEN READ 2 => WHEN READ 3 => WHEN READ 4 => END CASE; END PROCESS; Arhitektura mikrosistema

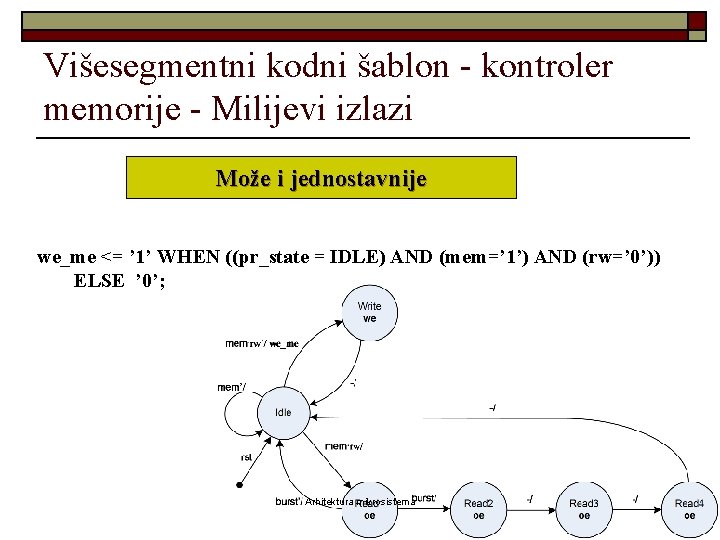

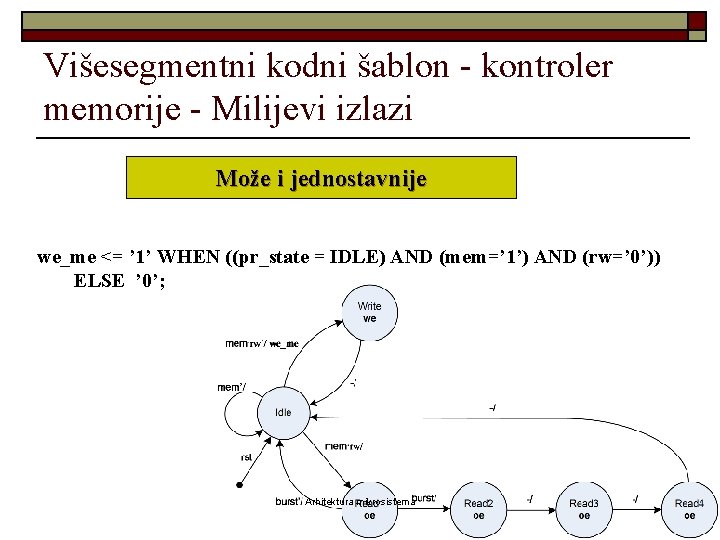

Višesegmentni kodni šablon - kontroler memorije - Milijevi izlazi Može i jednostavnije we_me <= ’ 1’ WHEN ((pr_state = IDLE) AND (mem=’ 1’) AND (rw=’ 0’)) ELSE ’ 0’; Arhitektura mikrosistema

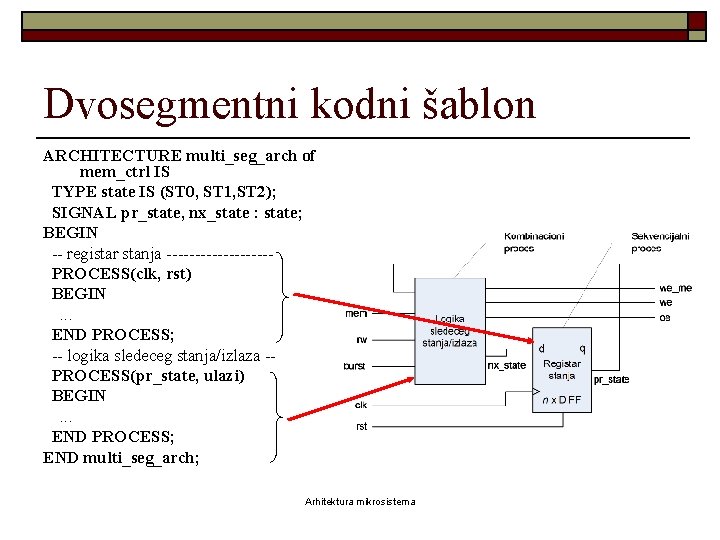

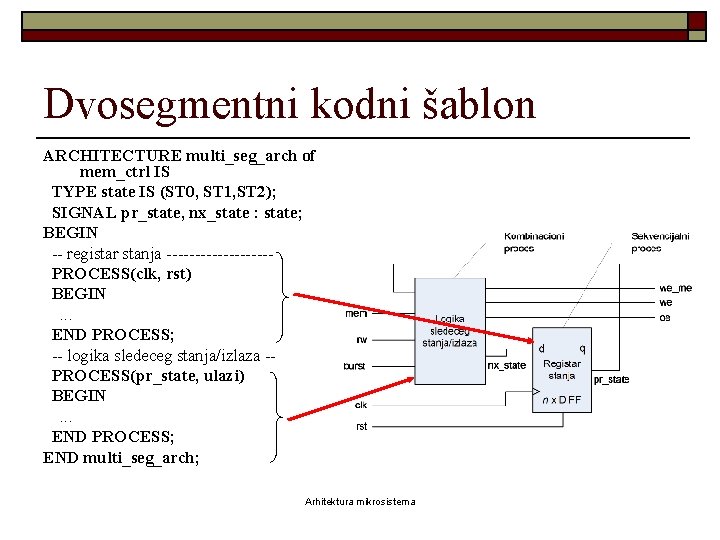

Dvosegmentni kodni šablon ARCHITECTURE multi_seg_arch of mem_ctrl IS TYPE state IS (ST 0, ST 1, ST 2); SIGNAL pr_state, nx_state : state; BEGIN -- registar stanja ---------PROCESS(clk, rst) BEGIN. . . END PROCESS; -- logika sledeceg stanja/izlaza -PROCESS(pr_state, ulazi) BEGIN. . . END PROCESS; END multi_seg_arch; Arhitektura mikrosistema

Dvosegmentni kodni šablon Kontroler memorije Arhitektura mikrosistema

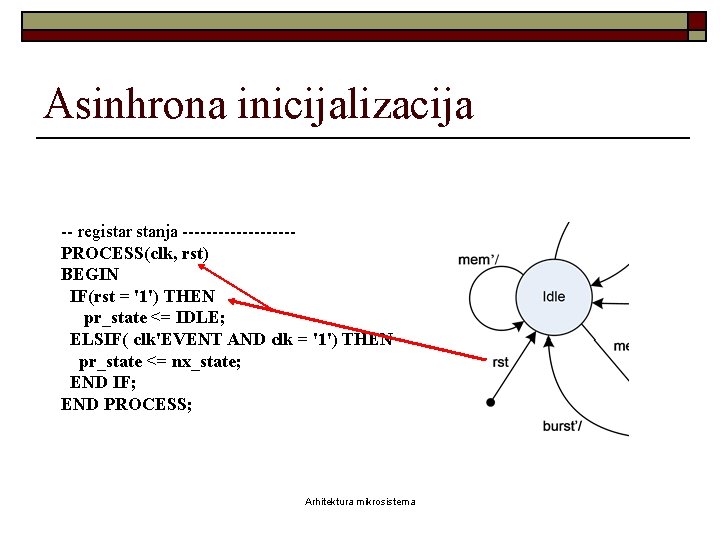

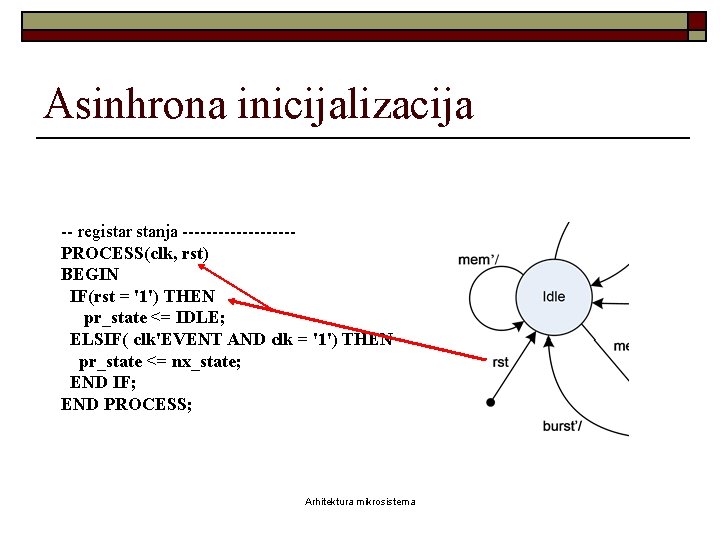

Asinhrona inicijalizacija -- registar stanja ---------PROCESS(clk, rst) BEGIN IF(rst = '1') THEN pr_state <= IDLE; ELSIF( clk'EVENT AND clk = '1') THEN pr_state <= nx_state; END IF; END PROCESS; Arhitektura mikrosistema

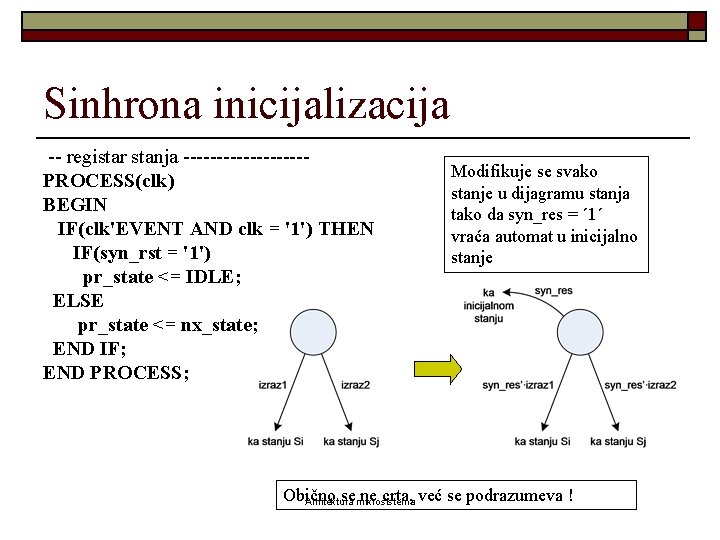

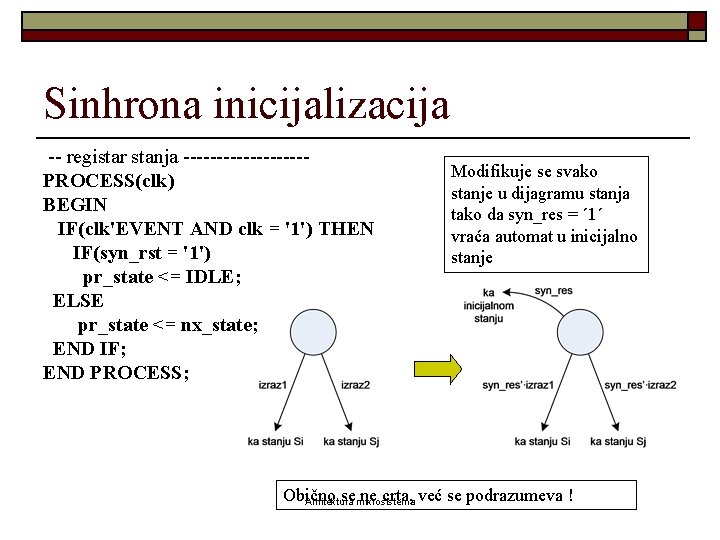

Sinhrona inicijalizacija -- registar stanja ---------PROCESS(clk) BEGIN IF(clk'EVENT AND clk = '1') THEN IF(syn_rst = '1') pr_state <= IDLE; ELSE pr_state <= nx_state; END IF; END PROCESS; Modifikuje se svako stanje u dijagramu stanja tako da syn_res = ´ 1´ vraća automat u inicijalno stanje Obično se mikrosistema ne crta, već se podrazumeva ! Arhitektura

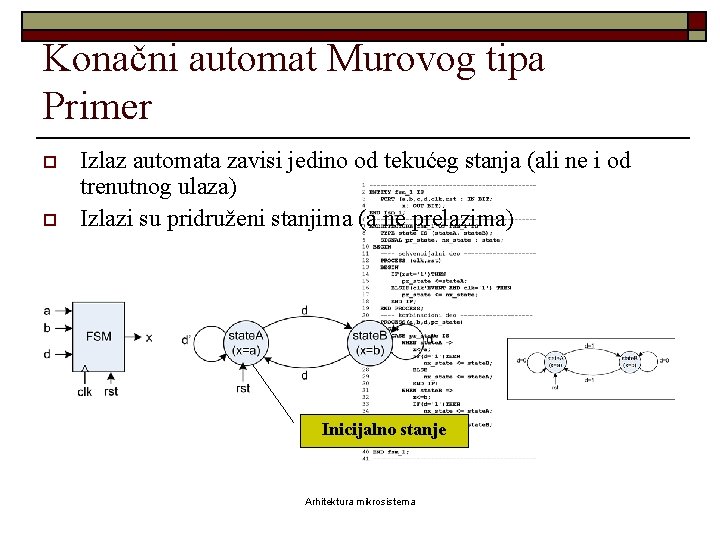

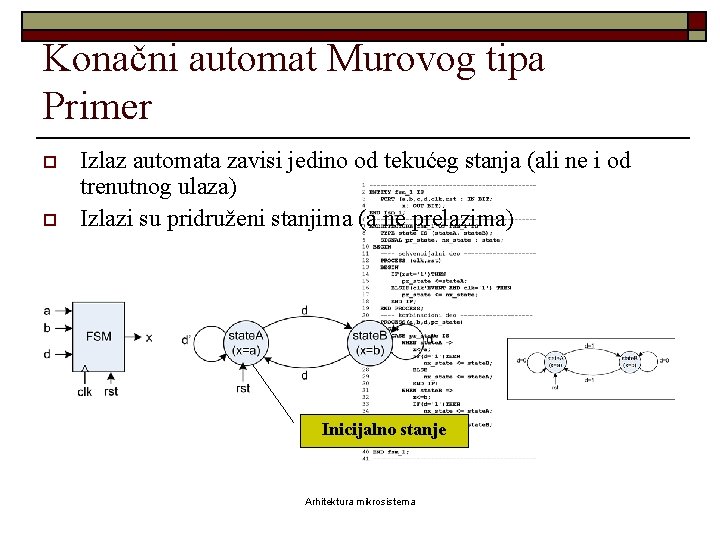

Konačni automat Murovog tipa Primer o o Izlaz automata zavisi jedino od tekućeg stanja (ali ne i od trenutnog ulaza) Izlazi su pridruženi stanjima (a ne prelazima) Inicijalno stanje Arhitektura mikrosistema

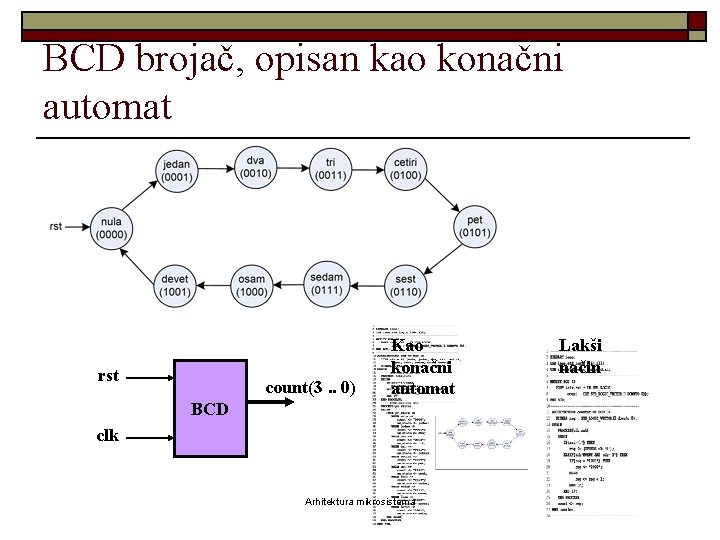

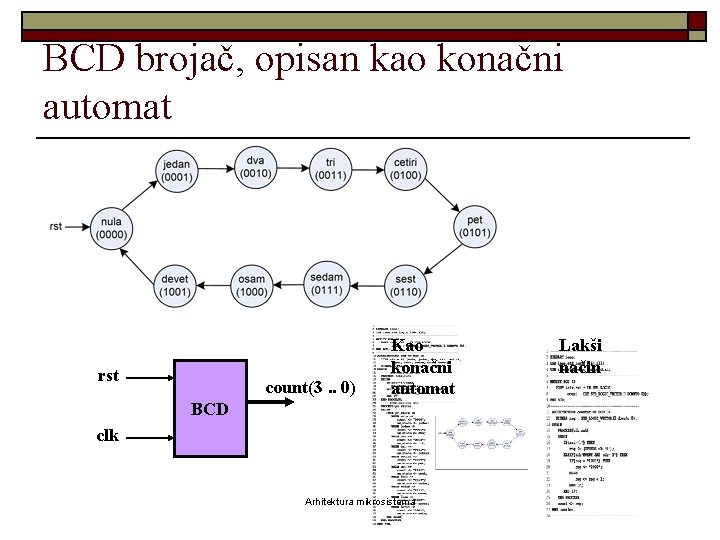

BCD brojač, opisan kao konačni automat rst count(3. . 0) Kao konačni automat BCD clk Arhitektura mikrosistema Lakši način

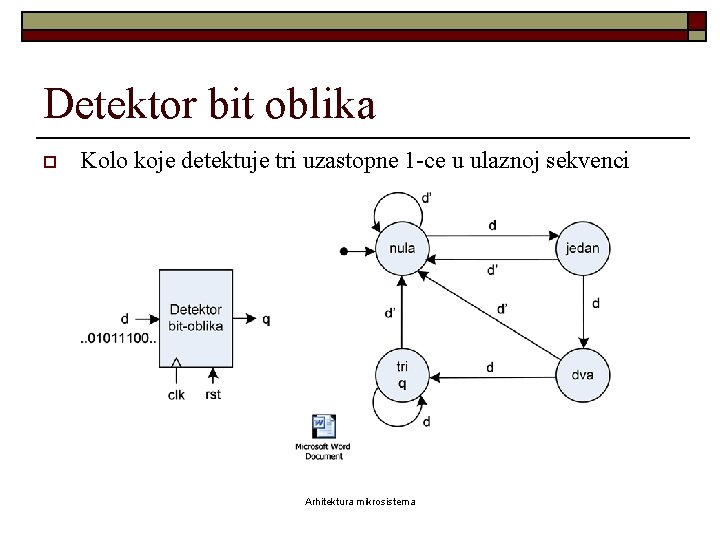

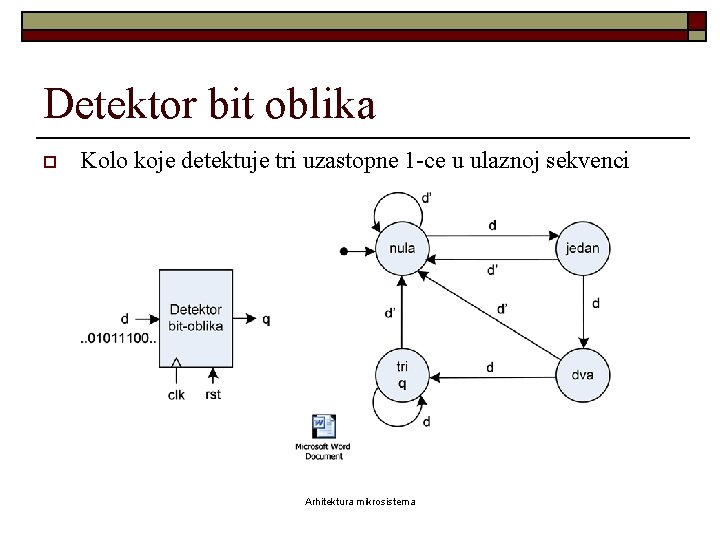

Detektor bit oblika o Kolo koje detektuje tri uzastopne 1 -ce u ulaznoj sekvenci Arhitektura mikrosistema

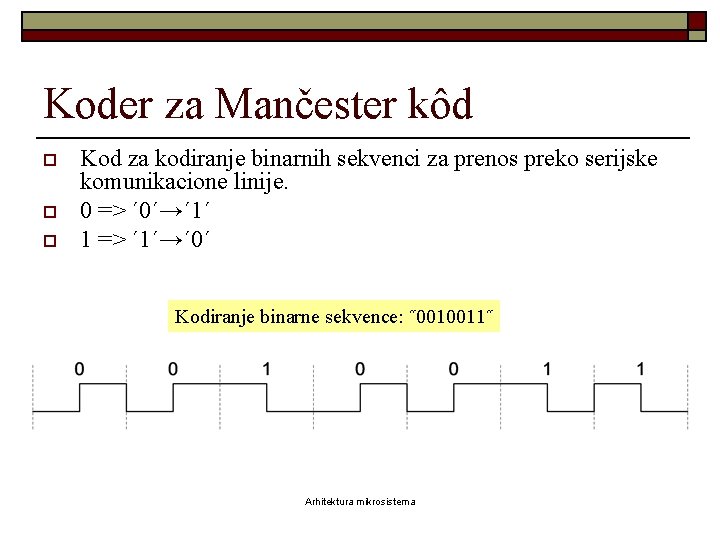

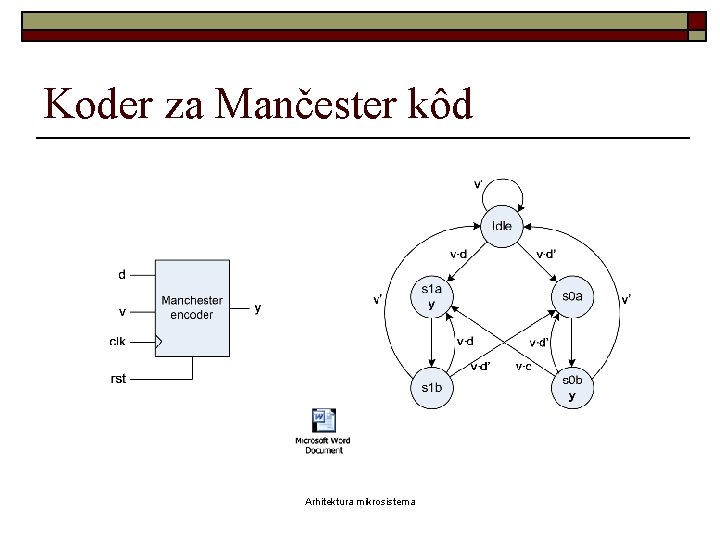

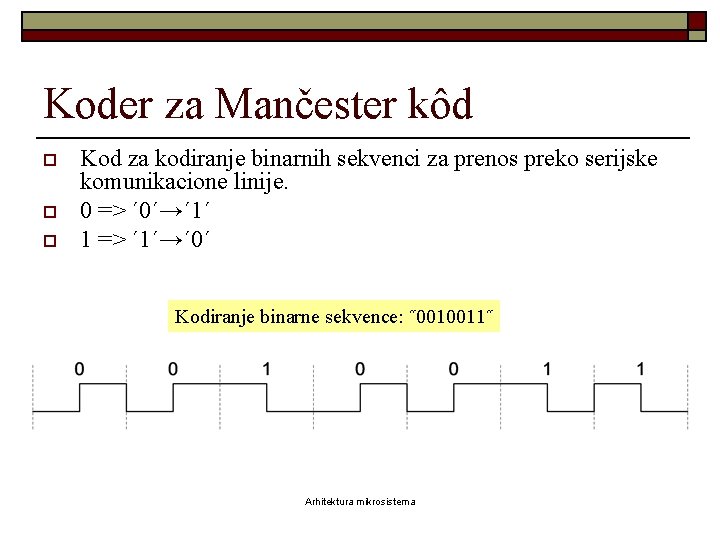

Koder za Mančester kôd o o o Kod za kodiranje binarnih sekvenci za prenos preko serijske komunikacione linije. 0 => ´ 0´→´ 1´ 1 => ´ 1´→´ 0´ Kodiranje binarne sekvence: ˝ 0010011˝ Arhitektura mikrosistema

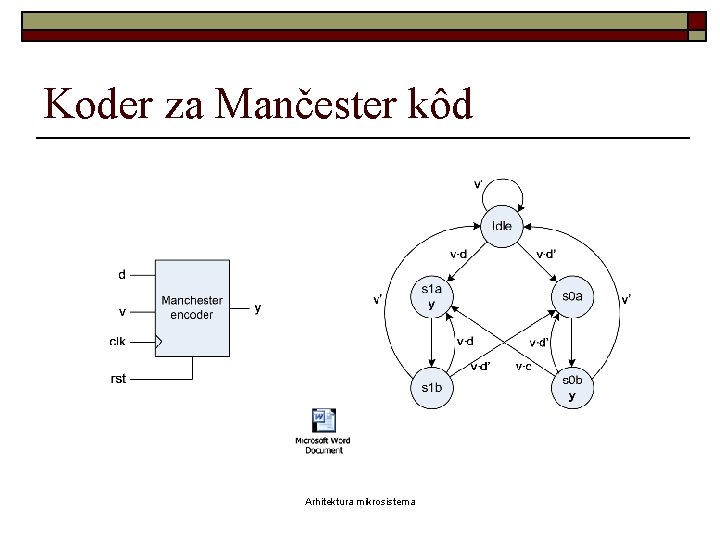

Koder za Mančester kôd Arhitektura mikrosistema

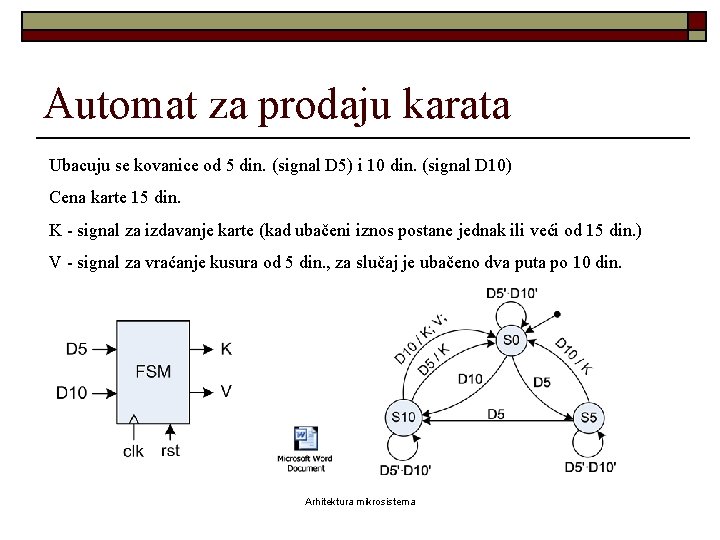

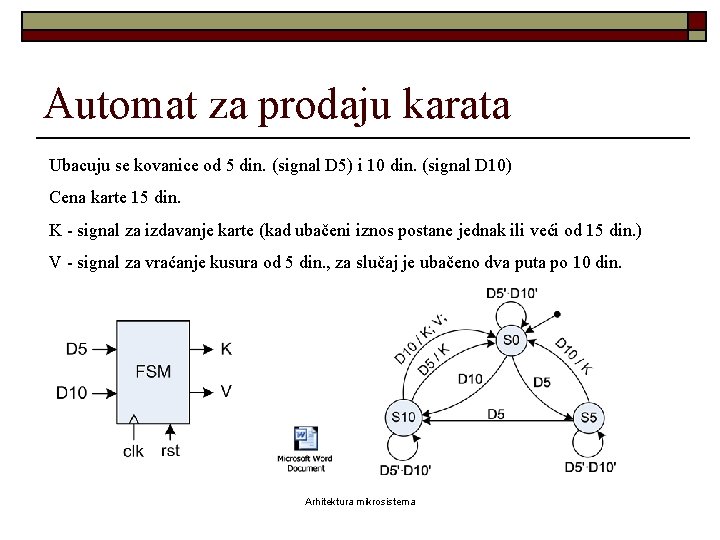

Automat za prodaju karata Ubacuju se kovanice od 5 din. (signal D 5) i 10 din. (signal D 10) Cena karte 15 din. K - signal za izdavanje karte (kad ubačeni iznos postane jednak ili veći od 15 din. ) V - signal za vraćanje kusura od 5 din. , za slučaj je ubačeno dva puta po 10 din. Arhitektura mikrosistema