History of Embedded Systems Discussion 0 1 Bell

History of Embedded Systems Discussion 0. 1

Bell Labs Museum The First Point-Contact Transistor 1947

Bell Labs The First Junction Transistor 1951 M 1752 Outside the Lab model

Texas Instrument’s First IC -- 1958 Jack Kilby Robert Noyce Fairchild Intel

Embedded System A single-purpose, programmable, digital system

1961 – Unimate Robot at GM

1965: PDP-8 first mass-produced Mini

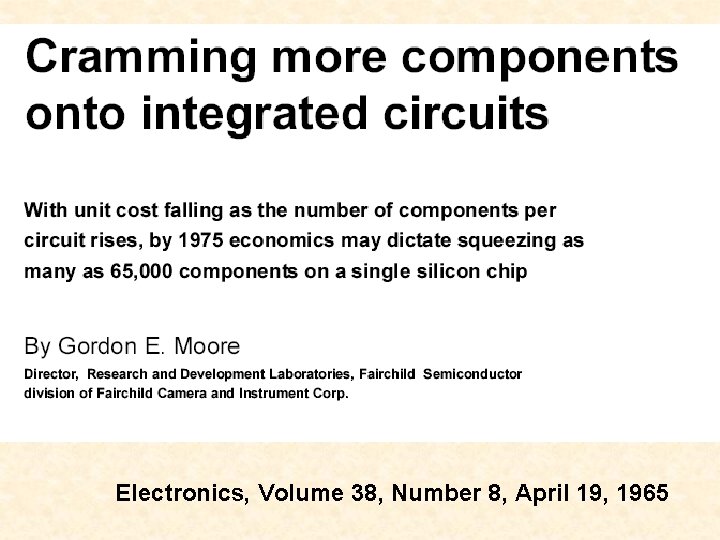

Electronics, Volume 38, Number 8, April 19, 1965

Moore’s law • Wow – This growth rate is hard to imagine, most people underestimate – How many ancestors do you have from 20 generations ago • i. e. , roughly how many people alive in the 1500’s did it take to make you? • 220 = more than 1 million people

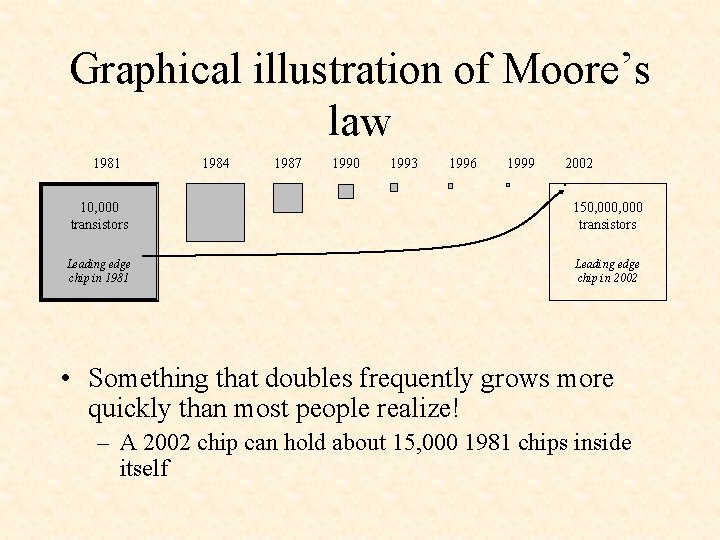

Graphical illustration of Moore’s law 1981 1984 1987 1990 1993 1996 1999 2002 10, 000 transistors 150, 000 transistors Leading edge chip in 1981 Leading edge chip in 2002 • Something that doubles frequently grows more quickly than most people realize! – A 2002 chip can hold about 15, 000 1981 chips inside itself

1968 – Apollo Guidance Computer

Intel 4004 source: Computer Museum

January 1975 cover of Popular Electronics http: //www. blinkenlights. com/pc. shtml

1978 – Industrial Holographics

Time's Man of the Year (1982)

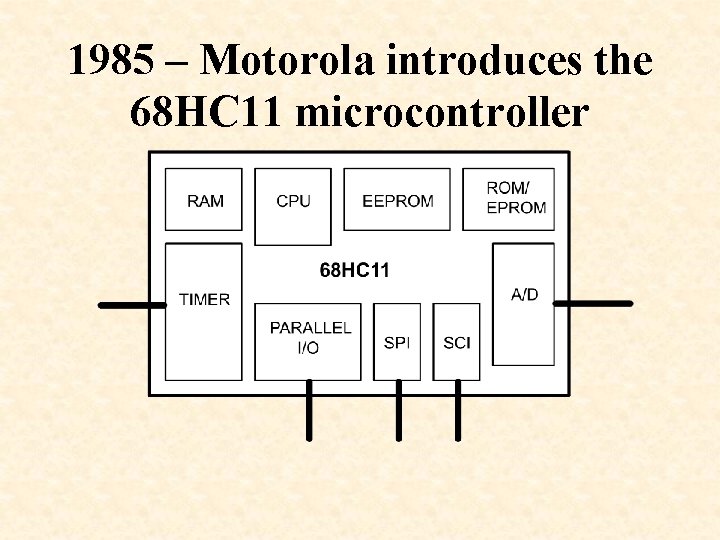

1985 – Motorola introduces the 68 HC 11 microcontroller

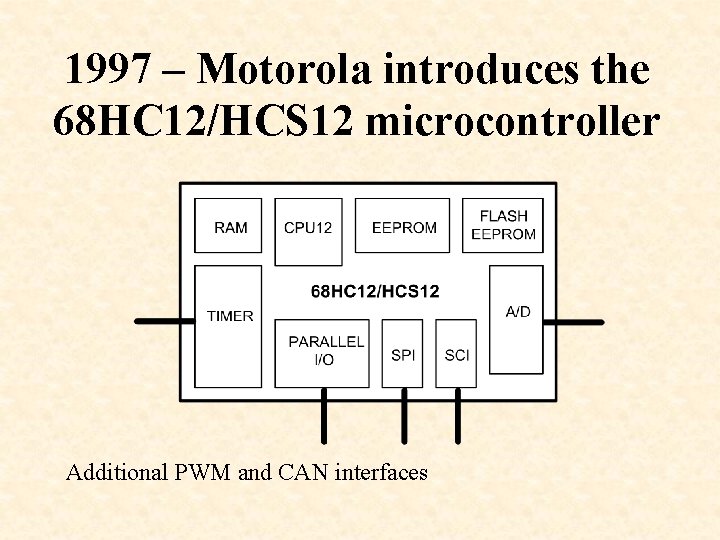

1997 – Motorola introduces the 68 HC 12/HCS 12 microcontroller Additional PWM and CAN interfaces

Develops WHYP – a subroutine-threaded Forth for the 68 HC 12

Chuck Moore, the inventor of Forth, reading Haskell’s WHYP book

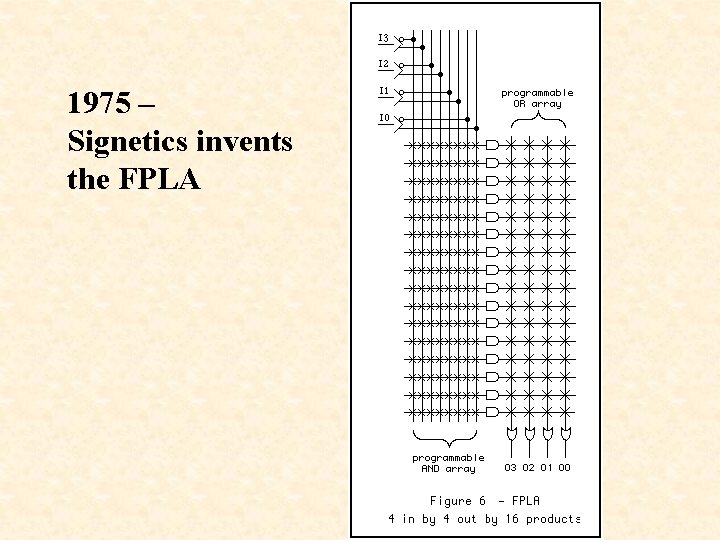

1975 – Signetics invents the FPLA

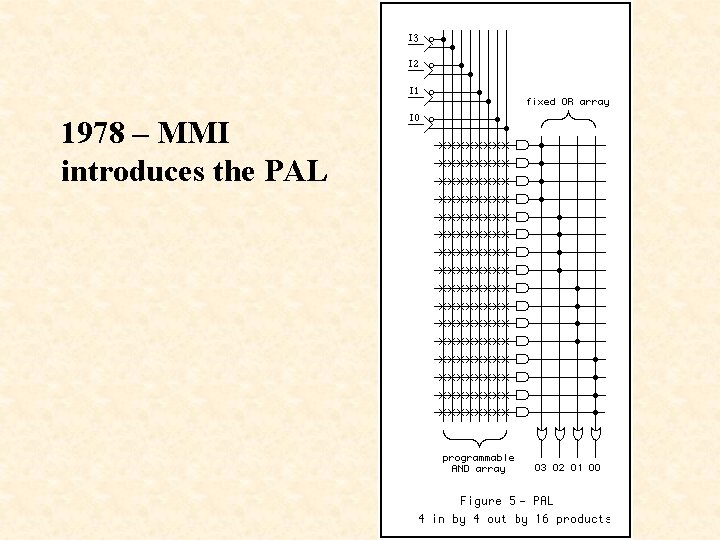

1978 – MMI introduces the PAL

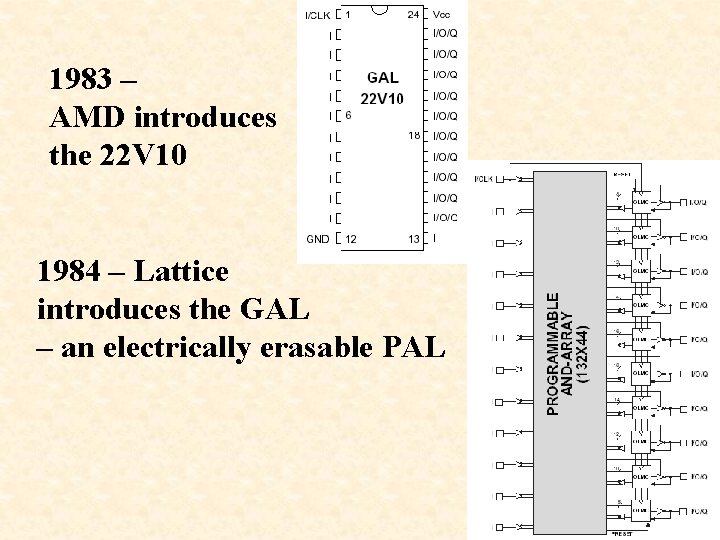

1983 – AMD introduces the 22 V 10 1984 – Lattice introduces the GAL – an electrically erasable PAL

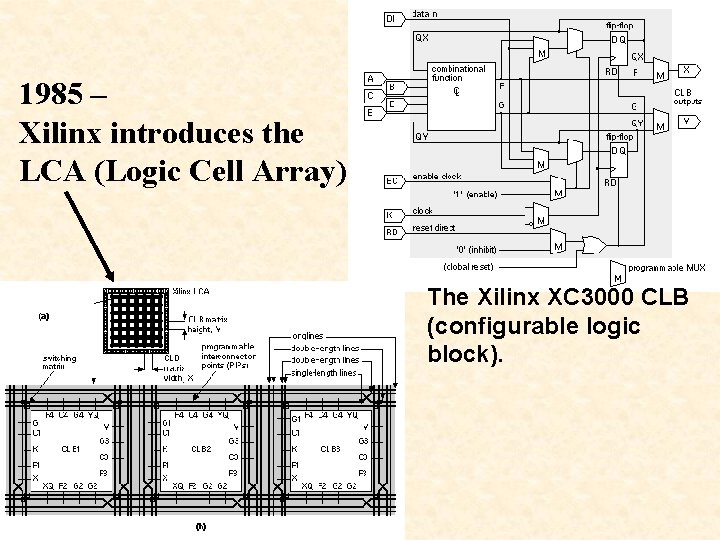

1985 – Xilinx introduces the LCA (Logic Cell Array) The Xilinx XC 3000 CLB (configurable logic block).

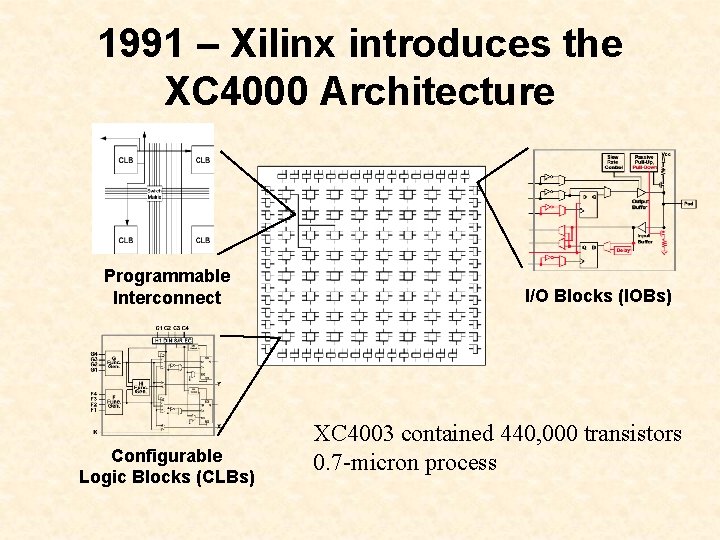

1991 – Xilinx introduces the XC 4000 Architecture Programmable Interconnect Configurable Logic Blocks (CLBs) I/O Blocks (IOBs) XC 4003 contained 440, 000 transistors 0. 7 -micron process

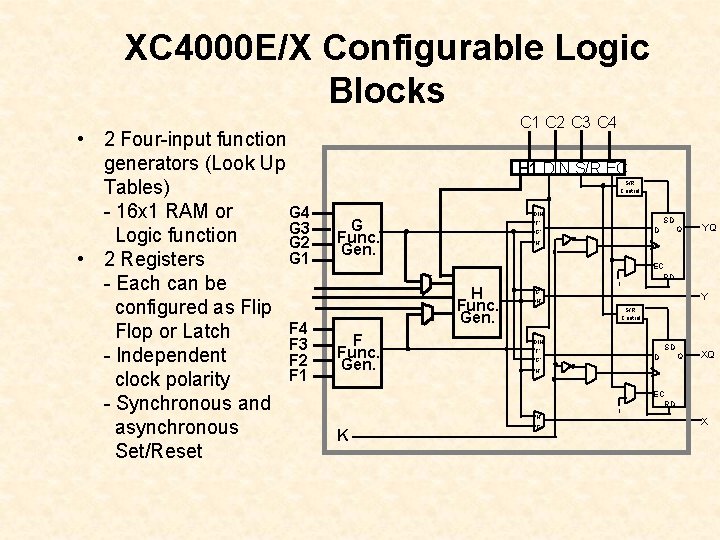

XC 4000 E/X Configurable Logic Blocks • 2 Four-input function generators (Look Up Tables) G 4 - 16 x 1 RAM or G 3 Logic function G 2 G 1 • 2 Registers - Each can be configured as Flip F 4 Flop or Latch F 3 - Independent F 2 F 1 clock polarity - Synchronous and asynchronous Set/Reset C 1 C 2 C 3 C 4 H 1 DIN S/R EC S/R Control DIN G Func. Gen. YQ 1 EC RD G' H' Y S/R Control DIN SD F' G' D Q XQ H' H' K Q D H' H Func. Gen. F Func. Gen. SD F' G' F' 1 EC RD X

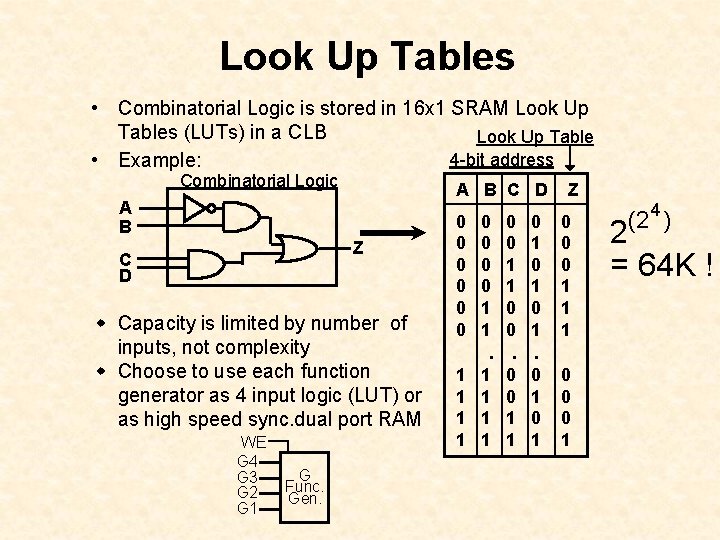

Look Up Tables • Combinatorial Logic is stored in 16 x 1 SRAM Look Up Tables (LUTs) in a CLB Look Up Table 4 -bit address • Example: Combinatorial Logic A B C D A B Z C D w Capacity is limited by number of inputs, not complexity w Choose to use each function generator as 4 input logic (LUT) or as high speed sync. dual port RAM WE G 4 G 3 G 2 G 1 G Func. Gen. 0 0 0 0 0 1 1 0 0 0 1 0 1 Z 0 0 0 1 1 1 . . . 1 1 1 1 0 0 1 1 0 1 0 0 0 1 4 2(2 ) = 64 K !

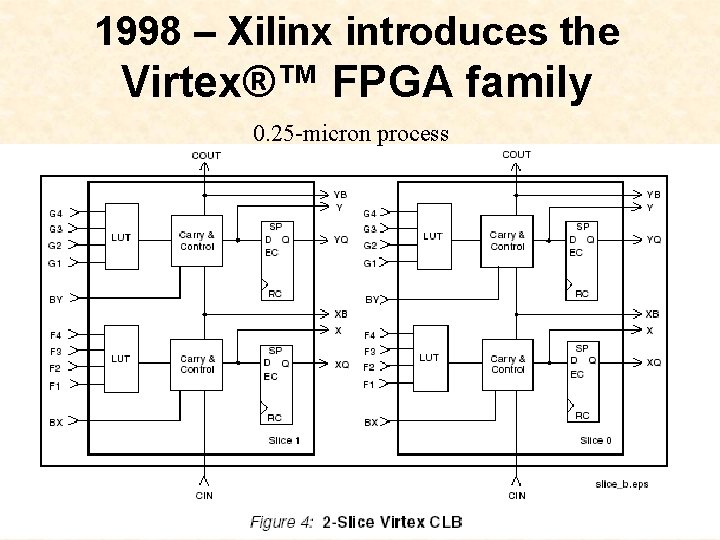

1998 – Xilinx introduces the Virtex®™ FPGA family 0. 25 -micron process

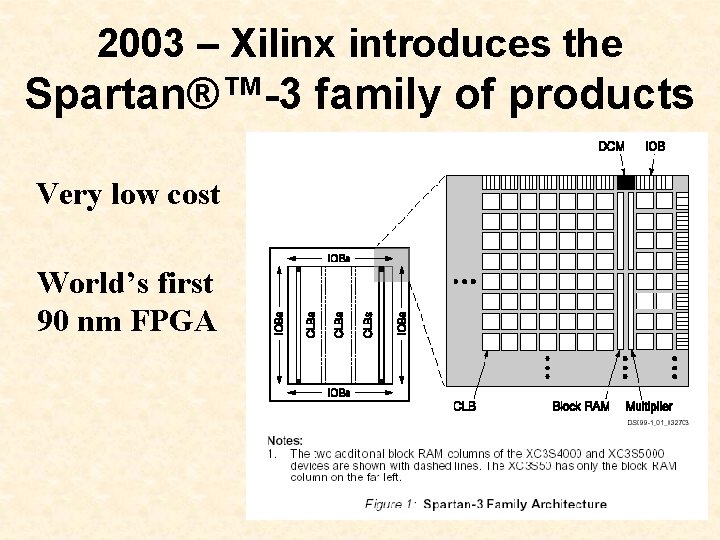

2003 – Xilinx introduces the Spartan®™-3 family of products Very low cost World’s first 90 nm FPGA

Xilinx will release the world’s first one-billion transistor device this year x

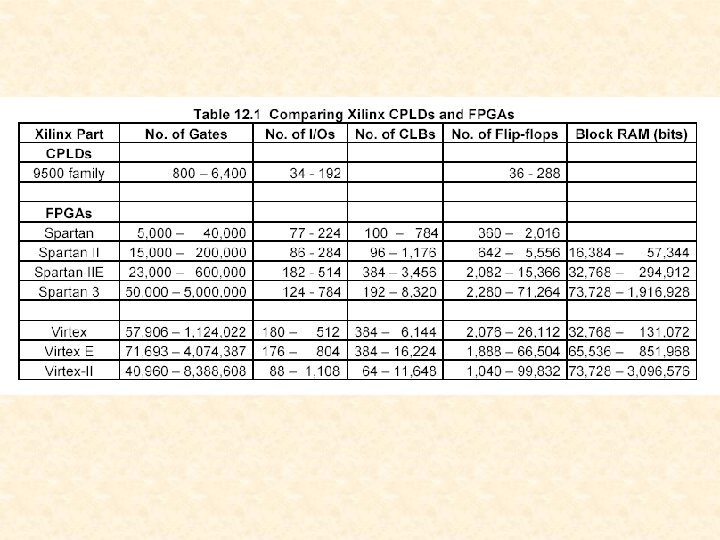

Logic Implementations • Fixed (ASICs) -- $12 billion market • Programmable (PLDs) -- $3. 5 billion market – CPLDs – FPGAs

Advantages of ASICs • Lower costs for very large volumes • Highest performance capabilities

Advantages of PLDs • • • Flexibility during design cycle Available – no long lead times No NRE costs Low inventory Can be modified after delivery

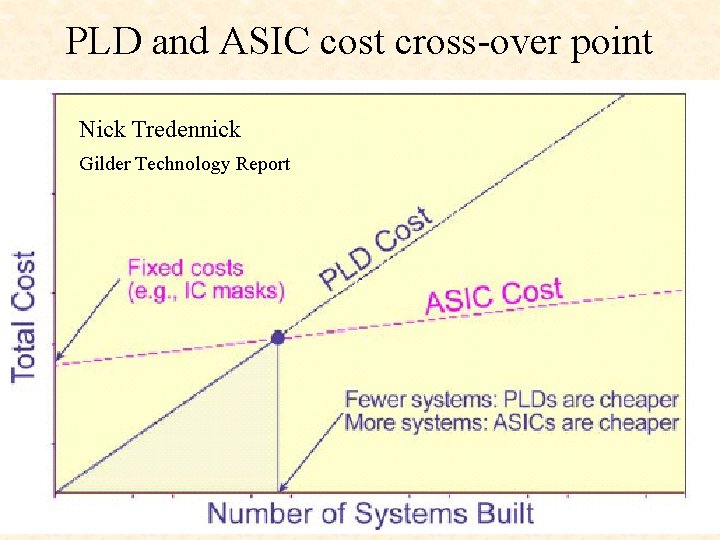

PLD and ASIC cost cross-over point Nick Tredennick Gilder Technology Report

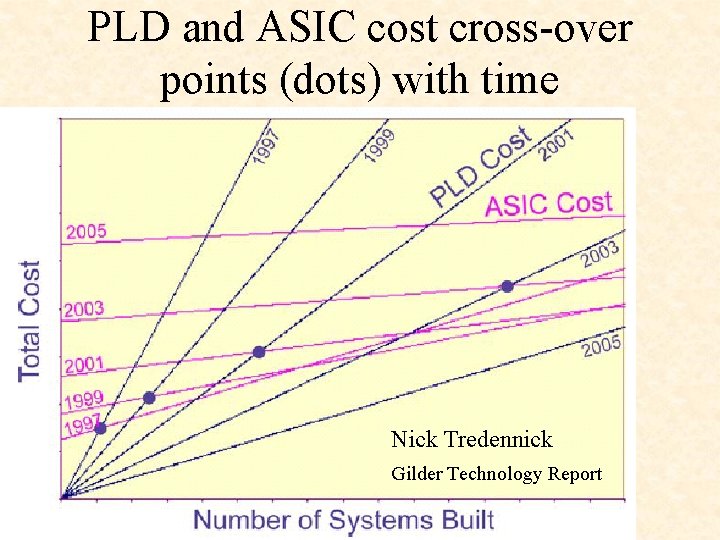

PLD and ASIC cost cross-over points (dots) with time Nick Tredennick Gilder Technology Report

- Slides: 37