Designing Embedded Systems with PIC Microcontrollers Principles and

Designing Embedded Systems with PIC Microcontrollers: Principles and Applications. 2 nd Edition. Tim Wilmshurst Chapter 12 Some PIC Microcontroller Advances The aims of this chapter are to introduce: • To introduce in overview two microcontrollers which show some enhanced features, the 16 F 88 and the 16 F 883; • To introduce some enhanced power management and oscillator techniques; • To introduce some enhanced peripherals. Instructors using Designing Embedded Systems with PIC Microcontrollers are welcome to use or change these slides as they see fit. Feedback, to t. j. wilmshurst@derby. ac. uk, is welcomed. The copyright to all diagrams is held by Microchip Technology, or T. Wilmshurst, unless otherwise stated

Some Challenges in Microcontroller Design • Can we add flexibility by loading on more peripherals, and increasing their configuration options? • At the same time, can we constrain the pin count, by making pins more multi-functional? • Can we reduce the overall system component count and hence free up pins, by making more things completely “on-chip”? • Can we conserve power, applying every trick possible with clock manipulation and selective power-down? • Can we respond to specialist protocols and applications, for example in the world of networking or machine control? • Can we still make a new microcontroller backward compatible with devices it aims to replace?

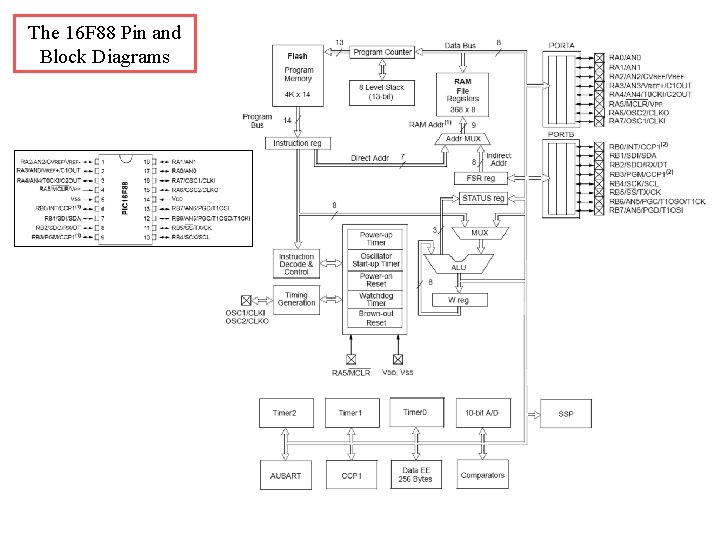

The 16 F 88 Pin and Block Diagrams

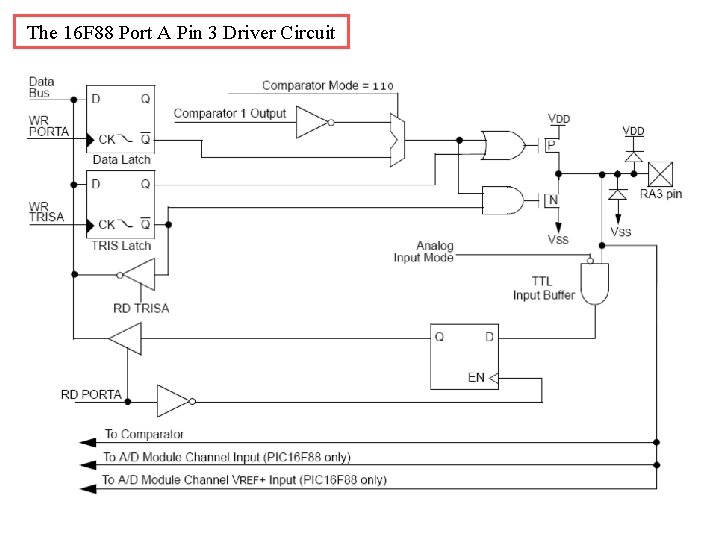

The 16 F 88 Port A Pin 3 Driver Circuit

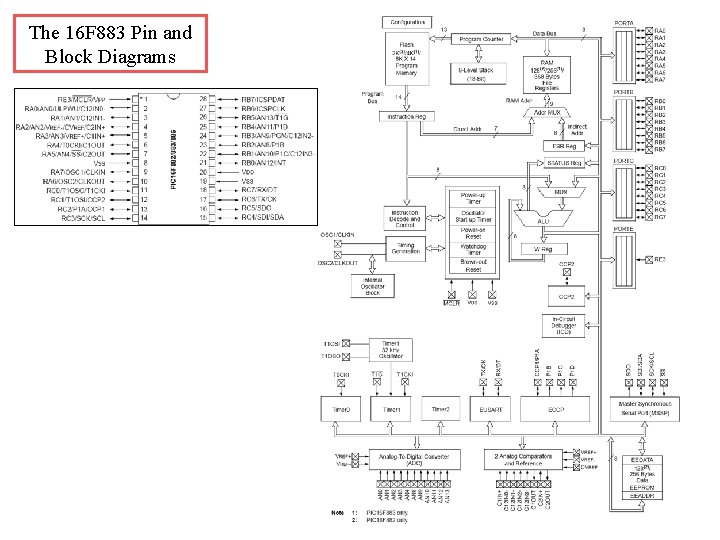

The 16 F 883 Pin and Block Diagrams

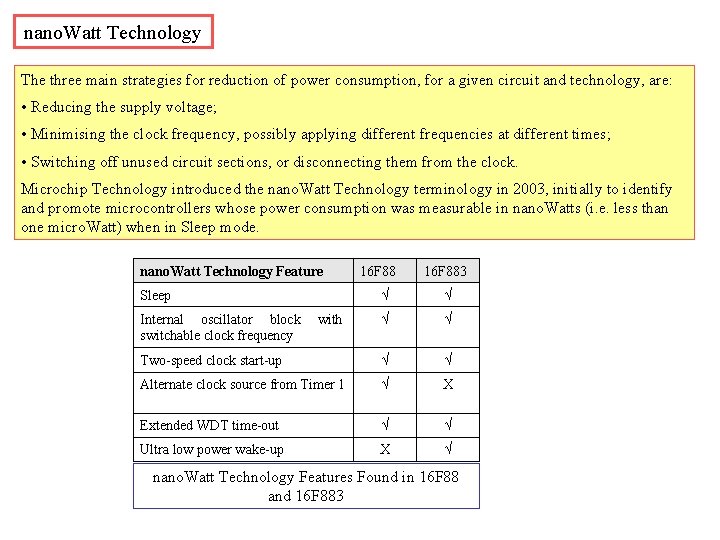

nano. Watt Technology The three main strategies for reduction of power consumption, for a given circuit and technology, are: • Reducing the supply voltage; • Minimising the clock frequency, possibly applying different frequencies at different times; • Switching off unused circuit sections, or disconnecting them from the clock. Microchip Technology introduced the nano. Watt Technology terminology in 2003, initially to identify and promote microcontrollers whose power consumption was measurable in nano. Watts (i. e. less than one micro. Watt) when in Sleep mode. nano. Watt Technology Feature 16 F 883 √ √ Two-speed clock start-up √ √ Alternate clock source from Timer 1 √ X Extended WDT time-out √ √ Ultra low power wake-up X √ Sleep Internal oscillator block switchable clock frequency with nano. Watt Technology Features Found in 16 F 88 and 16 F 883

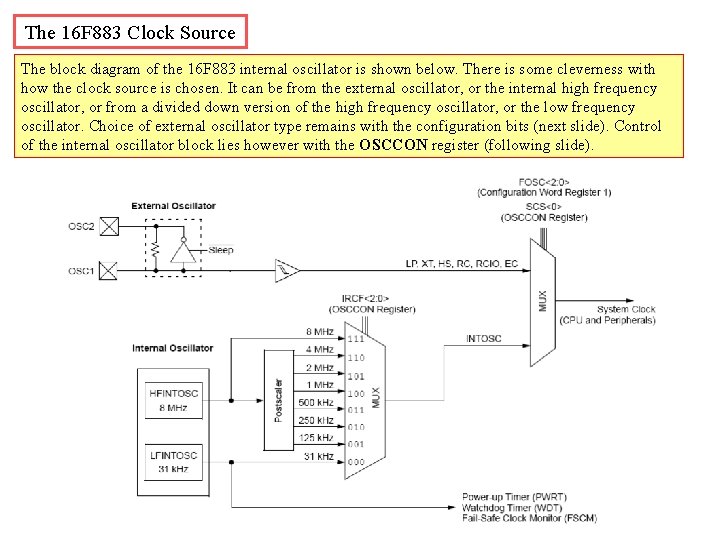

The 16 F 883 Clock Source The block diagram of the 16 F 883 internal oscillator is shown below. There is some cleverness with how the clock source is chosen. It can be from the external oscillator, or the internal high frequency oscillator, or from a divided down version of the high frequency oscillator, or the low frequency oscillator. Choice of external oscillator type remains with the configuration bits (next slide). Control of the internal oscillator block lies however with the OSCCON register (following slide).

External Oscillator Selection Bits within the Configuration Register

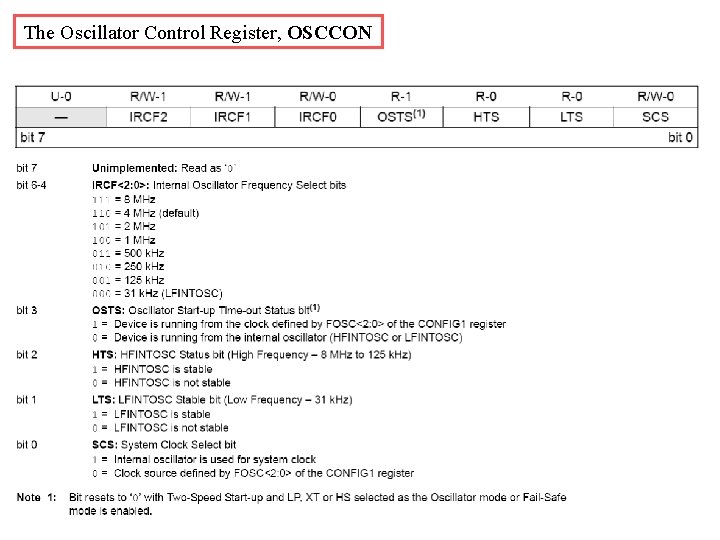

The Oscillator Control Register, OSCCON

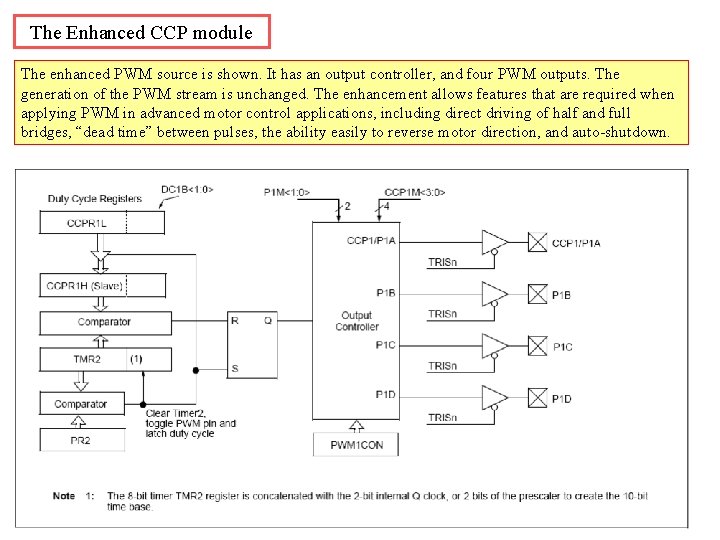

The Enhanced CCP module The enhanced PWM source is shown. It has an output controller, and four PWM outputs. The generation of the PWM stream is unchanged. The enhancement allows features that are required when applying PWM in advanced motor control applications, including direct driving of half and full bridges, “dead time” between pulses, the ability easily to reverse motor direction, and auto-shutdown.

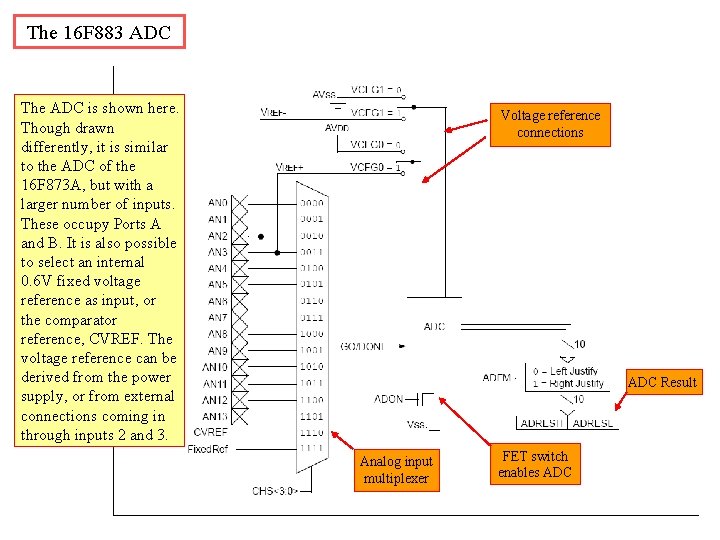

The 16 F 883 ADC The ADC is shown here. Though drawn differently, it is similar to the ADC of the 16 F 873 A, but with a larger number of inputs. These occupy Ports A and B. It is also possible to select an internal 0. 6 V fixed voltage reference as input, or the comparator reference, CVREF. The voltage reference can be derived from the power supply, or from external connections coming in through inputs 2 and 3. Voltage reference connections ADC Result Analog input multiplexer FET switch enables ADC

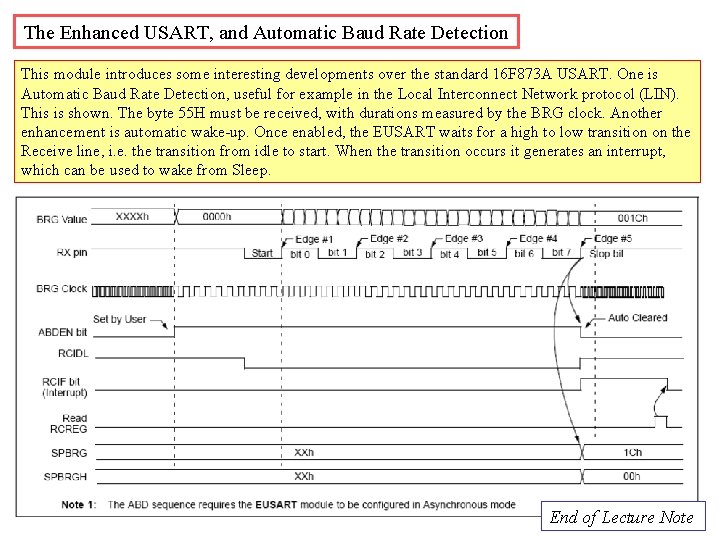

The Enhanced USART, and Automatic Baud Rate Detection This module introduces some interesting developments over the standard 16 F 873 A USART. One is Automatic Baud Rate Detection, useful for example in the Local Interconnect Network protocol (LIN). This is shown. The byte 55 H must be received, with durations measured by the BRG clock. Another enhancement is automatic wake-up. Once enabled, the EUSART waits for a high to low transition on the Receive line, i. e. the transition from idle to start. When the transition occurs it generates an interrupt, which can be used to wake from Sleep. End of Lecture Note

- Slides: 12