ELEC 7770 Advanced VLSI Design Spring 2016 Analog

![ILP § Define xi [0, 1], such that xi = 0 discard Ti. § ILP § Define xi [0, 1], such that xi = 0 discard Ti. §](https://slidetodoc.com/presentation_image/a477fdbc7c981102557c477f4a4fca3c/image-19.jpg)

- Slides: 36

ELEC 7770: Advanced VLSI Design Spring 2016 Analog and RF Test Strategies Vishwani D. Agrawal James J. Danaher Professor ECE Department, Auburn University Auburn, AL 36849 vagrawal@eng. auburn. edu http: //www. eng. auburn. edu/~vagrawal/COURSE/E 7770_Spr 16 Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 1

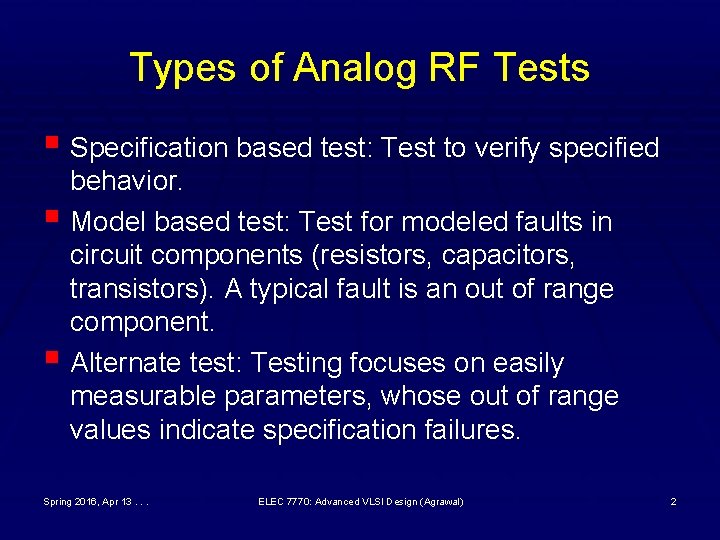

Types of Analog RF Tests § Specification based test: Test to verify specified behavior. § Model based test: Test for modeled faults in circuit components (resistors, capacitors, transistors). A typical fault is an out of range component. § Alternate test: Testing focuses on easily measurable parameters, whose out of range values indicate specification failures. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 2

References § A. Afshar, Principles of Semiconductor Network Testing, Boston: § § § § Butterworth-Heinemann, 1995. M. Burns and G. Roberts, Introduction to Mixed-Signal IC Test and Measurement, New York: Oxford University Press, 2000. M. L. Bushnell and V. D. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits, Boston: Springer, 2000. R. W. Liu, editor, Testing and Diagnosis of Analog Circuits and Systems, New York: Van Nostrand Reinhold, 1991. M. Mahoney, DSP-Based Testing of Analog and Mixed-Signal Circuits, Los Alamitos, California: IEEE Computer Society Press, 1987. A. Osseiran, Analog and Mixed-Signal Boundary Scan, Boston: Springer, 1999. T. Ozawa, editor, Analog Methods for Computer-Aided Circuit Analysis and Diagnosis, New York: Marcel Dekker, 1988. B. Vinnakota, editor, Analog and Mixed-Signal Test, Upper Saddle River, New Jersey: Prentice-Hall PTR, 1998. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 3

Specification Test Cost Reduction § Given a set of complete specification-based tests § § § for an analog or RF circuit, and An acceptable defect level (DL), Find the smallest set of tests that should be used. Reference: § S. Sindia and V. D. Agrawal, “Defect Level Constrained Optimization of Analog and Radio Frequency Specification Tests, ” J. Electronic Testing: Theory and Applications (JETTA), vol. 31, no. 5, pp. 479 -489, October 2015. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 4

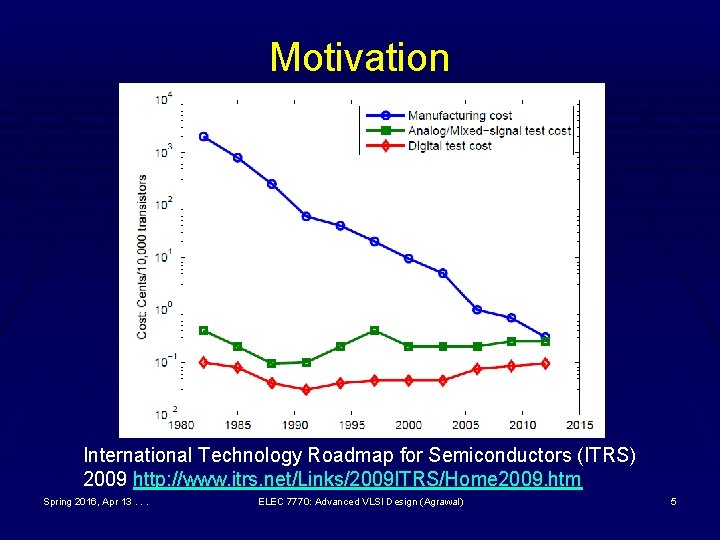

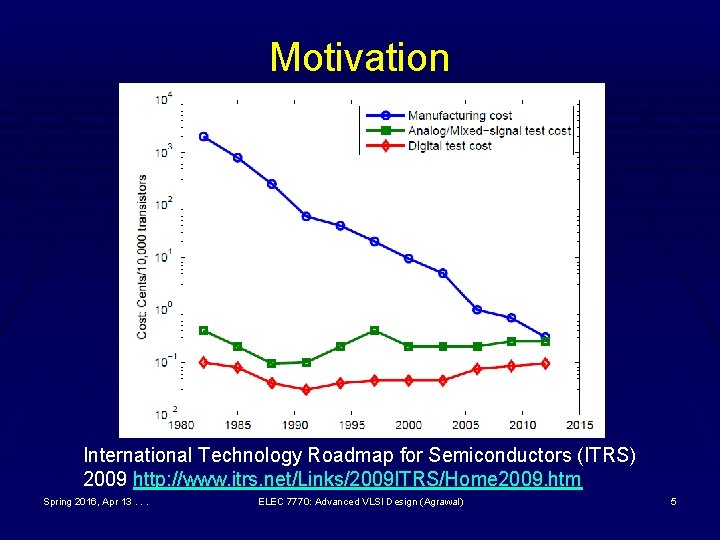

Motivation International Technology Roadmap for Semiconductors (ITRS) 2009 http: //www. itrs. net/Links/2009 ITRS/Home 2009. htm Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 5

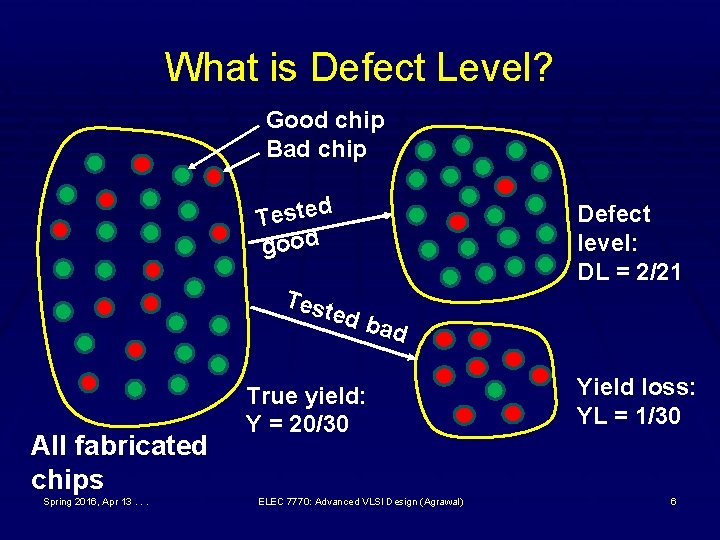

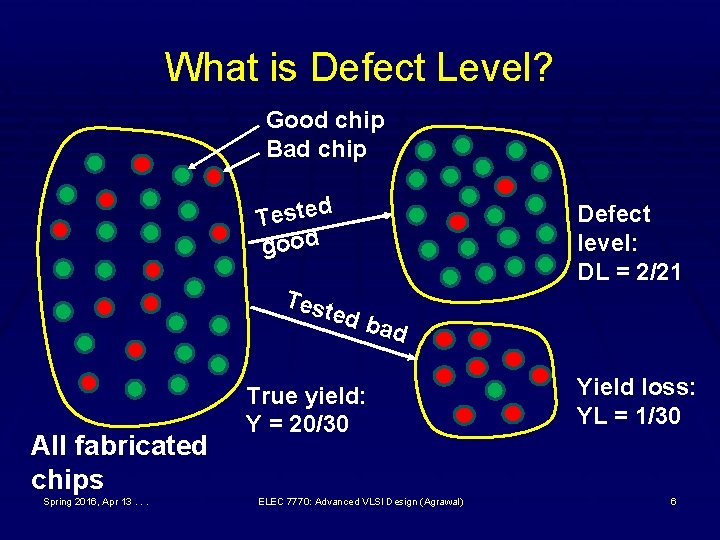

What is Defect Level? Good chip Bad chip Tested good Tes Defect level: DL = 2/21 ted b All fabricated chips Spring 2016, Apr 13. . . ad True yield: Y = 20/30 ELEC 7770: Advanced VLSI Design (Agrawal) Yield loss: YL = 1/30 6

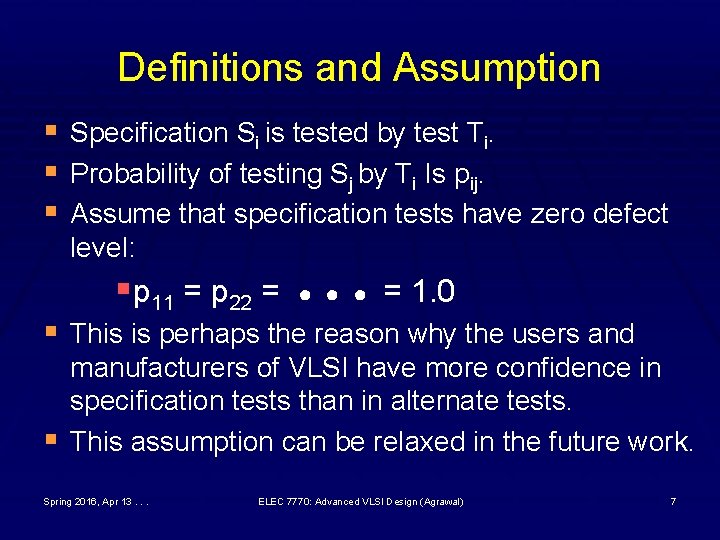

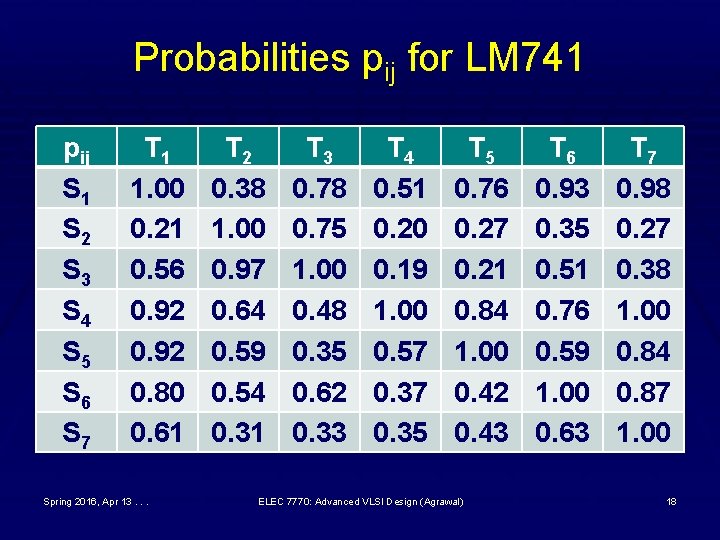

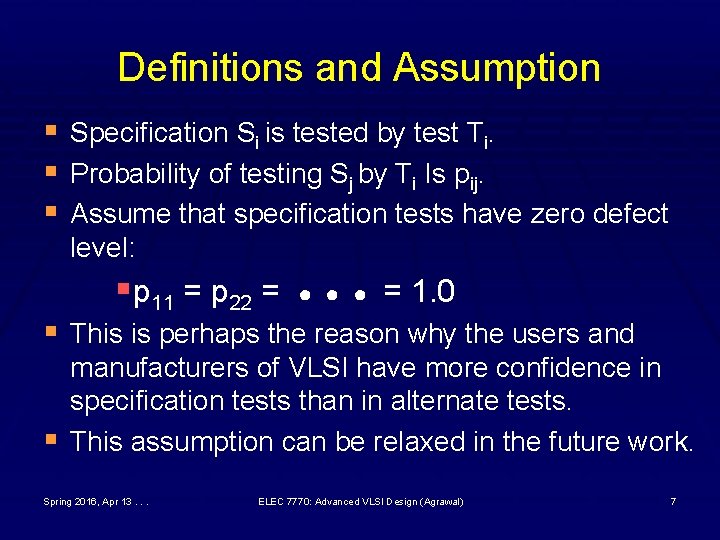

Definitions and Assumption § Specification Si is tested by test Ti. § Probability of testing Sj by Ti Is pij. § Assume that specification tests have zero defect level: §p 11 = p 22 = ● ● ● = 1. 0 § This is perhaps the reason why the users and § manufacturers of VLSI have more confidence in specification tests than in alternate tests. This assumption can be relaxed in the future work. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 7

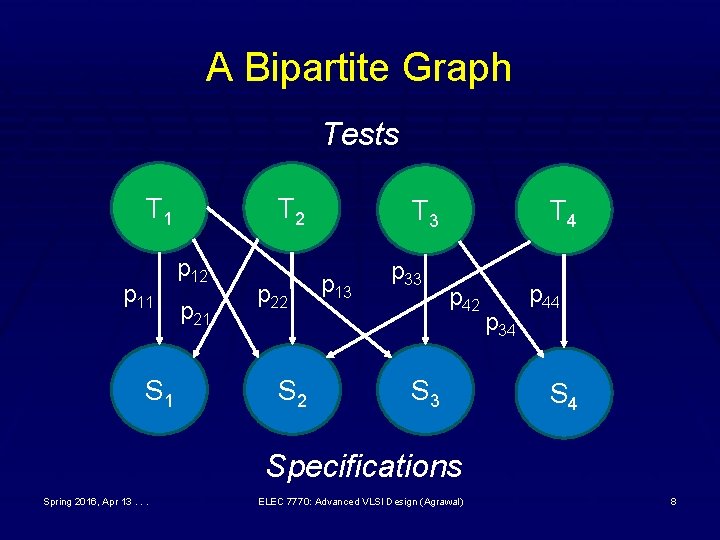

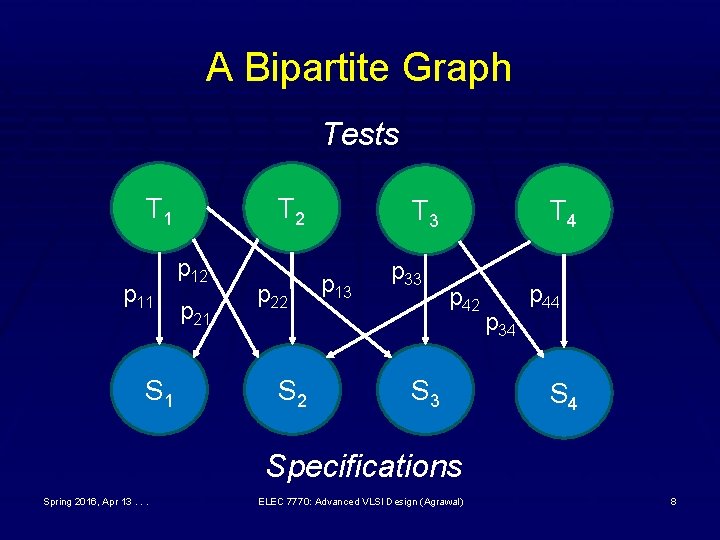

A Bipartite Graph Tests T 1 p 11 S 1 T 2 p 12 p 21 p 22 S 2 T 3 p 13 p 33 T 4 p 42 S 3 p 34 p 44 S 4 Specifications Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 8

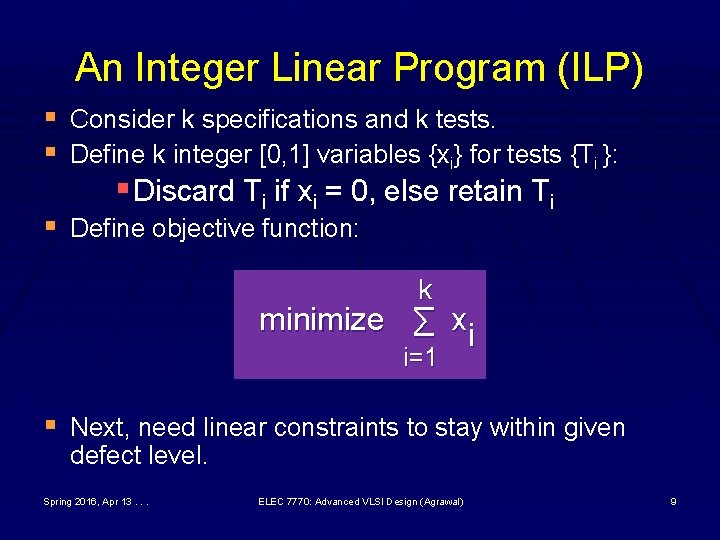

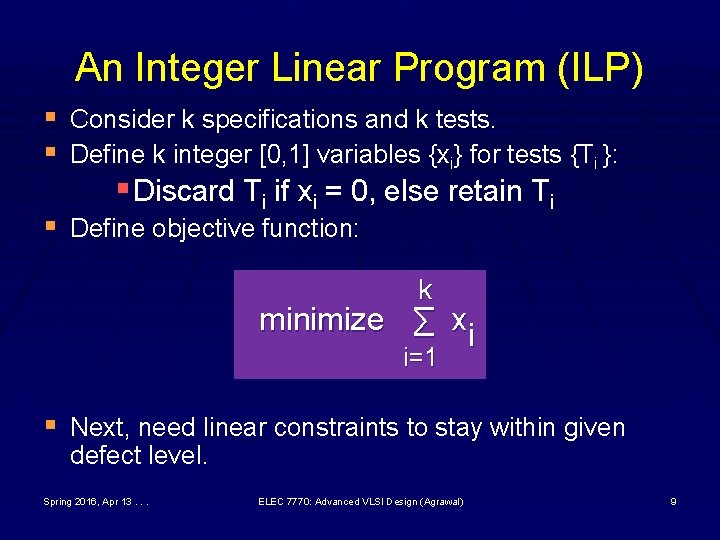

An Integer Linear Program (ILP) § Consider k specifications and k tests. § Define k integer [0, 1] variables {xi} for tests {Ti }: § Discard Ti if xi = 0, else retain Ti § Define objective function: k minimize ∑ xi i=1 § Next, need linear constraints to stay within given defect level. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 9

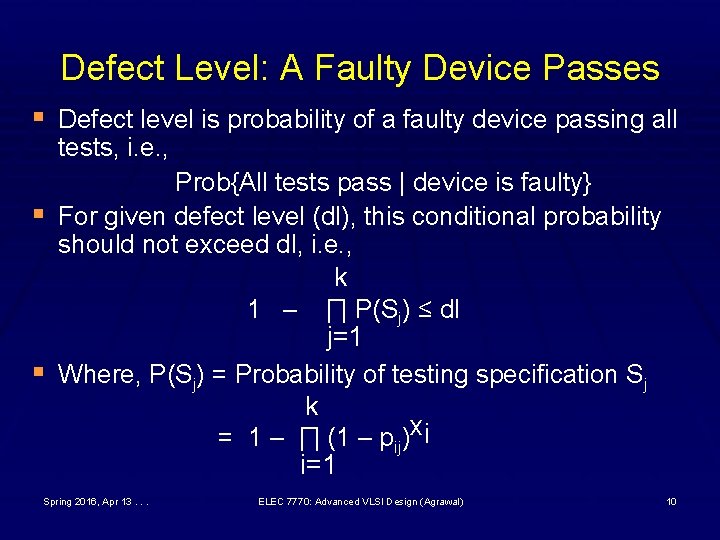

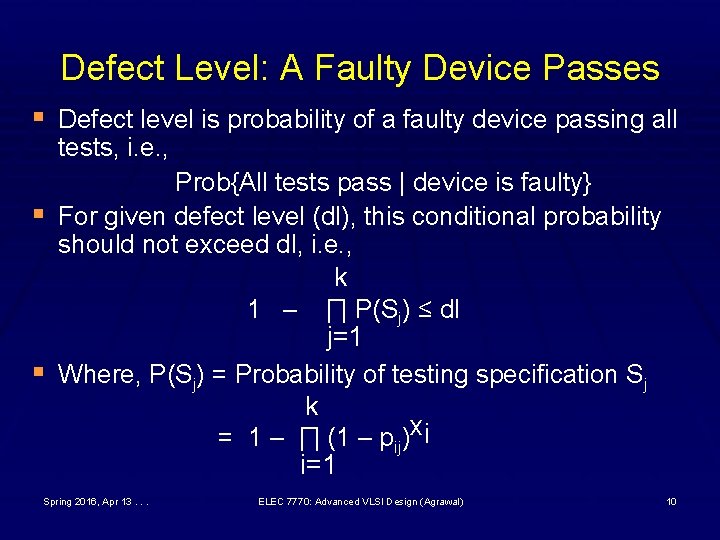

Defect Level: A Faulty Device Passes § Defect level is probability of a faulty device passing all tests, i. e. , § § Prob{All tests pass | device is faulty} For given defect level (dl), this conditional probability should not exceed dl, i. e. , k 1 – ∏ P(Sj) ≤ dl j=1 Where, P(Sj) = Probability of testing specification Sj k = 1 – ∏ (1 – pij)xi i=1 Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 10

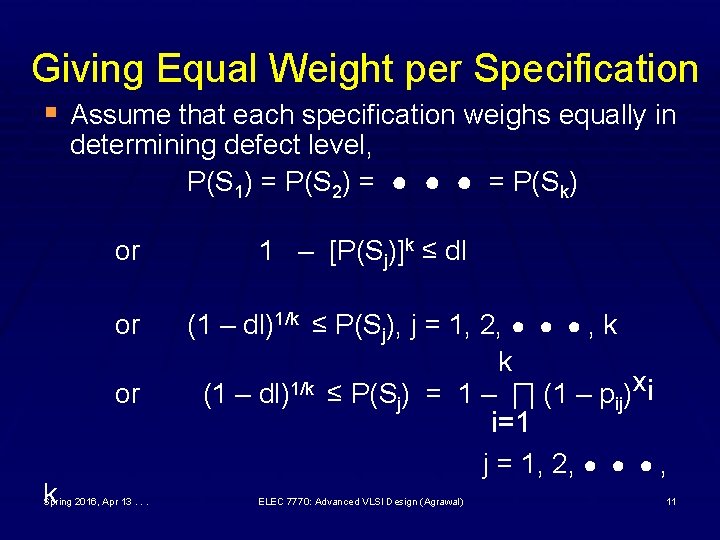

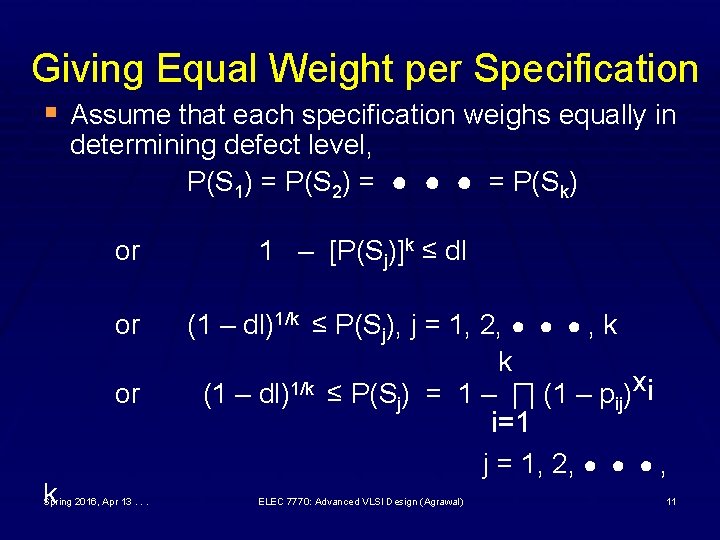

Giving Equal Weight per Specification § Assume that each specification weighs equally in determining defect level, P(S 1) = P(S 2) = ● ● ● = P(Sk) or or or k Spring 2016, Apr 13. . . 1 – [P(Sj)]k ≤ dl (1 – dl)1/k ≤ P(Sj), j = 1, 2, ● ● ● , k k (1 – dl)1/k ≤ P(Sj) = 1 – ∏ (1 – pij)xi i=1 j = 1, 2, ● ● ● , ELEC 7770: Advanced VLSI Design (Agrawal) 11

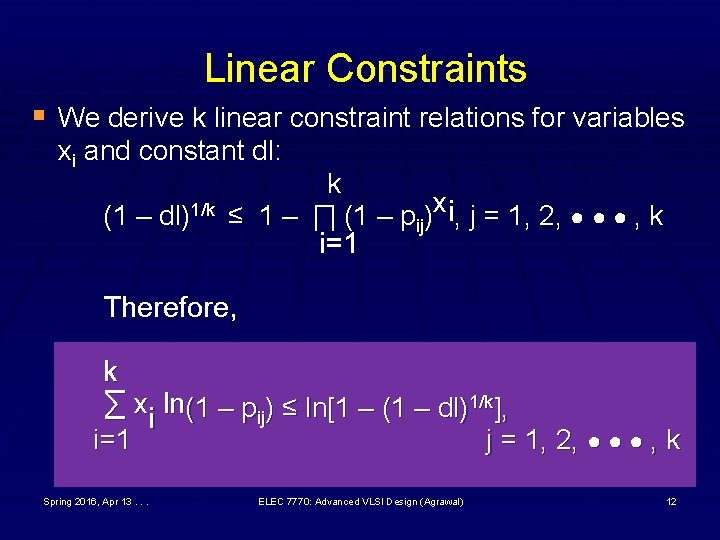

Linear Constraints § We derive k linear constraint relations for variables xi and constant dl: (1 – dl)1/k k ≤ 1 – ∏ (1 – pij)xi, j = 1, 2, ● ● ● , k i=1 Therefore, k ∑ xi ln(1 – pij) ≤ ln[1 – (1 – dl)1/k], i=1 Spring 2016, Apr 13. . . j = 1, 2, ● ● ● , k ELEC 7770: Advanced VLSI Design (Agrawal) 12

Operational Amplifier: TI LM 741 Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 13

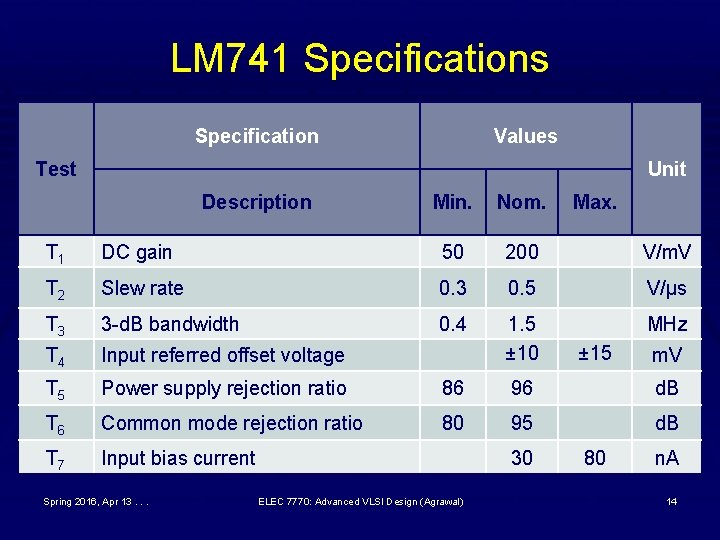

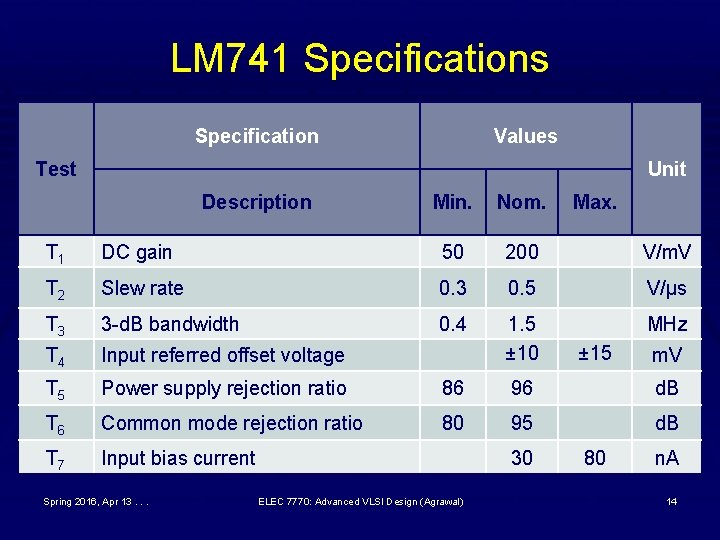

LM 741 Specifications Specification Values Test Unit Description Min. Nom. Max. T 1 DC gain 50 200 V/m. V T 2 Slew rate 0. 3 0. 5 V/μs T 3 3 -d. B bandwidth 0. 4 MHz T 4 Input referred offset voltage 1. 5 ± 10 T 5 Power supply rejection ratio 86 96 d. B T 6 Common mode rejection ratio 80 95 d. B T 7 Input bias current Spring 2016, Apr 13. . . 30 ELEC 7770: Advanced VLSI Design (Agrawal) ± 15 80 m. V n. A 14

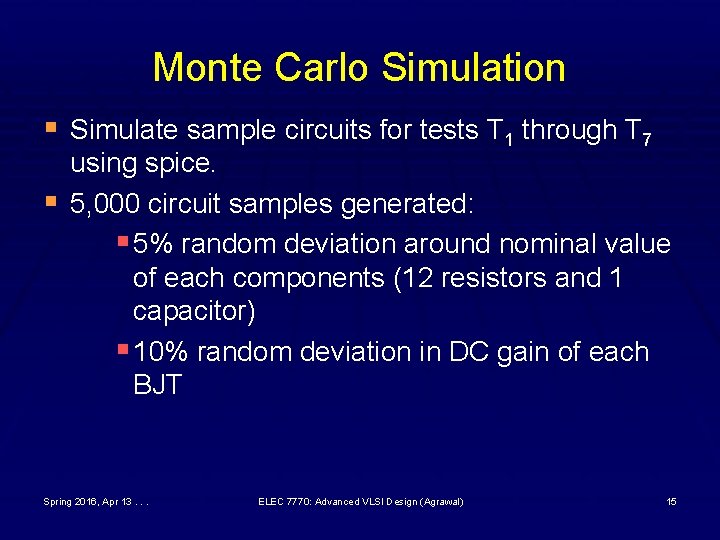

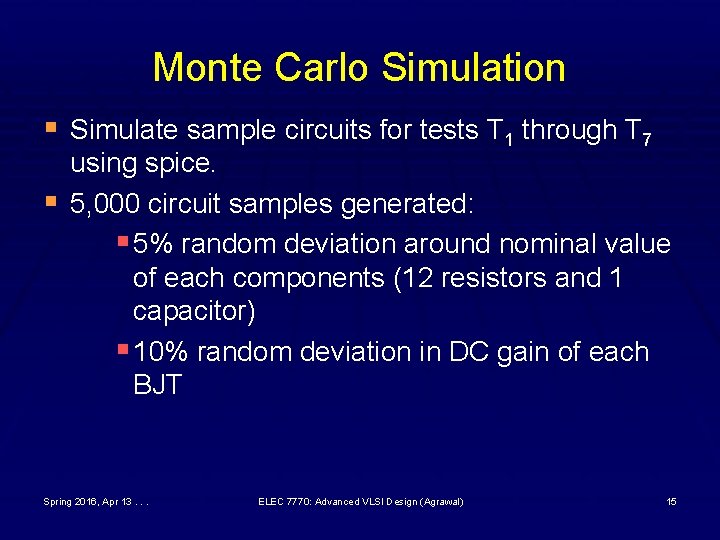

Monte Carlo Simulation § Simulate sample circuits for tests T 1 through T 7 § using spice. 5, 000 circuit samples generated: § 5% random deviation around nominal value of each components (12 resistors and 1 capacitor) § 10% random deviation in DC gain of each BJT Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 15

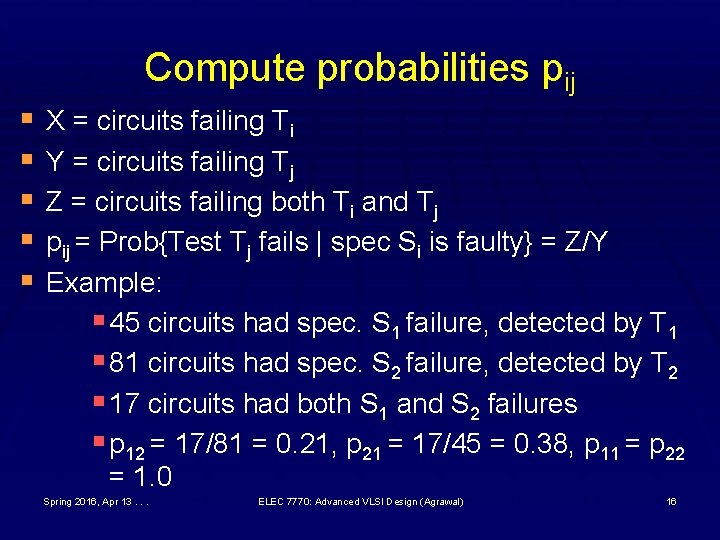

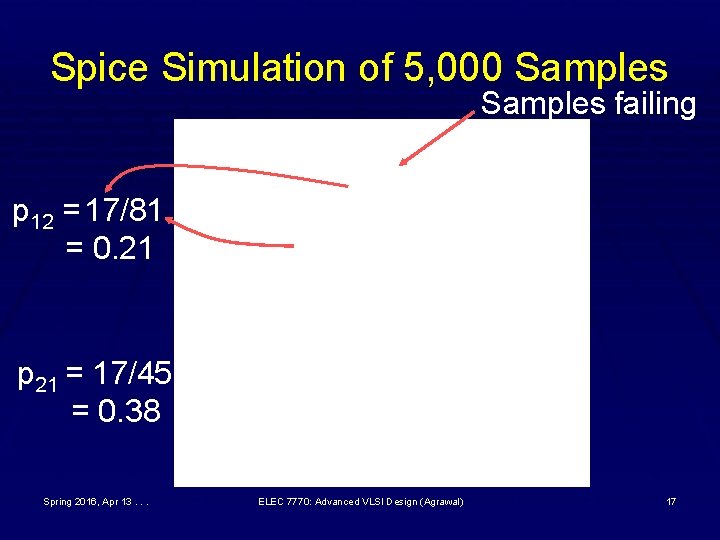

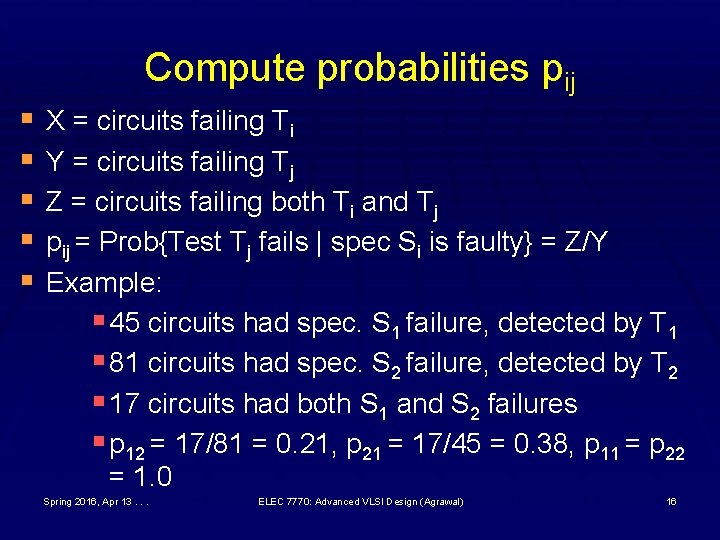

Compute probabilities pij § X = circuits failing Ti § Y = circuits failing Tj § Z = circuits failing both Ti and Tj § pij = Prob{Test Tj fails | spec Si is faulty} = Z/Y § Example: § 45 circuits had spec. S 1 failure, detected by T 1 § 81 circuits had spec. S 2 failure, detected by T 2 § 17 circuits had both S 1 and S 2 failures § p 12 = 17/81 = 0. 21, p 21 = 17/45 = 0. 38, p 11 = p 22 = 1. 0 Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 16

Spice Simulation of 5, 000 Samples failing p 12 =17/81 = 0. 21 p 21 = 17/45 = 0. 38 Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 17

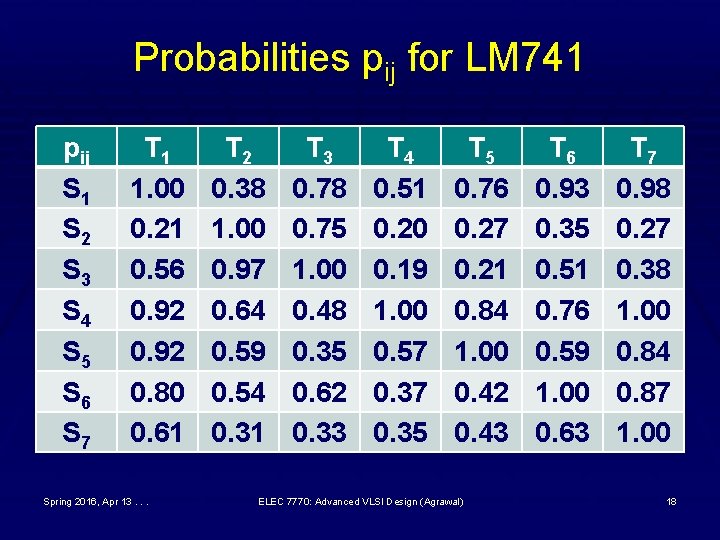

Probabilities pij for LM 741 pij S 1 S 2 S 3 S 4 S 5 S 6 S 7 T 1 1. 00 0. 21 0. 56 0. 92 0. 80 0. 61 Spring 2016, Apr 13. . . T 2 0. 38 1. 00 0. 97 0. 64 0. 59 0. 54 0. 31 T 3 0. 78 0. 75 1. 00 0. 48 0. 35 0. 62 0. 33 T 4 0. 51 0. 20 0. 19 1. 00 0. 57 0. 35 T 5 0. 76 0. 27 0. 21 0. 84 1. 00 0. 42 0. 43 ELEC 7770: Advanced VLSI Design (Agrawal) T 6 0. 93 0. 35 0. 51 0. 76 0. 59 1. 00 0. 63 T 7 0. 98 0. 27 0. 38 1. 00 0. 84 0. 87 1. 00 18

![ILP Define xi 0 1 such that xi 0 discard Ti ILP § Define xi [0, 1], such that xi = 0 discard Ti. §](https://slidetodoc.com/presentation_image/a477fdbc7c981102557c477f4a4fca3c/image-19.jpg)

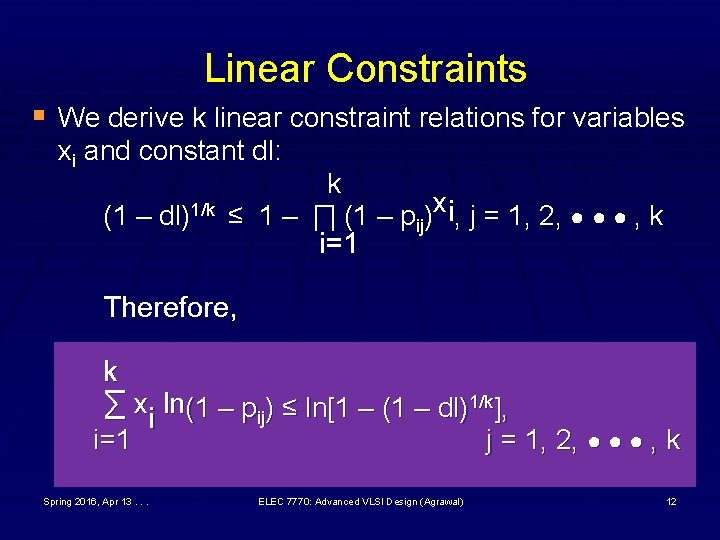

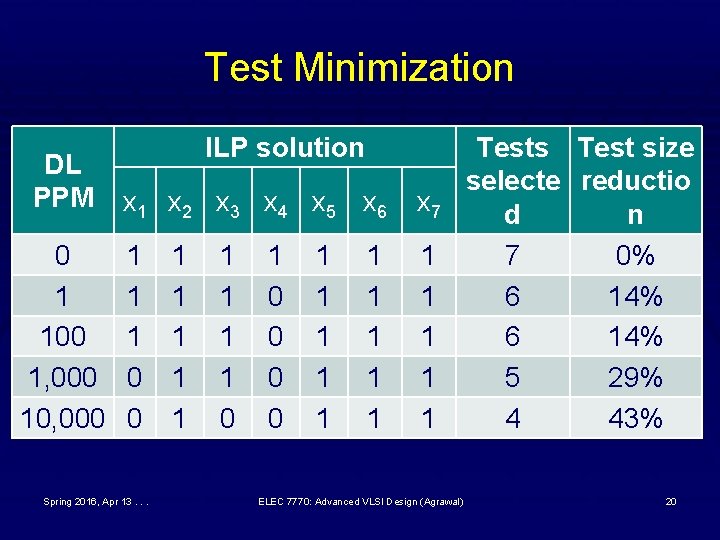

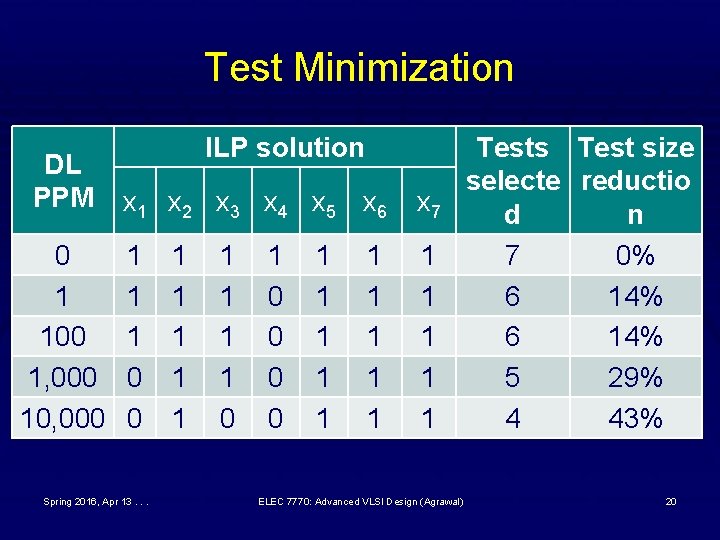

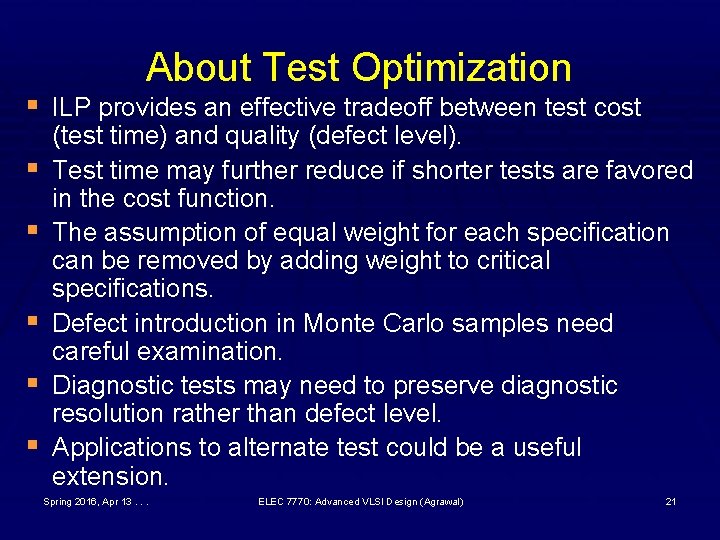

ILP § Define xi [0, 1], such that xi = 0 discard Ti. § Objective function: 7 minimize ∑ xi i=1 § Subject to: 7 ∑ xi ln(1 – pij) ≤ ln[1 – (1 – dl)1/7], i=1 j = 1, 2, ● ● ● , 7 where dl = defect level Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 19

Test Minimization DL PPM 0 1 100 1, 000 10, 000 ILP solution x 1 x 2 x 3 x 4 x 5 x 6 x 7 1 1 1 0 0 1 1 1 Spring 2016, Apr 13. . . 1 1 1 1 1 0 0 0 0 1 1 1 1 1 ELEC 7770: Advanced VLSI Design (Agrawal) Tests Test size selecte reductio d n 7 0% 6 14% 5 29% 4 43% 20

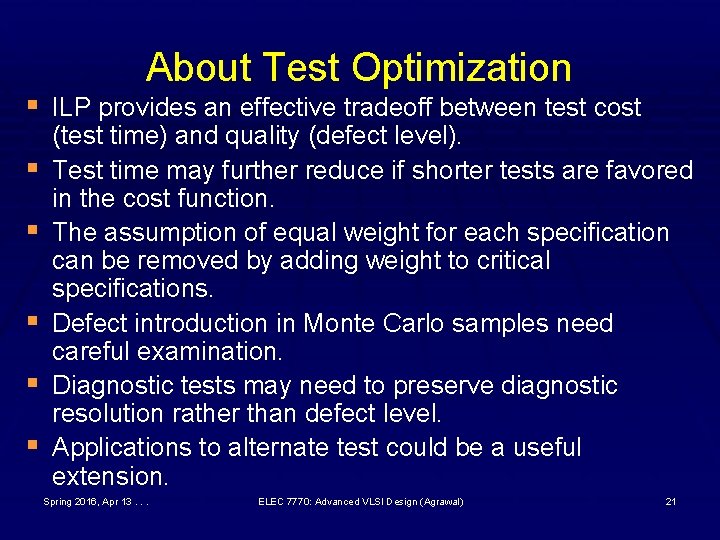

About Test Optimization § ILP provides an effective tradeoff between test cost § § § (test time) and quality (defect level). Test time may further reduce if shorter tests are favored in the cost function. The assumption of equal weight for each specification can be removed by adding weight to critical specifications. Defect introduction in Monte Carlo samples need careful examination. Diagnostic tests may need to preserve diagnostic resolution rather than defect level. Applications to alternate test could be a useful extension. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 21

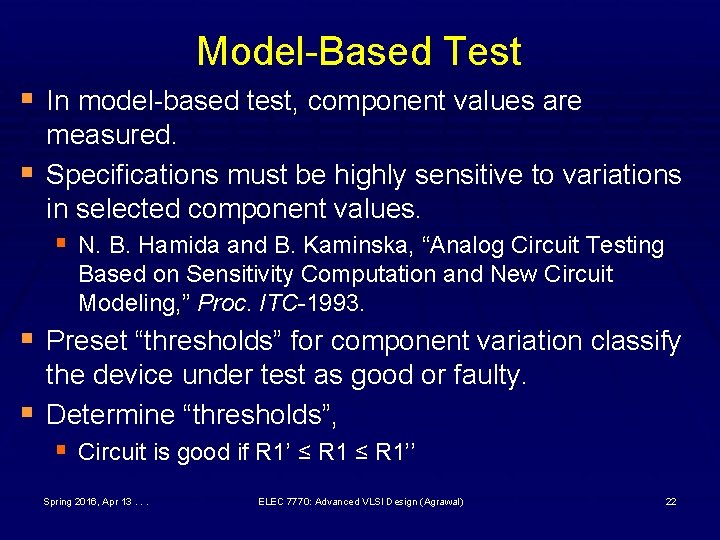

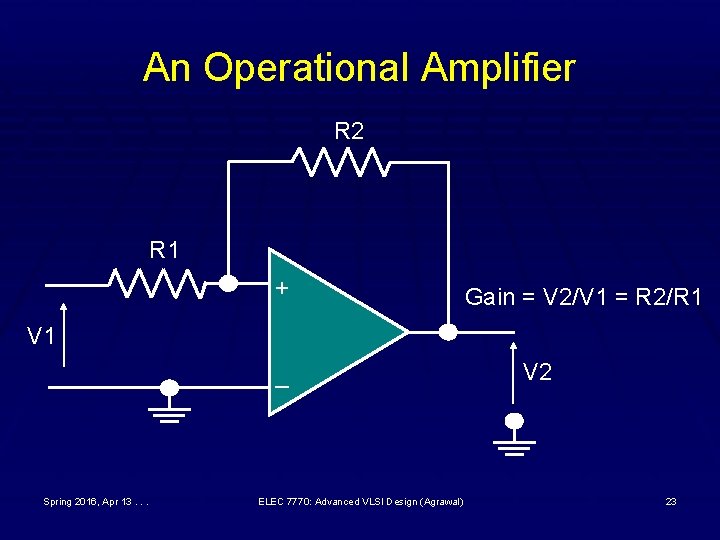

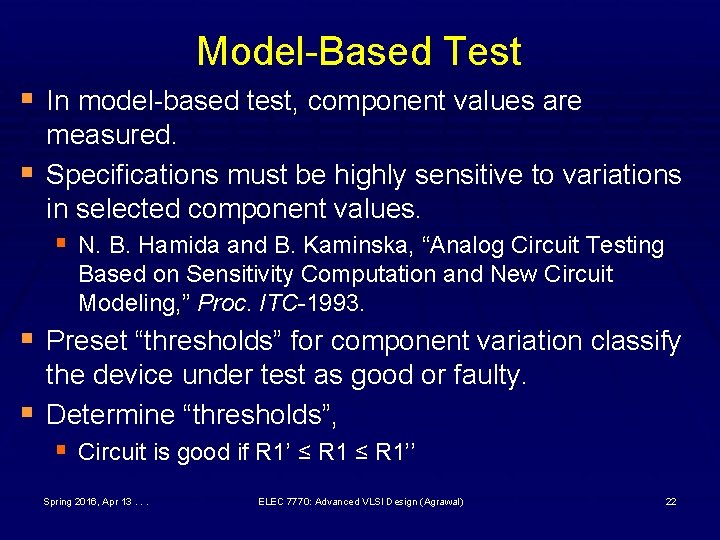

Model-Based Test § In model-based test, component values are § measured. Specifications must be highly sensitive to variations in selected component values. § N. B. Hamida and B. Kaminska, “Analog Circuit Testing Based on Sensitivity Computation and New Circuit Modeling, ” Proc. ITC-1993. § Preset “thresholds” for component variation classify § the device under test as good or faulty. Determine “thresholds”, § Circuit is good if R 1’ ≤ R 1’’ Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 22

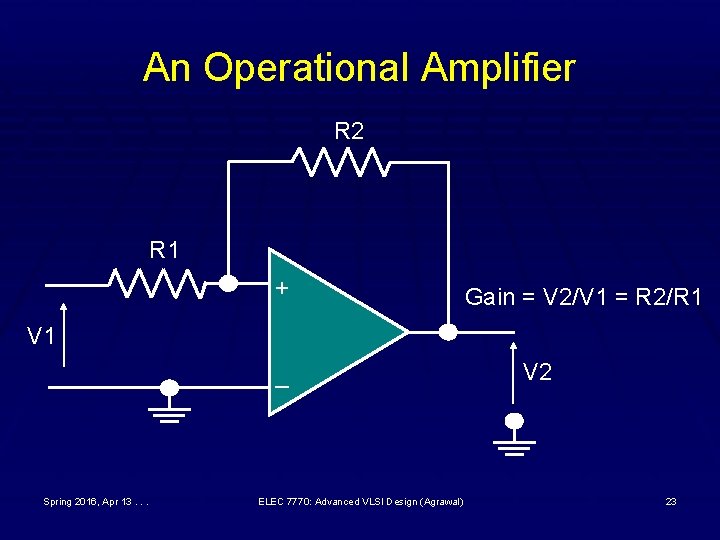

An Operational Amplifier R 2 R 1 + Gain = V 2/V 1 = R 2/R 1 V 1 _ Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) V 2 23

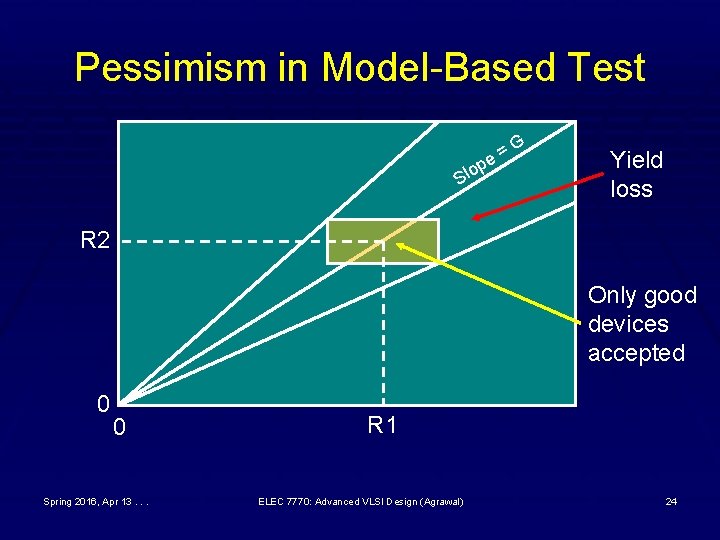

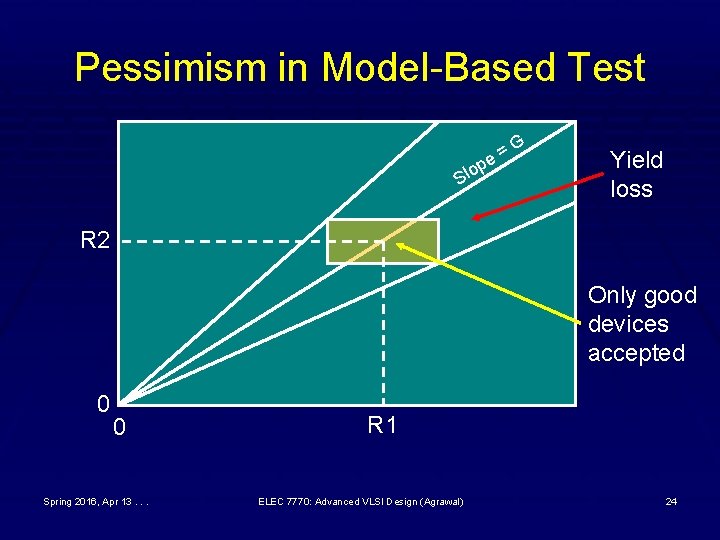

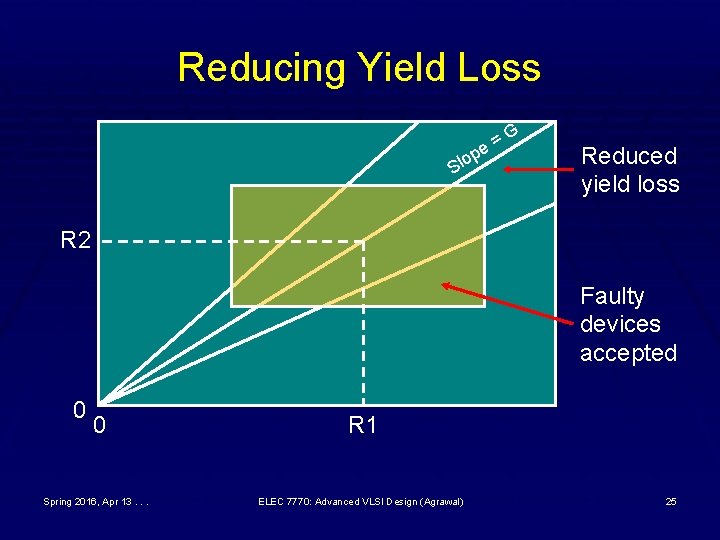

Pessimism in Model-Based Test G = e p Slo Yield loss R 2 Only good devices accepted 0 0 Spring 2016, Apr 13. . . R 1 ELEC 7770: Advanced VLSI Design (Agrawal) 24

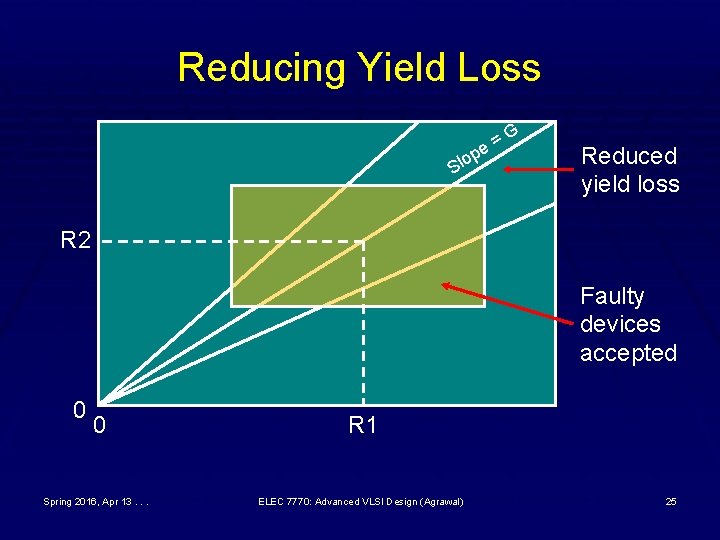

Reducing Yield Loss G = e p Slo Reduced yield loss R 2 Faulty devices accepted 0 0 Spring 2016, Apr 13. . . R 1 ELEC 7770: Advanced VLSI Design (Agrawal) 25

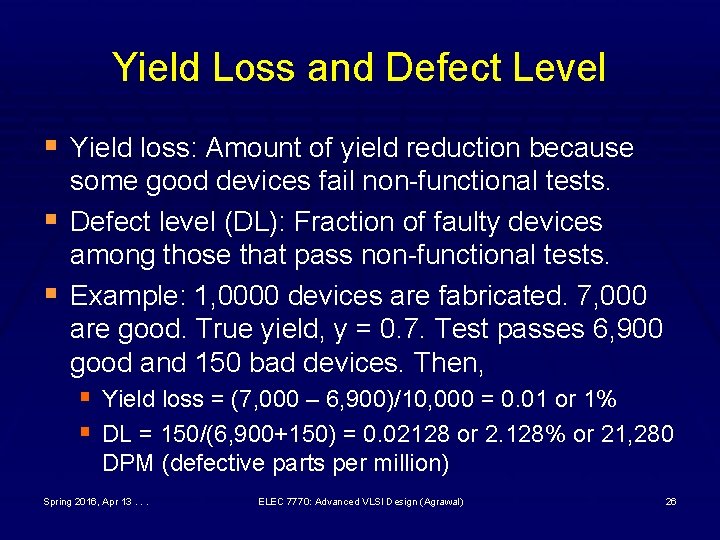

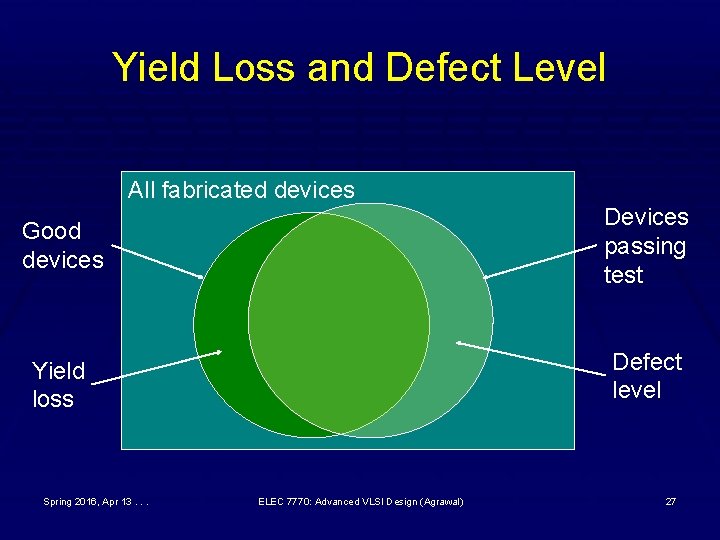

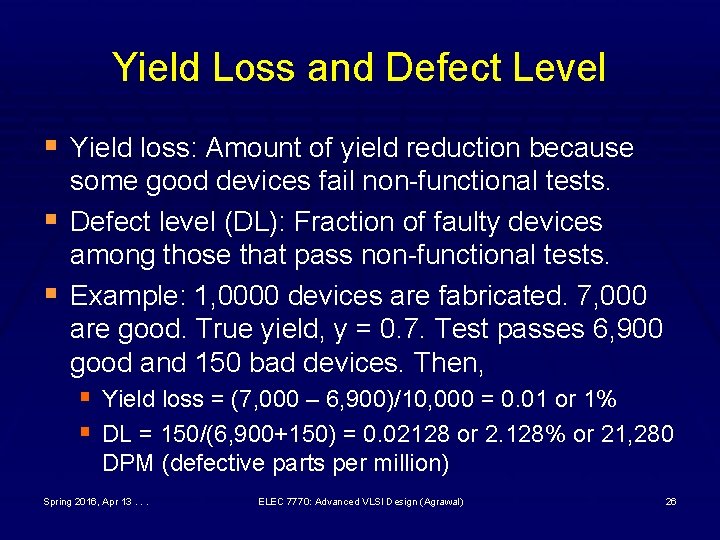

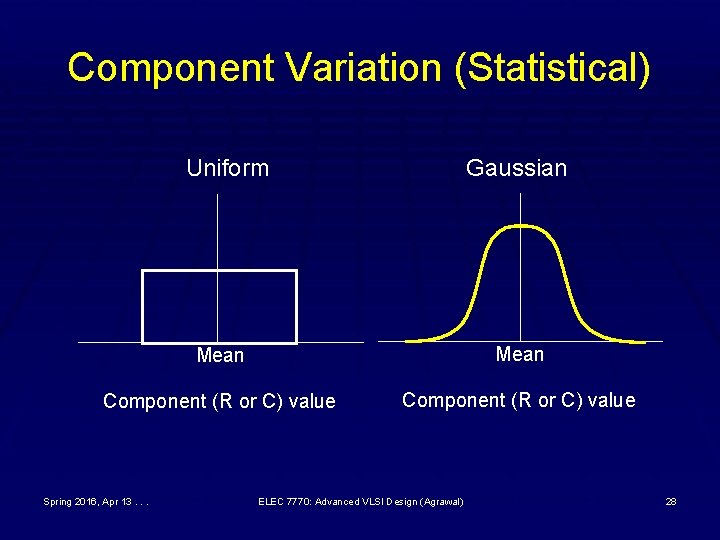

Yield Loss and Defect Level § Yield loss: Amount of yield reduction because § § some good devices fail non-functional tests. Defect level (DL): Fraction of faulty devices among those that pass non-functional tests. Example: 1, 0000 devices are fabricated. 7, 000 are good. True yield, y = 0. 7. Test passes 6, 900 good and 150 bad devices. Then, § Yield loss = (7, 000 – 6, 900)/10, 000 = 0. 01 or 1% § DL = 150/(6, 900+150) = 0. 02128 or 2. 128% or 21, 280 DPM (defective parts per million) Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 26

Yield Loss and Defect Level All fabricated devices Good devices Devices passing test Yield loss Defect level Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 27

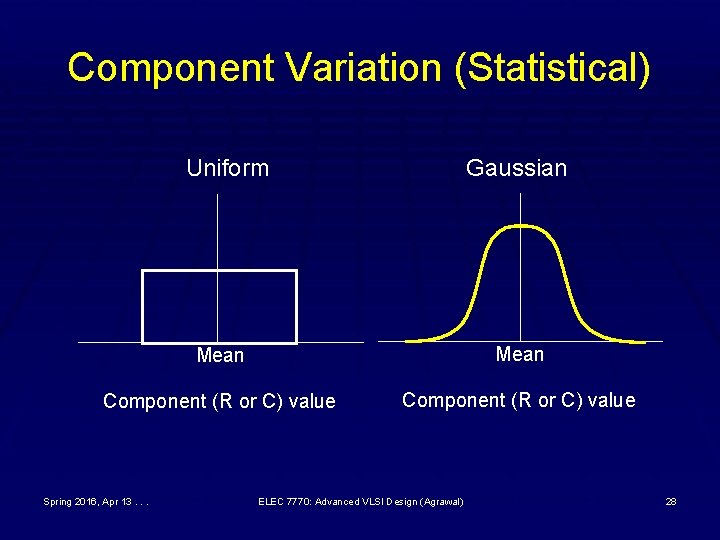

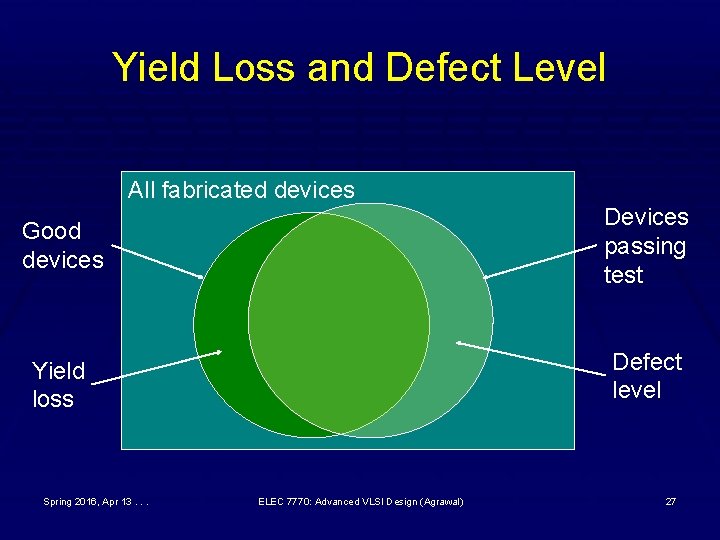

Component Variation (Statistical) Uniform Gaussian Mean Component (R or C) value Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 28

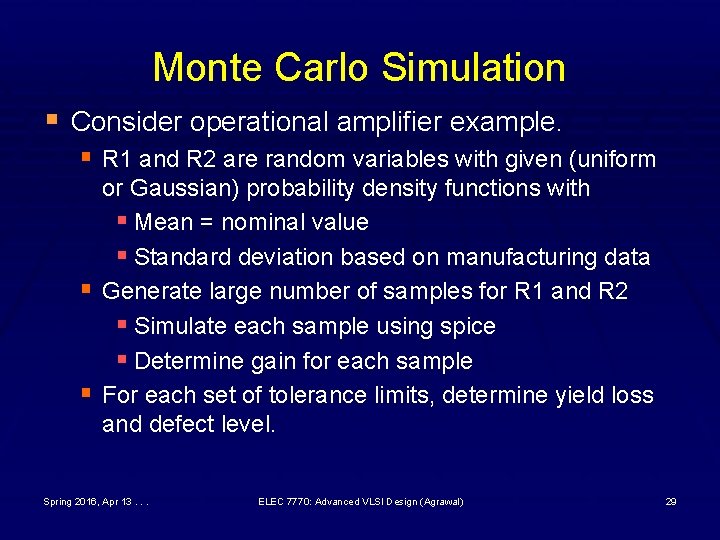

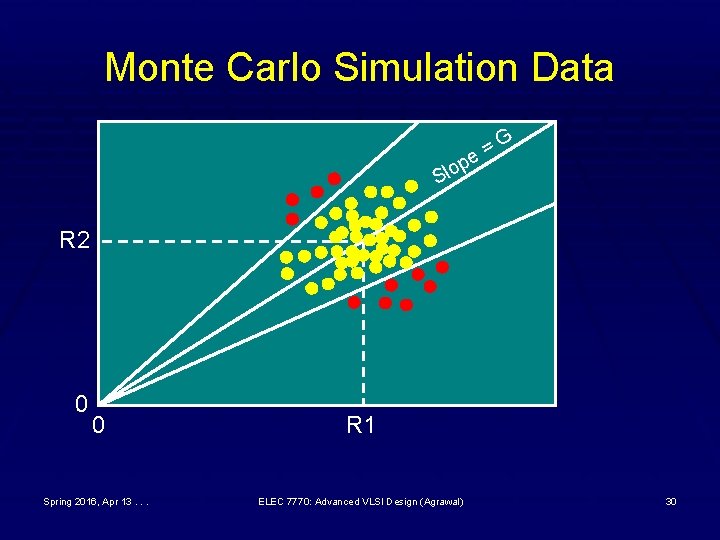

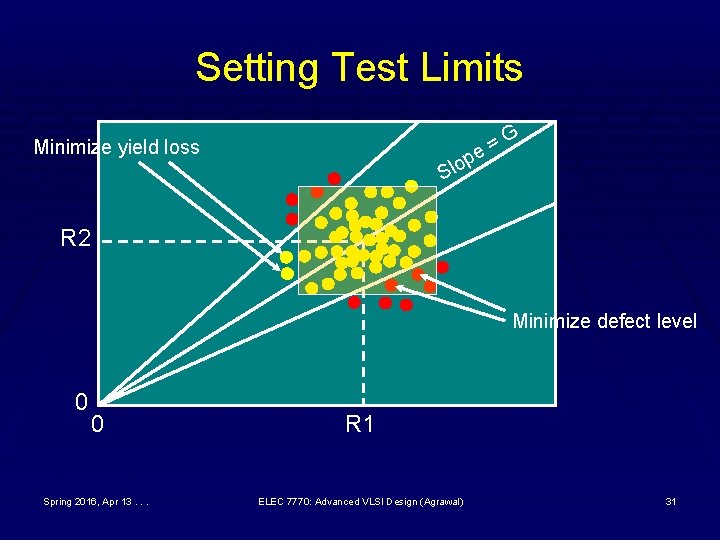

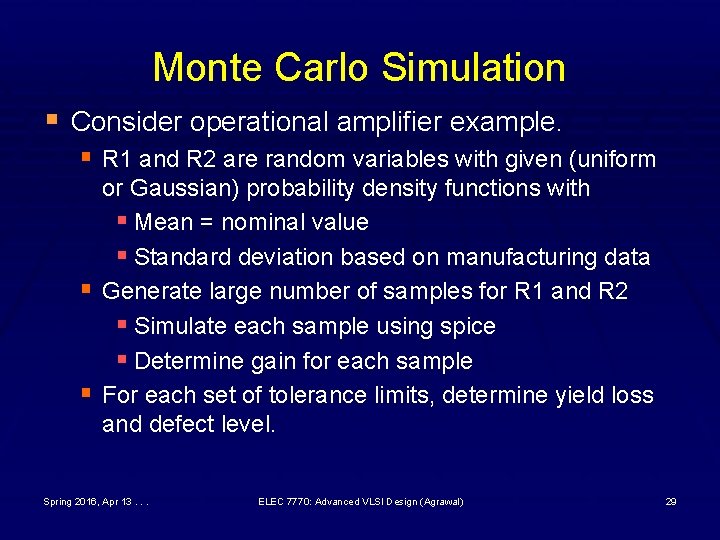

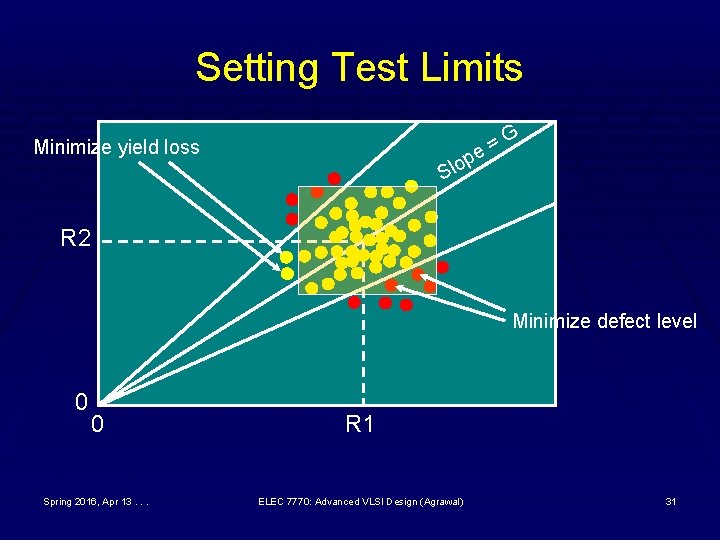

Monte Carlo Simulation § Consider operational amplifier example. § R 1 and R 2 are random variables with given (uniform § § or Gaussian) probability density functions with § Mean = nominal value § Standard deviation based on manufacturing data Generate large number of samples for R 1 and R 2 § Simulate each sample using spice § Determine gain for each sample For each set of tolerance limits, determine yield loss and defect level. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 29

Monte Carlo Simulation Data G = e p o l S R 2 0 0 R 1 Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 30

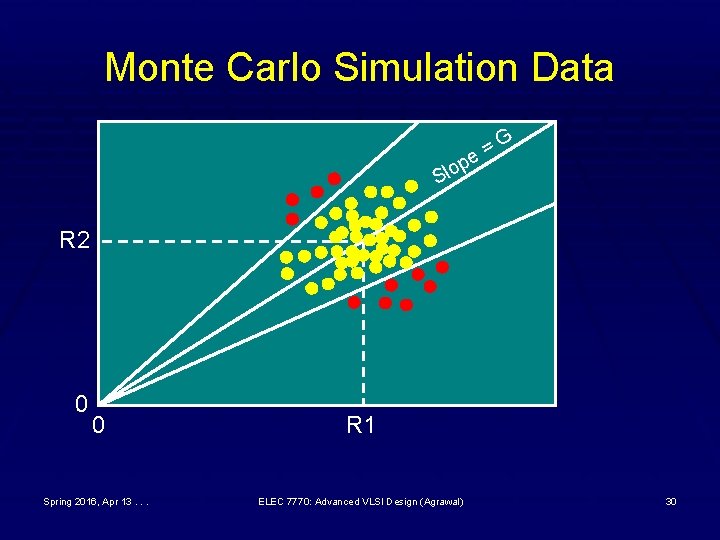

Setting Test Limits G = e Minimize yield loss p o l S R 2 Minimize defect level 0 0 R 1 Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 31

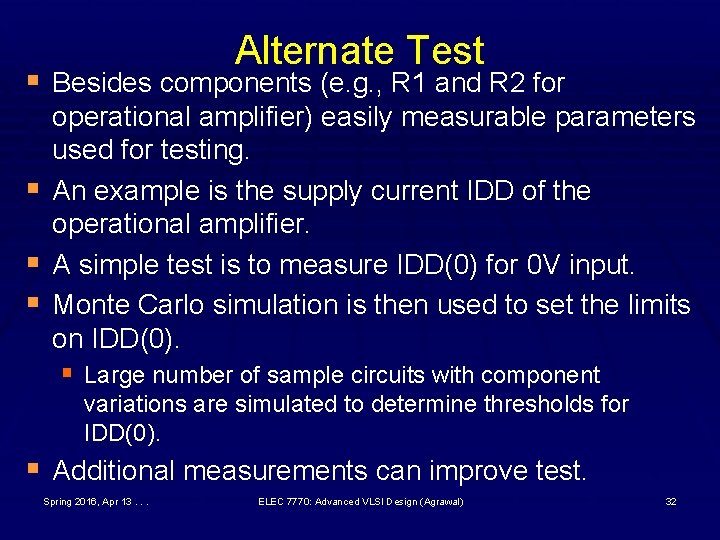

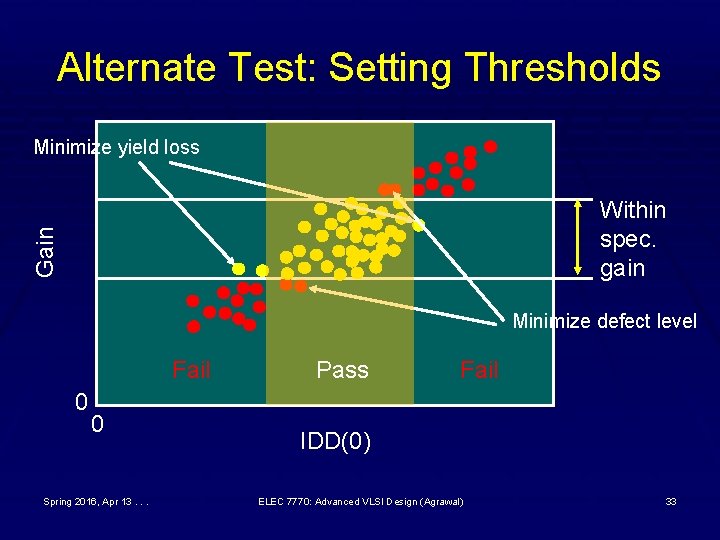

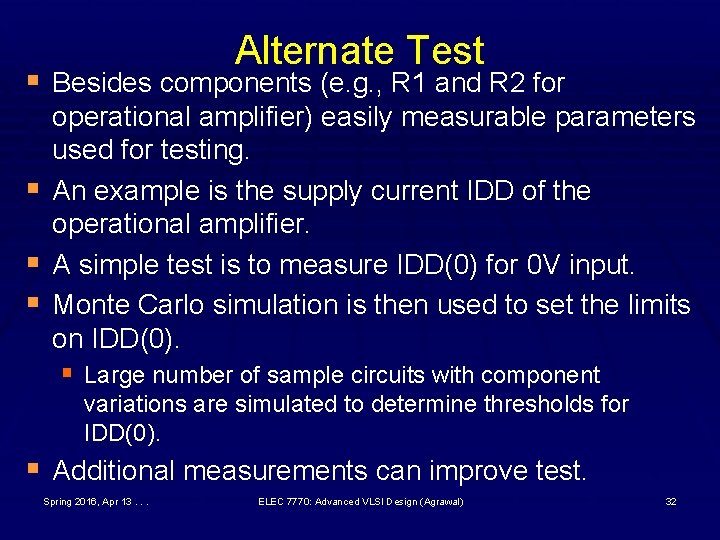

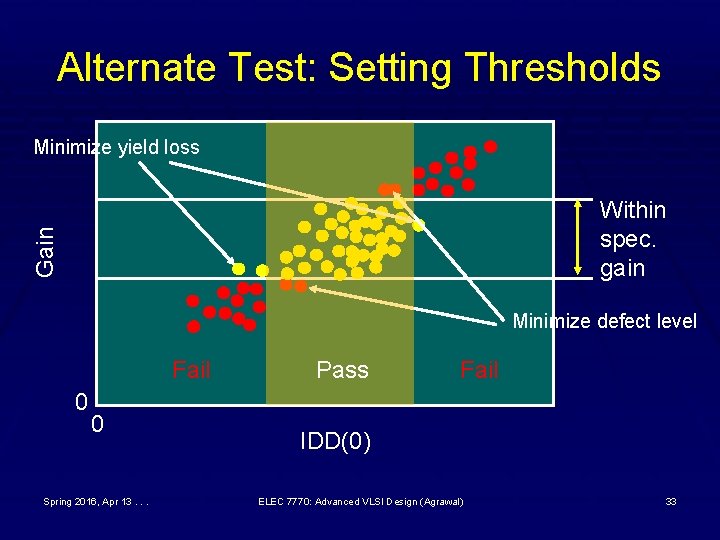

Alternate Test § Besides components (e. g. , R 1 and R 2 for § § § operational amplifier) easily measurable parameters used for testing. An example is the supply current IDD of the operational amplifier. A simple test is to measure IDD(0) for 0 V input. Monte Carlo simulation is then used to set the limits on IDD(0). § Large number of sample circuits with component variations are simulated to determine thresholds for IDD(0). § Additional measurements can improve test. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 32

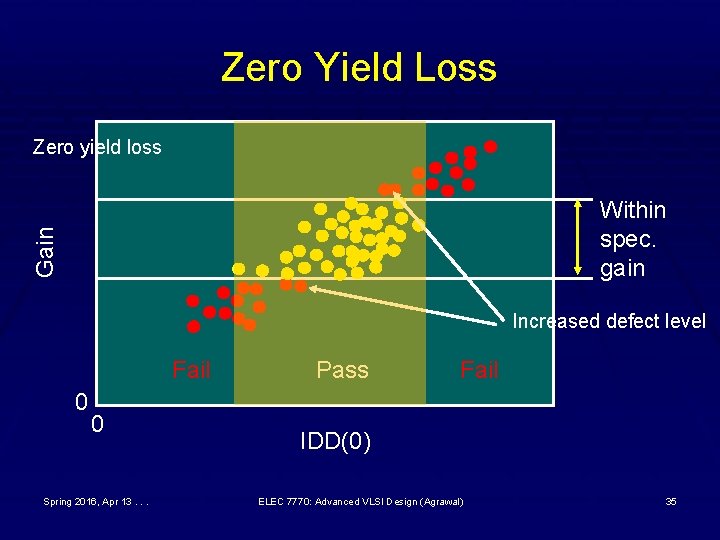

Alternate Test: Setting Thresholds Minimize yield loss Gain Within spec. gain Minimize defect level Fail 0 0 Spring 2016, Apr 13. . . Pass Fail IDD(0) ELEC 7770: Advanced VLSI Design (Agrawal) 33

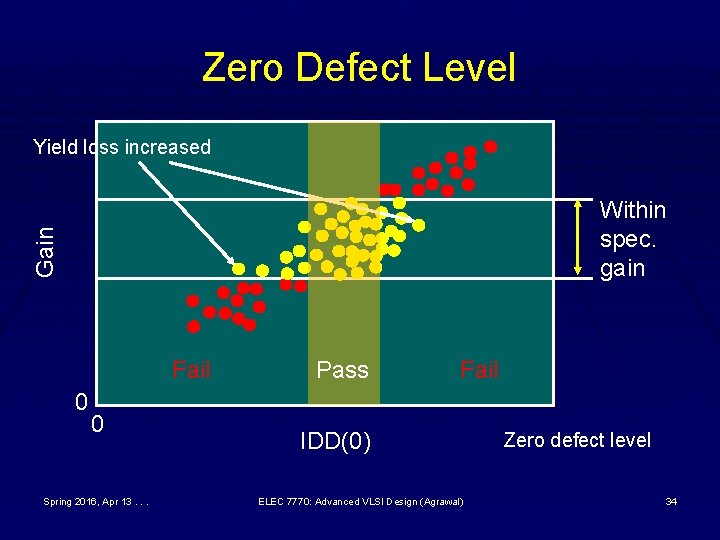

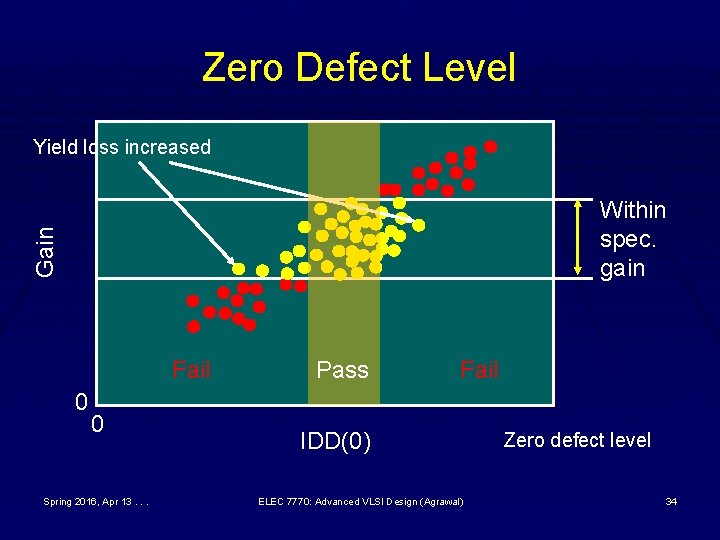

Zero Defect Level Yield loss increased Gain Within spec. gain Fail 0 0 Spring 2016, Apr 13. . . Pass Fail IDD(0) ELEC 7770: Advanced VLSI Design (Agrawal) Zero defect level 34

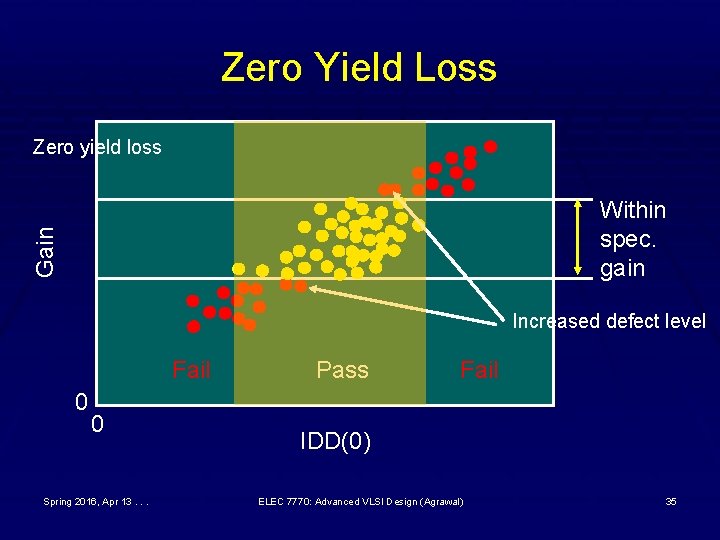

Zero Yield Loss Zero yield loss Gain Within spec. gain Increased defect level Fail 0 0 Spring 2016, Apr 13. . . Pass Fail IDD(0) ELEC 7770: Advanced VLSI Design (Agrawal) 35

References § P. N. Variyam, S. Cherubal and A. Chatterjee, § “Prediction of Analog Performance Parameters Using Fast Transient Testing, ” IEEE Trans. Computer-Aided Design, vol. 21, no. 3, pp. 349361, March 2002. H. -G. Stratigopoulos and Y. Makris, “Error Moderation in Low-Cost Machine-Learning. Based Analog/RF Testing, ” IEEE Trans. Computer-Aided Design, vol. 27, no. 2, pp. 339351, February 2008. Spring 2016, Apr 13. . . ELEC 7770: Advanced VLSI Design (Agrawal) 36