ELEC 7770 Advanced VLSI Design Spring 2008 Timing

- Slides: 34

ELEC 7770 Advanced VLSI Design Spring 2008 Timing Simulation and STA Vishwani D. Agrawal James J. Danaher Professor ECE Department, Auburn University, Auburn, AL 36849 vagrawal@eng. auburn. edu http: //www. eng. auburn. edu/~vagrawal/COURSE/E 7770_Spr 08/course. html Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 1

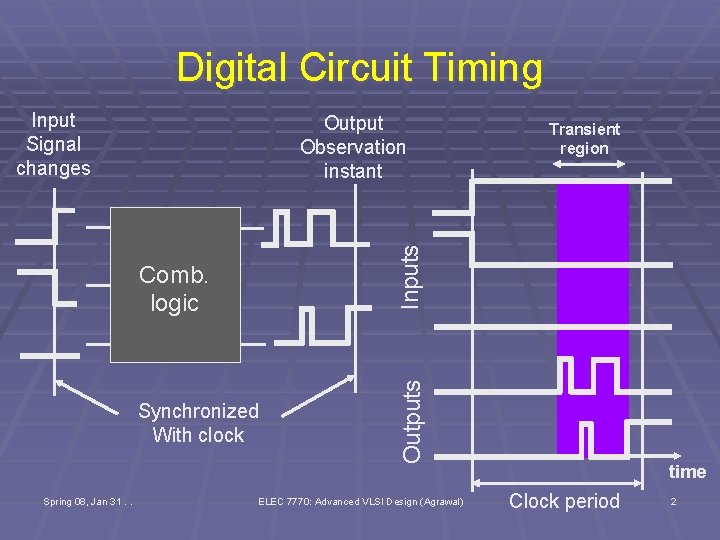

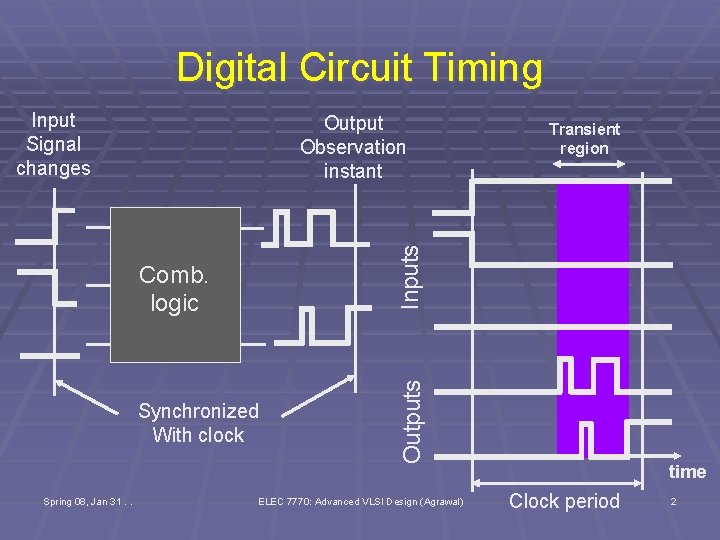

Digital Circuit Timing Input Signal changes Synchronized With clock Outputs Comb. logic Spring 08, Jan 31. . Transient region Inputs Output Observation instant ELEC 7770: Advanced VLSI Design (Agrawal) time Clock period 2

Timing Analysis and Optimization § Timing analysis § Dynamic analysis: Simulation. § Static timing analysis (STA): Vector-less topological analysis of circuit. § Timing optimization § Performance § Clock design § Other forms of design optimization § Chip area § Testability § Power Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 3

Circuit Delays § Switching or inertial delay is the interval between input change and output change of a gate: § Depends on input capacitance, device (transistor) characteristics and output capacitance of gate. § Also depends on input rise or fall times and states of other inputs (second-order effects). § Approximation: fixed rise and fall delays (or min-max delay range, or single fixed delay) for gate output. § Propagation or interconnect delay is the time a transition takes to travel between gates: § Depends on transmission line effects (distributed R, L, C parameters, length and loading) of routing paths. § Approximation: modeled as lumped delays for gate inputs. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 4

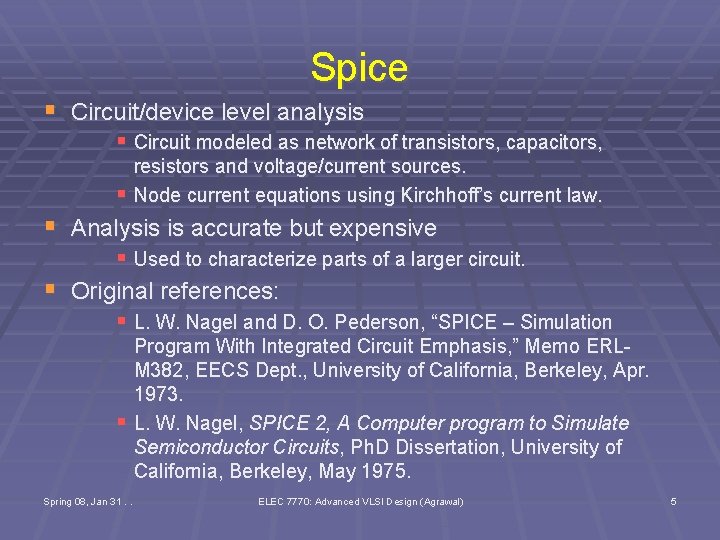

Spice § Circuit/device level analysis § Circuit modeled as network of transistors, capacitors, resistors and voltage/current sources. § Node current equations using Kirchhoff’s current law. § Analysis is accurate but expensive § § Used to characterize parts of a larger circuit. Original references: § L. W. Nagel and D. O. Pederson, “SPICE – Simulation Program With Integrated Circuit Emphasis, ” Memo ERLM 382, EECS Dept. , University of California, Berkeley, Apr. 1973. § L. W. Nagel, SPICE 2, A Computer program to Simulate Semiconductor Circuits, Ph. D Dissertation, University of California, Berkeley, May 1975. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 5

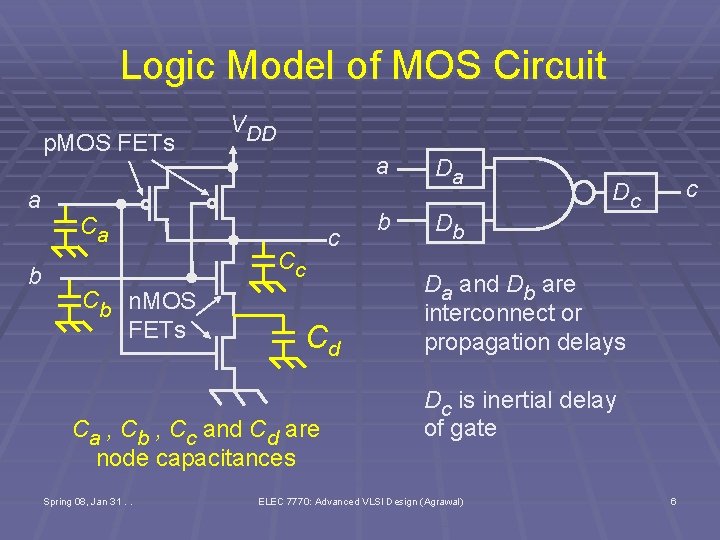

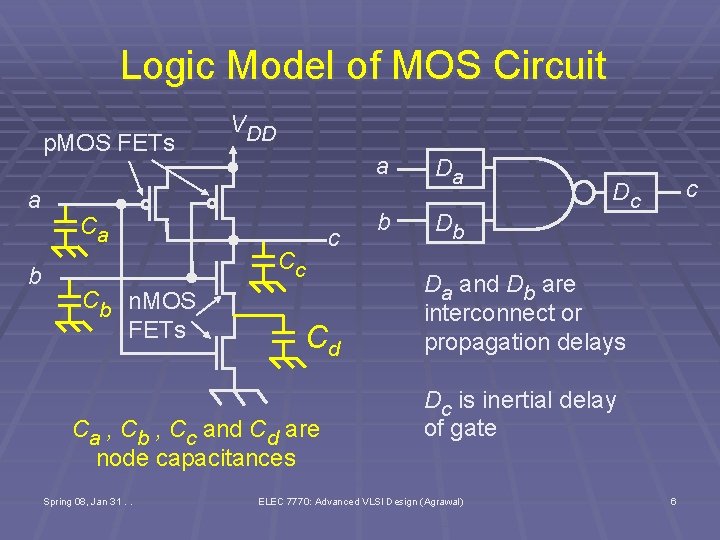

Logic Model of MOS Circuit p. MOS FETs a b VDD Ca Cc Cb n. MOS FETs Cd Ca , Cb , Cc and Cd are node capacitances Spring 08, Jan 31. . c a Da b Db c Dc Da and Db are interconnect or propagation delays Dc is inertial delay of gate ELEC 7770: Advanced VLSI Design (Agrawal) 6

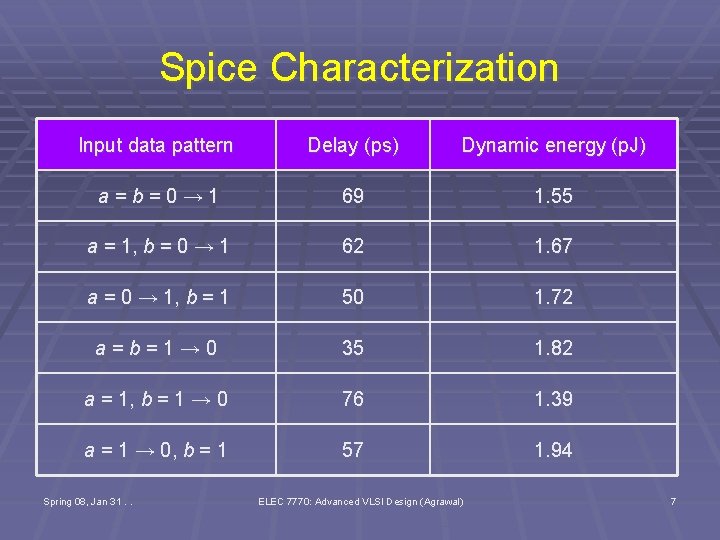

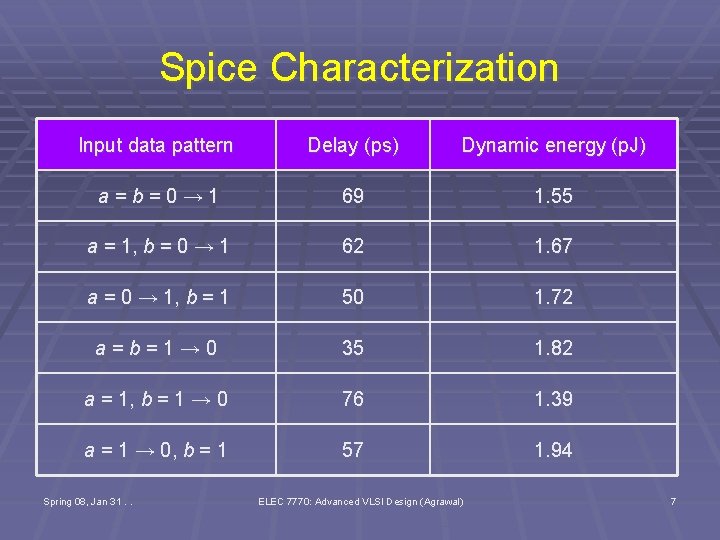

Spice Characterization Input data pattern Delay (ps) Dynamic energy (p. J) a = b = 0 → 1 69 1. 55 a = 1, b = 0 → 1 62 1. 67 a = 0 → 1, b = 1 50 1. 72 a = b = 1 → 0 35 1. 82 a = 1, b = 1 → 0 76 1. 39 a = 1 → 0, b = 1 57 1. 94 Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 7

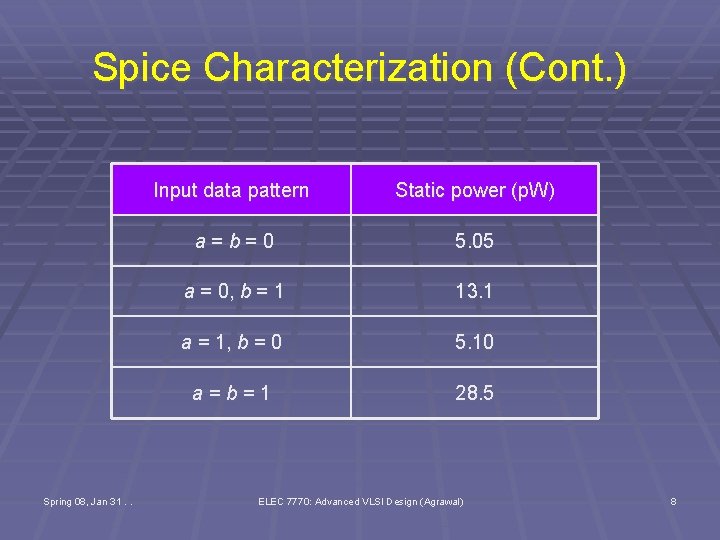

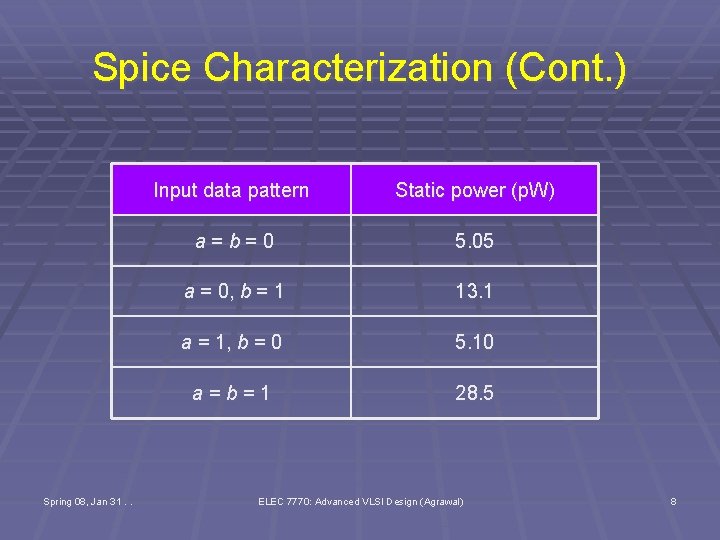

Spice Characterization (Cont. ) Spring 08, Jan 31. . Input data pattern Static power (p. W) a = b = 0 5. 05 a = 0, b = 1 13. 1 a = 1, b = 0 5. 10 a = b = 1 28. 5 ELEC 7770: Advanced VLSI Design (Agrawal) 8

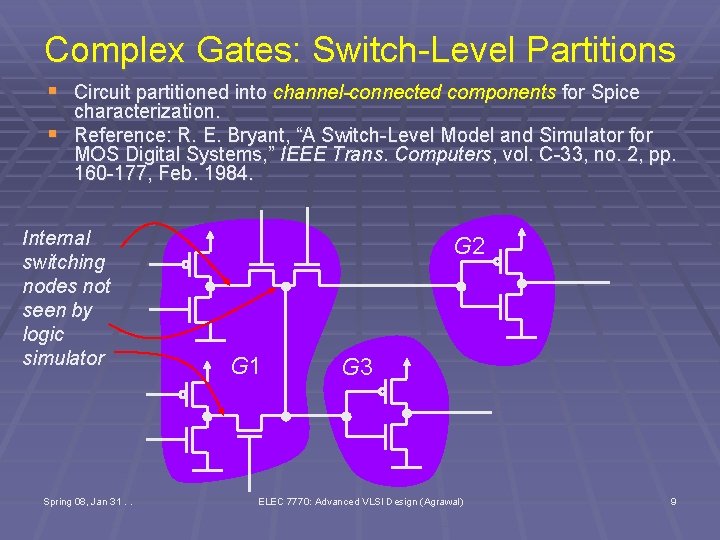

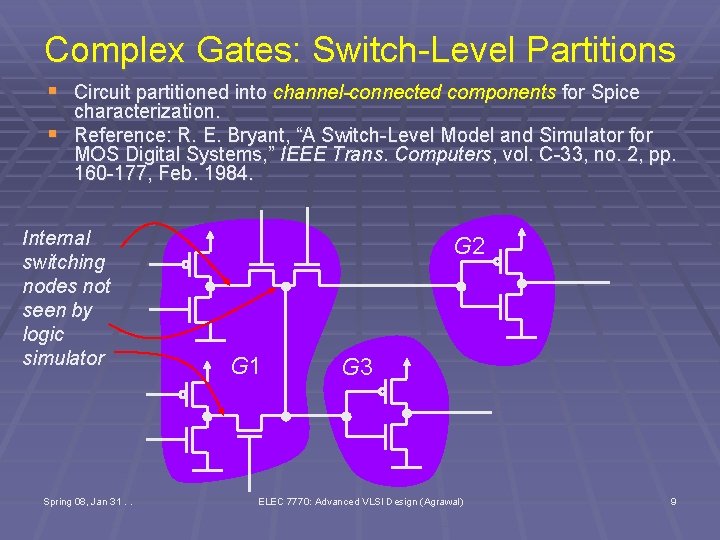

Complex Gates: Switch-Level Partitions § Circuit partitioned into channel-connected components for Spice § characterization. Reference: R. E. Bryant, “A Switch-Level Model and Simulator for MOS Digital Systems, ” IEEE Trans. Computers, vol. C-33, no. 2, pp. 160 -177, Feb. 1984. Internal switching nodes not seen by logic simulator Spring 08, Jan 31. . G 2 G 1 G 3 ELEC 7770: Advanced VLSI Design (Agrawal) 9

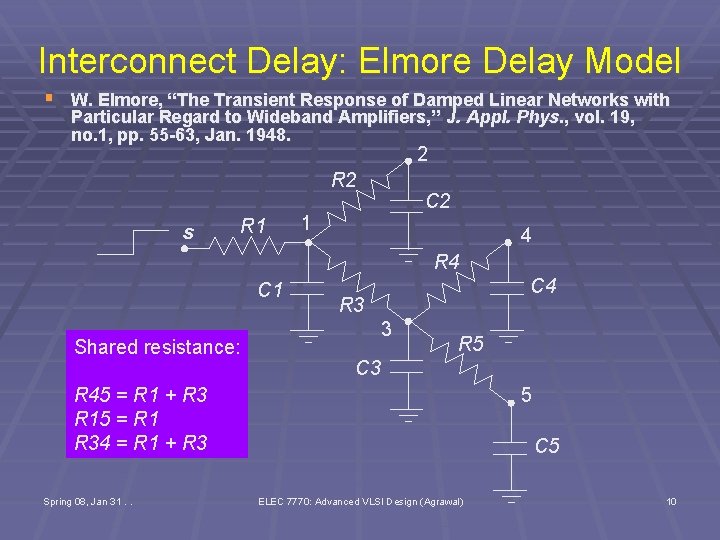

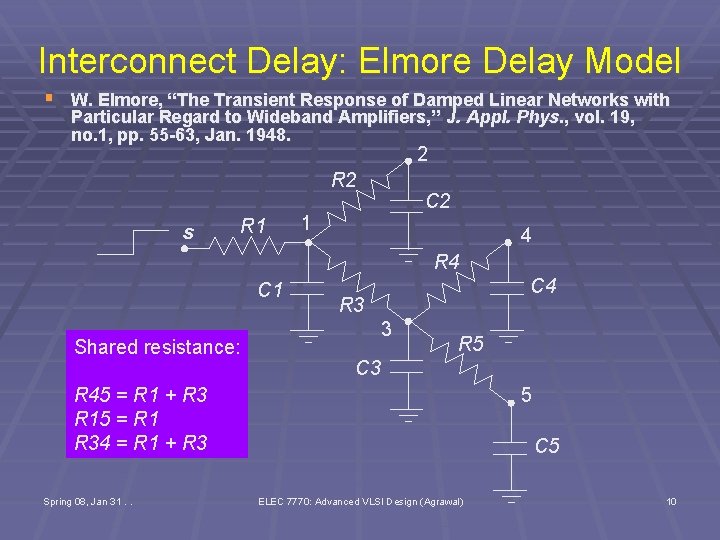

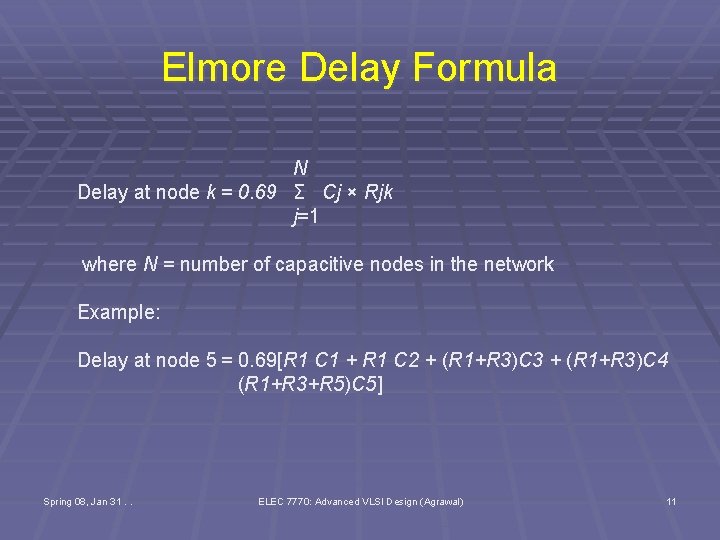

Interconnect Delay: Elmore Delay Model § W. Elmore, “The Transient Response of Damped Linear Networks with Particular Regard to Wideband Amplifiers, ” J. Appl. Phys. , vol. 19, no. 1, pp. 55 -63, Jan. 1948. 2 R 2 s R 1 C 2 1 4 R 4 C 1 Shared resistance: C 4 R 3 3 R 5 C 3 R 45 = R 1 + R 3 R 15 = R 1 R 34 = R 1 + R 3 Spring 08, Jan 31. . 5 C 5 ELEC 7770: Advanced VLSI Design (Agrawal) 10

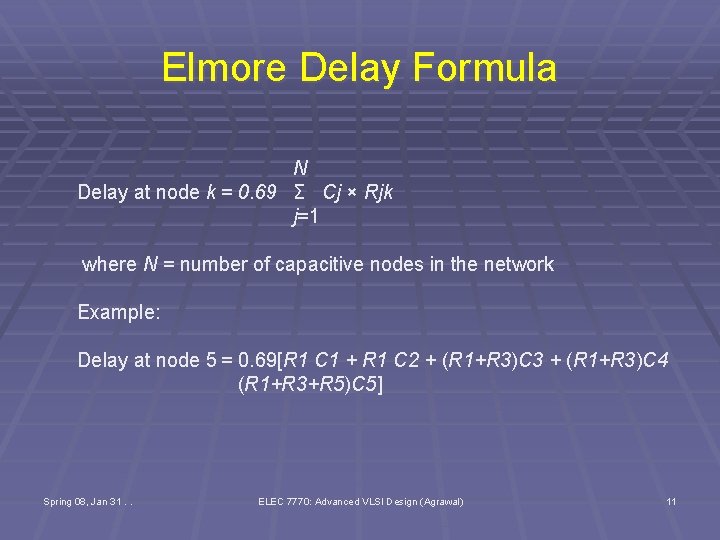

Elmore Delay Formula N Delay at node k = 0. 69 Σ Cj × Rjk j=1 where N = number of capacitive nodes in the network Example: Delay at node 5 = 0. 69[R 1 C 1 + R 1 C 2 + (R 1+R 3)C 3 + (R 1+R 3)C 4 (R 1+R 3+R 5)C 5] Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 11

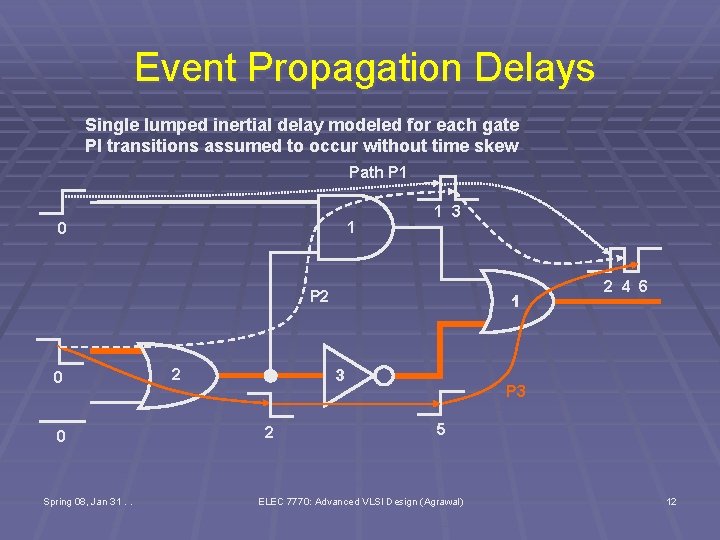

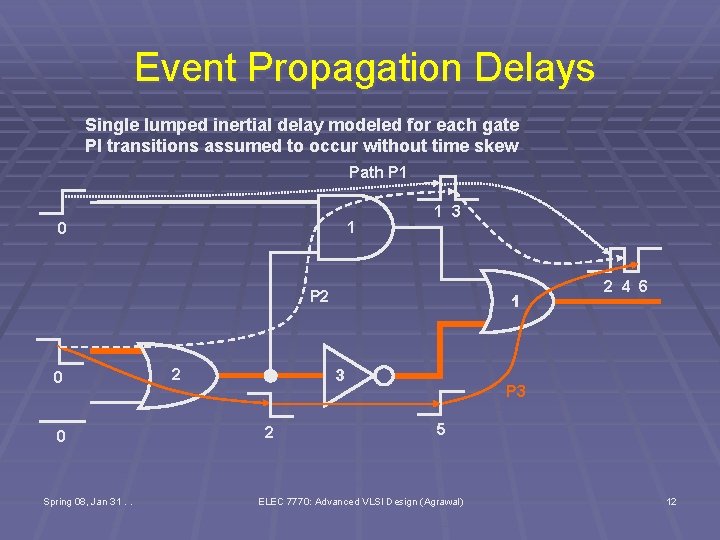

Event Propagation Delays Single lumped inertial delay modeled for each gate PI transitions assumed to occur without time skew Path P 1 1 0 1 3 P 2 0 0 Spring 08, Jan 31. . 1 3 2 2 2 4 6 P 3 5 ELEC 7770: Advanced VLSI Design (Agrawal) 12

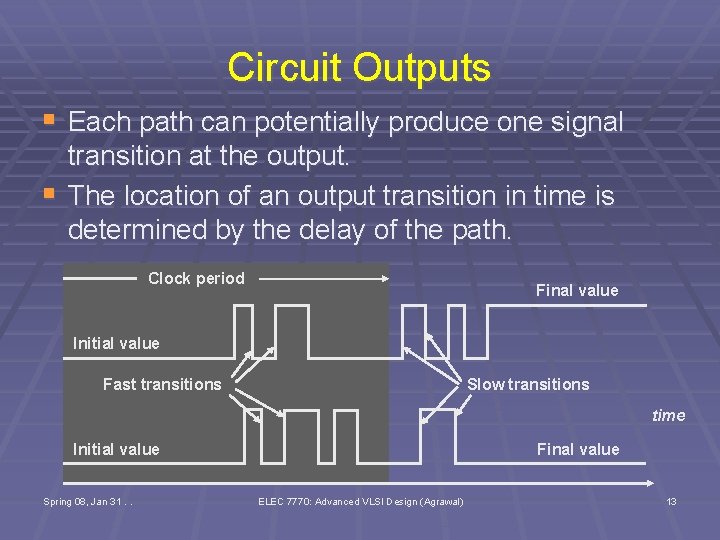

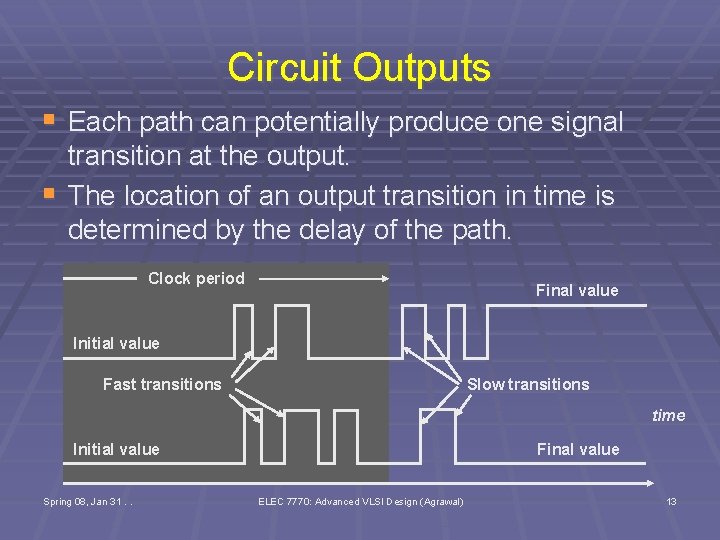

Circuit Outputs § Each path can potentially produce one signal § transition at the output. The location of an output transition in time is determined by the delay of the path. Clock period Final value Initial value Slow transitions Fast transitions time Initial value Spring 08, Jan 31. . Final value ELEC 7770: Advanced VLSI Design (Agrawal) 13

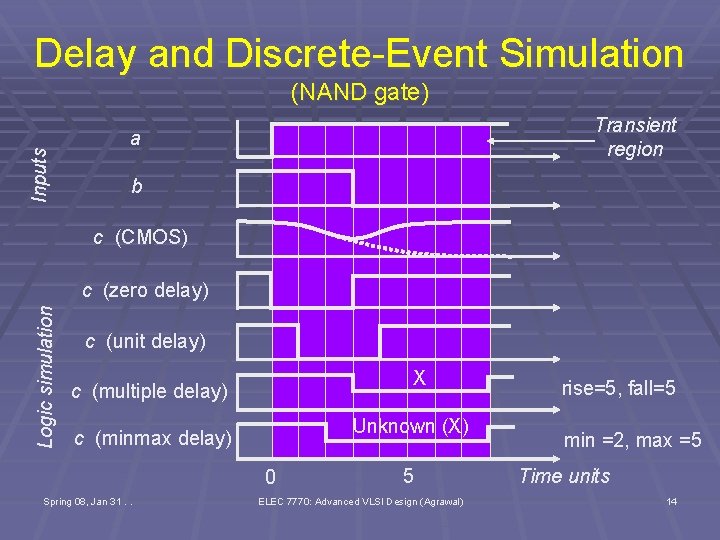

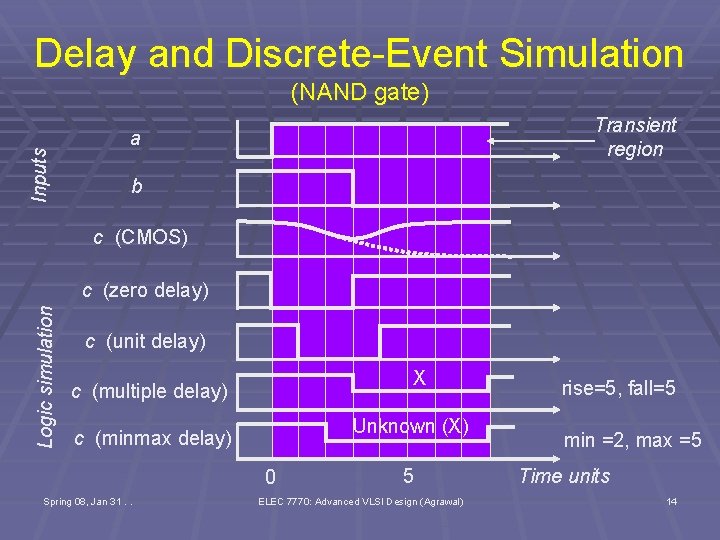

Delay and Discrete-Event Simulation Inputs (NAND gate) Transient region a b c (CMOS) Logic simulation c (zero delay) c (unit delay) X c (multiple delay) Unknown (X) c (minmax delay) 0 Spring 08, Jan 31. . 5 ELEC 7770: Advanced VLSI Design (Agrawal) rise=5, fall=5 min =2, max =5 Time units 14

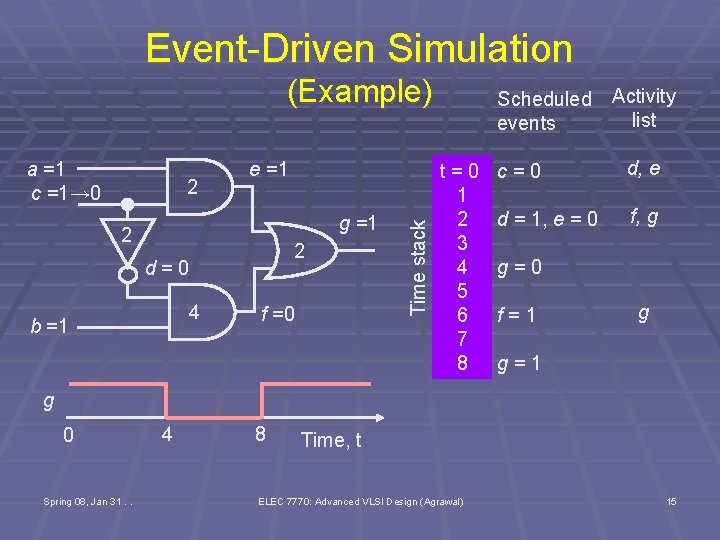

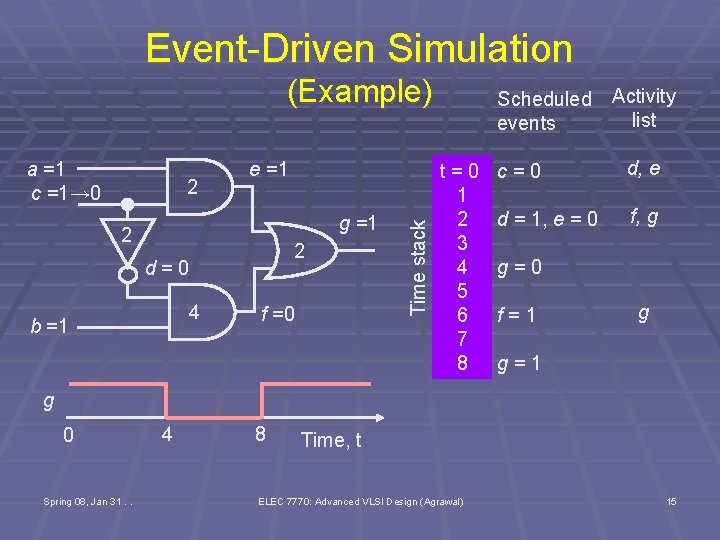

Event-Driven Simulation (Example) 2 e =1 g =1 2 2 d = 0 4 b =1 f =0 Time stack a =1 c =1→ 0 Scheduled events t = 0 1 2 3 4 5 6 7 8 Activity list c = 0 d, e d = 1, e = 0 f, g g = 0 f = 1 g g = 1 g 0 Spring 08, Jan 31. . 4 8 Time, t ELEC 7770: Advanced VLSI Design (Agrawal) 15

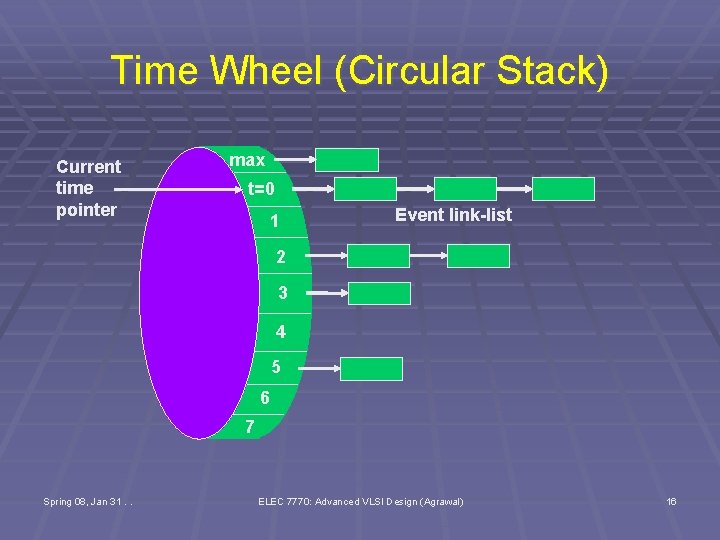

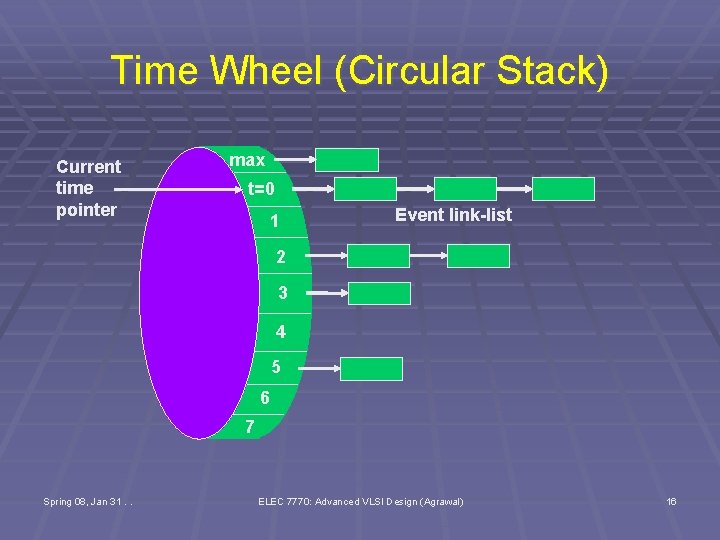

Time Wheel (Circular Stack) Current time pointer max t=0 1 Event link-list 2 3 4 5 6 7 Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 16

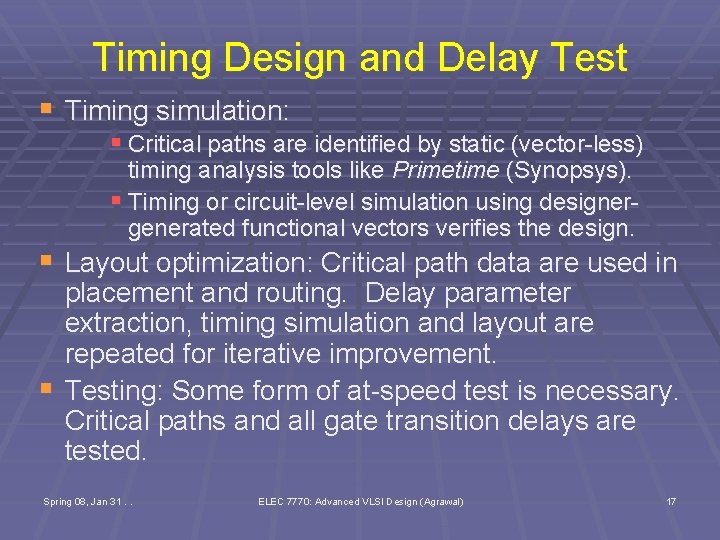

Timing Design and Delay Test § Timing simulation: § Critical paths are identified by static (vector-less) timing analysis tools like Primetime (Synopsys). § Timing or circuit-level simulation using designergenerated functional vectors verifies the design. § Layout optimization: Critical path data are used in § placement and routing. Delay parameter extraction, timing simulation and layout are repeated for iterative improvement. Testing: Some form of at-speed test is necessary. Critical paths and all gate transition delays are tested. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 17

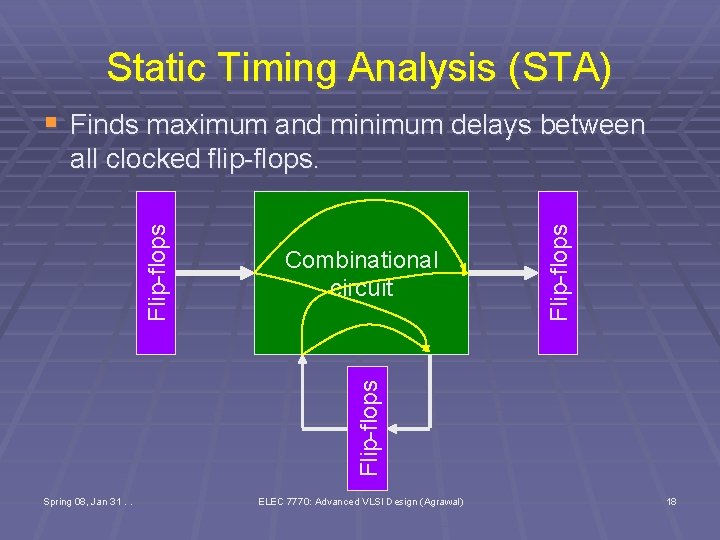

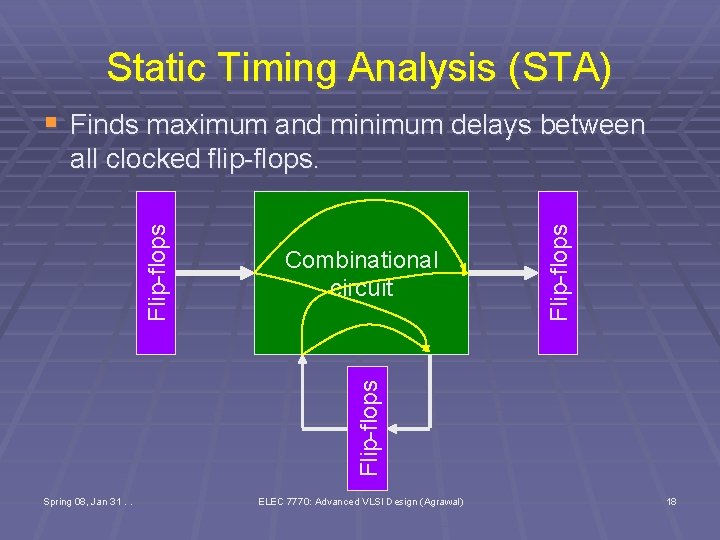

Static Timing Analysis (STA) § Finds maximum and minimum delays between Flip-flops Combinational circuit Flip-flops all clocked flip-flops. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 18

Early References § T. I. Kirkpatrick and N. R. Clark, “PERT as an § § Aid to Logic Design, ” IBM J. Res. Dev. , vol. 10, no. 2, pp. 135 -141, March 1966. R. B. Hitchcock, Sr. , “Timing Verification and the Timing Analysis Program, ” Proc. 19 th Design Automation Conf. , 1982, pp. 594 -604. V. D. Agrawal, “Synchronous Path Analysis in MOS Circuit Simulator, ” Proc. 19 th Design Automation Conf. , 1982, pp. 629 -635. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 19

Basic Ideas § Adopted from project management § Frederick W. Taylor (1856 -1915) § Henry Gantt (1861 -1919) § PERT – Program Evaluation and Review Technique § CPM – Critical Path Method Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 20

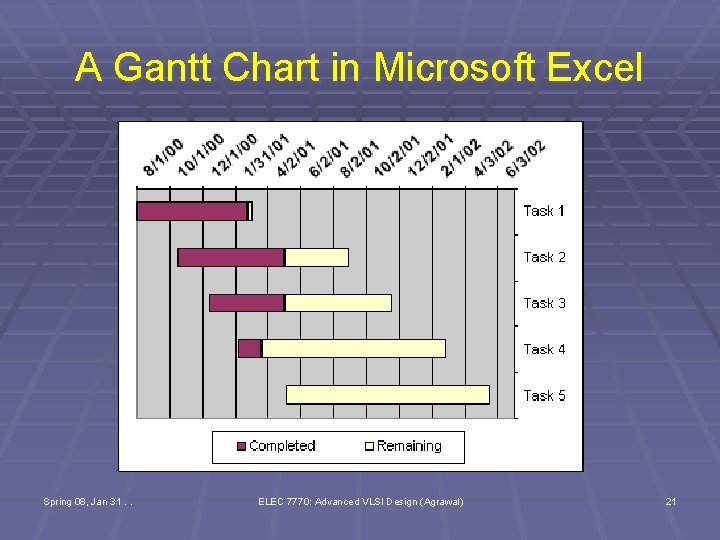

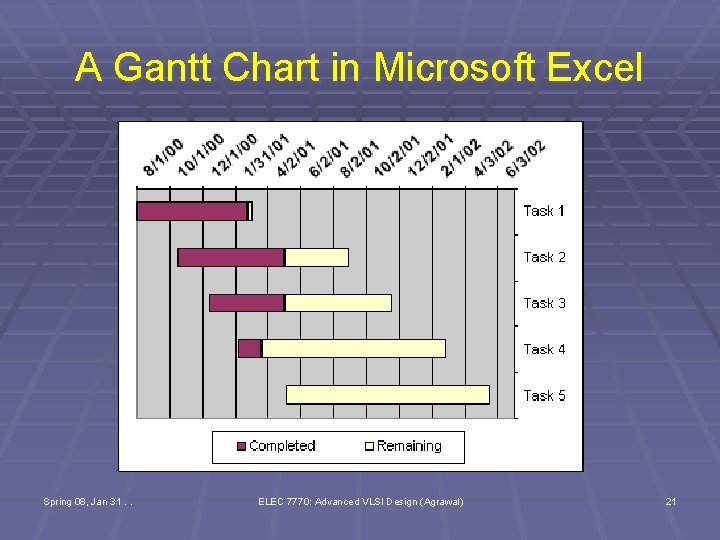

A Gantt Chart in Microsoft Excel Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 21

Using a Gantt Chart § Track progress of subtasks and project. § Assess resource needs as a function of time. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 22

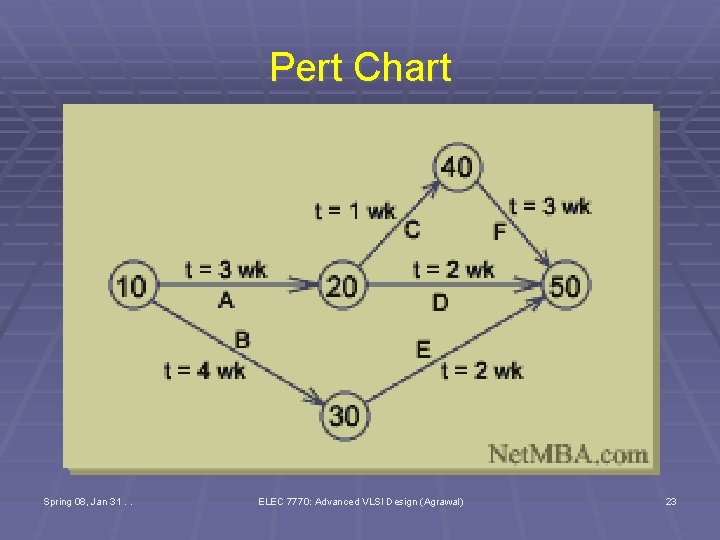

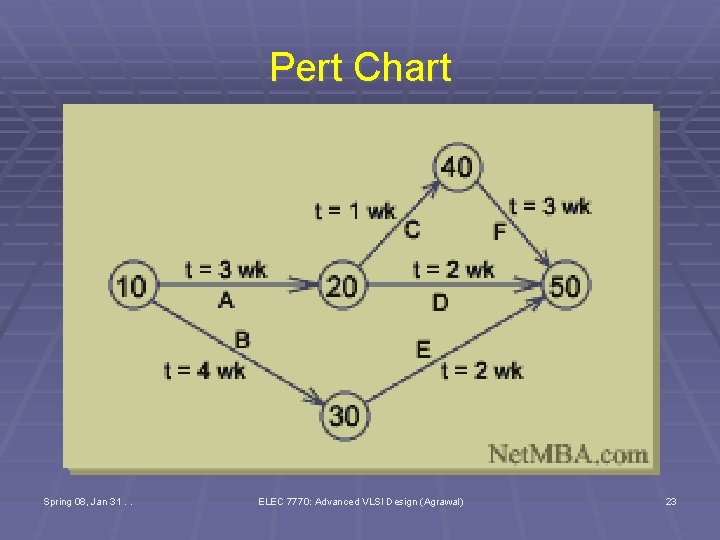

Pert Chart Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 23

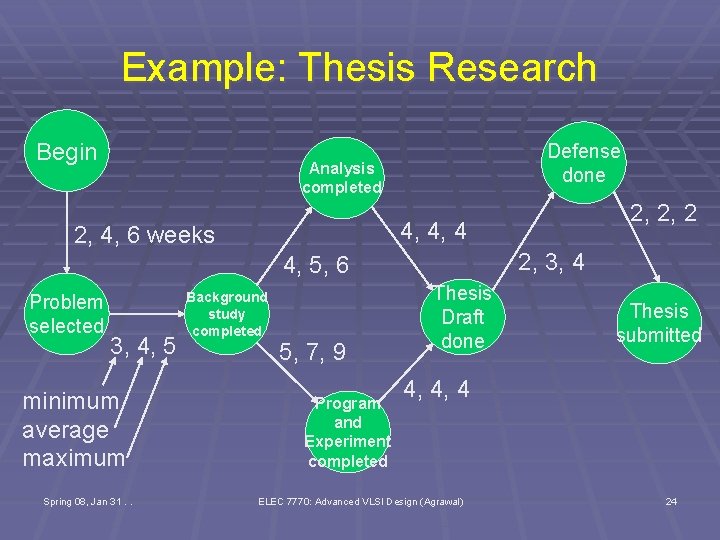

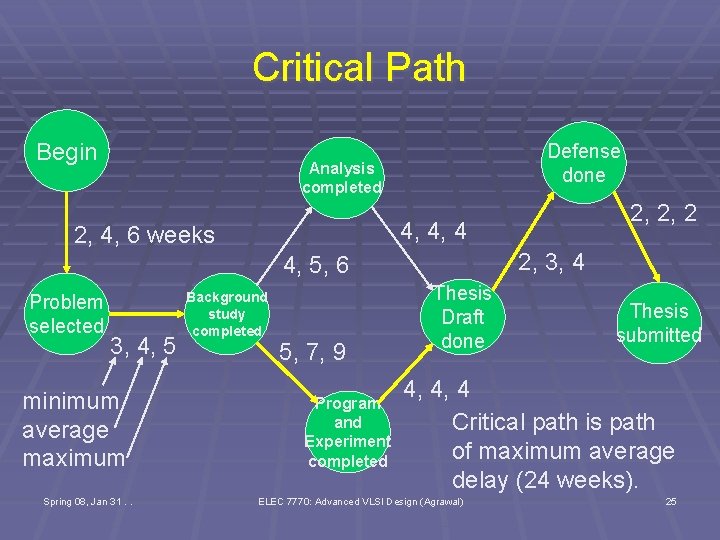

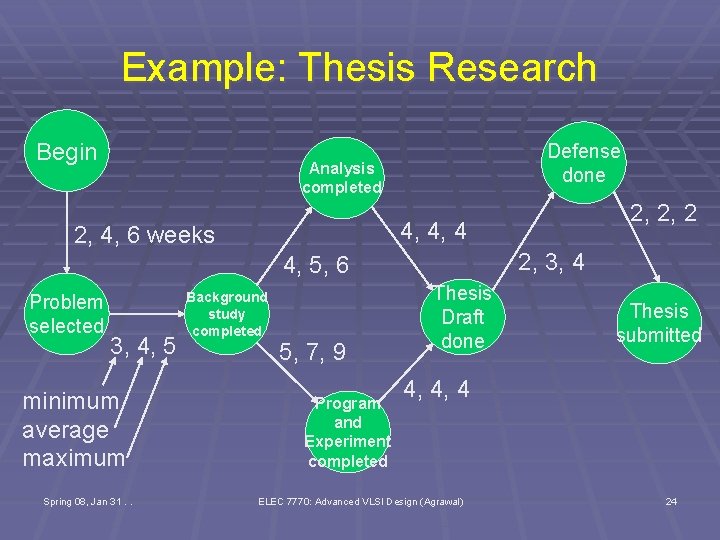

Example: Thesis Research Begin Defense done Analysis completed 4, 4, 4 2, 4, 6 weeks 2, 3, 4 4, 5, 6 Problem selected 3, 4, 5 minimum average maximum Spring 08, Jan 31. . 2, 2, 2 Background study completed 5, 7, 9 Program and Experiment completed Thesis Draft done Thesis submitted 4, 4, 4 ELEC 7770: Advanced VLSI Design (Agrawal) 24

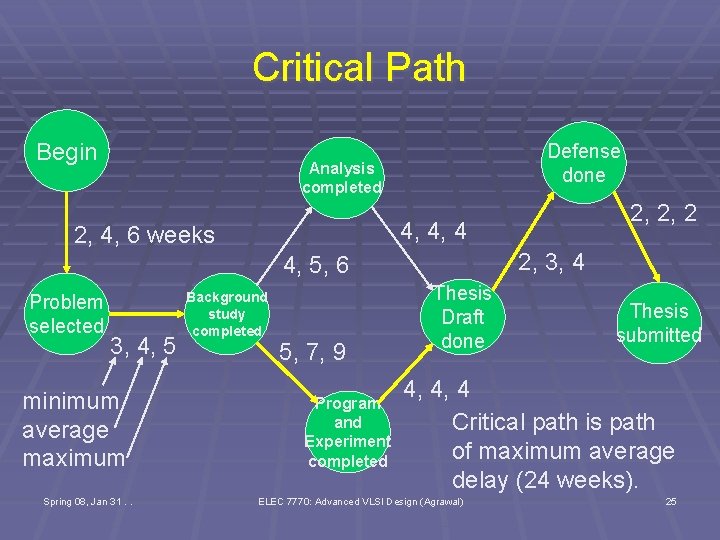

Critical Path Begin Defense done Analysis completed 4, 4, 4 2, 4, 6 weeks 2, 3, 4 4, 5, 6 Problem selected 3, 4, 5 minimum average maximum Spring 08, Jan 31. . 2, 2, 2 Background study completed 5, 7, 9 Program and Experiment completed Thesis Draft done Thesis submitted 4, 4, 4 Critical path is path of maximum average delay (24 weeks). ELEC 7770: Advanced VLSI Design (Agrawal) 25

A Basic Timing Analysis Algorithm § Combinational logic. § Circuit represented as an acyclic directed graph § (DAG). Gates characterized by delays. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 26

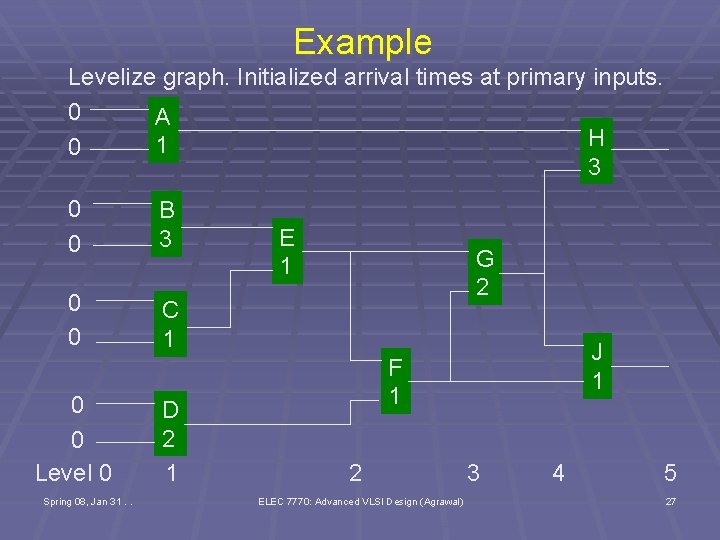

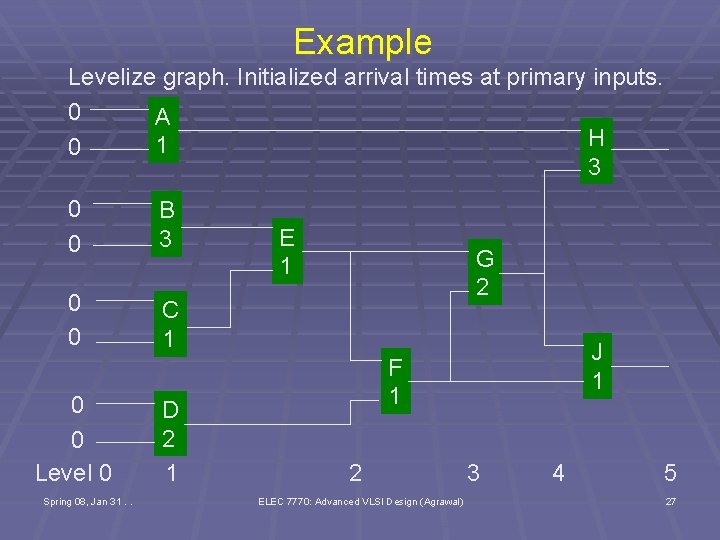

Example Levelize graph. Initialized arrival times at primary inputs. 0 A H 1 0 3 0 0 B 3 0 0 C 1 0 D 2 0 Level 0 1 Spring 08, Jan 31. . E 1 G 2 J 1 F 1 2 ELEC 7770: Advanced VLSI Design (Agrawal) 3 4 5 27

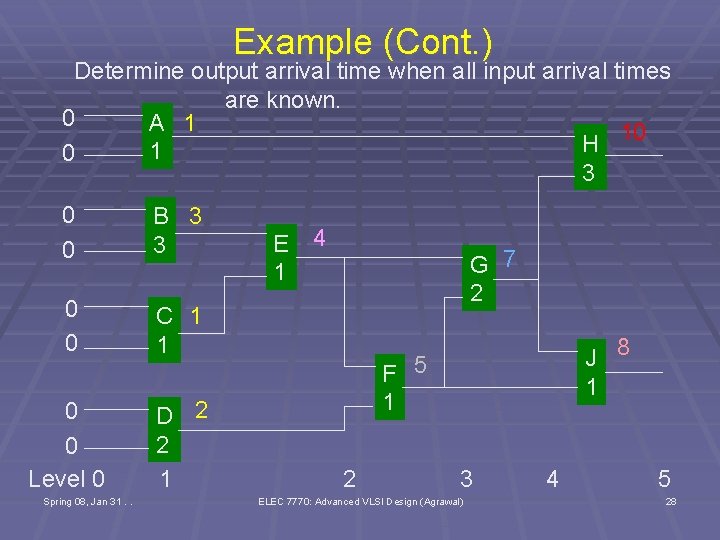

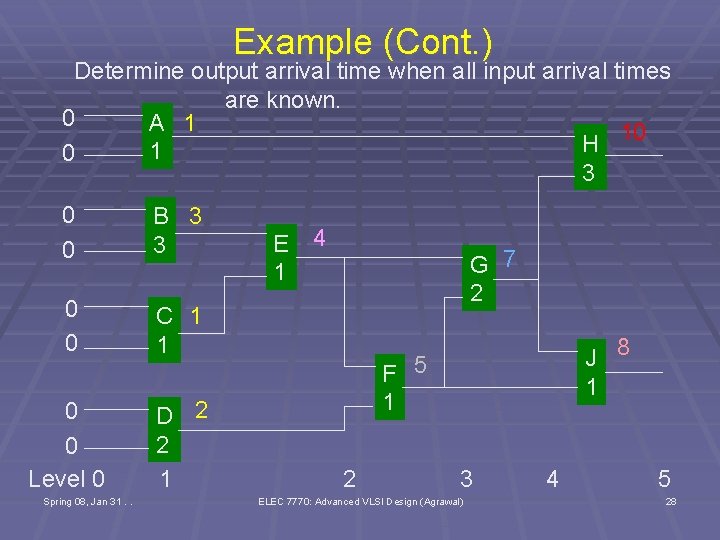

Example (Cont. ) Determine output arrival time when all input arrival times are known. 0 A 1 10 H 1 0 3 0 0 B 3 3 0 0 C 1 1 0 D 2 2 0 Level 0 1 Spring 08, Jan 31. . E 4 1 G 7 2 J 8 1 F 5 1 2 3 ELEC 7770: Advanced VLSI Design (Agrawal) 4 5 28

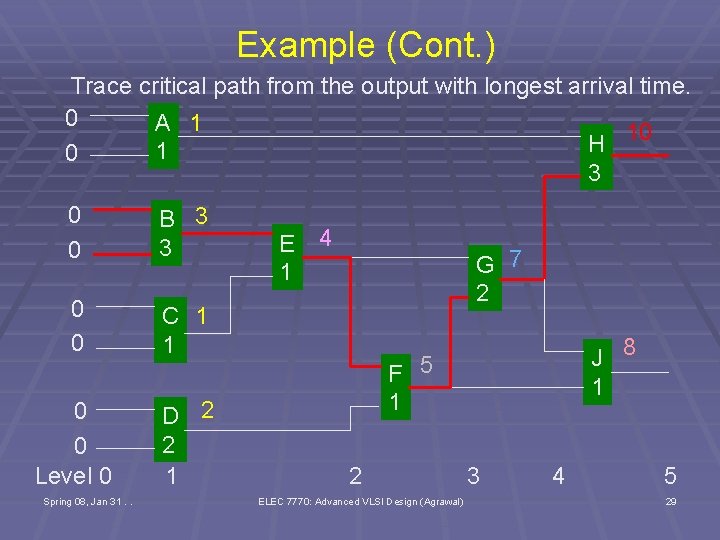

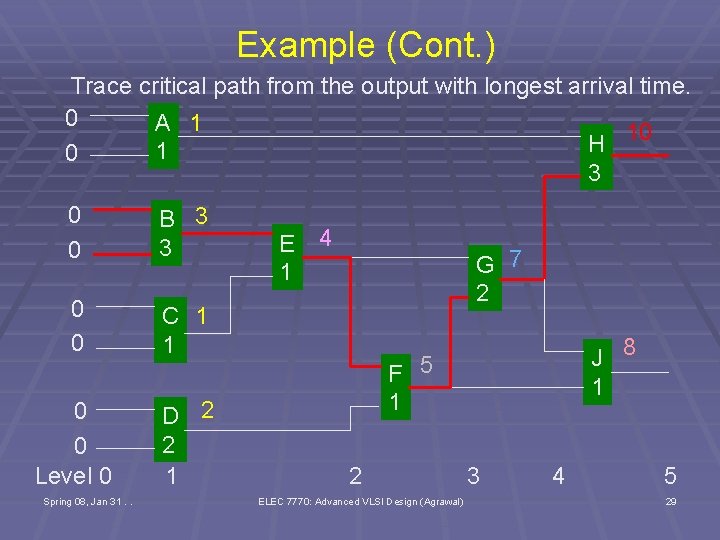

Example (Cont. ) Trace critical path from the output with longest arrival time. 0 A 1 10 H 1 0 3 0 0 B 3 3 0 0 C 1 1 0 D 2 2 0 Level 0 1 Spring 08, Jan 31. . E 4 1 G 7 2 J 8 1 F 5 1 2 ELEC 7770: Advanced VLSI Design (Agrawal) 3 4 5 29

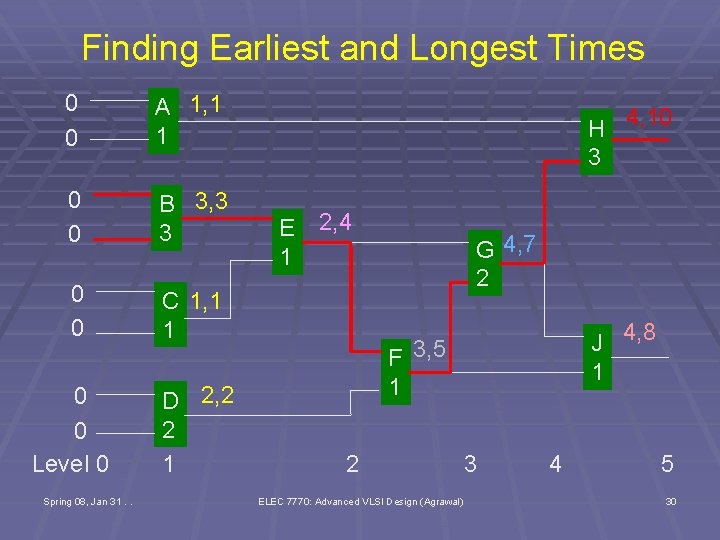

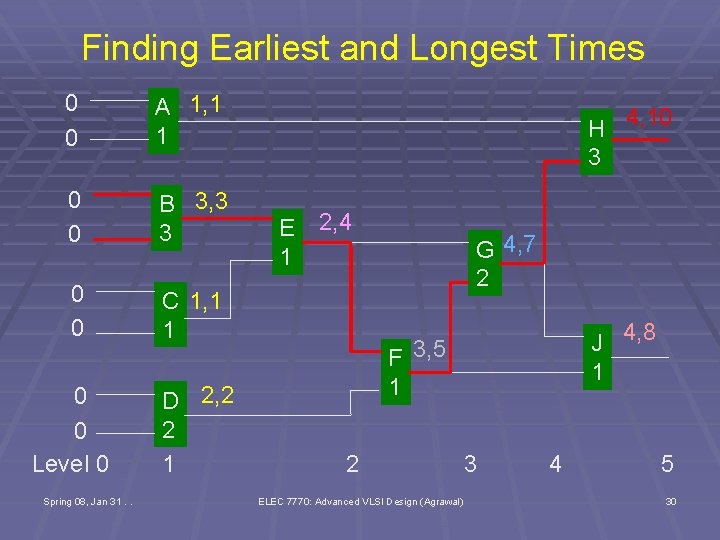

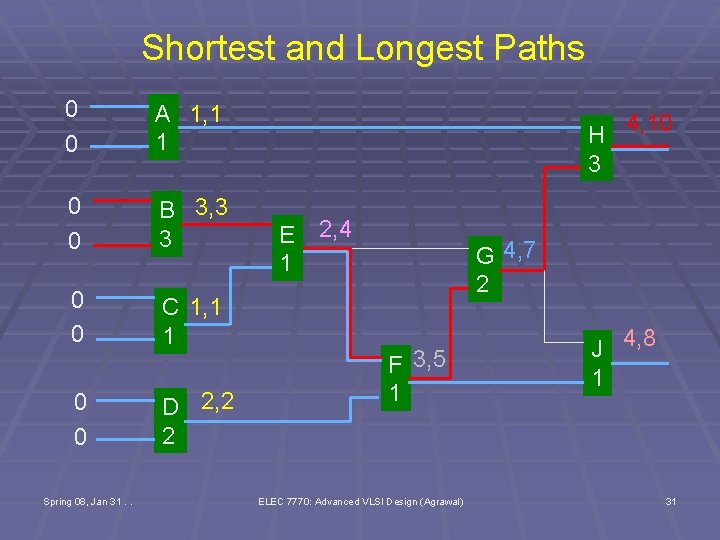

Finding Earliest and Longest Times 0 0 A 1, 1 1 0 0 B 3, 3 3 0 0 C 1, 1 1 0 D 2, 2 2 0 Level 0 1 Spring 08, Jan 31. . H 4, 10 3 E 2, 4 1 G 4, 7 2 J 4, 8 1 F 3, 5 1 2 ELEC 7770: Advanced VLSI Design (Agrawal) 3 4 5 30

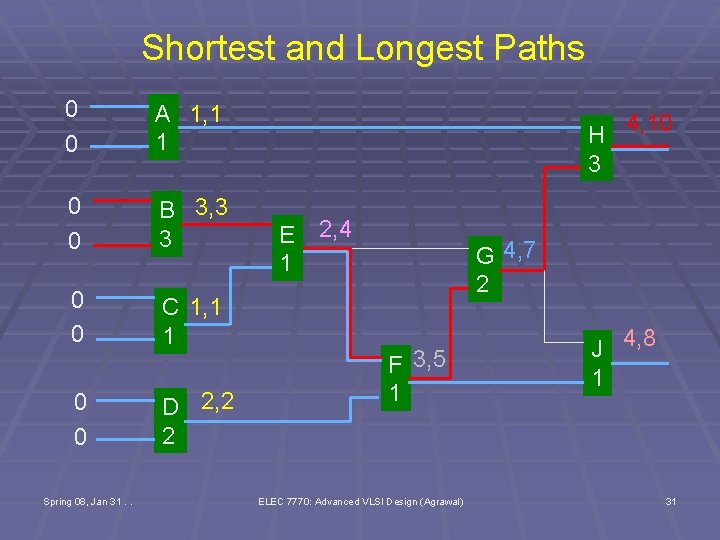

Shortest and Longest Paths 0 0 A 1, 1 1 0 0 B 3, 3 3 0 0 C 1, 1 1 0 0 D 2, 2 2 Spring 08, Jan 31. . H 4, 10 3 E 2, 4 1 G 4, 7 2 F 3, 5 1 ELEC 7770: Advanced VLSI Design (Agrawal) J 4, 8 1 31

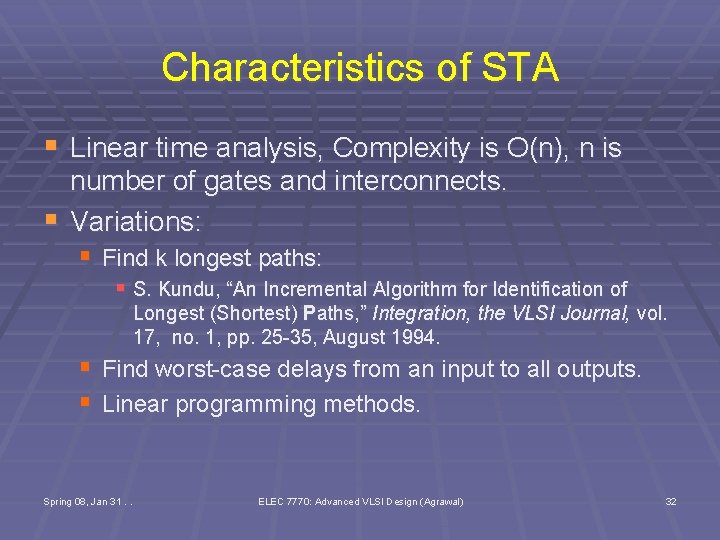

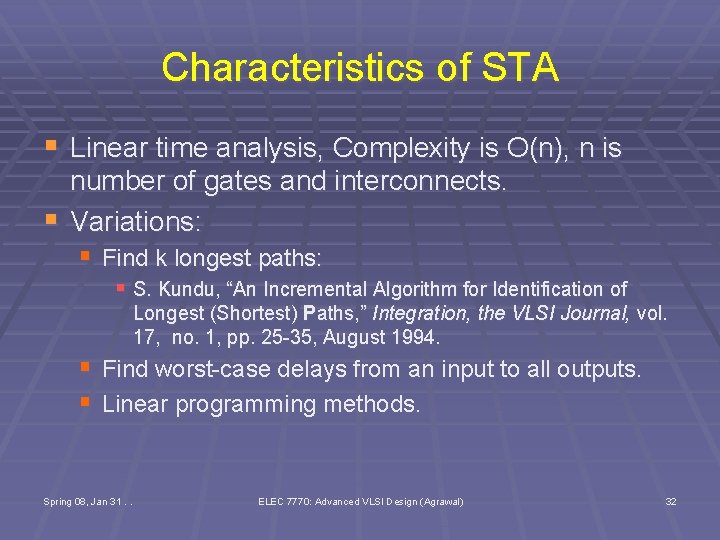

Characteristics of STA § Linear time analysis, Complexity is O(n), n is § number of gates and interconnects. Variations: § Find k longest paths: § S. Kundu, “An Incremental Algorithm for Identification of Longest (Shortest) Paths, ” Integration, the VLSI Journal, vol. 17, no. 1, pp. 25 -35, August 1994. § Find worst-case delays from an input to all outputs. § Linear programming methods. Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 32

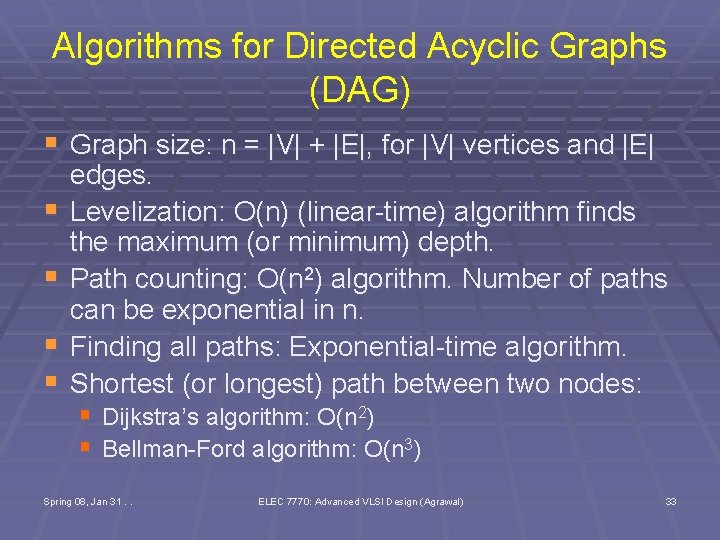

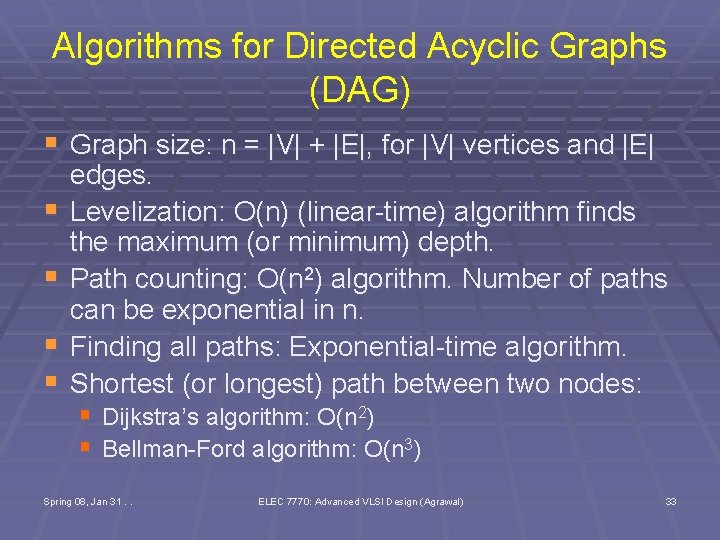

Algorithms for Directed Acyclic Graphs (DAG) § Graph size: n = |V| + |E|, for |V| vertices and |E| § § edges. Levelization: O(n) (linear-time) algorithm finds the maximum (or minimum) depth. Path counting: O(n 2) algorithm. Number of paths can be exponential in n. Finding all paths: Exponential-time algorithm. Shortest (or longest) path between two nodes: § Dijkstra’s algorithm: O(n 2) § Bellman-Ford algorithm: O(n 3) Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 33

References § Delay modeling, simulation and testing: § M. L. Bushnell and V. D. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits, Springer, 2000. § Analysis and Design: § G. De Micheli, Synthesis and Optimization of Digital Circuits, § Mc. Graw-Hill, 1994. N. Maheshwari and S. S. Sapatnekar, Timing Analysis and Optimization of Sequential Circuits, Springer, 1999. § Prime. Time (Static timing analysis tool): § H. Bhatnagar, Advanced ASIC Chip Synthesis, Second Edition, Springer, 2002 Spring 08, Jan 31. . ELEC 7770: Advanced VLSI Design (Agrawal) 34