DIPLOMADO EN SISTEMAS DIGITALES USO DE LOS PERIFERICOS

- Slides: 50

DIPLOMADO EN SISTEMAS DIGITALES USO DE LOS PERIFERICOS DEL SISTEMA DE DESARROLLO SPARTAN 3 E Instructor: MC. Rodrigo Lucio Maya Ramírez

Uso del LCD

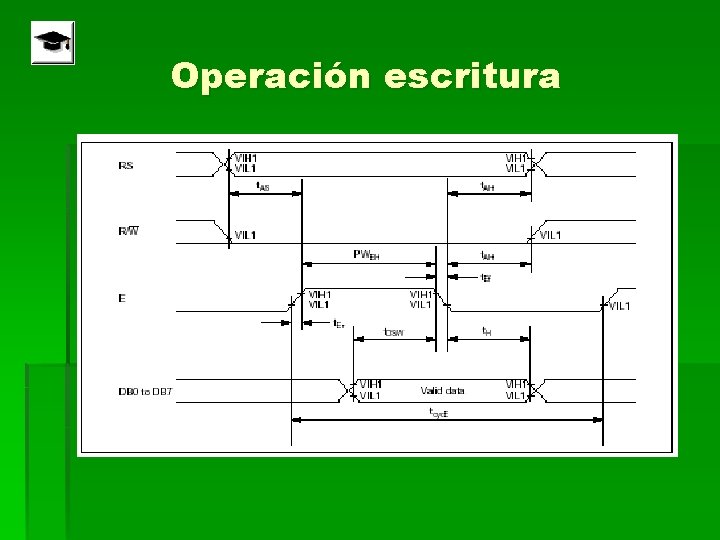

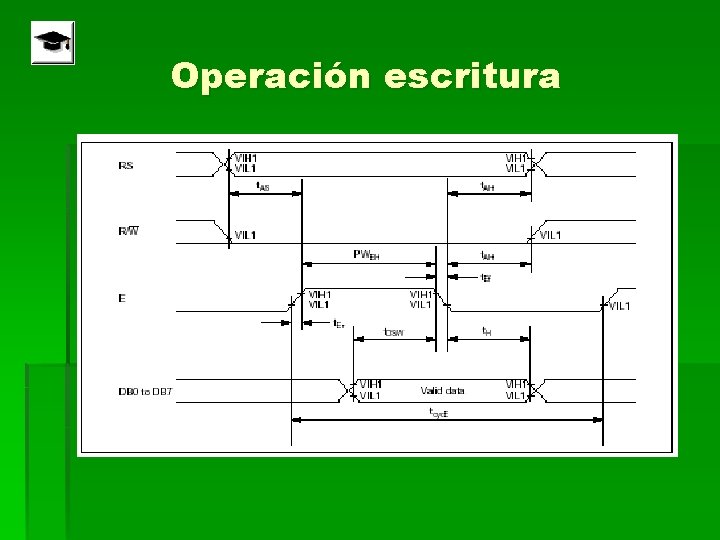

Operación escritura

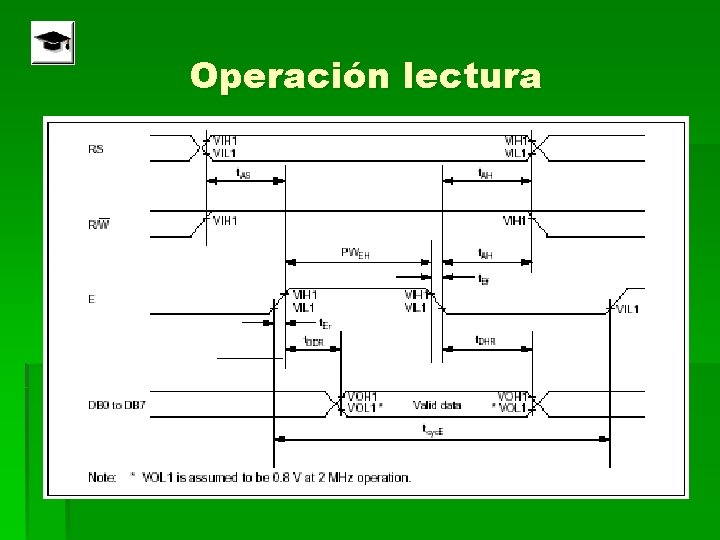

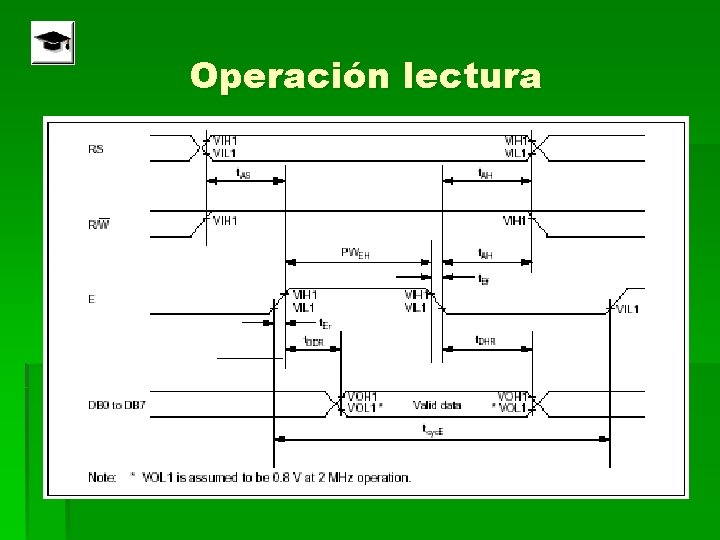

Operación lectura

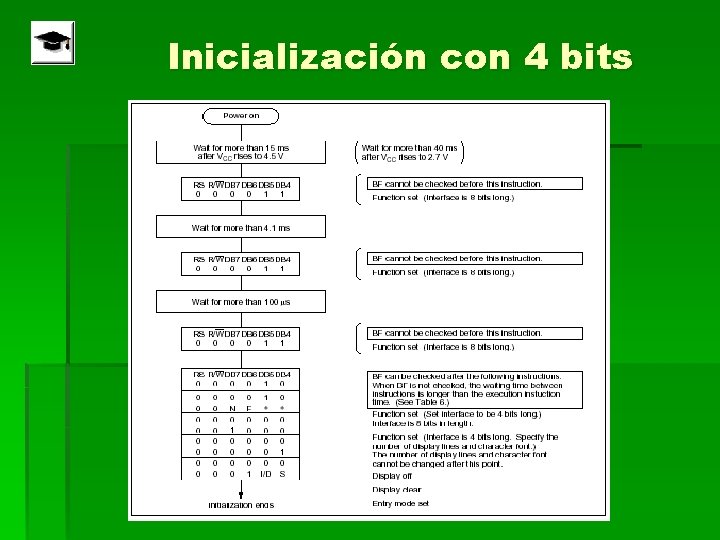

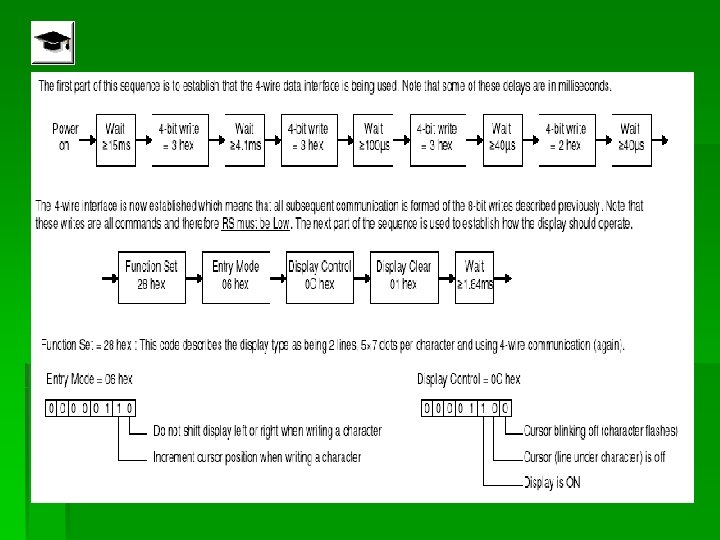

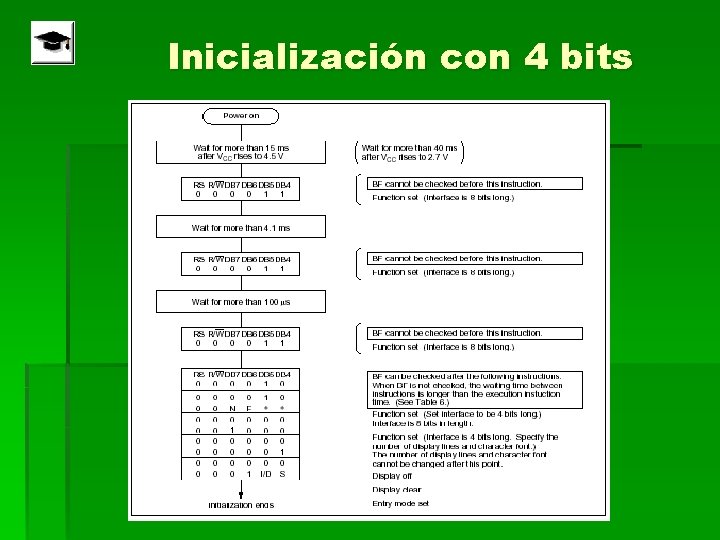

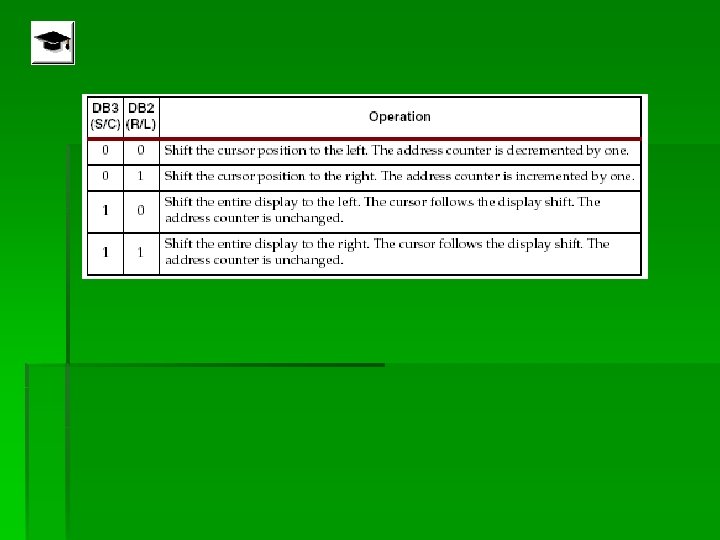

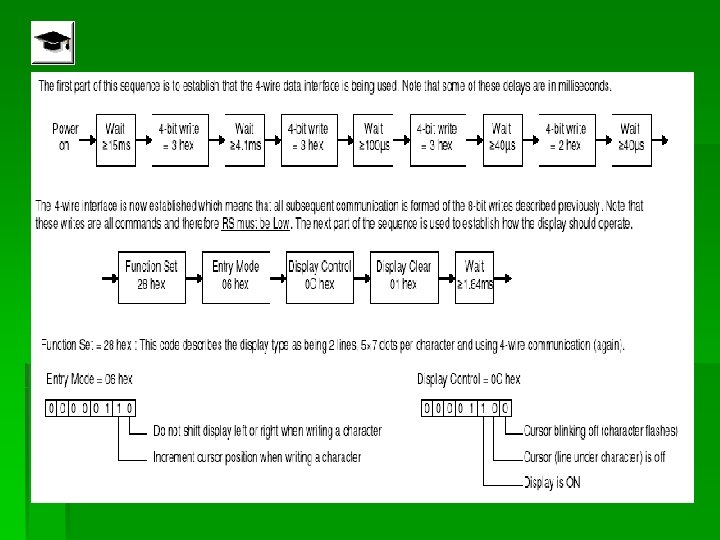

Inicialización con 4 bits

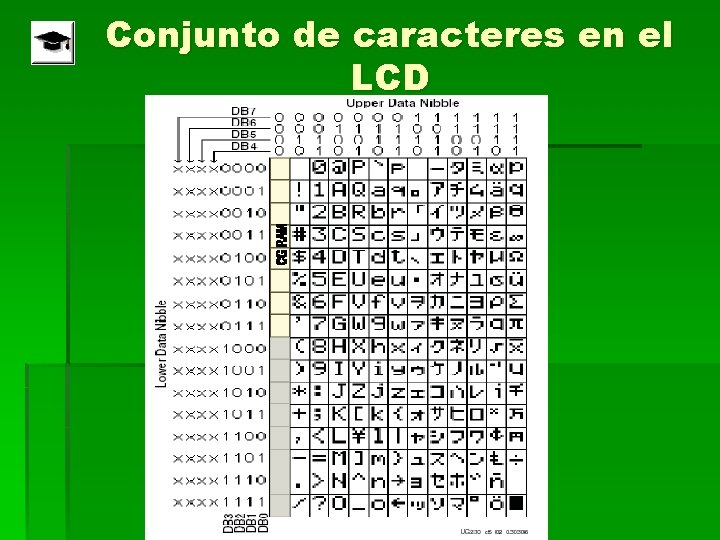

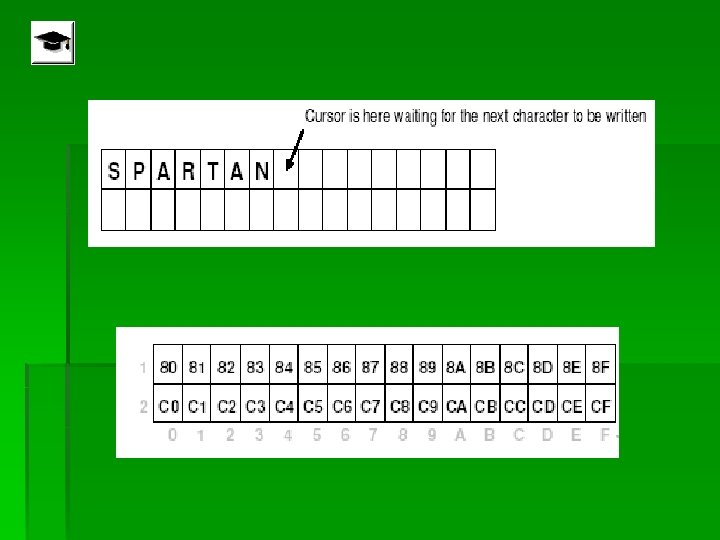

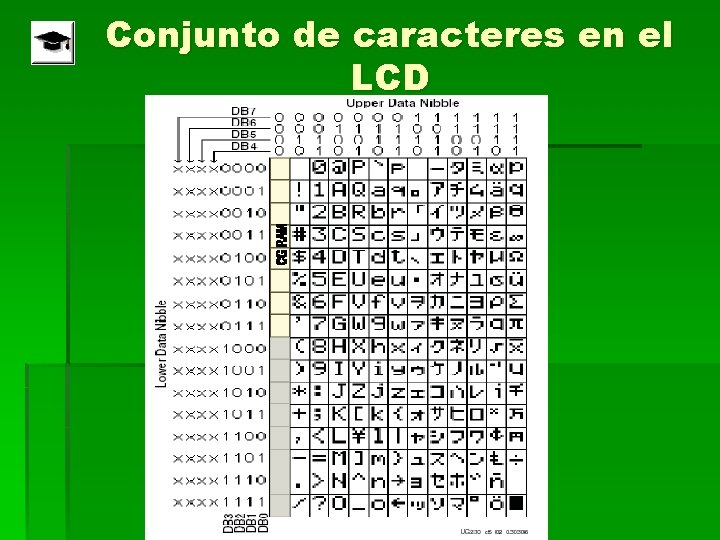

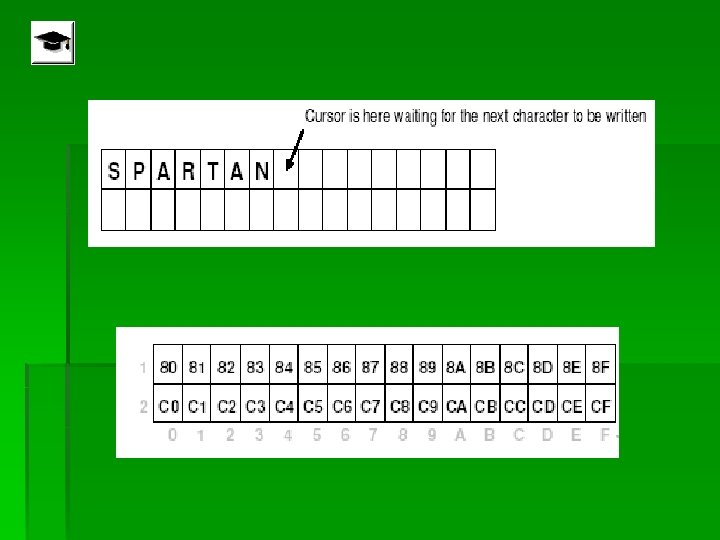

Conjunto de caracteres en el LCD

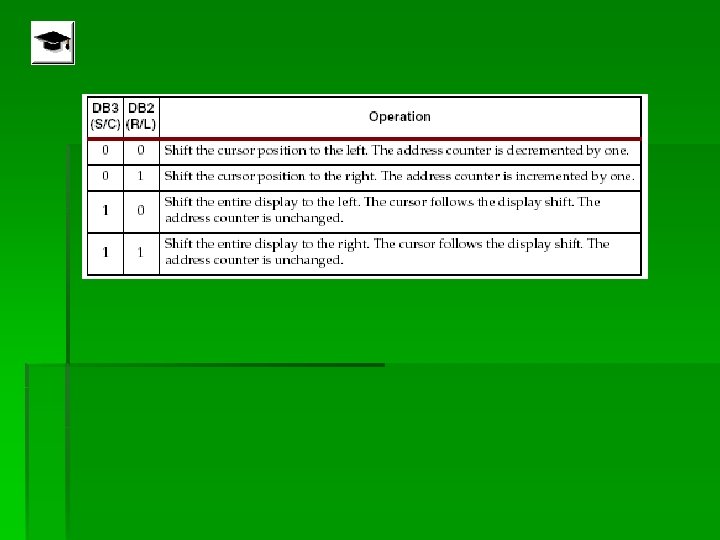

Conjunto de comandos

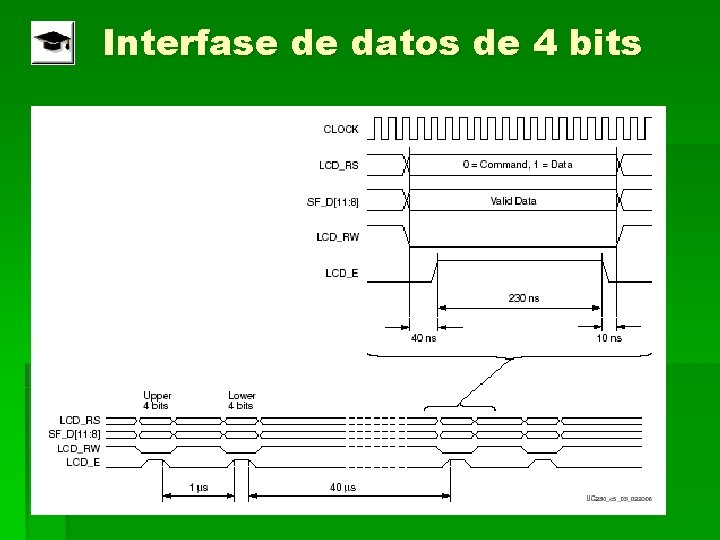

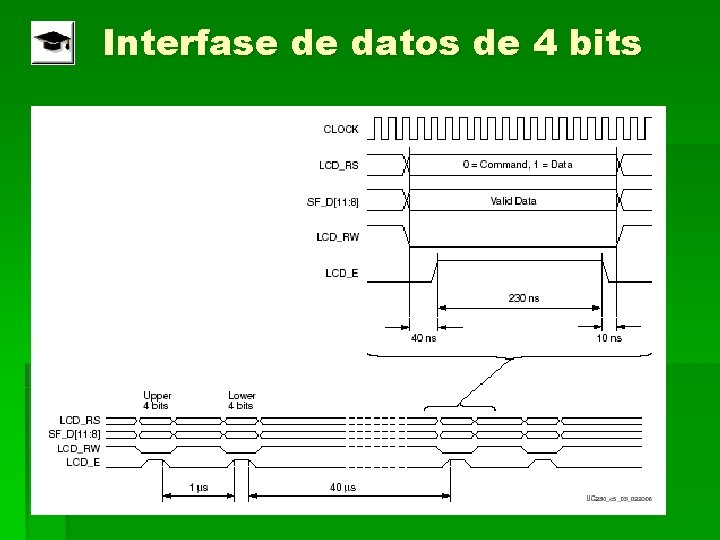

Interfase de datos de 4 bits

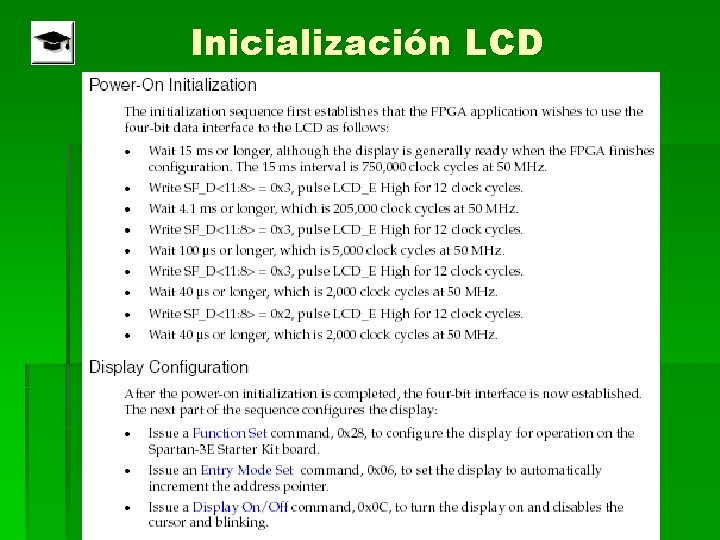

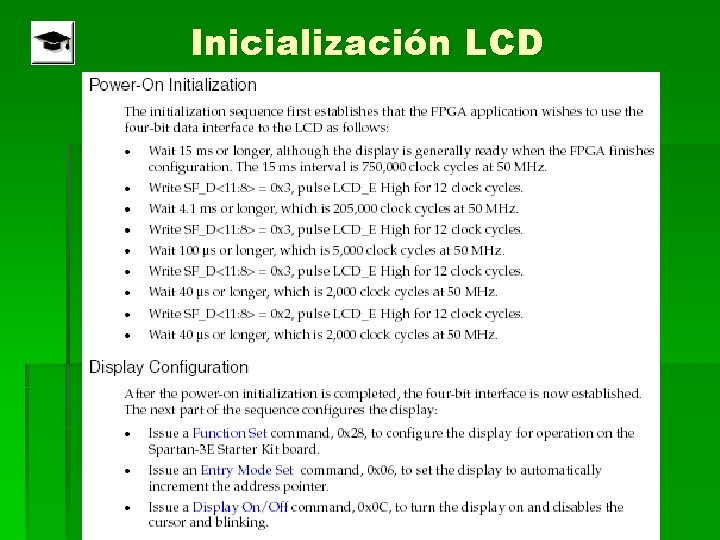

Inicialización LCD

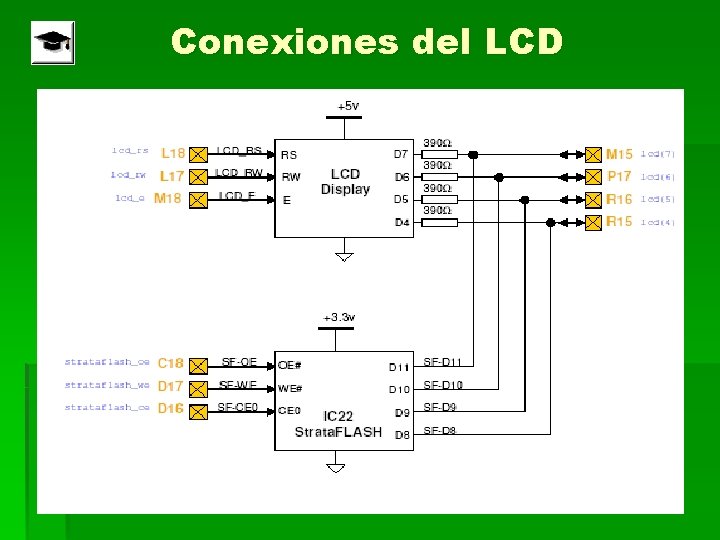

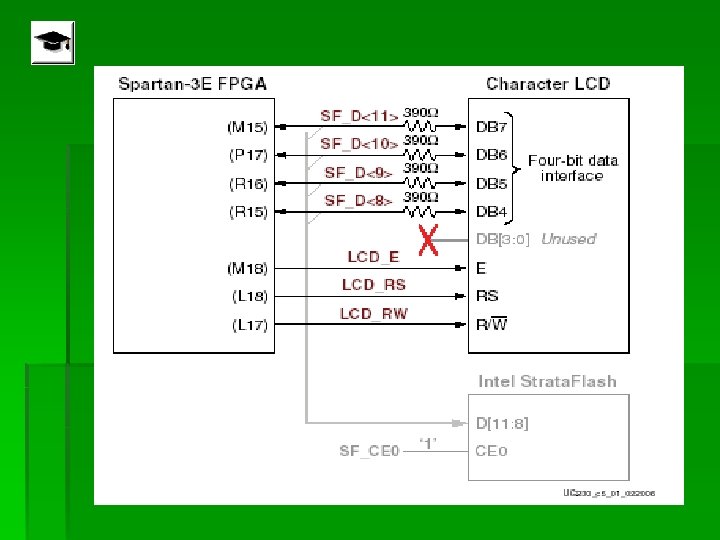

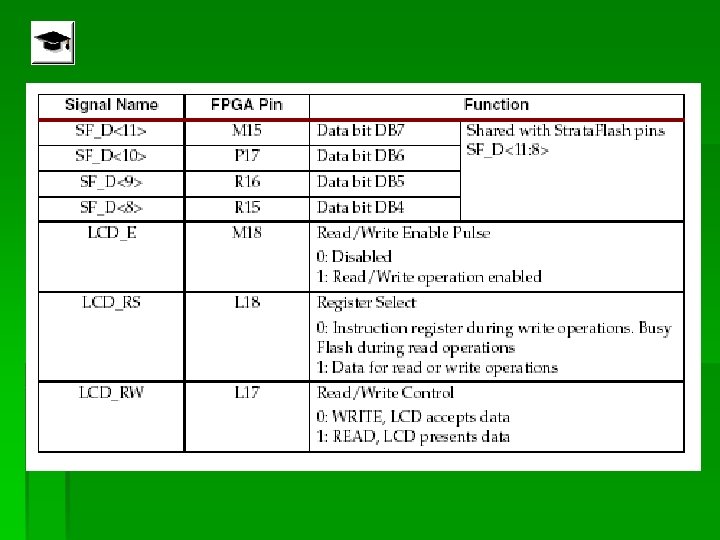

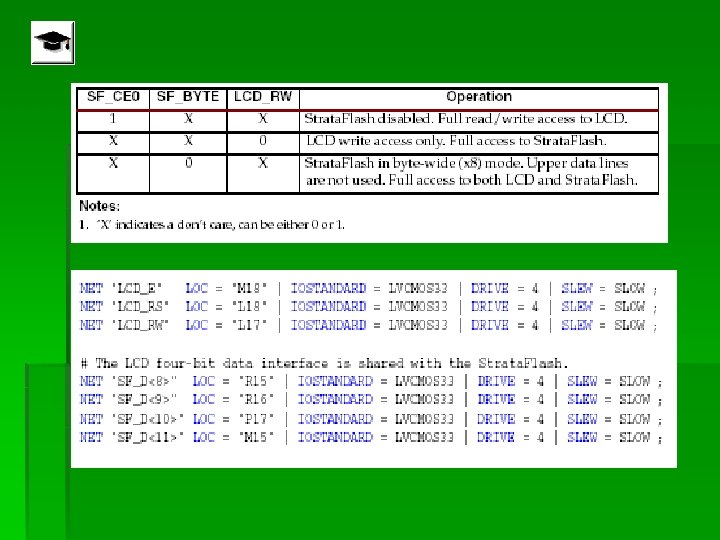

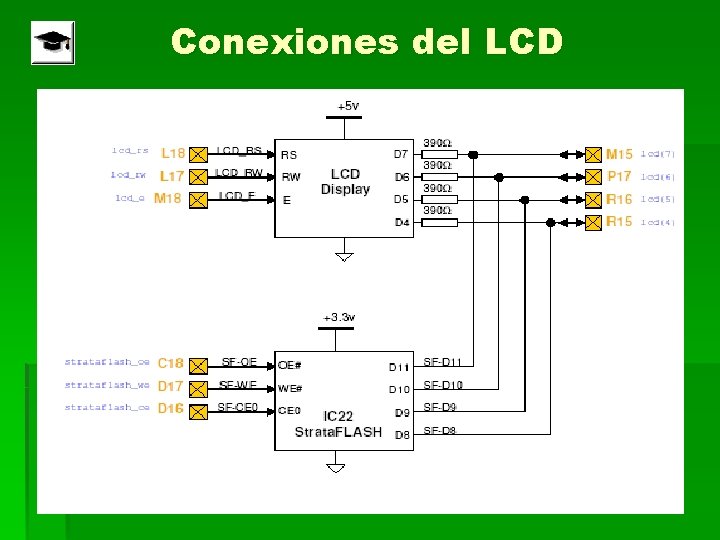

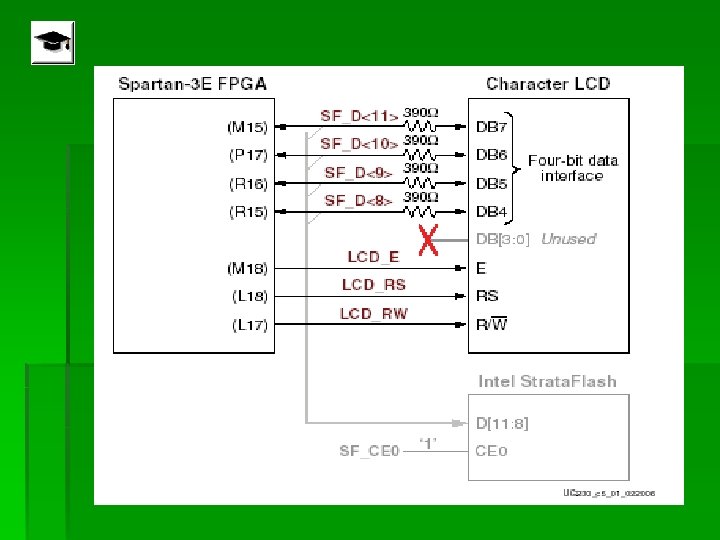

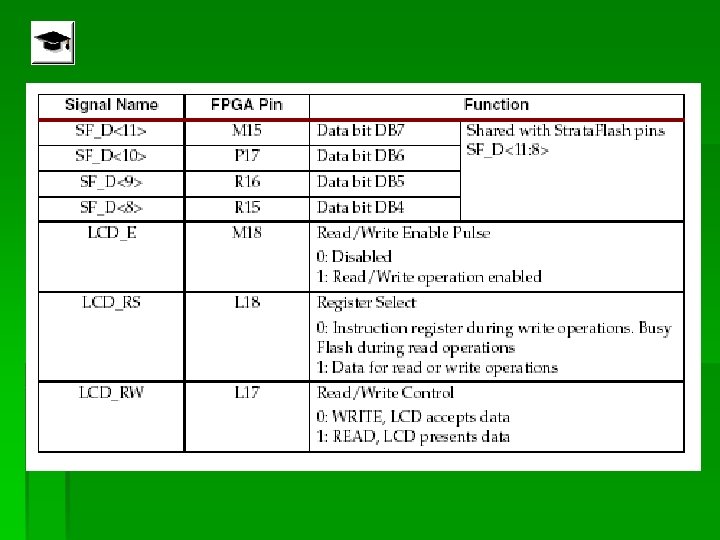

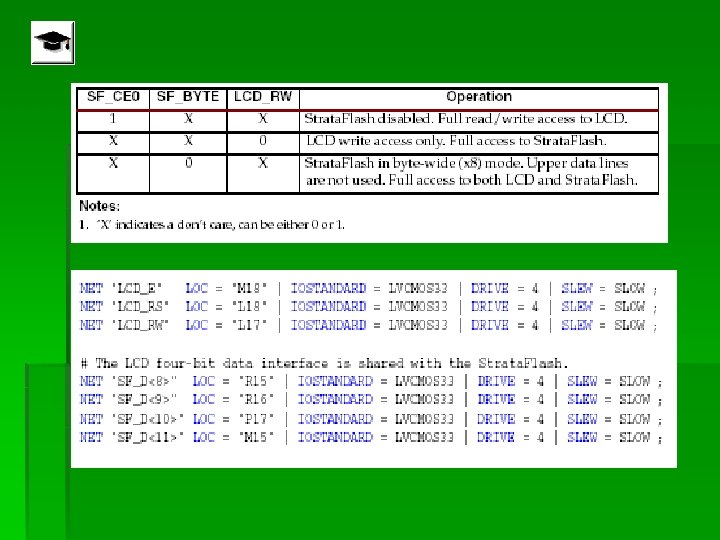

Conexiones del LCD

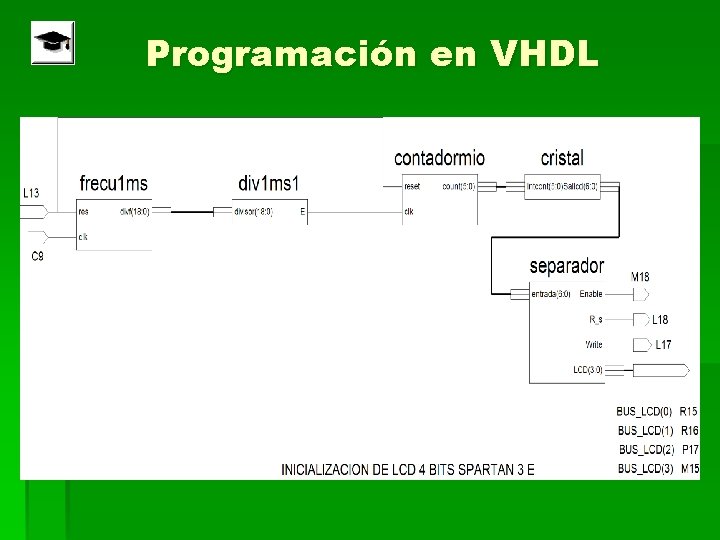

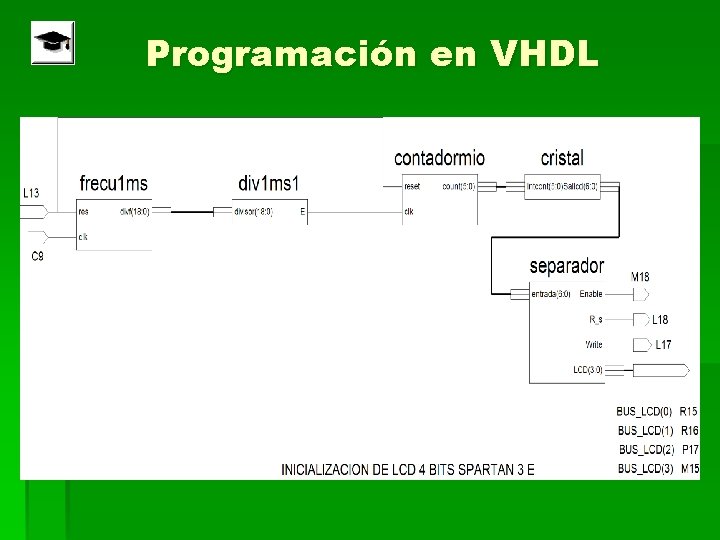

Programación en VHDL

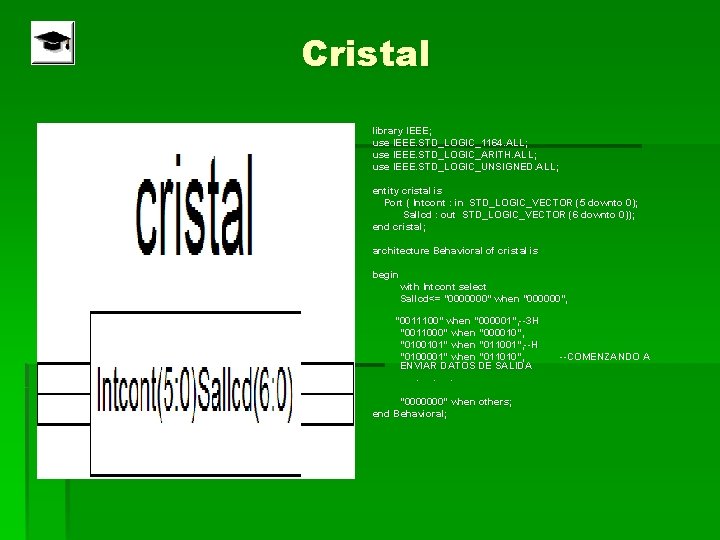

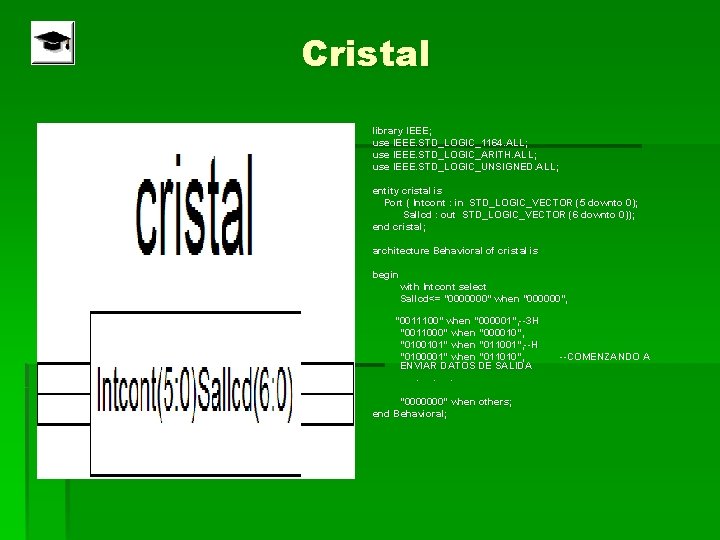

Cristal library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity cristal is Port ( Intcont : in STD_LOGIC_VECTOR (5 downto 0); Sallcd : out STD_LOGIC_VECTOR (6 downto 0)); end cristal; architecture Behavioral of cristal is begin with Intcont select Sallcd<= "0000000" when "000000", "0011100" when "000001", --3 H "0011000" when "000010", "0100101" when "011001", --H "0100001" when "011010", ENVIAR DATOS DE SALIDA. . . "0000000" when others; end Behavioral; --COMENZANDO A

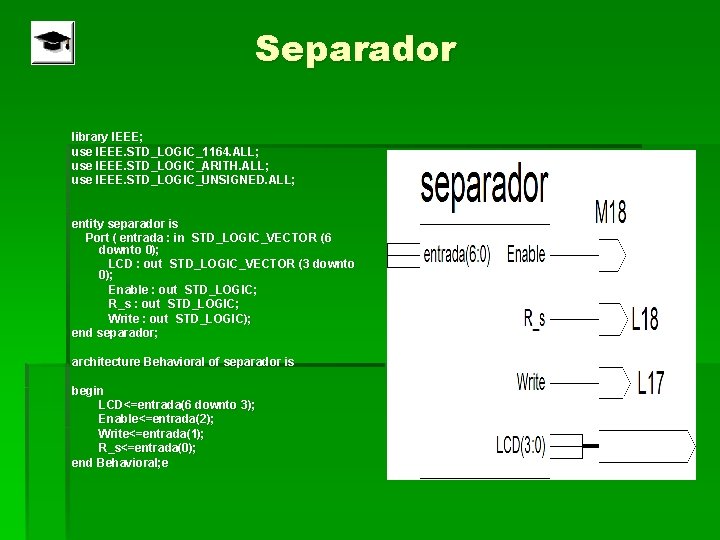

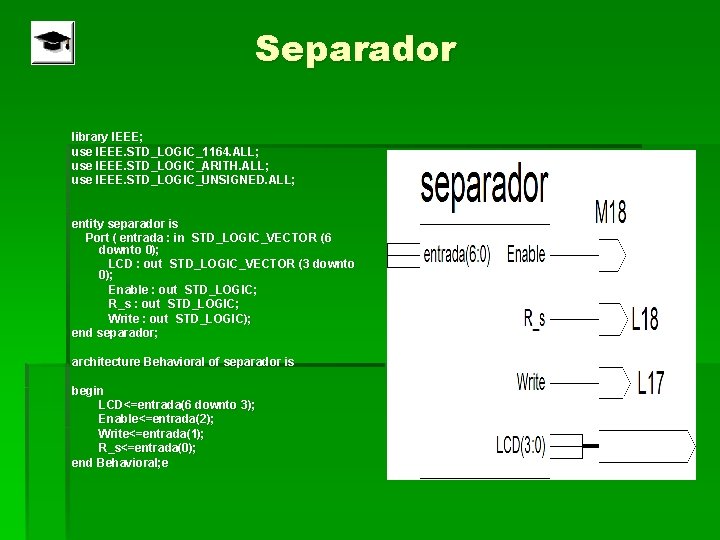

Separador library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity separador is Port ( entrada : in STD_LOGIC_VECTOR (6 downto 0); LCD : out STD_LOGIC_VECTOR (3 downto 0); Enable : out STD_LOGIC; R_s : out STD_LOGIC; Write : out STD_LOGIC); end separador; architecture Behavioral of separador is begin LCD<=entrada(6 downto 3); Enable<=entrada(2); Write<=entrada(1); R_s<=entrada(0); end Behavioral; e

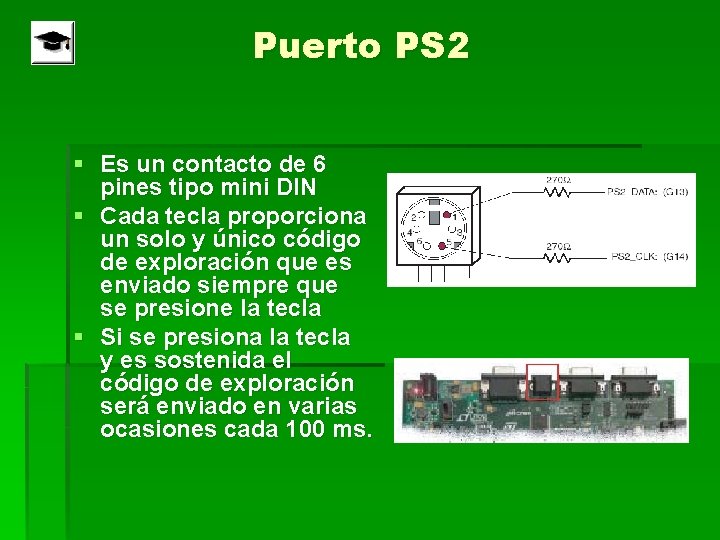

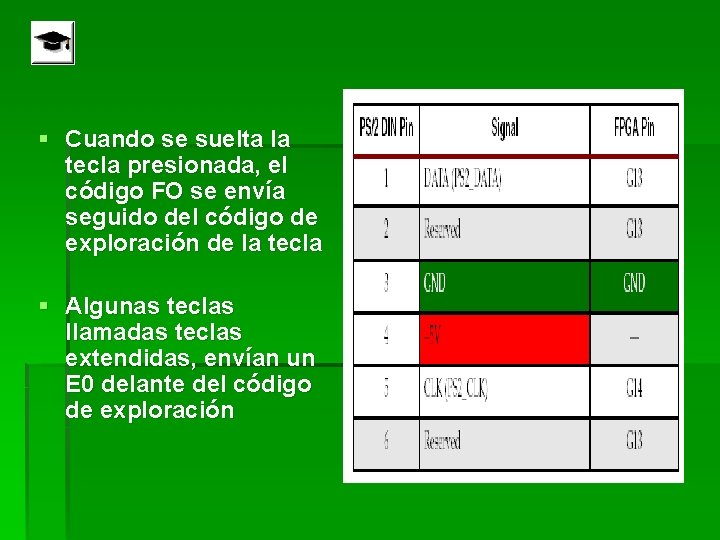

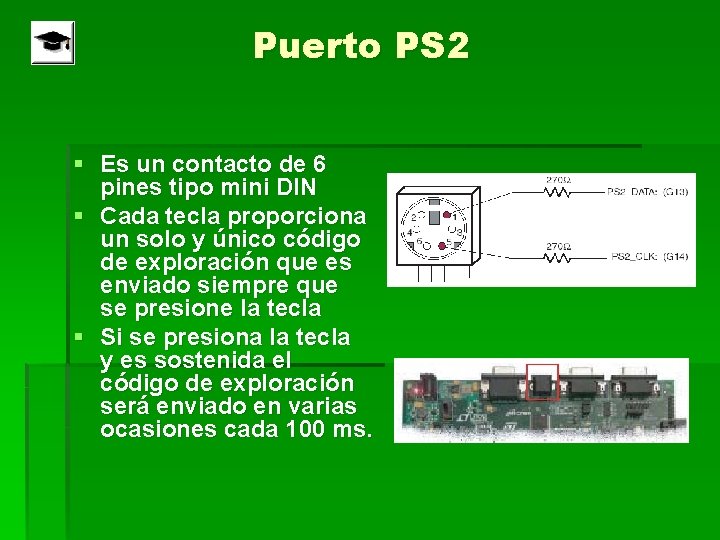

Puerto PS 2 § Es un contacto de 6 pines tipo mini DIN § Cada tecla proporciona un solo y único código de exploración que es enviado siempre que se presione la tecla § Si se presiona la tecla y es sostenida el código de exploración será enviado en varias ocasiones cada 100 ms.

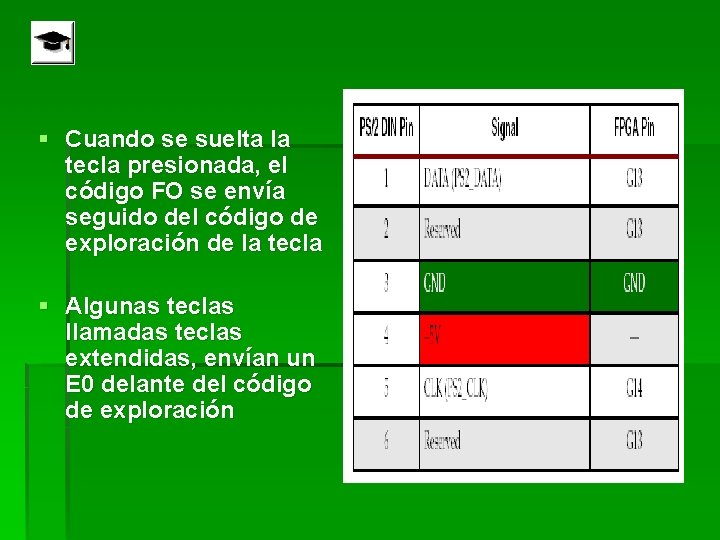

§ Cuando se suelta la tecla presionada, el código FO se envía seguido del código de exploración de la tecla § Algunas teclas llamadas teclas extendidas, envían un E 0 delante del código de exploración

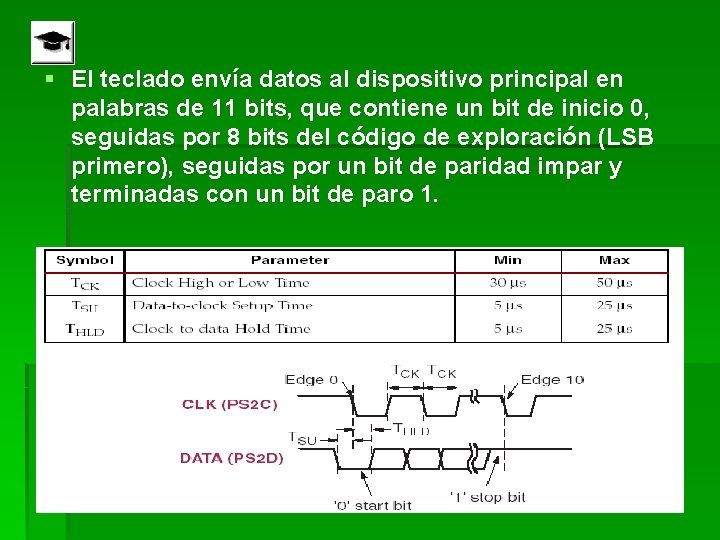

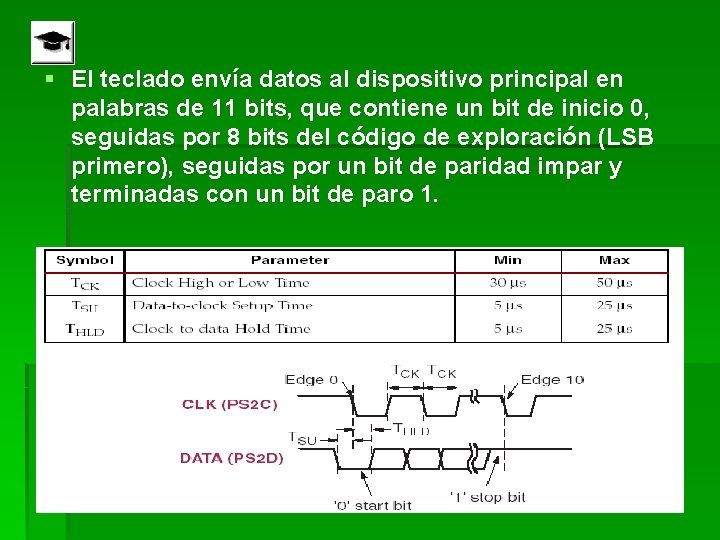

§ El teclado envía datos al dispositivo principal en palabras de 11 bits, que contiene un bit de inicio 0, seguidas por 8 bits del código de exploración (LSB primero), seguidas por un bit de paridad impar y terminadas con un bit de paro 1.

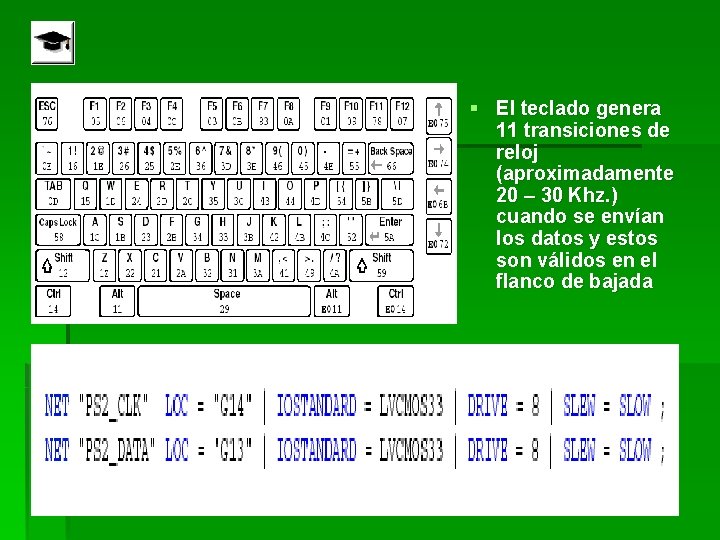

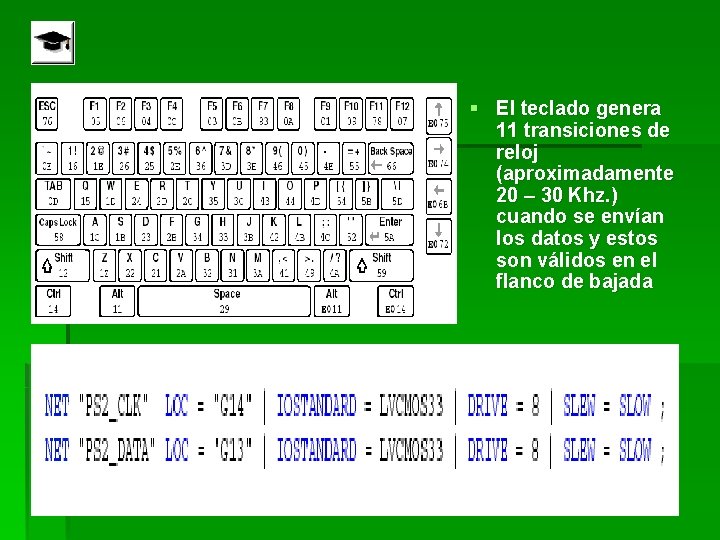

§ El teclado genera 11 transiciones de reloj (aproximadamente 20 – 30 Khz. ) cuando se envían los datos y estos son válidos en el flanco de bajada

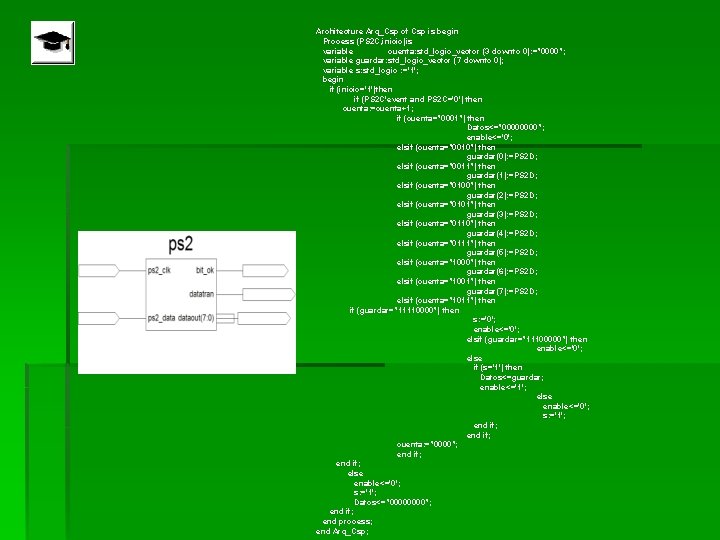

Programación en VHDL

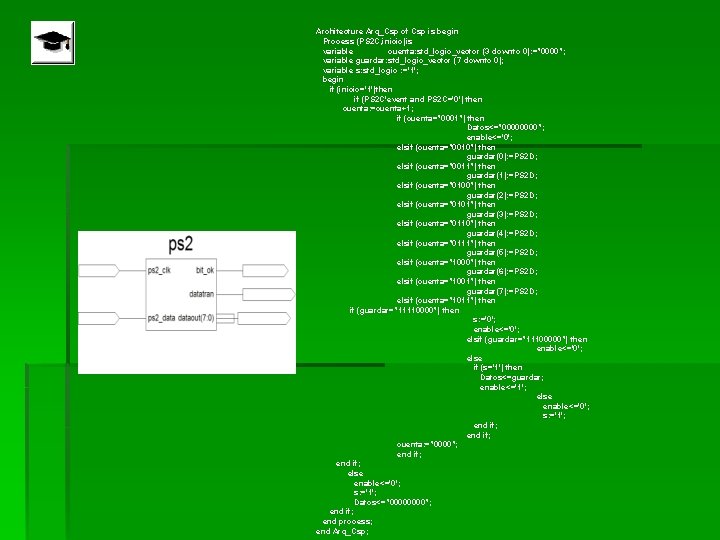

Architecture Arq_Csp of Csp is begin Process (PS 2 C, inicio)is variable cuenta: std_logic_vector (3 downto 0): ="0000"; variable guardar: std_logic_vector (7 downto 0); variable s: std_logic : ='1'; begin if (inicio='1')then if (PS 2 C'event and PS 2 C='0') then cuenta: =cuenta+1; if (cuenta="0001") then Datos<="0000"; enable<='0'; elsif (cuenta="0010") then guardar(0): =PS 2 D; elsif (cuenta="0011") then guardar(1): =PS 2 D; elsif (cuenta="0100") then guardar(2): =PS 2 D; elsif (cuenta="0101") then guardar(3): =PS 2 D; elsif (cuenta="0110") then guardar(4): =PS 2 D; elsif (cuenta="0111") then guardar(5): =PS 2 D; elsif (cuenta="1000") then guardar(6): =PS 2 D; elsif (cuenta="1001") then guardar(7): =PS 2 D; elsif (cuenta="1011") then if (guardar="11110000") then s: ='0'; enable<='0'; elsif (guardar="11100000") then enable<='0'; else if (s='1') then Datos<=guardar; enable<='1'; else enable<='0'; s: ='1'; end if; if; cuenta: ="0000"; end if; if; else enable<='0'; s: ='1'; Datos<="0000"; end if; end process; end Arq_Csp;

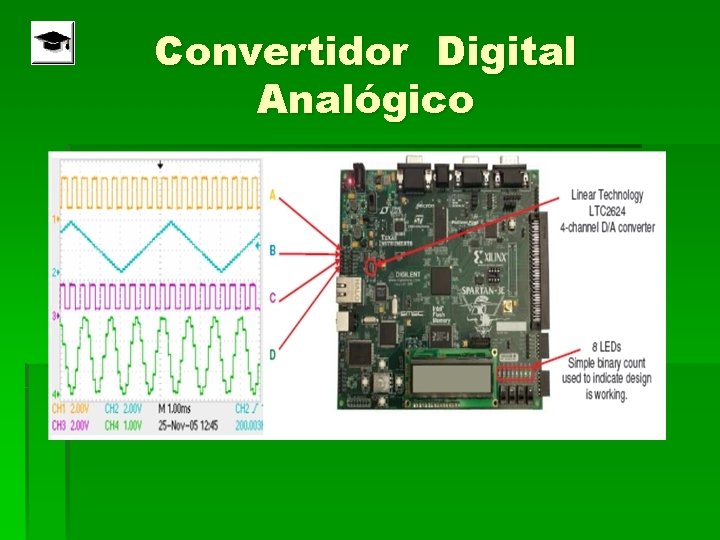

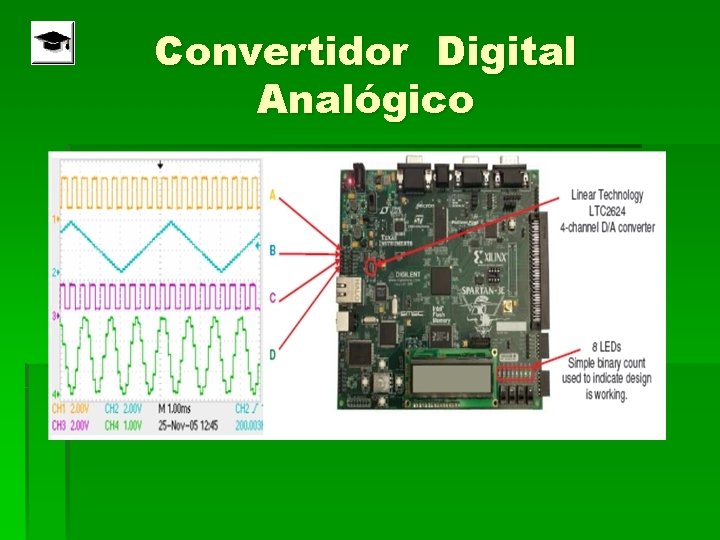

Convertidor Digital Analógico

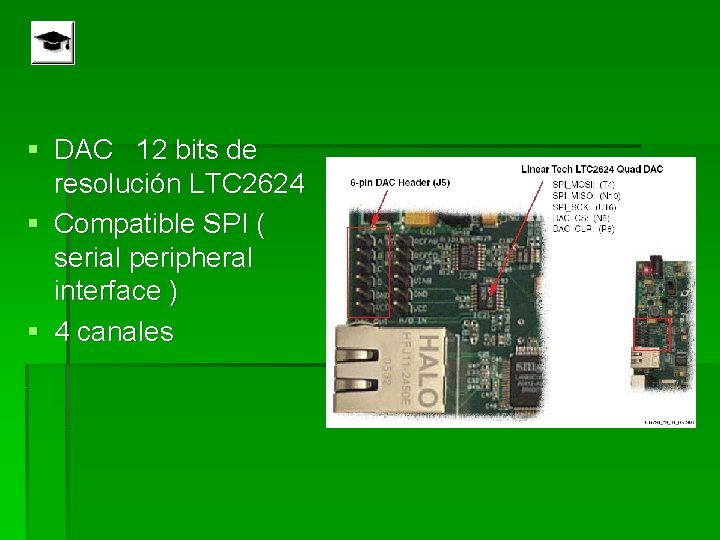

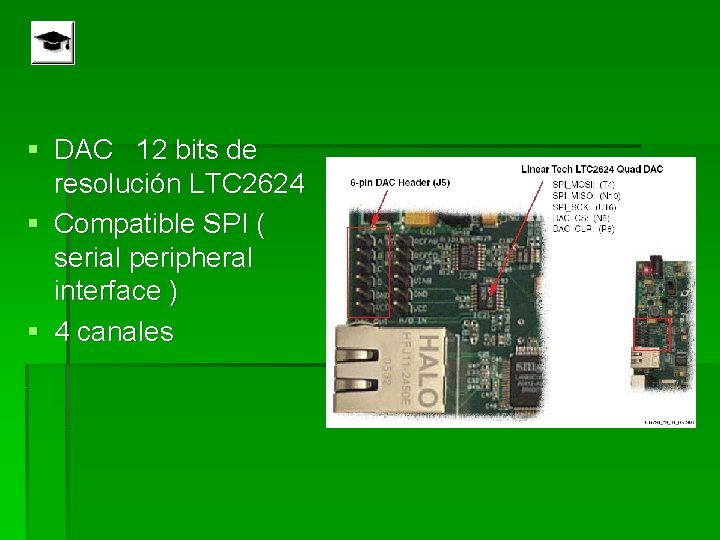

§ DAC 12 bits de resolución LTC 2624 § Compatible SPI ( serial peripheral interface ) § 4 canales

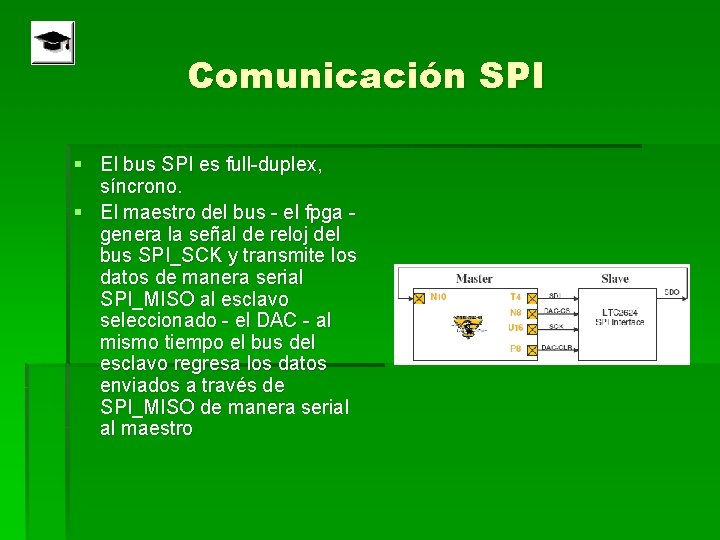

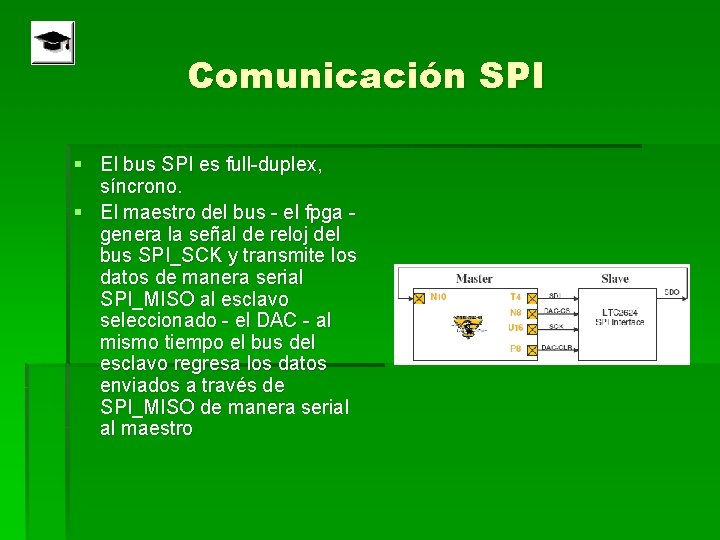

Comunicación SPI § El bus SPI es full-duplex, síncrono. § El maestro del bus - el fpga genera la señal de reloj del bus SPI_SCK y transmite los datos de manera serial SPI_MISO al esclavo seleccionado - el DAC - al mismo tiempo el bus del esclavo regresa los datos enviados a través de SPI_MISO de manera serial al maestro

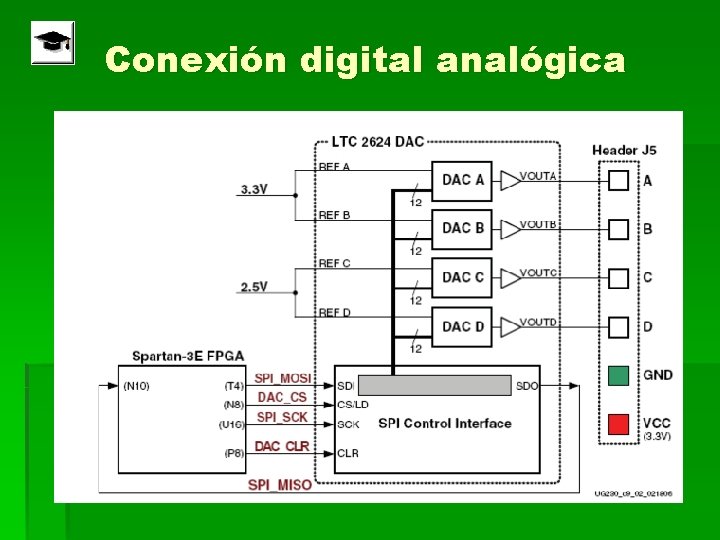

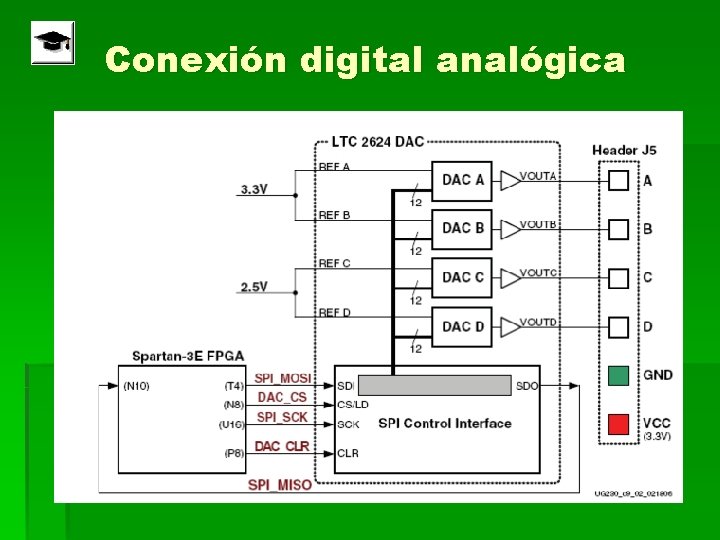

Conexión digital analógica

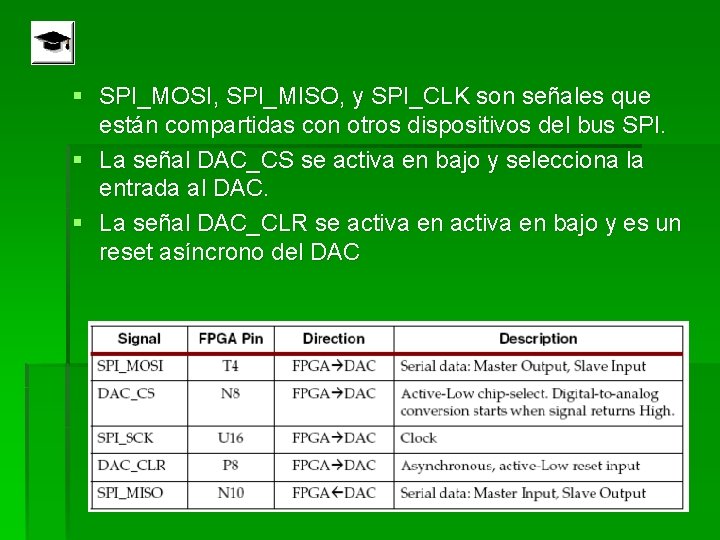

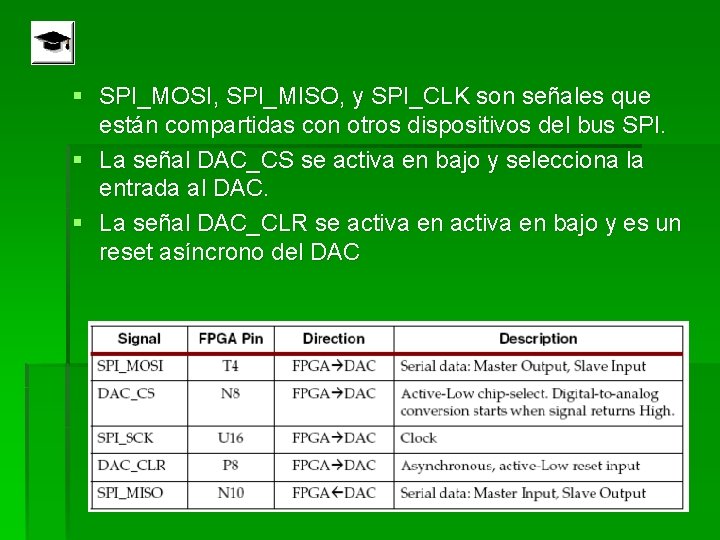

§ SPI_MOSI, SPI_MISO, y SPI_CLK son señales que están compartidas con otros dispositivos del bus SPI. § La señal DAC_CS se activa en bajo y selecciona la entrada al DAC. § La señal DAC_CLR se activa en bajo y es un reset asíncrono del DAC

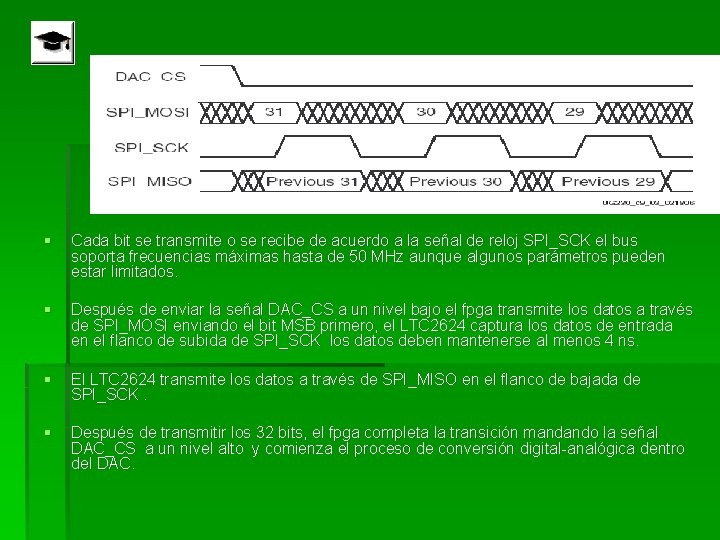

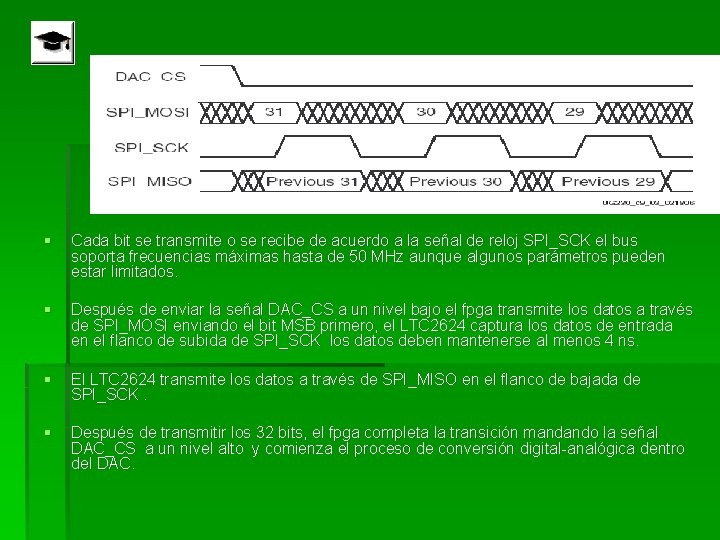

§ Cada bit se transmite o se recibe de acuerdo a la señal de reloj SPI_SCK el bus soporta frecuencias máximas hasta de 50 MHz aunque algunos parámetros pueden estar limitados. § Después de enviar la señal DAC_CS a un nivel bajo el fpga transmite los datos a través de SPI_MOSI enviando el bit MSB primero, el LTC 2624 captura los datos de entrada en el flanco de subida de SPI_SCK los datos deben mantenerse al menos 4 ns. § El LTC 2624 transmite los datos a través de SPI_MISO en el flanco de bajada de SPI_SCK. § Después de transmitir los 32 bits, el fpga completa la transición mandando la señal DAC_CS a un nivel alto y comienza el proceso de conversión digital-analógica dentro del DAC.

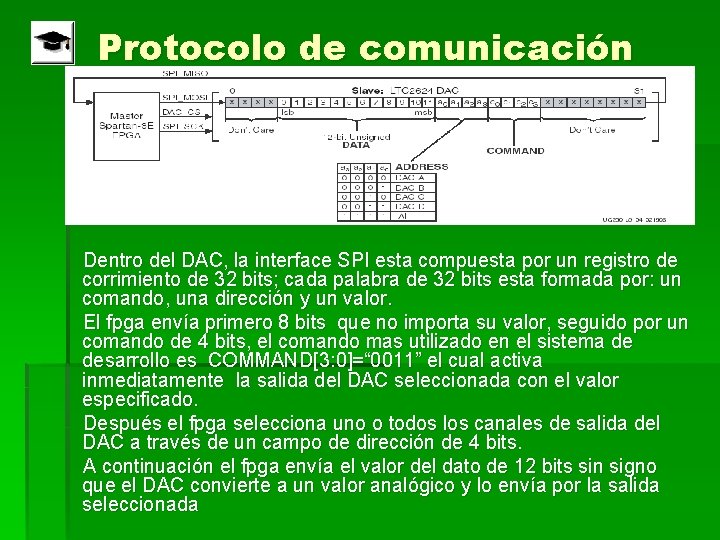

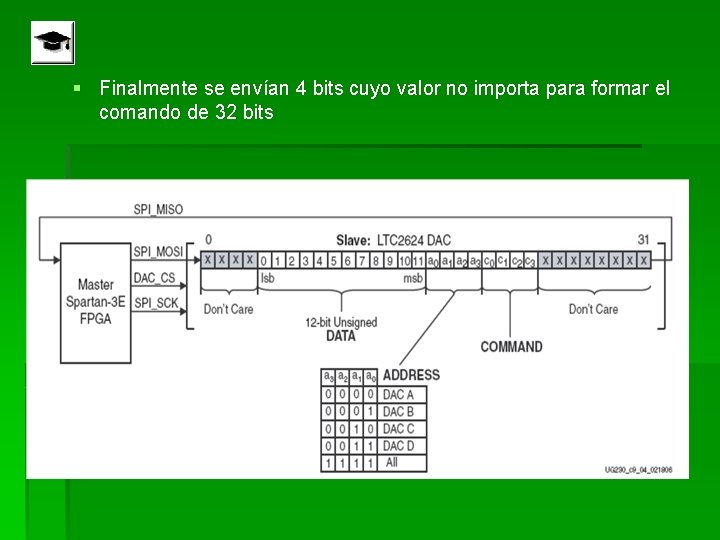

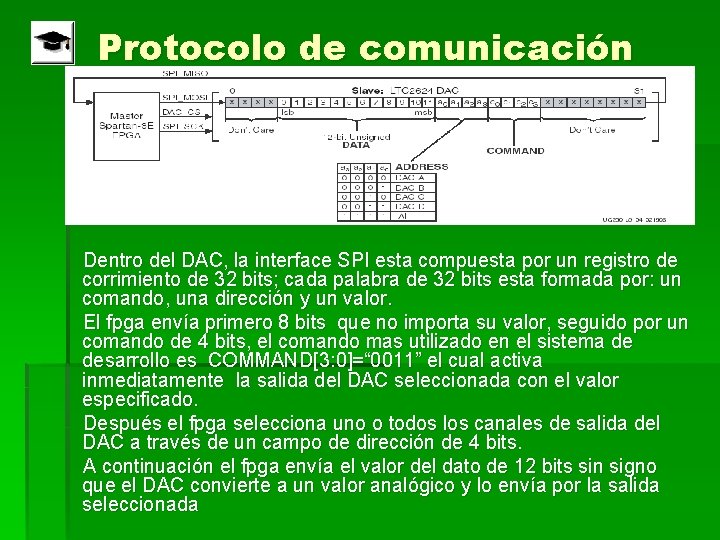

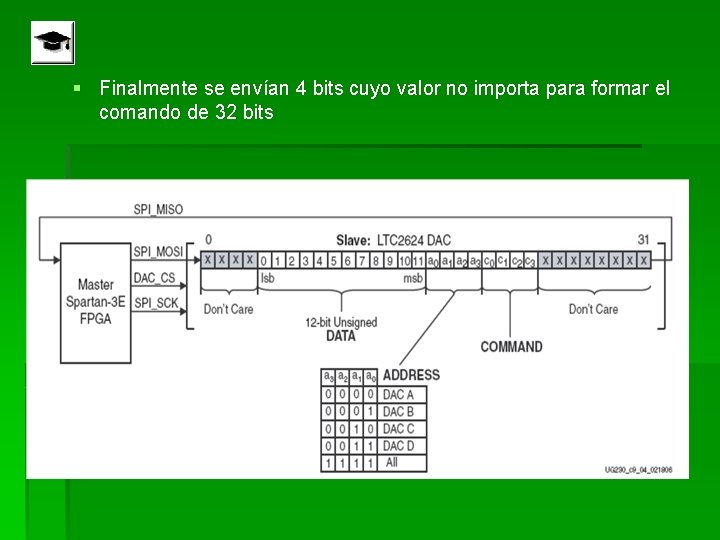

Protocolo de comunicación Dentro del DAC, la interface SPI esta compuesta por un registro de corrimiento de 32 bits; cada palabra de 32 bits esta formada por: un comando, una dirección y un valor. El fpga envía primero 8 bits que no importa su valor, seguido por un comando de 4 bits, el comando mas utilizado en el sistema de desarrollo es COMMAND[3: 0]=“ 0011” el cual activa inmediatamente la salida del DAC seleccionada con el valor especificado. Después el fpga selecciona uno o todos los canales de salida del DAC a través de un campo de dirección de 4 bits. A continuación el fpga envía el valor del dato de 12 bits sin signo que el DAC convierte a un valor analógico y lo envía por la salida seleccionada

§ Finalmente se envían 4 bits cuyo valor no importa para formar el comando de 32 bits

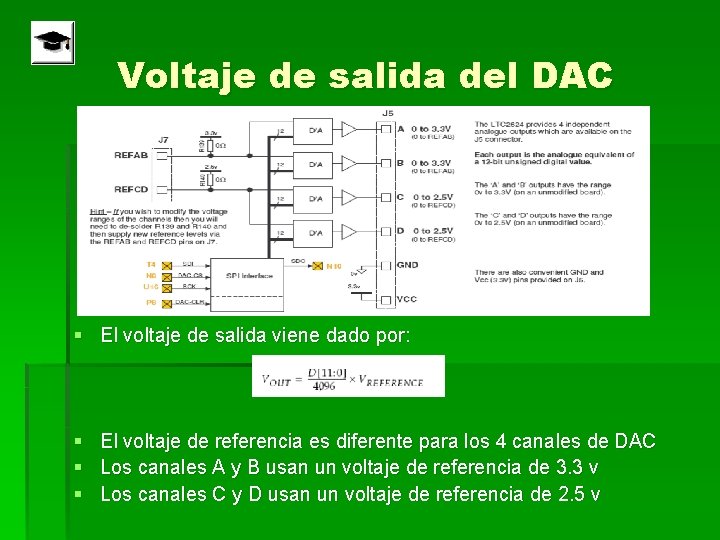

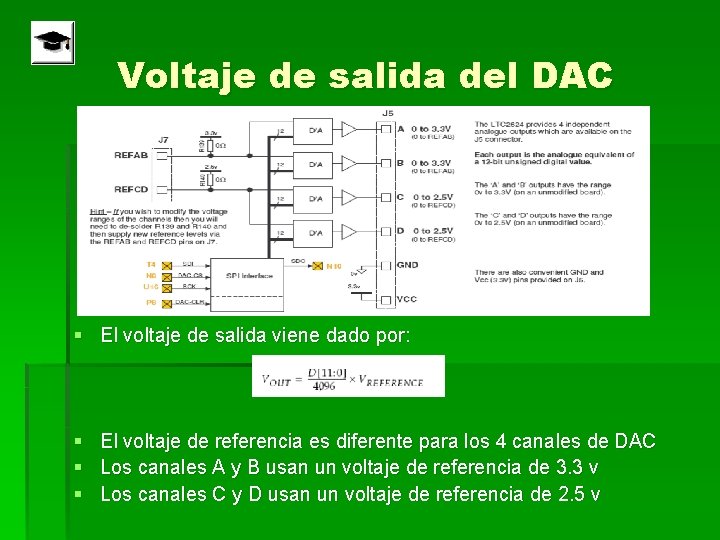

Voltaje de salida del DAC § El voltaje de salida viene dado por: § § § El voltaje de referencia es diferente para los 4 canales de DAC Los canales A y B usan un voltaje de referencia de 3. 3 v Los canales C y D usan un voltaje de referencia de 2. 5 v

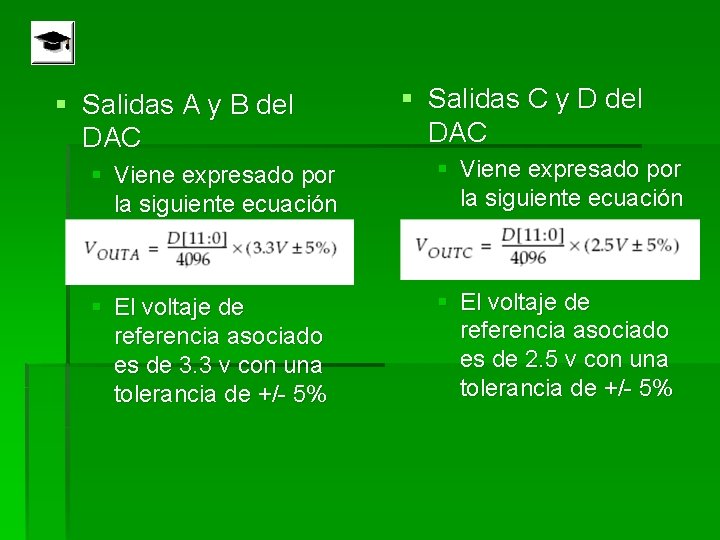

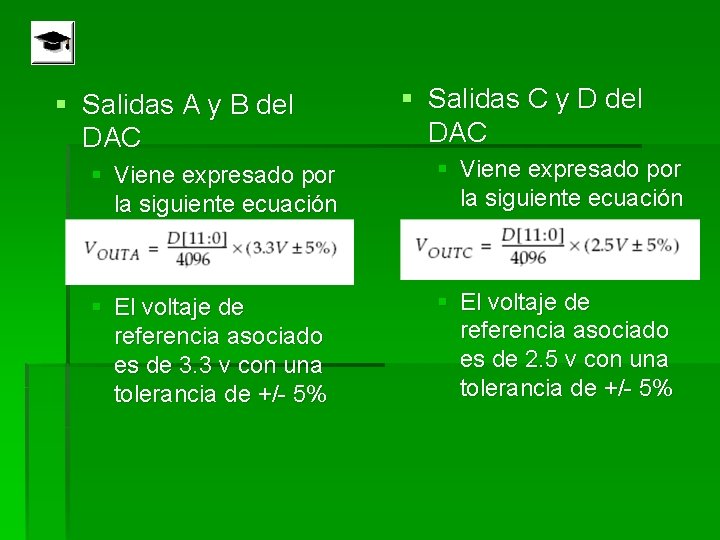

§ Salidas A y B del DAC § Salidas C y D del DAC § Viene expresado por la siguiente ecuación § El voltaje de referencia asociado es de 3. 3 v con una tolerancia de +/- 5% § El voltaje de referencia asociado es de 2. 5 v con una tolerancia de +/- 5%

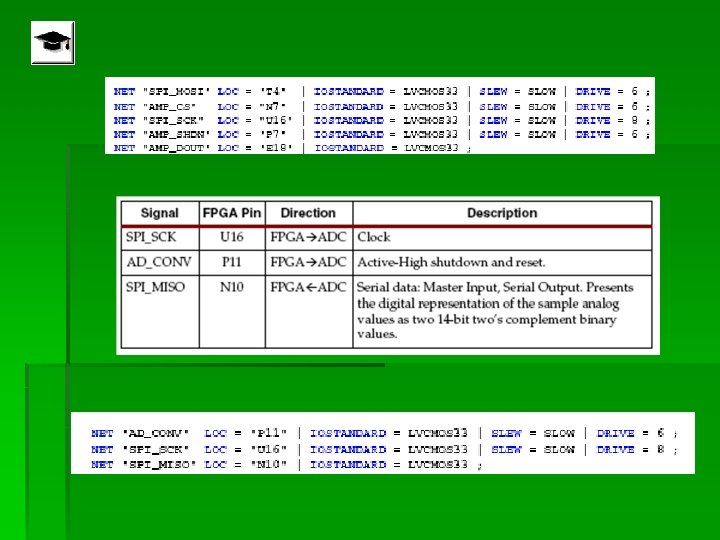

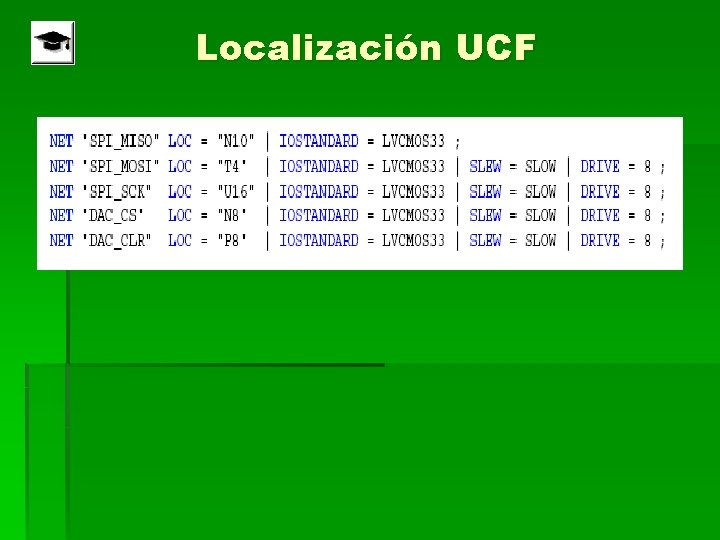

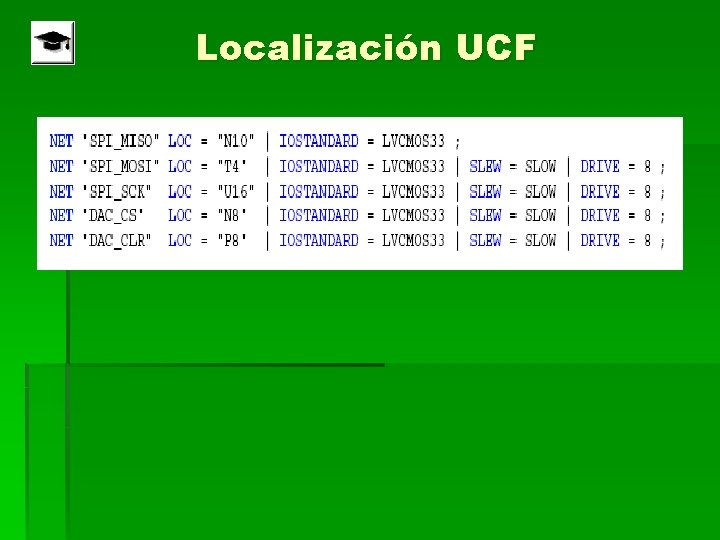

Localización UCF

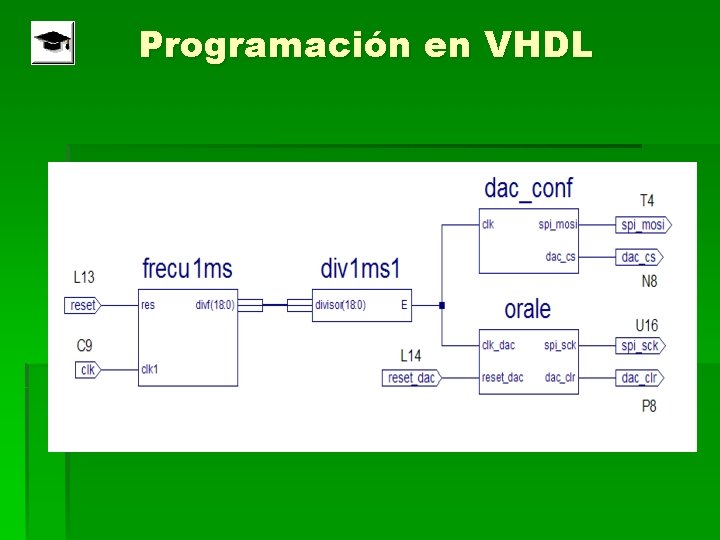

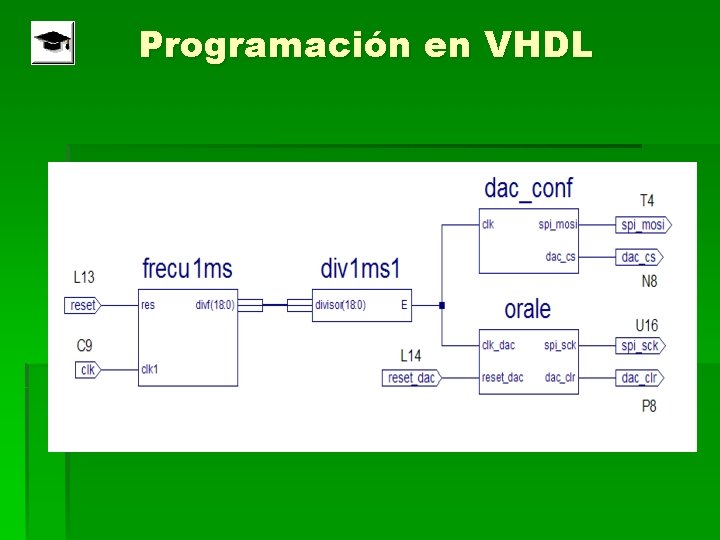

Programación en VHDL

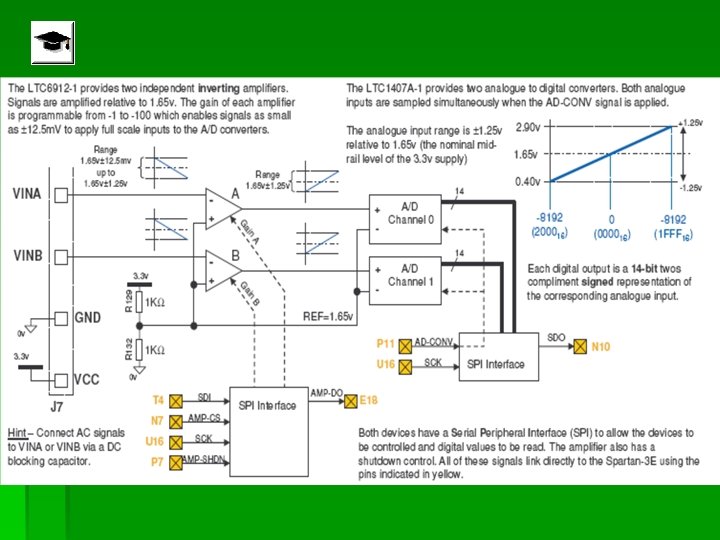

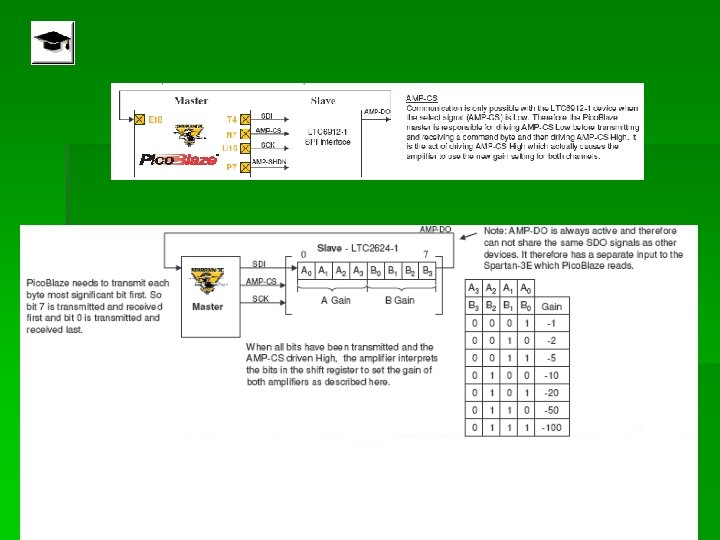

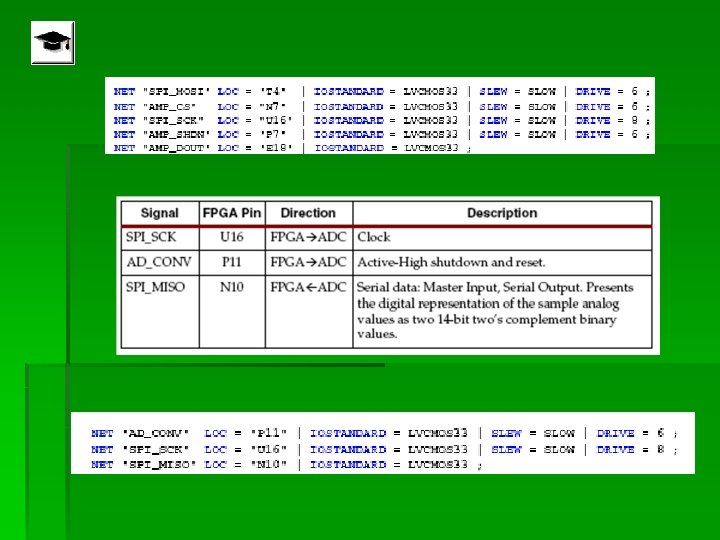

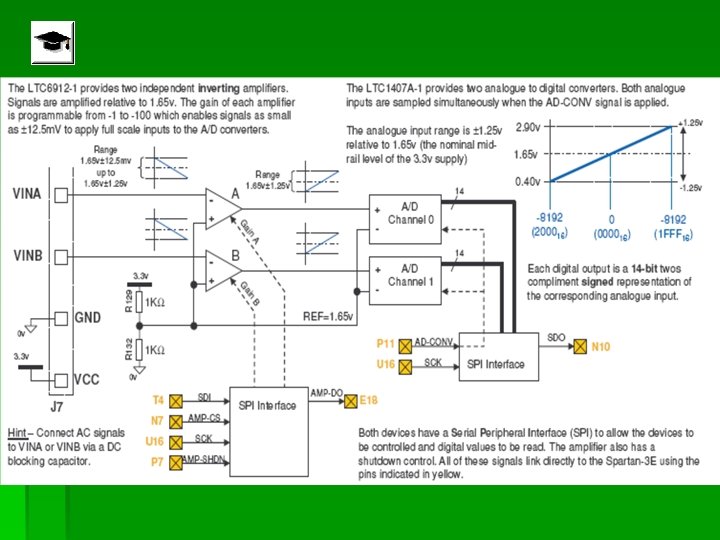

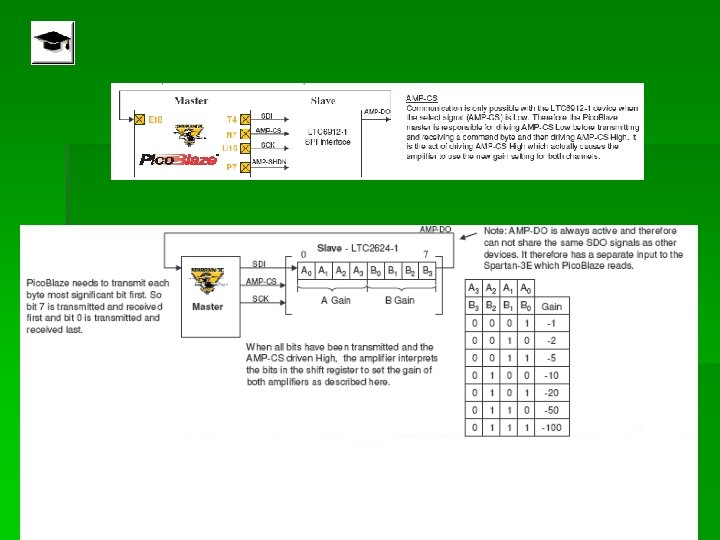

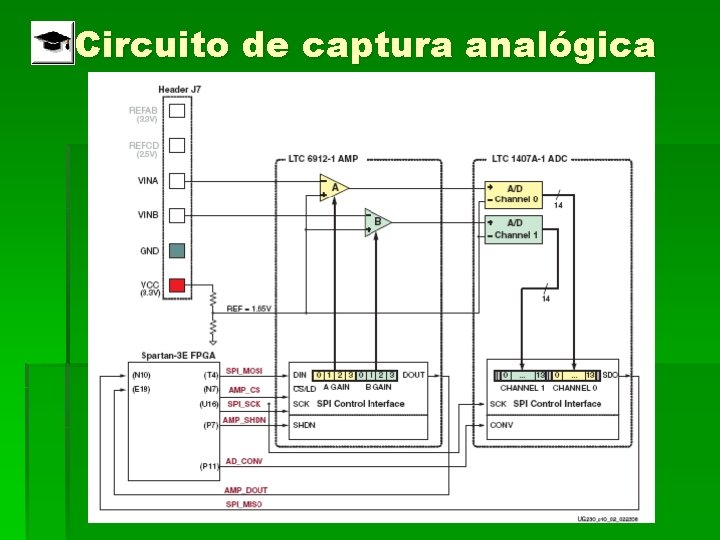

Convertidor Analógico Digital § Preamplificador programable LTC 6912 I (j 7) § ADC LTC 1407 A § Ambos programables serialmente

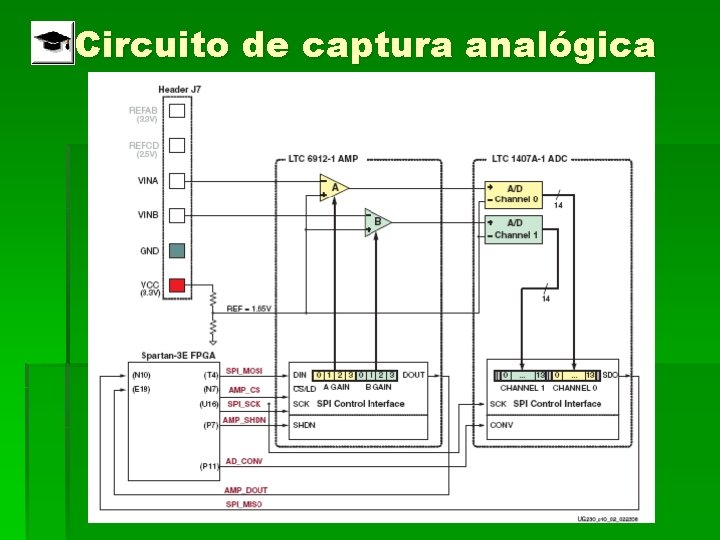

Circuito de captura analógica

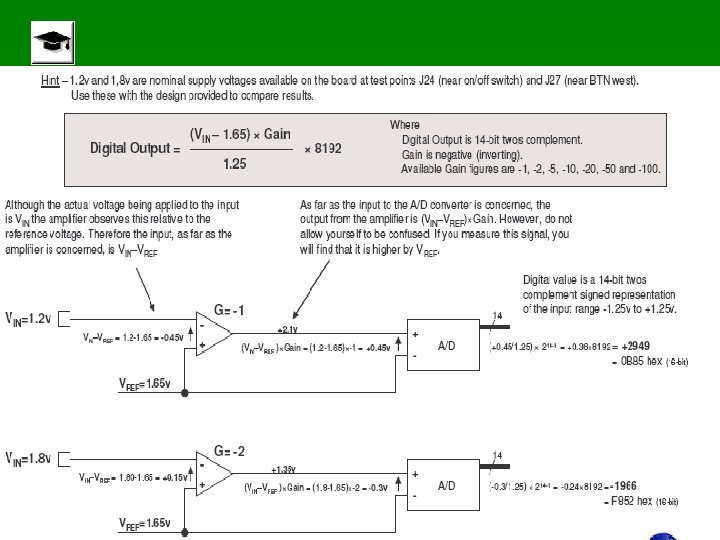

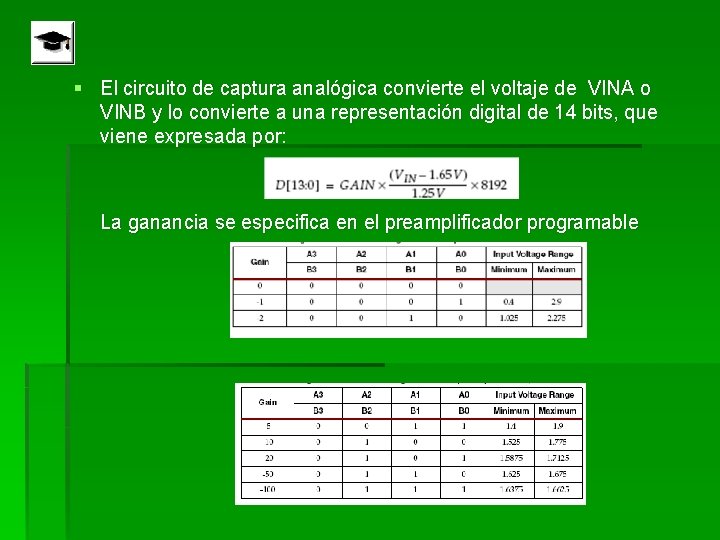

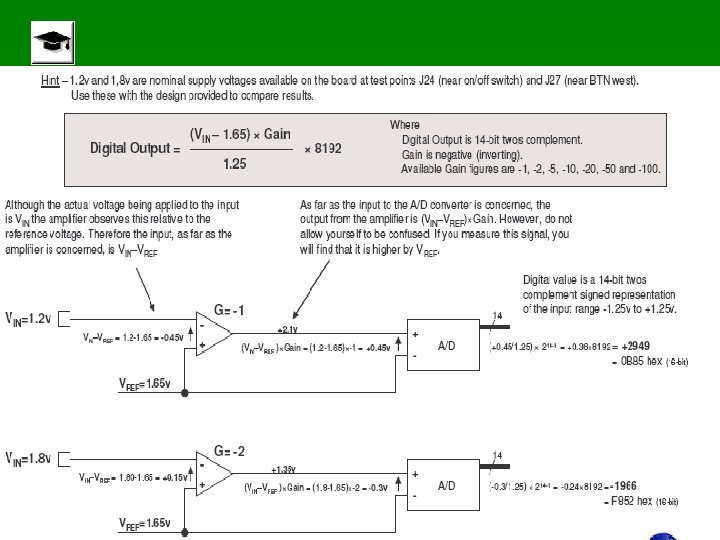

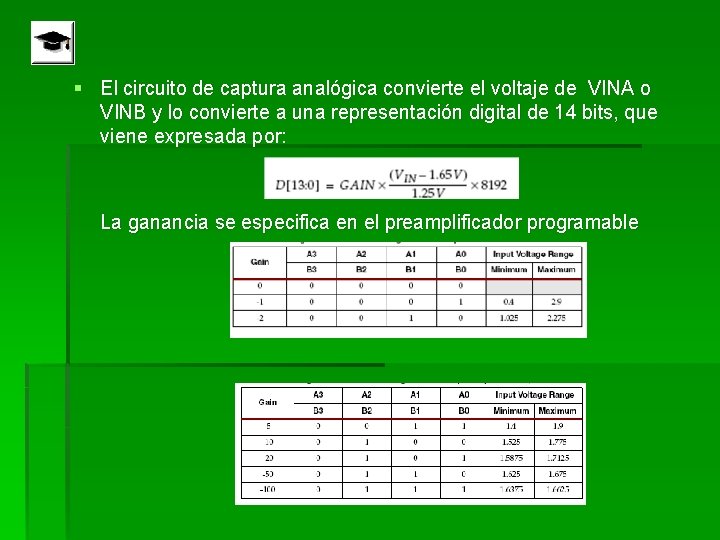

§ El circuito de captura analógica convierte el voltaje de VINA o VINB y lo convierte a una representación digital de 14 bits, que viene expresada por: La ganancia se especifica en el preamplificador programable

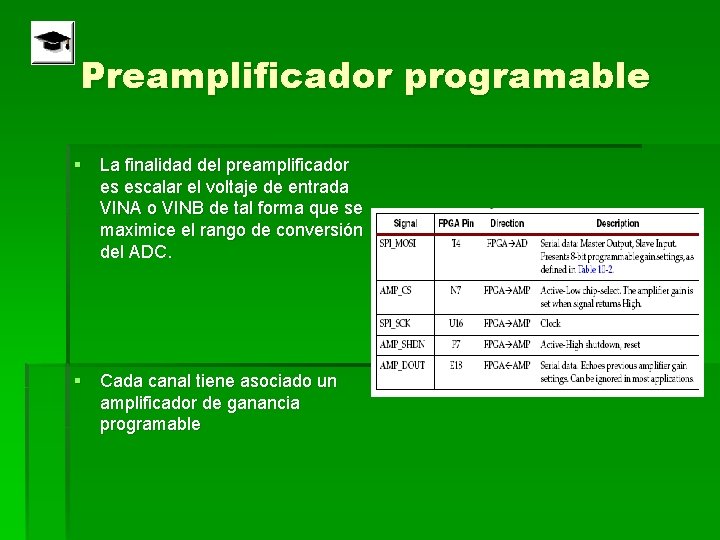

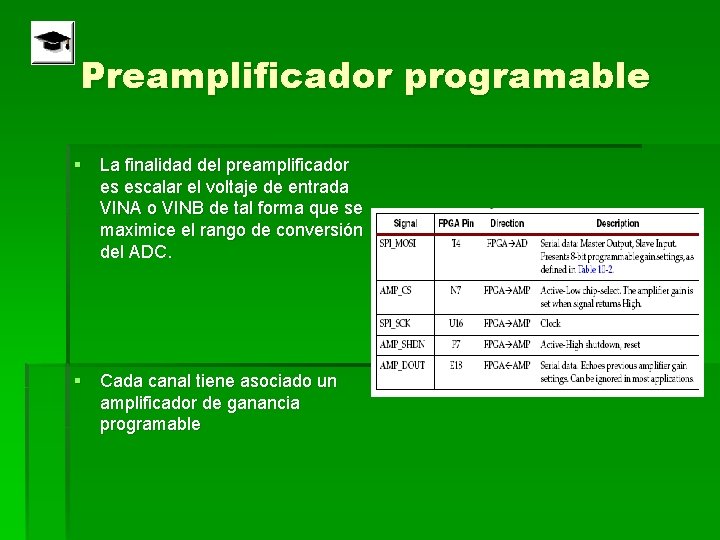

Preamplificador programable § La finalidad del preamplificador es escalar el voltaje de entrada VINA o VINB de tal forma que se maximice el rango de conversión del ADC. § Cada canal tiene asociado un amplificador de ganancia programable

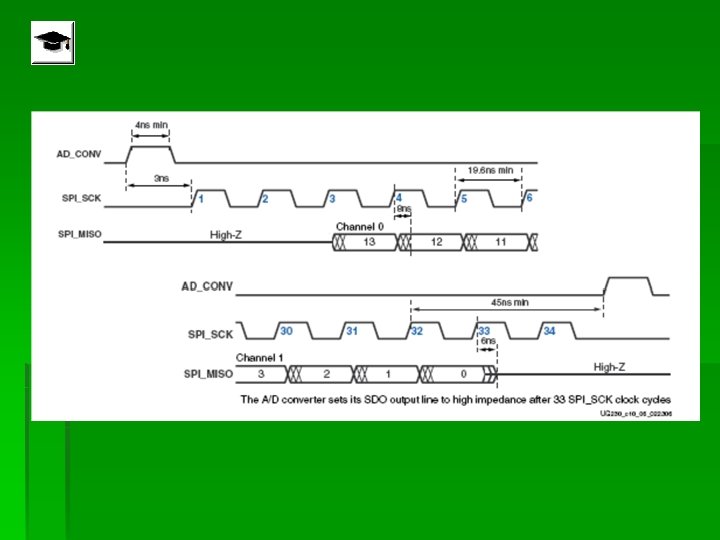

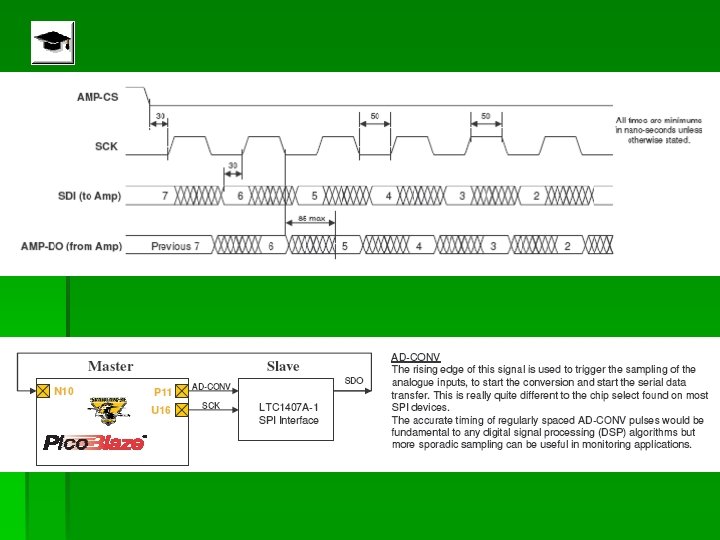

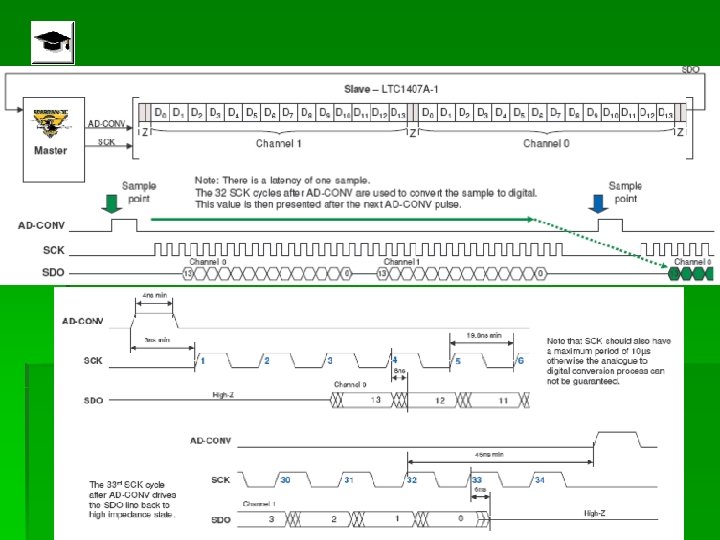

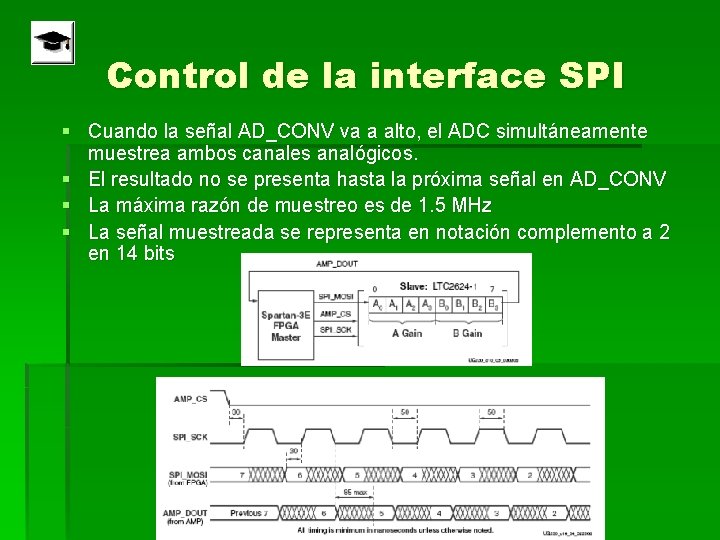

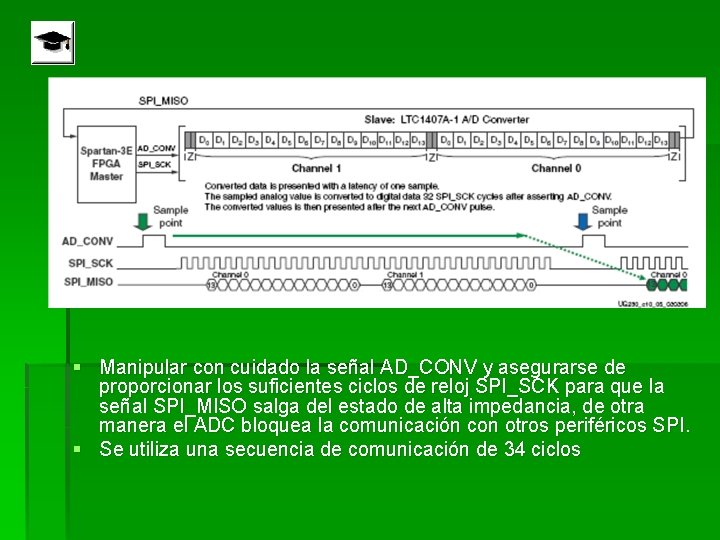

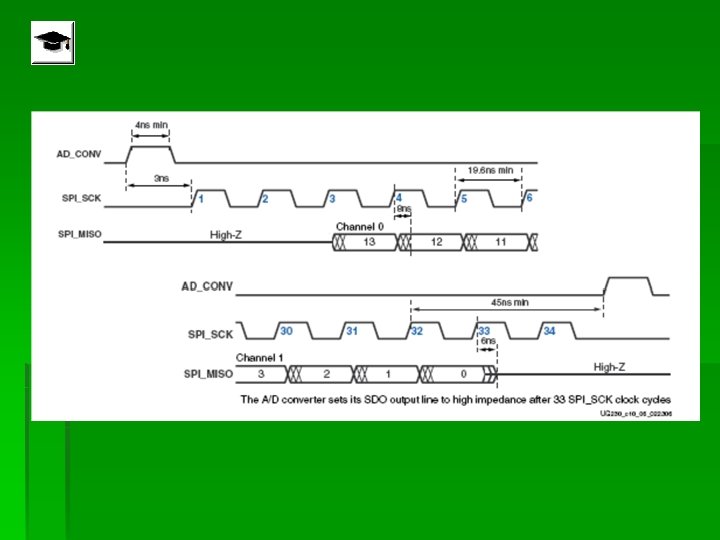

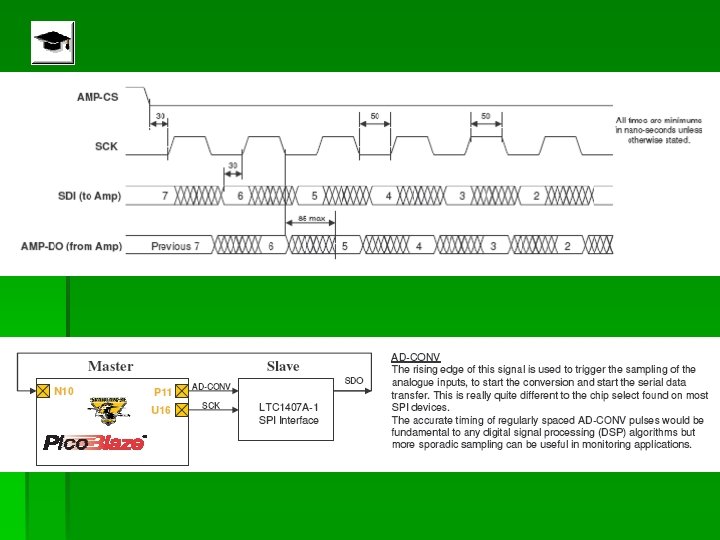

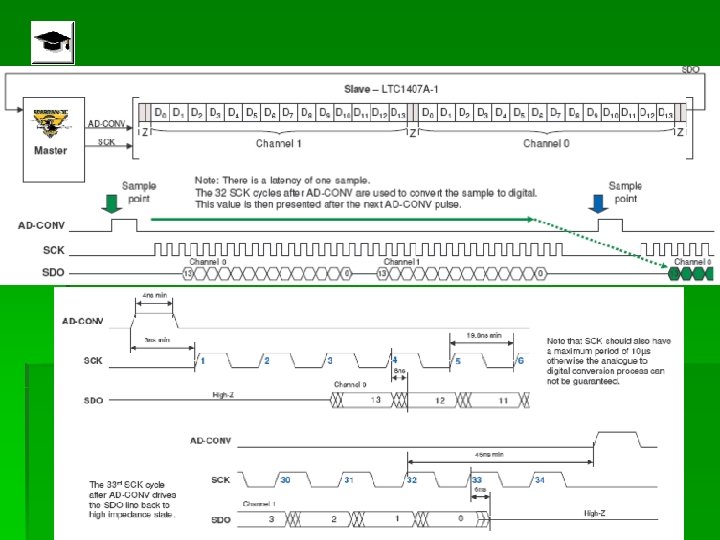

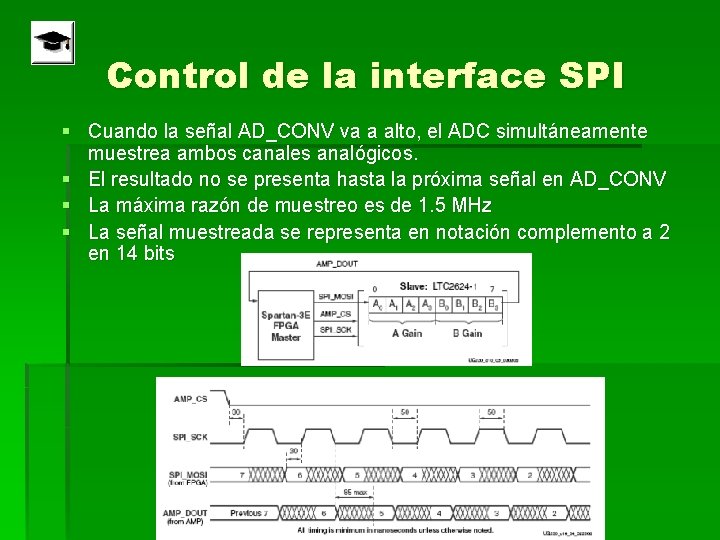

Control de la interface SPI § Cuando la señal AD_CONV va a alto, el ADC simultáneamente muestrea ambos canales analógicos. § El resultado no se presenta hasta la próxima señal en AD_CONV § La máxima razón de muestreo es de 1. 5 MHz § La señal muestreada se representa en notación complemento a 2 en 14 bits

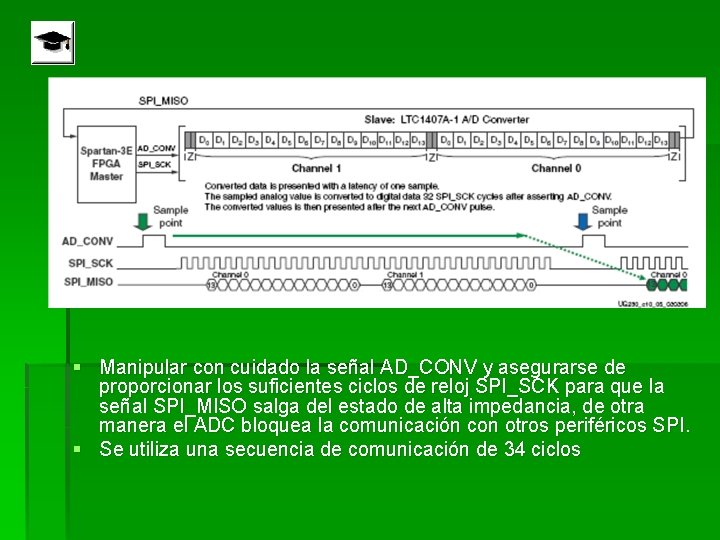

§ Manipular con cuidado la señal AD_CONV y asegurarse de proporcionar los suficientes ciclos de reloj SPI_SCK para que la señal SPI_MISO salga del estado de alta impedancia, de otra manera el ADC bloquea la comunicación con otros periféricos SPI. § Se utiliza una secuencia de comunicación de 34 ciclos