Csci 136 Computer Architecture II Data Hazard Forwarding

- Slides: 30

Csci 136 Computer Architecture II – Data Hazard, Forwarding, Stall Xiuzhen Cheng cheng@gwu. edu

Announcement Homework assignment #10, Due time – Before class, April 12 Readings: Sections 6. 4 – 6. 5 Problems: 6. 17 -6. 19, 6. 21 -6. 22, 6. 33 -6. 36, 6. 39 -6. 40 (six of them will be graded. Your TA will give hints in the lab sections. ) Project #3 is due on April 17, 2005 Final: Thursday, May 12, 12: 40 AM-2: 40 PM Note: you must pass final to pass this course!

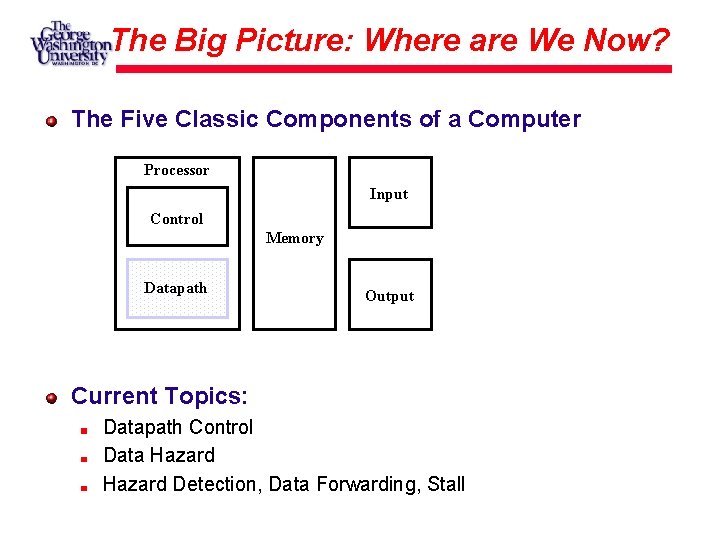

The Big Picture: Where are We Now? The Five Classic Components of a Computer Processor Input Control Memory Datapath Output Current Topics: Datapath Control Data Hazard Detection, Data Forwarding, Stall

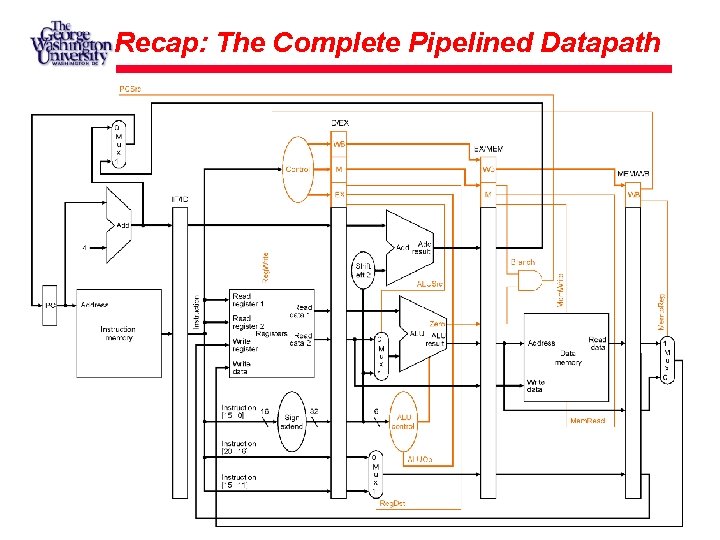

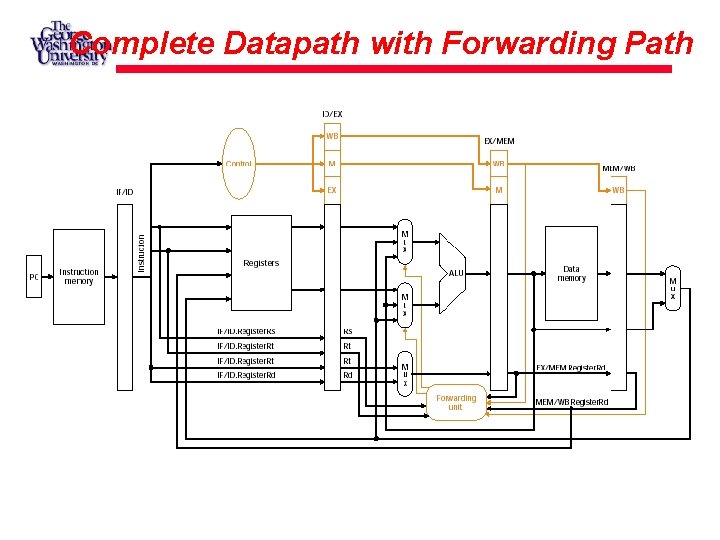

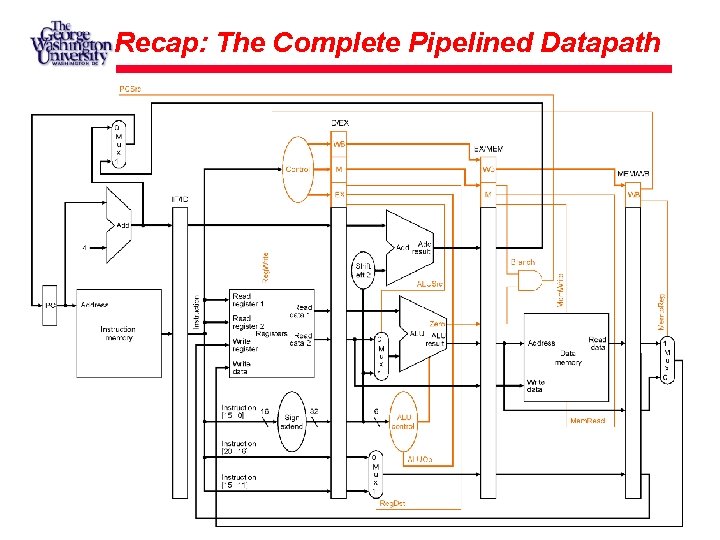

Recap: The Complete Pipelined Datapath

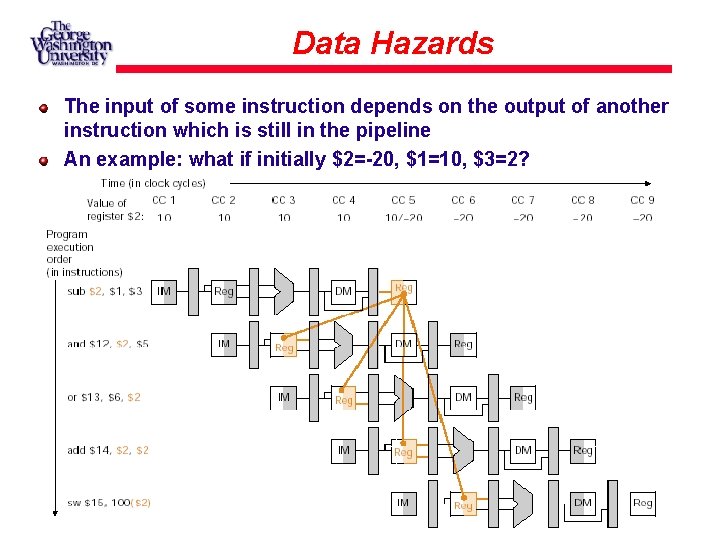

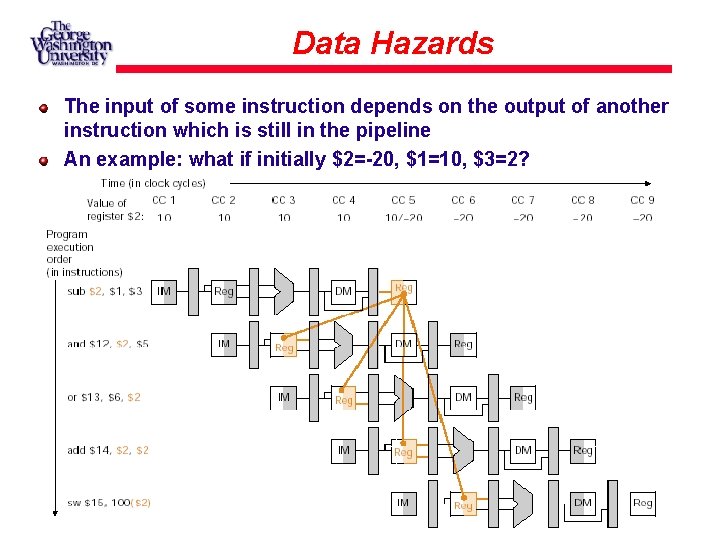

Data Hazards The input of some instruction depends on the output of another instruction which is still in the pipeline An example: what if initially $2=-20, $1=10, $3=2?

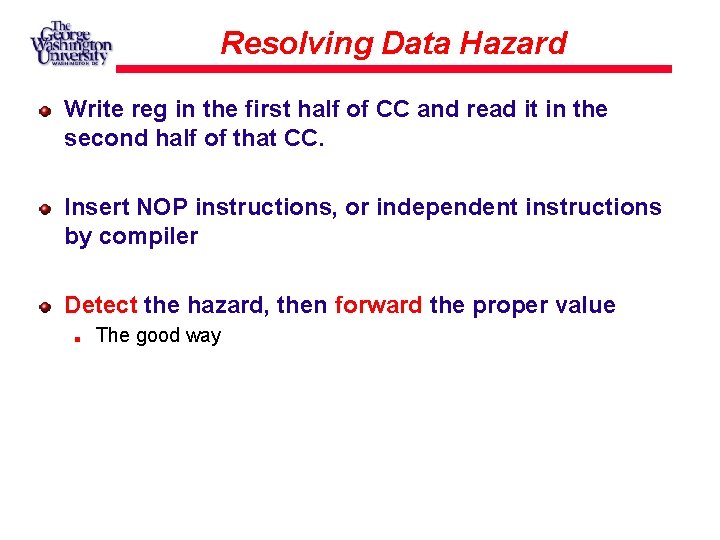

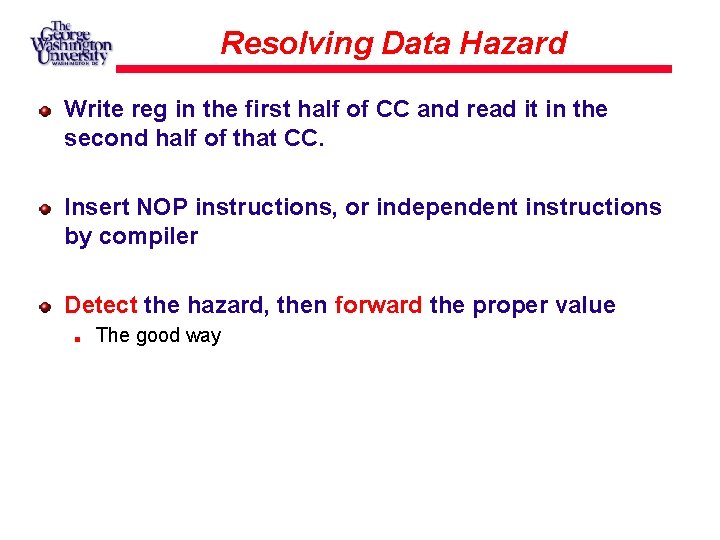

Resolving Data Hazard Write reg in the first half of CC and read it in the second half of that CC. Insert NOP instructions, or independent instructions by compiler Detect the hazard, then forward the proper value The good way

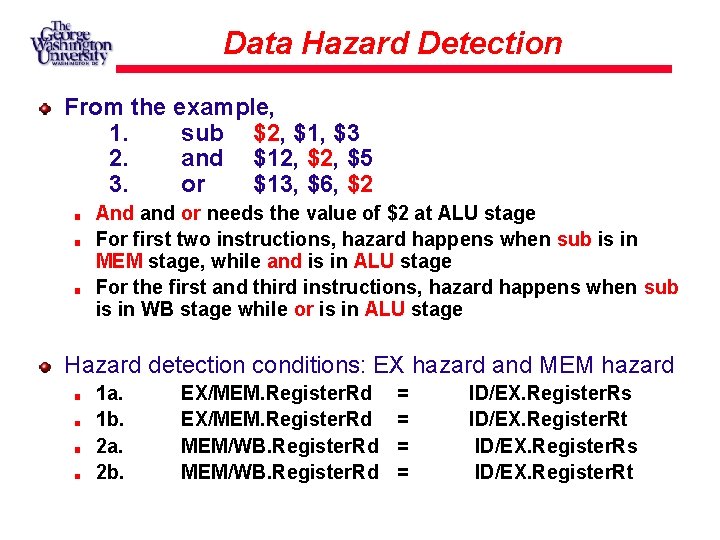

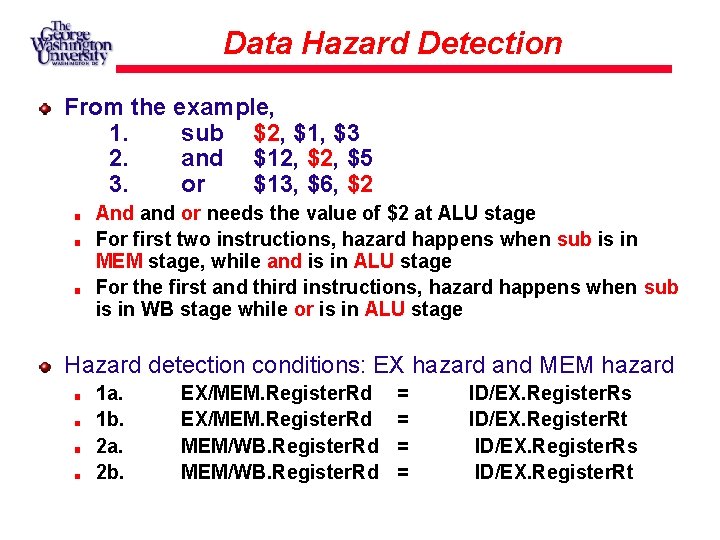

Data Hazard Detection From the example, 1. sub $2, $1, $3 2. and $12, $5 3. or $13, $6, $2 And and or needs the value of $2 at ALU stage For first two instructions, hazard happens when sub is in MEM stage, while and is in ALU stage For the first and third instructions, hazard happens when sub is in WB stage while or is in ALU stage Hazard detection conditions: EX hazard and MEM hazard 1 a. 1 b. 2 a. 2 b. EX/MEM. Register. Rd MEM/WB. Register. Rd = = ID/EX. Register. Rs ID/EX. Register. Rt

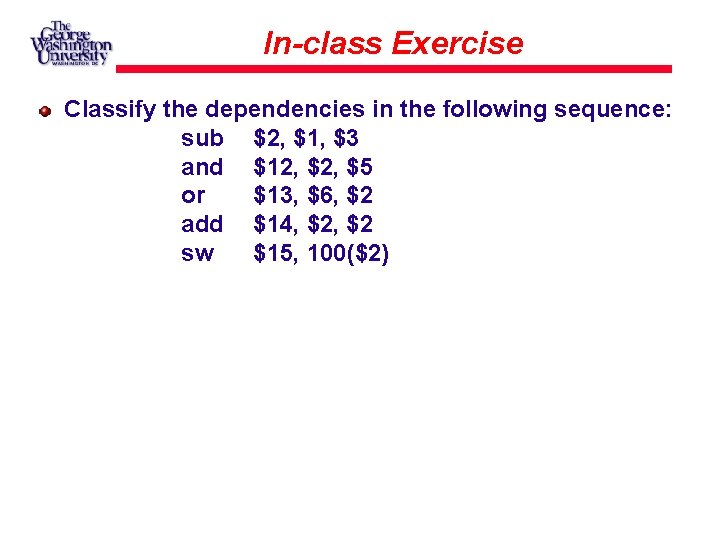

In-class Exercise Classify the dependencies in the following sequence: sub $2, $1, $3 and $12, $5 or $13, $6, $2 add $14, $2 sw $15, 100($2)

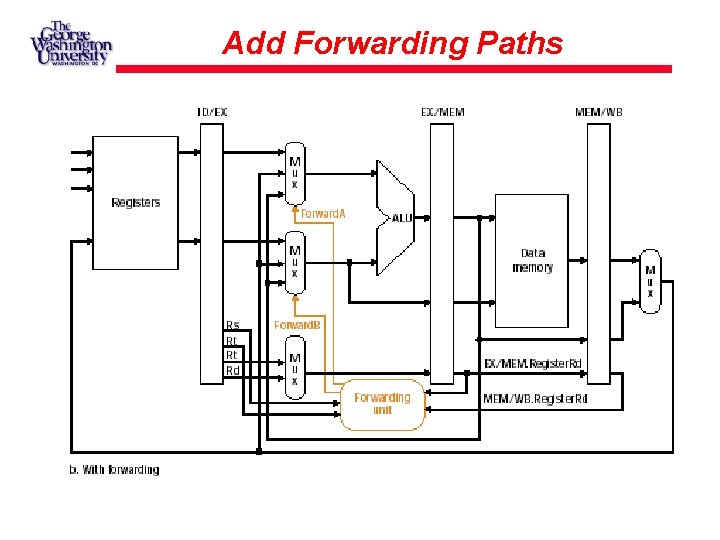

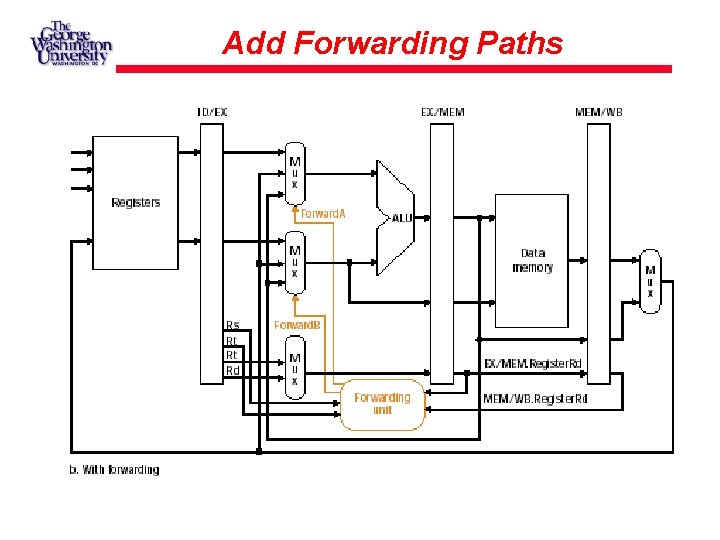

Add Forwarding Paths

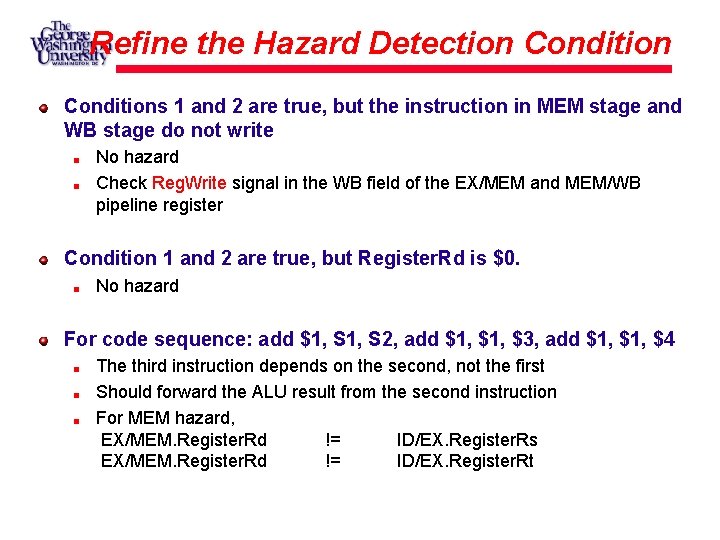

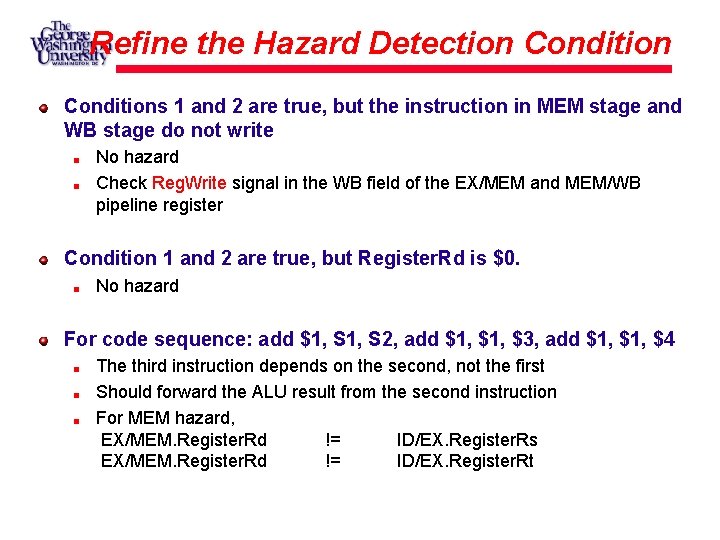

Refine the Hazard Detection Conditions 1 and 2 are true, but the instruction in MEM stage and WB stage do not write No hazard Check Reg. Write signal in the WB field of the EX/MEM and MEM/WB pipeline register Condition 1 and 2 are true, but Register. Rd is $0. No hazard For code sequence: add $1, S 2, add $1, $3, add $1, $4 The third instruction depends on the second, not the first Should forward the ALU result from the second instruction For MEM hazard, EX/MEM. Register. Rd != ID/EX. Register. Rs EX/MEM. Register. Rd != ID/EX. Register. Rt

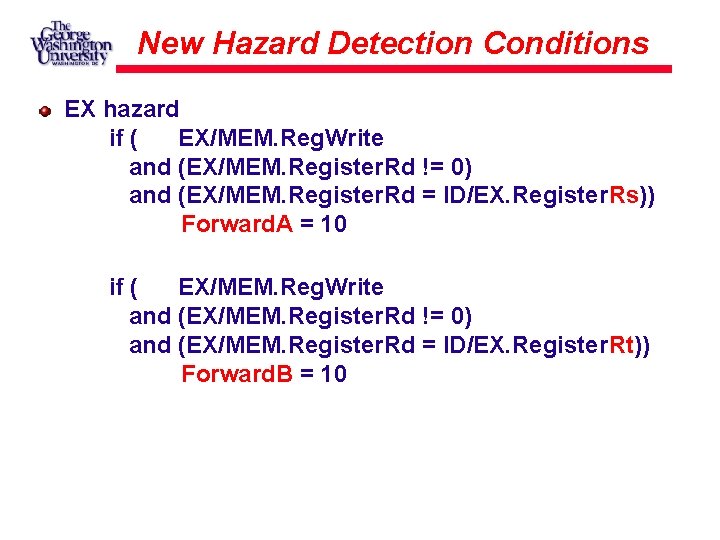

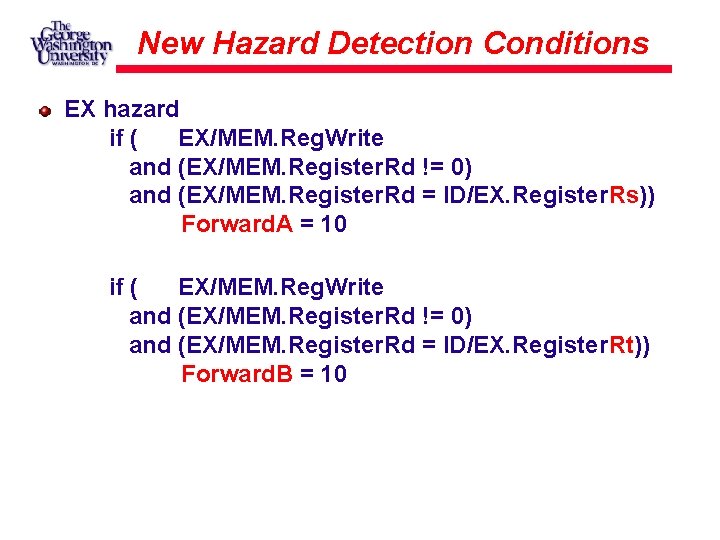

New Hazard Detection Conditions EX hazard if ( EX/MEM. Reg. Write and (EX/MEM. Register. Rd != 0) and (EX/MEM. Register. Rd = ID/EX. Register. Rs)) Forward. A = 10 if ( EX/MEM. Reg. Write and (EX/MEM. Register. Rd != 0) and (EX/MEM. Register. Rd = ID/EX. Register. Rt)) Forward. B = 10

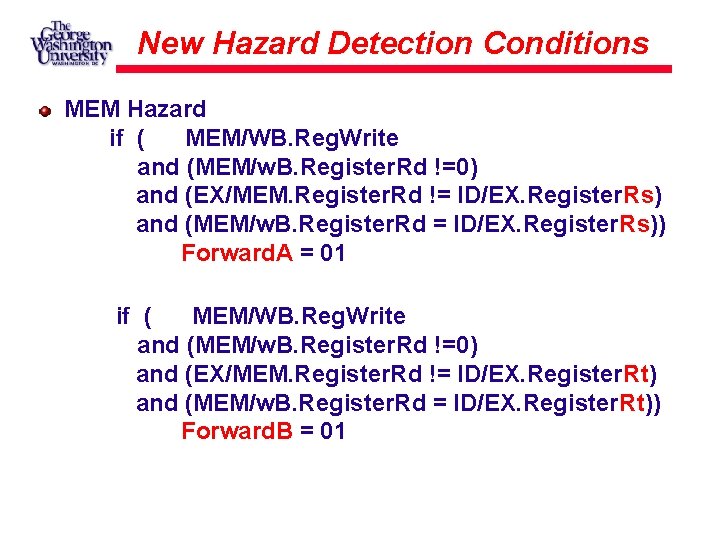

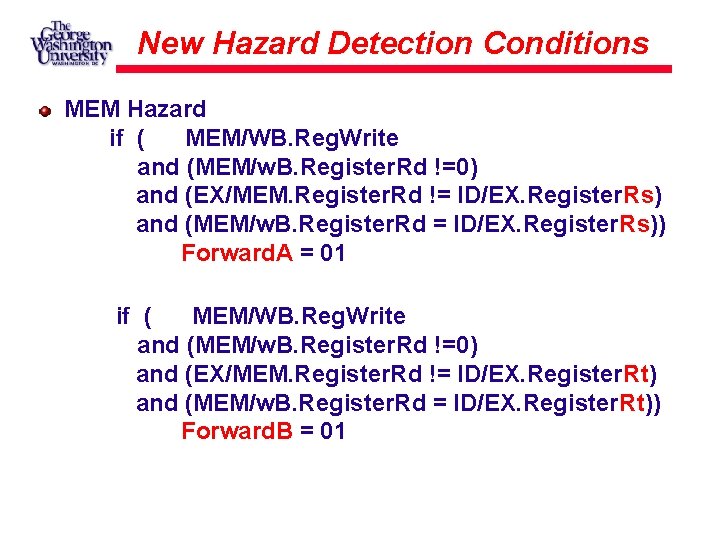

New Hazard Detection Conditions MEM Hazard if ( MEM/WB. Reg. Write and (MEM/w. B. Register. Rd !=0) and (EX/MEM. Register. Rd != ID/EX. Register. Rs) and (MEM/w. B. Register. Rd = ID/EX. Register. Rs)) Forward. A = 01 if ( MEM/WB. Reg. Write and (MEM/w. B. Register. Rd !=0) and (EX/MEM. Register. Rd != ID/EX. Register. Rt) and (MEM/w. B. Register. Rd = ID/EX. Register. Rt)) Forward. B = 01

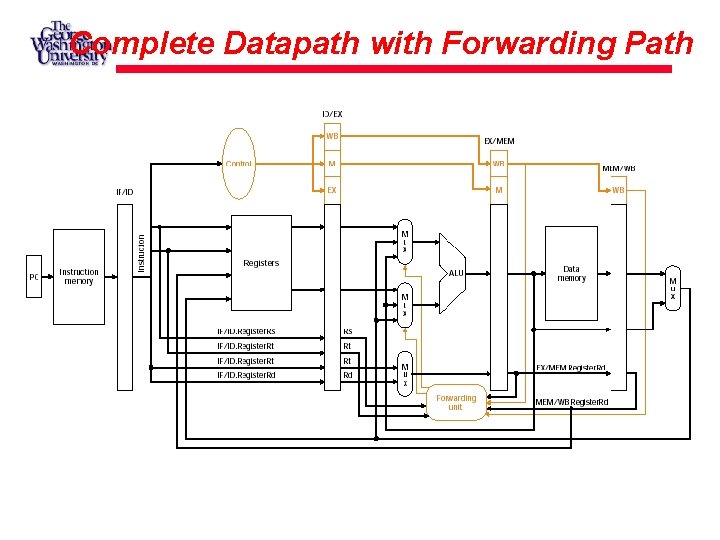

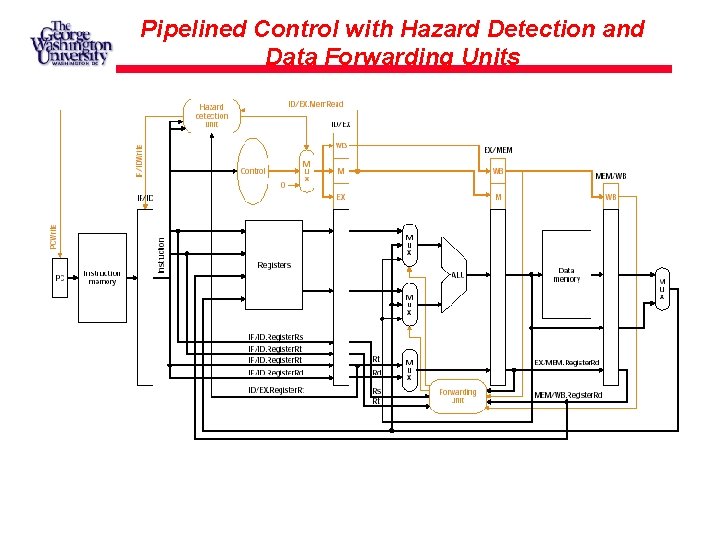

Complete Datapath with Forwarding Path

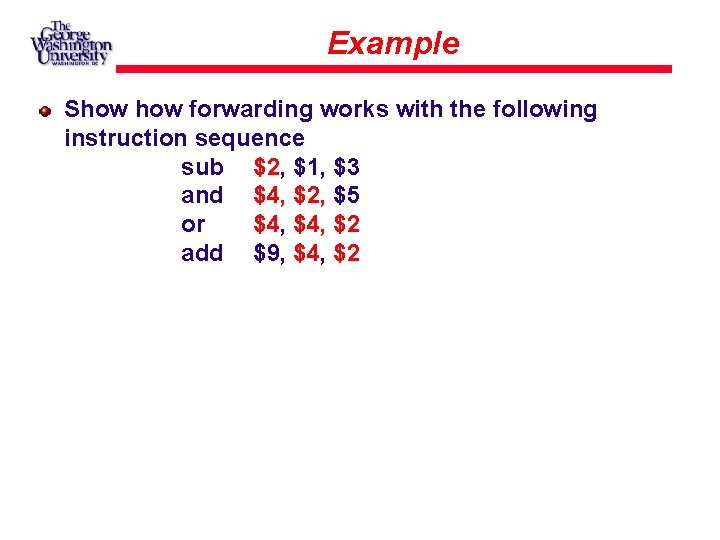

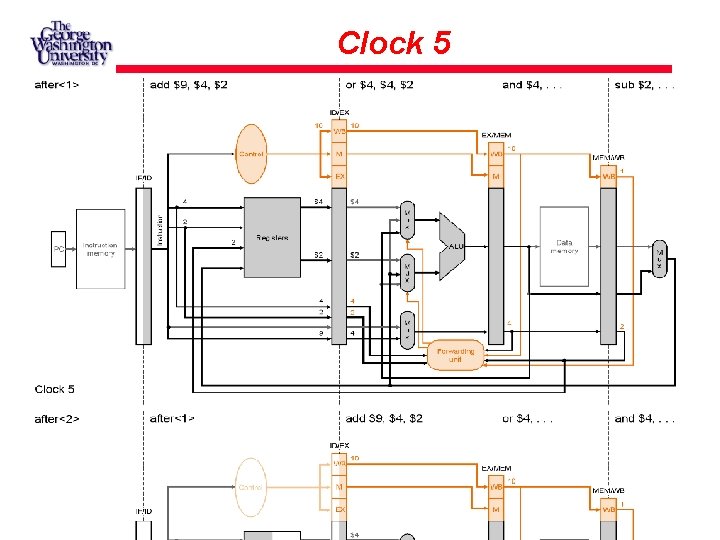

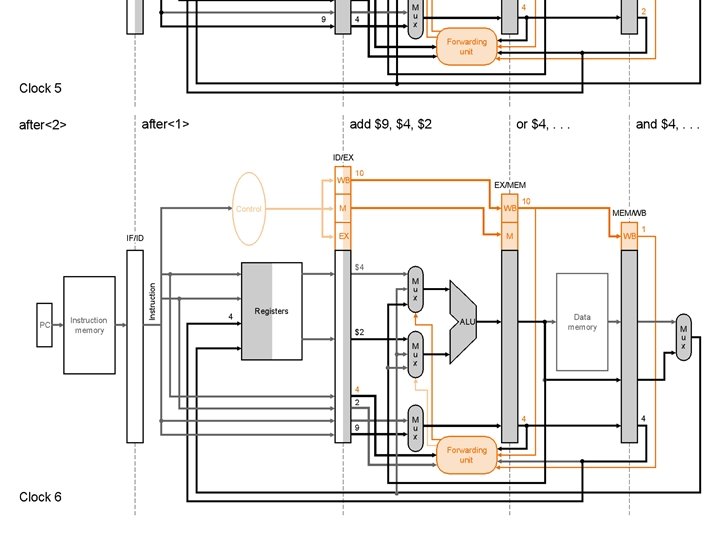

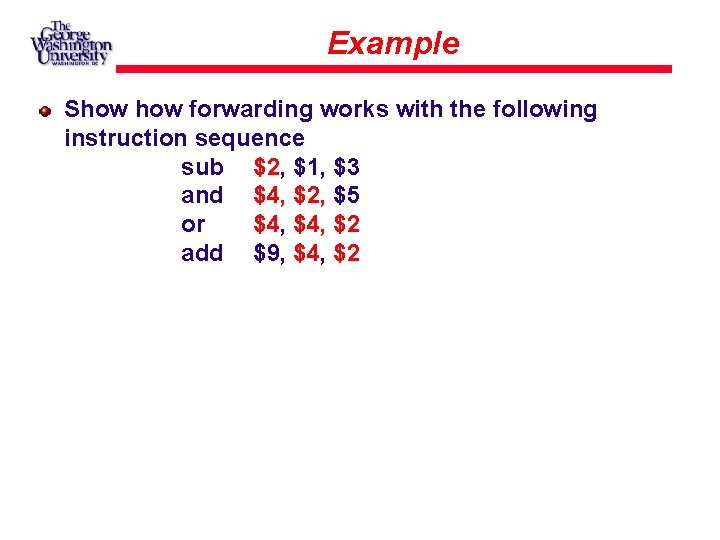

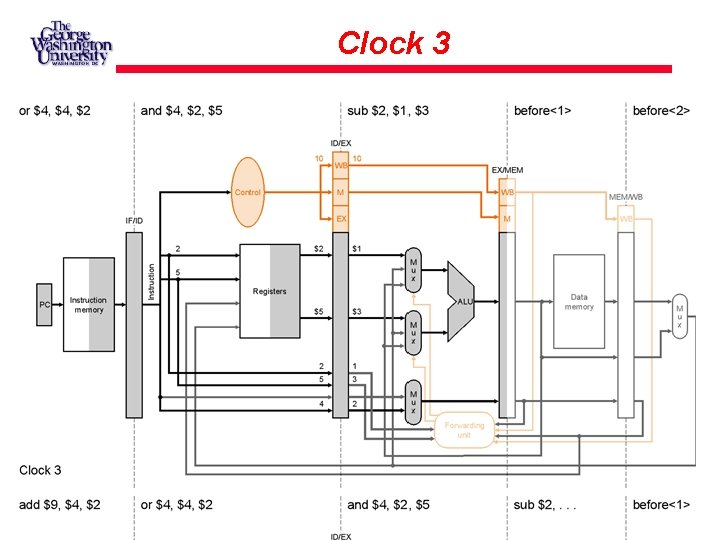

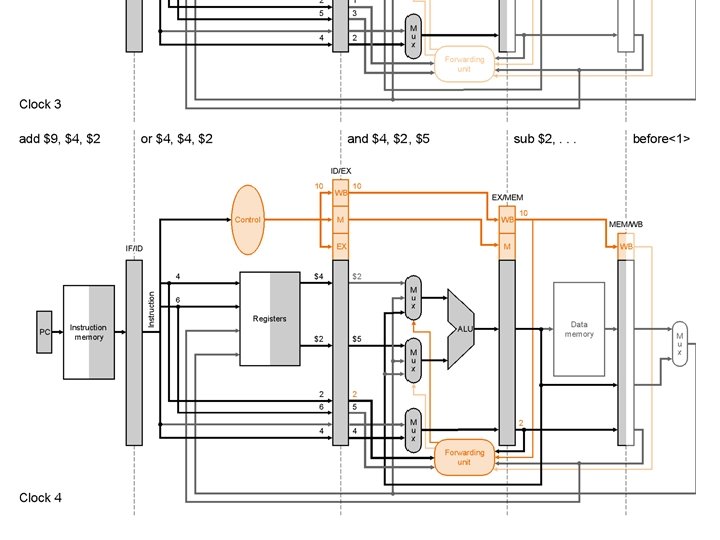

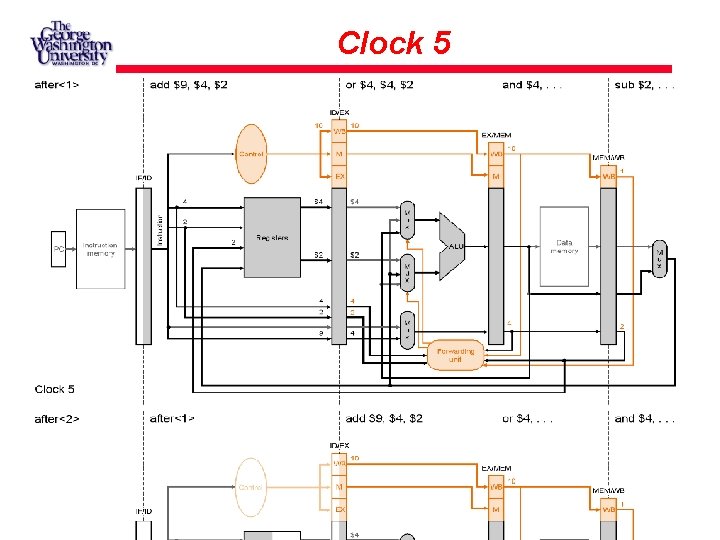

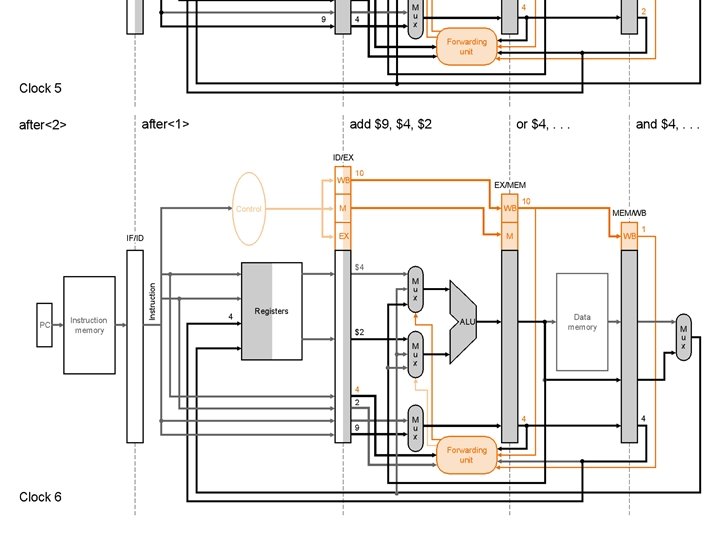

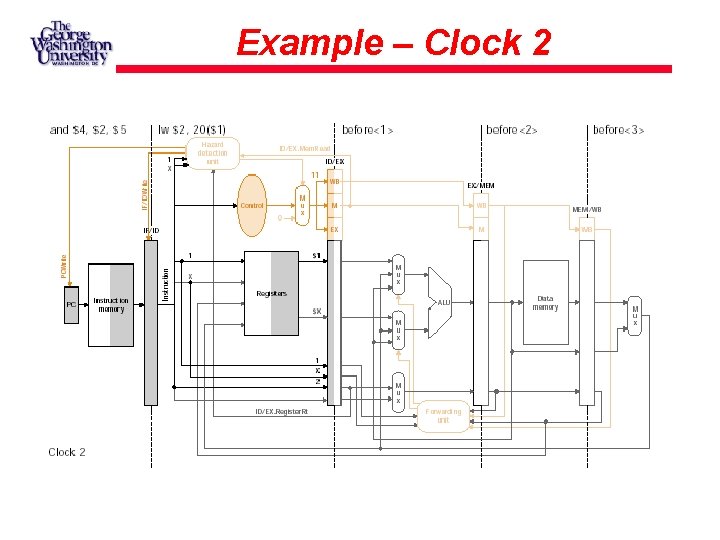

Example Show forwarding works with the following instruction sequence sub $2, $1, $3 and $4, $2, $5 or $4, $2 add $9, $4, $2

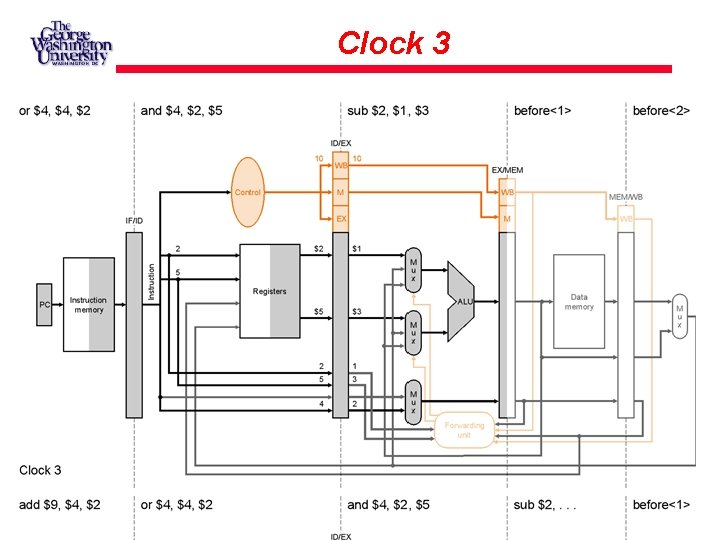

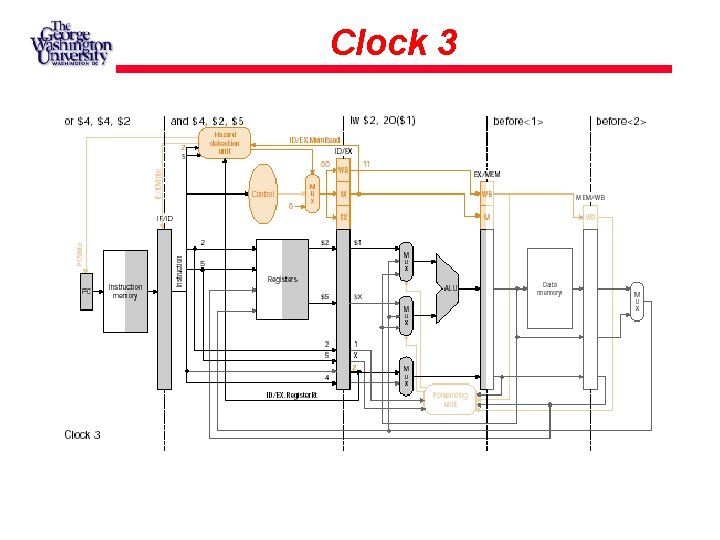

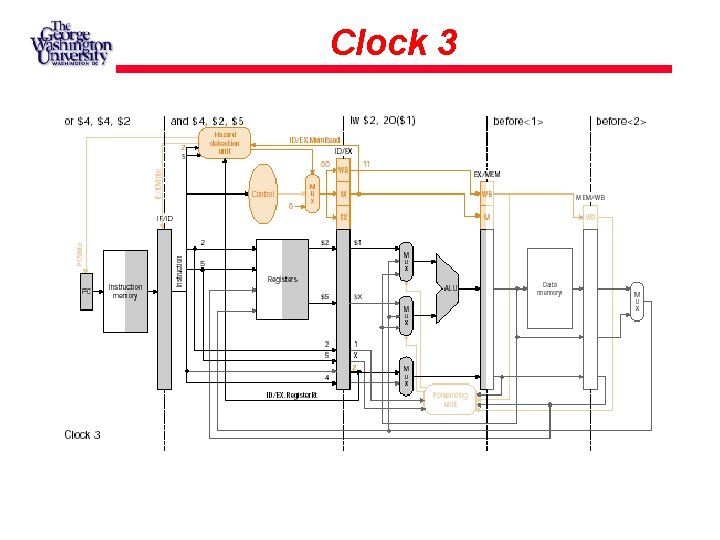

Clock 3

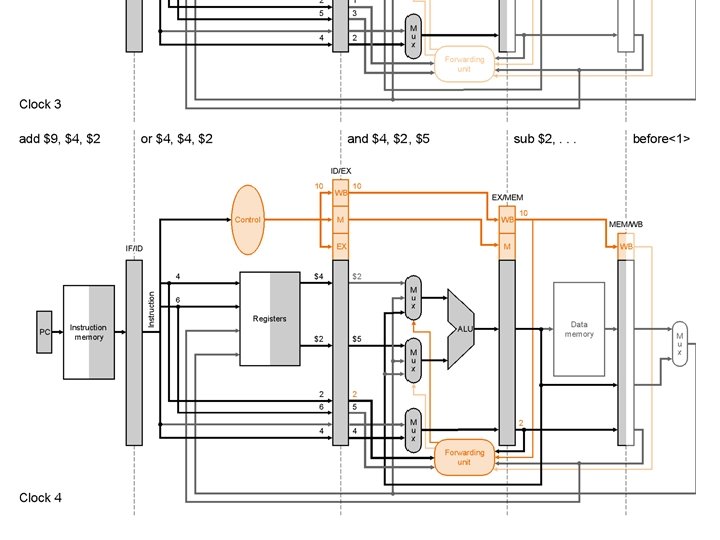

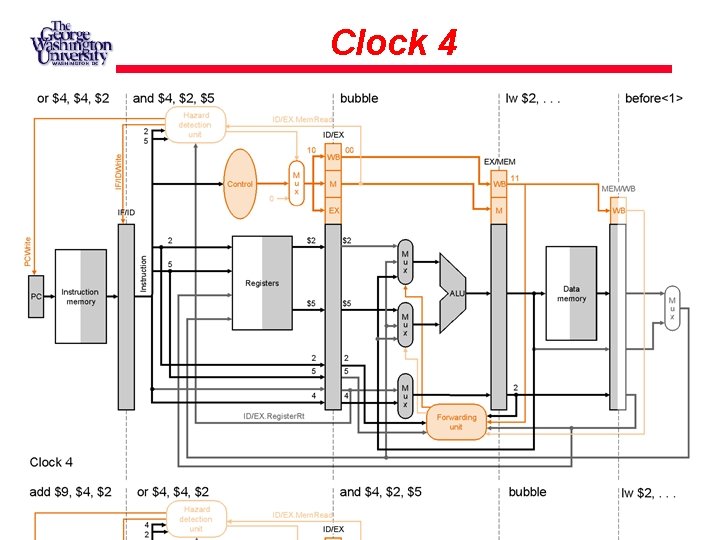

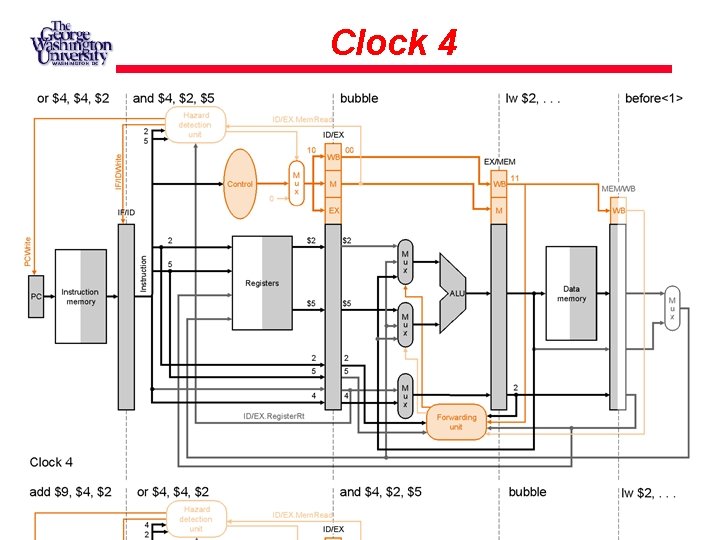

Clock 4

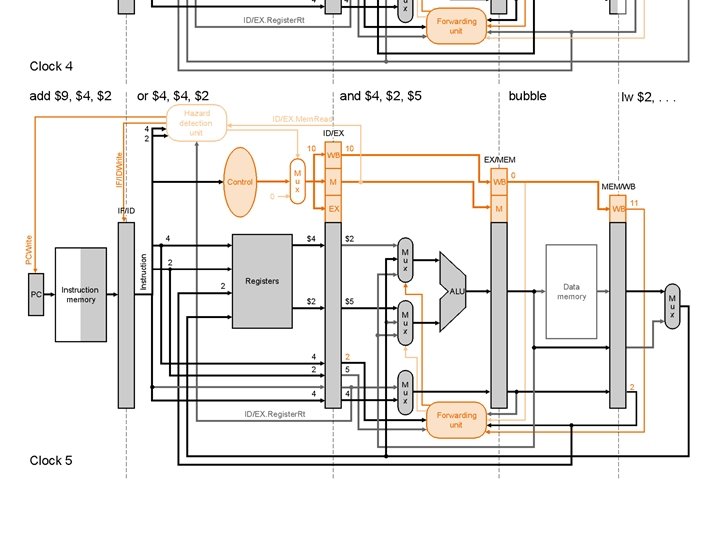

Clock 5

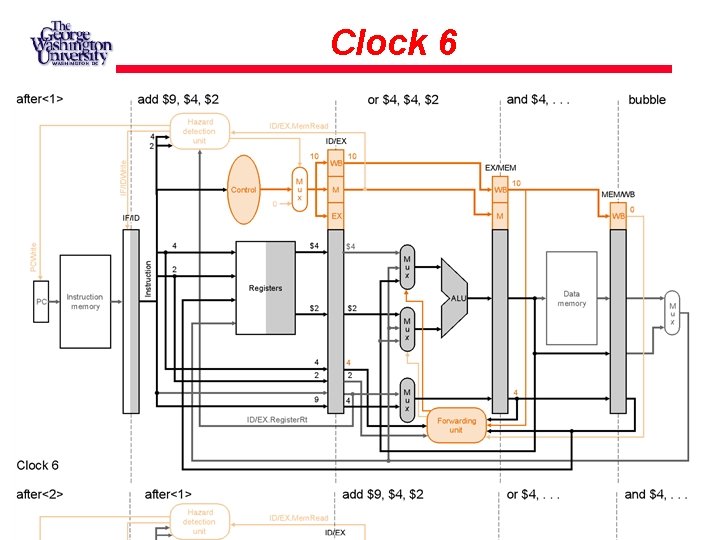

Clock 6

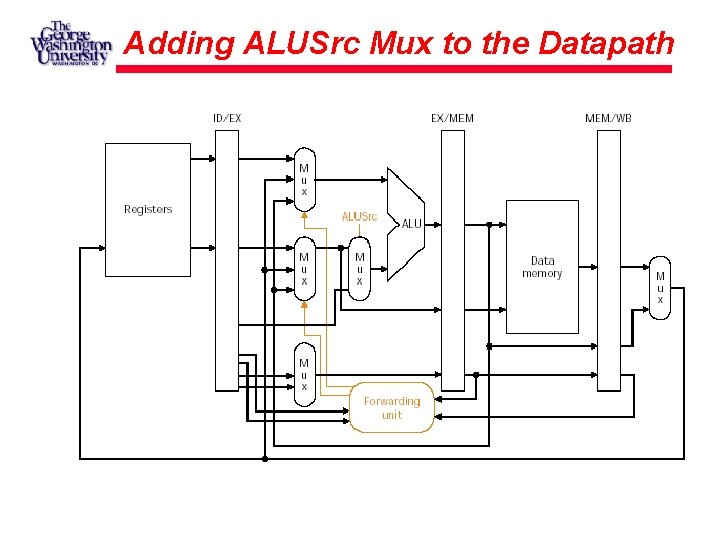

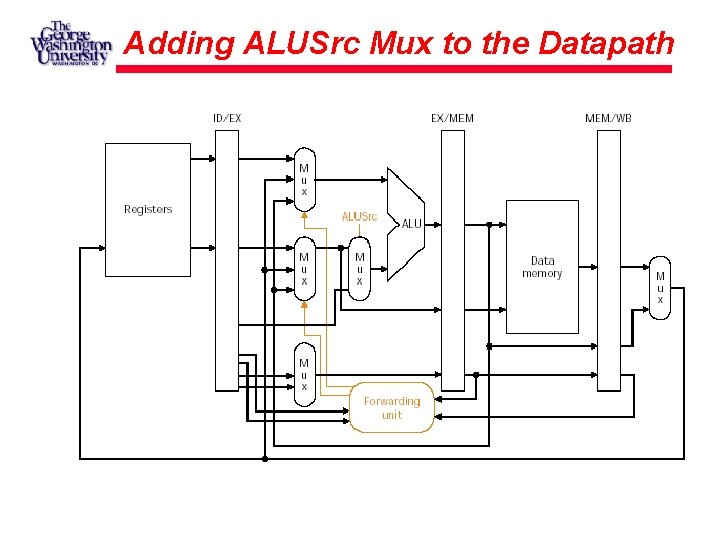

Adding ALUSrc Mux to the Datapath

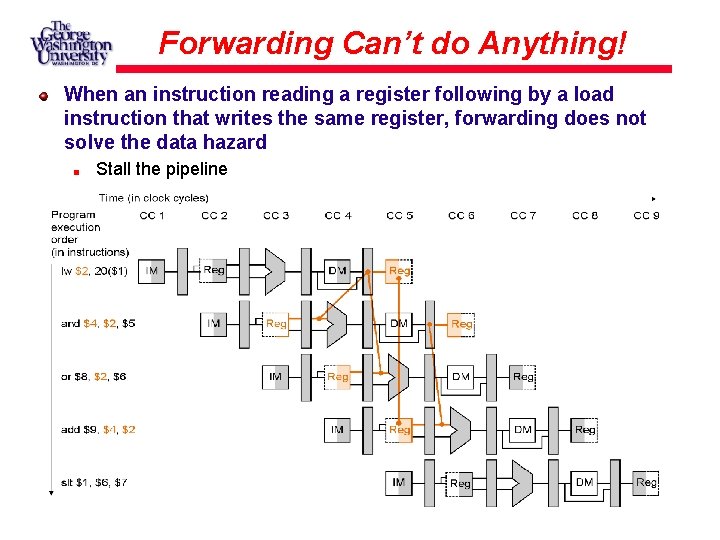

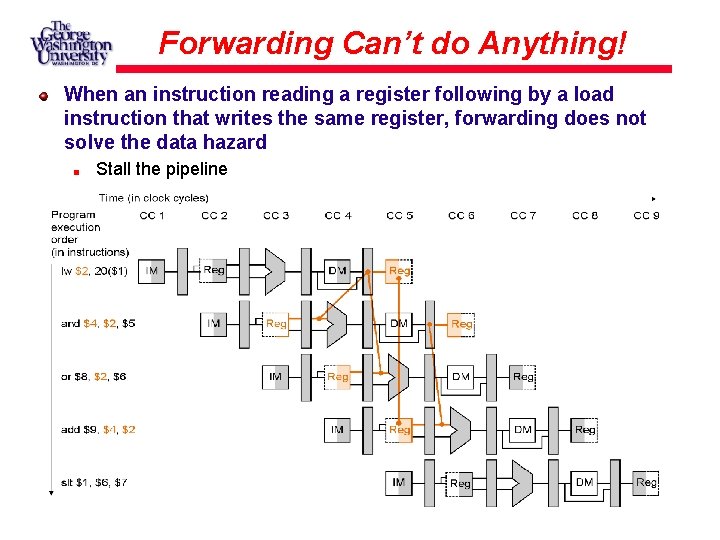

Forwarding Can’t do Anything! When an instruction reading a register following by a load instruction that writes the same register, forwarding does not solve the data hazard Stall the pipeline

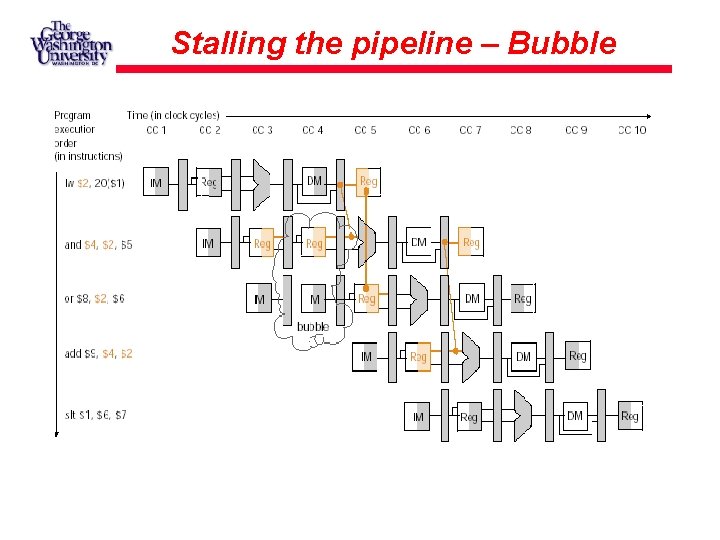

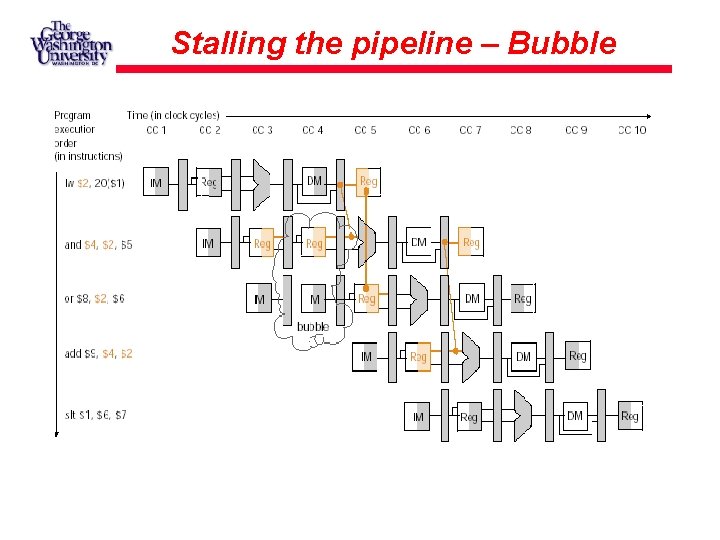

Stalling the pipeline – Bubble

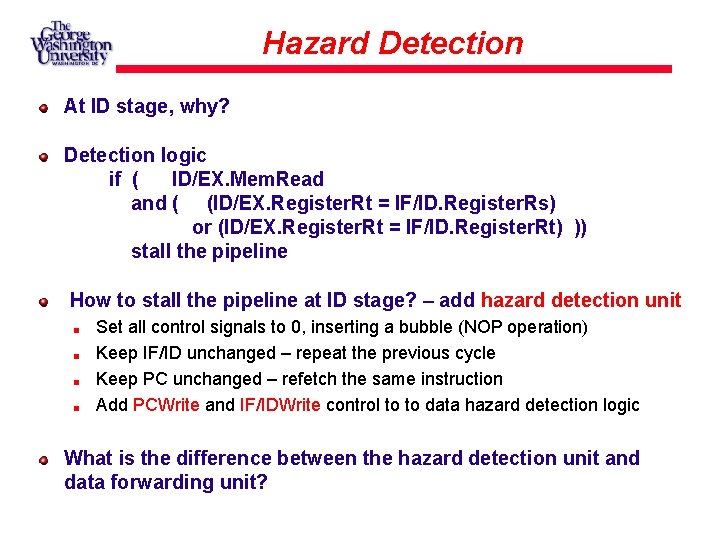

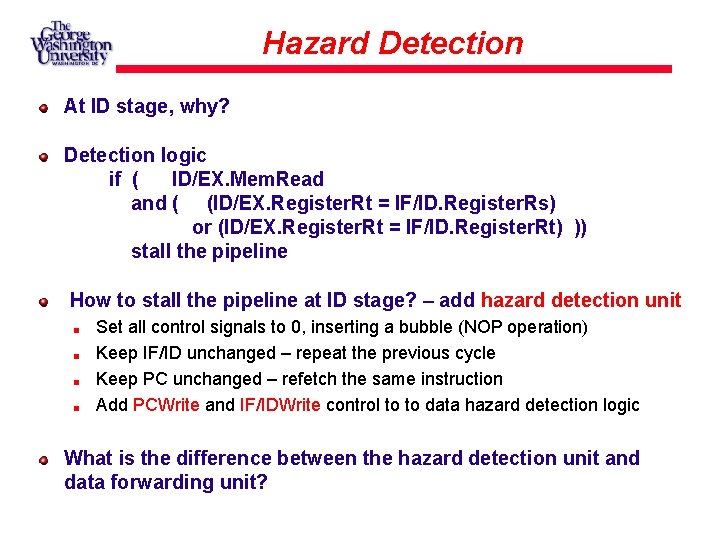

Hazard Detection At ID stage, why? Detection logic if ( ID/EX. Mem. Read and ( (ID/EX. Register. Rt = IF/ID. Register. Rs) or (ID/EX. Register. Rt = IF/ID. Register. Rt) )) stall the pipeline How to stall the pipeline at ID stage? – add hazard detection unit Set all control signals to 0, inserting a bubble (NOP operation) Keep IF/ID unchanged – repeat the previous cycle Keep PC unchanged – refetch the same instruction Add PCWrite and IF/IDWrite control to to data hazard detection logic What is the difference between the hazard detection unit and data forwarding unit?

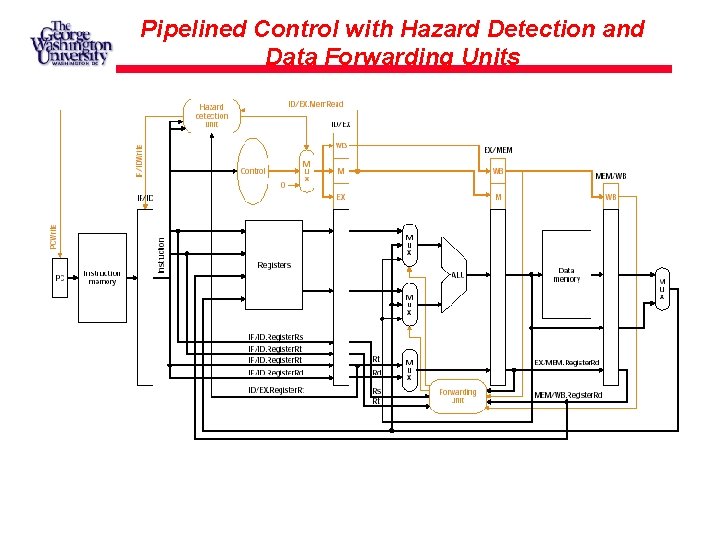

Pipelined Control with Hazard Detection and Data Forwarding Units

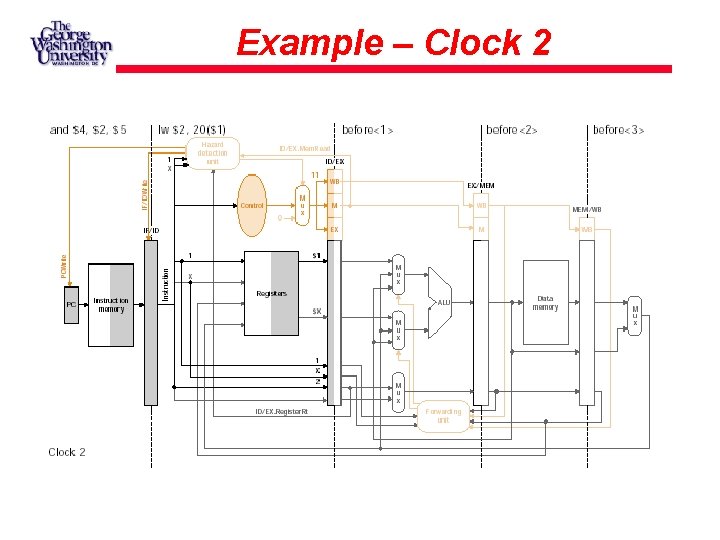

Example – Clock 2

Clock 3

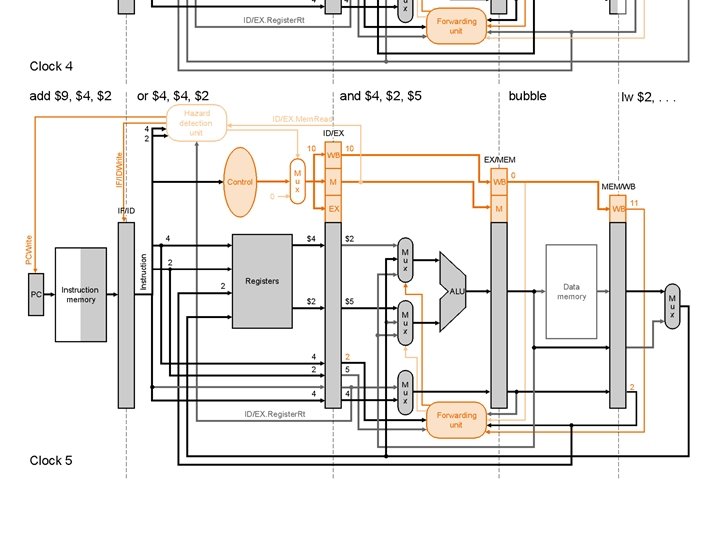

Clock 4

Clock 5

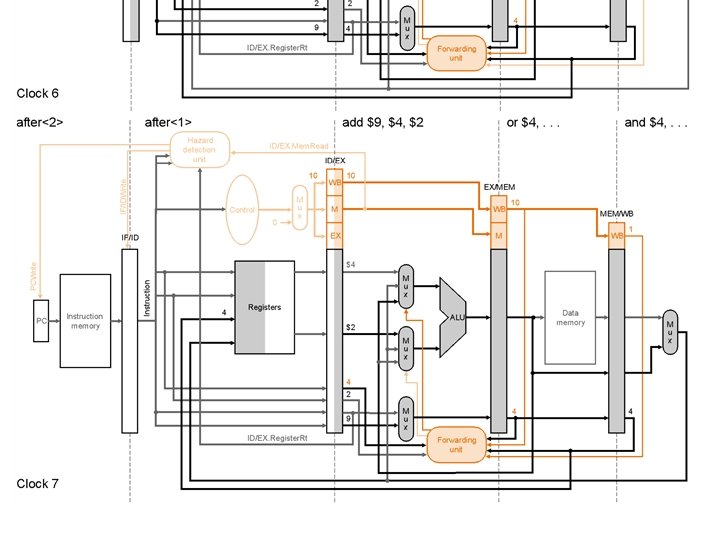

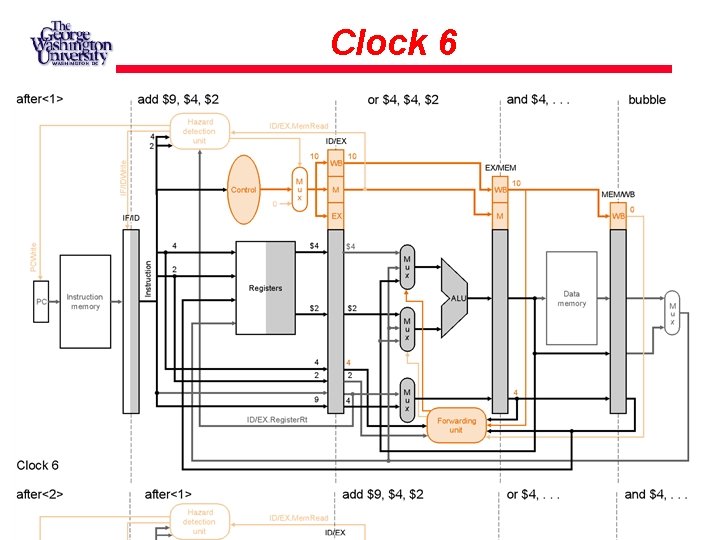

Clock 6

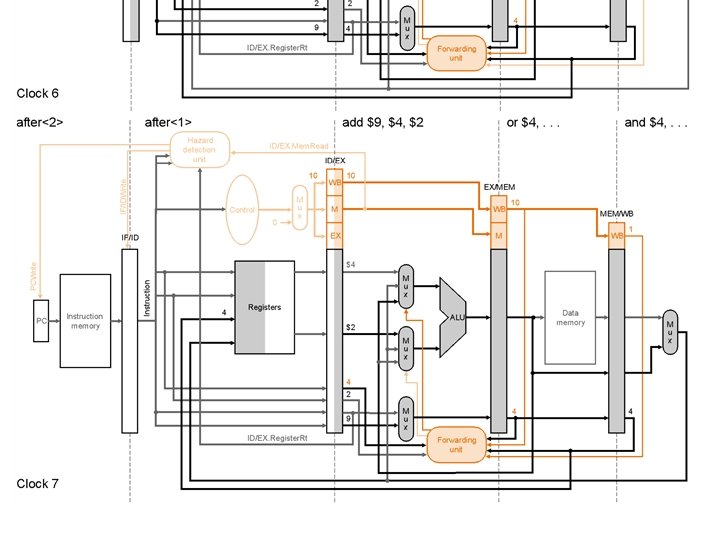

Clock 7

Questions?