COMBINATIONAL CIRCUITS USING TTL 74 XX ICS Study

COMBINATIONAL CIRCUITS USING TTL 74 XX ICS • • Study of logic gates using 74 XX ICs, Four-bit parallel adder(IC 7483), Comparator(IC 7485), Decoder(IC 74138, IC 74154), BCD-to-7 -segment decoder(IC 7447), Encoder(IC 74147), Multiplexer(IC 74151), Demultiplexer (IC 74154).

Four-bit Parallel Adder IC 7483

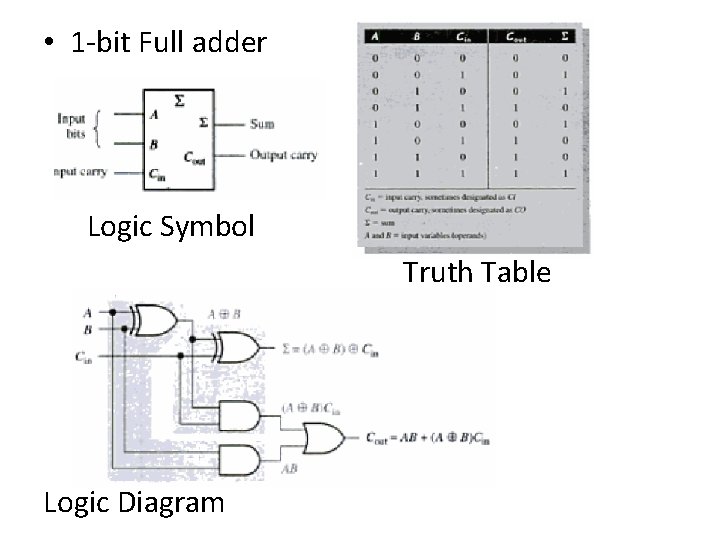

• 1 -bit Full adder Logic Symbol Truth Table Logic Diagram

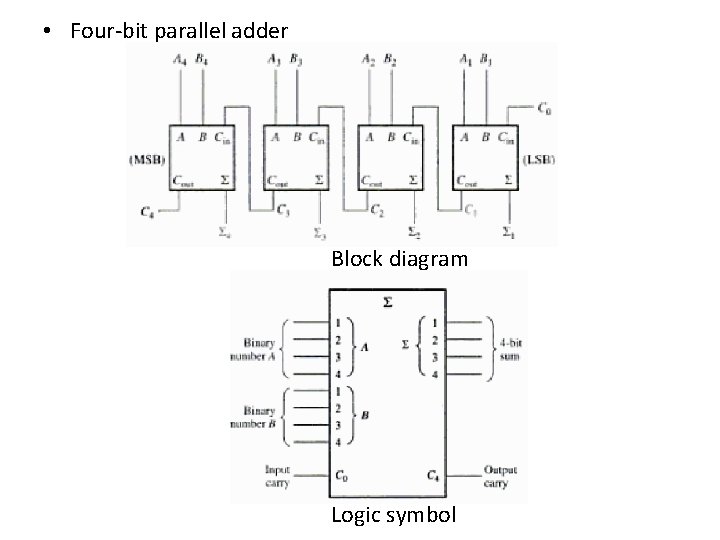

• Four-bit parallel adder Block diagram Logic symbol

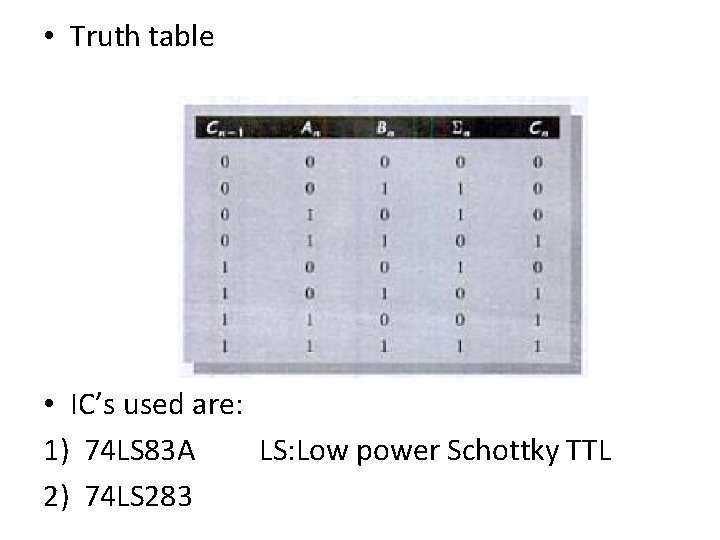

• Truth table • IC’s used are: 1) 74 LS 83 A LS: Low power Schottky TTL 2) 74 LS 283

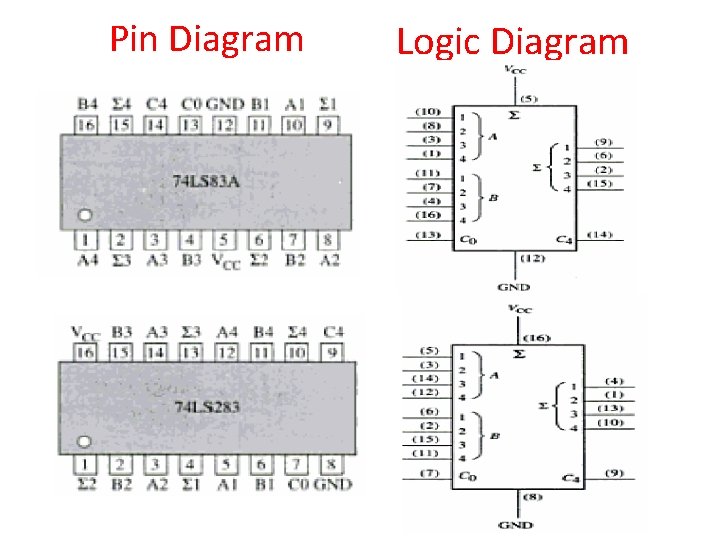

Pin Diagram Logic Diagram

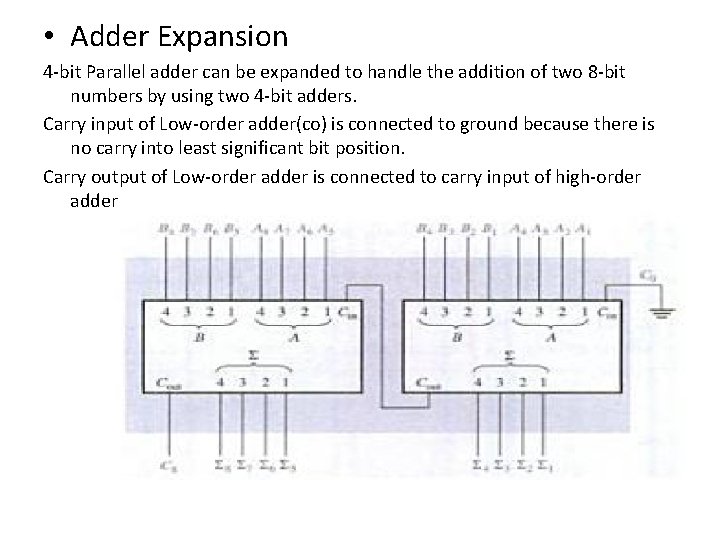

• Adder Expansion 4 -bit Parallel adder can be expanded to handle the addition of two 8 -bit numbers by using two 4 -bit adders. Carry input of Low-order adder(co) is connected to ground because there is no carry into least significant bit position. Carry output of Low-order adder is connected to carry input of high-order adder.

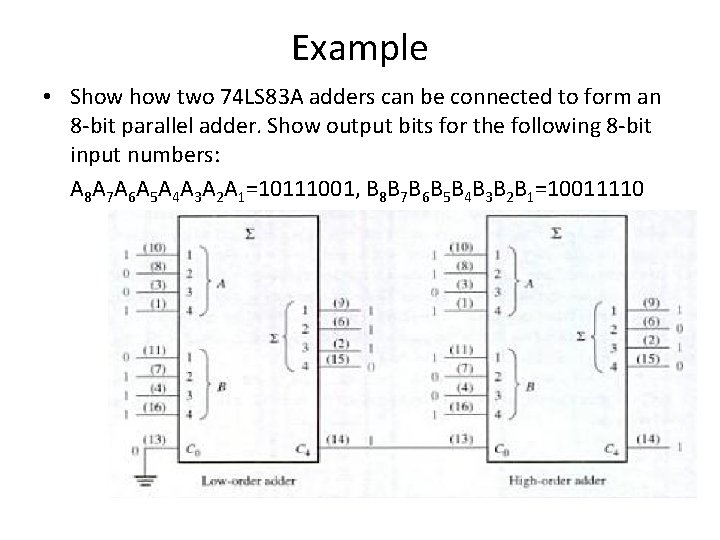

Example • Show two 74 LS 83 A adders can be connected to form an 8 -bit parallel adder. Show output bits for the following 8 -bit input numbers: A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1=10111001, B 8 B 7 B 6 B 5 B 4 B 3 B 2 B 1=10011110

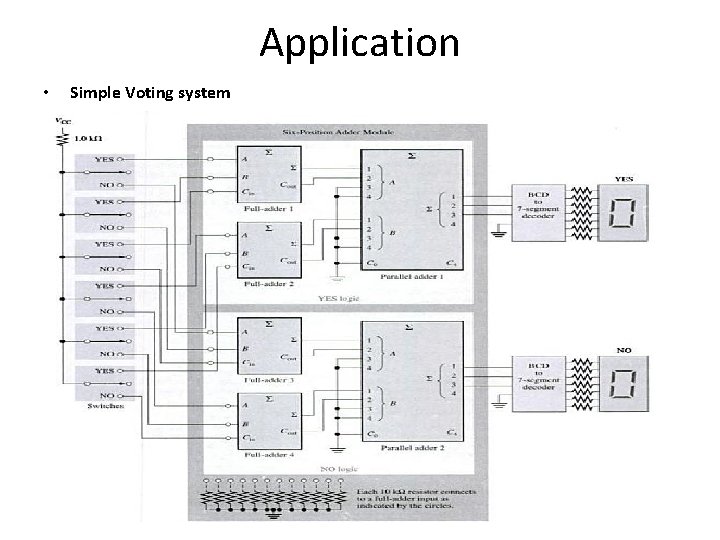

Application • Simple Voting system

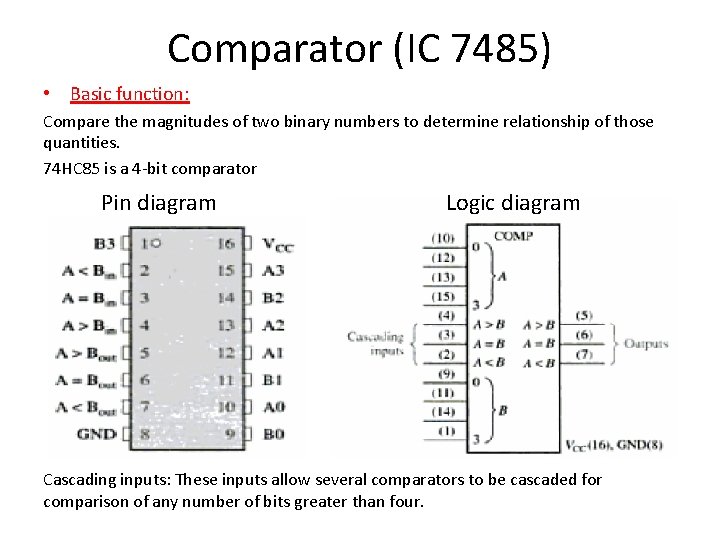

Comparator (IC 7485) • Basic function: Compare the magnitudes of two binary numbers to determine relationship of those quantities. 74 HC 85 is a 4 -bit comparator Pin diagram Logic diagram Cascading inputs: These inputs allow several comparators to be cascaded for comparison of any number of bits greater than four.

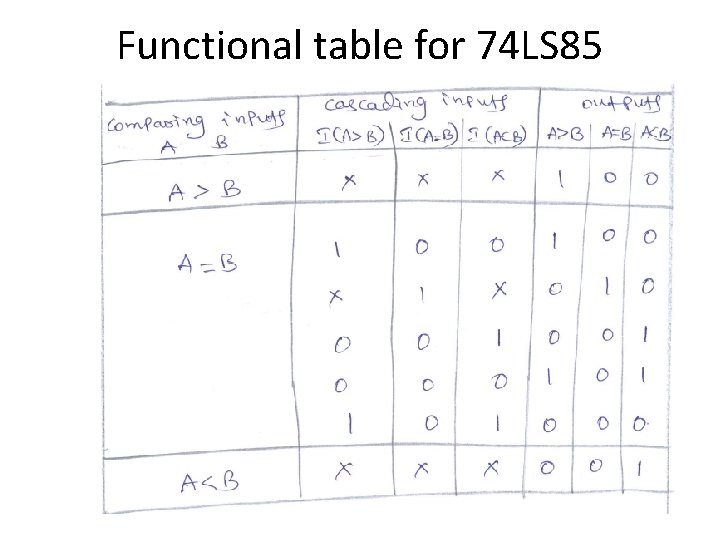

Functional table for 74 LS 85

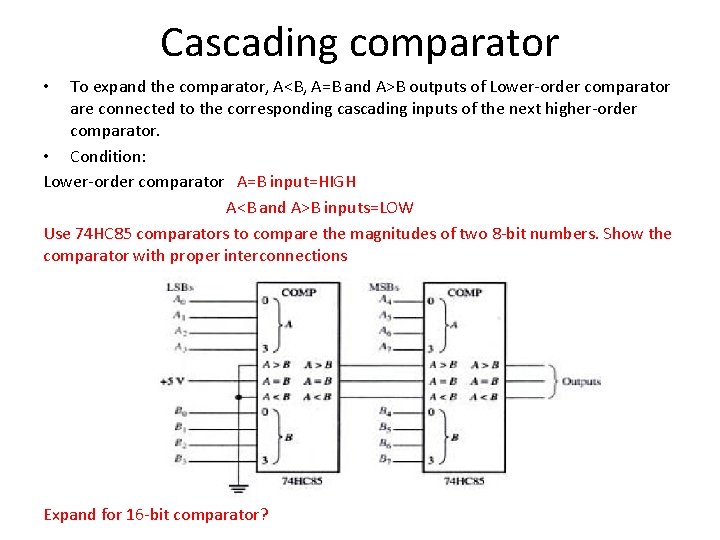

Cascading comparator To expand the comparator, A<B, A=B and A>B outputs of Lower-order comparator are connected to the corresponding cascading inputs of the next higher-order comparator. • Condition: Lower-order comparator A=B input=HIGH A<B and A>B inputs=LOW Use 74 HC 85 comparators to compare the magnitudes of two 8 -bit numbers. Show the comparator with proper interconnections • Expand for 16 -bit comparator?

Problems 1) The binary numbers A=1011 and B=1010 are applied to the inputs of 74 LS 85. Determine the outputs. 2) The binary numbers A=11001011 and B=11010100 are applied to 8 -bit comparator. Determine the states of output pins 5, 6 and 7 on each 74 LS 85.

Decoder(IC 74138, IC 74154) Basic function: To detect the presence of a specified combination of bits(code) on its inputs and to indicate the presence of that code by a specified output level. It has n inputs to handle n bits and from one to 2 n output lines to indicate the presence of one or more n-bit combinations. Applications: 1) It is used to implement Combinational circuit. 2) It is used to convert BCD to 7 -segment code. 3) It is used in memories to select particular register.

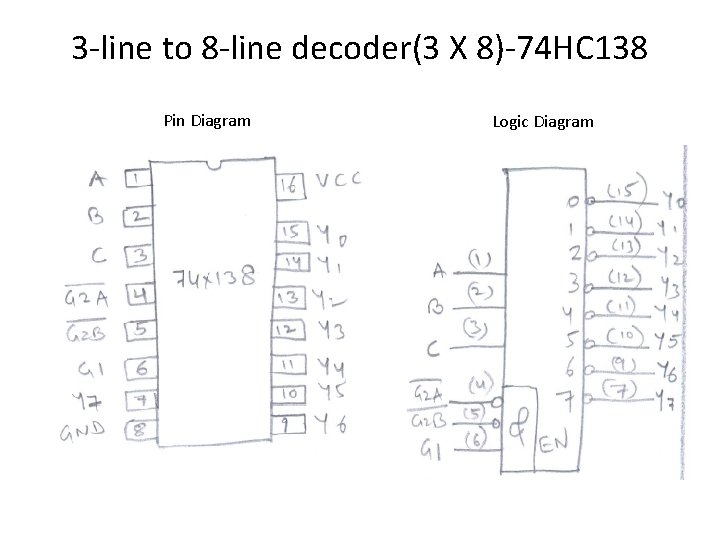

3 -line to 8 -line decoder(3 X 8)-74 HC 138 Pin Diagram Logic Diagram

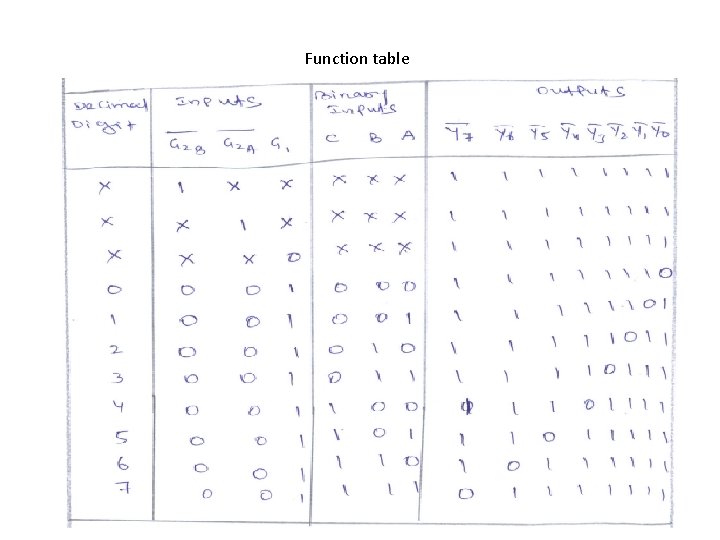

Function table

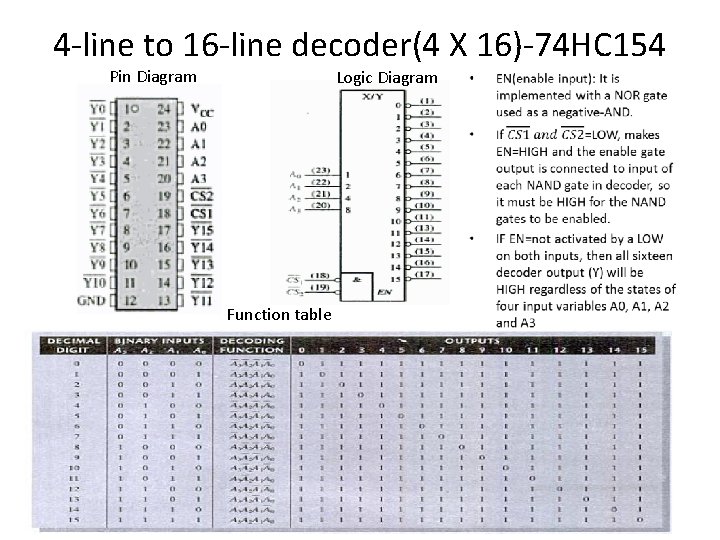

4 -line to 16 -line decoder(4 X 16)-74 HC 154 Pin Diagram Logic Diagram Function table

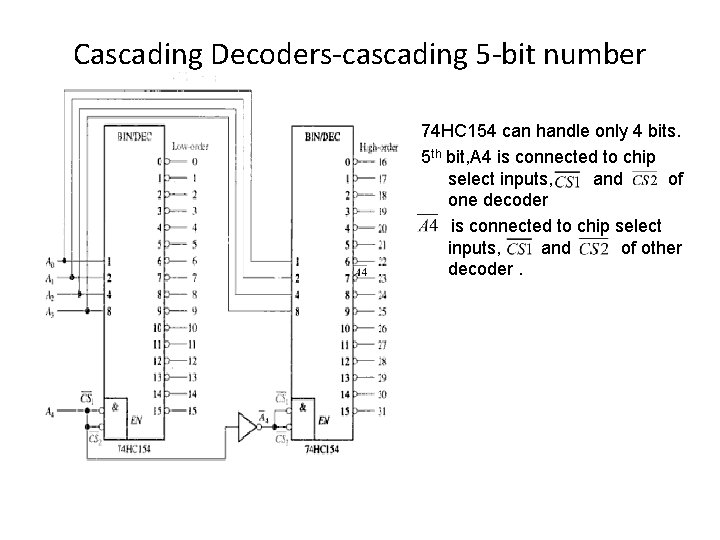

Cascading Decoders-cascading 5 -bit number 74 HC 154 can handle only 4 bits. 5 th bit, A 4 is connected to chip select inputs, and of one decoder is connected to chip select inputs, and of other decoder.

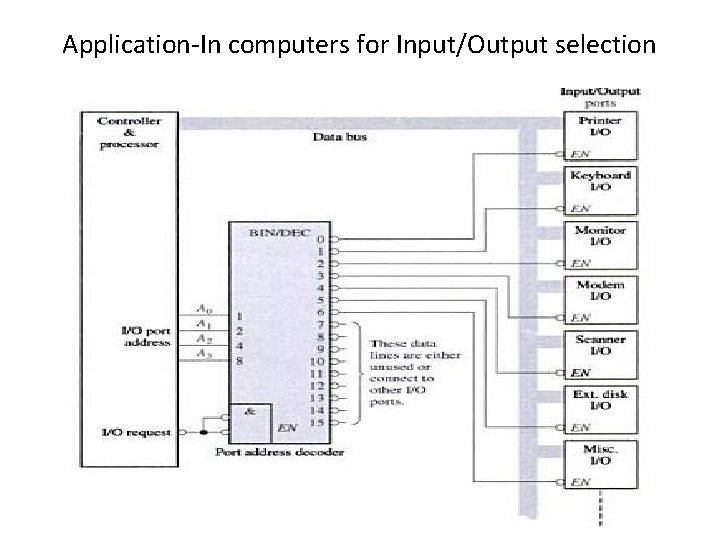

Application-In computers for Input/Output selection

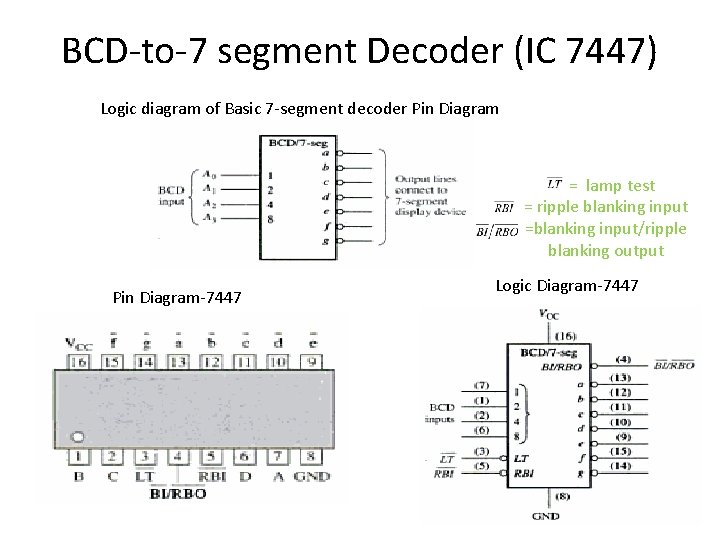

BCD-to-7 segment Decoder (IC 7447) Logic diagram of Basic 7 -segment decoder Pin Diagram = lamp test = ripple blanking input =blanking input/ripple blanking output Pin Diagram-7447 Logic Diagram-7447

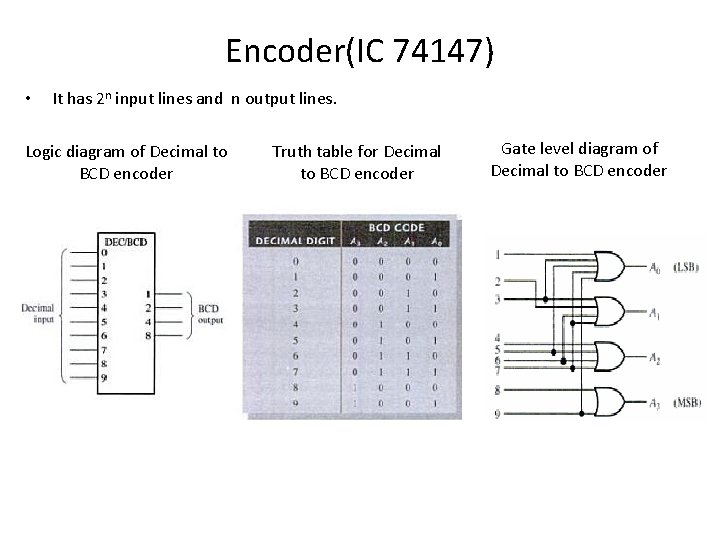

Encoder(IC 74147) • It has 2 n input lines and n output lines. Logic diagram of Decimal to BCD encoder Truth table for Decimal to BCD encoder Gate level diagram of Decimal to BCD encoder

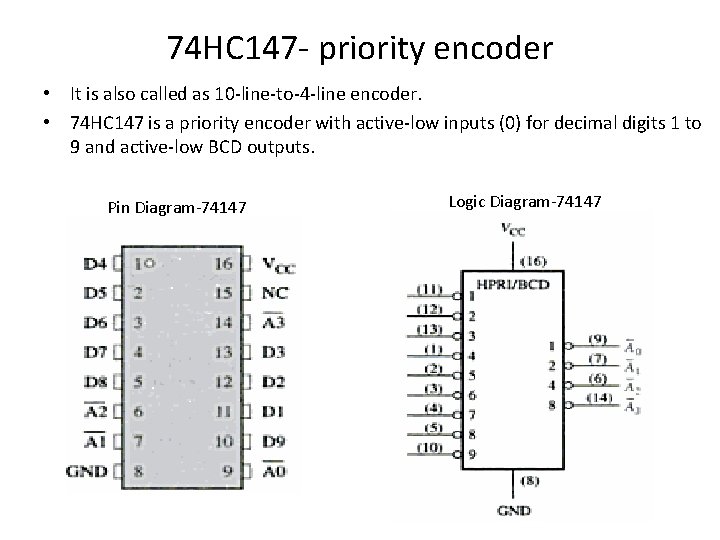

74 HC 147 - priority encoder • It is also called as 10 -line-to-4 -line encoder. • 74 HC 147 is a priority encoder with active-low inputs (0) for decimal digits 1 to 9 and active-low BCD outputs. Pin Diagram-74147 Logic Diagram-74147

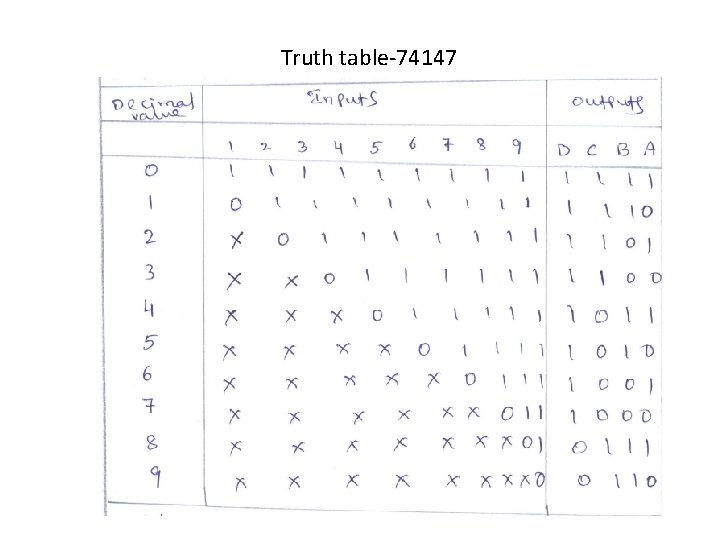

Truth table-74147

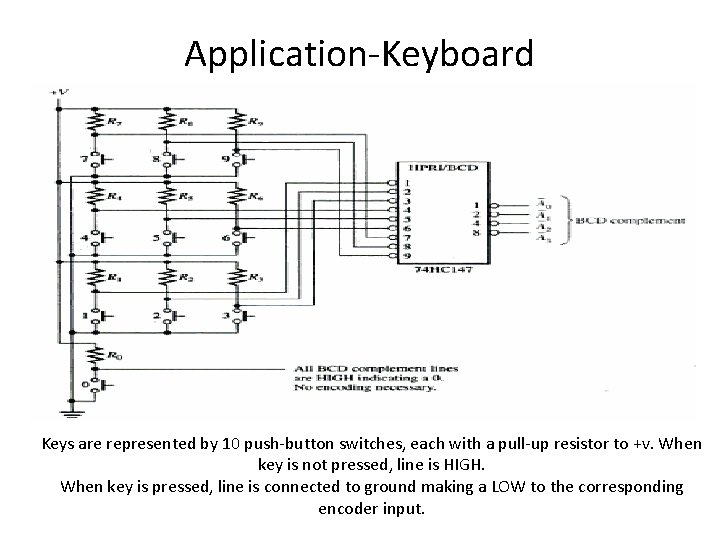

Application-Keyboard Keys are represented by 10 push-button switches, each with a pull-up resistor to +v. When key is not pressed, line is HIGH. When key is pressed, line is connected to ground making a LOW to the corresponding encoder input.

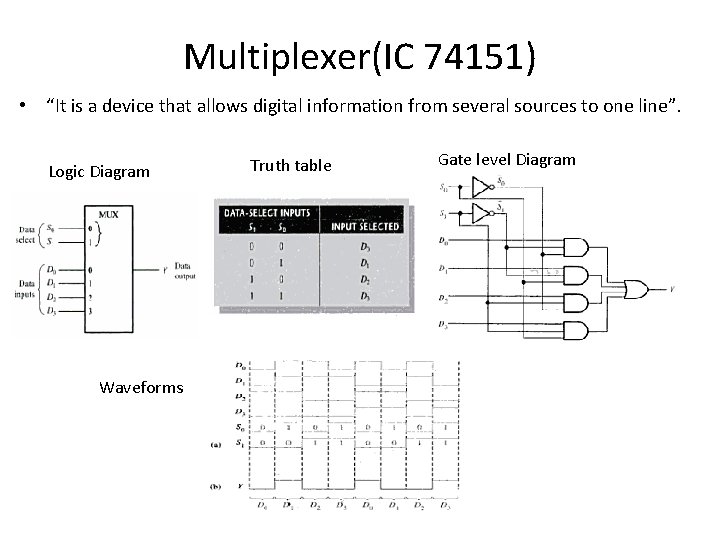

Multiplexer(IC 74151) • “It is a device that allows digital information from several sources to one line”. Logic Diagram Waveforms Truth table Gate level Diagram

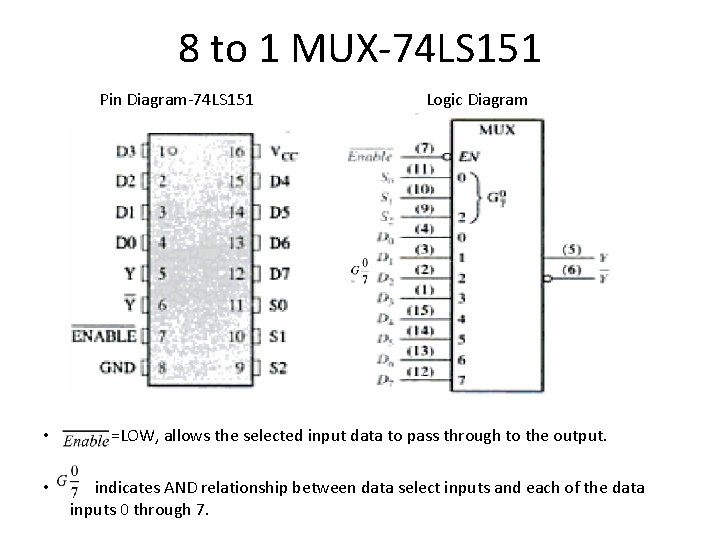

8 to 1 MUX-74 LS 151 Pin Diagram-74 LS 151 Logic Diagram • =LOW, allows the selected input data to pass through to the output. • indicates AND relationship between data select inputs and each of the data inputs 0 through 7.

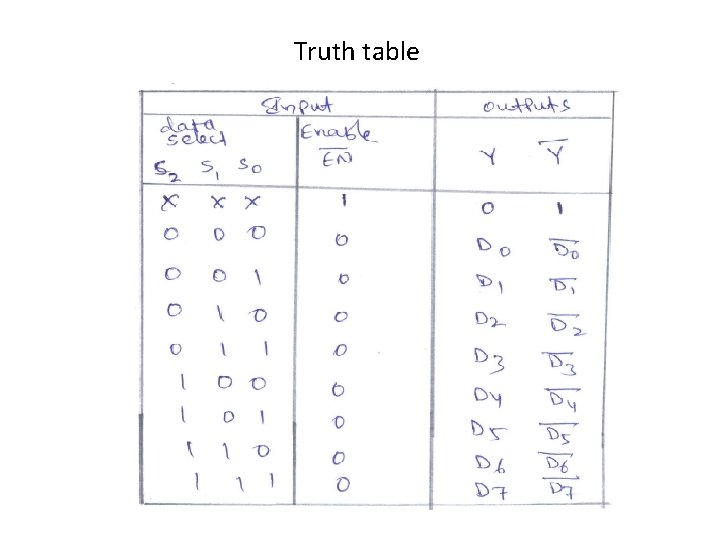

Truth table

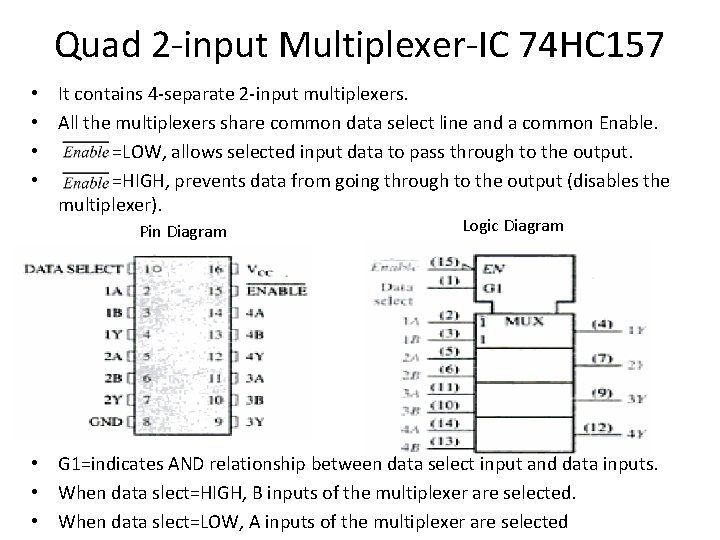

Quad 2 -input Multiplexer-IC 74 HC 157 • It contains 4 -separate 2 -input multiplexers. • All the multiplexers share common data select line and a common Enable. • =LOW, allows selected input data to pass through to the output. • =HIGH, prevents data from going through to the output (disables the multiplexer). Pin Diagram Logic Diagram • G 1=indicates AND relationship between data select input and data inputs. • When data slect=HIGH, B inputs of the multiplexer are selected. • When data slect=LOW, A inputs of the multiplexer are selected

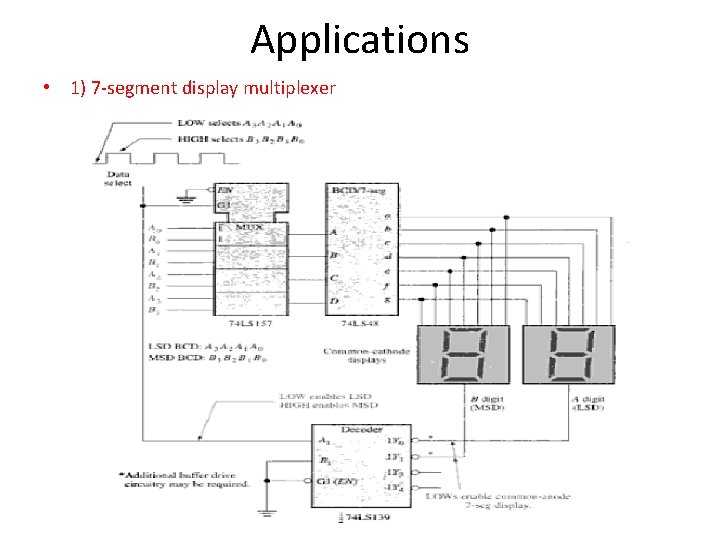

Applications • 1) 7 -segment display multiplexer

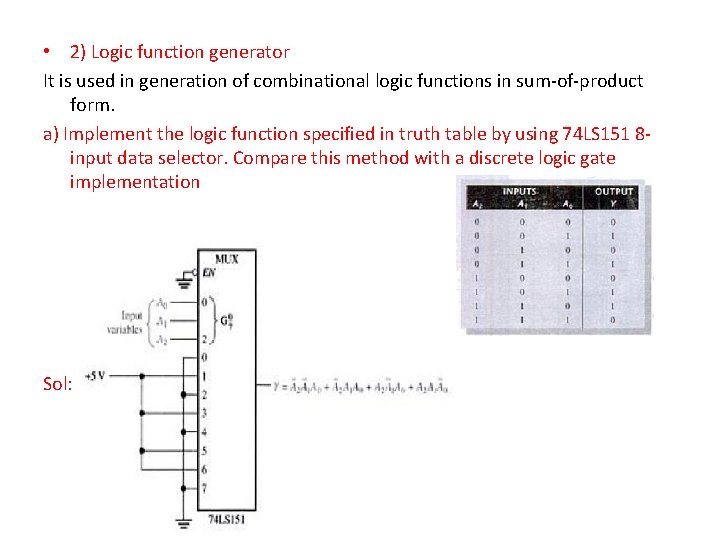

• 2) Logic function generator It is used in generation of combinational logic functions in sum-of-product form. a) Implement the logic function specified in truth table by using 74 LS 151 8 input data selector. Compare this method with a discrete logic gate implementation Sol:

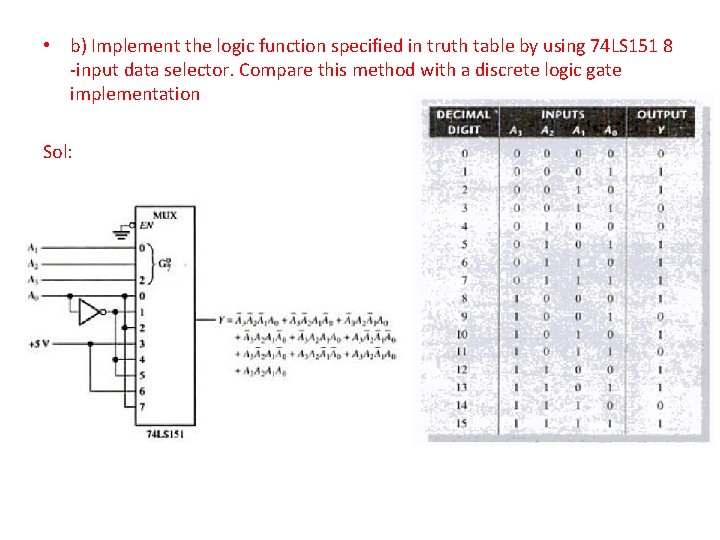

• b) Implement the logic function specified in truth table by using 74 LS 151 8 -input data selector. Compare this method with a discrete logic gate implementation Sol:

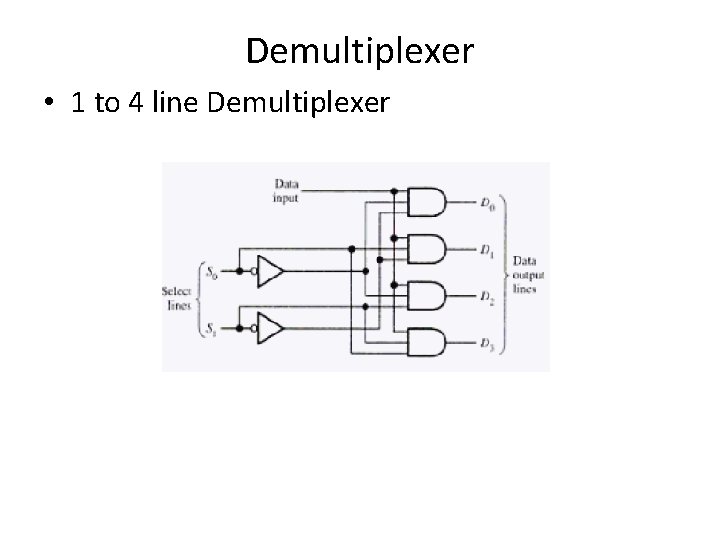

Demultiplexer • 1 to 4 line Demultiplexer

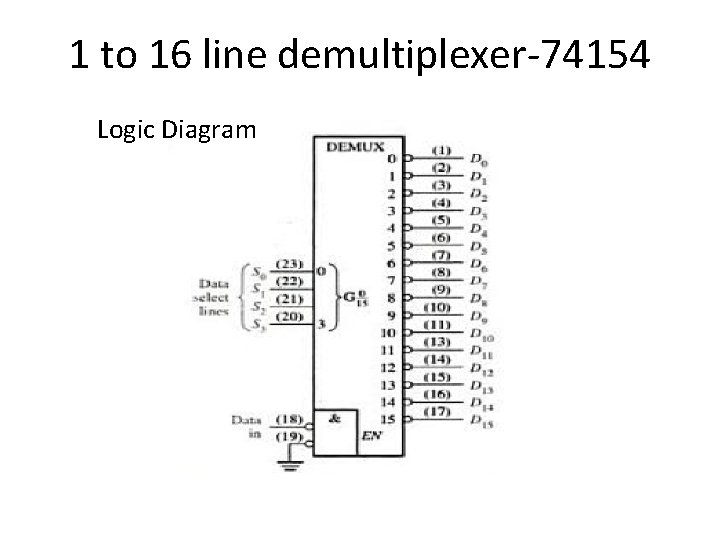

1 to 16 line demultiplexer-74154 Logic Diagram

- Slides: 33