Bramki logiczne w standardzie TTL Bramki logiczne w

Bramki logiczne w standardzie TTL

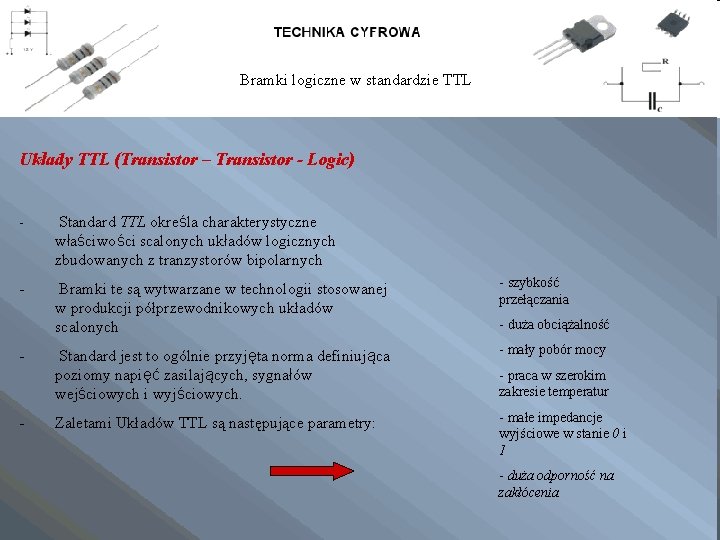

Bramki logiczne w standardzie TTL Układy TTL (Transistor – Transistor - Logic) - Standard TTL określa charakterystyczne właściwości scalonych układów logicznych zbudowanych z tranzystorów bipolarnych - Bramki te są wytwarzane w technologii stosowanej w produkcji półprzewodnikowych układów scalonych - szybkość przełączania Standard jest to ogólnie przyjęta norma definiująca poziomy napięć zasilających, sygnałów wejściowych i wyjściowych. - mały pobór mocy Zaletami Układów TTL są następujące parametry: - małe impedancje wyjściowe w stanie 0 i 1 - - - duża obciążalność - praca w szerokim zakresie temperatur - duża odporność na zakłócenia

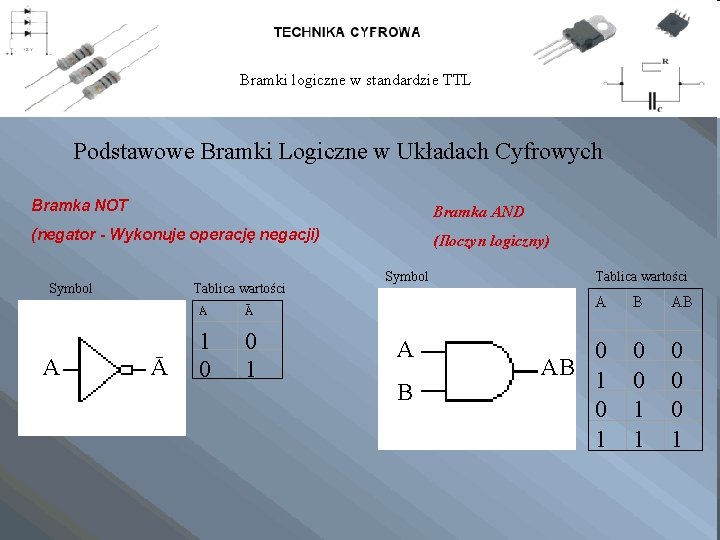

Bramki logiczne w standardzie TTL Podstawowe Bramki Logiczne w Układach Cyfrowych Bramka NOT Bramka AND (negator - Wykonuje operację negacji) (Iloczyn logiczny) Symbol A Tablica wartości Ā A Ā 1 0 0 1 Symbol A B Tablica wartości A B AB 0 AB 1 0 0 1 1 0 0 0 1

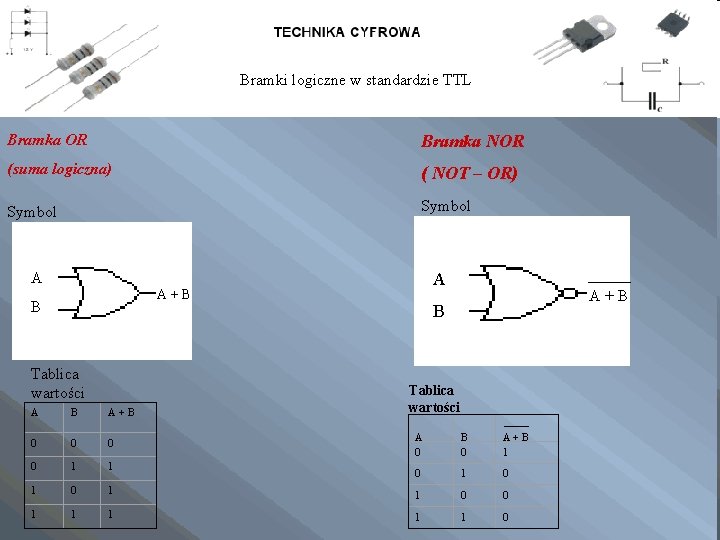

Bramki logiczne w standardzie TTL Bramka OR Bramka NOR (suma logiczna) ( NOT – OR) Symbol A A A+B B Tablica wartości A B A+B 0 0 1 1 1 0 1 1 A+B B Tablica wartości A 0 B 0 A+B 1 0 1 1 0 0 1 1 1 0

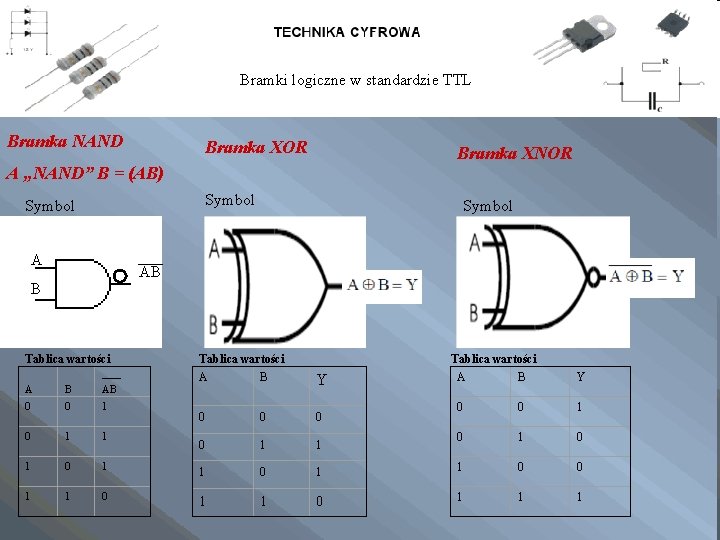

Bramki logiczne w standardzie TTL Bramka NAND Bramka XOR Bramka XNOR A „NAND” B = (AB) Symbol AB B Tablica wartości A B Y 0 0 1 1 A B AB 0 0 1 1 1 0 1 1 Tablica wartości A B Y 0 0 1 0 1 1 0 0 0 1 1 1

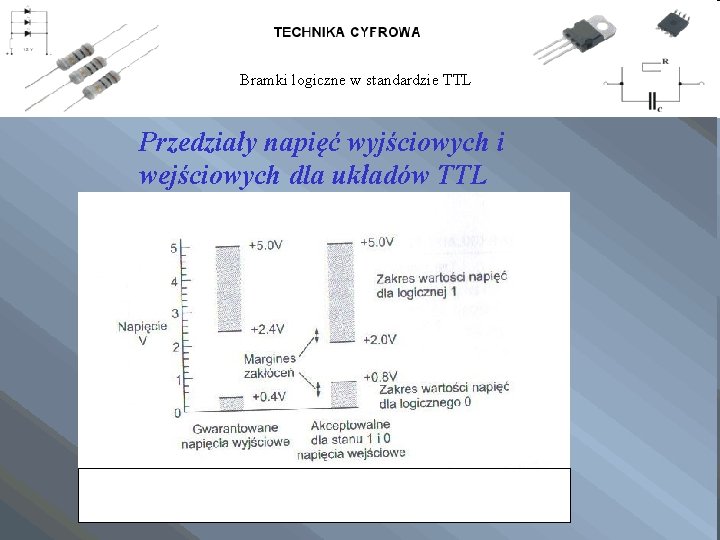

Bramki logiczne w standardzie TTL Przedziały napięć wyjściowych i wejściowych dla układów TTL

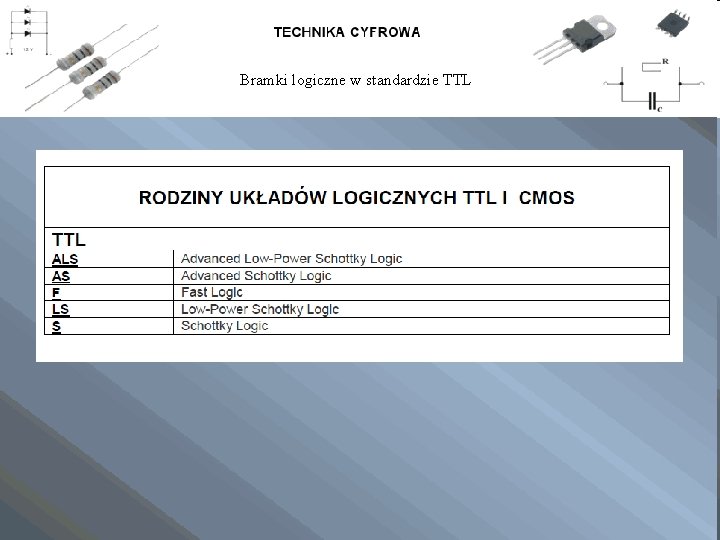

Bramki logiczne w standardzie TTL

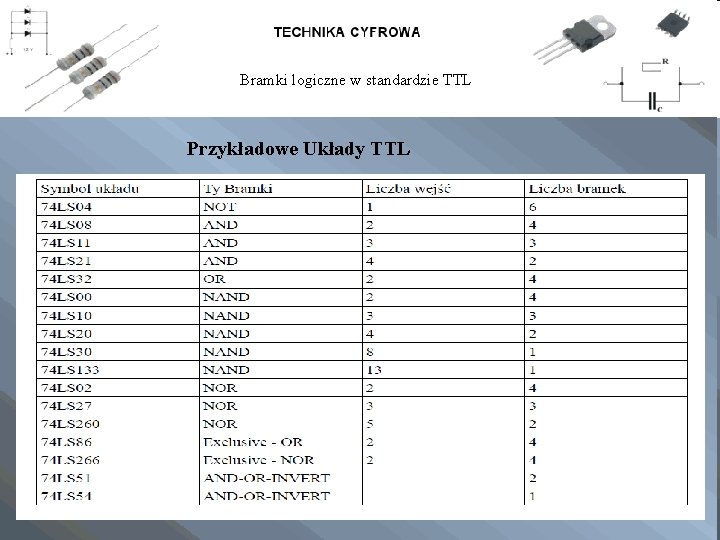

Bramki logiczne w standardzie TTL Przykładowe Układy TTL

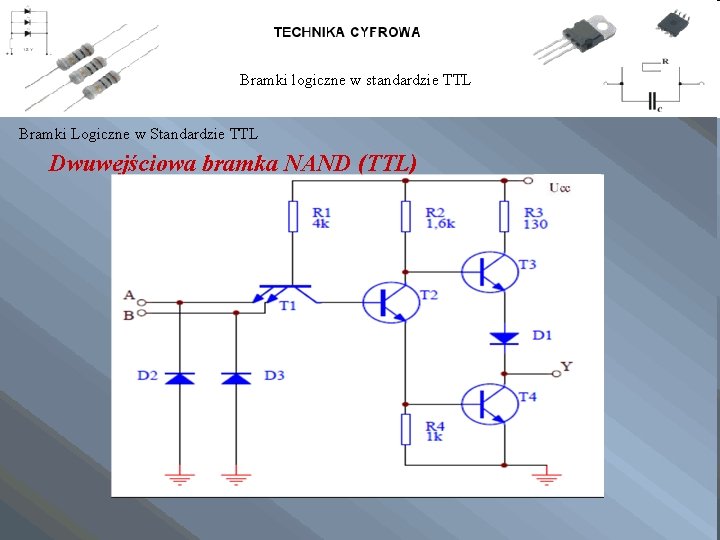

Bramki logiczne w standardzie TTL Bramki Logiczne w Standardzie TTL Dwuwejściowa bramka NAND (TTL)

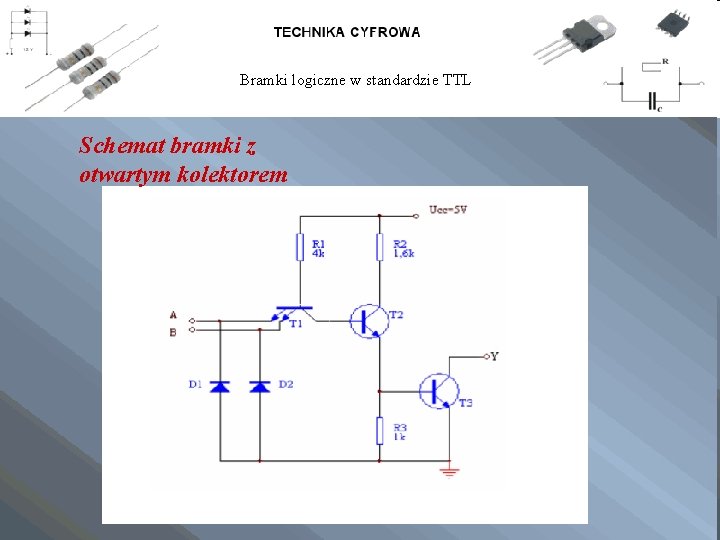

Bramki logiczne w standardzie TTL Schemat bramki z otwartym kolektorem

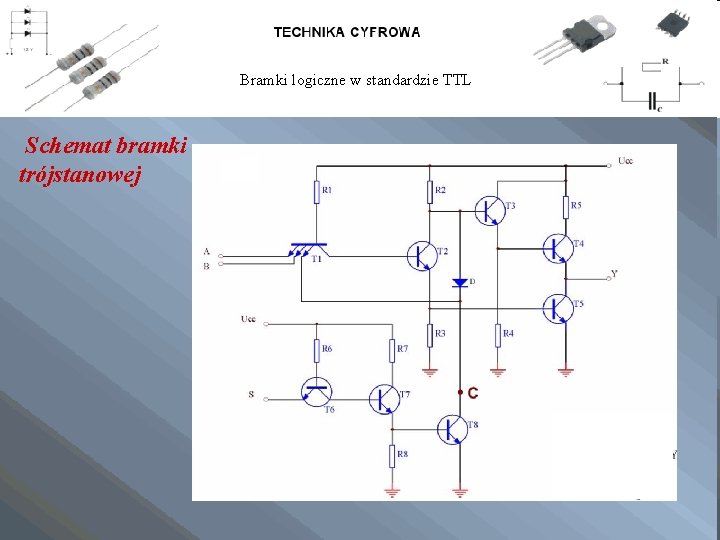

Bramki logiczne w standardzie TTL Schemat bramki trójstanowej

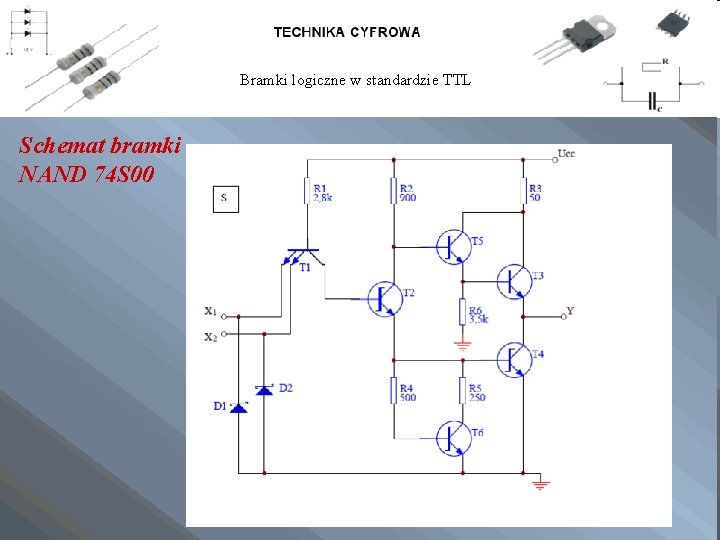

Bramki logiczne w standardzie TTL Schemat bramki NAND 74 S 00

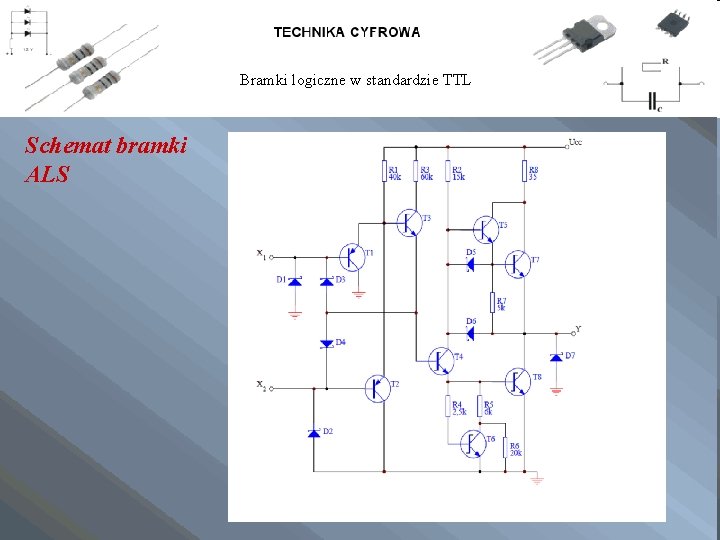

Bramki logiczne w standardzie TTL Schemat bramki ALS

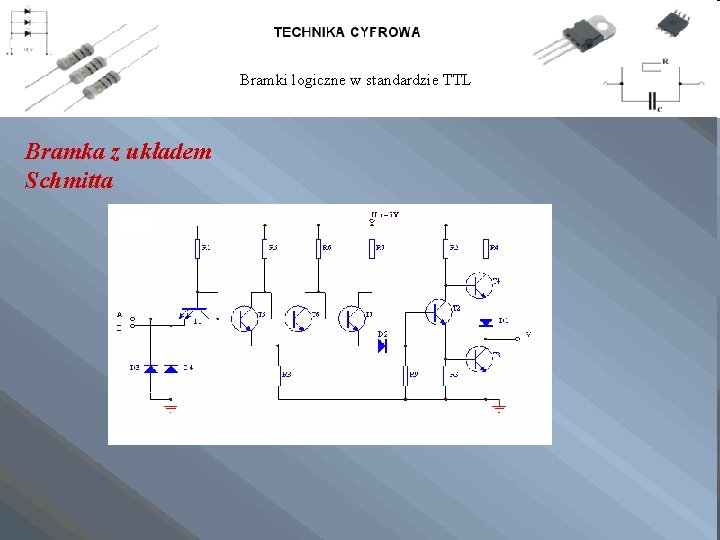

Bramki logiczne w standardzie TTL Bramka z układem Schmitta

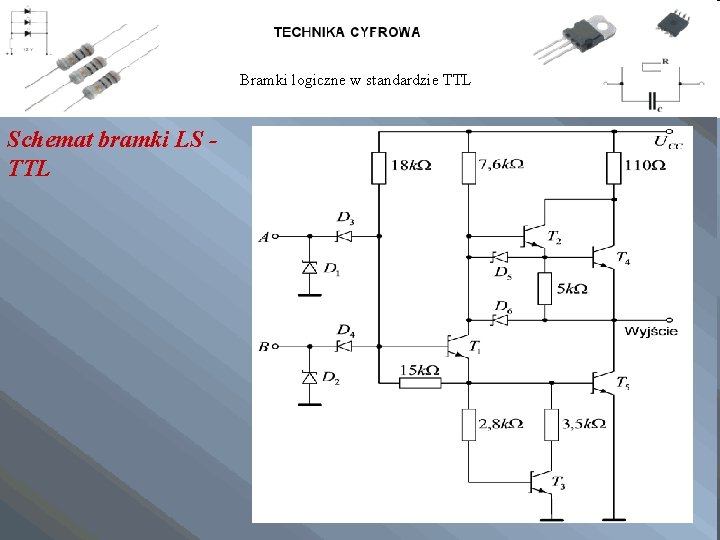

Bramki logiczne w standardzie TTL Schemat bramki LS TTL

Bramki logiczne w standardzie TTL Bibliografia: 1. P. Gajewski, J. Turczyński, Cyfrowe układy scalone CMOS. 2. W. Głodzki, L. Grabowski, Pracownia podstaw techniki cyfrowej. 3. P. Horowitz, W. Hill, Sztuka elektroniki t. 2, WKŁ, Warszawa 2001. 4. J. Kalisz, Podstawy elektroniki cyfrowej, WKŁ, Warszawa 1998. 5. S. Kuta, Elementy i układy elektroniczne Cz. II 6. M. Łakomy, J. Zabrodzki, Cyfrowe układy scalone TTL, PWN, Warszawa 1976. 7. P. Misiurewicz, M. Grzybek, Półprzewodnikowe układy logiczne, WNT, Warszawa 1975. 8. J. Pienkos, J. Turczyński, Układy scalone TTL w systemach cyfrowych, WKŁ Warszawa 1980 9. W. Sasal, Układy scalone serii UCY 74 LS i UCY 74 S 10. B. Wilkinson, Układy cyfrowe, WKŁ, Warszawa 2000. 11. http: //adam. dunat. freehost. pl/data/se/uklady_cyfrowe. pdf 12. http: //www. ti. com/ 13. http: //www. fairchildsemi. com/ 14. http: //www. elektroda. pl

Bramki logiczne w standardzie TTL Tomasz Palonek III rok ETI Instytut Techniki UP Kraków 2011

- Slides: 17