Chapter 12 Counter Circuits and Applications William Kleitz

- Slides: 78

Chapter 12 Counter Circuits and Applications William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

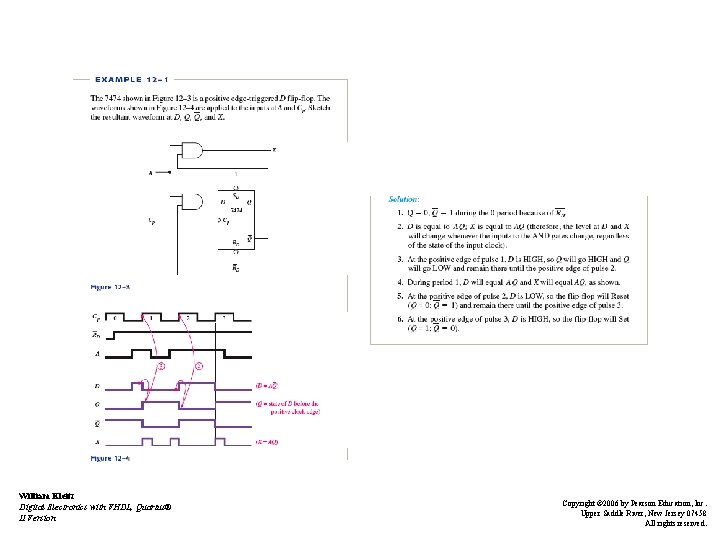

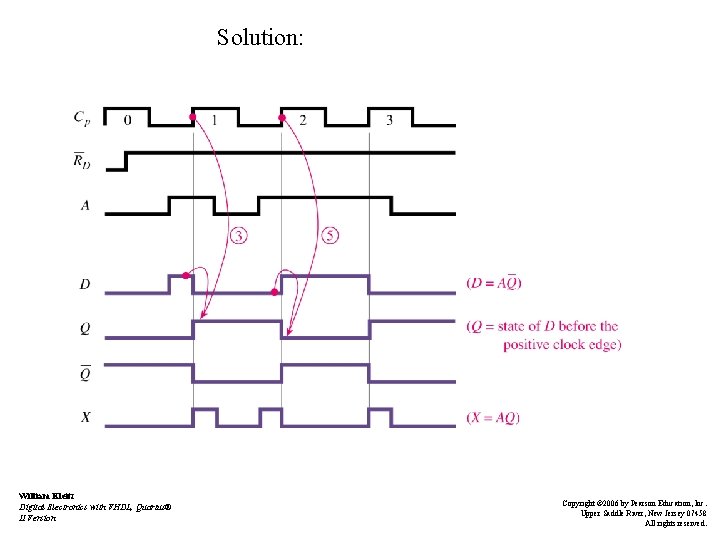

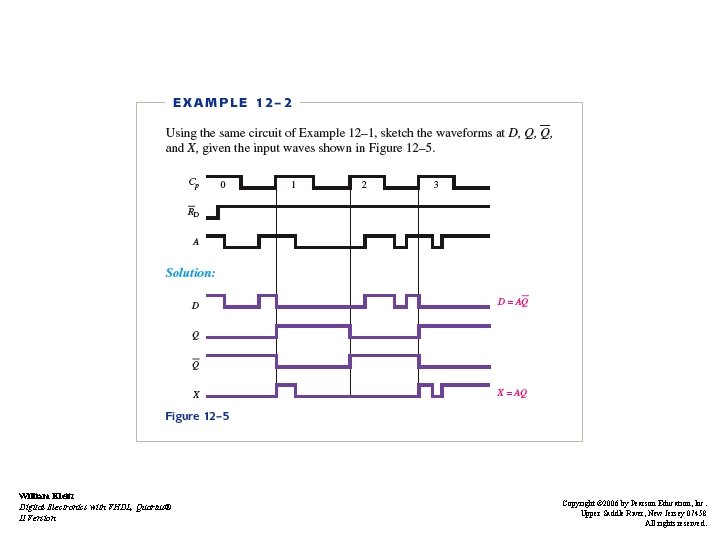

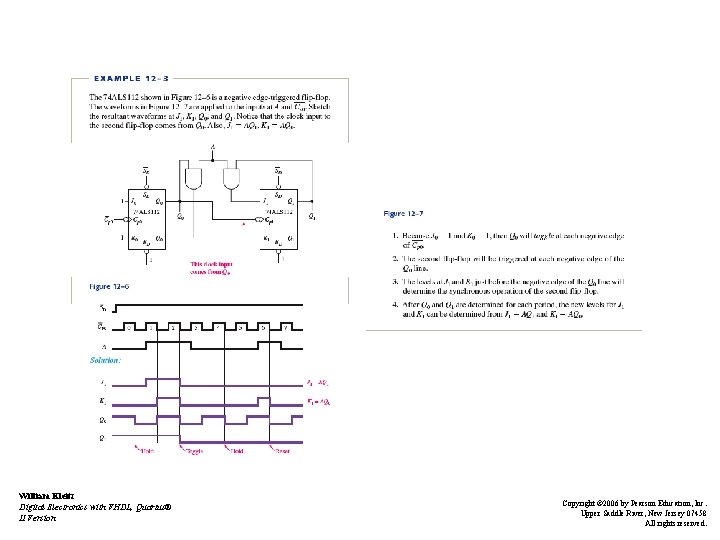

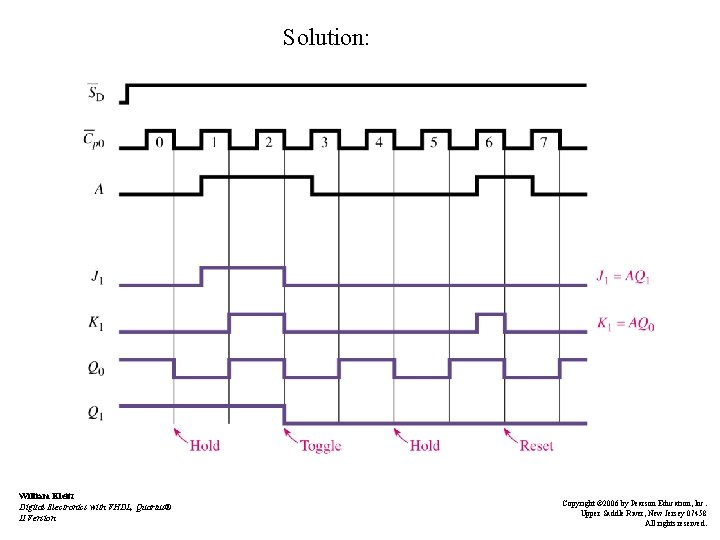

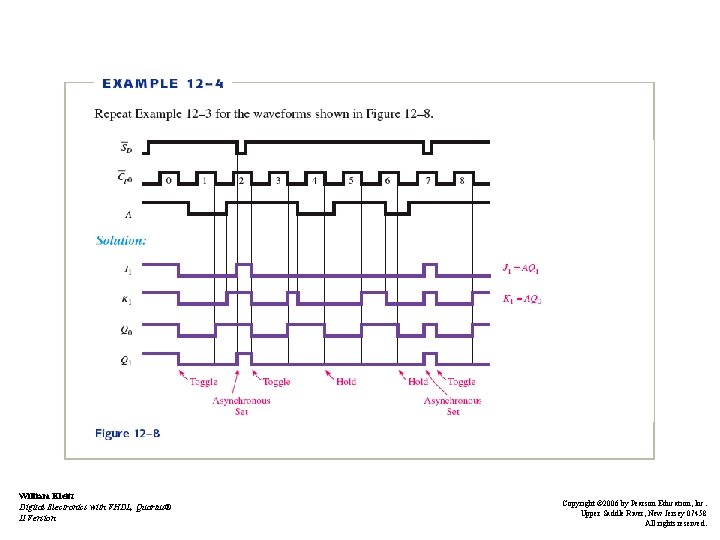

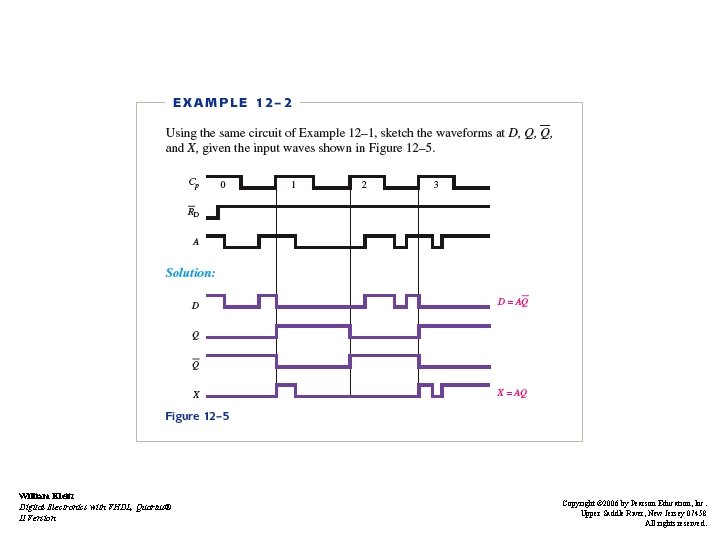

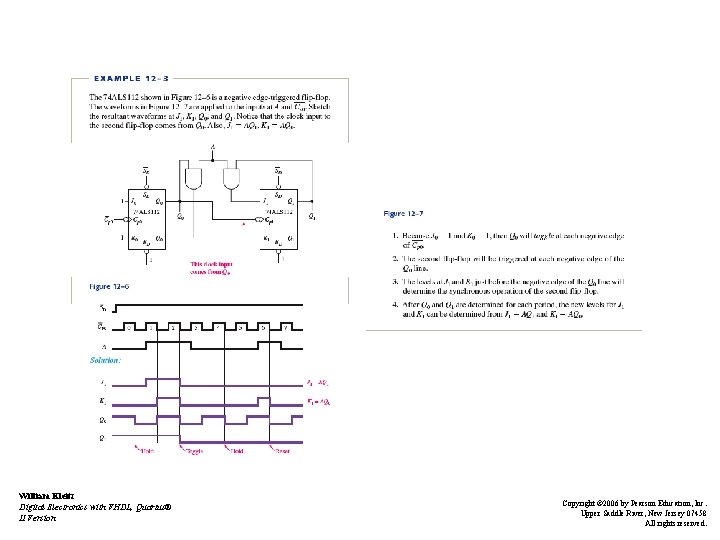

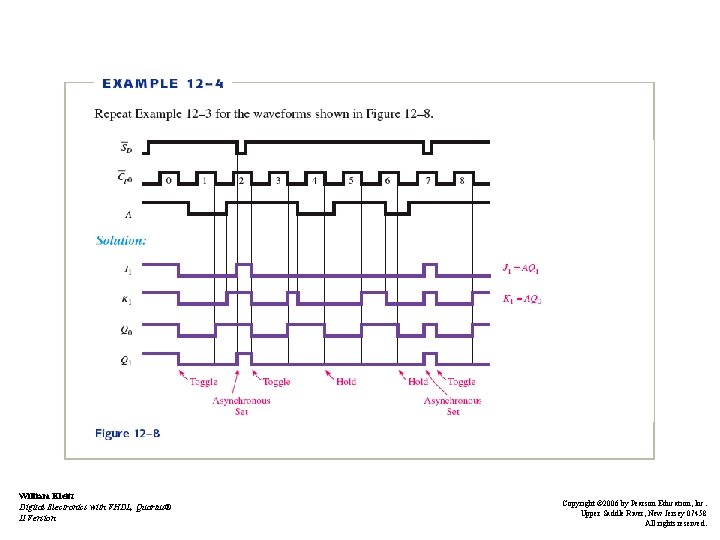

Analysis of Sequential Circuits • Mix of combinational logic gates and flipflops • See Examples 12 -1, 12 -2, 12 -3 and 12 -4 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

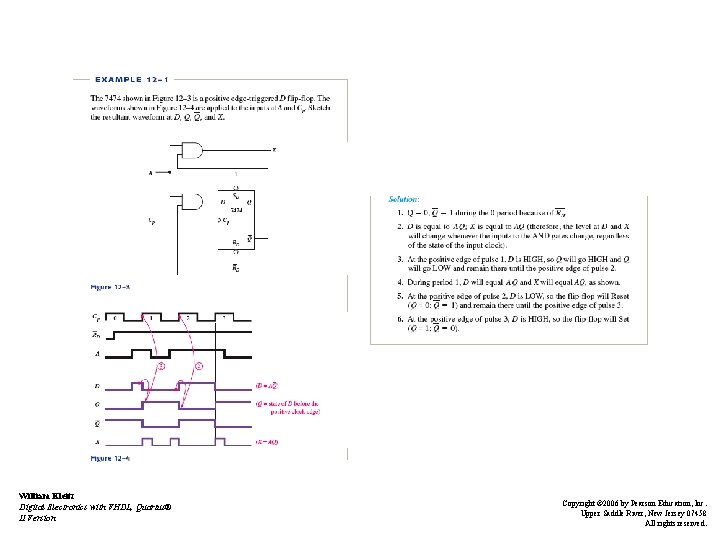

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

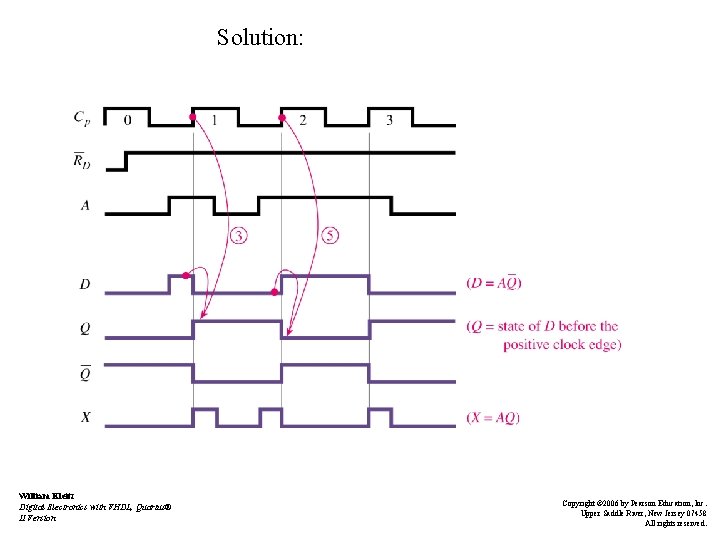

Solution: William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

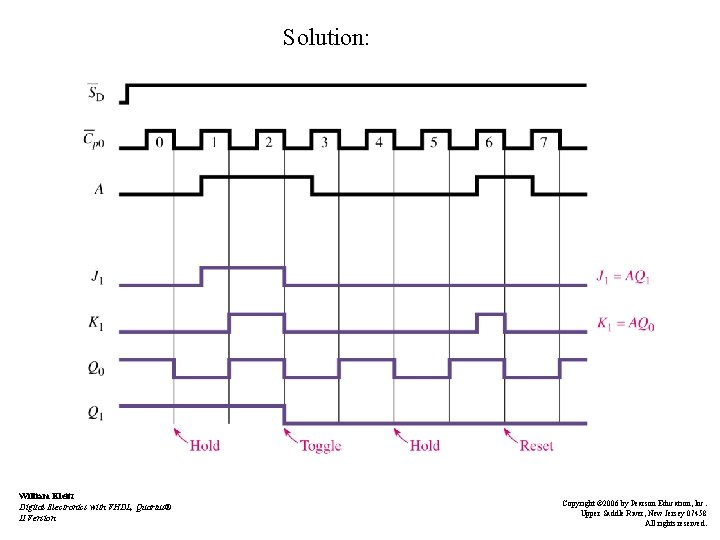

Solution: William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

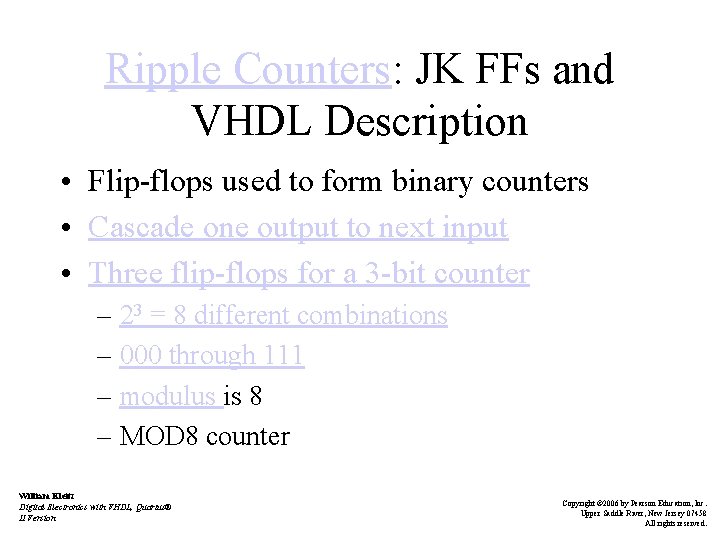

Ripple Counters: JK FFs and VHDL Description • Flip-flops used to form binary counters • Cascade one output to next input • Three flip-flops for a 3 -bit counter – 23 = 8 different combinations – 000 through 111 – modulus is 8 – MOD 8 counter William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

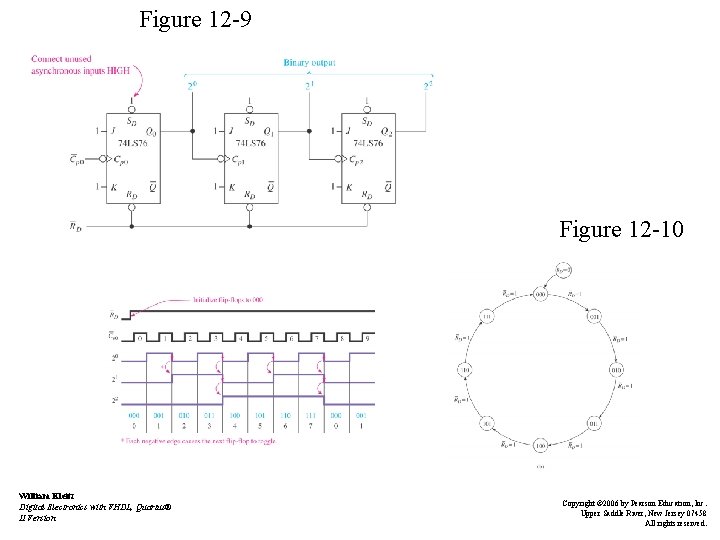

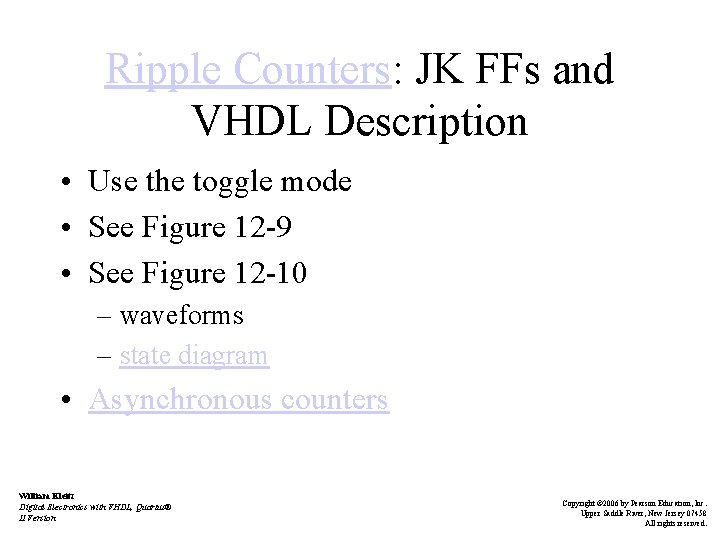

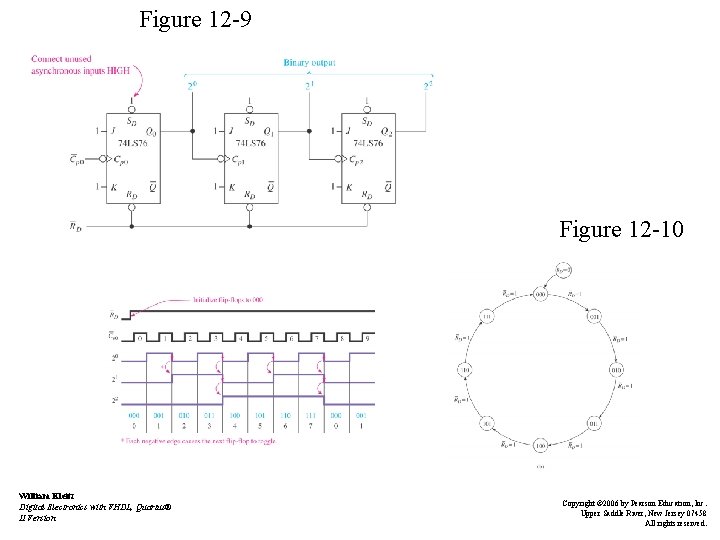

Ripple Counters: JK FFs and VHDL Description • Use the toggle mode • See Figure 12 -9 • See Figure 12 -10 – waveforms – state diagram • Asynchronous counters William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -9 Figure 12 -10 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

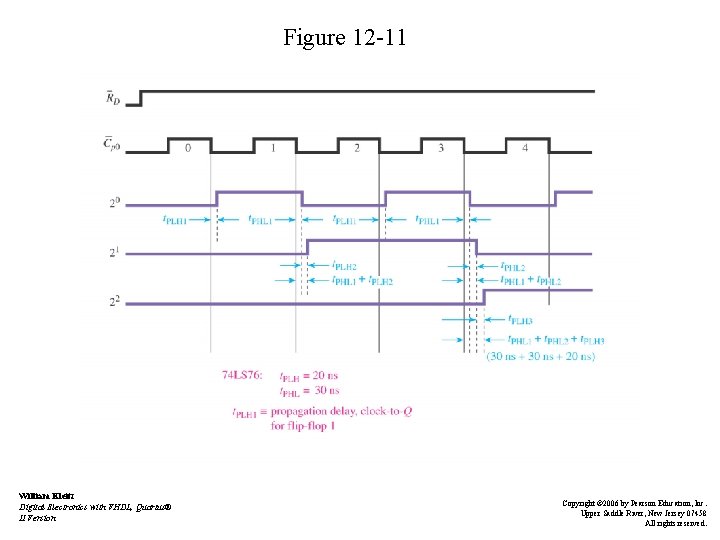

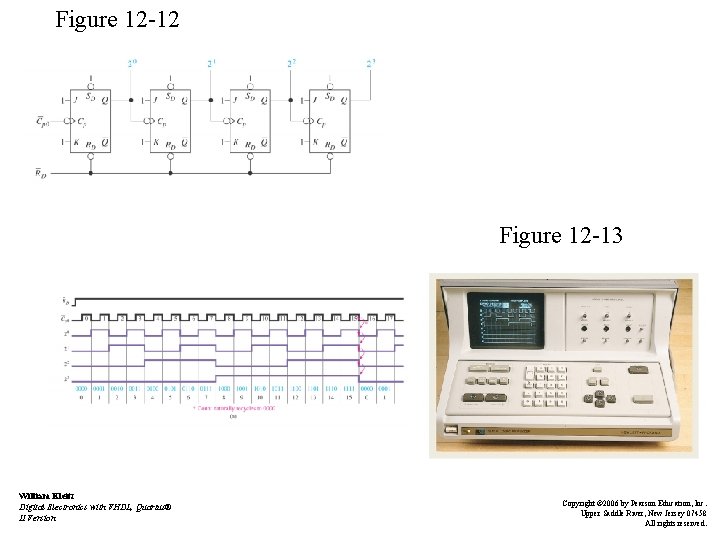

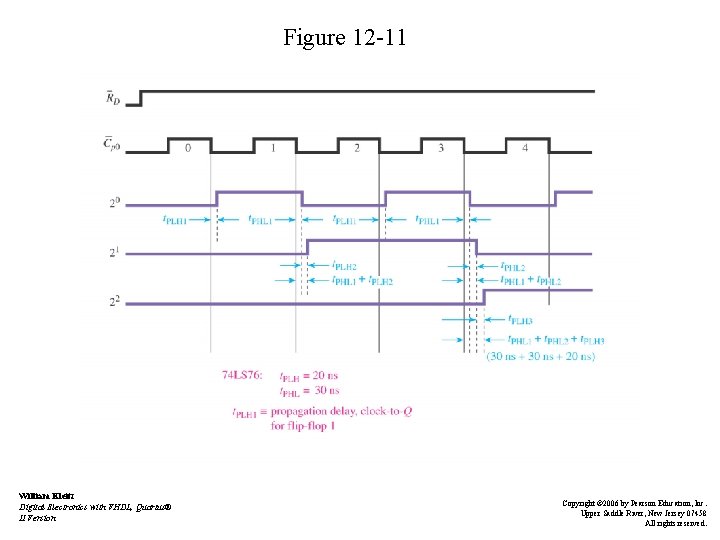

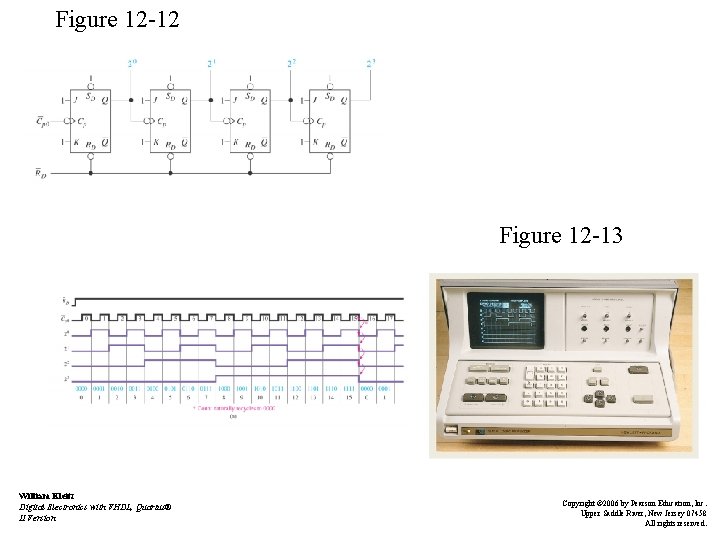

Ripple Counters: JK FFs and VHDL Description • Propagation delay skews the waveform – See Figure 12 -11 • Maximum frequency is determined by reciprocal of the combination of propagation delays • MOD 16 counter – four flip-flops – See Figure 12 -12 and 12 -13 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -11 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -12 Figure 12 -13 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

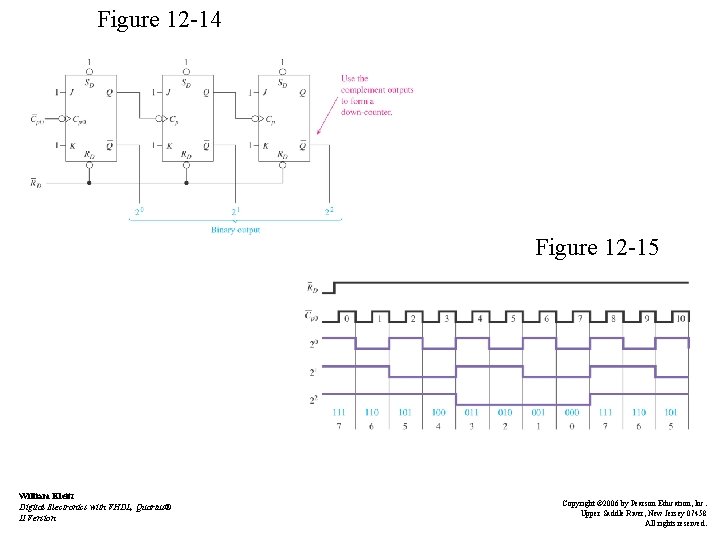

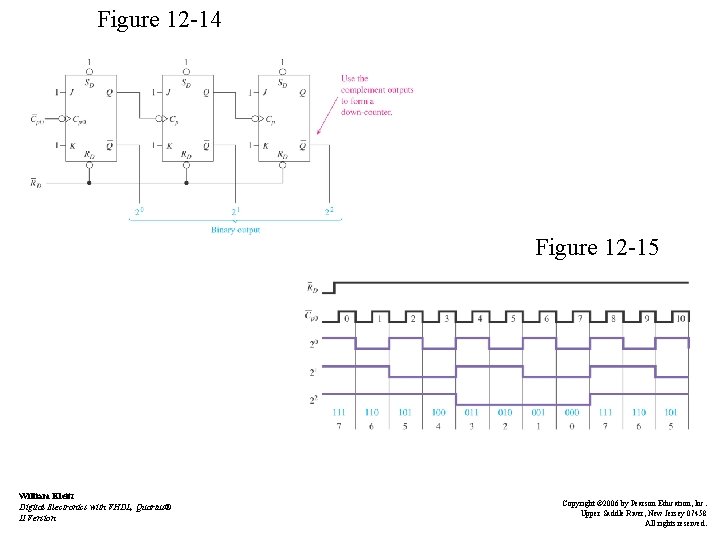

Ripple Counters: JK FFs and VHDL Description • Down Counters – take binary outputs from the not-Q outputs – See Figure 12 -14 and 12 -15 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -14 Figure 12 -15 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

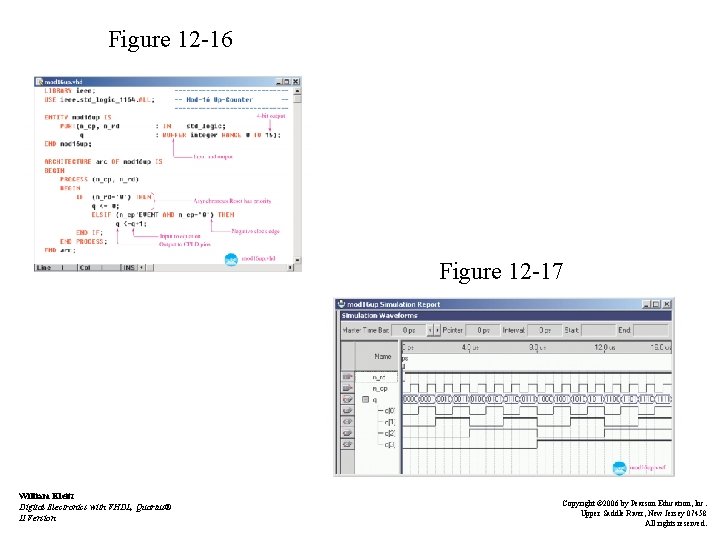

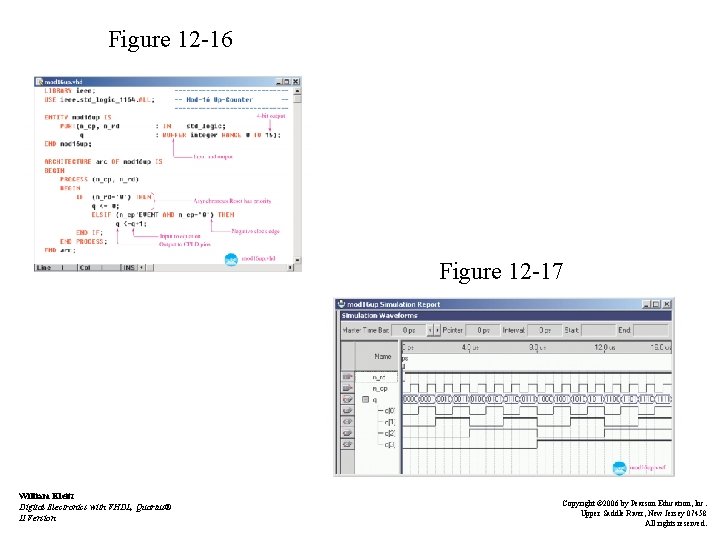

Ripple Counters: JK FFs and VHDL Description • VHDL description of a Mod-16 up counter – VHDL description – simulation – see figure 12 -16 and 12 -17 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -16 Figure 12 -17 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

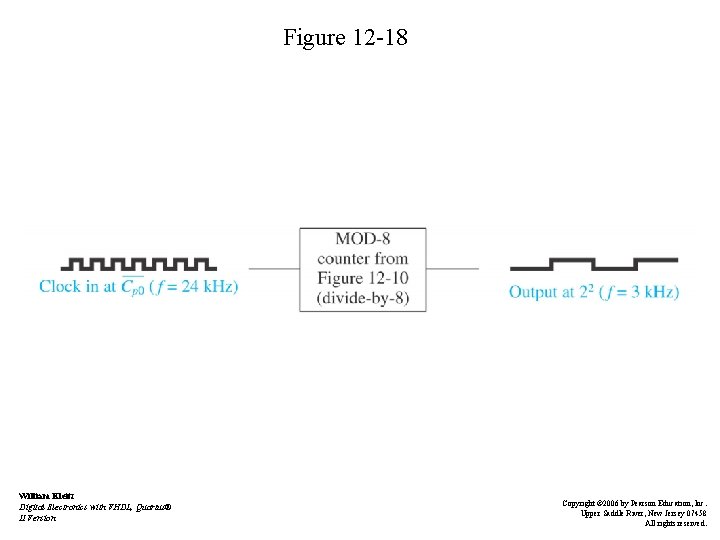

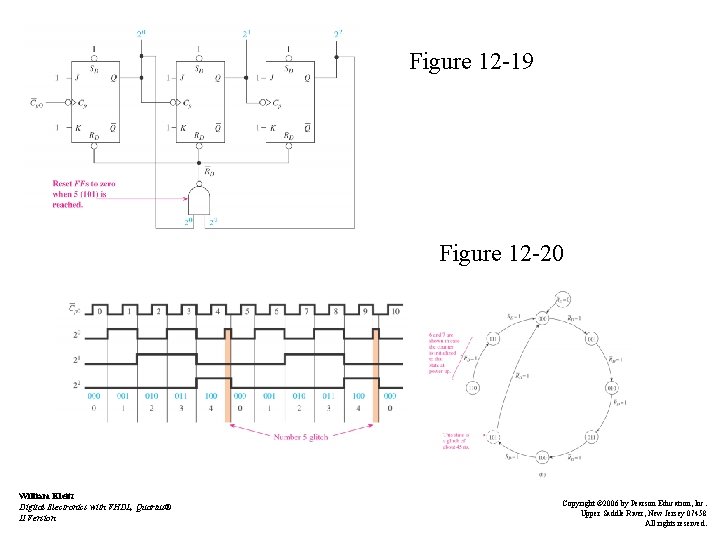

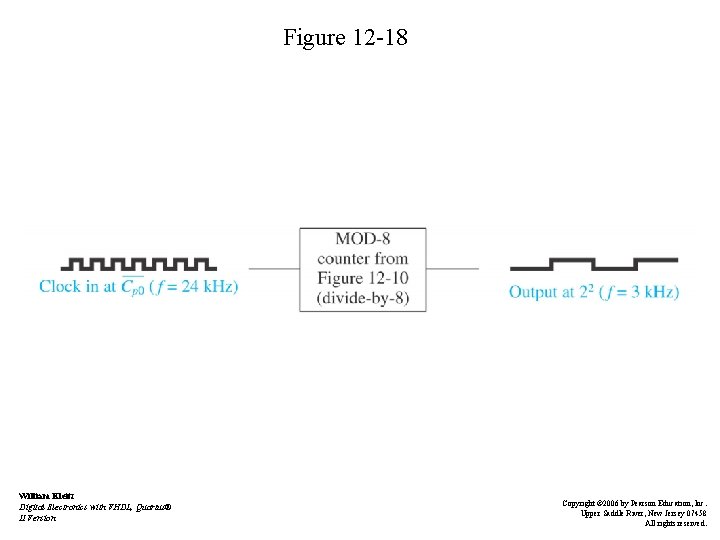

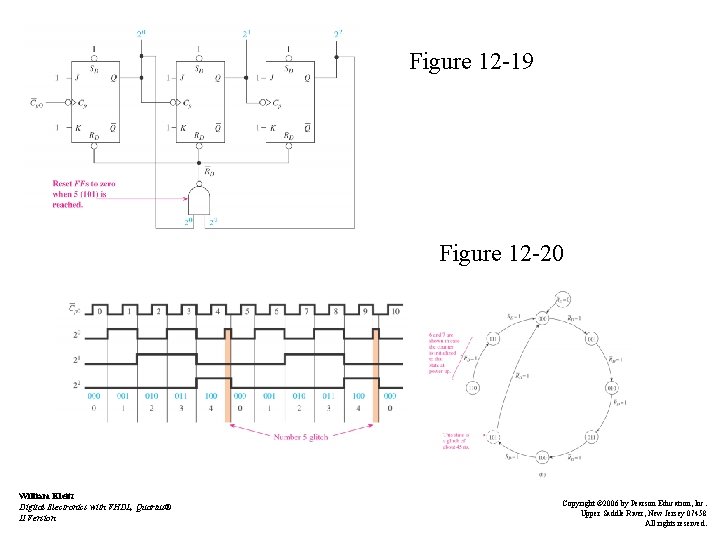

Design of Divide-by-N Counters • Reduce the frequency of periodic waveforms – See Figure 12 -18 • Divide-by-5 (MOD 5) counter – See Figure 12 -19 – See Figure 12 -20 • waveforms • state diagram • Any modulus counter can be formed by using external gating William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -18 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -19 Figure 12 -20 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

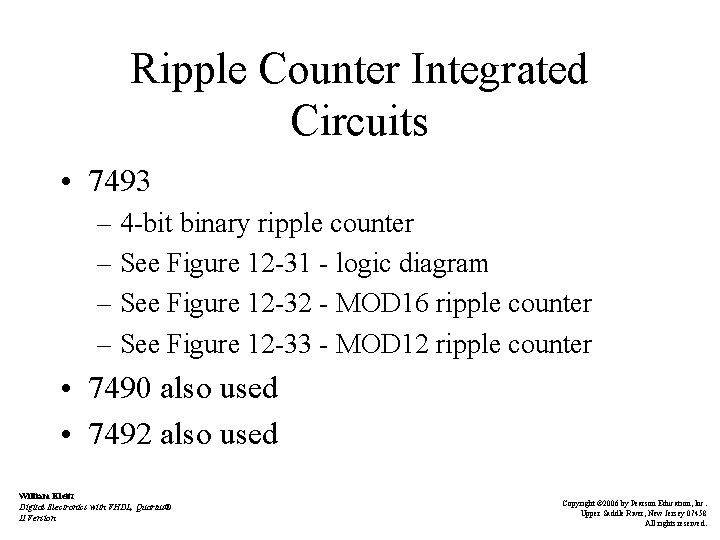

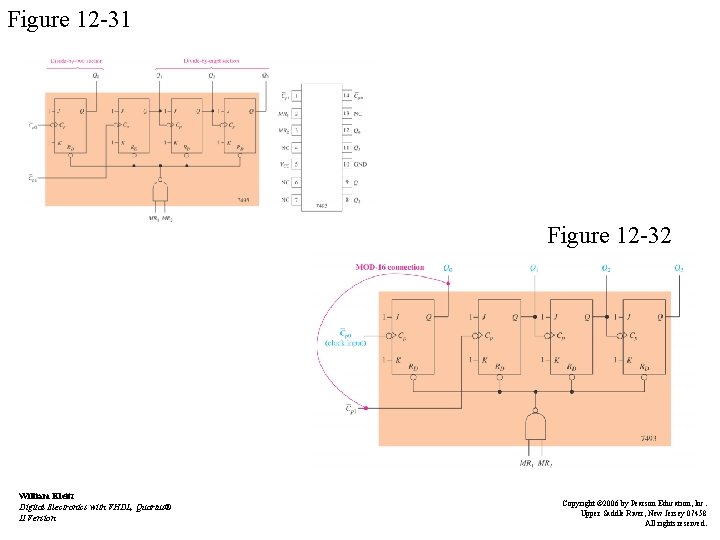

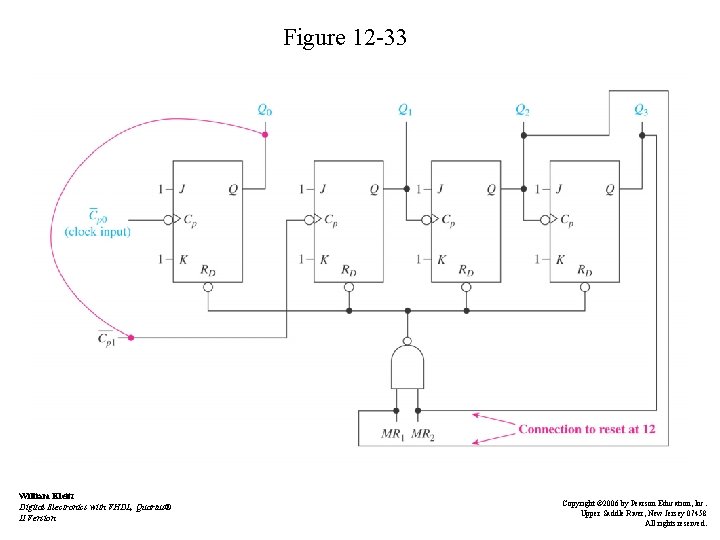

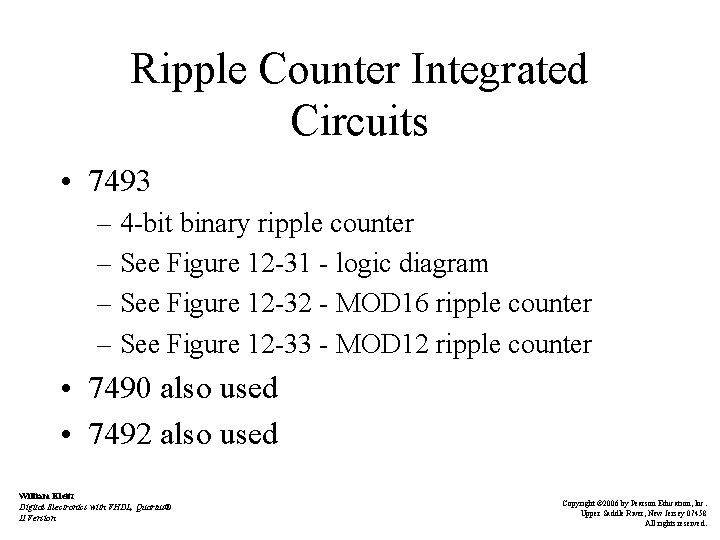

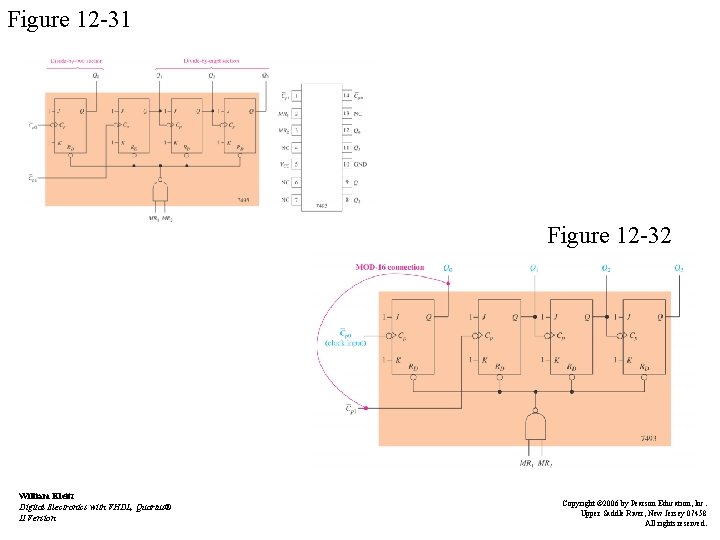

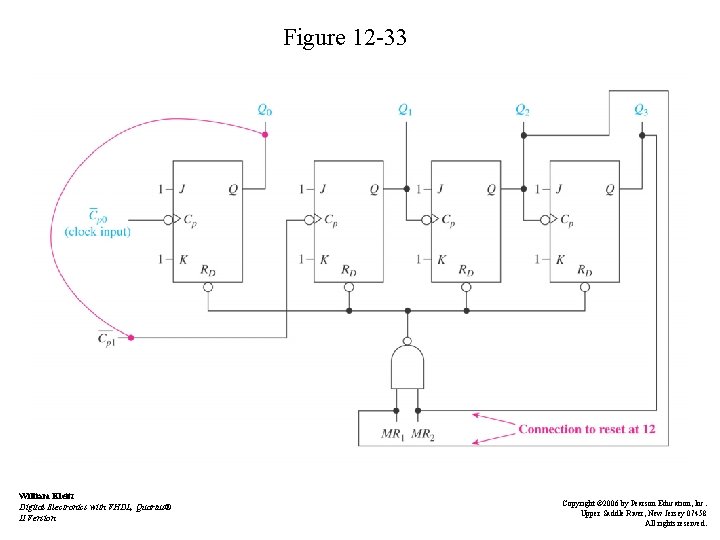

Ripple Counter Integrated Circuits • 7493 – 4 -bit binary ripple counter – See Figure 12 -31 - logic diagram – See Figure 12 -32 - MOD 16 ripple counter – See Figure 12 -33 - MOD 12 ripple counter • 7490 also used • 7492 also used William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -31 Figure 12 -32 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -33 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

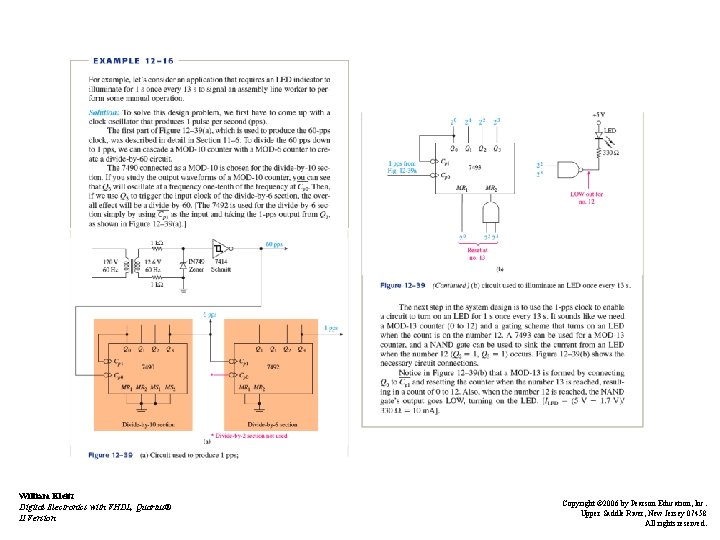

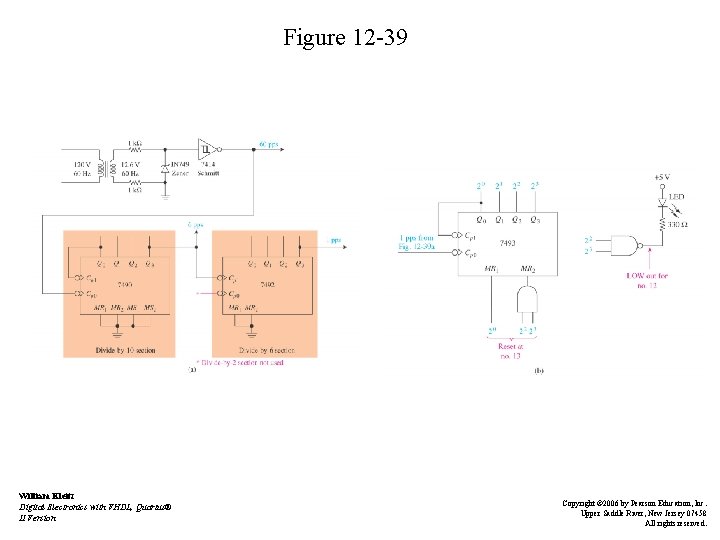

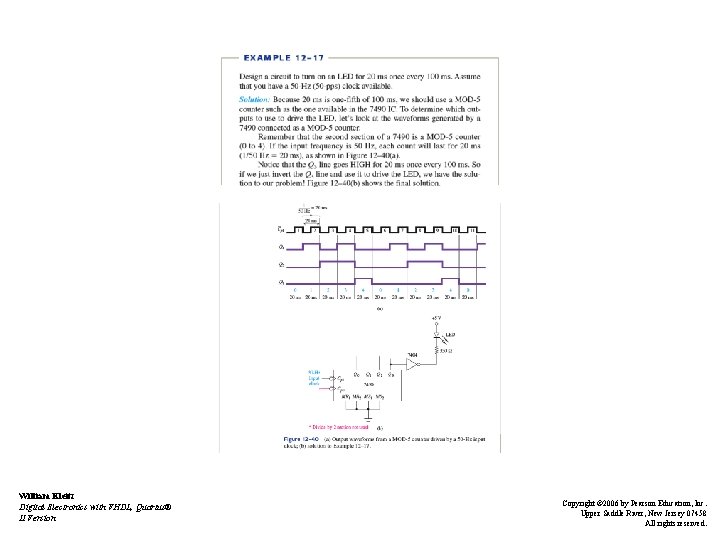

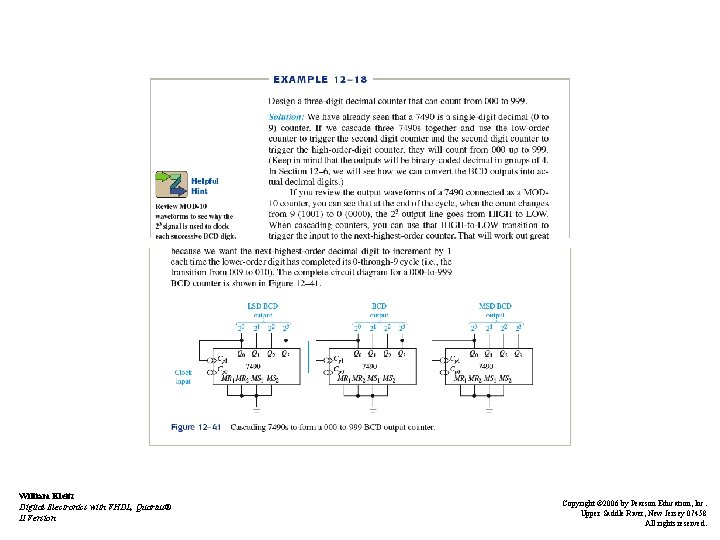

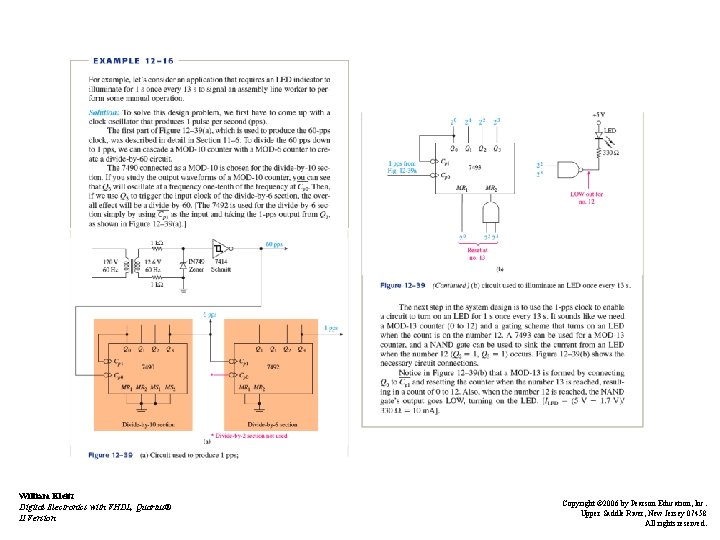

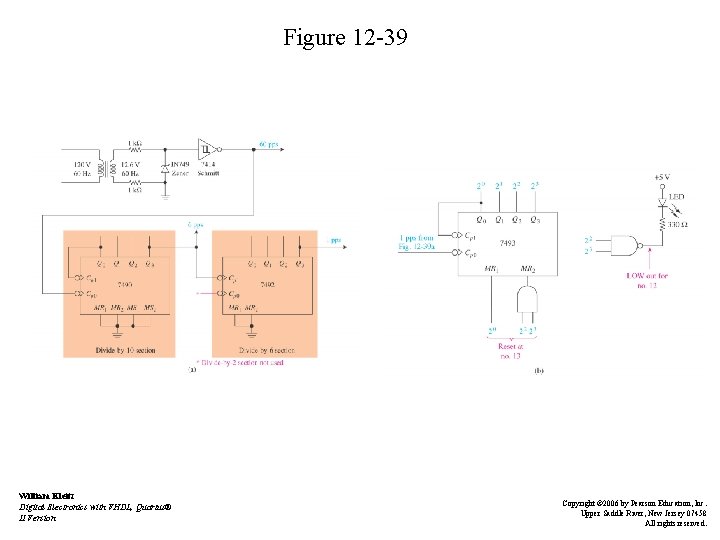

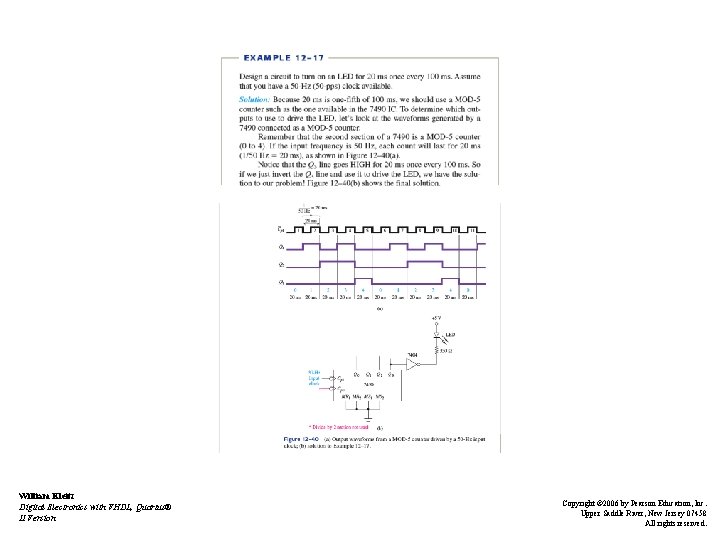

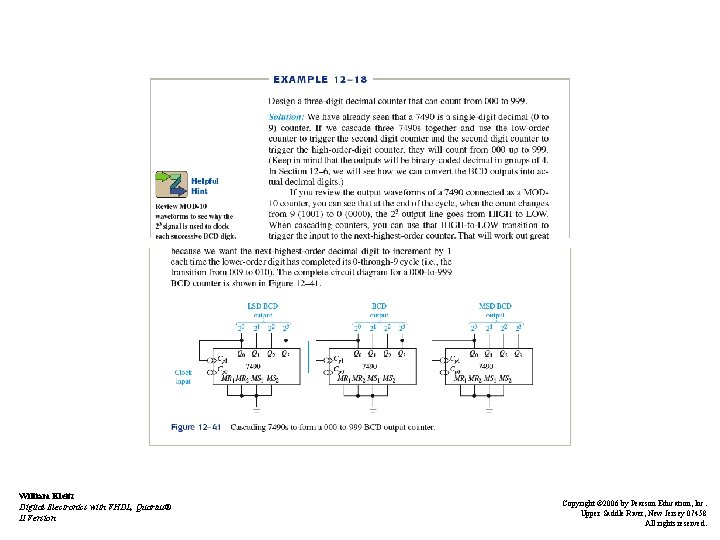

System Design Applications • LED illuminate for 1 s once every 13 s – See example 12 -16 • Turn on LED for 20 ms once every 100 ms – See Application 12 -17 • Three digit decimal counter 000 - 999 – See Application 12 -18 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -39 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

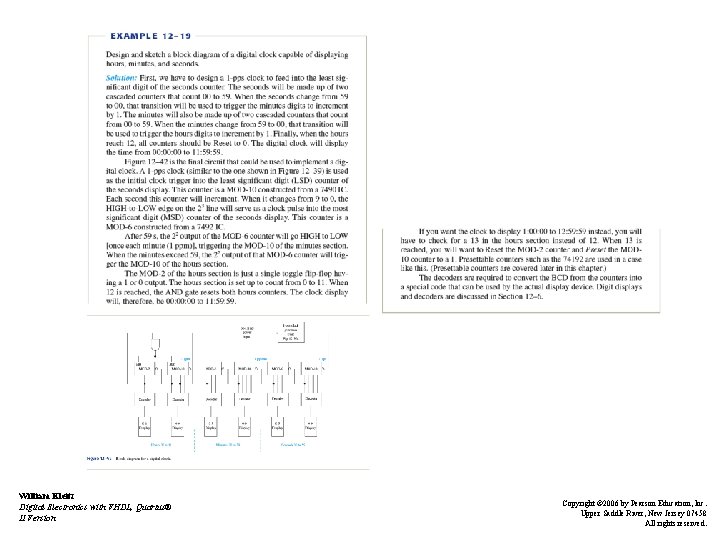

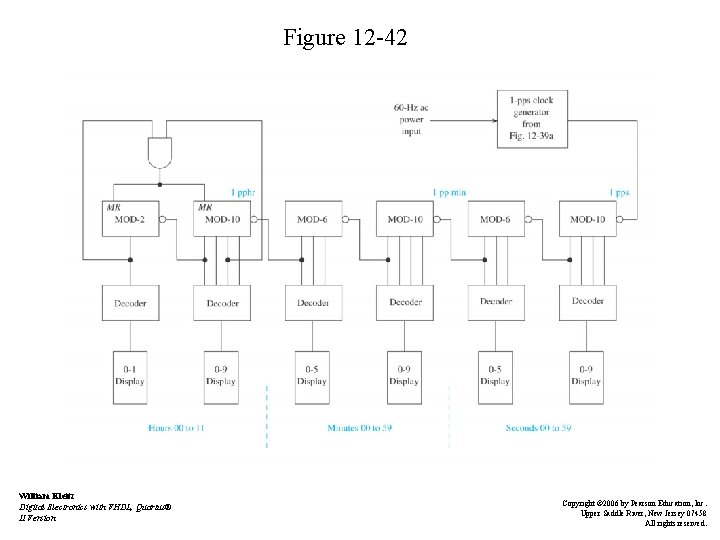

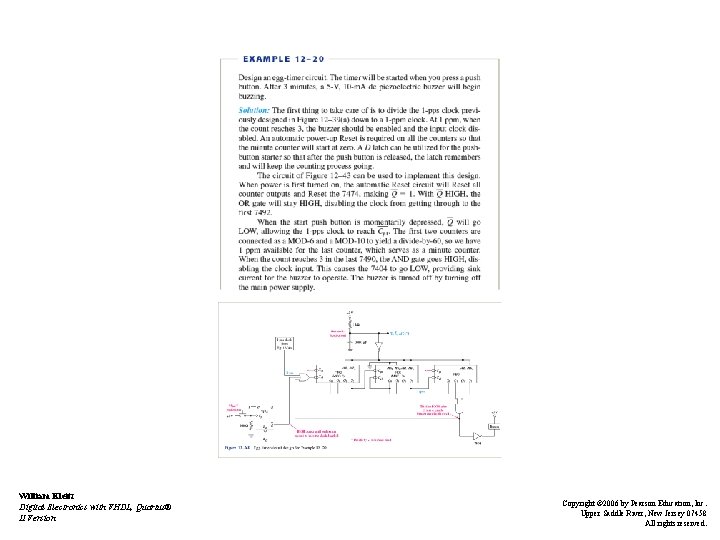

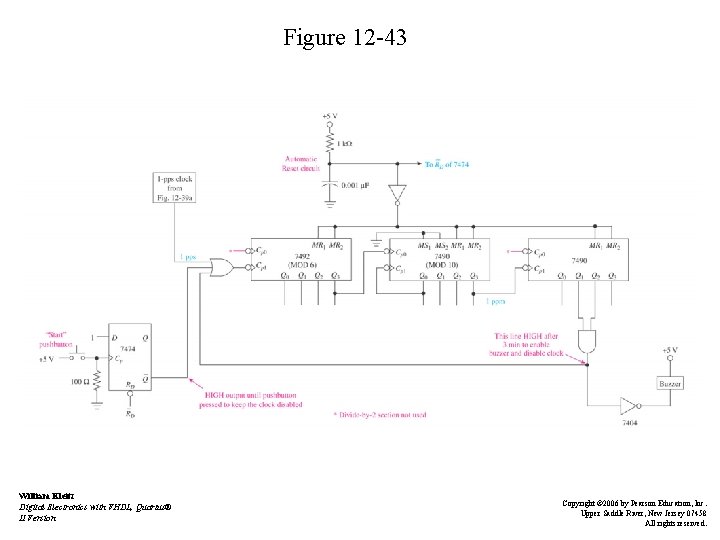

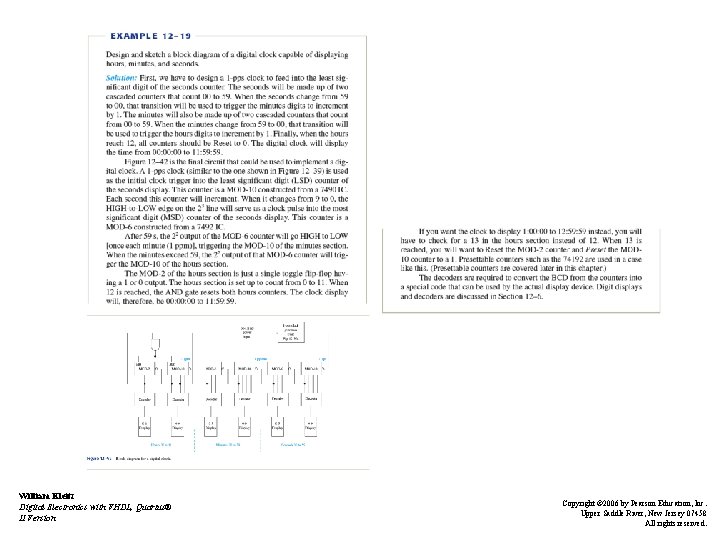

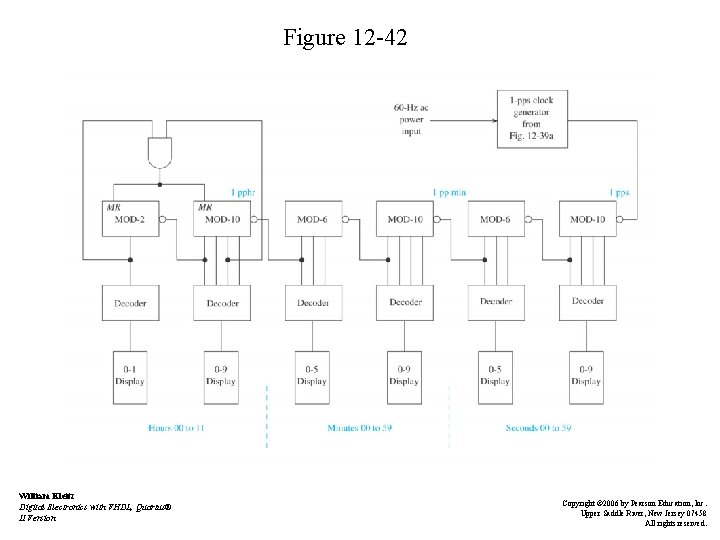

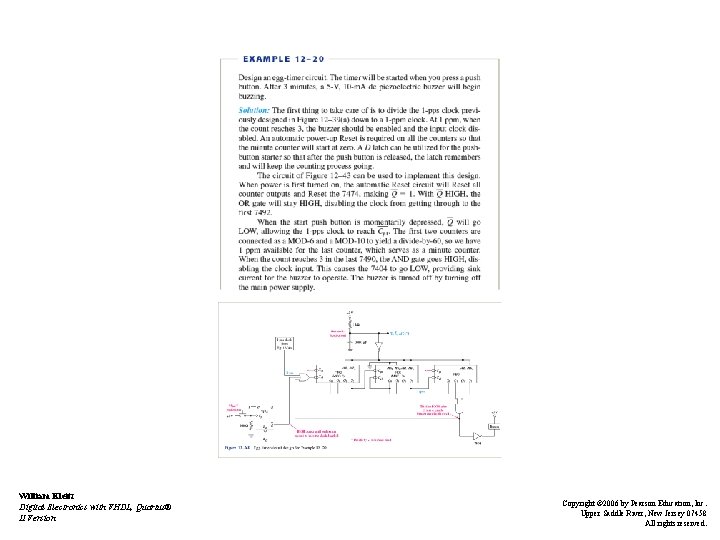

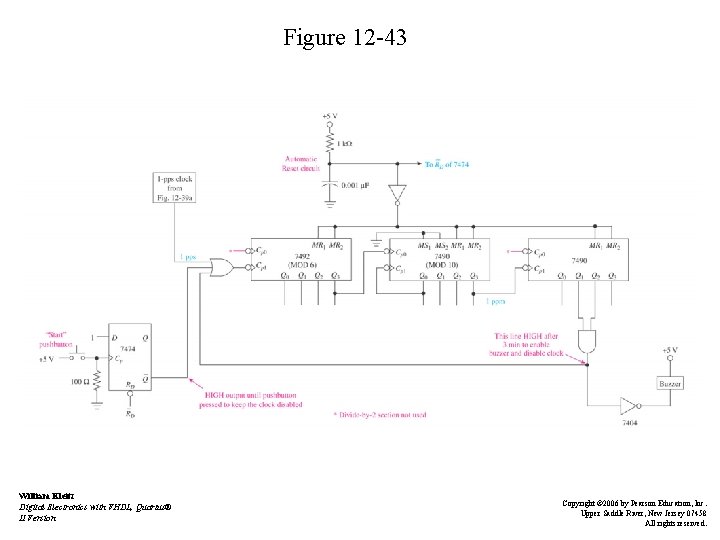

System Design Applications • Digital clock capable of hours, min and sec – See example 12 -19 • Egg timer circuit – See example 12 -20 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -42 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -43 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

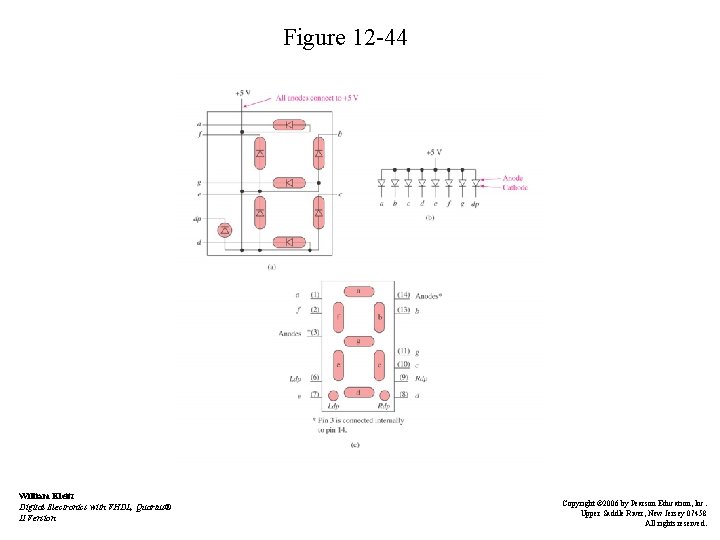

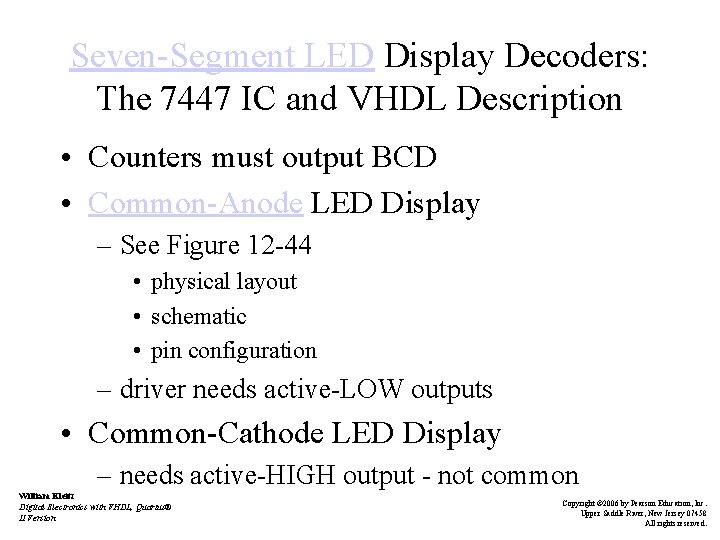

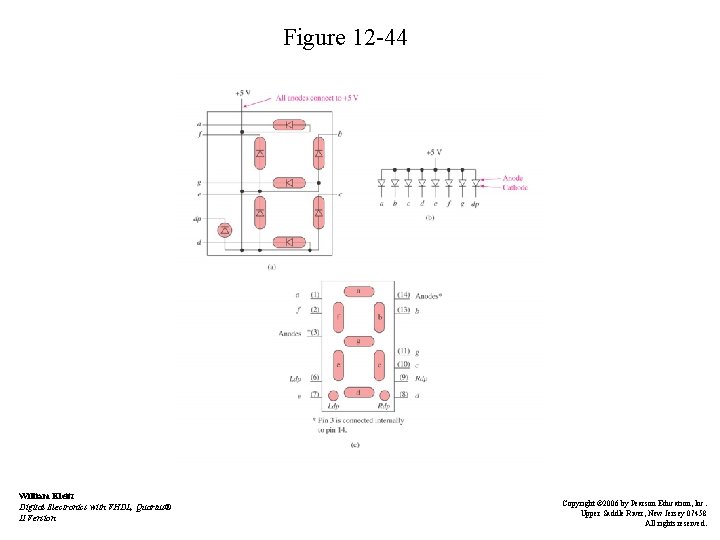

Seven-Segment LED Display Decoders: The 7447 IC and VHDL Description • Counters must output BCD • Common-Anode LED Display – See Figure 12 -44 • physical layout • schematic • pin configuration – driver needs active-LOW outputs • Common-Cathode LED Display – needs active-HIGH output - not common William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -44 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

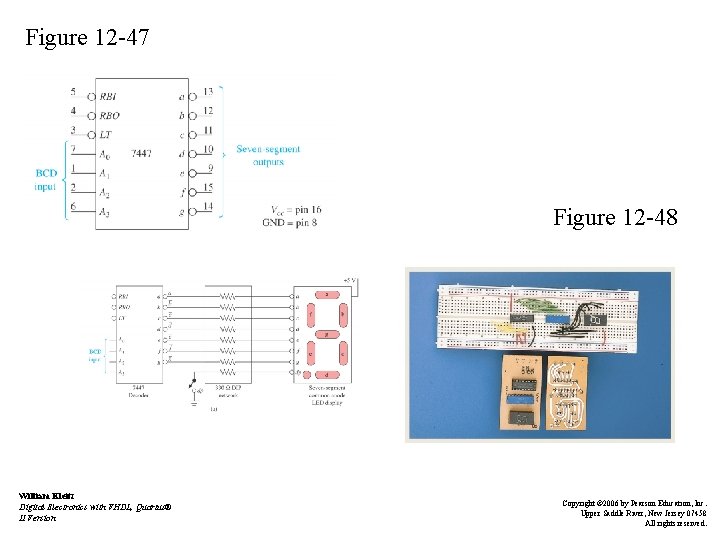

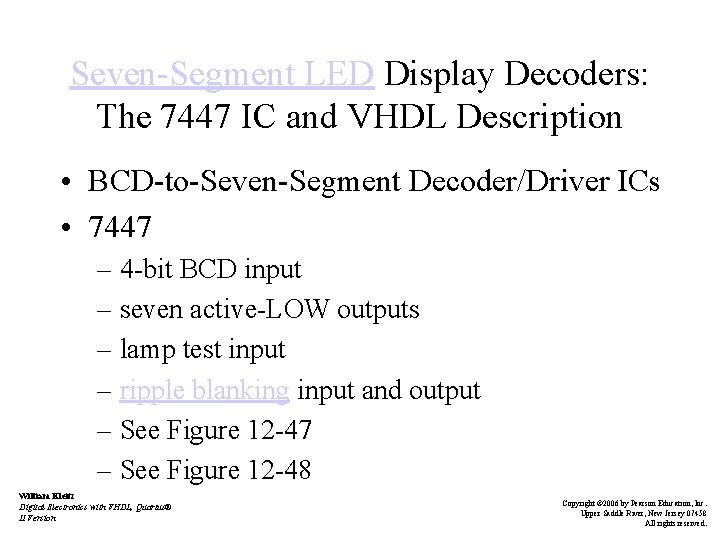

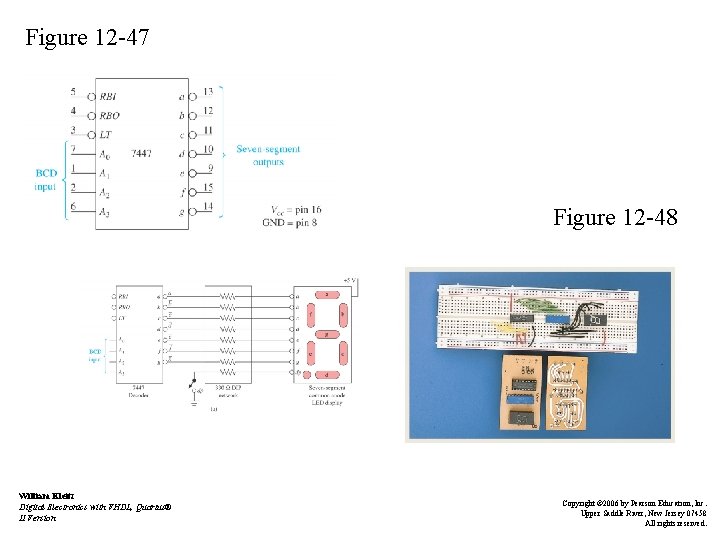

Seven-Segment LED Display Decoders: The 7447 IC and VHDL Description • BCD-to-Seven-Segment Decoder/Driver ICs • 7447 – 4 -bit BCD input – seven active-LOW outputs – lamp test input – ripple blanking input and output – See Figure 12 -47 – See Figure 12 -48 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -47 Figure 12 -48 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

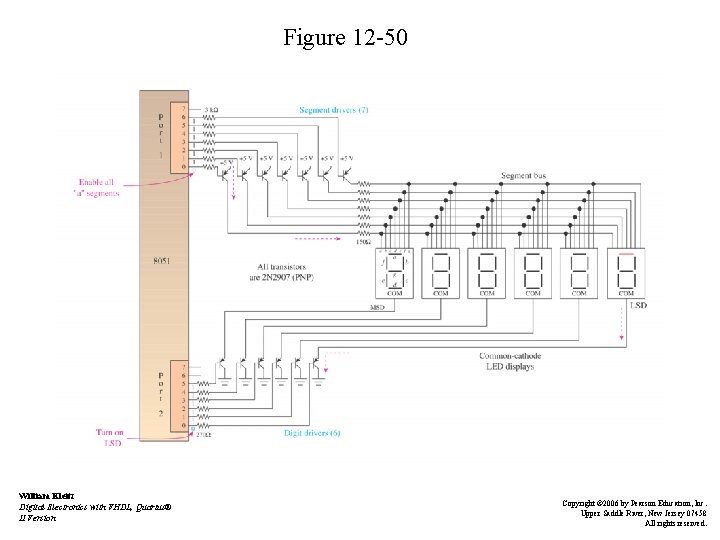

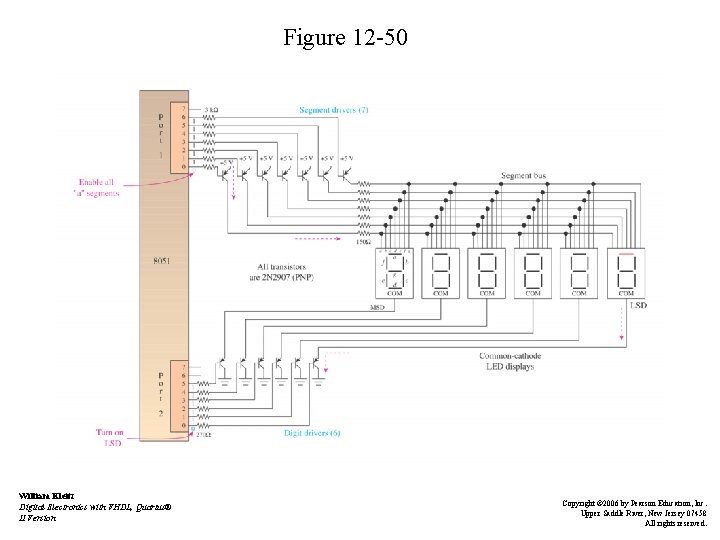

Seven-Segment LED Display Decoders: The 7447 IC and VHDL Description • Driving a Multiplexed Display with a Microcontroller – to save power – not all displays on at once – See Figure 12 -50 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -50 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

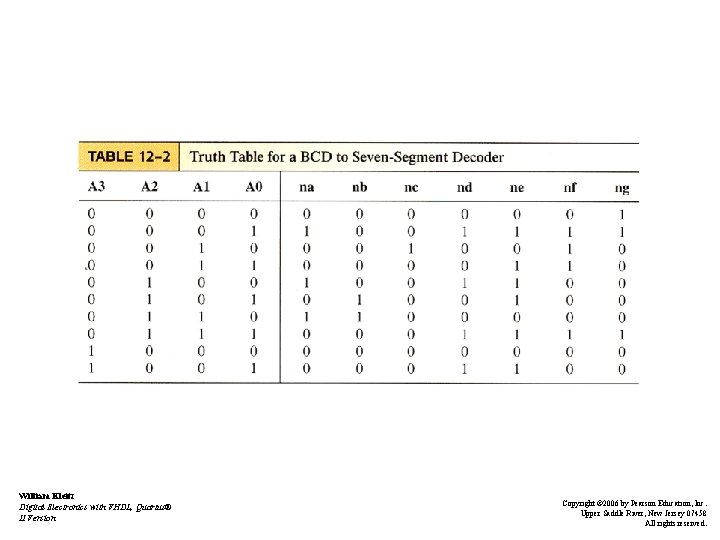

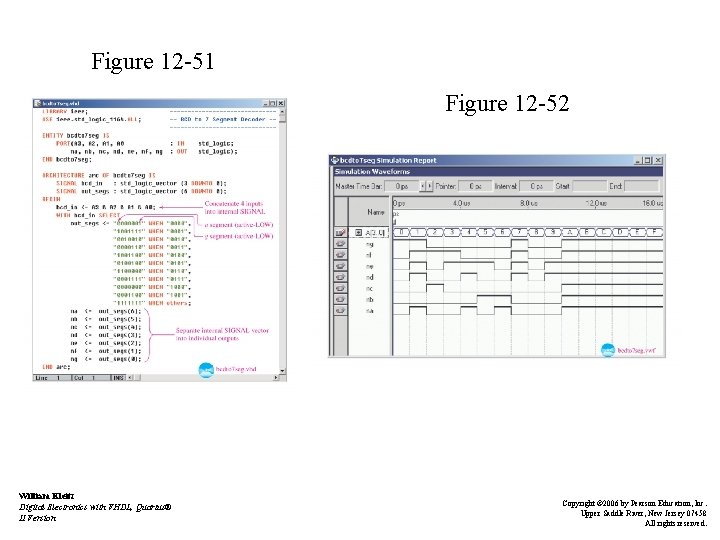

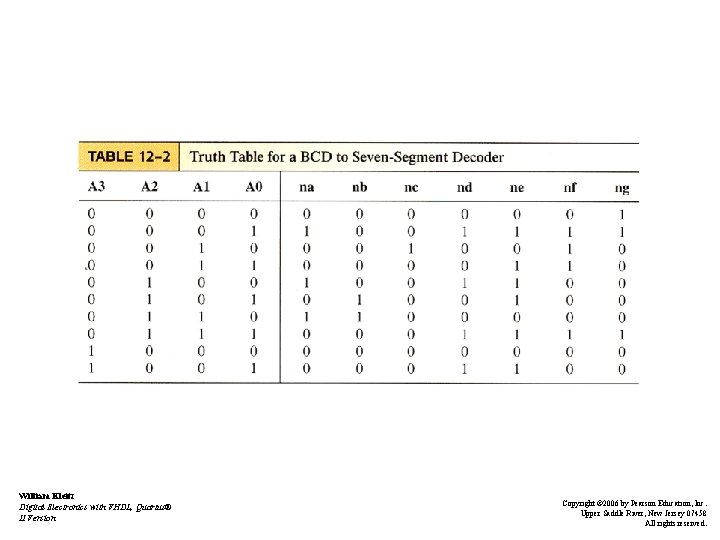

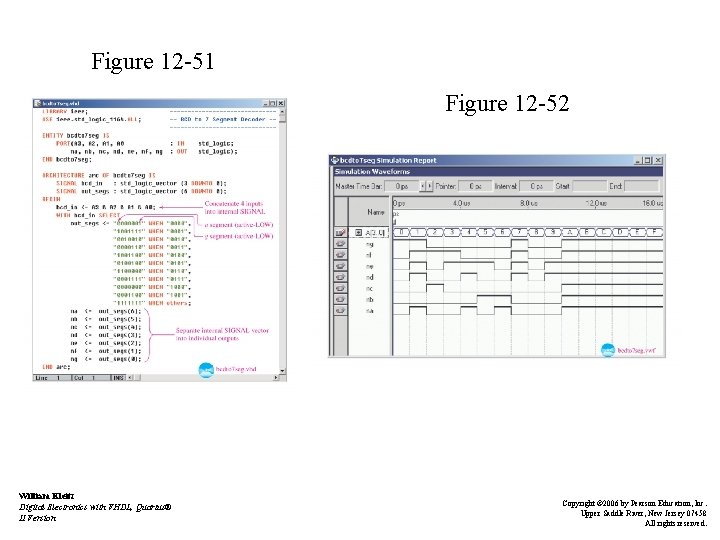

Seven-Segment LED Display Decoders: The 7447 IC and VHDL Description • VHDL description of the seven segment decoder – 7447 decoding features in VHDL – truth table – see table 12 -2 – see figure 12 -51 – see figure 12 -52 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -51 Figure 12 -52 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

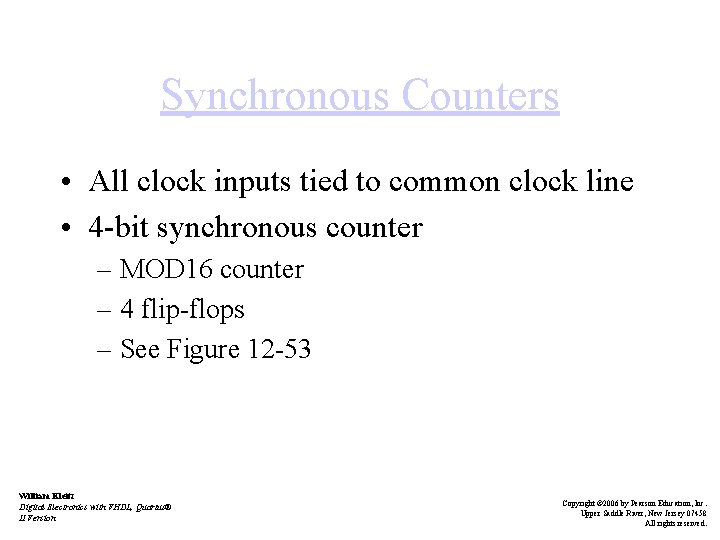

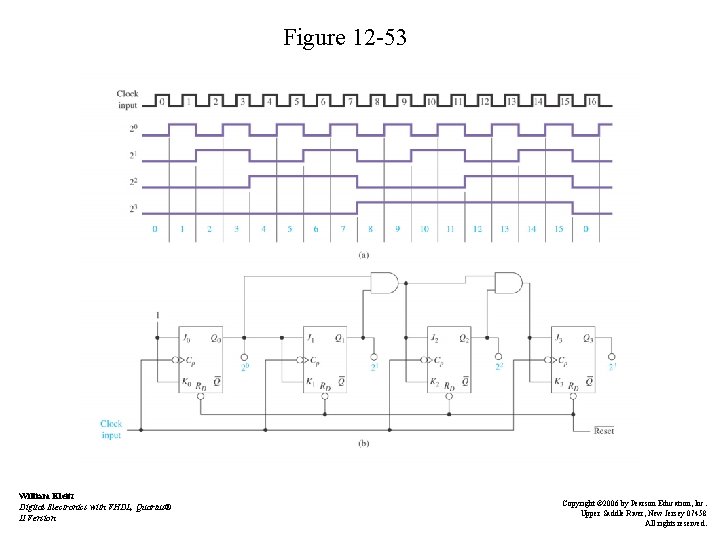

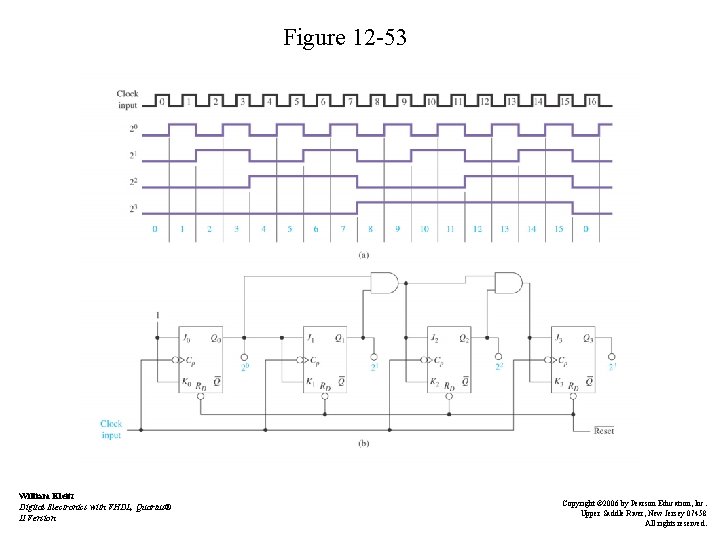

Synchronous Counters • All clock inputs tied to common clock line • 4 -bit synchronous counter – MOD 16 counter – 4 flip-flops – See Figure 12 -53 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -53 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

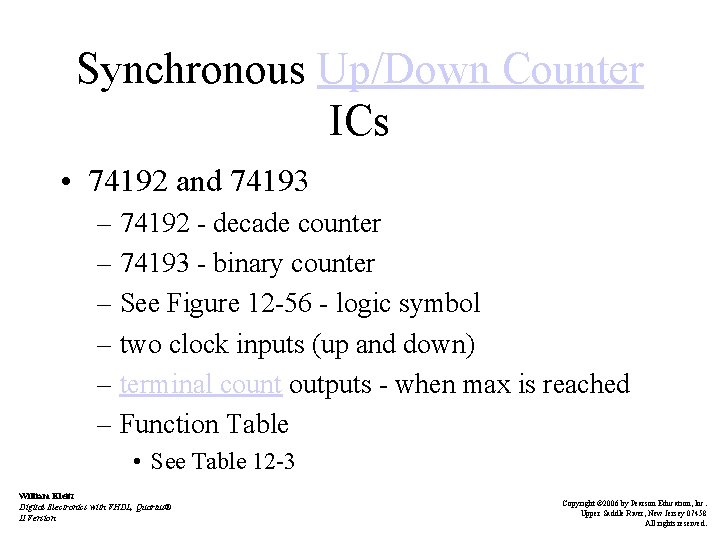

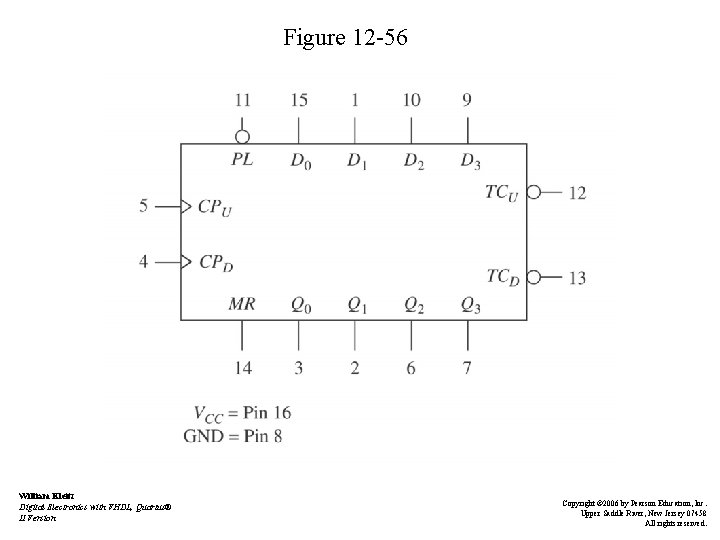

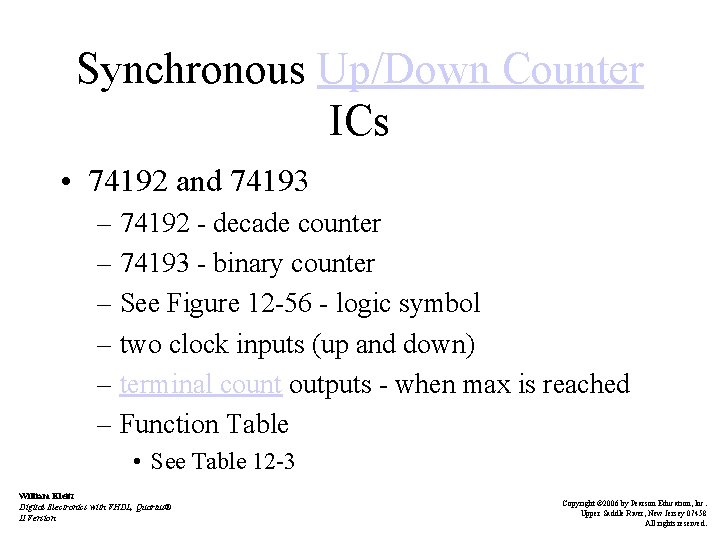

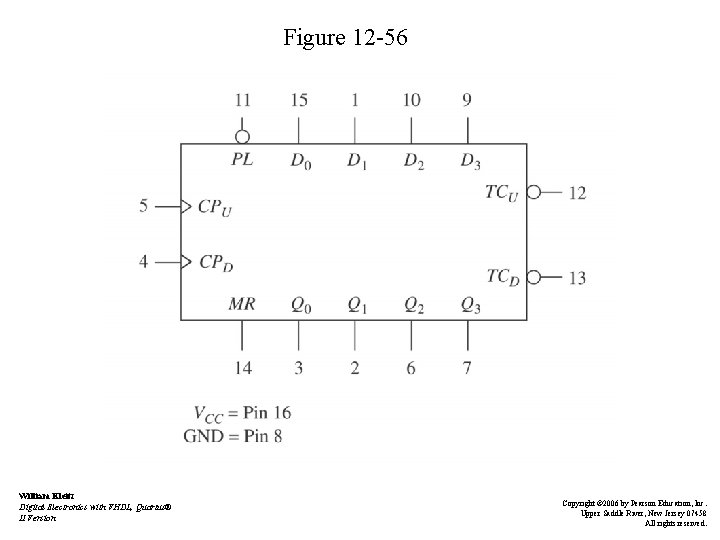

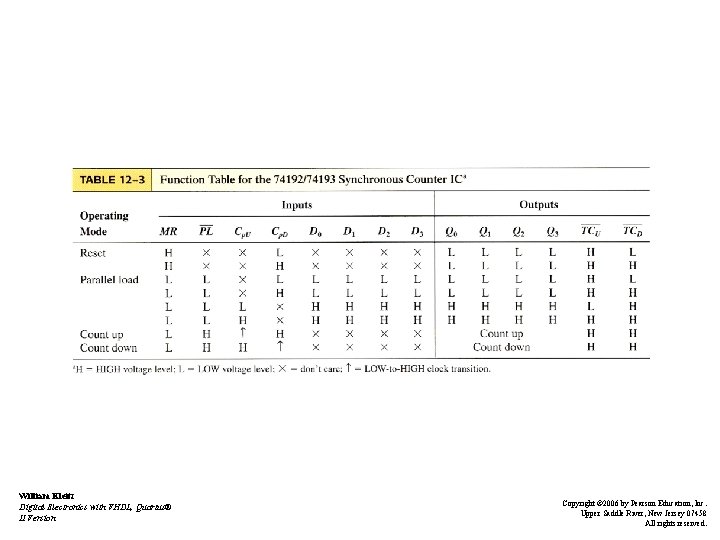

Synchronous Up/Down Counter ICs • 74192 and 74193 – 74192 - decade counter – 74193 - binary counter – See Figure 12 -56 - logic symbol – two clock inputs (up and down) – terminal count outputs - when max is reached – Function Table • See Table 12 -3 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -56 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

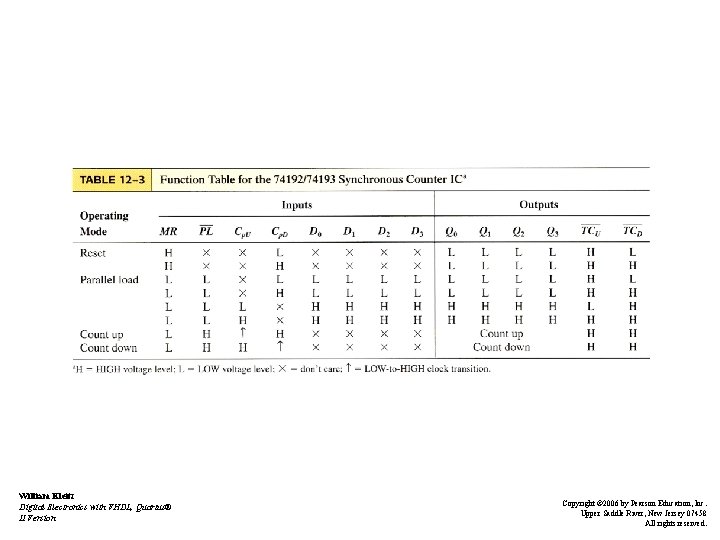

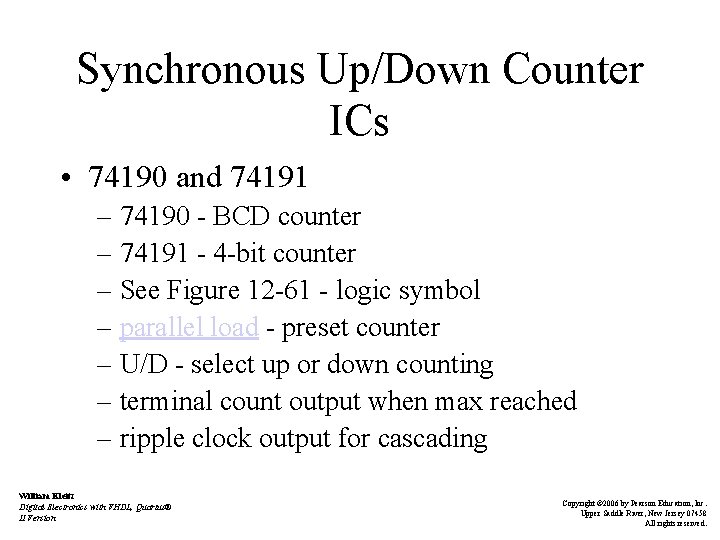

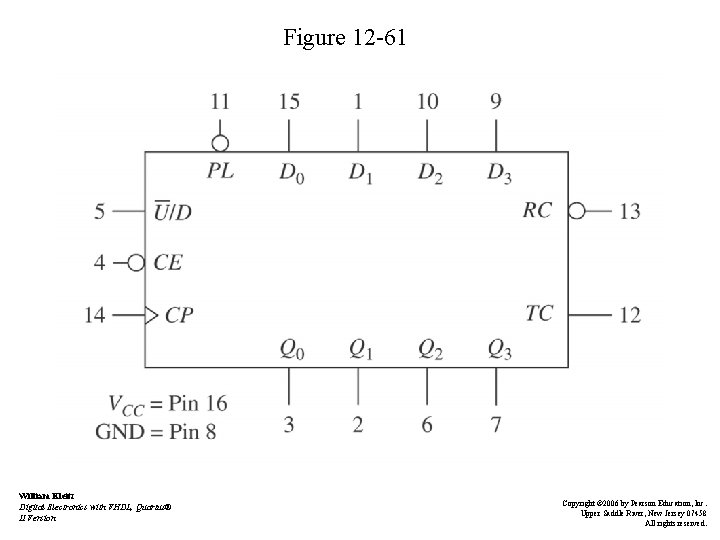

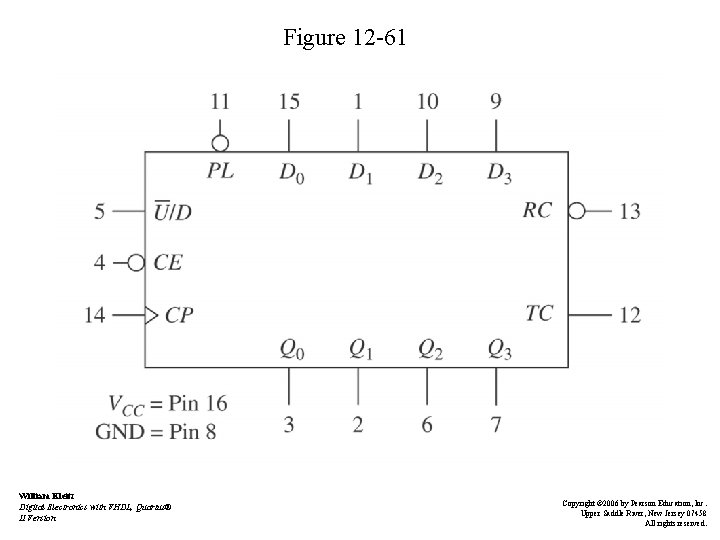

Synchronous Up/Down Counter ICs • 74190 and 74191 – 74190 - BCD counter – 74191 - 4 -bit counter – See Figure 12 -61 - logic symbol – parallel load - preset counter – U/D - select up or down counting – terminal count output when max reached – ripple clock output for cascading William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -61 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

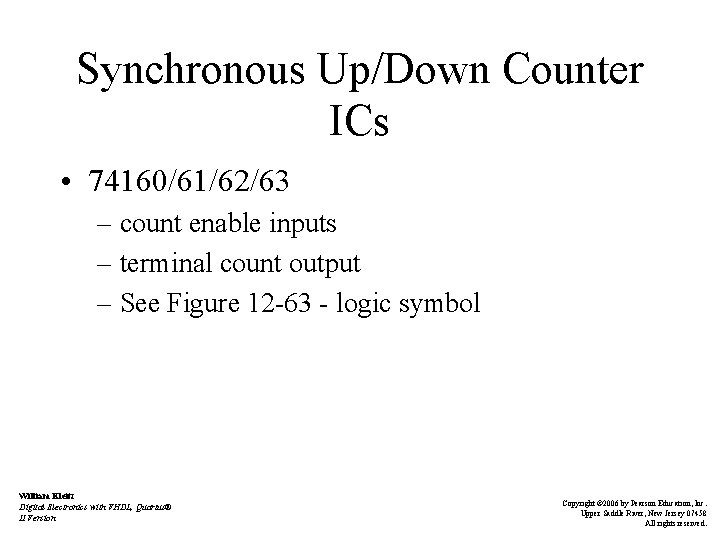

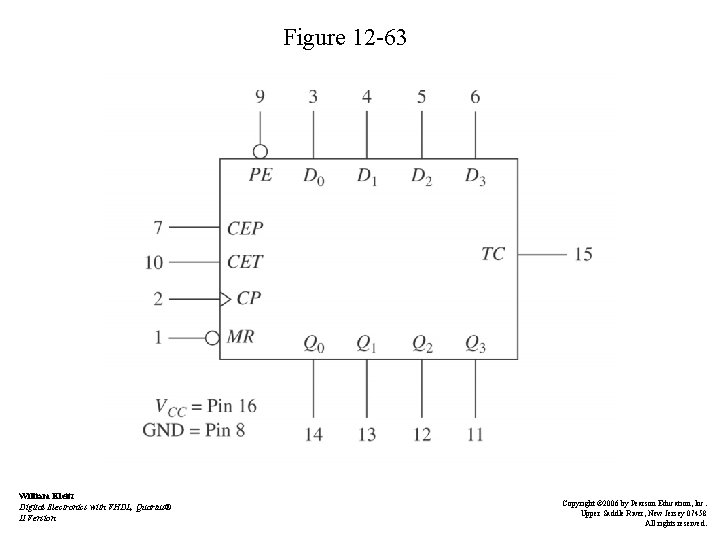

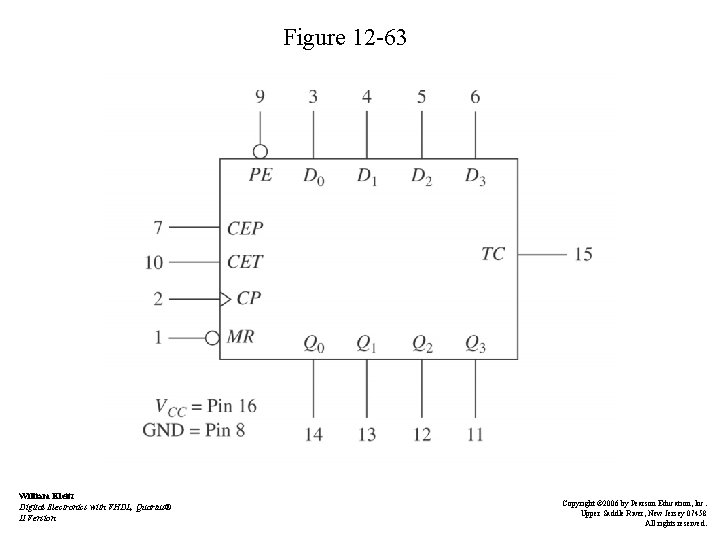

Synchronous Up/Down Counter ICs • 74160/61/62/63 – count enable inputs – terminal count output – See Figure 12 -63 - logic symbol William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -63 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

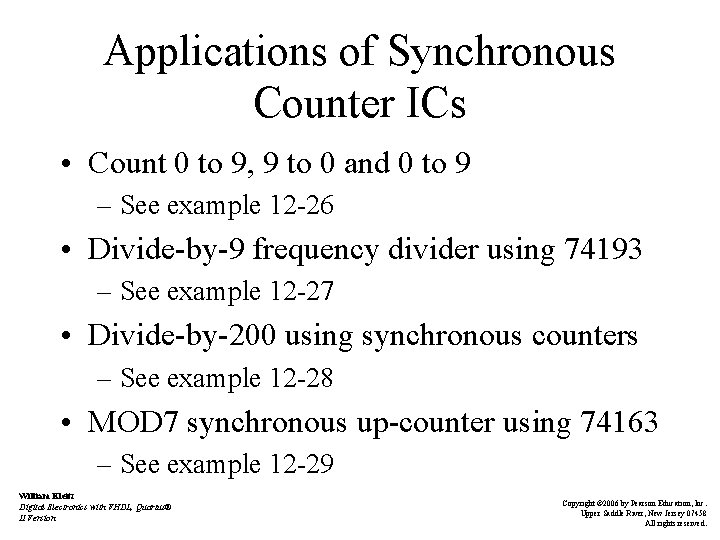

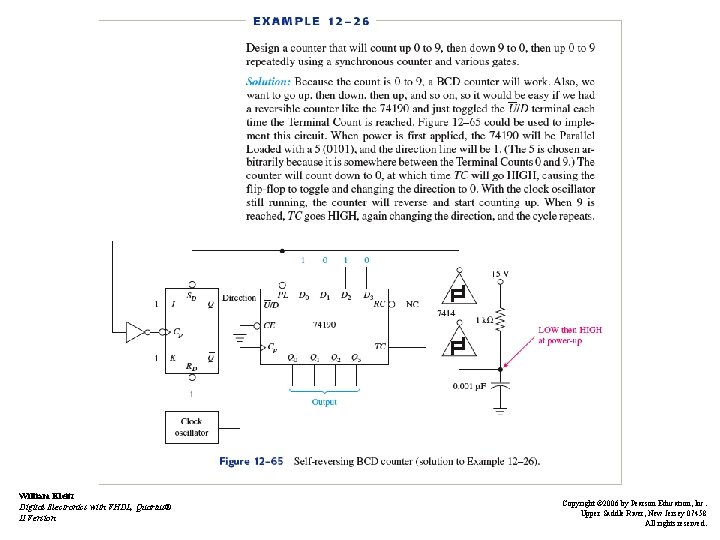

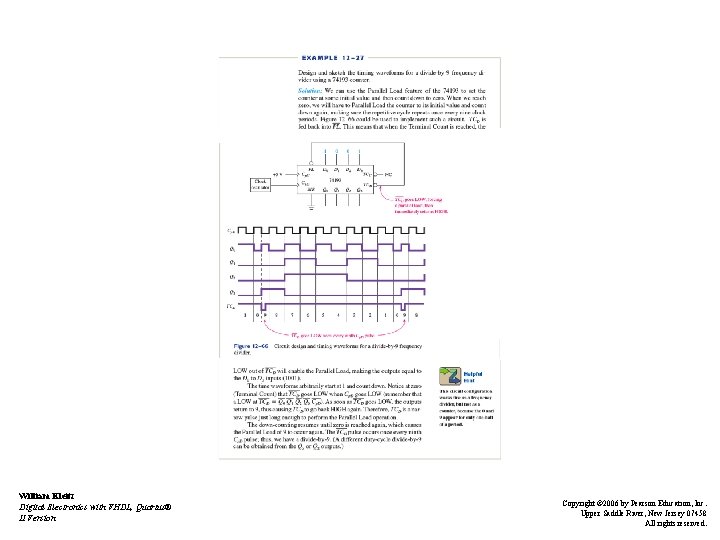

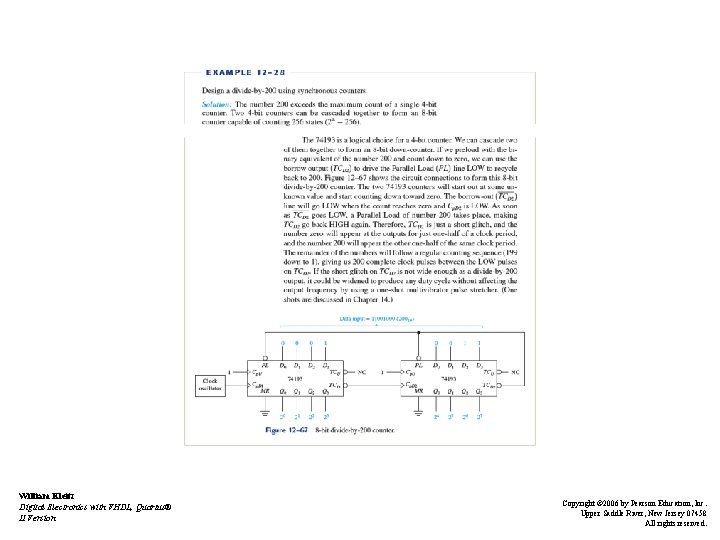

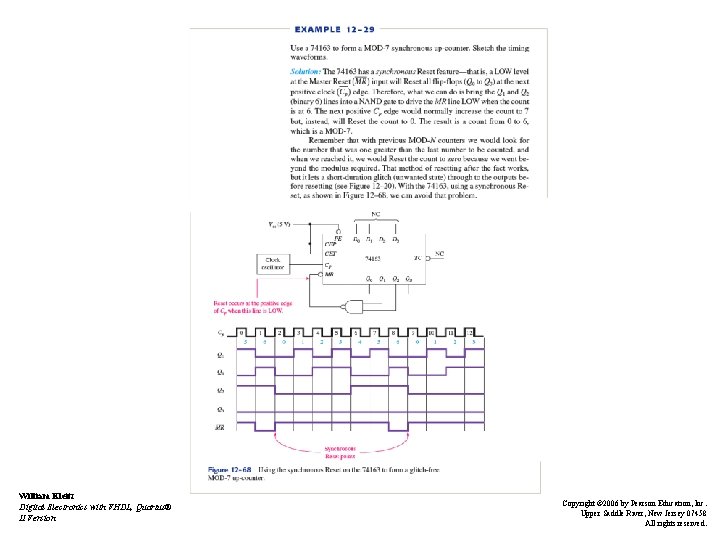

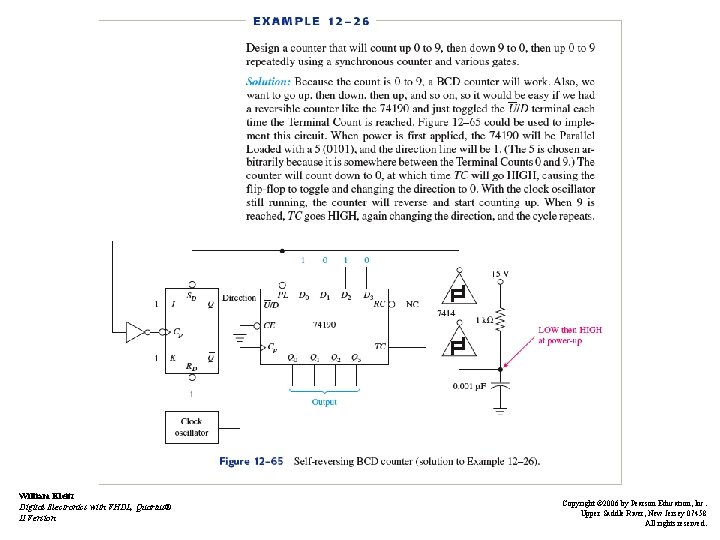

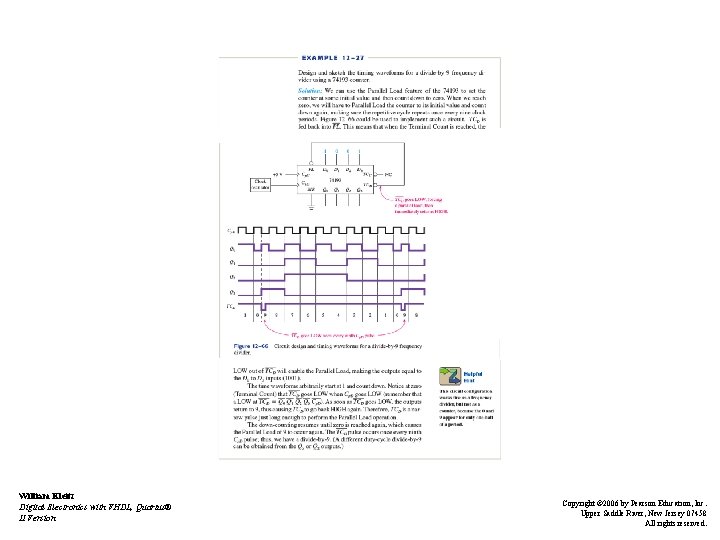

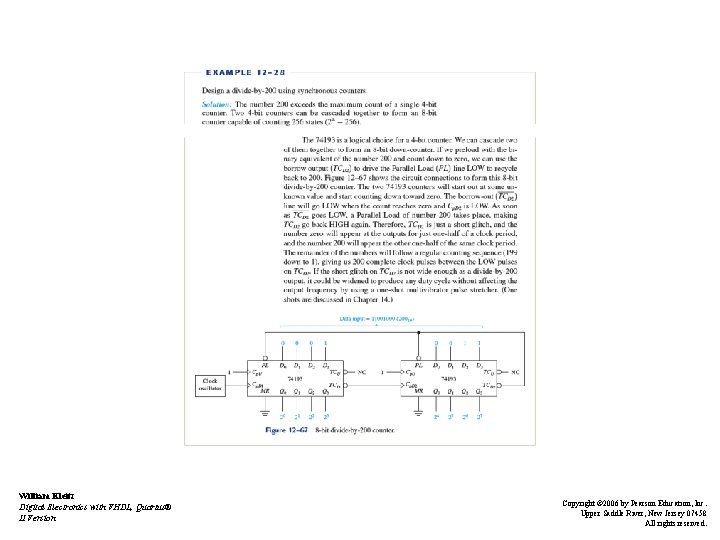

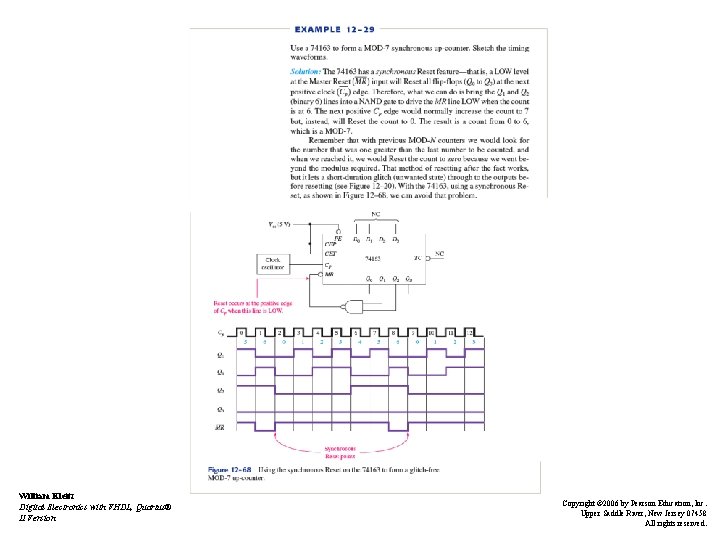

Applications of Synchronous Counter ICs • Count 0 to 9, 9 to 0 and 0 to 9 – See example 12 -26 • Divide-by-9 frequency divider using 74193 – See example 12 -27 • Divide-by-200 using synchronous counters – See example 12 -28 • MOD 7 synchronous up-counter using 74163 – See example 12 -29 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

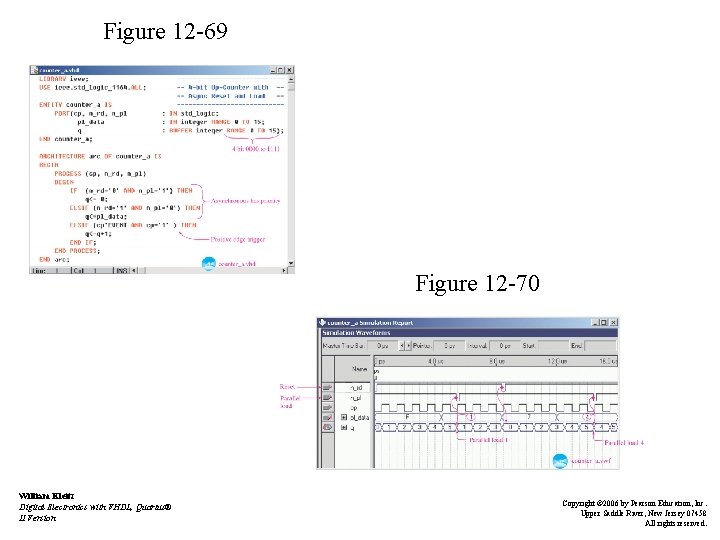

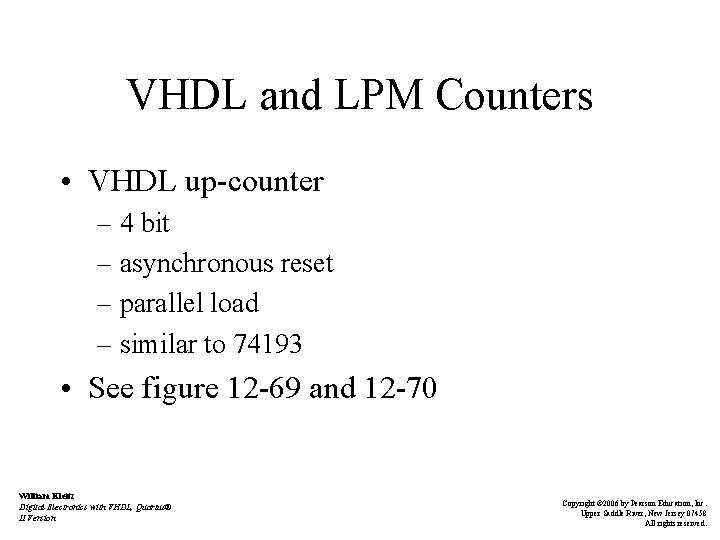

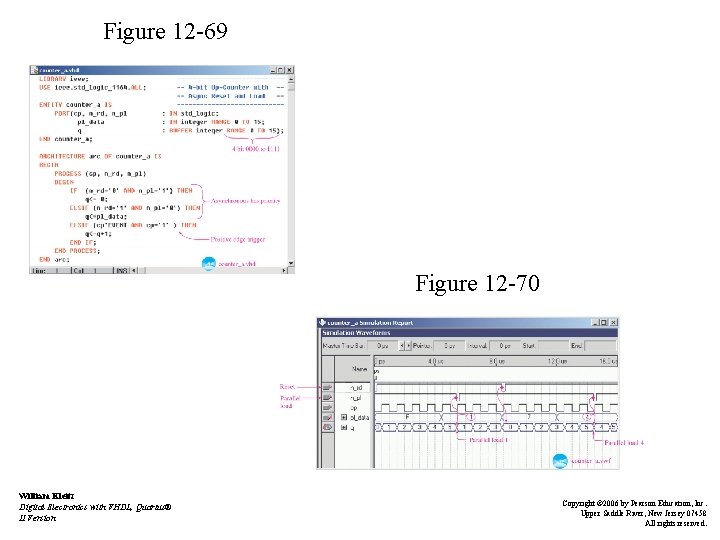

VHDL and LPM Counters • VHDL up-counter – 4 bit – asynchronous reset – parallel load – similar to 74193 • See figure 12 -69 and 12 -70 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -69 Figure 12 -70 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

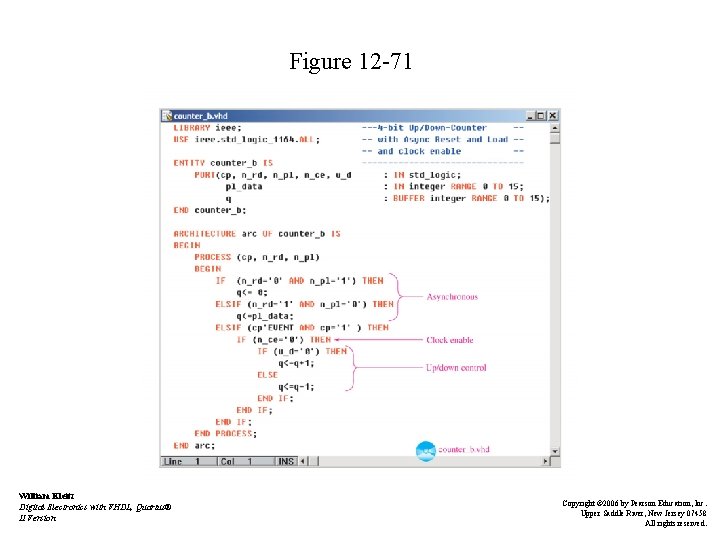

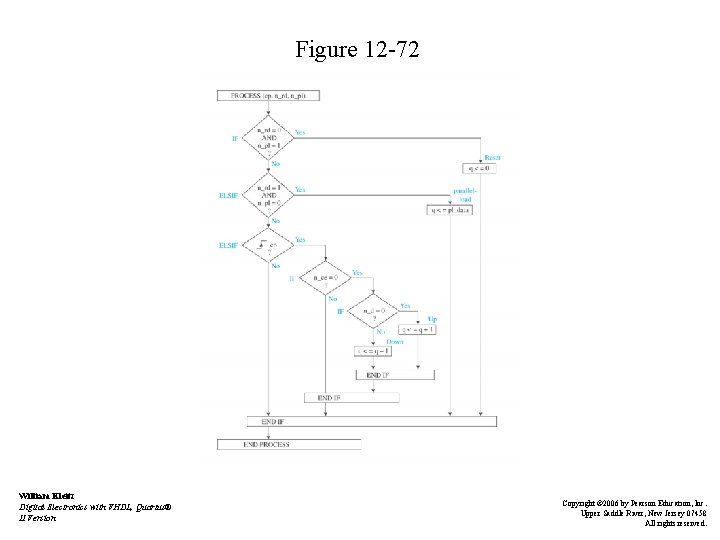

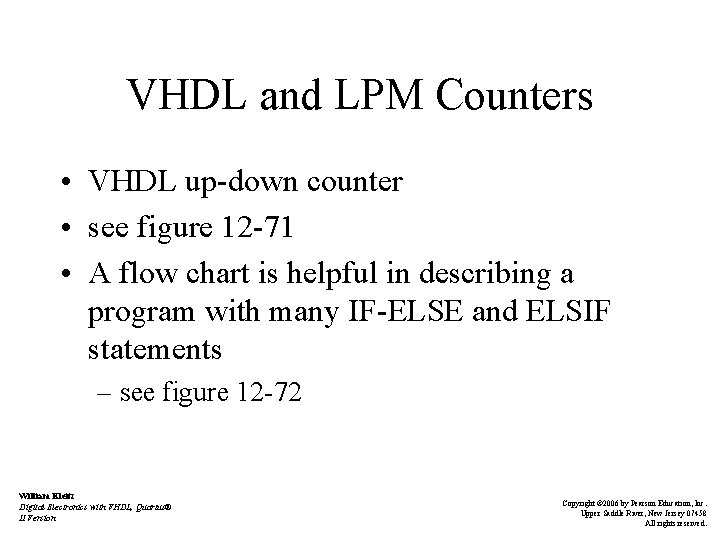

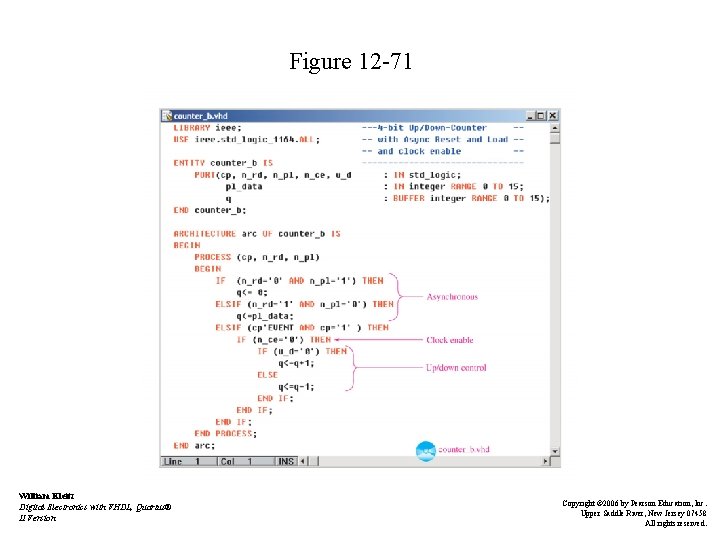

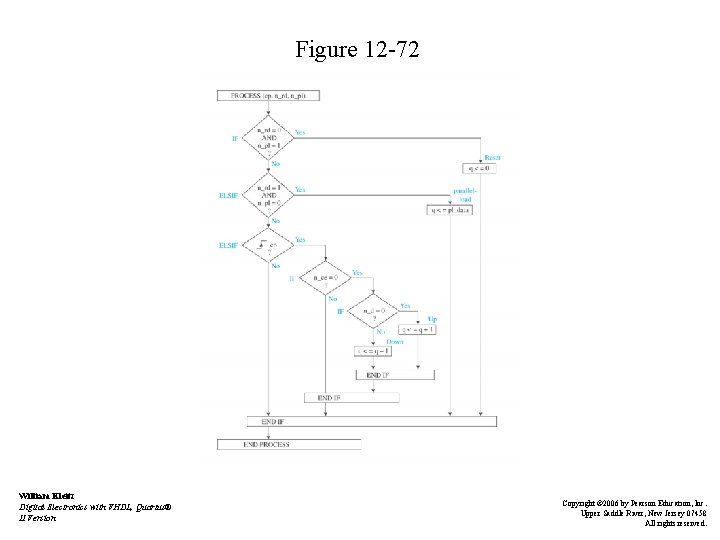

VHDL and LPM Counters • VHDL up-down counter • see figure 12 -71 • A flow chart is helpful in describing a program with many IF-ELSE and ELSIF statements – see figure 12 -72 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -71 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -72 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

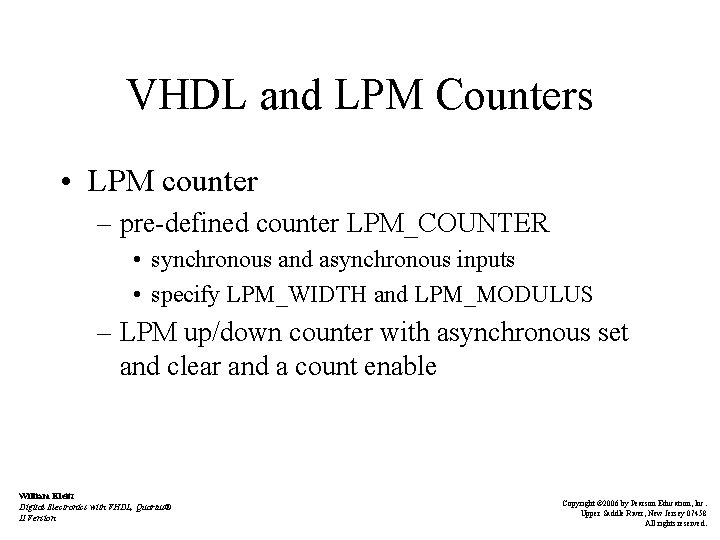

VHDL and LPM Counters • LPM counter – pre-defined counter LPM_COUNTER • synchronous and asynchronous inputs • specify LPM_WIDTH and LPM_MODULUS – LPM up/down counter with asynchronous set and clear and a count enable William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

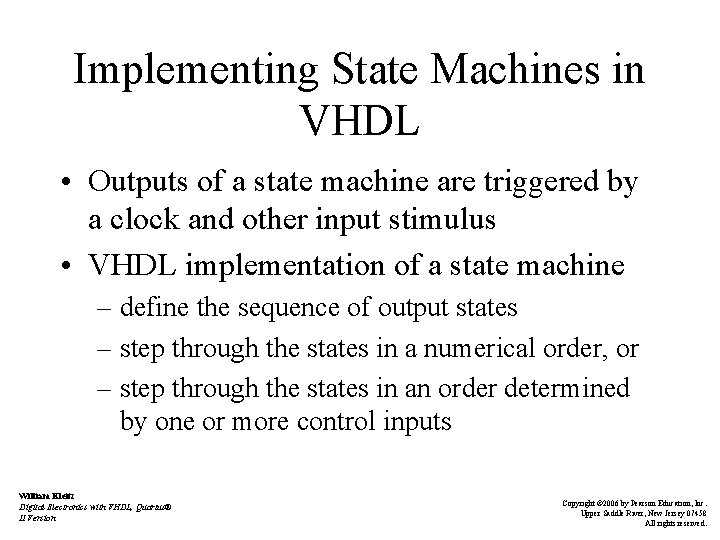

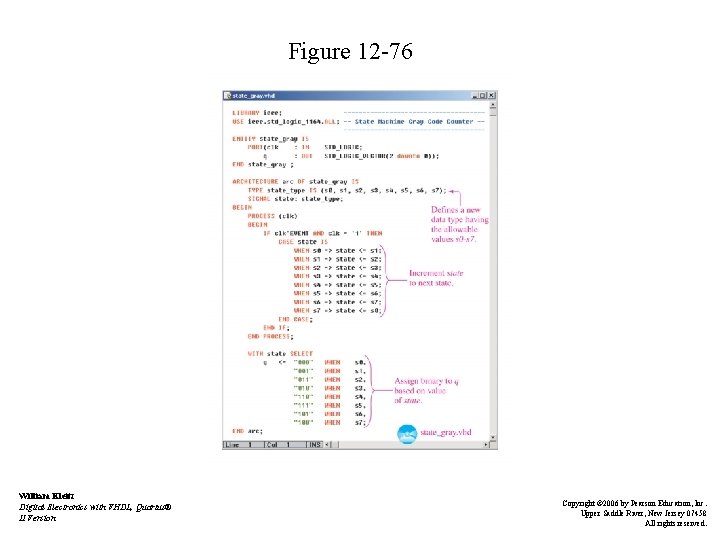

Implementing State Machines in VHDL • Outputs of a state machine are triggered by a clock and other input stimulus • VHDL implementation of a state machine – define the sequence of output states – step through the states in a numerical order, or – step through the states in an order determined by one or more control inputs William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

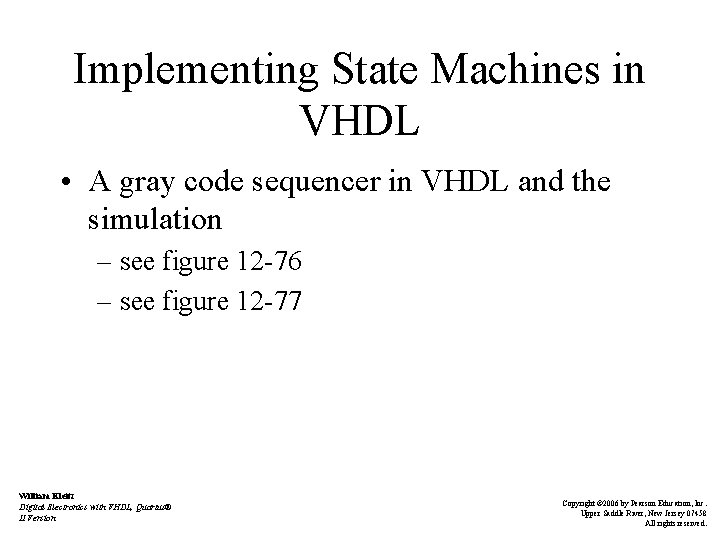

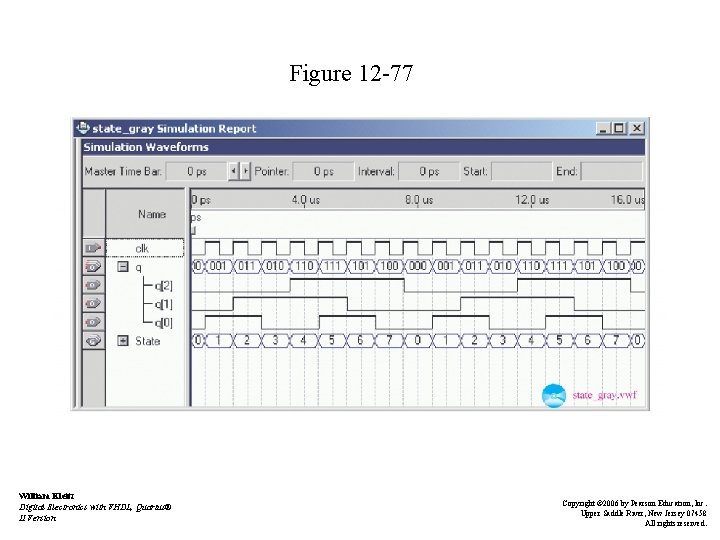

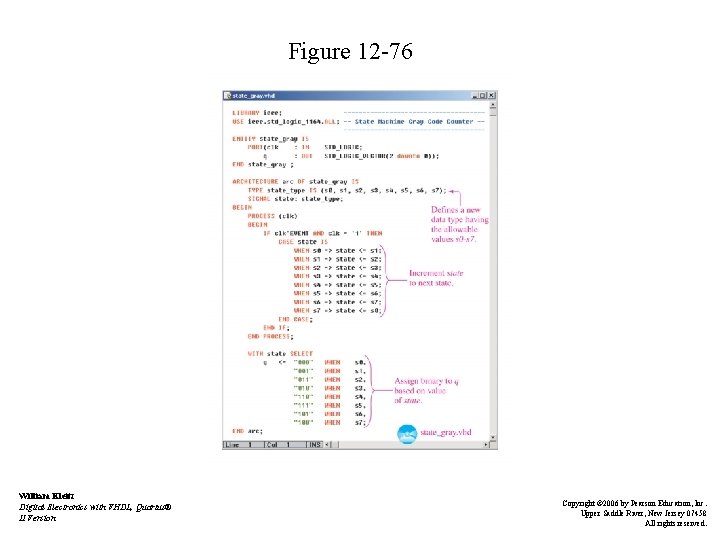

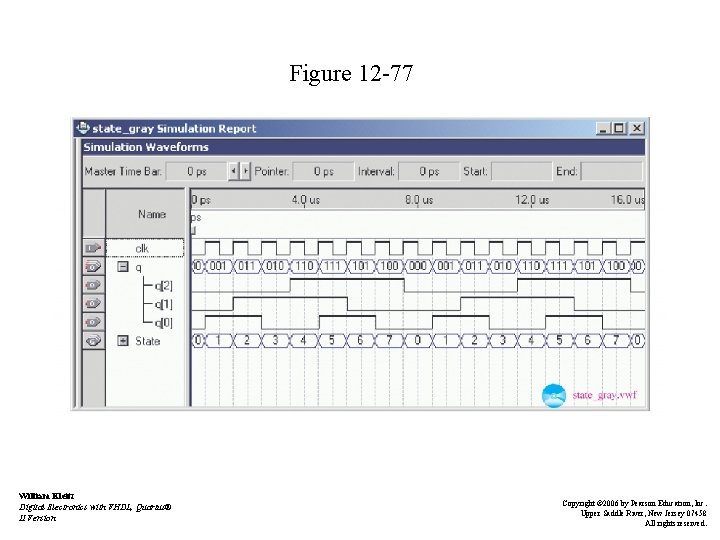

Implementing State Machines in VHDL • A gray code sequencer in VHDL and the simulation – see figure 12 -76 – see figure 12 -77 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -76 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -77 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

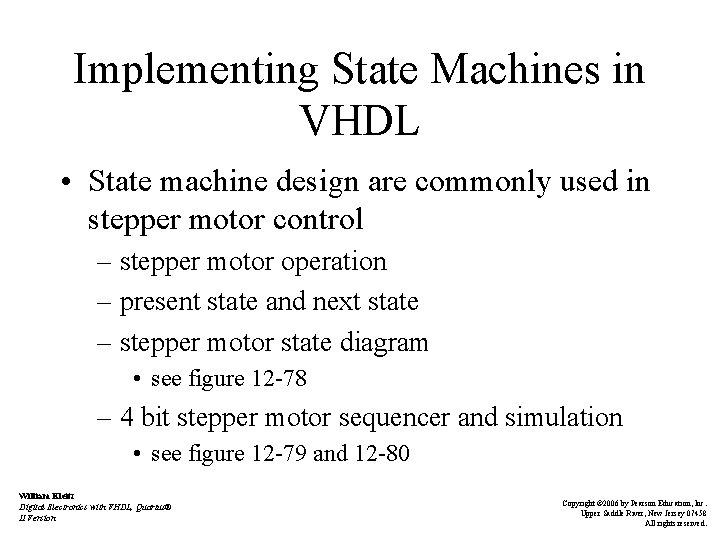

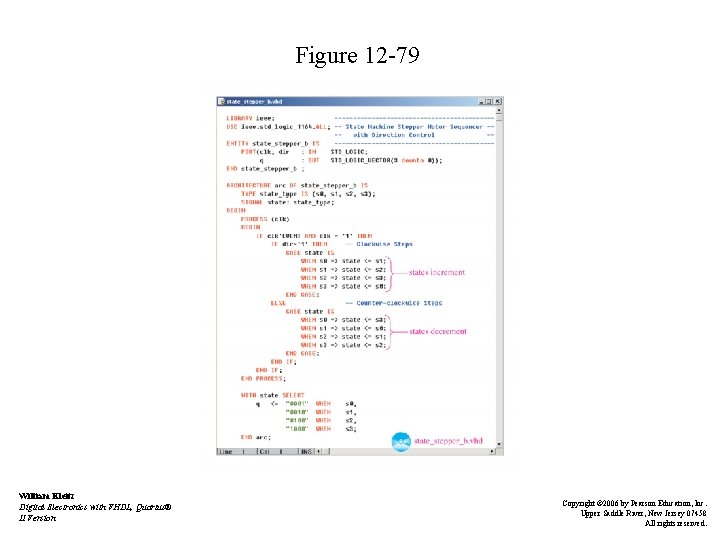

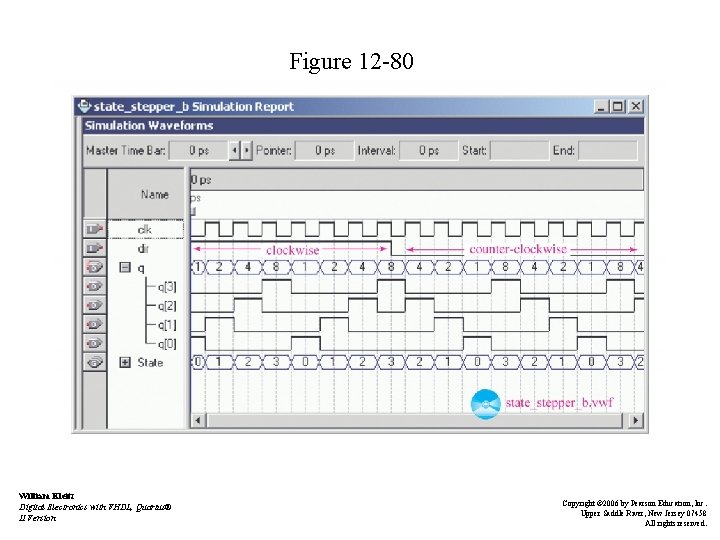

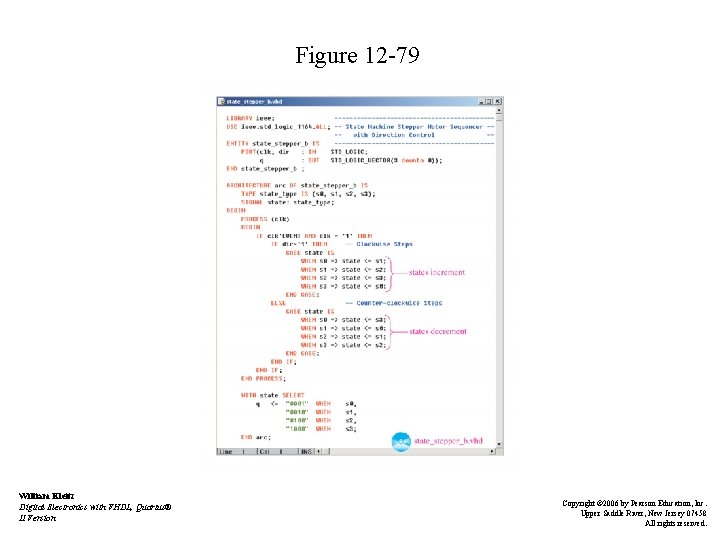

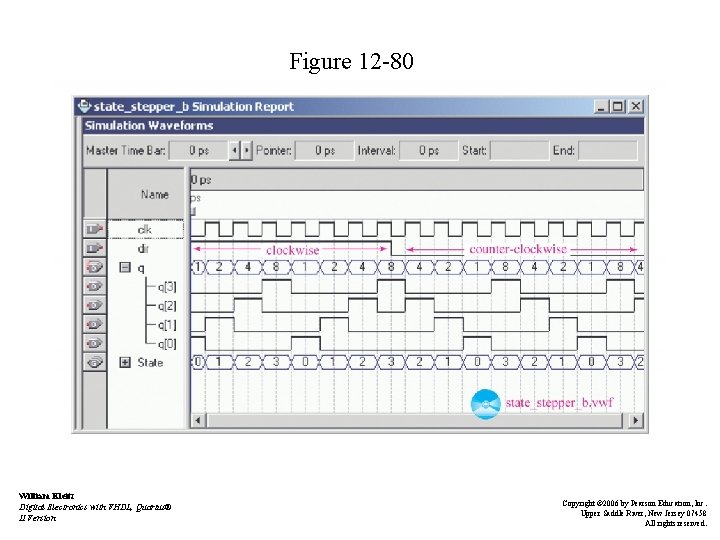

Implementing State Machines in VHDL • State machine design are commonly used in stepper motor control – stepper motor operation – present state and next state – stepper motor state diagram • see figure 12 -78 – 4 bit stepper motor sequencer and simulation • see figure 12 -79 and 12 -80 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -79 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Figure 12 -80 William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Implementing State Machines in VHDL • State machines with multiple control inputs – control (handshake) signals between peripherals and the microprocessor • read, write, ready to receive, ready to transmit, buffer full, end of transmit, and parity error • 8 bit Analog to digital converter (ADC) operation – the ADC in VHDL William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Summary • Toggle flip-flops can be cascaded end to form ripple counters. • Ripple counters cannot be used in highspeed circuits because of the problem they have with the accumulation of propagation delay through all the flip-flops. • A down counter can be built by taking the outputs from the not-Q’s of a ripple counter. William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Summary • Any modulus (or divide-by) counter can be formed by resetting the basic ripple counter when a specific count is reached. • A glitch is a short-duration pulse that may appear on some of the output bits of a counter. William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Summary • Ripple counter ICs such as the 7490, 7492, and 7493 have four flip-flops integrated into a single package providing four-bit counter operations. • Four-bit counter ICs can be cascaded end to form counters with higher than MOD 16 capability. William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Summary • Seven-segment LED displays choose between seven separate LEDs (plus a decimal point LED) to form the 10 decimal digits. They are constructed with either the anodes or the cathodes connected to a common pin. William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Summary • LED displays require a decoder/driver IC such as the 7447 to decode BCD data into a seven-bit code to activate the appropriate segments to illuminate the correct digit. • Synchronous counters eliminate the problem of accumulated propagation delay associated with ripple counters by driving all four flip-flops with a common clock. William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Summary • The 74192 and 74193 are 4 -bit synchronous counter ICs. They have a count-up/countdown feature and can accept a 4 -bit parallel load of binary data. • The 74190 and 74191 synchronous counter ICs are similar to the 74192/74193 except they are better for constructing multistage counters of more than 4 bits. William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Summary • VHDL can be used to implement Mod-n counters. • A seven segment decoder can be effectively described in VHDL. • The library of parameterized modules provides an LPM counter that can be customized to perform many counting tasks. • State Machines can be implemented in VHDL. William Kleitz Digital Electronics with VHDL, Quartus® II Version Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.