Capitolul 3 Sinteza clasic a SLS 2010 Proiectarea

- Slides: 39

Capitolul 3 Sinteza clasică a SLS 2010 Proiectarea sistemelor digitale 1

Tematica Etapele sintezei clasice a SLS sincrone Ø Determinarea maşinii reduse minime Ø Sinteza cu ajutorul registrelor Ø 2010 Proiectarea sistemelor digitale 2

Etapele sintezei clasice E 1. Pornind de la descrierea verbală se trece la descrierea formală prin diagrame de stare. E 2. Se trece de la diagrama de stare la tabelul de evoluţie a stărilor. E 3. Se încearcă reducerea numărului de stări. E 4. Se asignează stările, adică se trece de la reprezentarea prin nume simbolice, la reprezentarea codificată binar a stărilor. E 5. Se trece de la tabelul de stare la tabelul de tranziţie a stărilor şi tabelul de ieşire. E 6. Din tabelul de ieşire se sintetizează funcţiile de ieşire printr-una dintre metodele cunoscute pentru sinteza SLC. E 7. Se alege tipul de bistabil utilizat pentru sinteză. E 8. Pornind de la tabelul de tranziţie a stărilor şi tabelul de excitaţie a bistabilelor, se generează tabelul de excitaţie al SLS sintetizate. 2010 Proiectarea sistemelor digitale 3

Etapele sintezei clasice E 9. Din tabelul de excitaţie se sintetizează funcţiile de excitaţie printr-una dintre metodele cunoscute pentru sinteza SLC. E 10. Se desenează SLS sintetizată. E 11. Se analizează evoluţia în spaţiul stărilor pentru a verifica corectitudinea sintezei şi pentru a pune în evidenţă eventualele anomalii datorate caracterului incomplet specificat al funcţiilor de excitaţie şi de ieşire. De obicei, astfel de anomalii pot fi rezolvate prin introducerea unei comenzi asincrone de iniţializare dar, în anumite situaţii, se poate recurge la reproiectare prin precizarea corespunzătoare a valorilor nespecificate din tabelul de tranziţie al stărilor şi în tabelul de ieşire, care au generat anomalia. E 12. Din cataloagele de componente se aleg circuitele integrate utilizate pentru implementarea efectivă a schemei. E 13. În cazul unor scheme de mare complexitate sau care lucrează la valori apropiate de valoarea maximă admisă pentru frecvenţa impulsului de tact, este necesară şi analiza temporală a schemei obţinute. Eventualele anomalii puse în evidenţă aici pot conduce la necesitatea alegerii altor componente pentru implementare sau chiar la necesitatea alegerii unei alte metode de sinteză a funcţiilor de excitaţie şi ieşire. 2010 Proiectarea sistemelor digitale 4

Asignarea stărilor Prin asignarea stărilor vom ȋnțelege asocierea de către proiectant a unei combinații binare unice fiecărei stări simbolice a unei maşini secvențiale. Se observă că procesul de asignare este un proces artificial şi principial există o infinitate de asignări posibile, cu condiția ca la două stări diferite să fie asociate două combinații binare diferite. În procesul de asignare se utilizează ca ipoteză de lucru fundamentală codificarea tuturor stărilor cu combinații binare având aceeaşi lungime. În continuare vor fi analizate două metode frecvent utilizate pentru asignarea stărilor. 2010 Proiectarea sistemelor digitale 5

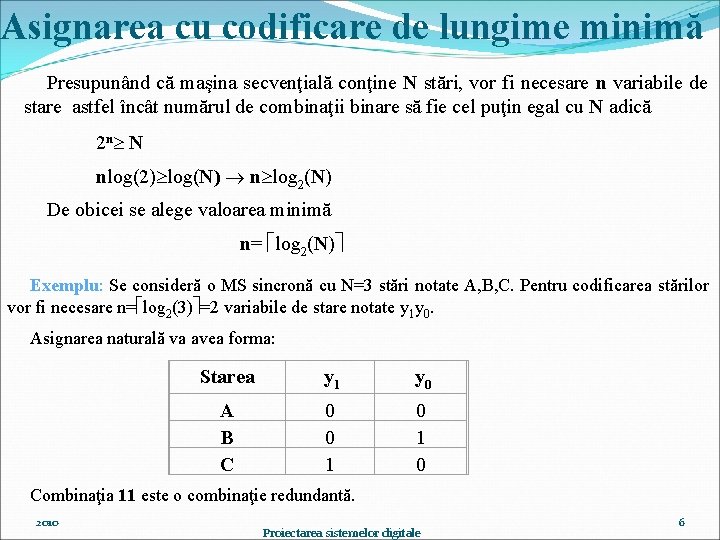

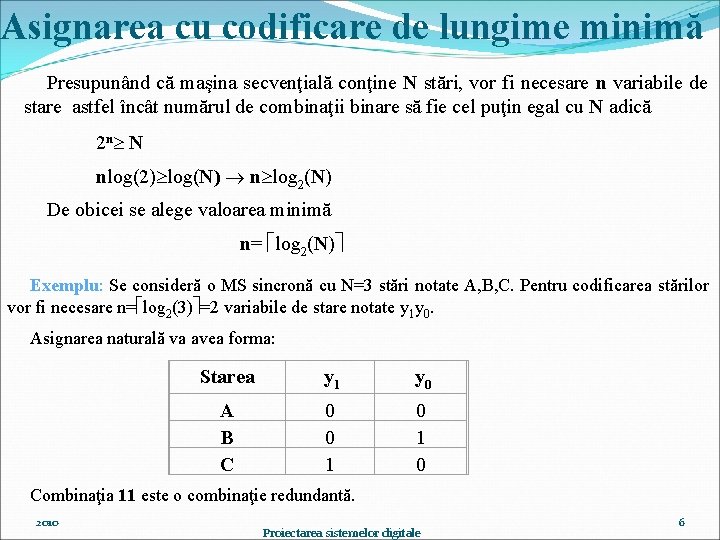

Asignarea cu codificare de lungime minimă Presupunând că maşina secvenţială conţine N stări, vor fi necesare n variabile de stare astfel încât numărul de combinaţii binare să fie cel puţin egal cu N adică 2 n N nlog(2) log(N) n log 2(N) De obicei se alege valoarea minimă n= log 2(N) Exemplu: Se consideră o MS sincronă cu N=3 stări notate A, B, C. Pentru codificarea stărilor vor fi necesare n= log 2(3) =2 variabile de stare notate y 1 y 0. Asignarea naturală va avea forma: Starea y 1 y 0 A B C 0 0 1 0 Combinaţia 11 este o combinaţie redundantă. 2010 Proiectarea sistemelor digitale 6

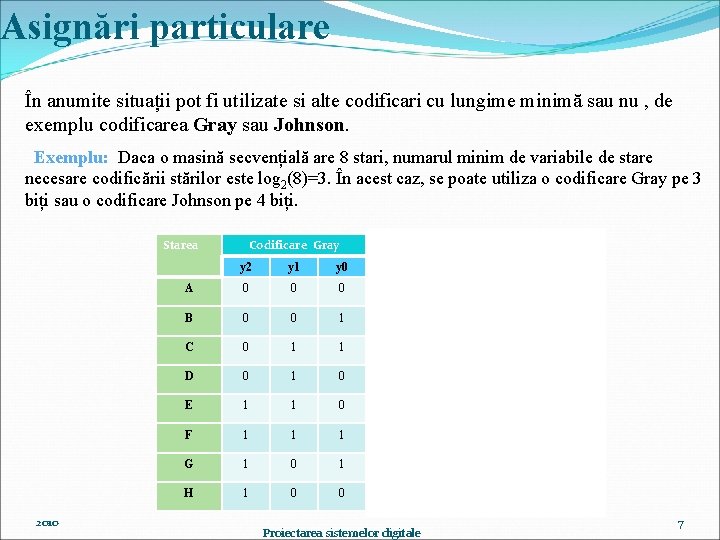

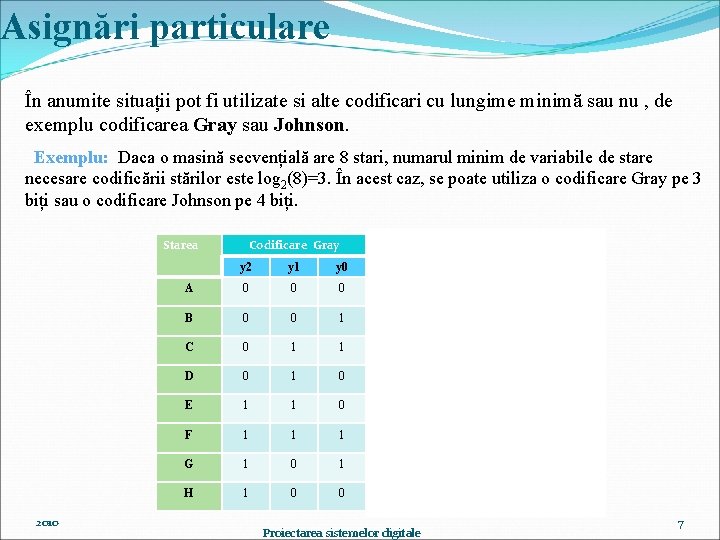

Asignări particulare În anumite situații pot fi utilizate si alte codificari cu lungime minimă sau nu , de exemplu codificarea Gray sau Johnson. Exemplu: Daca o masină secvențială are 8 stari, numarul minim de variabile de stare necesare codificării stărilor este log 2(8)=3. În acest caz, se poate utiliza o codificare Gray pe 3 biți sau o codificare Johnson pe 4 biți. Starea 2010 Codificare Gray Codificare Johnson y 2 y 1 y 0 y 3 y 2 y 1 y 0 A 0 0 0 0 B 0 0 1 0 0 0 1 C 0 1 1 0 0 1 1 D 0 1 0 0 1 1 1 E 1 1 0 1 1 F 1 1 1 0 G 1 0 1 1 1 0 0 H 1 0 0 0 Proiectarea sistemelor digitale 7

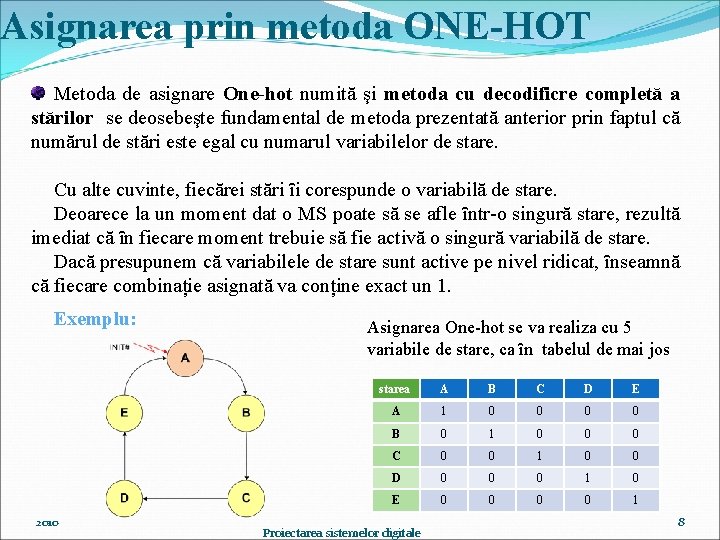

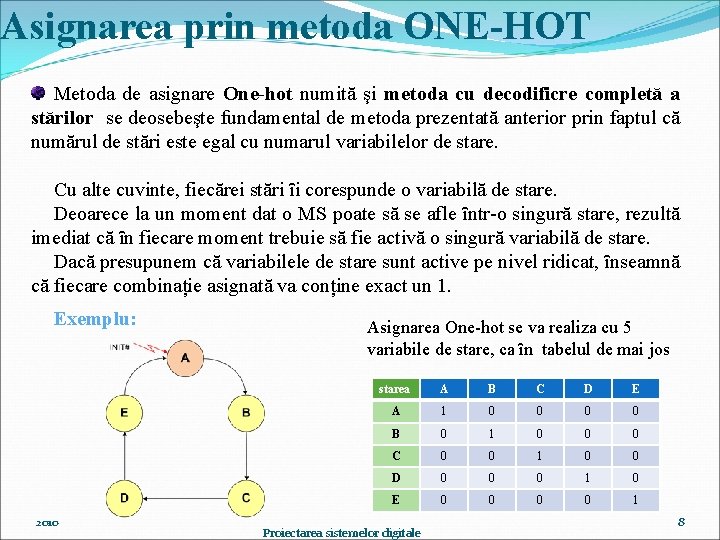

Asignarea prin metoda ONE-HOT Metoda de asignare One-hot numită şi metoda cu decodificre completă a stărilor se deosebeşte fundamental de metoda prezentată anterior prin faptul că numărul de stări este egal cu numarul variabilelor de stare. Cu alte cuvinte, fiecărei stări ȋi corespunde o variabilă de stare. Deoarece la un moment dat o MS poate să se afle ȋntr-o singură stare, rezultă imediat că ȋn fiecare moment trebuie să fie activă o singură variabilă de stare. Dacă presupunem că variabilele de stare sunt active pe nivel ridicat, ȋnseamnă că fiecare combinație asignată va conține exact un 1. Exemplu: 2010 Asignarea One-hot se va realiza cu 5 variabile de stare, ca ȋn tabelul de mai jos starea A B C D E A 1 0 0 B 0 1 0 0 0 C 0 0 1 0 0 D 0 0 0 1 0 E 0 0 1 Proiectarea sistemelor digitale 8

Exemple de sinteză 2010 Proiectarea sistemelor digitale 9

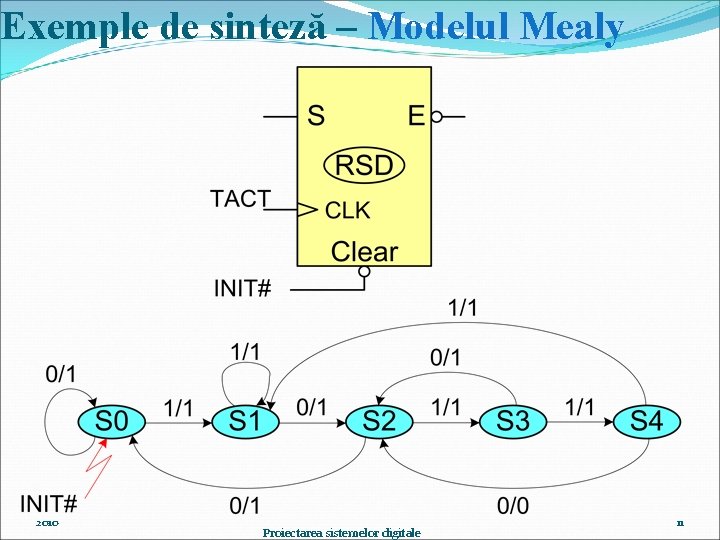

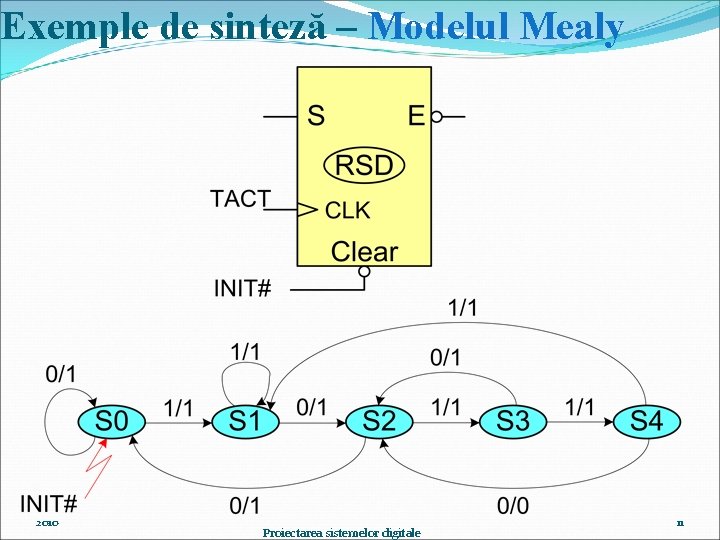

Exemple de sinteză Să se sintetizeze un recunoscător de secvenţă dinamic (RSD) care semnalează prin 0 logic la ieşire ori de câte ori în şirul binar de la intrare apare secvenţa 10110. Schema este prevăzută şi cu o intrare de iniţializare asincronă Clear activă pe nivel coborât. Se vor lua în considerare atât varianta Mealy cât şi varianta Moore. 2010 Proiectarea sistemelor digitale 10

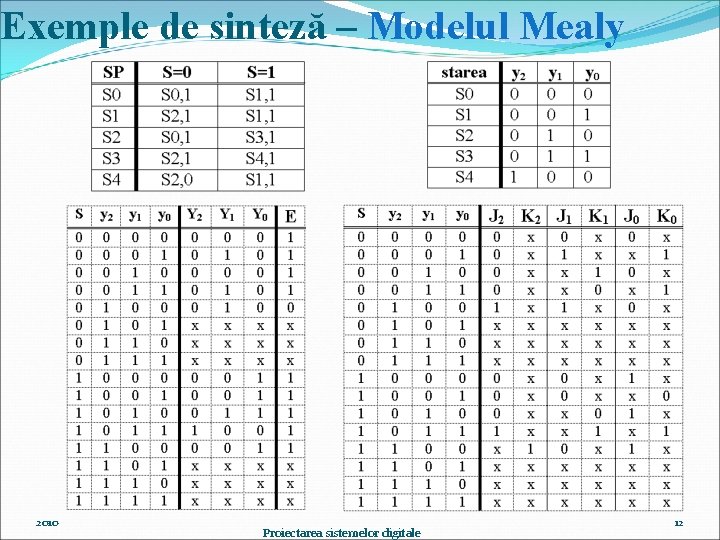

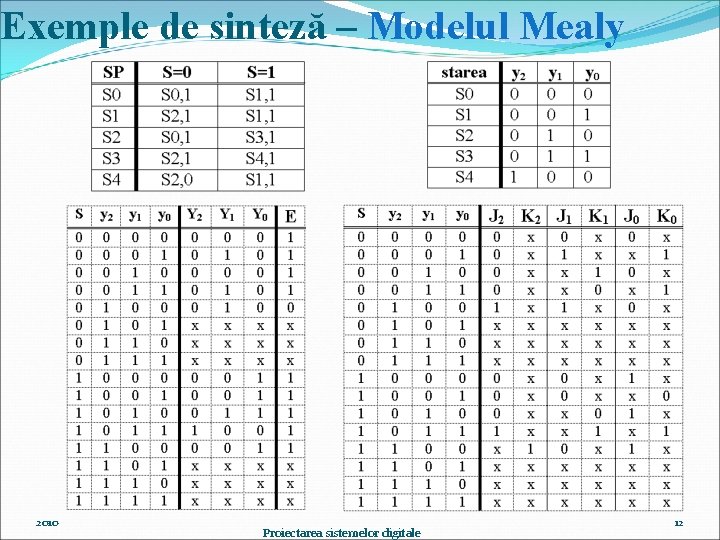

Exemple de sinteză – Modelul Mealy 2010 Proiectarea sistemelor digitale 11

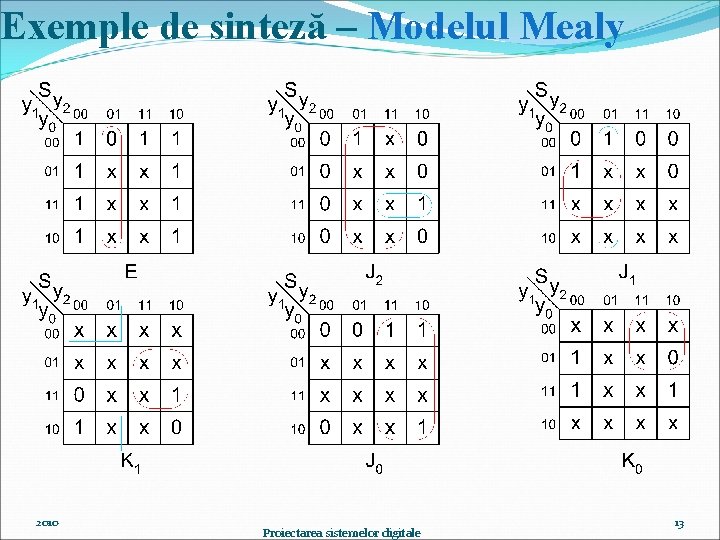

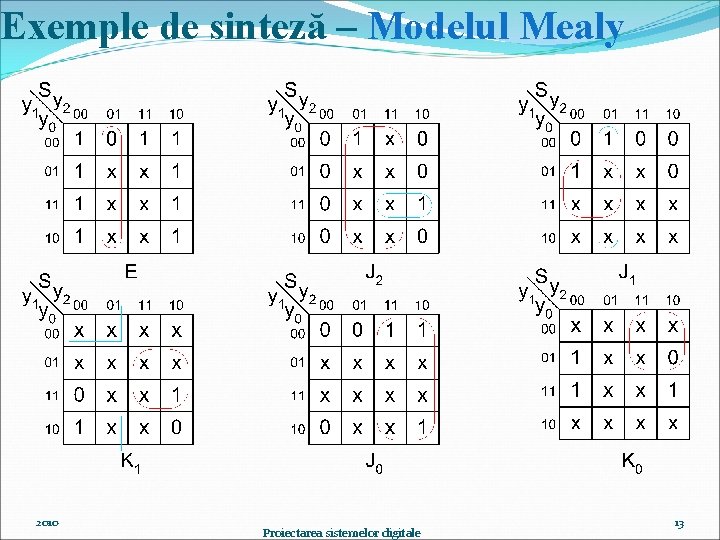

Exemple de sinteză – Modelul Mealy 2010 Proiectarea sistemelor digitale 12

Exemple de sinteză – Modelul Mealy 2010 Proiectarea sistemelor digitale 13

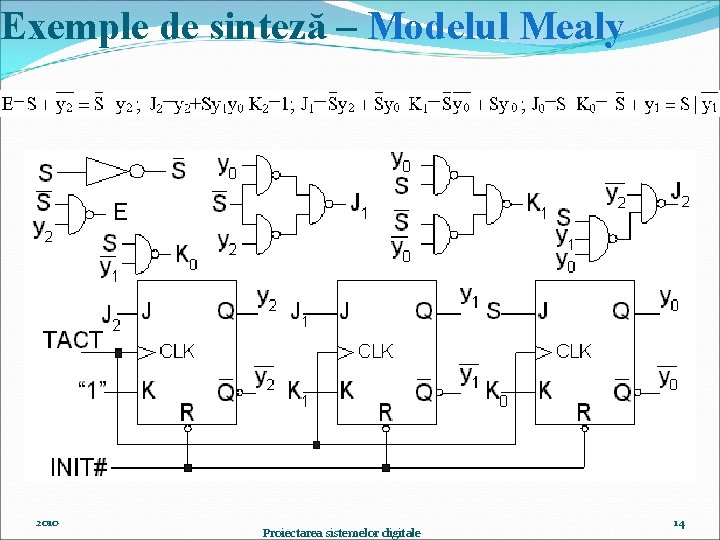

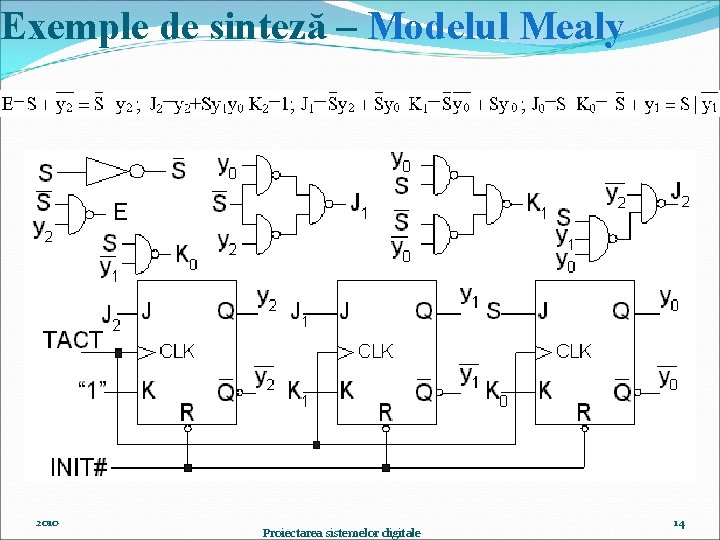

Exemple de sinteză – Modelul Mealy 2010 Proiectarea sistemelor digitale 14

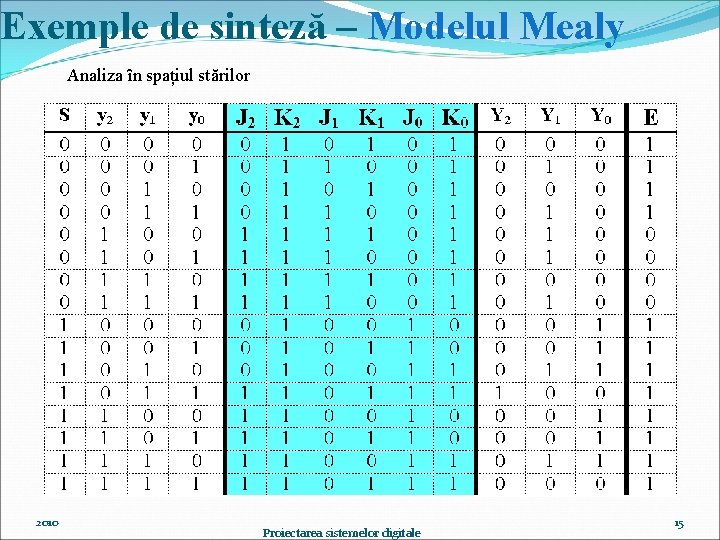

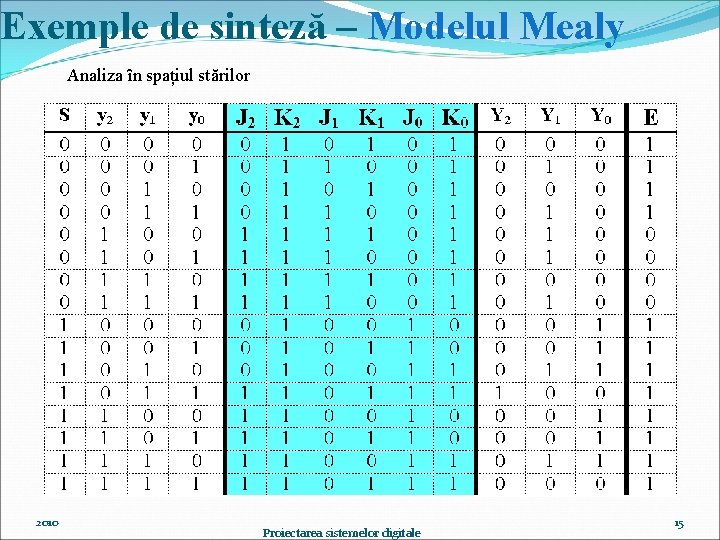

Exemple de sinteză – Modelul Mealy Analiza ȋn spațiul stărilor 2010 Proiectarea sistemelor digitale 15

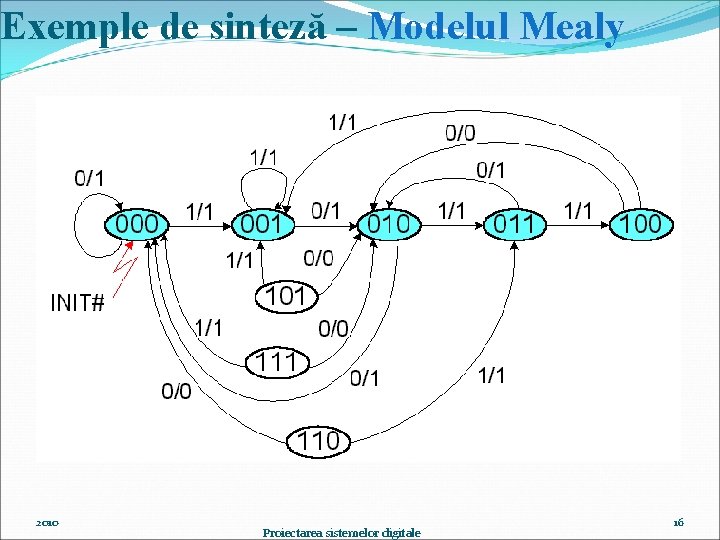

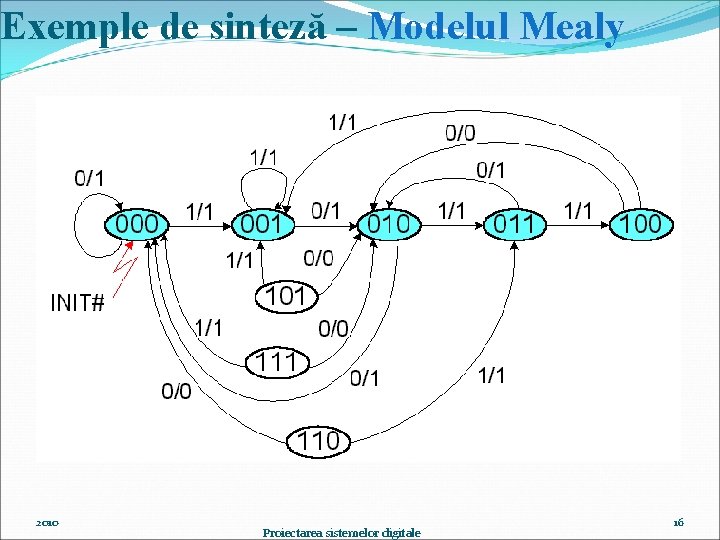

Exemple de sinteză – Modelul Mealy 2010 Proiectarea sistemelor digitale 16

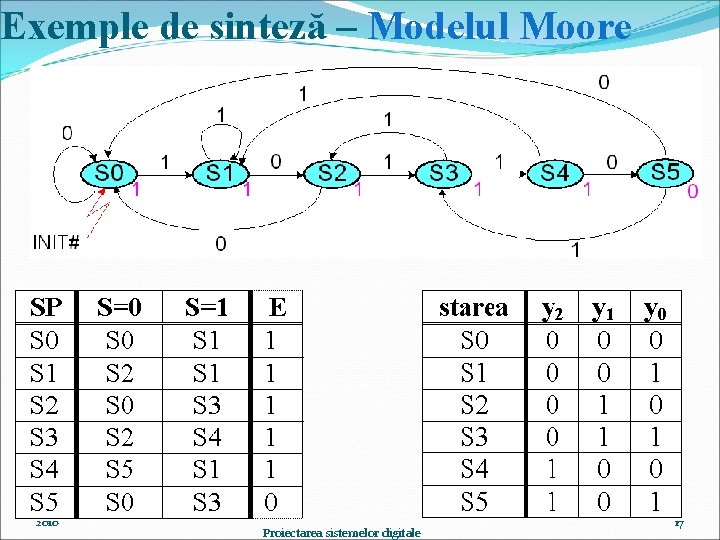

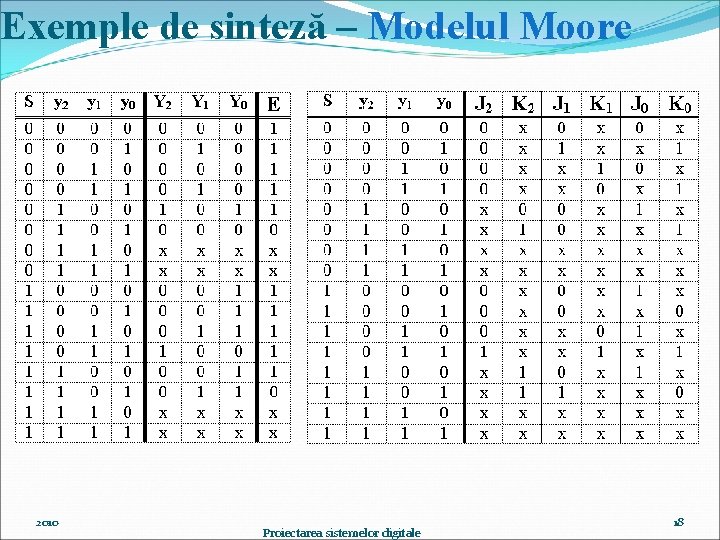

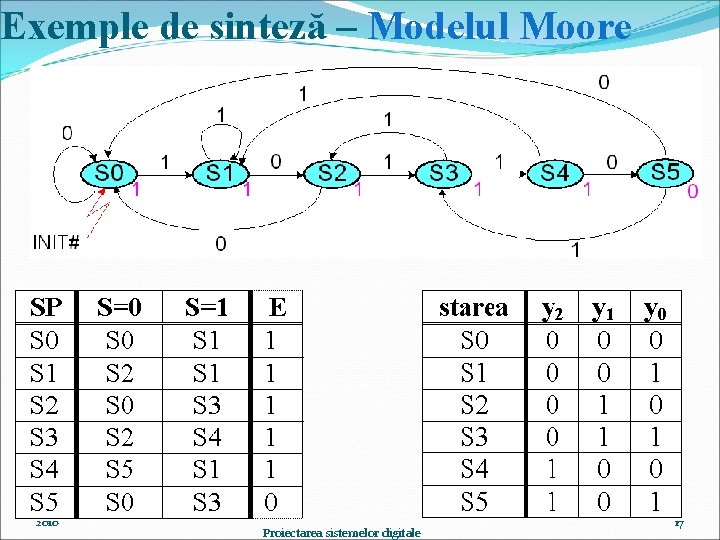

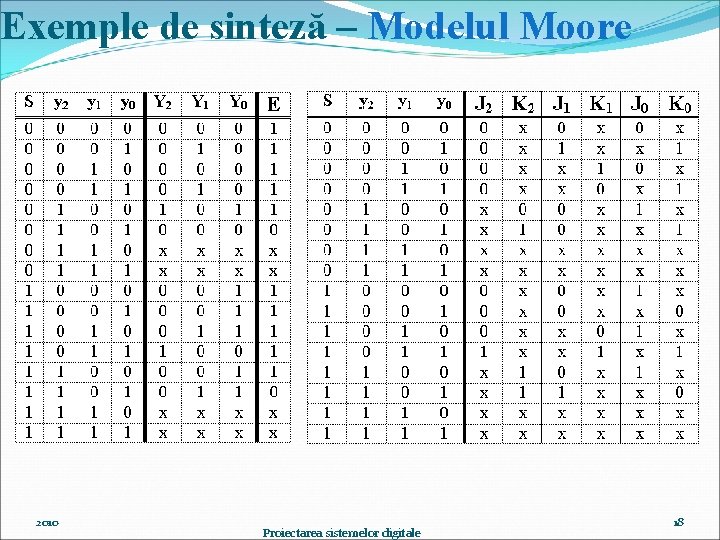

Exemple de sinteză – Modelul Moore 2010 Proiectarea sistemelor digitale 17

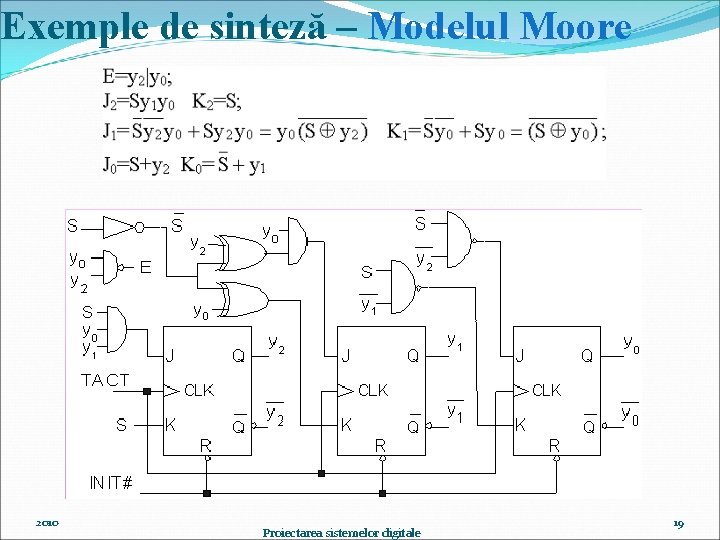

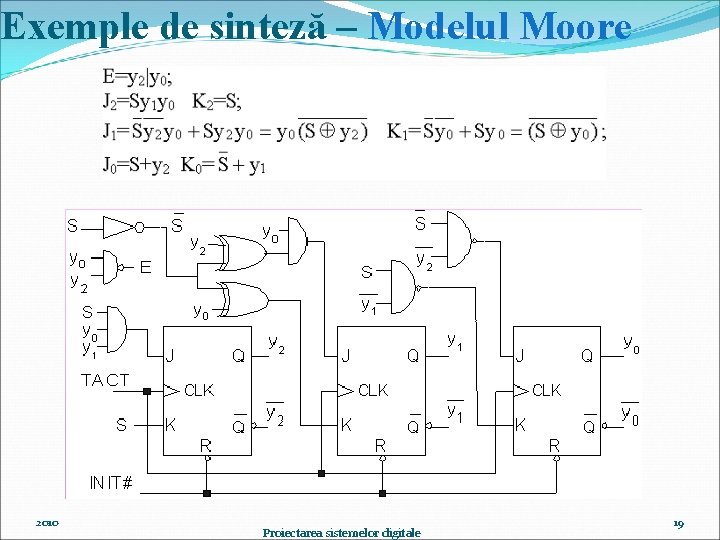

Exemple de sinteză – Modelul Moore 2010 Proiectarea sistemelor digitale 18

Exemple de sinteză – Modelul Moore 2010 Proiectarea sistemelor digitale 19

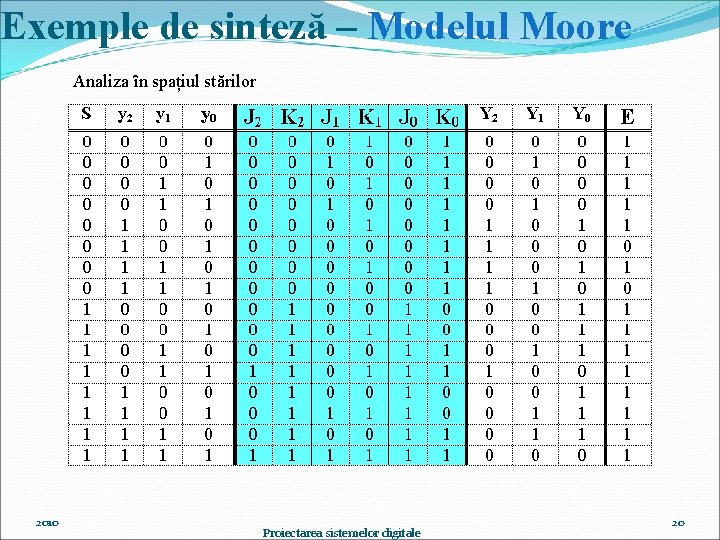

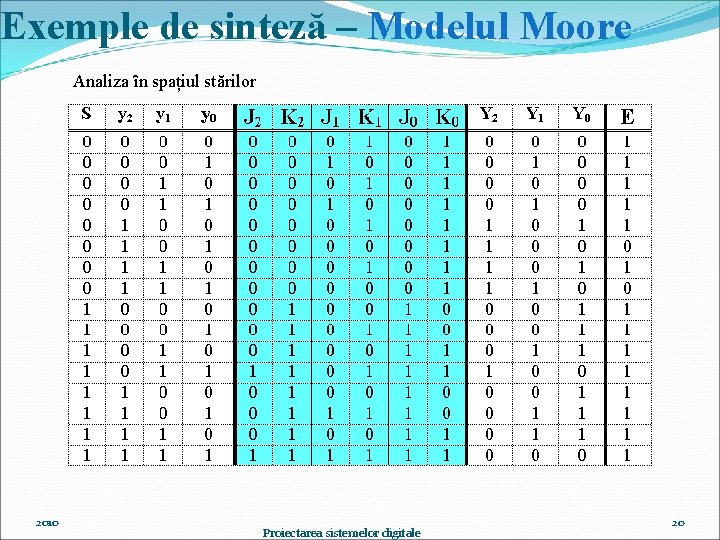

Exemple de sinteză – Modelul Moore Analiza ȋn spațiul stărilor 2010 Proiectarea sistemelor digitale 20

Exemple de sinteză – Modelul Moore 2010 Proiectarea sistemelor digitale 21

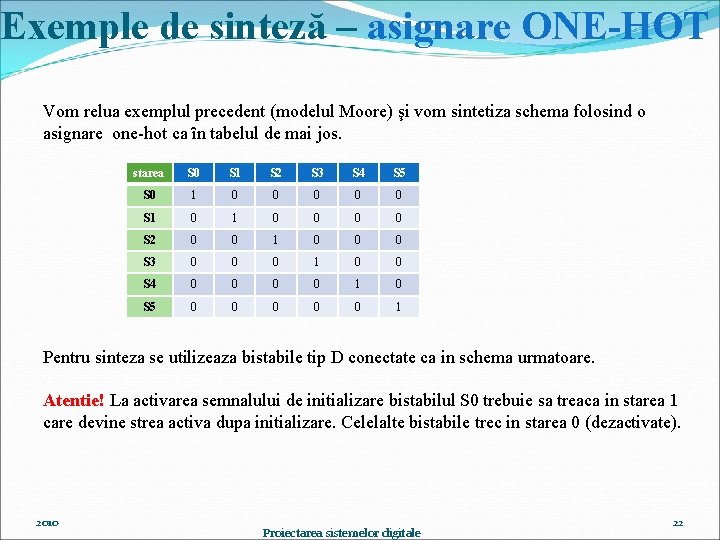

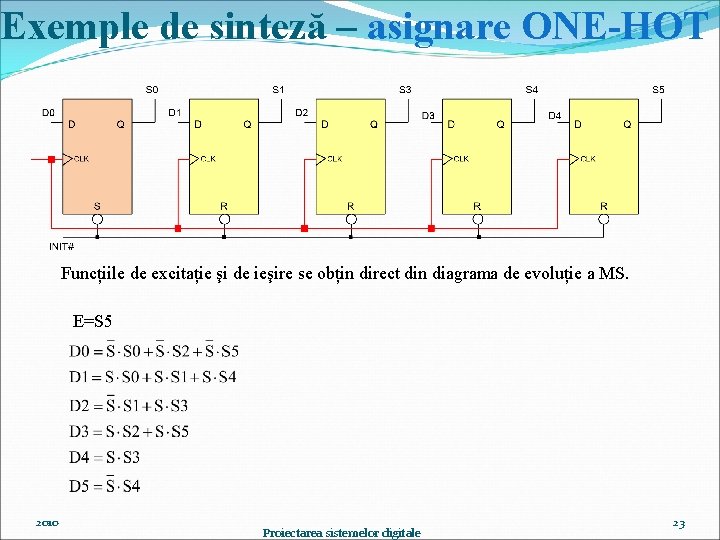

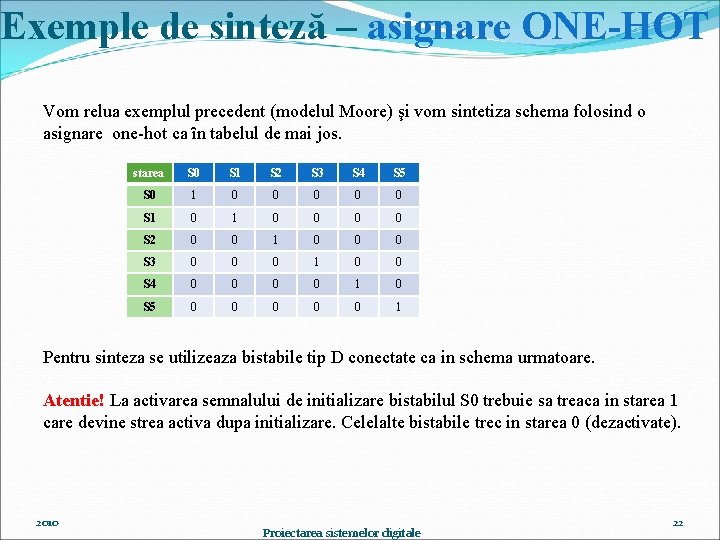

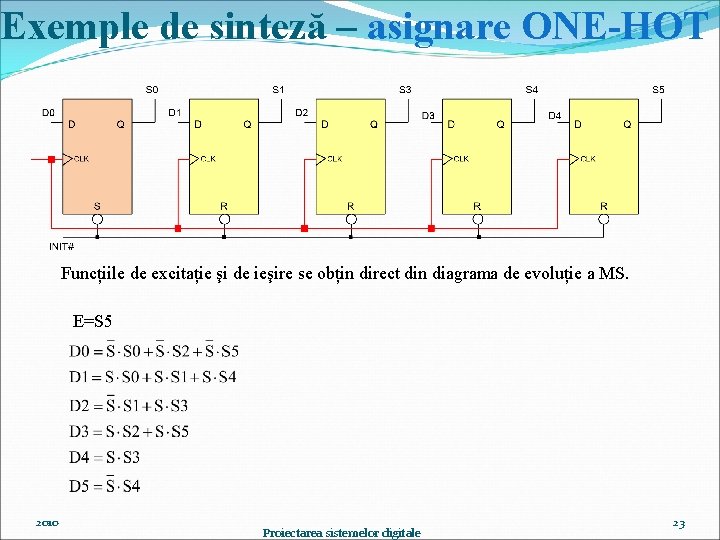

Exemple de sinteză – asignare ONE-HOT Vom relua exemplul precedent (modelul Moore) şi vom sintetiza schema folosind o asignare one-hot ca ȋn tabelul de mai jos. starea S 0 S 1 S 2 S 3 S 4 S 5 S 0 1 0 0 0 S 1 0 0 0 0 S 2 0 0 1 0 0 0 S 3 0 0 0 1 0 0 S 4 0 0 1 0 S 5 0 0 0 1 Pentru sinteza se utilizeaza bistabile tip D conectate ca in schema urmatoare. Atentie! La activarea semnalului de initializare bistabilul S 0 trebuie sa treaca in starea 1 care devine strea activa dupa initializare. Celelalte bistabile trec in starea 0 (dezactivate). 2010 Proiectarea sistemelor digitale 22

Exemple de sinteză – asignare ONE-HOT Funcțiile de excitație şi de ieşire se obțin direct din diagrama de evoluție a MS. E=S 5 2010 Proiectarea sistemelor digitale 23

Determinarea maşinii reduse minime 2010 Proiectarea sistemelor digitale 24

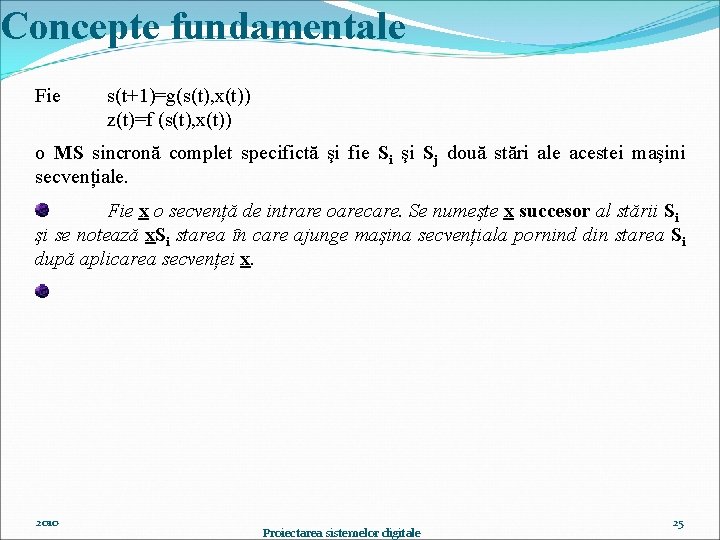

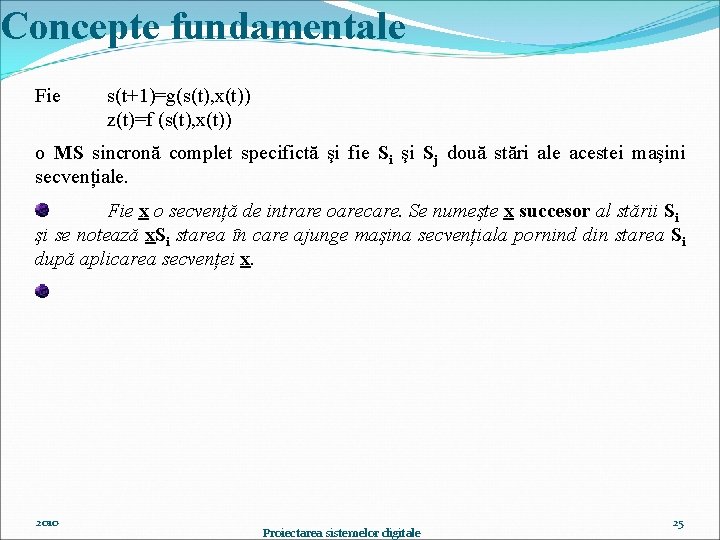

Concepte fundamentale Fie s(t+1)=g(s(t), x(t)) z(t)=f (s(t), x(t)) o MS sincronă complet specifictă şi fie Si şi Sj două stări ale acestei maşini secvențiale. Fie x o secvență de intrare oarecare. Se numeşte x succesor al stării Si şi se notează x. Si starea ȋn care ajunge maşina secvențiala pornind din starea Si după aplicarea secvenței x. 2010 Proiectarea sistemelor digitale 25

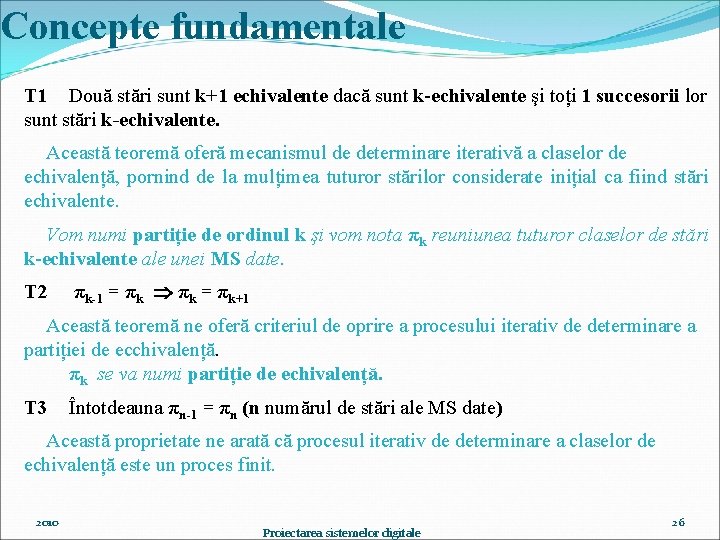

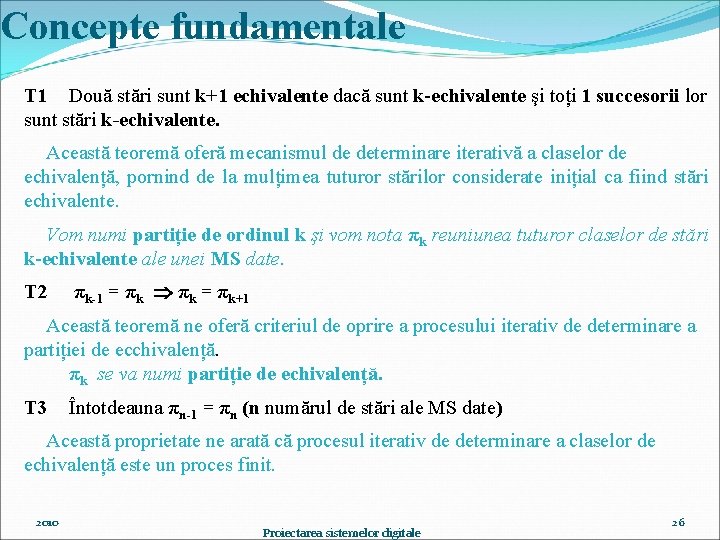

Concepte fundamentale T 1 Două stări sunt k+1 echivalente dacă sunt k-echivalente şi toți 1 succesorii lor sunt stări k-echivalente. Această teoremă oferă mecanismul de determinare iterativă a claselor de echivalență, pornind de la mulțimea tuturor stărilor considerate inițial ca fiind stări echivalente. Vom numi partiție de ordinul k şi vom nota πk reuniunea tuturor claselor de stări k-echivalente ale unei MS date. T 2 πk-1 = πk+1 Această teoremă ne oferă criteriul de oprire a procesului iterativ de determinare a partiției de ecchivalență. πk se va numi partiție de echivalență. T 3 Întotdeauna πn-1 = πn (n numărul de stări ale MS date) Această proprietate ne arată că procesul iterativ de determinare a claselor de echivalență este un proces finit. 2010 Proiectarea sistemelor digitale 26

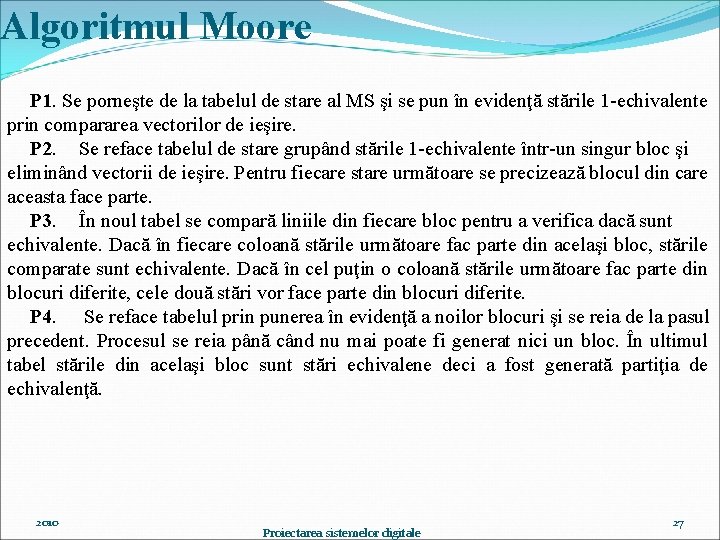

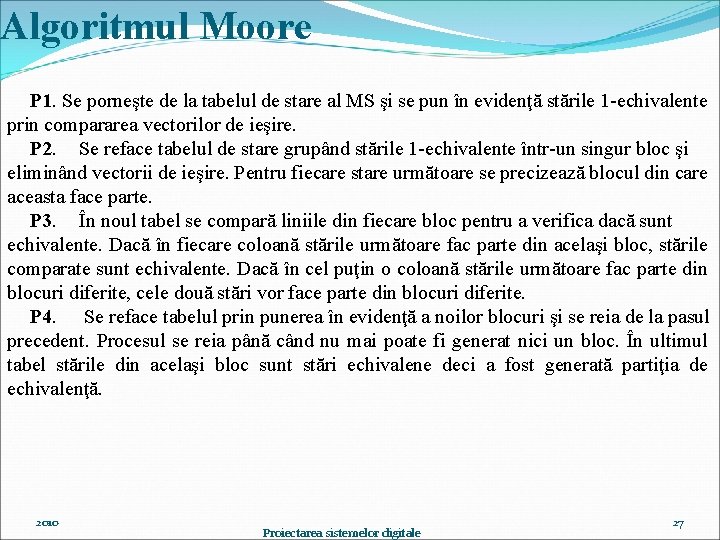

Algoritmul Moore P 1. Se porneşte de la tabelul de stare al MS şi se pun în evidenţă stările 1 -echivalente prin compararea vectorilor de ieşire. P 2. Se reface tabelul de stare grupând stările 1 -echivalente într-un singur bloc şi eliminând vectorii de ieşire. Pentru fiecare stare următoare se precizează blocul din care aceasta face parte. P 3. În noul tabel se compară liniile din fiecare bloc pentru a verifica dacă sunt echivalente. Dacă în fiecare coloană stările următoare fac parte din acelaşi bloc, stările comparate sunt echivalente. Dacă în cel puţin o coloană stările următoare fac parte din blocuri diferite, cele două stări vor face parte din blocuri diferite. P 4. Se reface tabelul prin punerea în evidenţă a noilor blocuri şi se reia de la pasul precedent. Procesul se reia până când nu mai poate fi generat nici un bloc. În ultimul tabel stările din acelaşi bloc sunt stări echivalene deci a fost generată partiţia de echivalenţă. 2010 Proiectarea sistemelor digitale 27

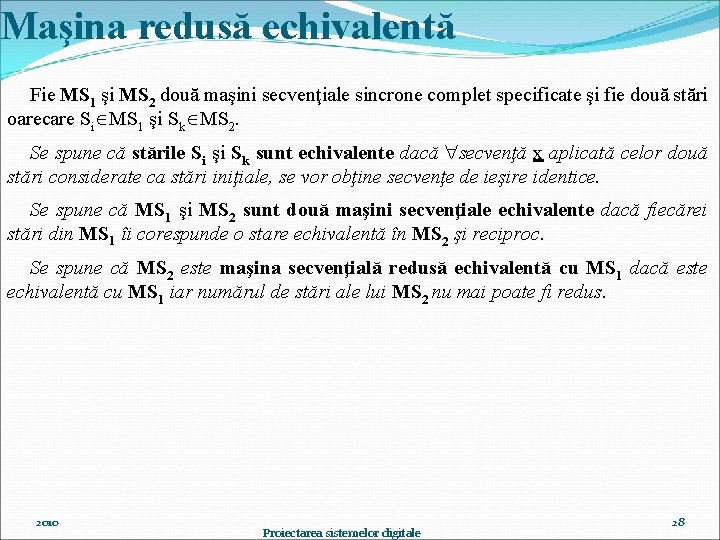

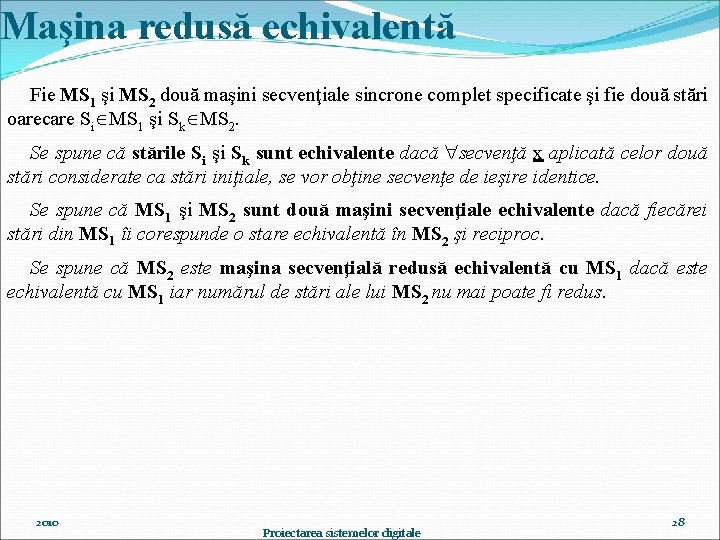

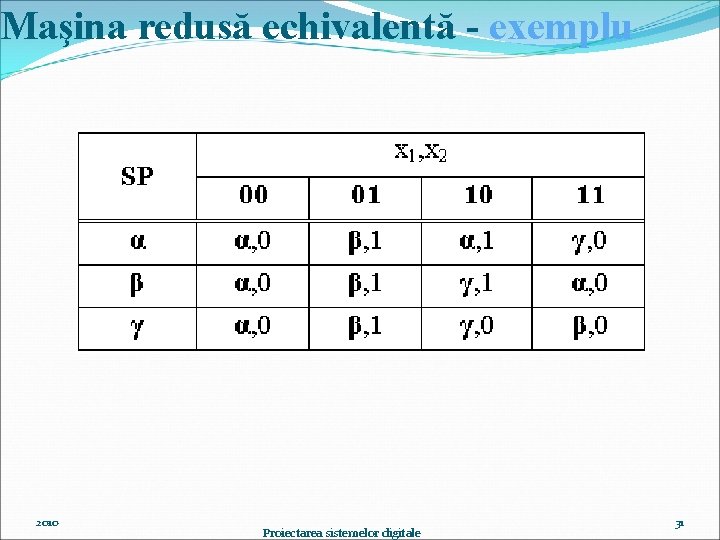

Maşina redusă echivalentă Fie MS 1 şi MS 2 două maşini secvenţiale sincrone complet specificate şi fie două stări oarecare Si MS 1 şi Sk MS 2. Se spune că stările Si şi Sk sunt echivalente dacă secvenţă x aplicată celor două stări considerate ca stări iniţiale, se vor obţine secvenţe de ieşire identice. Se spune că MS 1 şi MS 2 sunt două maşini secvenţiale echivalente dacă fiecărei stări din MS 1 îi corespunde o stare echivalentă în MS 2 şi reciproc. Se spune că MS 2 este maşina secvenţială redusă echivalentă cu MS 1 dacă este echivalentă cu MS 1 iar numărul de stări ale lui MS 2 nu mai poate fi redus. 2010 Proiectarea sistemelor digitale 28

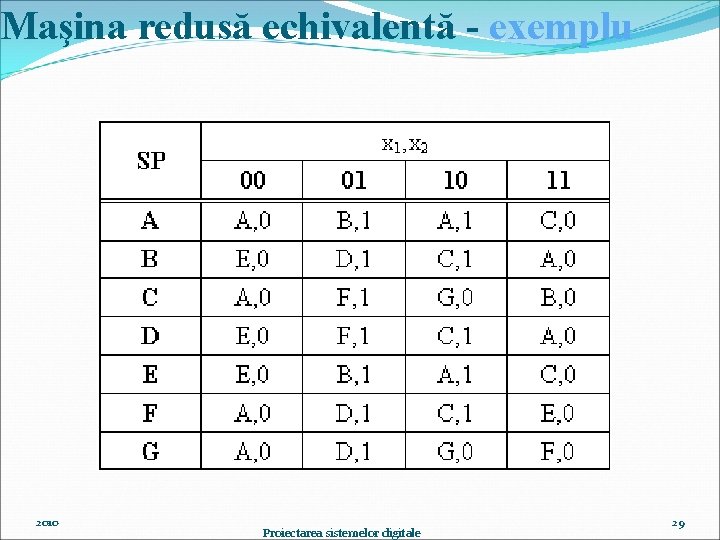

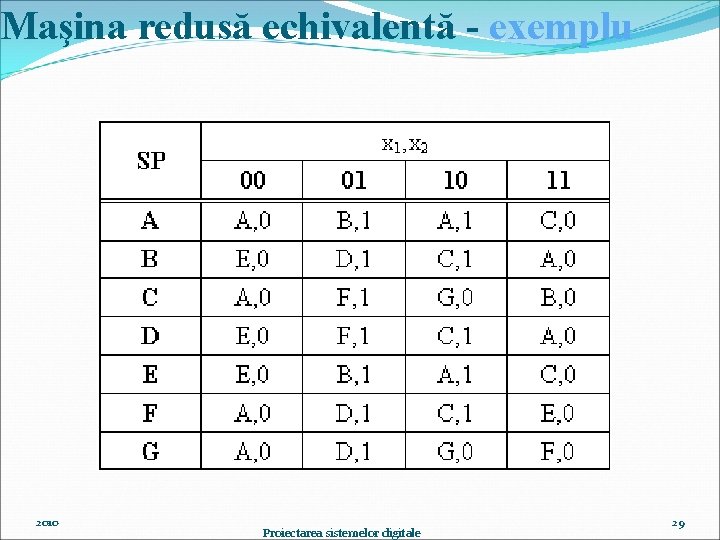

Maşina redusă echivalentă - exemplu 2010 Proiectarea sistemelor digitale 29

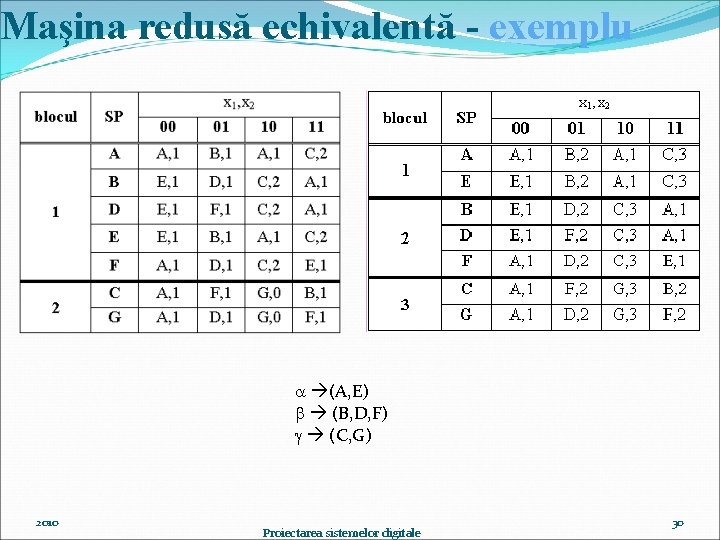

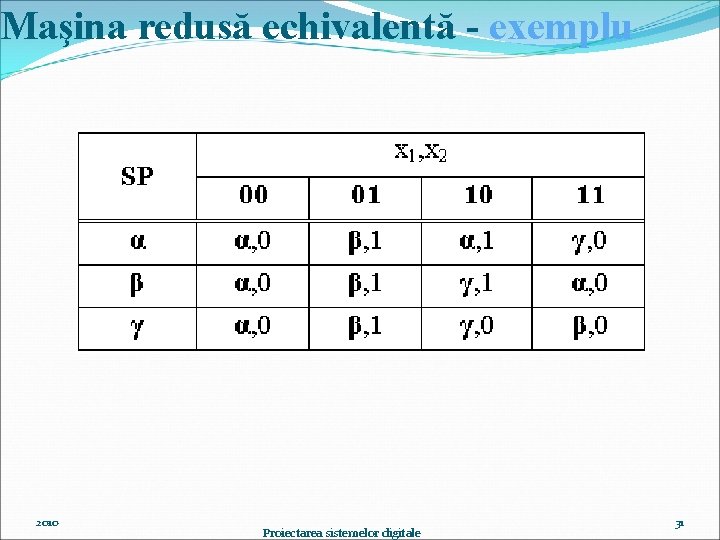

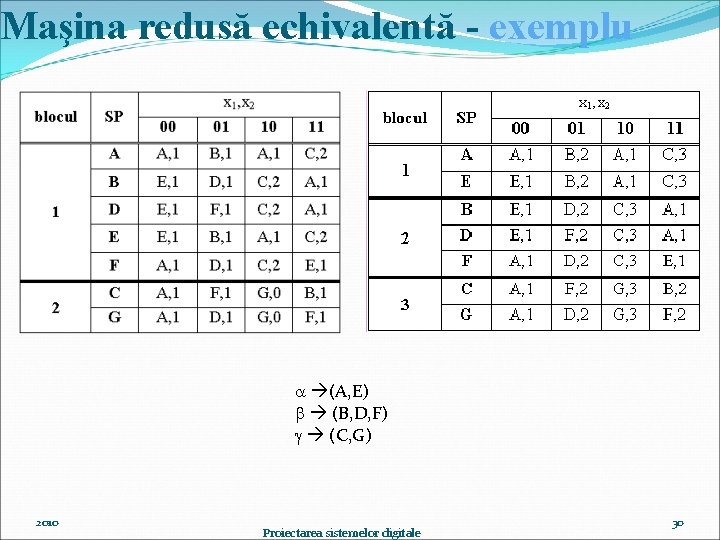

Maşina redusă echivalentă - exemplu (A, E) (B, D, F) (C, G) 2010 Proiectarea sistemelor digitale 30

Maşina redusă echivalentă - exemplu 2010 Proiectarea sistemelor digitale 31

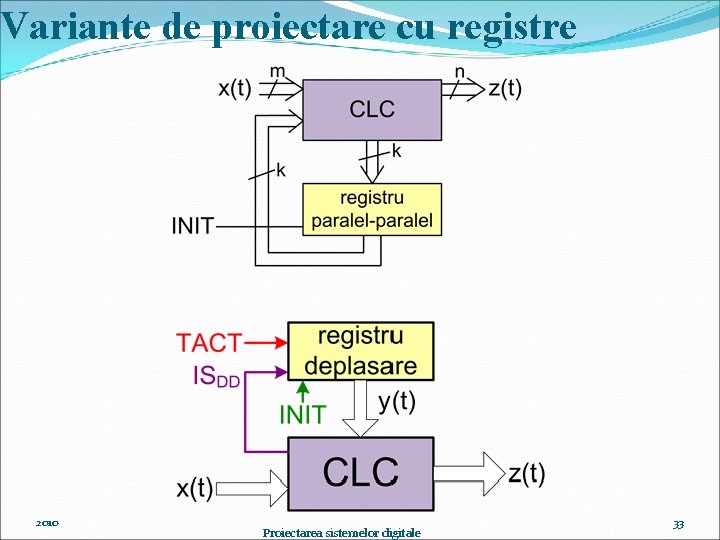

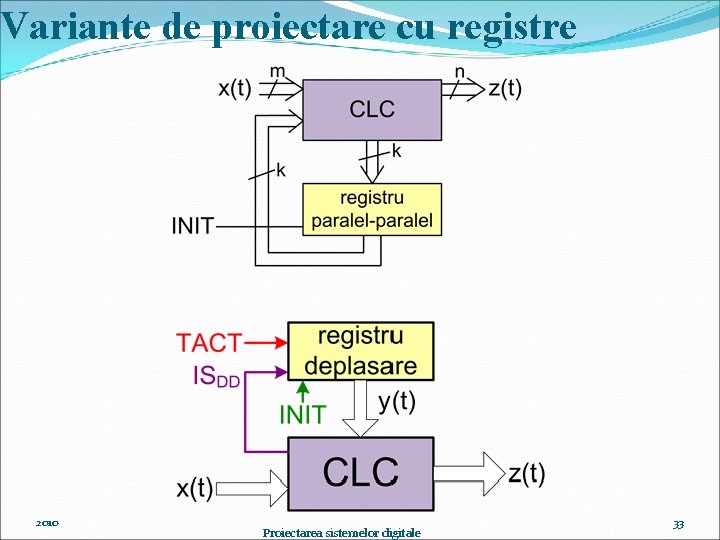

Proiectarea SLS cu registre 2010 Proiectarea sistemelor digitale 32

Variante de proiectare cu registre 2010 Proiectarea sistemelor digitale 33

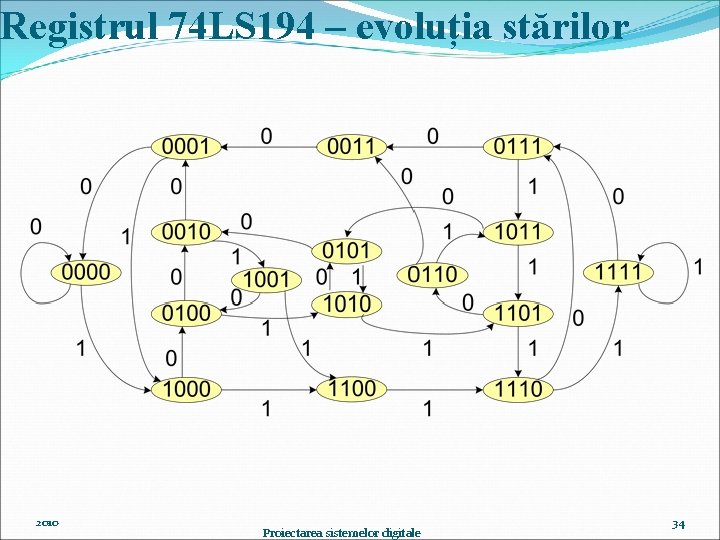

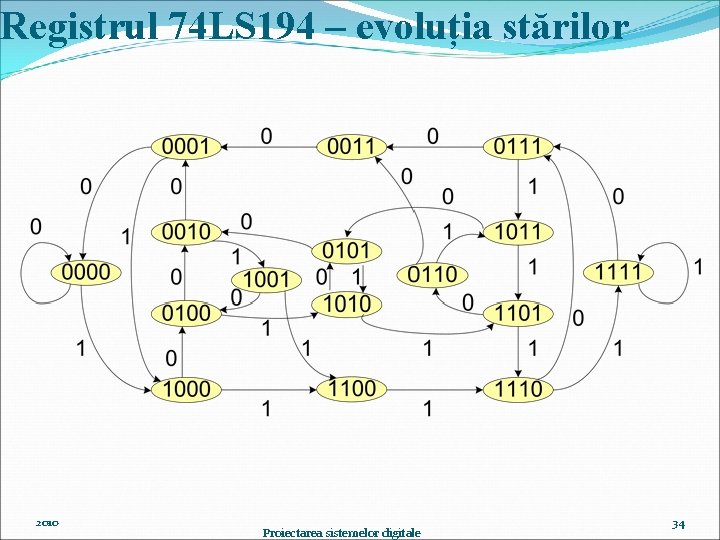

Registrul 74 LS 194 – evoluția stărilor 2010 Proiectarea sistemelor digitale 34

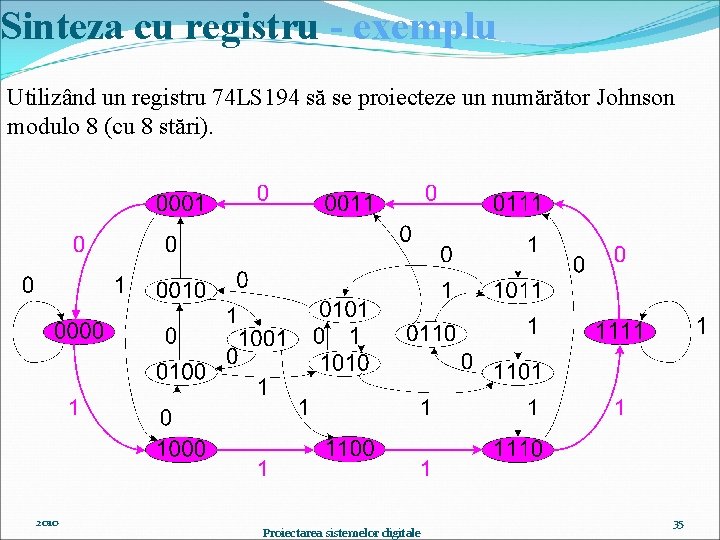

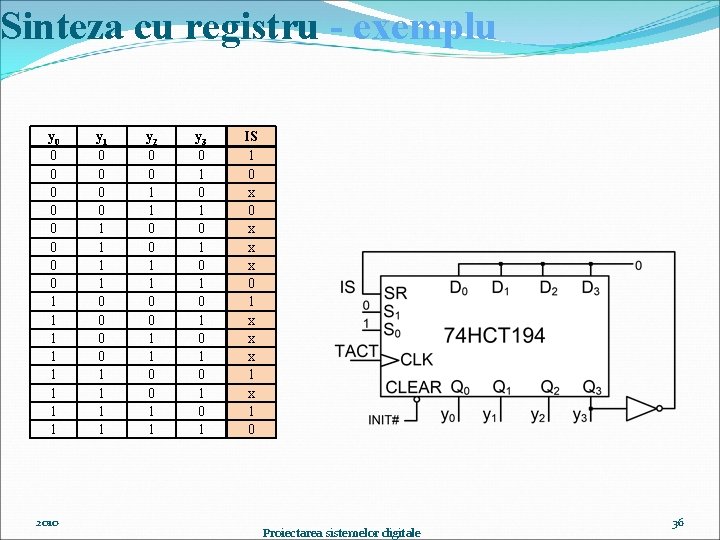

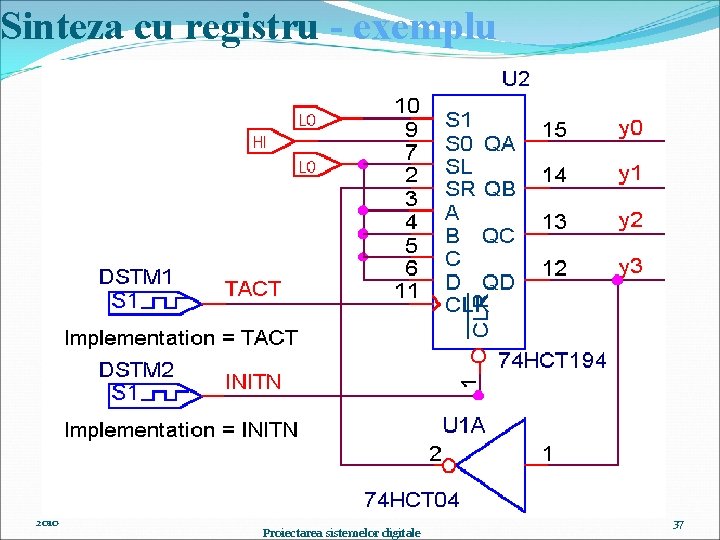

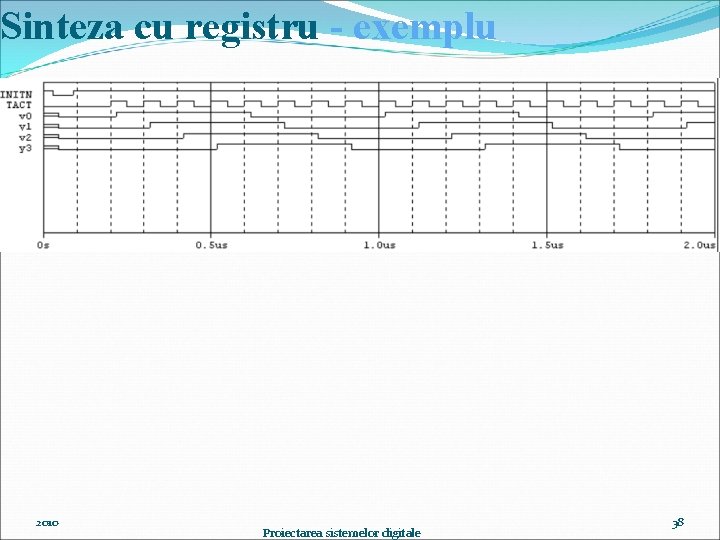

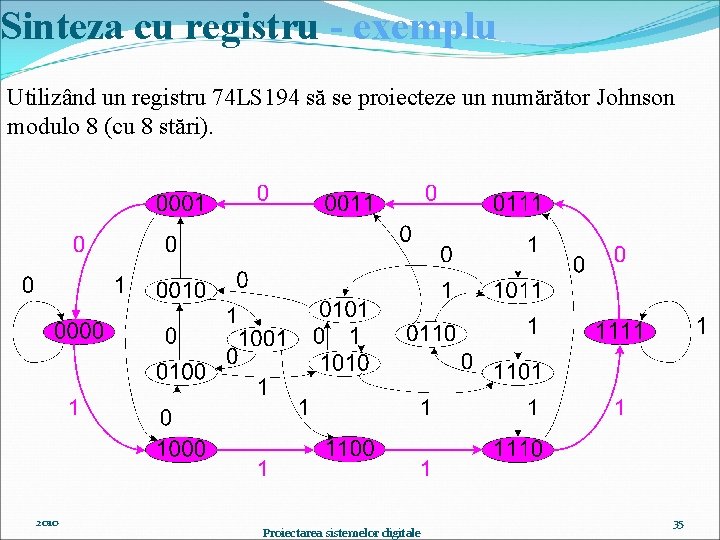

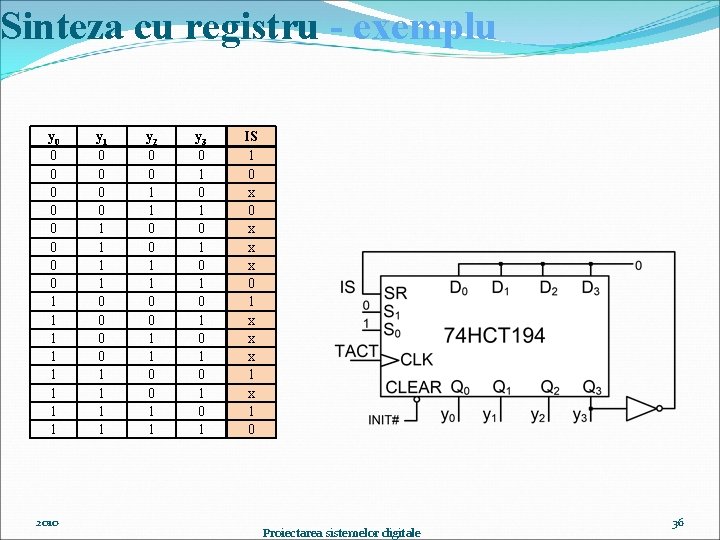

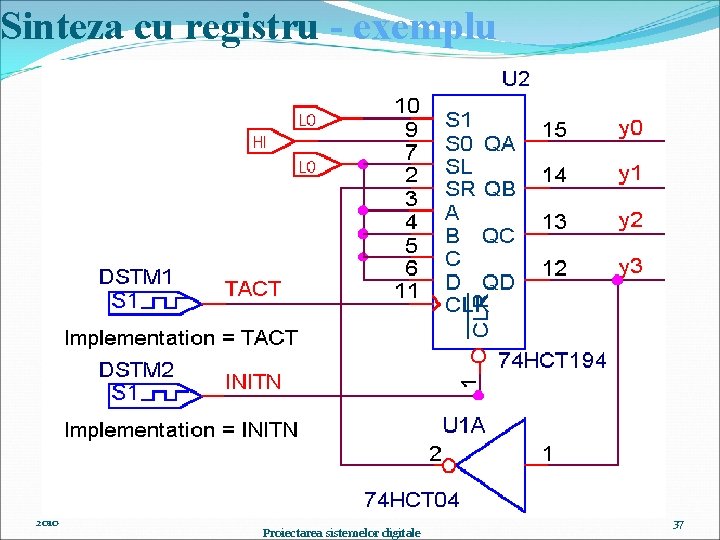

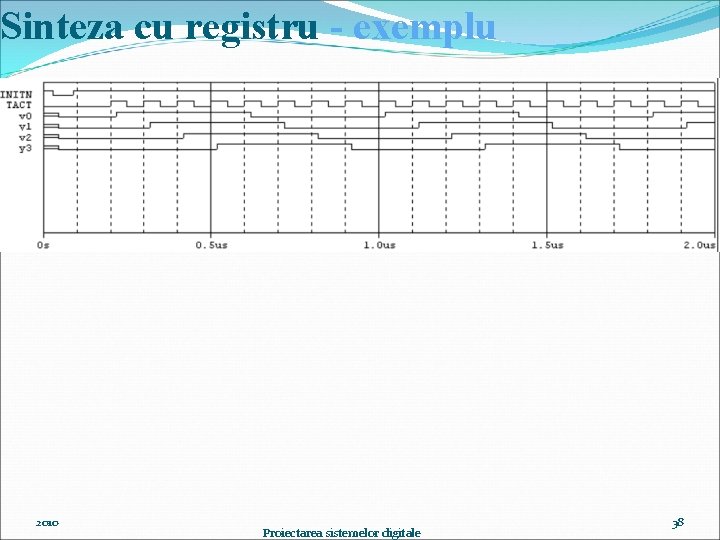

Sinteza cu registru - exemplu Utilizând un registru 74 LS 194 să se proiecteze un numărător Johnson modulo 8 (cu 8 stări). 2010 Proiectarea sistemelor digitale 35

Sinteza cu registru - exemplu y 0 0 0 0 0 1 1 1 1 2010 y 1 0 0 0 0 1 1 1 1 y 2 0 0 1 1 y 3 0 1 0 1 IS 1 0 x x x 0 1 x x x 1 0 Proiectarea sistemelor digitale 36

Sinteza cu registru - exemplu 2010 Proiectarea sistemelor digitale 37

Sinteza cu registru - exemplu 2010 Proiectarea sistemelor digitale 38

Intrebări ? 2010 Proiectarea sistemelor digitale 39