Proiectarea Microsistemelor Digitale Curs 4 1 Proiectarea Microsistemelor

- Slides: 37

Proiectarea Microsistemelor Digitale Curs 4 1

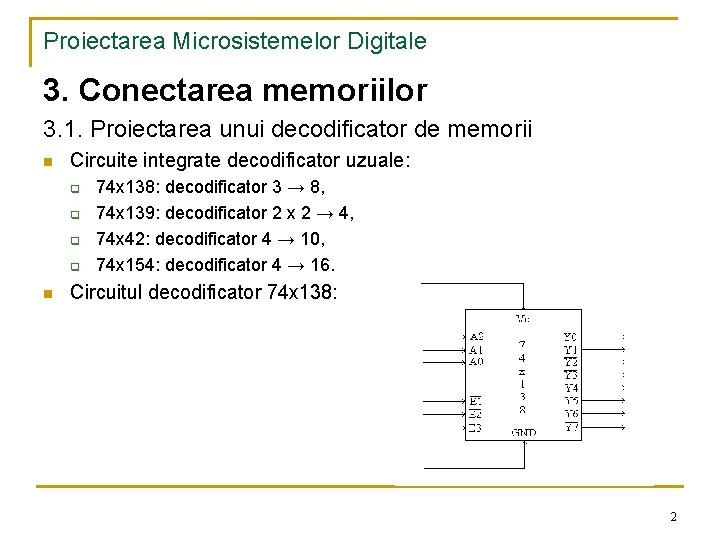

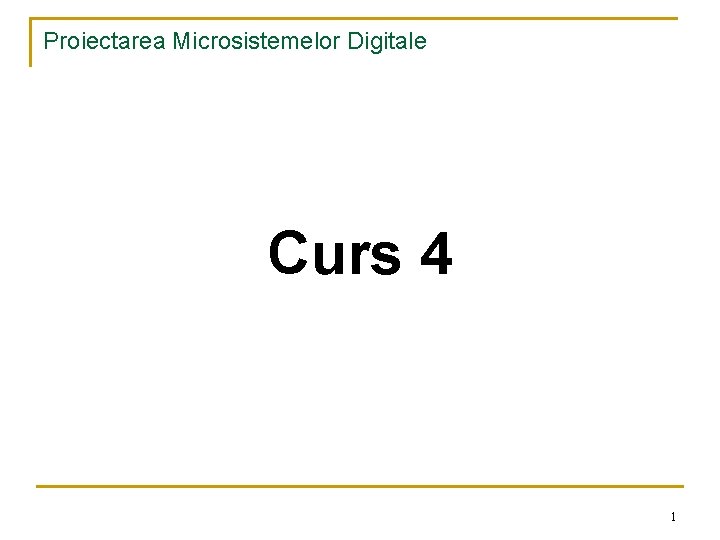

Proiectarea Microsistemelor Digitale 3. Conectarea memoriilor 3. 1. Proiectarea unui decodificator de memorii n Circuite integrate decodificator uzuale: q q n 74 x 138: decodificator 3 → 8, 74 x 139: decodificator 2 x 2 → 4, 74 x 42: decodificator 4 → 10, 74 x 154: decodificator 4 → 16. Circuitul decodificator 74 x 138: 2

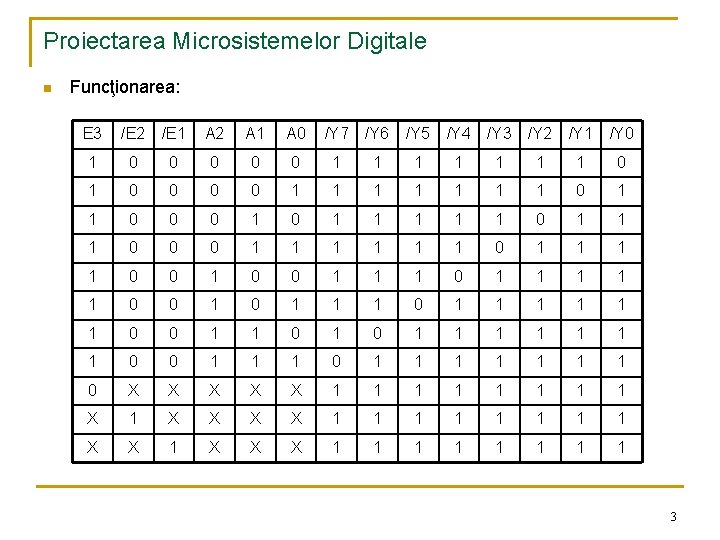

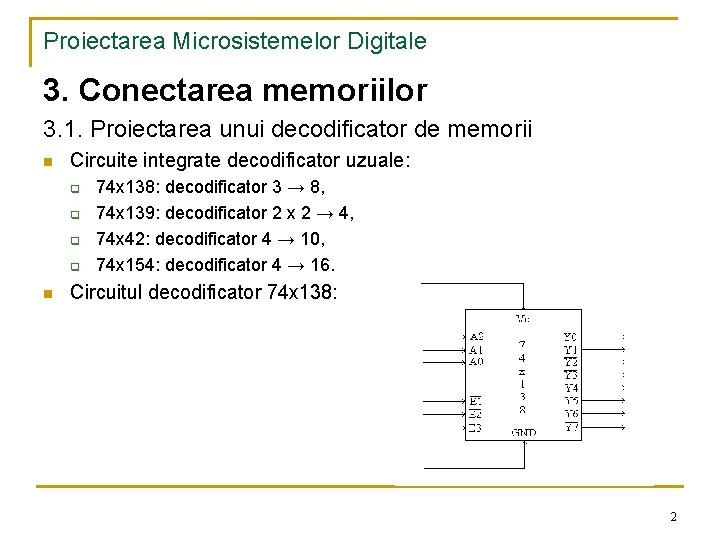

Proiectarea Microsistemelor Digitale n Funcţionarea: E 3 /E 2 /E 1 A 2 A 1 A 0 /Y 7 /Y 6 /Y 5 /Y 4 /Y 3 /Y 2 /Y 1 /Y 0 1 0 0 0 1 1 1 1 0 1 1 0 0 0 1 1 1 0 1 1 0 0 1 1 1 0 1 1 1 0 0 1 1 1 1 0 0 1 1 1 1 1 0 X X X 1 1 1 1 X 1 X X 1 1 1 1 X X X 1 1 1 1 3

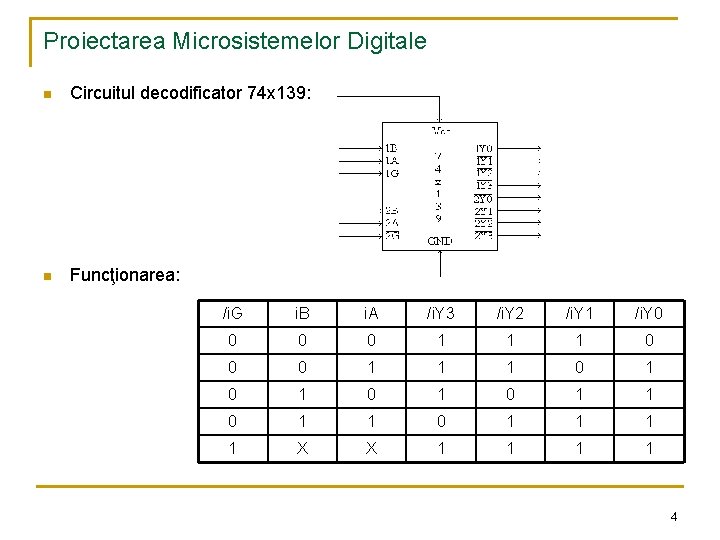

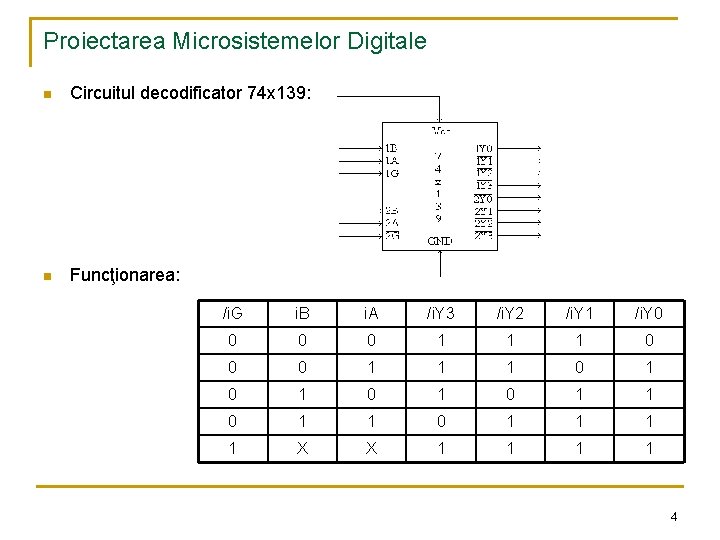

Proiectarea Microsistemelor Digitale n Circuitul decodificator 74 x 139: n Funcţionarea: /i. G i. B i. A /i. Y 3 /i. Y 2 /i. Y 1 /i. Y 0 0 1 1 1 0 1 0 1 1 X X 1 1 4

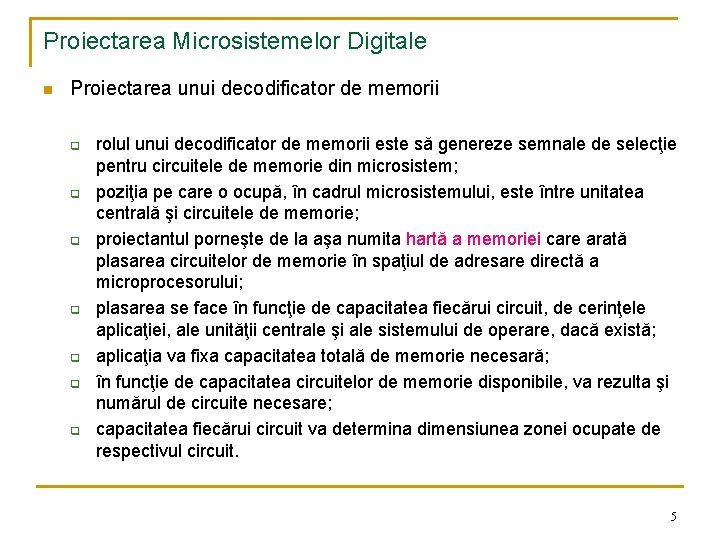

Proiectarea Microsistemelor Digitale n Proiectarea unui decodificator de memorii q q q q rolul unui decodificator de memorii este să genereze semnale de selecţie pentru circuitele de memorie din microsistem; poziţia pe care o ocupă, în cadrul microsistemului, este între unitatea centrală şi circuitele de memorie; proiectantul porneşte de la aşa numita hartă a memoriei care arată plasarea circuitelor de memorie în spaţiul de adresare directă a microprocesorului; plasarea se face în funcţie de capacitatea fiecărui circuit, de cerinţele aplicaţiei, ale unităţii centrale şi ale sistemului de operare, dacă există; aplicaţia va fixa capacitatea totală de memorie necesară; în funcţie de capacitatea circuitelor de memorie disponibile, va rezulta şi numărul de circuite necesare; capacitatea fiecărui circuit va determina dimensiunea zonei ocupate de respectivul circuit. 5

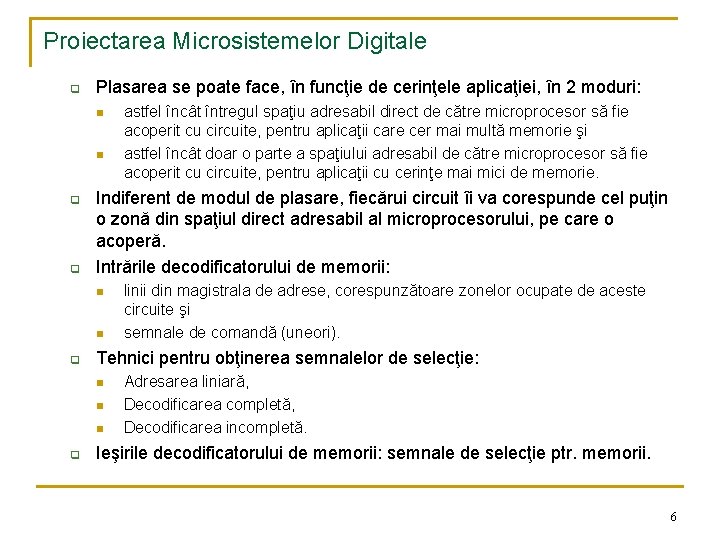

Proiectarea Microsistemelor Digitale q Plasarea se poate face, în funcţie de cerinţele aplicaţiei, în 2 moduri: n n q q Indiferent de modul de plasare, fiecărui circuit îi va corespunde cel puţin o zonă din spaţiul direct adresabil al microprocesorului, pe care o acoperă. Intrările decodificatorului de memorii: n n q linii din magistrala de adrese, corespunzătoare zonelor ocupate de aceste circuite şi semnale de comandă (uneori). Tehnici pentru obţinerea semnalelor de selecţie: n n n q astfel încât întregul spaţiu adresabil direct de către microprocesor să fie acoperit cu circuite, pentru aplicaţii care cer mai multă memorie şi astfel încât doar o parte a spaţiului adresabil de către microprocesor să fie acoperit cu circuite, pentru aplicaţii cu cerinţe mai mici de memorie. Adresarea liniară, Decodificarea completă, Decodificarea incompletă. Ieşirile decodificatorului de memorii: semnale de selecţie ptr. memorii. 6

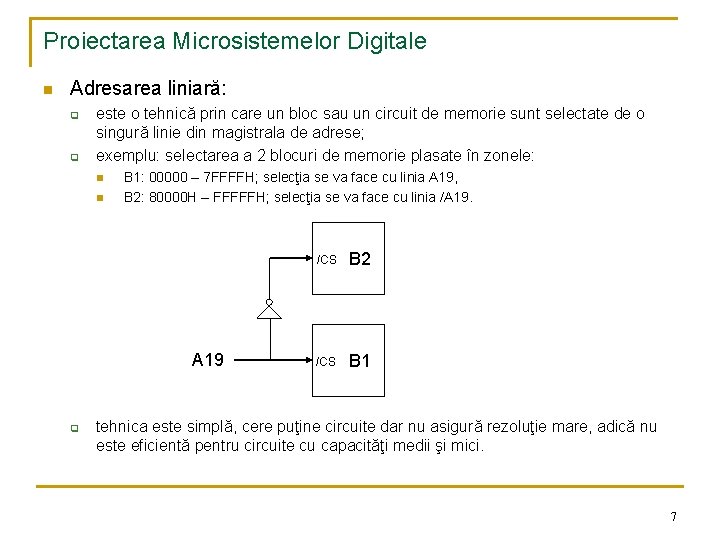

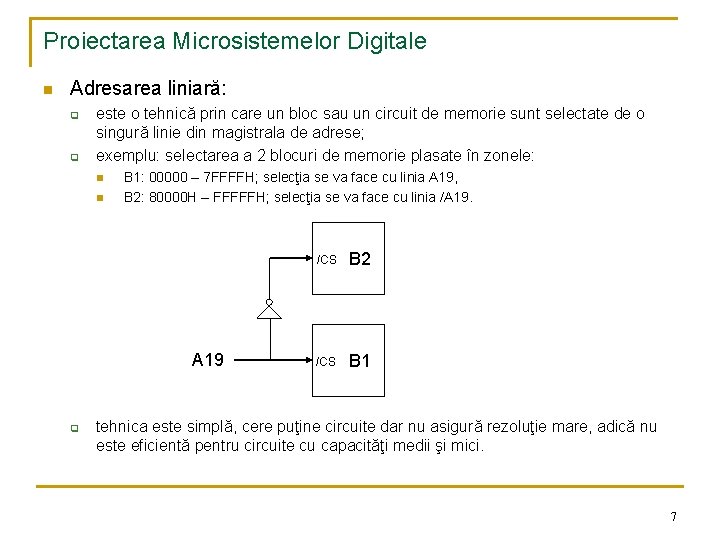

Proiectarea Microsistemelor Digitale n Adresarea liniară: q q este o tehnică prin care un bloc sau un circuit de memorie sunt selectate de o singură linie din magistrala de adrese; exemplu: selectarea a 2 blocuri de memorie plasate în zonele: n n B 1: 00000 – 7 FFFFH; selecţia se va face cu linia A 19, B 2: 80000 H – FFFFFH; selecţia se va face cu linia /A 19. A 19 q /CS B 2 /CS B 1 tehnica este simplă, cere puţine circuite dar nu asigură rezoluţie mare, adică nu este eficientă pentru circuite cu capacităţi medii şi mici. 7

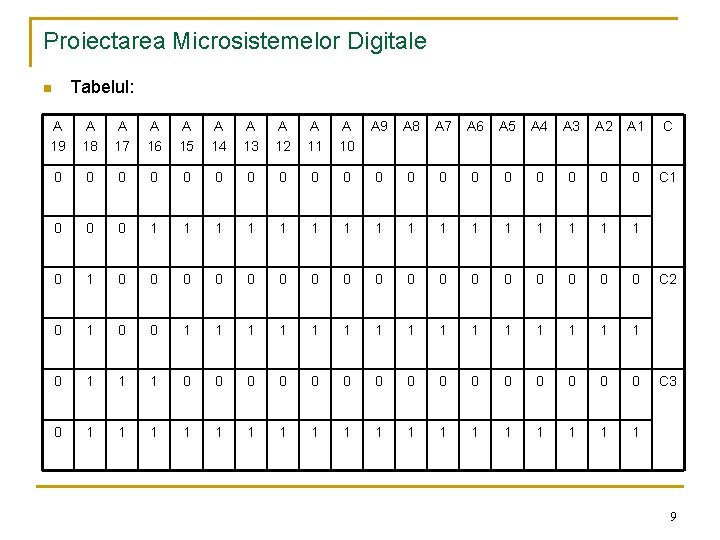

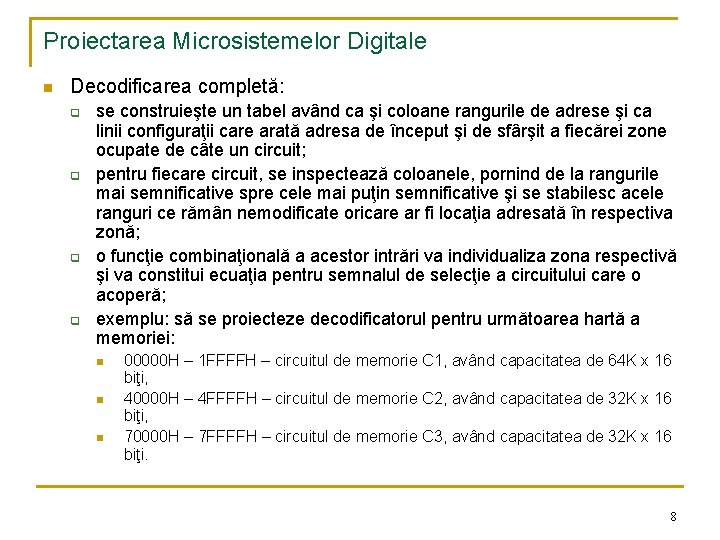

Proiectarea Microsistemelor Digitale n Decodificarea completă: q q se construieşte un tabel având ca şi coloane rangurile de adrese şi ca linii configuraţii care arată adresa de început şi de sfârşit a fiecărei zone ocupate de câte un circuit; pentru fiecare circuit, se inspectează coloanele, pornind de la rangurile mai semnificative spre cele mai puţin semnificative şi se stabilesc acele ranguri ce rămân nemodificate oricare ar fi locaţia adresată în respectiva zonă; o funcţie combinaţională a acestor intrări va individualiza zona respectivă şi va constitui ecuaţia pentru semnalul de selecţie a circuitului care o acoperă; exemplu: să se proiecteze decodificatorul pentru următoarea hartă a memoriei: n n n 00000 H – 1 FFFFH – circuitul de memorie C 1, având capacitatea de 64 K x 16 biţi, 40000 H – 4 FFFFH – circuitul de memorie C 2, având capacitatea de 32 K x 16 biţi, 70000 H – 7 FFFFH – circuitul de memorie C 3, având capacitatea de 32 K x 16 biţi. 8

Proiectarea Microsistemelor Digitale Tabelul: n A 19 A 18 A 17 A 16 A 15 A 14 A 13 A 12 A 11 A 10 A 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 C 0 0 0 0 0 C 1 0 0 0 1 1 1 1 0 1 0 0 0 0 0 1 0 0 1 1 1 1 0 1 1 1 0 0 0 0 1 1 1 1 1 C 2 C 3 9

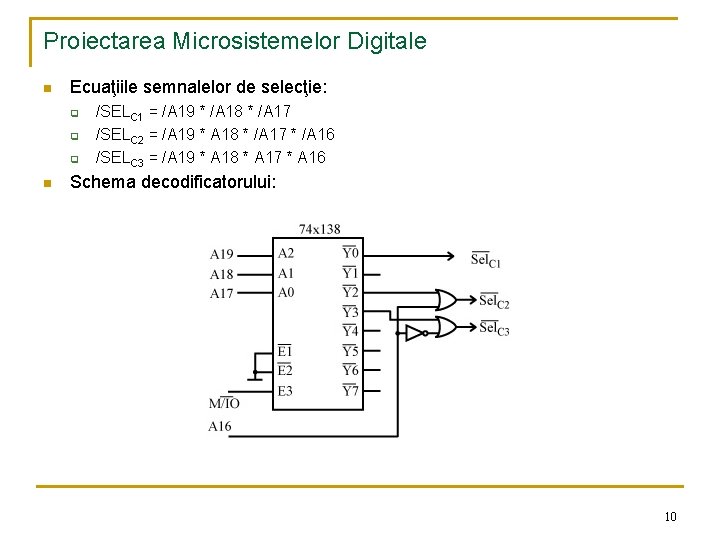

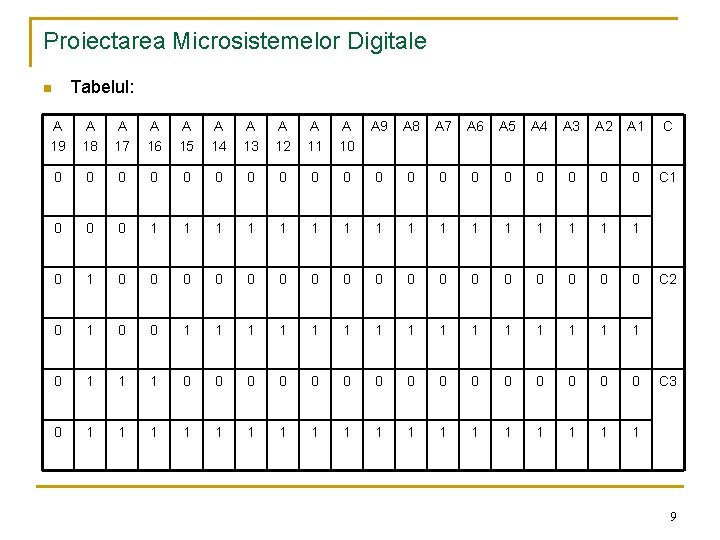

Proiectarea Microsistemelor Digitale n Ecuaţiile semnalelor de selecţie: q q q n /SELC 1 = /A 19 * /A 18 * /A 17 /SELC 2 = /A 19 * A 18 * /A 17 * /A 16 /SELC 3 = /A 19 * A 18 * A 17 * A 16 Schema decodificatorului: 10

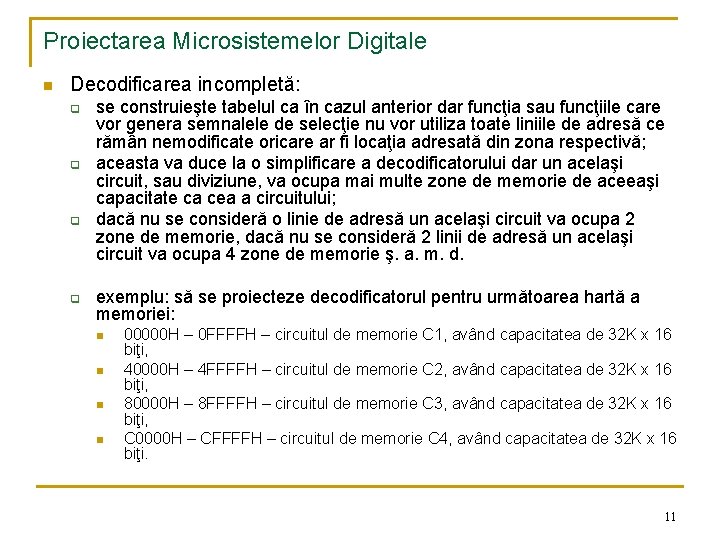

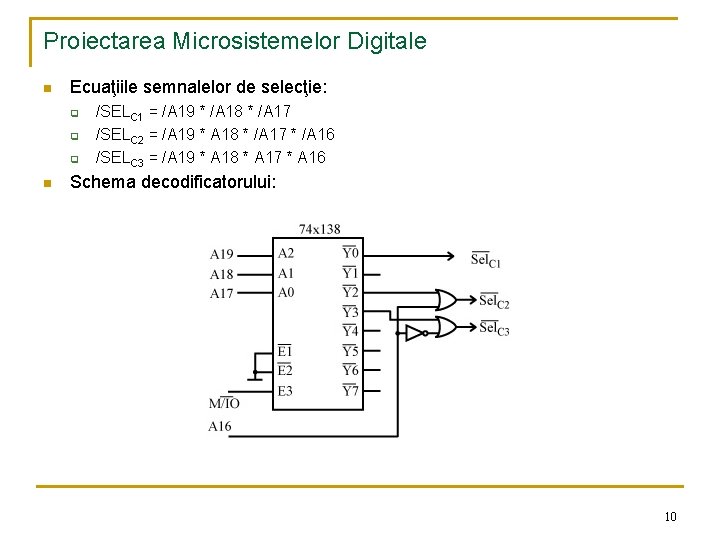

Proiectarea Microsistemelor Digitale n Decodificarea incompletă: q q se construieşte tabelul ca în cazul anterior dar funcţia sau funcţiile care vor genera semnalele de selecţie nu vor utiliza toate liniile de adresă ce rămân nemodificate oricare ar fi locaţia adresată din zona respectivă; aceasta va duce la o simplificare a decodificatorului dar un acelaşi circuit, sau diviziune, va ocupa mai multe zone de memorie de aceeaşi capacitate ca cea a circuitului; dacă nu se consideră o linie de adresă un acelaşi circuit va ocupa 2 zone de memorie, dacă nu se consideră 2 linii de adresă un acelaşi circuit va ocupa 4 zone de memorie ş. a. m. d. exemplu: să se proiecteze decodificatorul pentru următoarea hartă a memoriei: n n 00000 H – 0 FFFFH – circuitul de memorie C 1, având capacitatea de 32 K x 16 biţi, 40000 H – 4 FFFFH – circuitul de memorie C 2, având capacitatea de 32 K x 16 biţi, 80000 H – 8 FFFFH – circuitul de memorie C 3, având capacitatea de 32 K x 16 biţi, C 0000 H – CFFFFH – circuitul de memorie C 4, având capacitatea de 32 K x 16 biţi. 11

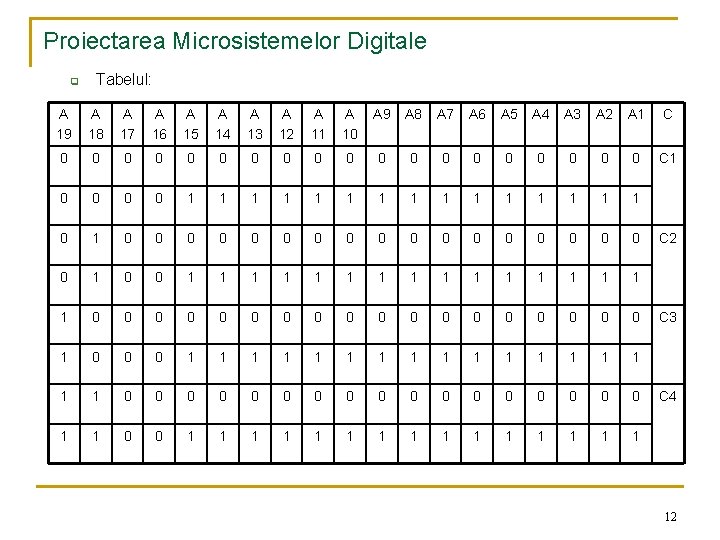

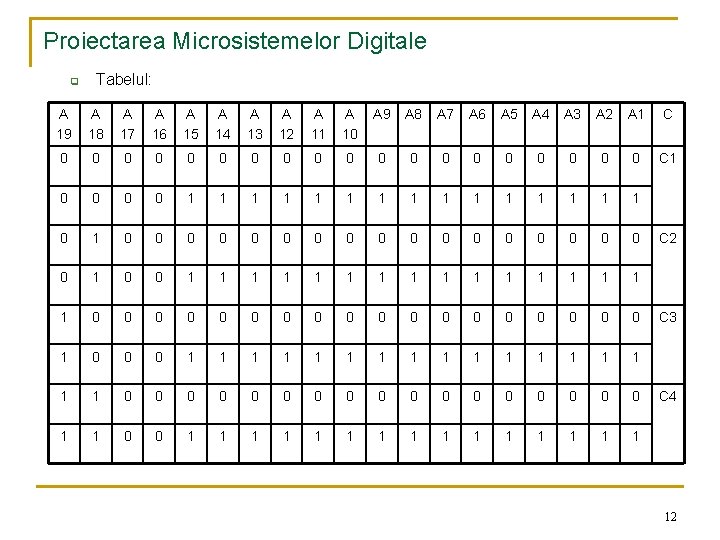

Proiectarea Microsistemelor Digitale q Tabelul: A 19 A 18 A 17 A 16 A 15 A 14 A 13 A 12 A 11 A 10 A 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 C 0 0 0 0 0 C 1 0 0 1 1 1 1 0 0 0 0 0 1 0 0 1 1 1 1 0 0 0 0 0 1 0 0 0 1 1 1 1 1 0 0 0 0 0 1 1 0 0 1 1 1 1 C 2 C 3 C 4 12

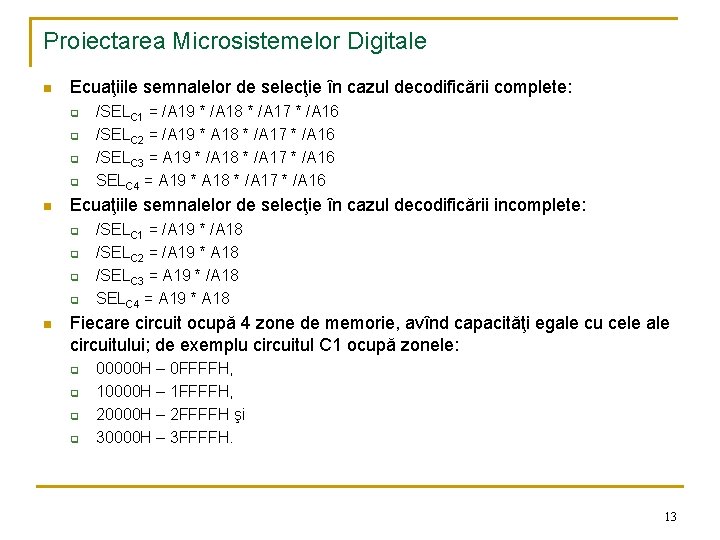

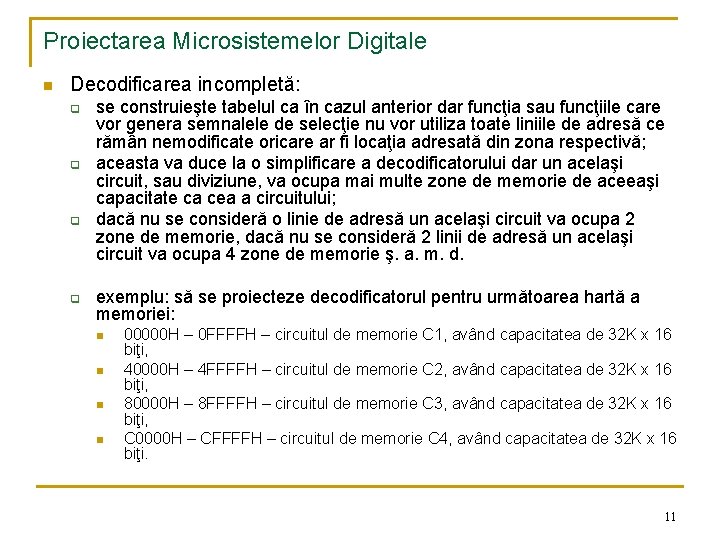

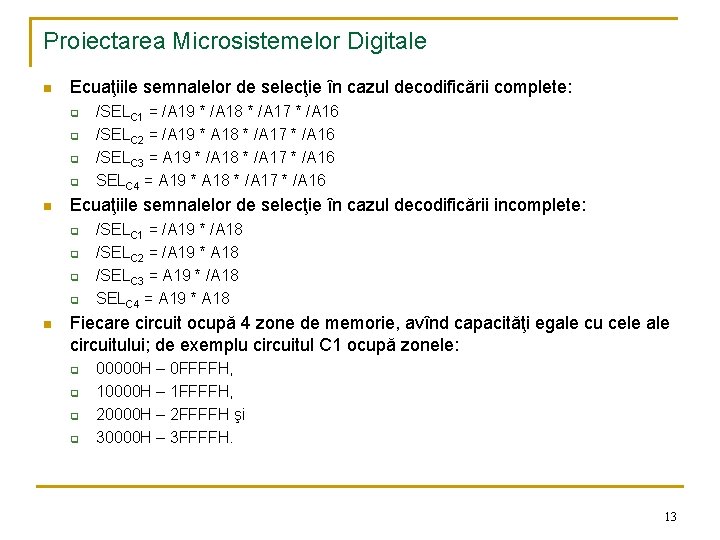

Proiectarea Microsistemelor Digitale n Ecuaţiile semnalelor de selecţie în cazul decodificării complete: q q n Ecuaţiile semnalelor de selecţie în cazul decodificării incomplete: q q n /SELC 1 = /A 19 * /A 18 * /A 17 * /A 16 /SELC 2 = /A 19 * A 18 * /A 17 * /A 16 /SELC 3 = A 19 * /A 18 * /A 17 * /A 16 SELC 4 = A 19 * A 18 * /A 17 * /A 16 /SELC 1 = /A 19 * /A 18 /SELC 2 = /A 19 * A 18 /SELC 3 = A 19 * /A 18 SELC 4 = A 19 * A 18 Fiecare circuit ocupă 4 zone de memorie, avînd capacităţi egale cu cele ale circuitului; de exemplu circuitul C 1 ocupă zonele: q q 00000 H – 0 FFFFH, 10000 H – 1 FFFFH, 20000 H – 2 FFFFH şi 30000 H – 3 FFFFH. 13

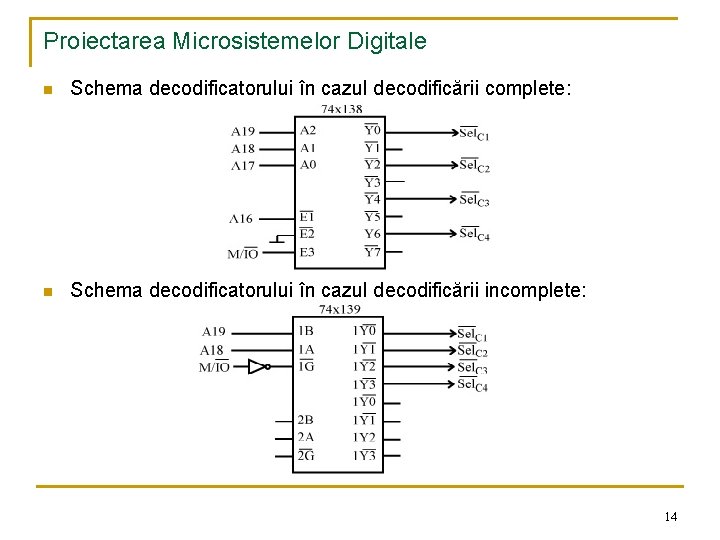

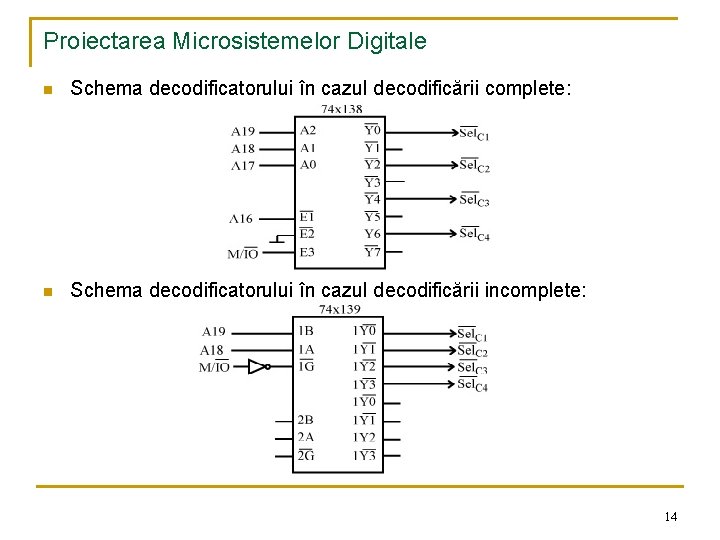

Proiectarea Microsistemelor Digitale n Schema decodificatorului în cazul decodificării complete: n Schema decodificatorului în cazul decodificării incomplete: 14

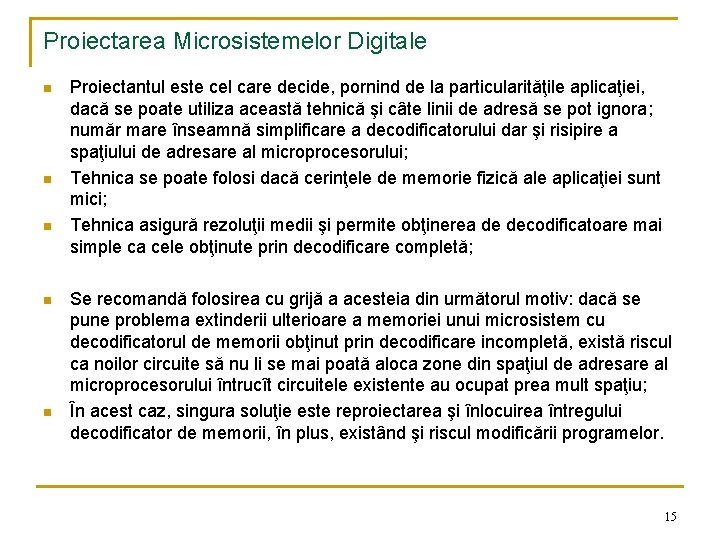

Proiectarea Microsistemelor Digitale n n n Proiectantul este cel care decide, pornind de la particularităţile aplicaţiei, dacă se poate utiliza această tehnică şi câte linii de adresă se pot ignora; număr mare înseamnă simplificare a decodificatorului dar şi risipire a spaţiului de adresare al microprocesorului; Tehnica se poate folosi dacă cerinţele de memorie fizică ale aplicaţiei sunt mici; Tehnica asigură rezoluţii medii şi permite obţinerea de decodificatoare mai simple ca cele obţinute prin decodificare completă; Se recomandă folosirea cu grijă a acesteia din următorul motiv: dacă se pune problema extinderii ulterioare a memoriei unui microsistem cu decodificatorul de memorii obţinut prin decodificare incompletă, există riscul ca noilor circuite să nu li se mai poată aloca zone din spaţiul de adresare al microprocesorului întrucît circuitele existente au ocupat prea mult spaţiu; În acest caz, singura soluţie este reproiectarea şi înlocuirea întregului decodificator de memorii, în plus, existând şi riscul modificării programelor. 15

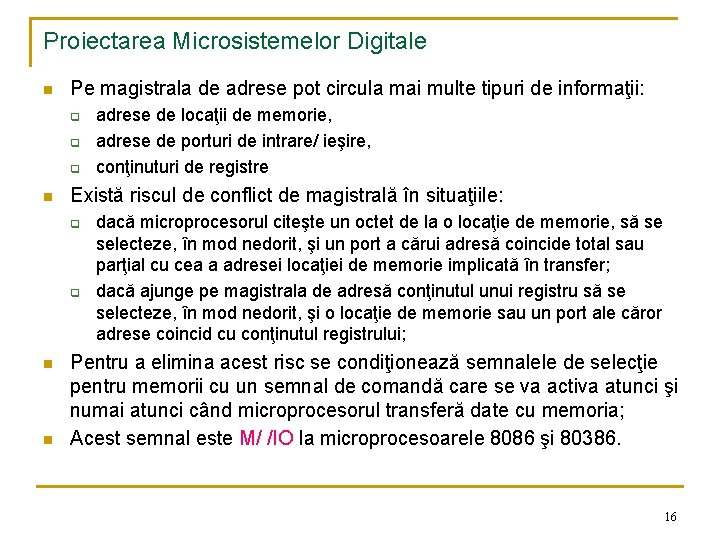

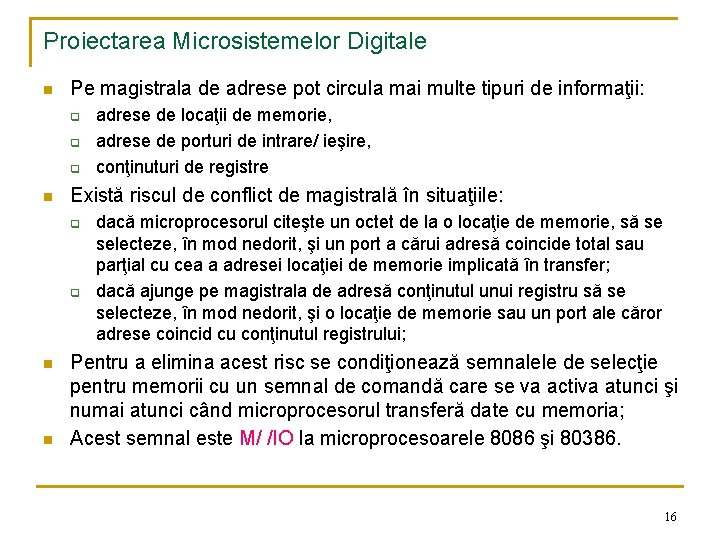

Proiectarea Microsistemelor Digitale n Pe magistrala de adrese pot circula mai multe tipuri de informaţii: q q q n Există riscul de conflict de magistrală în situaţiile: q q n n adrese de locaţii de memorie, adrese de porturi de intrare/ ieşire, conţinuturi de registre dacă microprocesorul citeşte un octet de la o locaţie de memorie, să se selecteze, în mod nedorit, şi un port a cărui adresă coincide total sau parţial cu cea a adresei locaţiei de memorie implicată în transfer; dacă ajunge pe magistrala de adresă conţinutul unui registru să se selecteze, în mod nedorit, şi o locaţie de memorie sau un port ale căror adrese coincid cu conţinutul registrului; Pentru a elimina acest risc se condiţionează semnalele de selecţie pentru memorii cu un semnal de comandă care se va activa atunci şi numai atunci când microprocesorul transferă date cu memoria; Acest semnal este M/ /IO la microprocesoarele 8086 şi 80386. 16

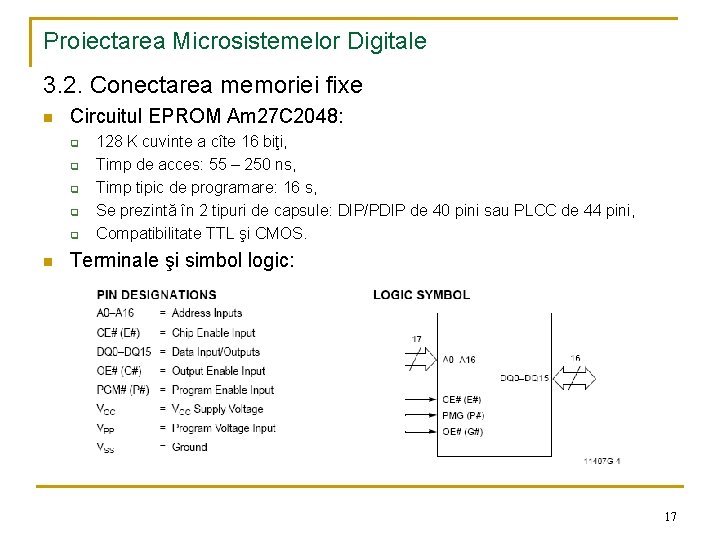

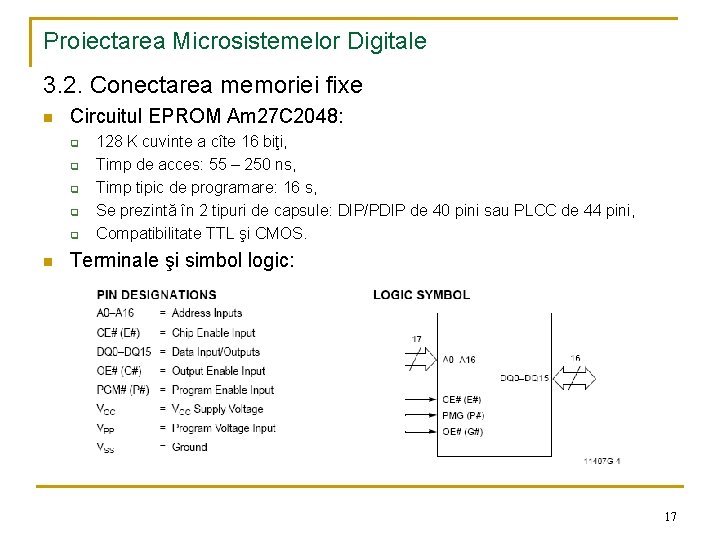

Proiectarea Microsistemelor Digitale 3. 2. Conectarea memoriei fixe n Circuitul EPROM Am 27 C 2048: q q q n 128 K cuvinte a cîte 16 biţi, Timp de acces: 55 – 250 ns, Timp tipic de programare: 16 s, Se prezintă în 2 tipuri de capsule: DIP/PDIP de 40 pini sau PLCC de 44 pini, Compatibilitate TTL şi CMOS. Terminale şi simbol logic: 17

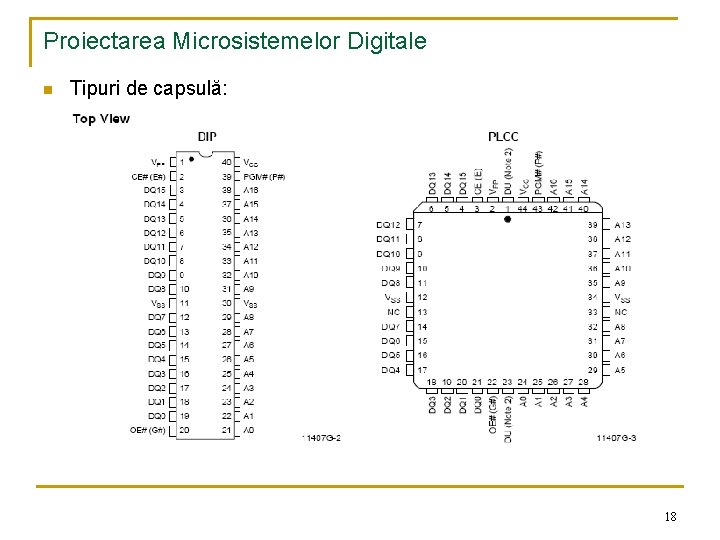

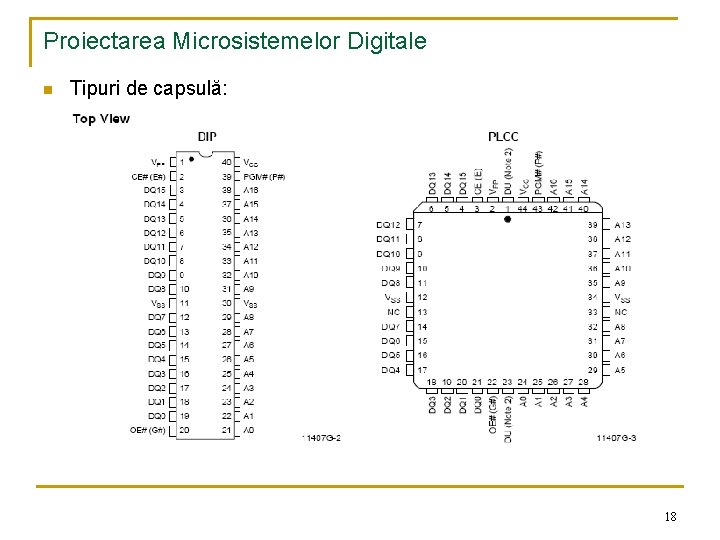

Proiectarea Microsistemelor Digitale n Tipuri de capsulă: 18

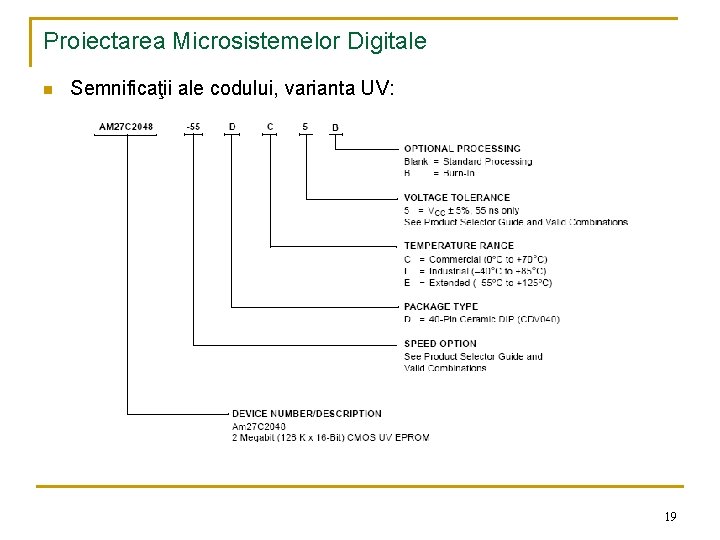

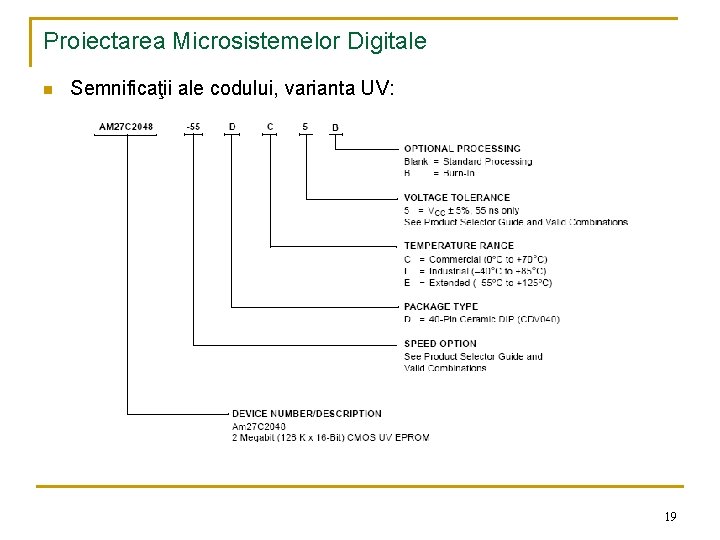

Proiectarea Microsistemelor Digitale n Semnificaţii ale codului, varianta UV: 19

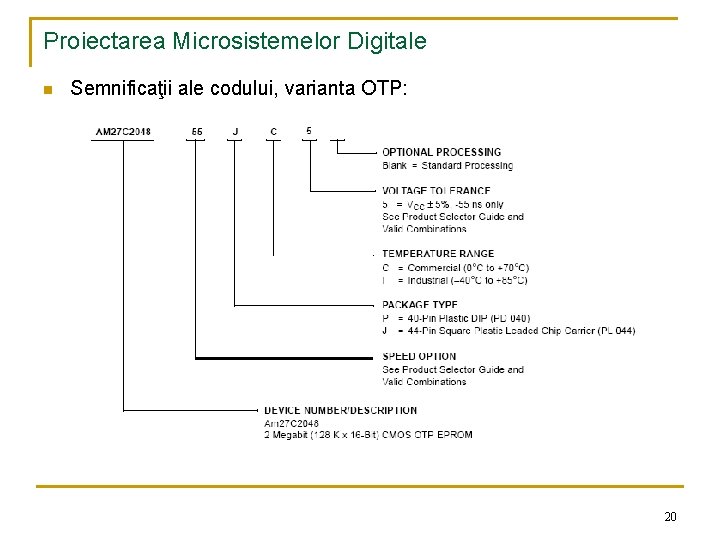

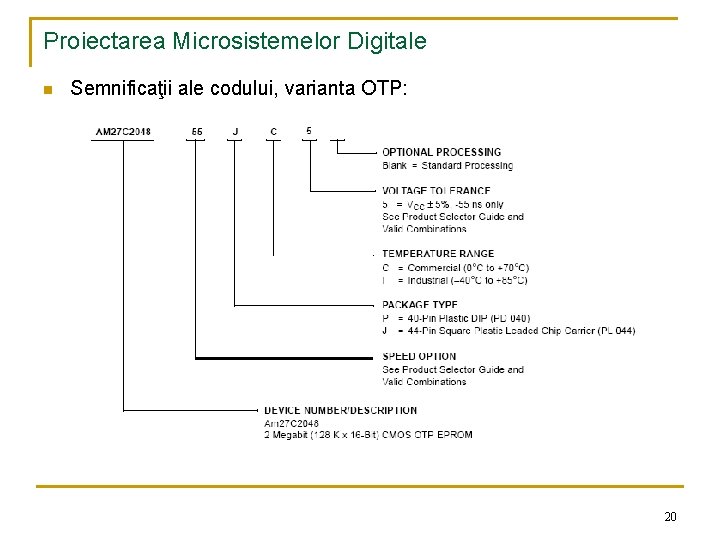

Proiectarea Microsistemelor Digitale n Semnificaţii ale codului, varianta OTP: 20

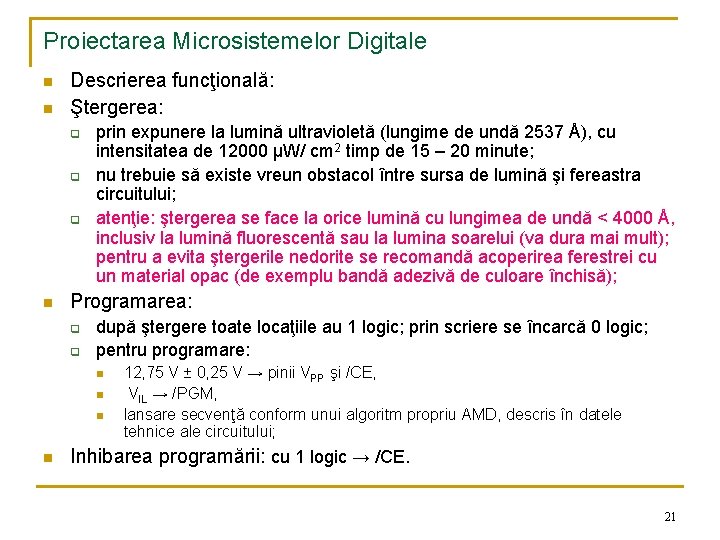

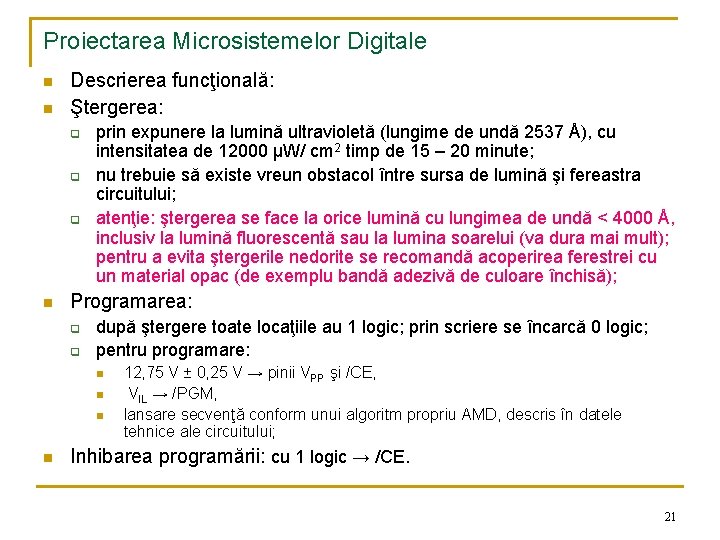

Proiectarea Microsistemelor Digitale n n Descrierea funcţională: Ştergerea: q q q n prin expunere la lumină ultravioletă (lungime de undă 2537 Å), cu intensitatea de 12000 µW/ cm 2 timp de 15 – 20 minute; nu trebuie să existe vreun obstacol între sursa de lumină şi fereastra circuitului; atenţie: ştergerea se face la orice lumină cu lungimea de undă < 4000 Å, inclusiv la lumină fluorescentă sau la lumina soarelui (va dura mai mult); pentru a evita ştergerile nedorite se recomandă acoperirea ferestrei cu un material opac (de exemplu bandă adezivă de culoare închisă); Programarea: q q după ştergere toate locaţiile au 1 logic; prin scriere se încarcă 0 logic; pentru programare: n n 12, 75 V ± 0, 25 V → pinii VPP şi /CE, VIL → /PGM, lansare secvenţă conform unui algoritm propriu AMD, descris în datele tehnice ale circuitului; Inhibarea programării: cu 1 logic → /CE. 21

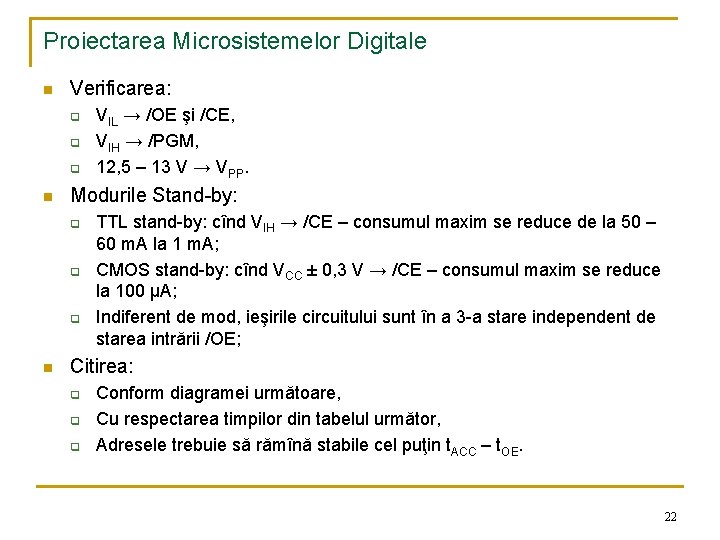

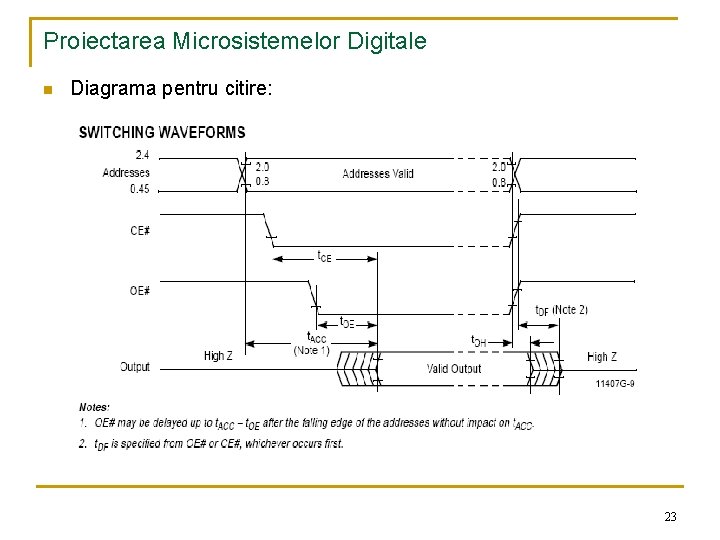

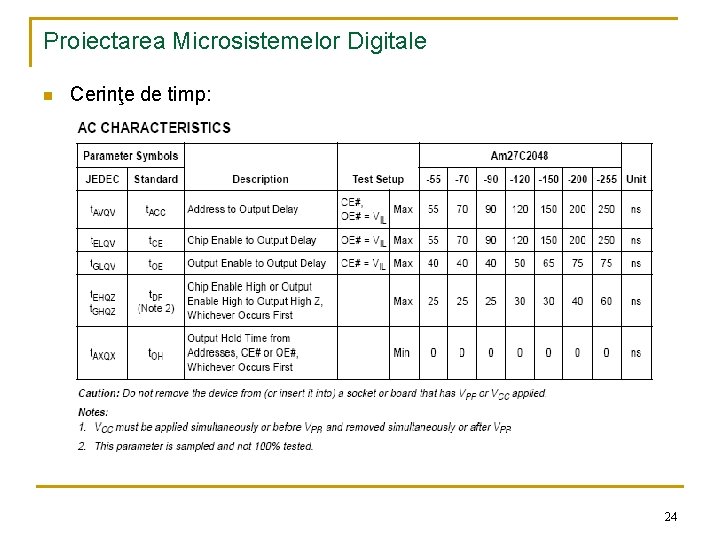

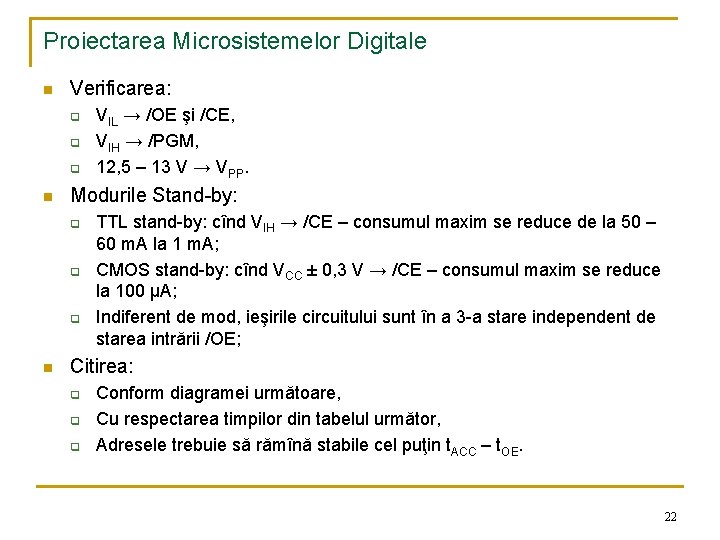

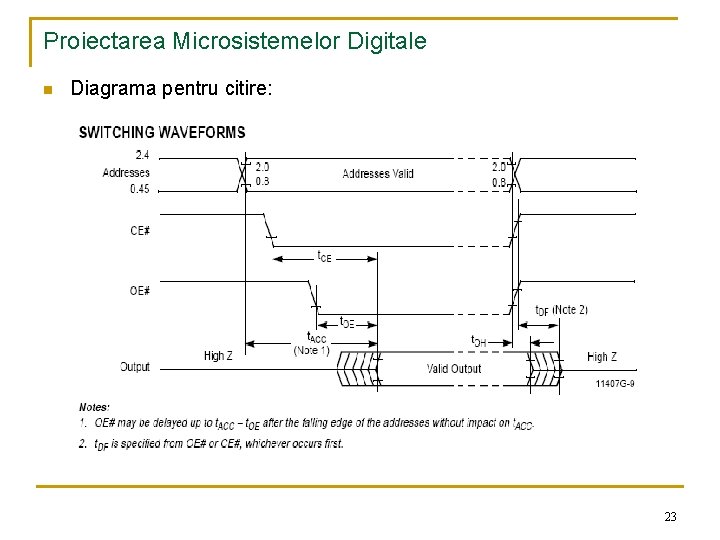

Proiectarea Microsistemelor Digitale n Verificarea: q q q n Modurile Stand-by: q q q n VIL → /OE şi /CE, VIH → /PGM, 12, 5 – 13 V → VPP. TTL stand-by: cînd VIH → /CE – consumul maxim se reduce de la 50 – 60 m. A la 1 m. A; CMOS stand-by: cînd VCC ± 0, 3 V → /CE – consumul maxim se reduce la 100 µA; Indiferent de mod, ieşirile circuitului sunt în a 3 -a stare independent de starea intrării /OE; Citirea: q q q Conform diagramei următoare, Cu respectarea timpilor din tabelul următor, Adresele trebuie să rămînă stabile cel puţin t. ACC – t. OE. 22

Proiectarea Microsistemelor Digitale n Diagrama pentru citire: 23

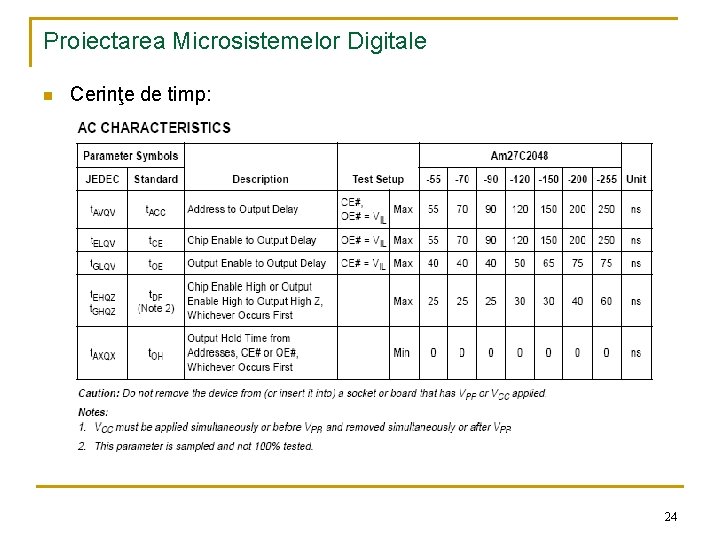

Proiectarea Microsistemelor Digitale n Cerinţe de timp: 24

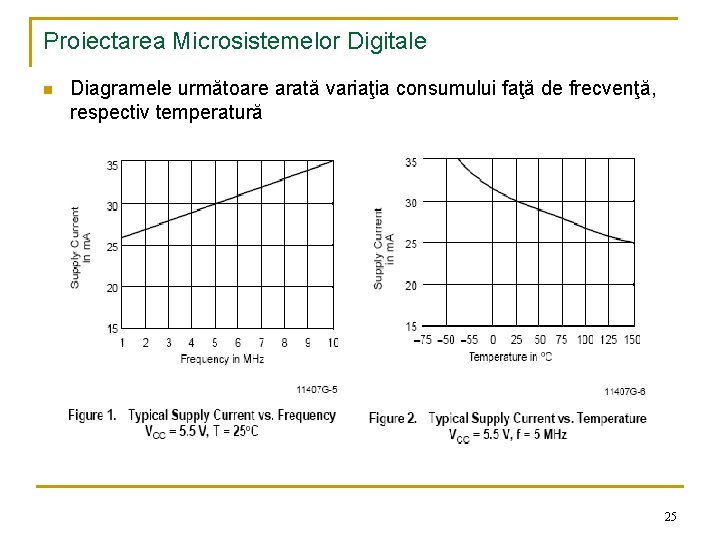

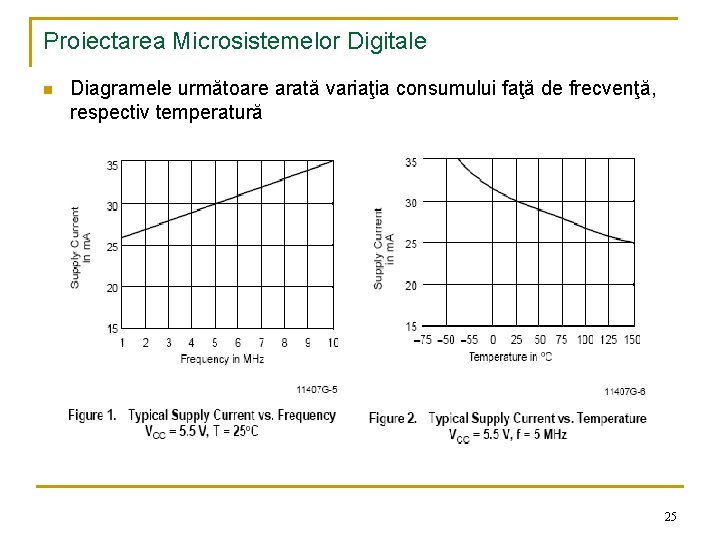

Proiectarea Microsistemelor Digitale n Diagramele următoare arată variaţia consumului faţă de frecvenţă, respectiv temperatură 25

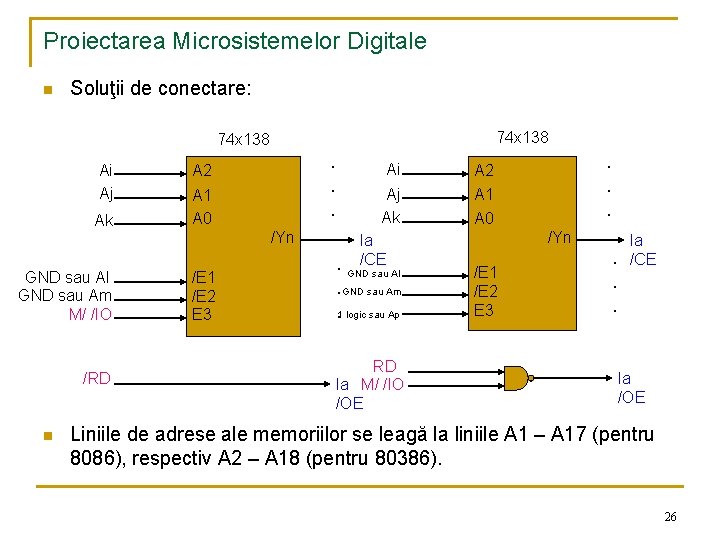

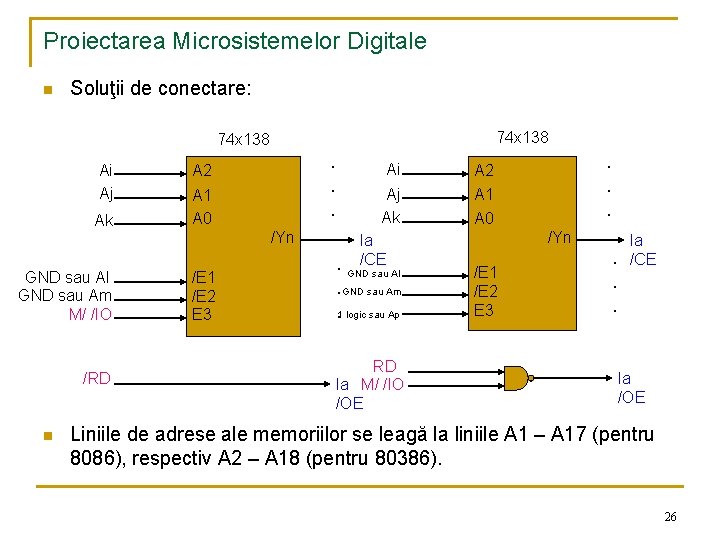

Proiectarea Microsistemelor Digitale n Soluţii de conectare: 74 x 138 Ai Aj Ak GND sau Al GND sau Am M/ /IO /RD n . . . A 2 A 1 A 0 /Yn /E 1 /E 2 E 3 Ai Aj Ak la /CE . GND sau Al. GND sau Am. 1 logic sau Ap RD la M/ /IO /OE . . . A 2 A 1 A 0 /Yn /E 1 /E 2 E 3 . . . la /CE la /OE Liniile de adrese ale memoriilor se leagă la liniile A 1 – A 17 (pentru 8086), respectiv A 2 – A 18 (pentru 80386). 26

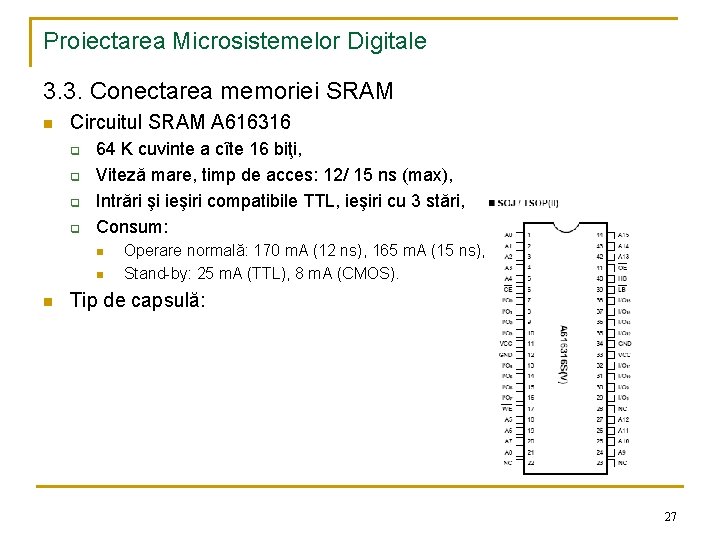

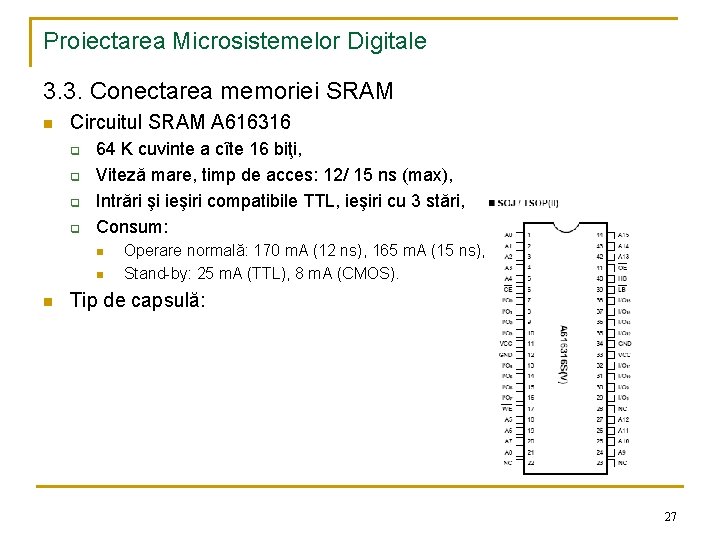

Proiectarea Microsistemelor Digitale 3. 3. Conectarea memoriei SRAM n Circuitul SRAM A 616316 q q 64 K cuvinte a cîte 16 biţi, Viteză mare, timp de acces: 12/ 15 ns (max), Intrări şi ieşiri compatibile TTL, ieşiri cu 3 stări, Consum: n n n Operare normală: 170 m. A (12 ns), 165 m. A (15 ns), Stand-by: 25 m. A (TTL), 8 m. A (CMOS). Tip de capsulă: 27

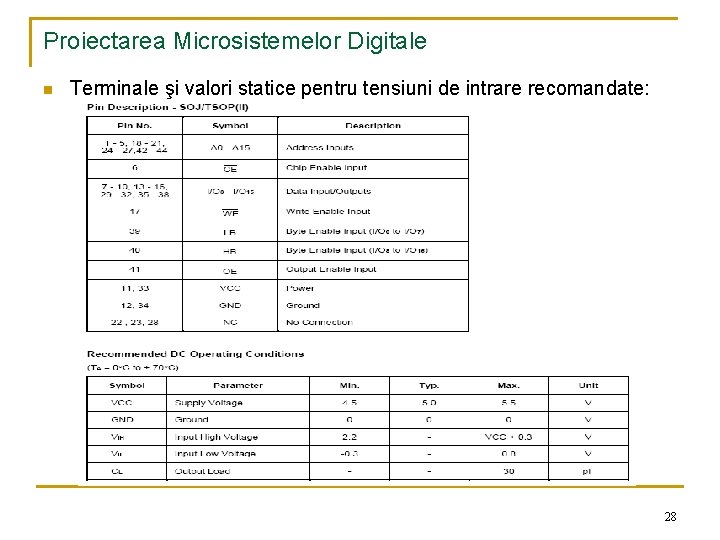

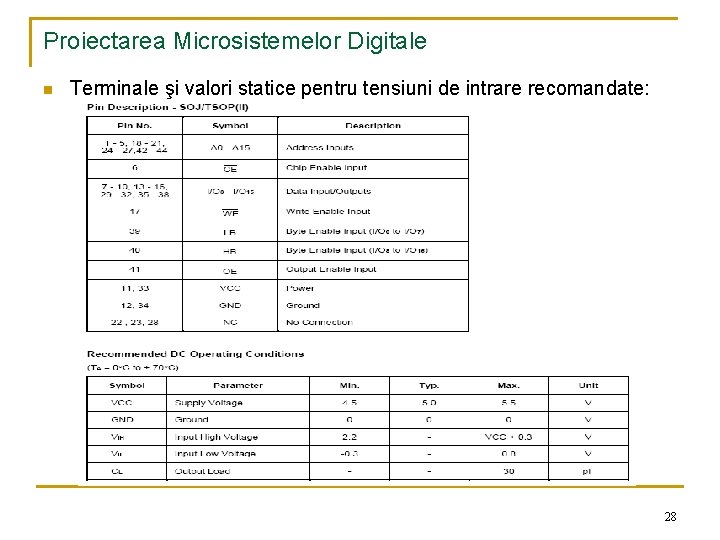

Proiectarea Microsistemelor Digitale n Terminale şi valori statice pentru tensiuni de intrare recomandate: 28

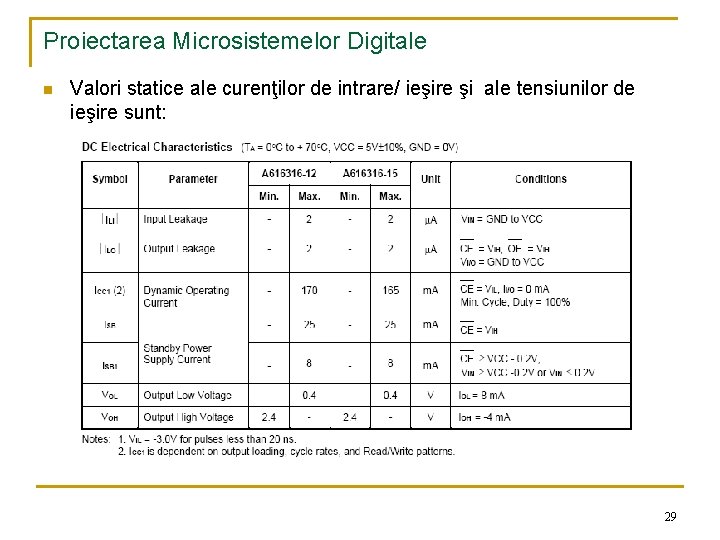

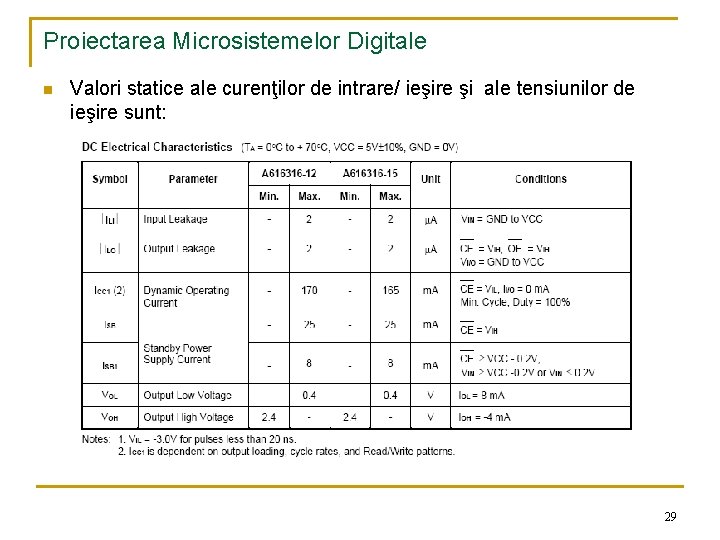

Proiectarea Microsistemelor Digitale n Valori statice ale curenţilor de intrare/ ieşire şi ale tensiunilor de ieşire sunt: 29

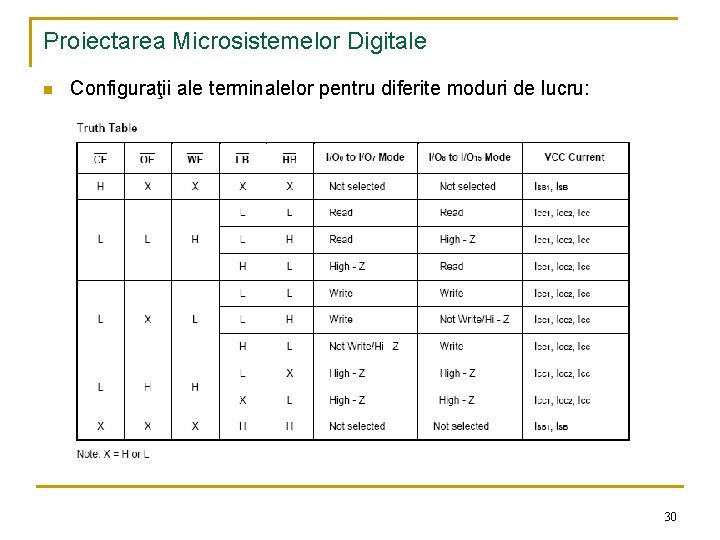

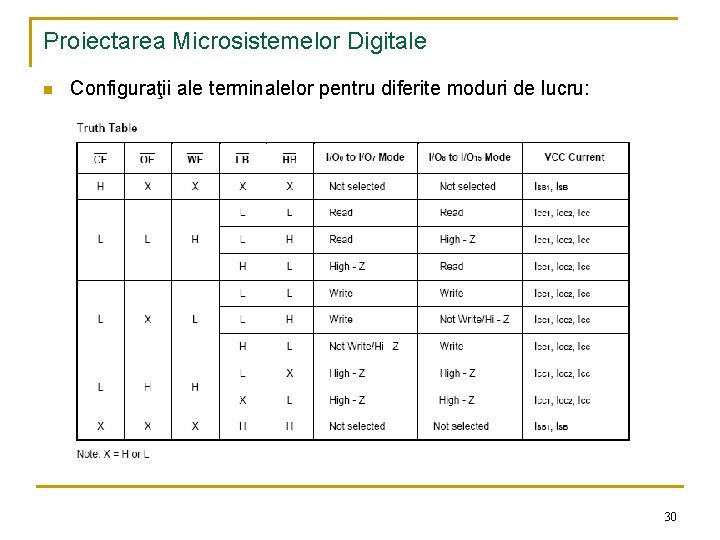

Proiectarea Microsistemelor Digitale n Configuraţii ale terminalelor pentru diferite moduri de lucru: 30

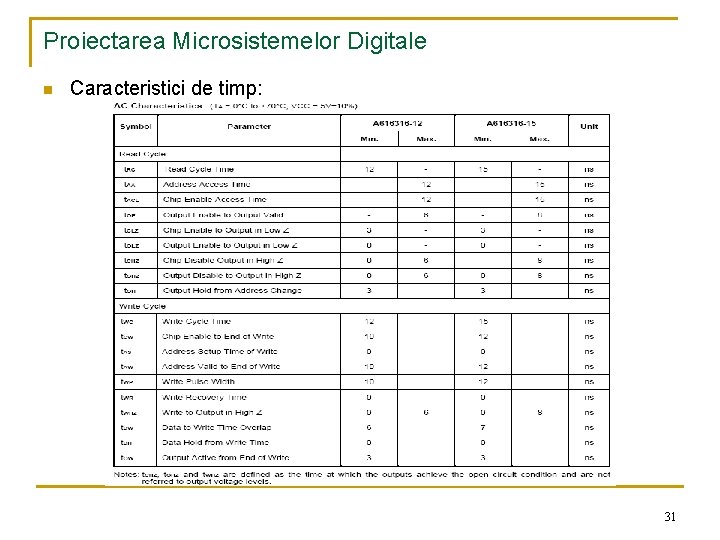

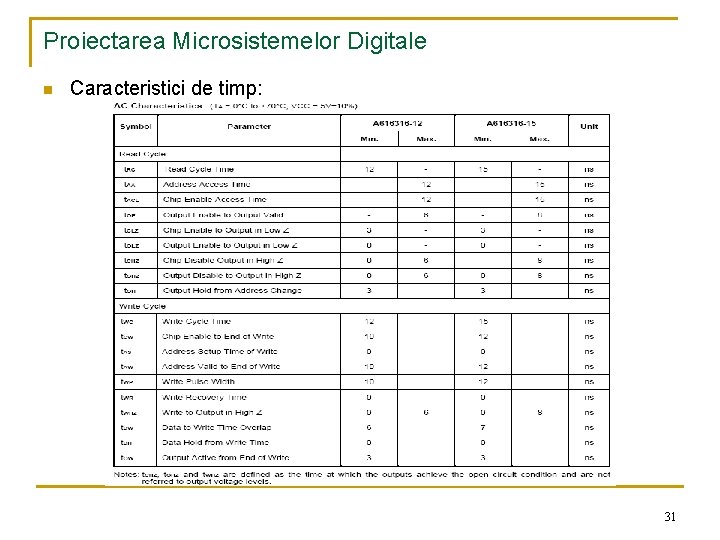

Proiectarea Microsistemelor Digitale n Caracteristici de timp: 31

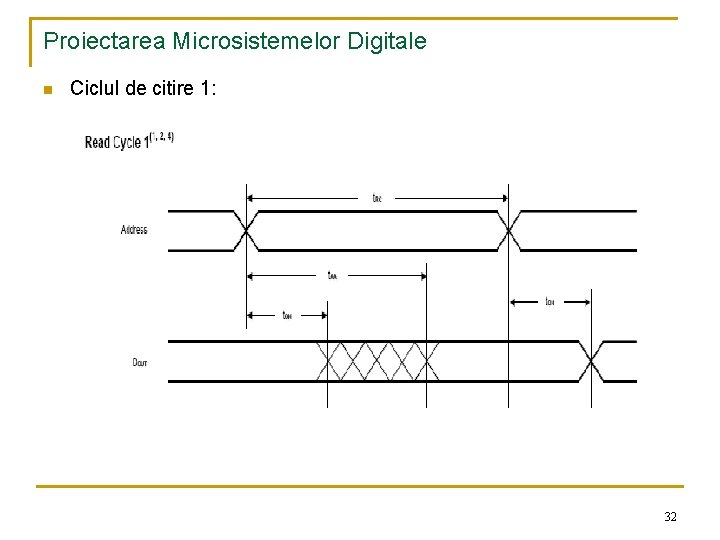

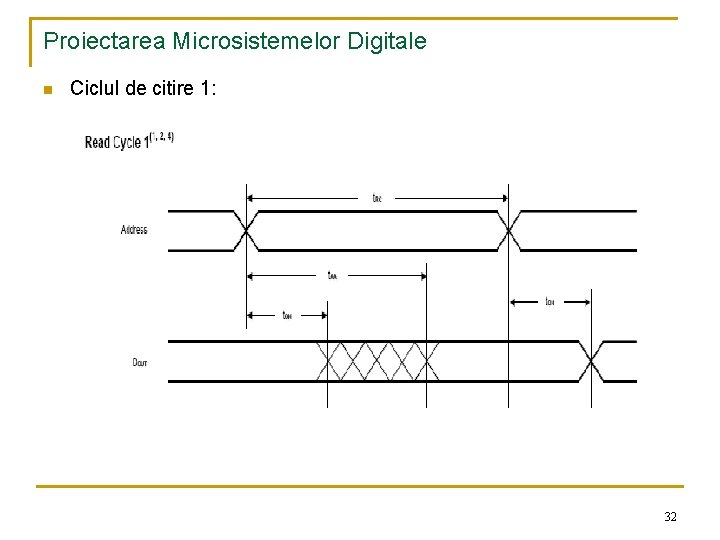

Proiectarea Microsistemelor Digitale n Ciclul de citire 1: 32

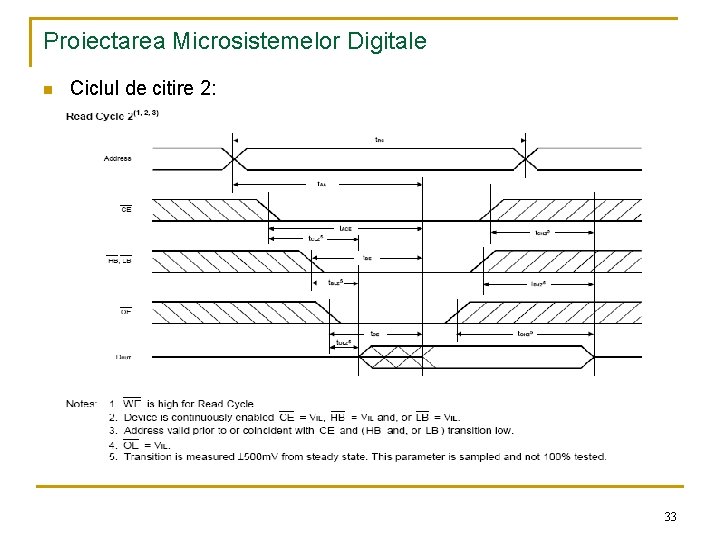

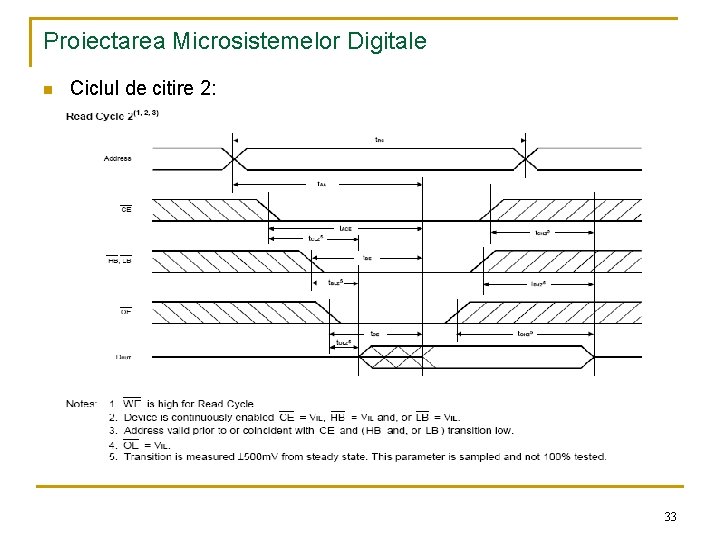

Proiectarea Microsistemelor Digitale n Ciclul de citire 2: 33

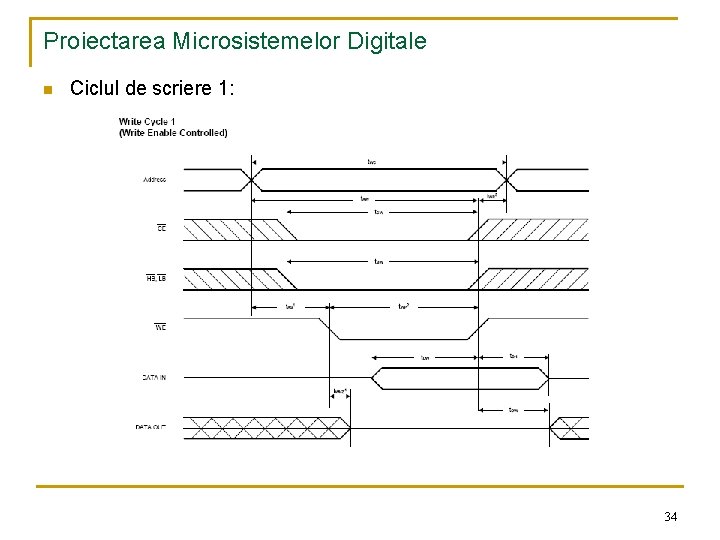

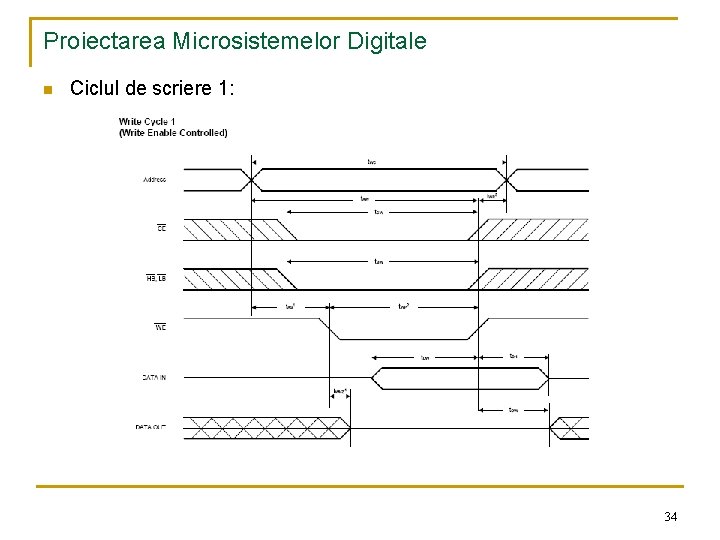

Proiectarea Microsistemelor Digitale n Ciclul de scriere 1: 34

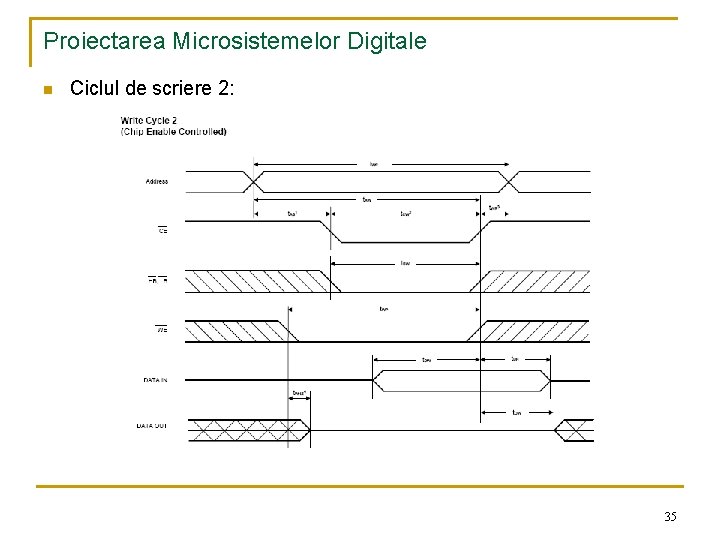

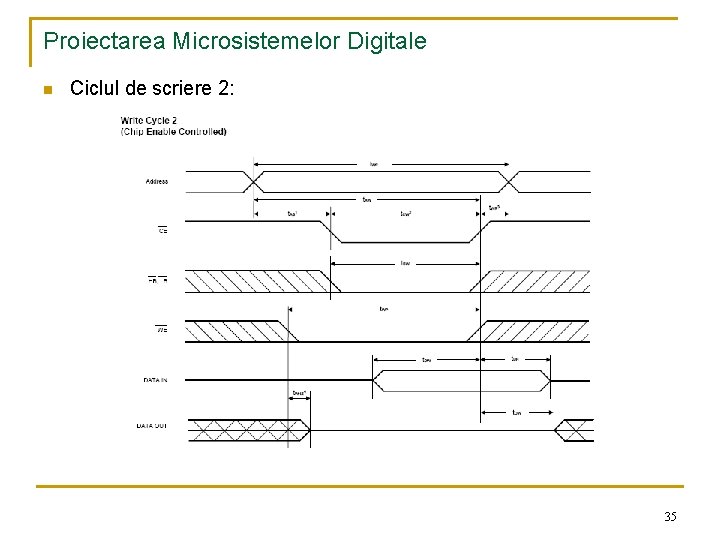

Proiectarea Microsistemelor Digitale n Ciclul de scriere 2: 35

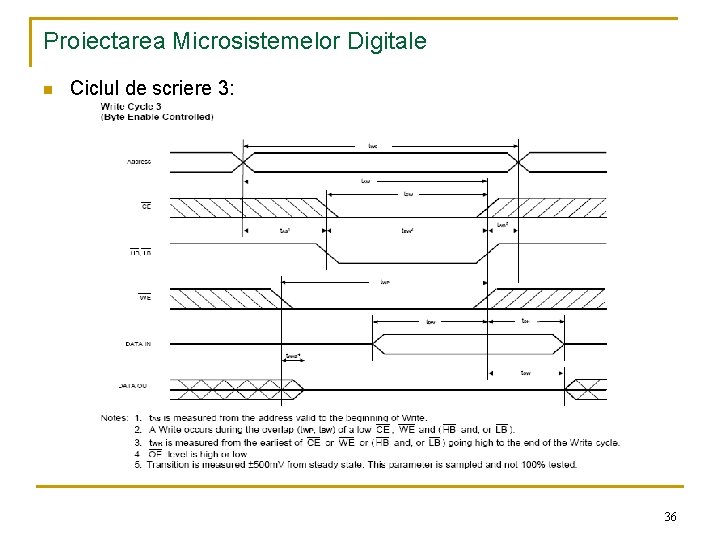

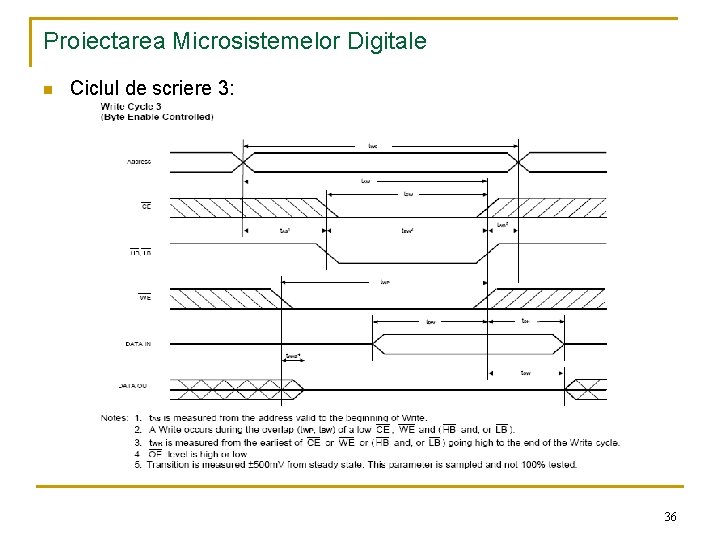

Proiectarea Microsistemelor Digitale n Ciclul de scriere 3: 36

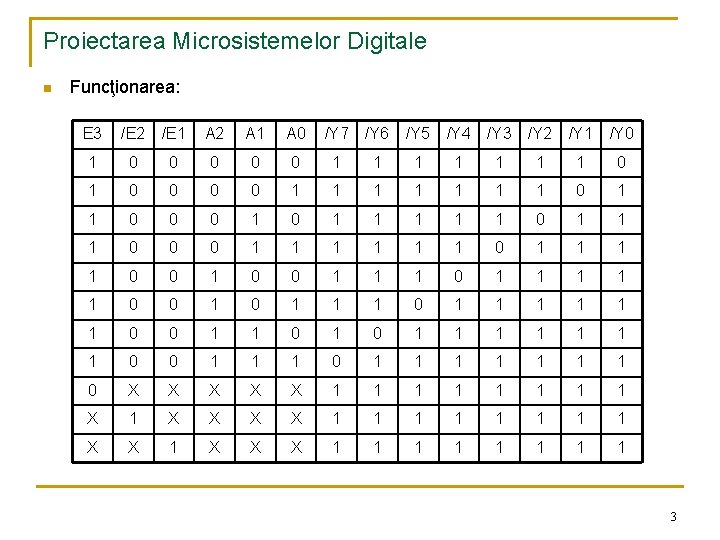

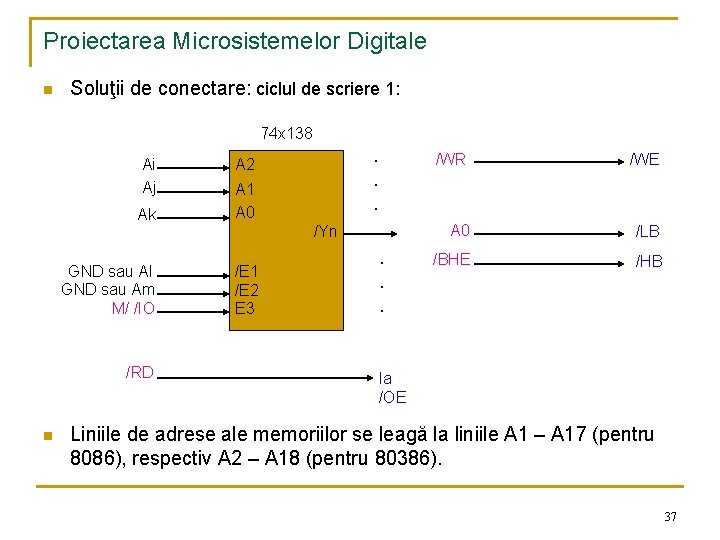

Proiectarea Microsistemelor Digitale n Soluţii de conectare: ciclul de scriere 1: 74 x 138 Ai Aj Ak GND sau Al GND sau Am M/ /IO /RD n . . . A 2 A 1 A 0 /Yn /E 1 /E 2 E 3 . . . /WR /WE A 0 /LB /BHE /HB la /OE Liniile de adrese ale memoriilor se leagă la liniile A 1 – A 17 (pentru 8086), respectiv A 2 – A 18 (pentru 80386). 37