Capitolul 6 Sinteza CLC folosind VHDL 2010 Proiectarea

- Slides: 40

Capitolul 6 Sinteza CLC folosind VHDL 2010 Proiectarea sistemelor digitale 1

Tematica Ø Informații generale Ø Etapele proiectării asistate de calculator Ø Etapele sintezei şi implementării Ø Exemple de sinteza cu FPGA 2010 Proiectarea sistemelor digitale 2

Informații introductive 2009 -2010 Utilizarea VHDL ȋn sinteza circuitelor logice presupune existența unei platforme pentru proiectarea asistatǎ de calculator. Ȋn cadrul cursului se va utiliza platforma Xilinx ISE 9. 2 i pentru editarea, compilarea programelor și generarea testelor, respectiv Model. Sim XE III 6. 4 b pentru simulare. Implementǎrile se vor face pe un modul FPGA al firmei Xilinx, cu indicativul xc 3 s 400 -4 ft 256. PDSD 3

Etapele proiectarii asistate de calculator Editarea modelului VHDL. Verificarea corectitudinii sintaxei programului. Aceastǎ verificare este necesarǎ dar nu și suficientǎ deoarece nu garanteazǎ corectitudinea modelului sau faptul cǎ acesta este implementabil la nivel fizic pe modulul avut ȋn vedere. Declararea unor constrȃngeri de proiectare cum ar fi asignarea porturilor la pinii modulului utilizat, criteriile de optimizare a proiectǎrii. Aceastǎ etapǎ nu este necesarǎ decȃt ȋn cazul ȋn care se dorește implementarea efectivǎ a circuitului proiectat. Generarea programului pentru modulul utilizat la implementare. Suplimentar utilizatorului i se oferǎ schema bloc sau diverse detalii ale schemei la nivel logic și fizic. Pe durata generǎrii programului, sunt generate diverse mesaje de avertizare sau eroare care ghideazǎ proiectantul ȋn depanarea modelului sau optimizarea soluției alese. 2009 -2010 PDSD 4

Etapele proiectarii asistate de calculator Folosind opțiunile de generare a testelor se genereazǎ programele de test (test bench) tot ȋn limbaj VHDL (scrierea programelor de test nu face obiectul acestui curs). Se testeazǎ funcționarea funcționalǎ (fǎrǎ luarea ȋn considerare a ȋntȃrzierilor) și dacǎ nu apar anomalii se trece la simularea funcționǎrii reale. Se transferǎ programul pentru FPGA ȋn modulul disponibil. Se efectueazǎ testele pentru verificarea și validarea funcționǎrii ȋn condiții reale. Ȋn cazul ȋn care testele eșueazǎ se modifică soluția propusǎ, parcurgǎnd din nou toate etapele. Dacǎ toate testele efectuate nu mai pun ȋn evidențǎ nici o eroare, se trece la producția de serie. 2009 -2010 PDSD 5

2009 -2010 Exemple de sinteză PDSD 6

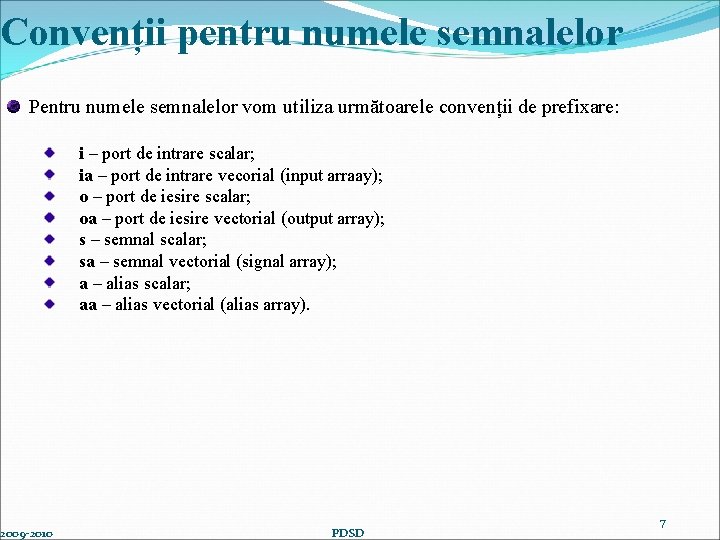

Convenții pentru numele semnalelor Pentru numele semnalelor vom utiliza următoarele convenții de prefixare: 2009 -2010 i – port de intrare scalar; ia – port de intrare vecorial (input arraay); o – port de iesire scalar; oa – port de iesire vectorial (output array); s – semnal scalar; sa – semnal vectorial (signal array); a – alias scalar; aa – alias vectorial (alias array). PDSD 7

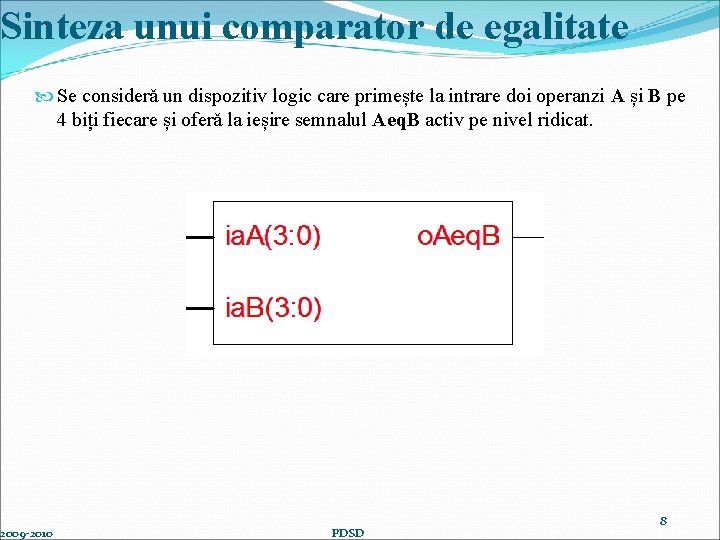

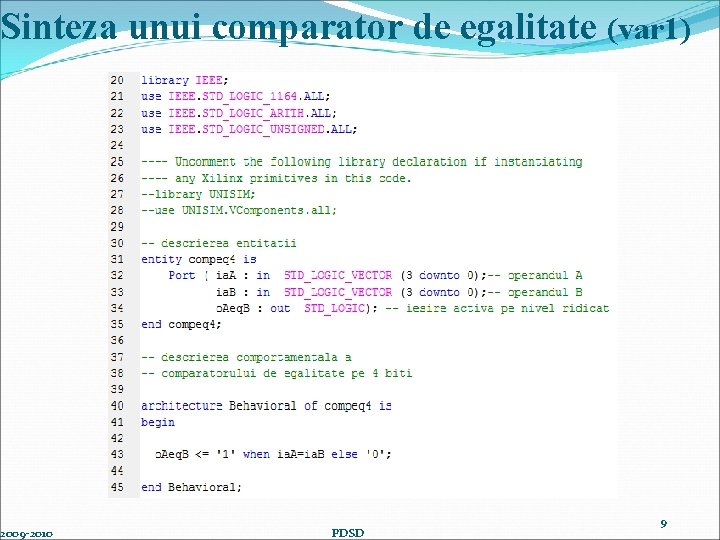

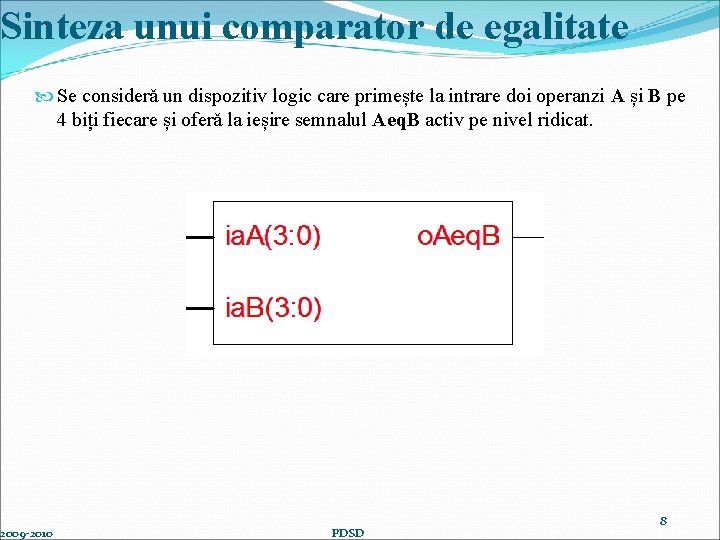

Sinteza unui comparator de egalitate Se considerǎ un dispozitiv logic care primește la intrare doi operanzi A și B pe 4 biți fiecare și oferǎ la ieșire semnalul Aeq. B activ pe nivel ridicat. 2009 -2010 PDSD 8

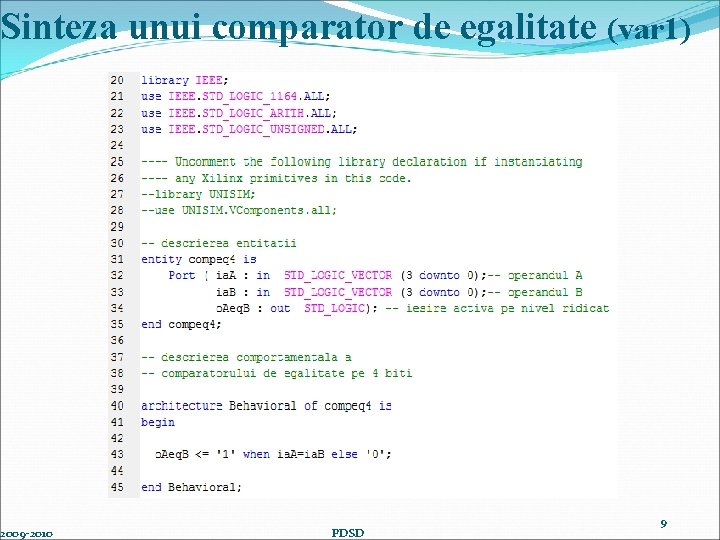

Sinteza unui comparator de egalitate (var 1) 2009 -2010 PDSD 9

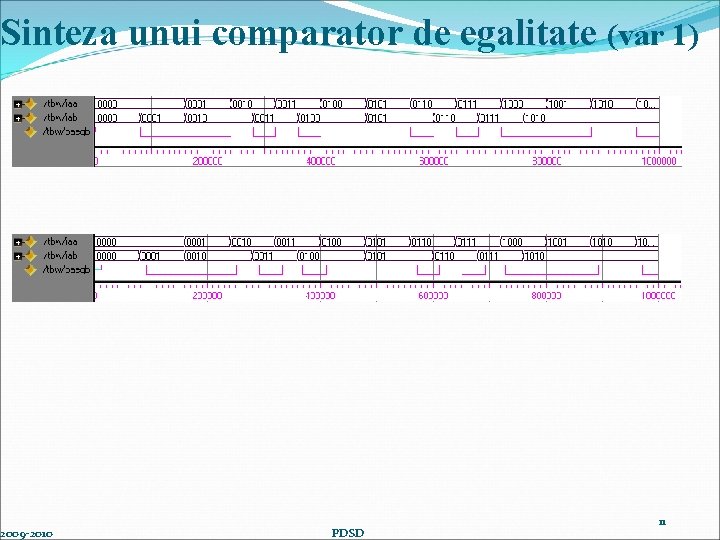

Sinteza unui comparator de egalitate (var 1) 2009 -2010 PDSD 10

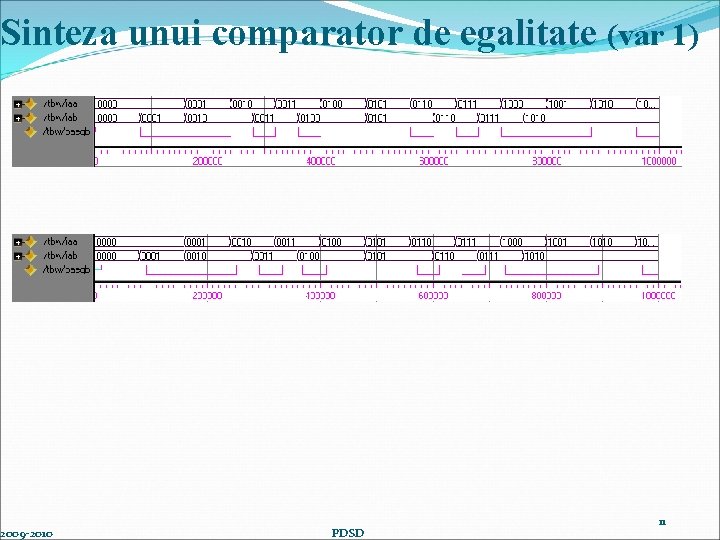

Sinteza unui comparator de egalitate (var 1) 2009 -2010 PDSD 11

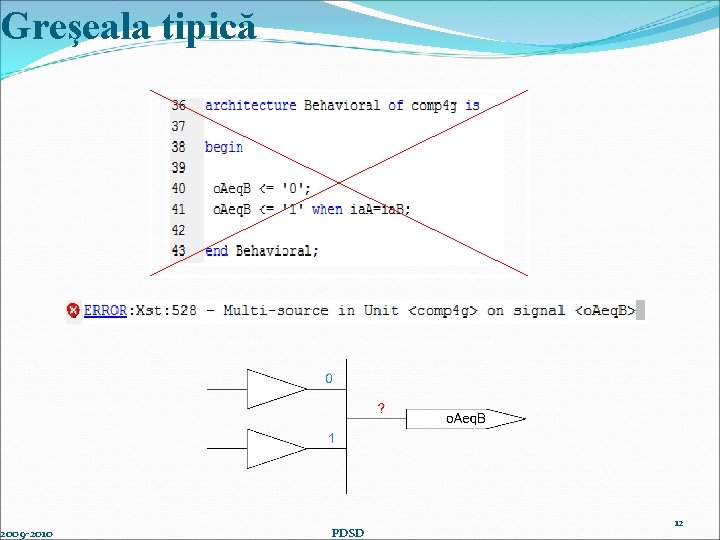

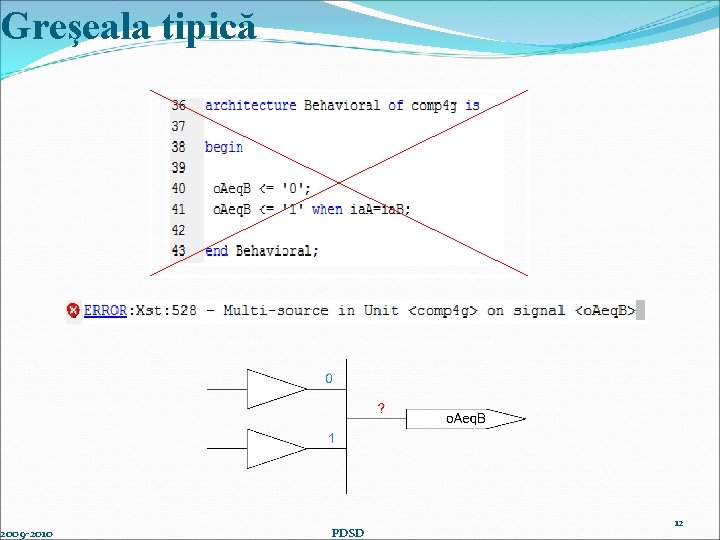

Greşeala tipică 2009 -2010 PDSD 12

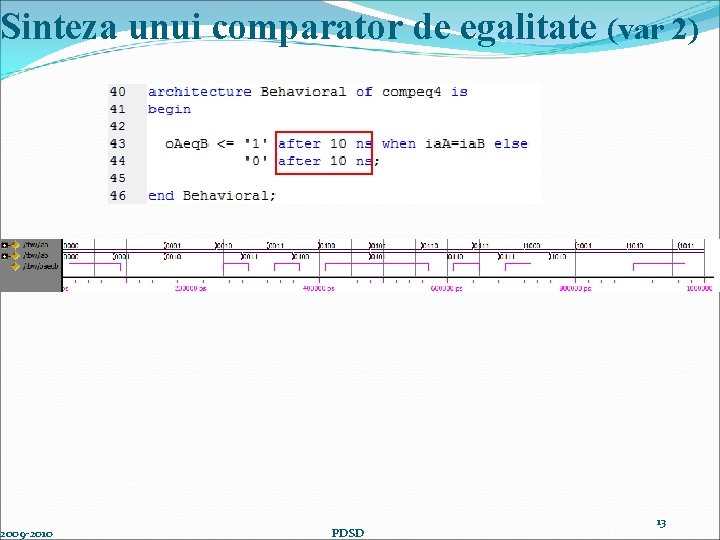

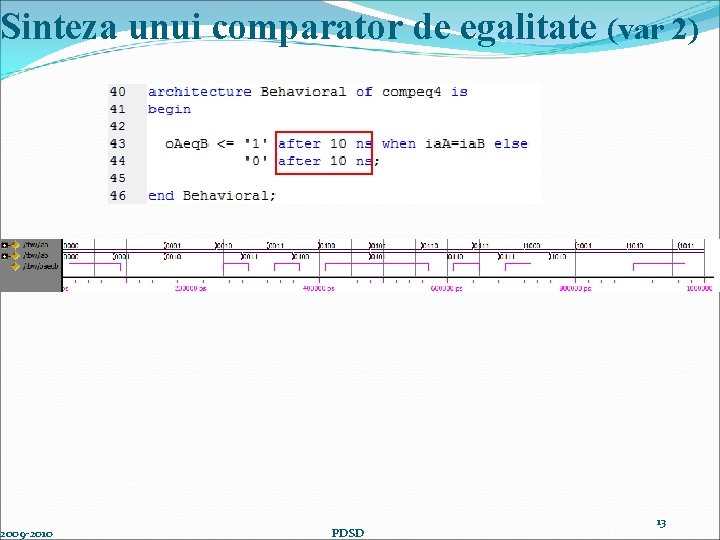

Sinteza unui comparator de egalitate (var 2) 2009 -2010 PDSD 13

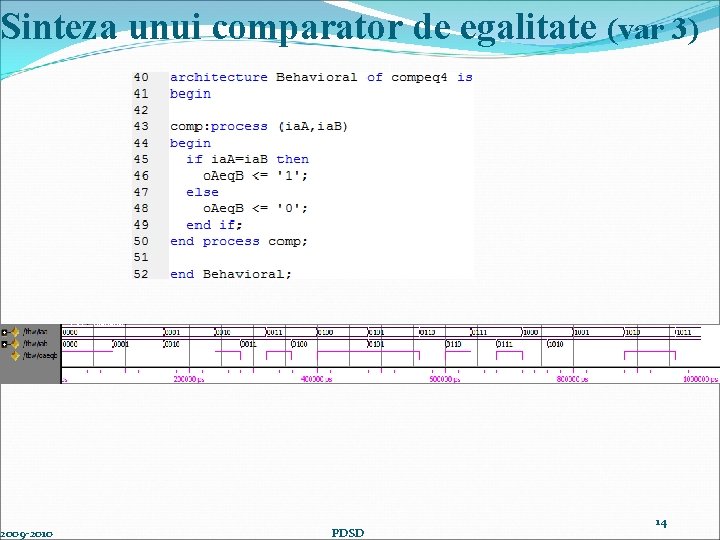

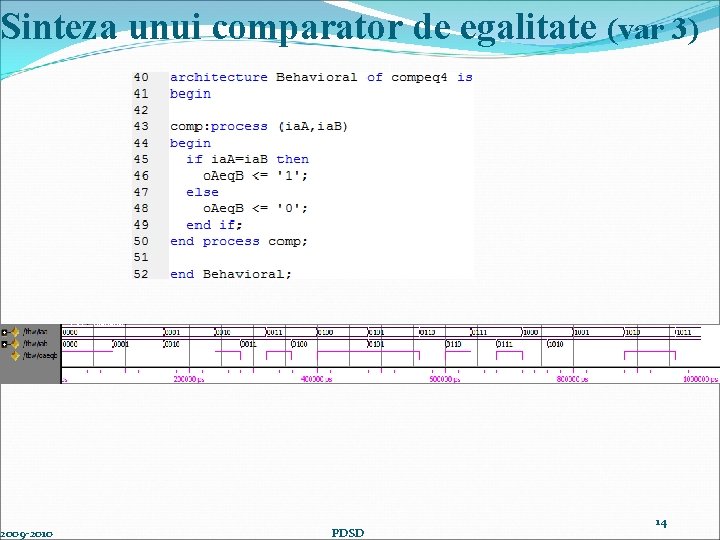

Sinteza unui comparator de egalitate (var 3) 2009 -2010 PDSD 14

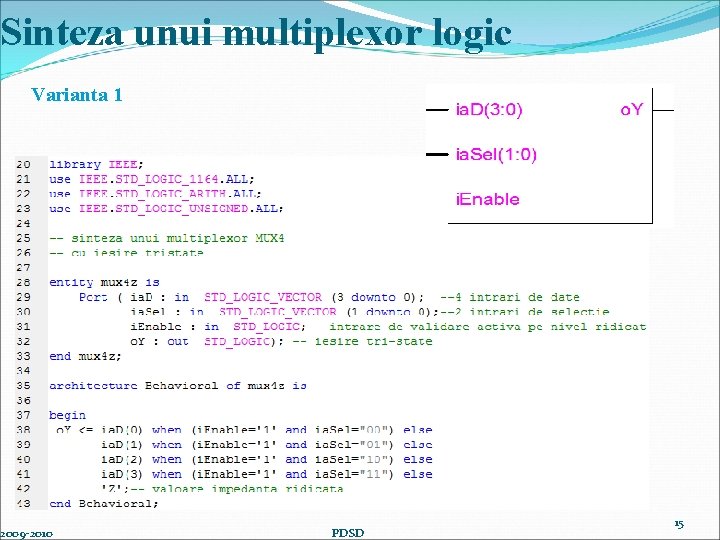

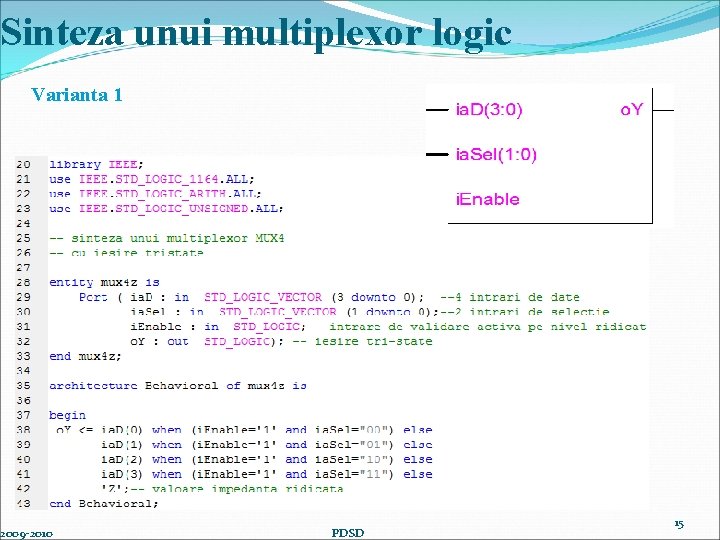

Sinteza unui multiplexor logic Varianta 1 2009 -2010 PDSD 15

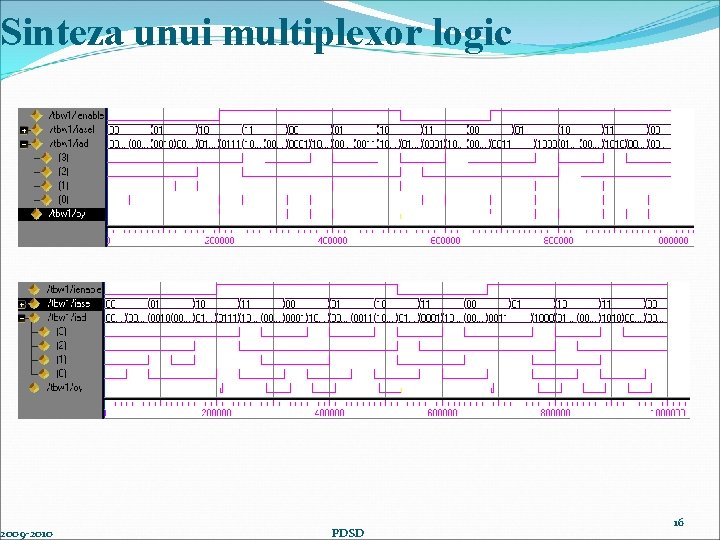

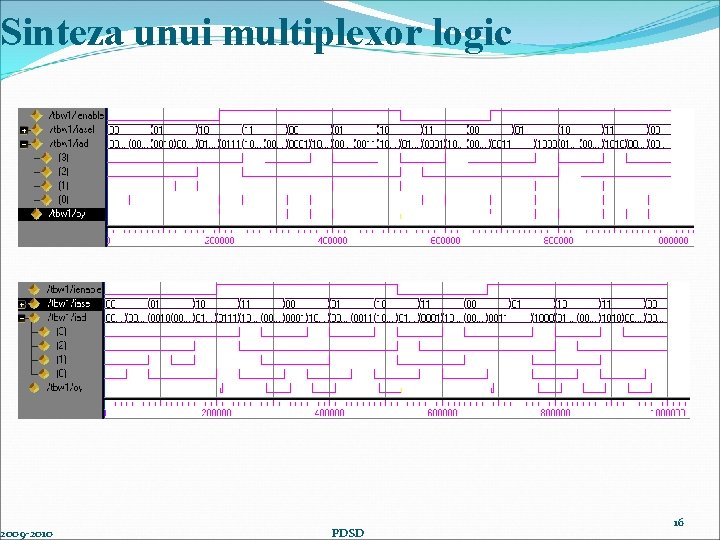

Sinteza unui multiplexor logic 2009 -2010 PDSD 16

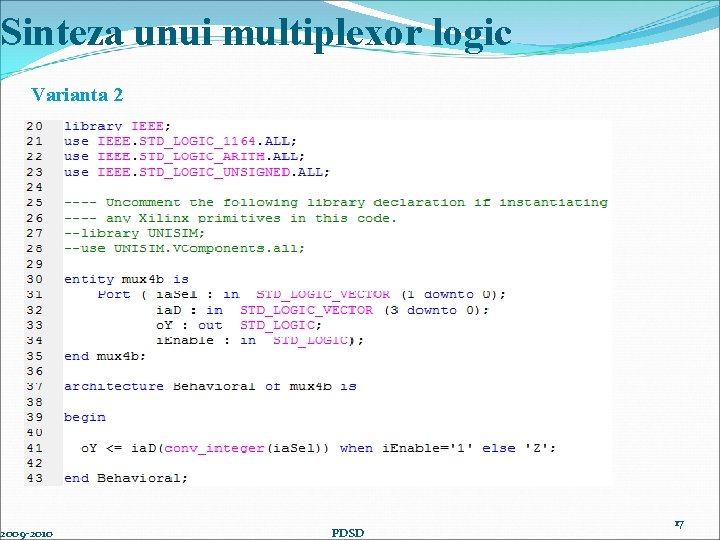

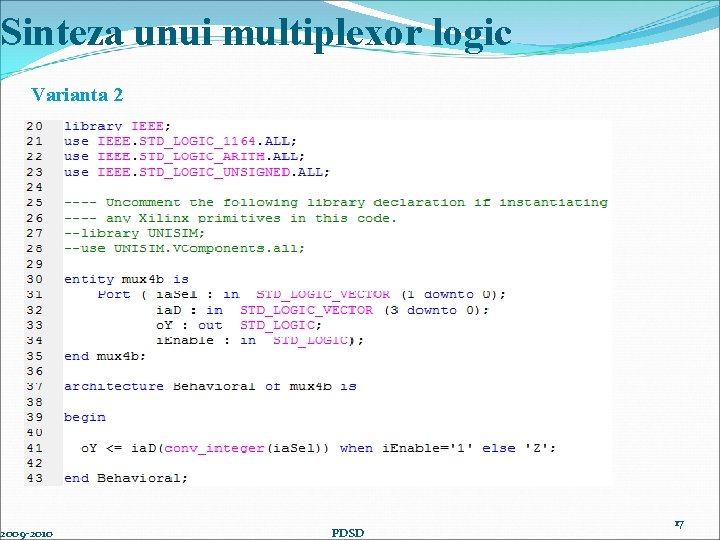

Sinteza unui multiplexor logic Varianta 2 2009 -2010 PDSD 17

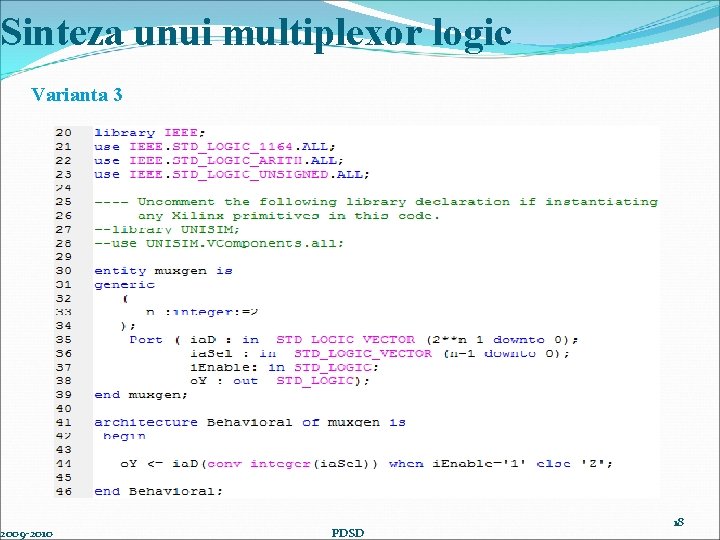

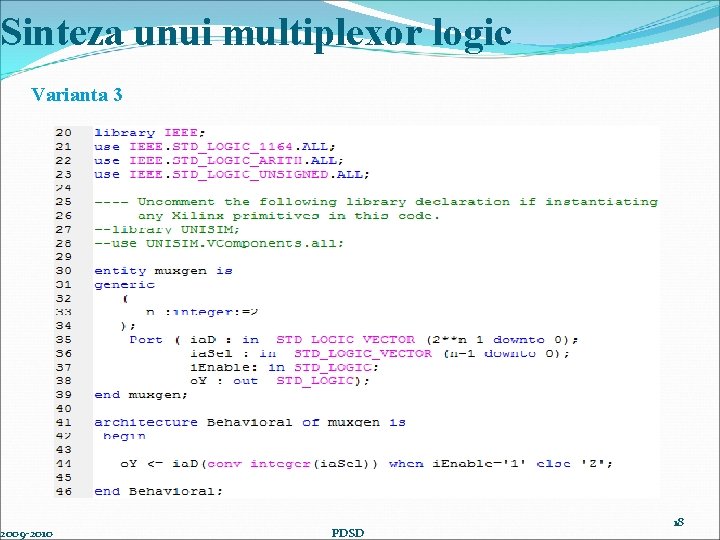

Sinteza unui multiplexor logic Varianta 3 2009 -2010 PDSD 18

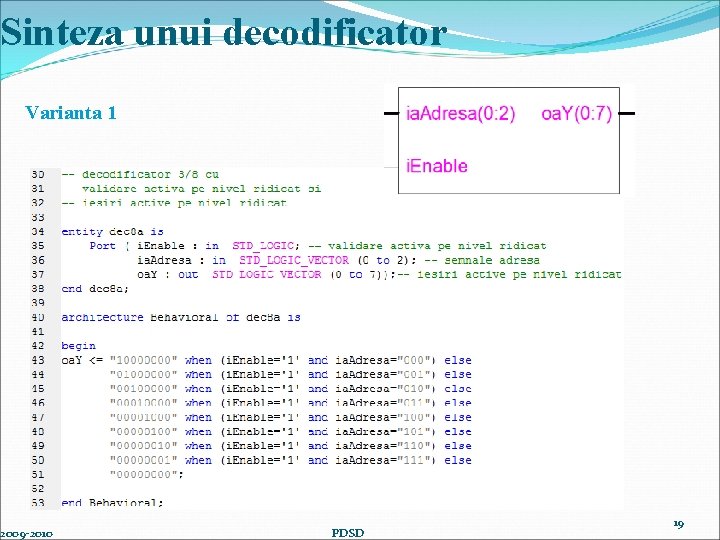

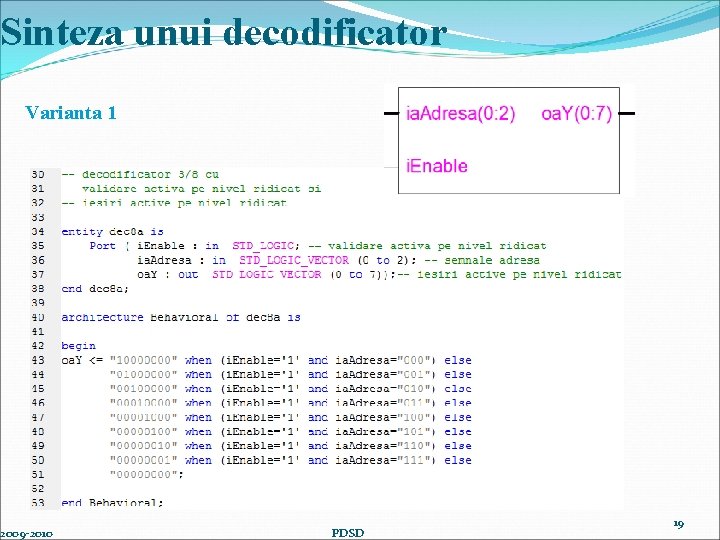

Sinteza unui decodificator Varianta 1 2009 -2010 PDSD 19

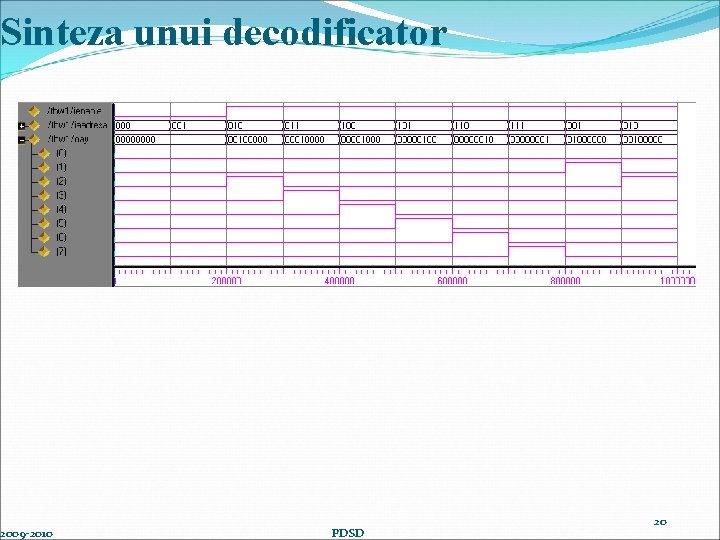

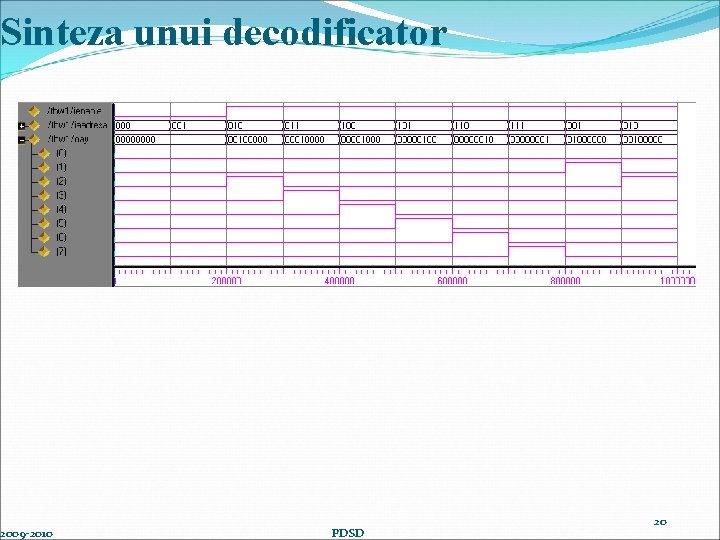

Sinteza unui decodificator 2009 -2010 PDSD 20

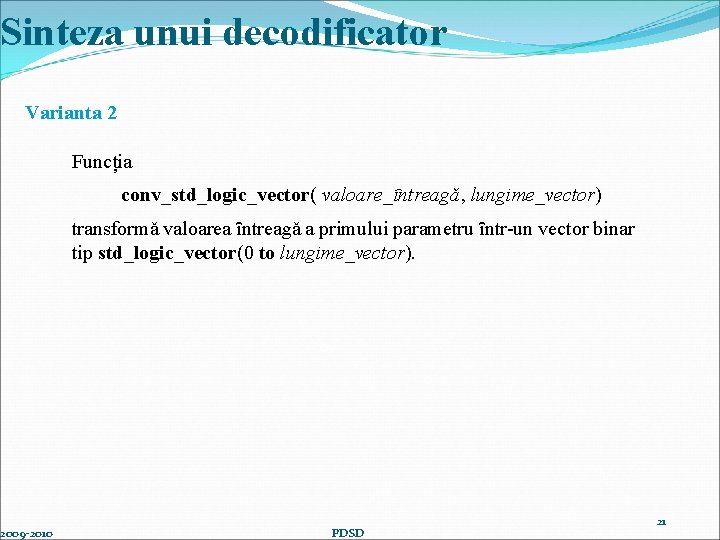

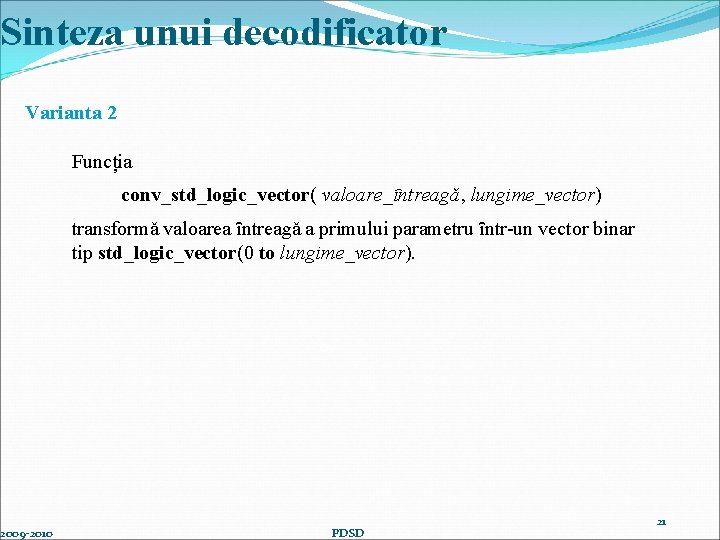

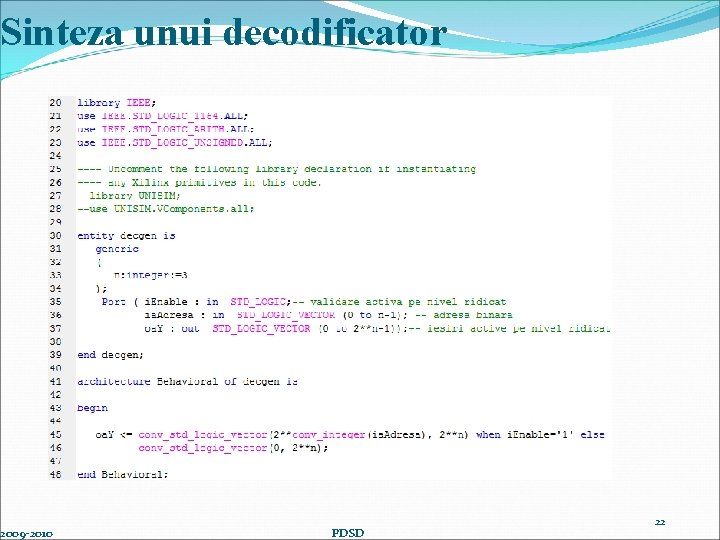

Sinteza unui decodificator Varianta 2 2009 -2010 Funcția conv_std_logic_vector( valoare_ȋntreagǎ, lungime_vector) transformǎ valoarea ȋntreagǎ a primului parametru ȋntr-un vector binar tip std_logic_vector(0 to lungime_vector). PDSD 21

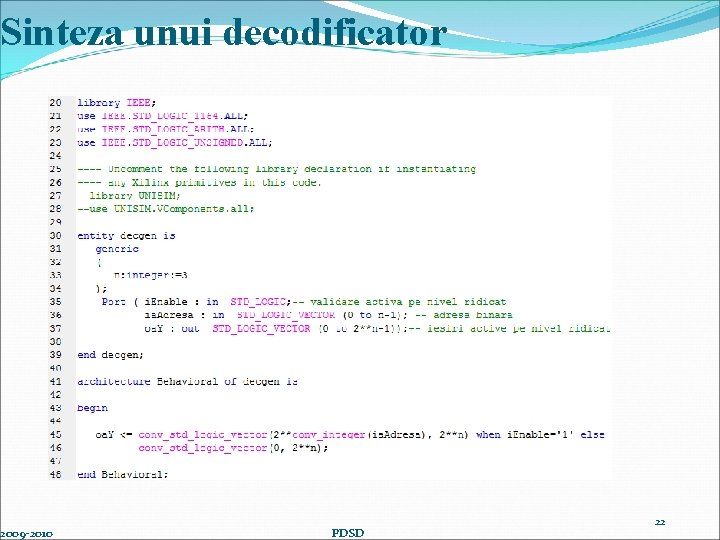

Sinteza unui decodificator 2009 -2010 PDSD 22

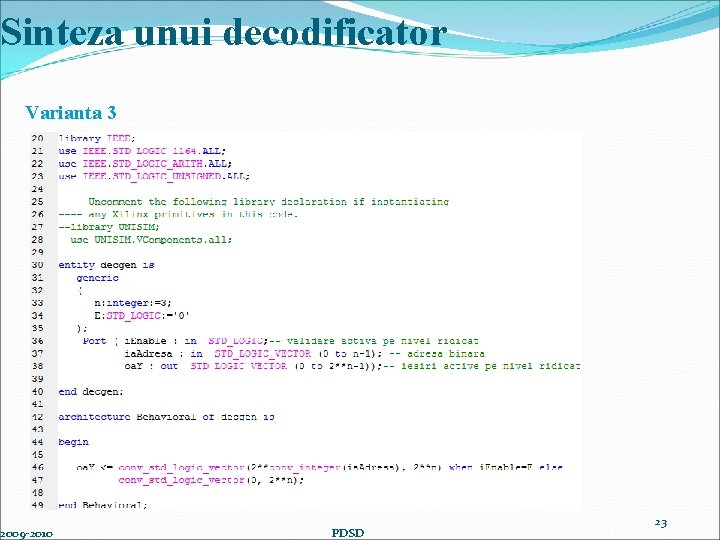

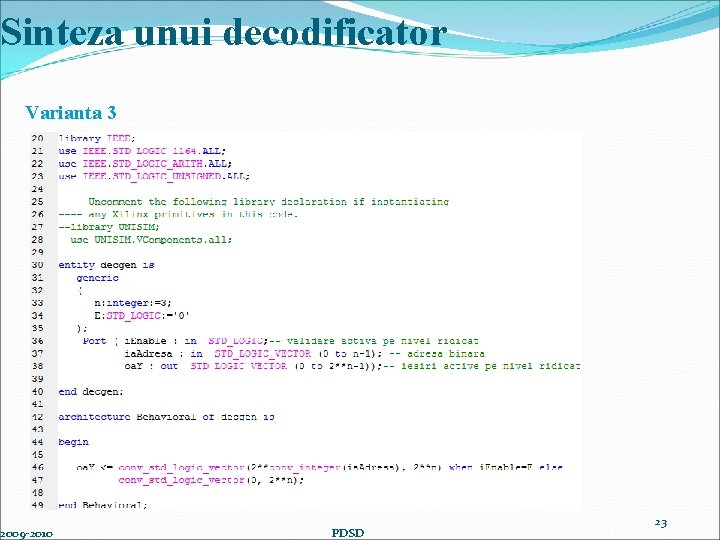

Sinteza unui decodificator Varianta 3 2009 -2010 PDSD 23

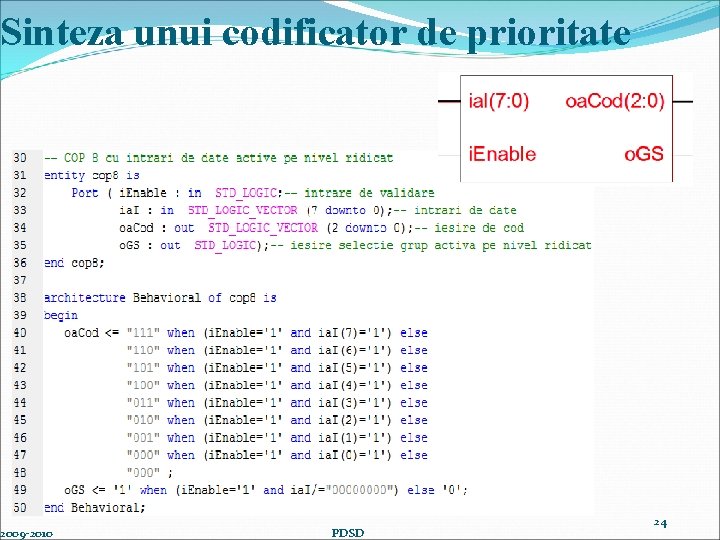

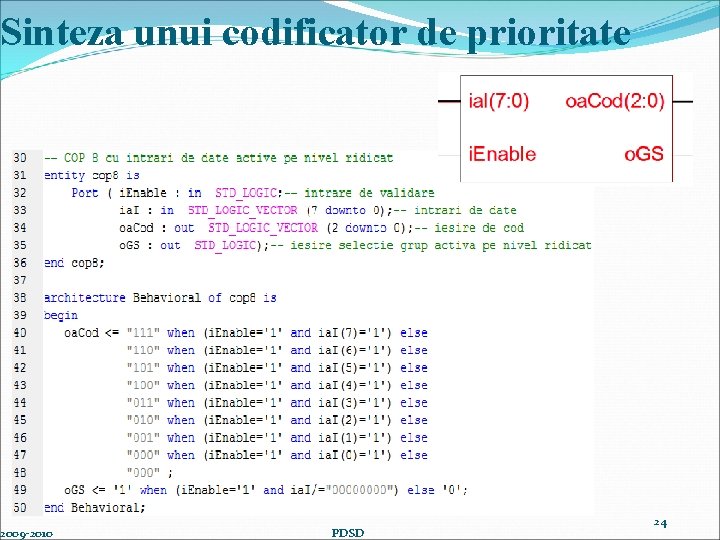

Sinteza unui codificator de prioritate 2009 -2010 PDSD 24

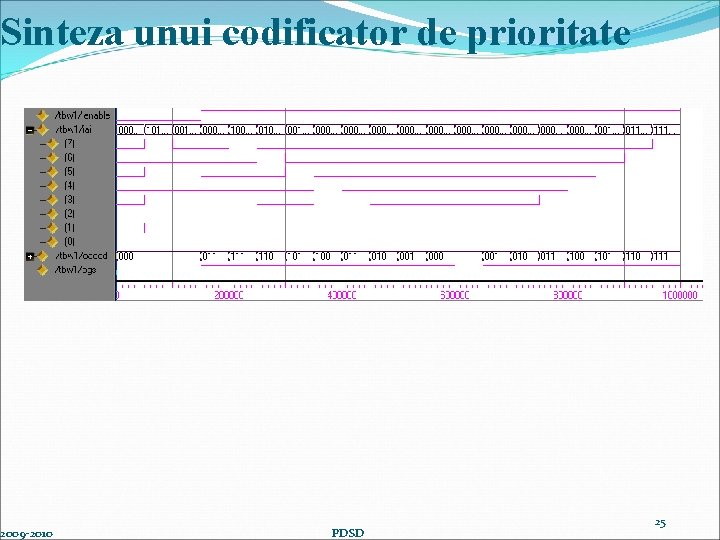

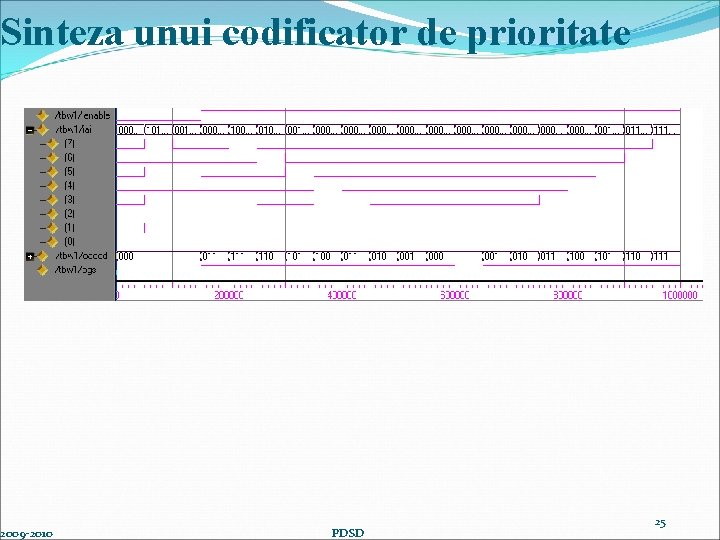

Sinteza unui codificator de prioritate 2009 -2010 PDSD 25

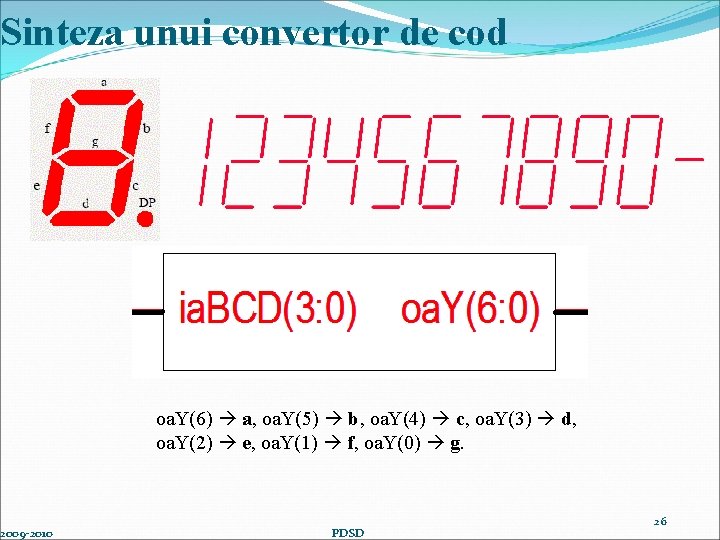

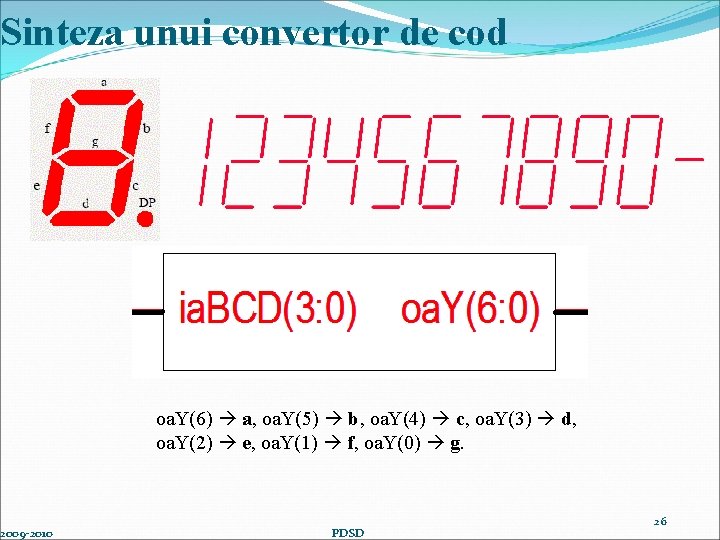

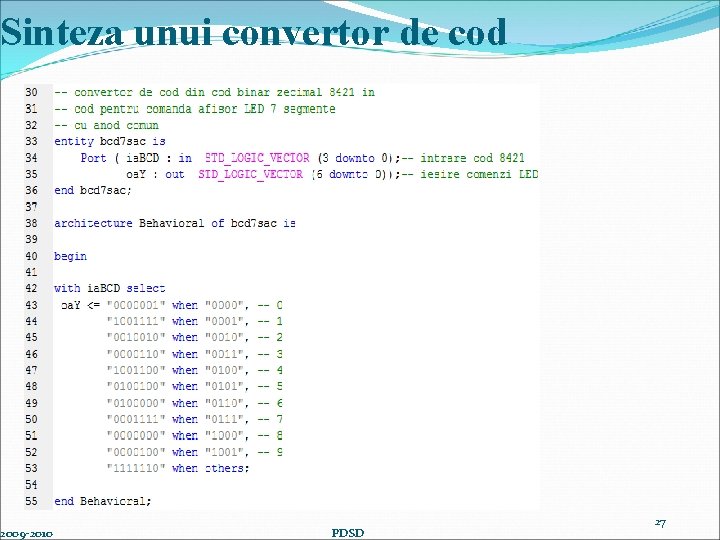

Sinteza unui convertor de cod 2009 -2010 oa. Y(6) a, oa. Y(5) b, oa. Y(4) c, oa. Y(3) d, oa. Y(2) e, oa. Y(1) f, oa. Y(0) g. PDSD 26

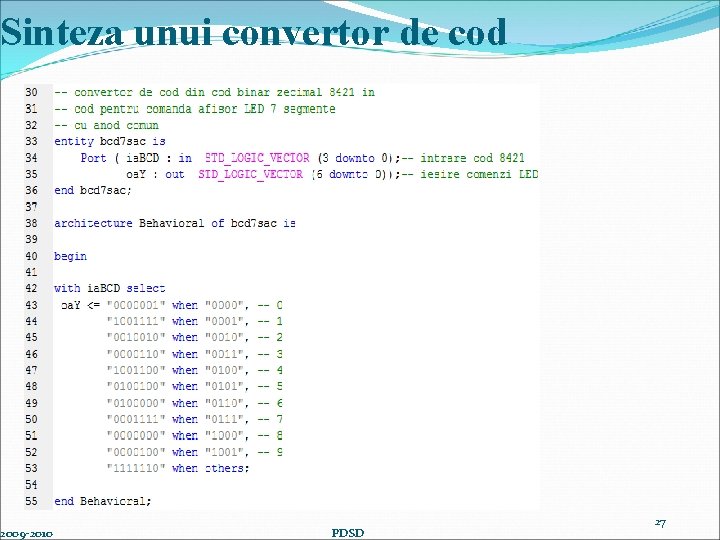

Sinteza unui convertor de cod 2009 -2010 PDSD 27

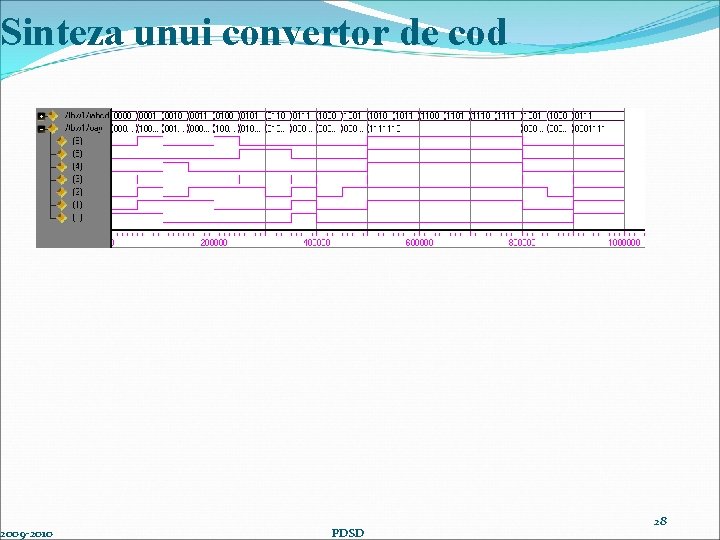

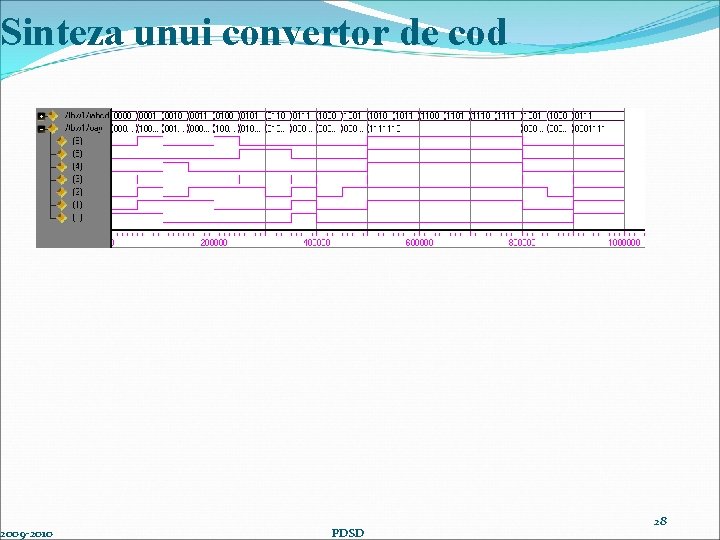

Sinteza unui convertor de cod 2009 -2010 PDSD 28

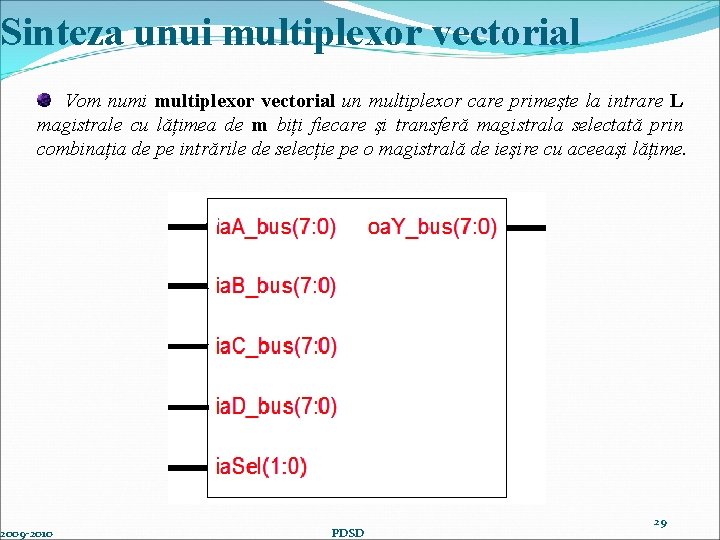

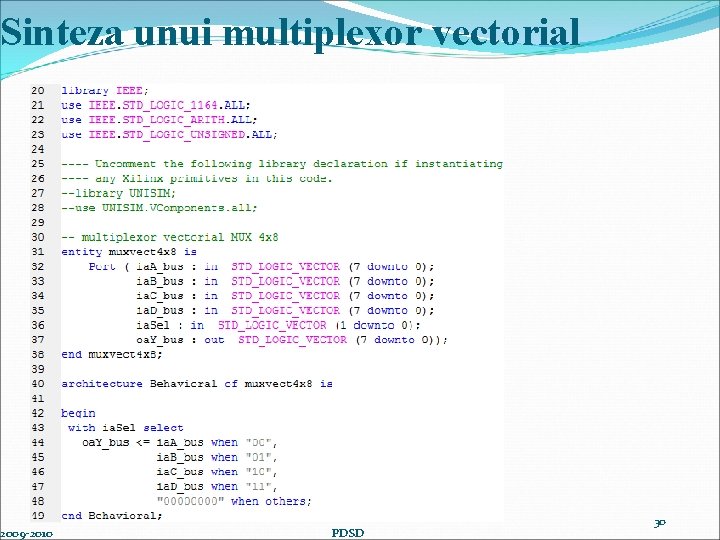

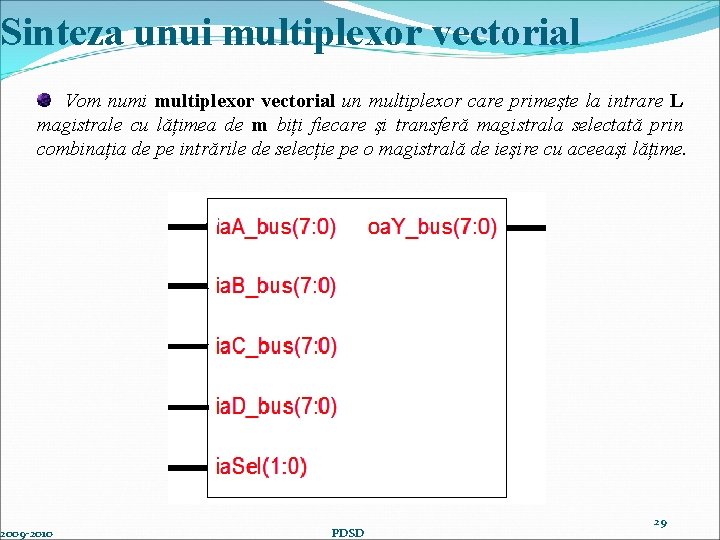

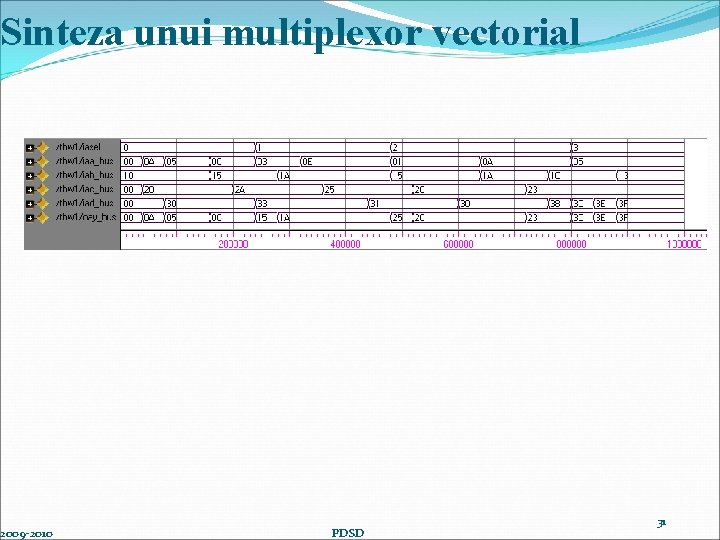

Sinteza unui multiplexor vectorial Vom numi multiplexor vectorial un multiplexor care primeşte la intrare L magistrale cu lățimea de m biți fiecare şi transferă magistrala selectată prin combinația de pe intrările de selecție pe o magistrală de ieşire cu aceeaşi lățime. 2009 -2010 PDSD 29

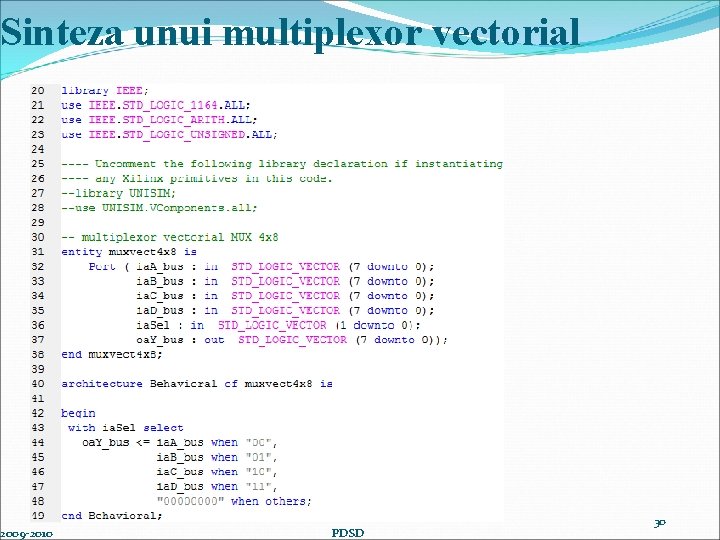

Sinteza unui multiplexor vectorial 2009 -2010 PDSD 30

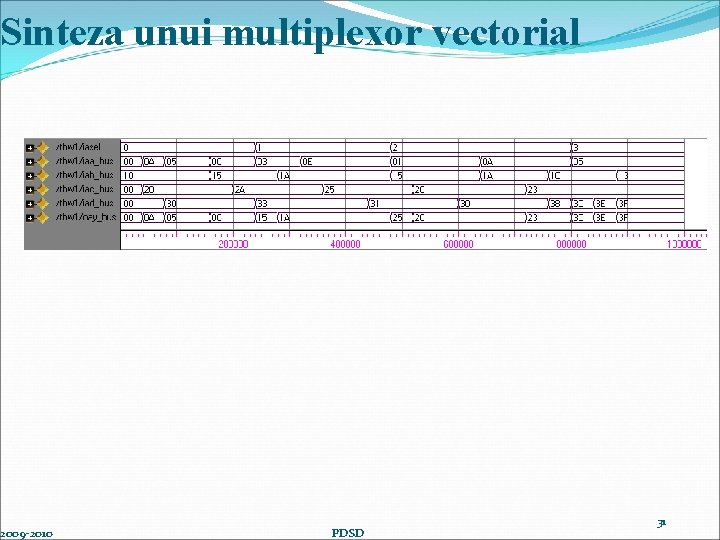

Sinteza unui multiplexor vectorial 2009 -2010 PDSD 31

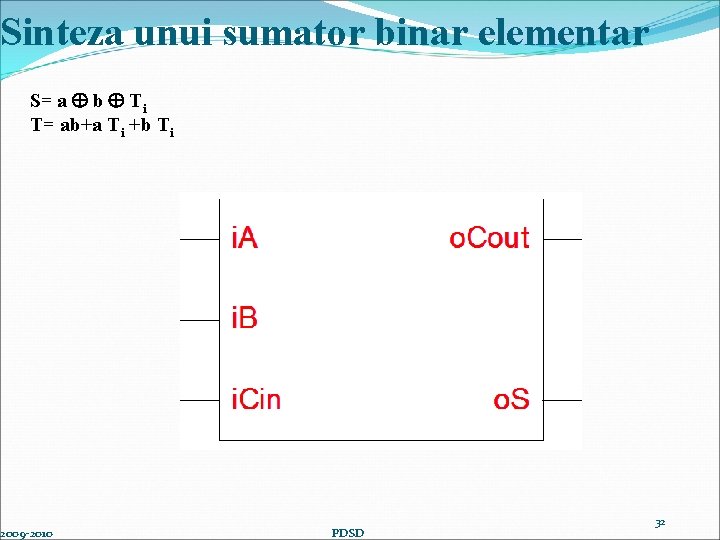

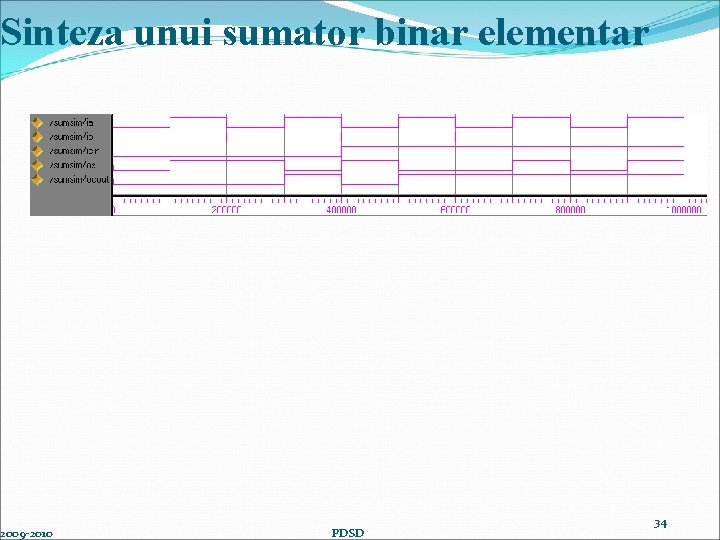

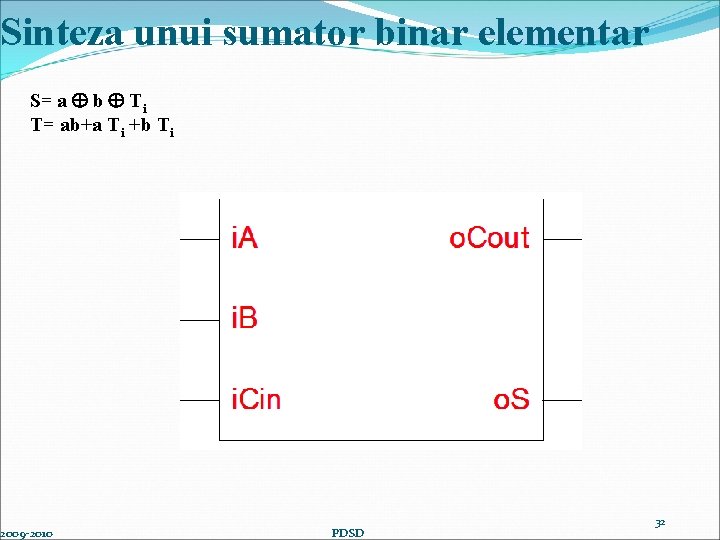

Sinteza unui sumator binar elementar S= a b Ti T= ab+a Ti +b Ti 2009 -2010 PDSD 32

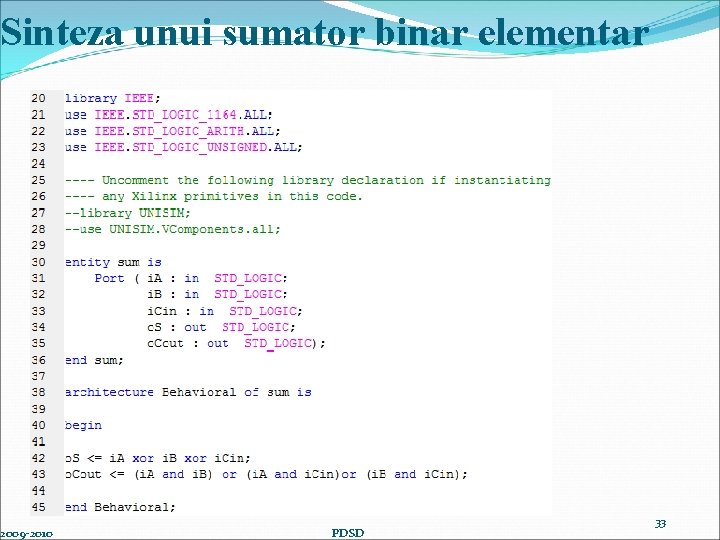

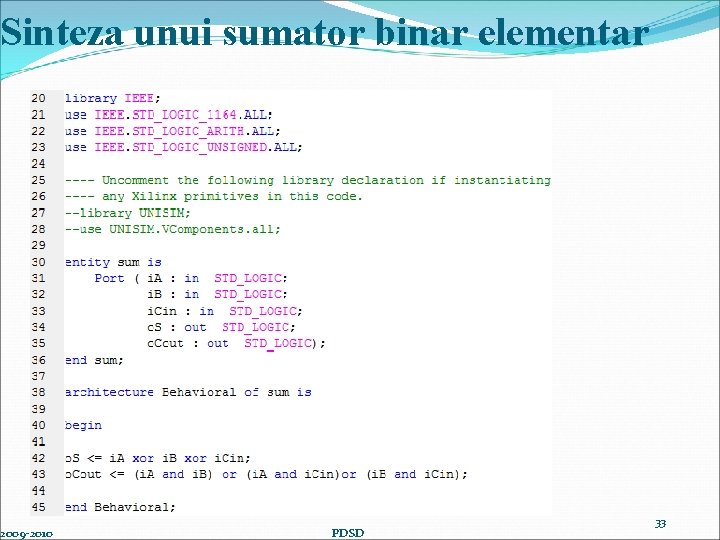

Sinteza unui sumator binar elementar 2009 -2010 PDSD 33

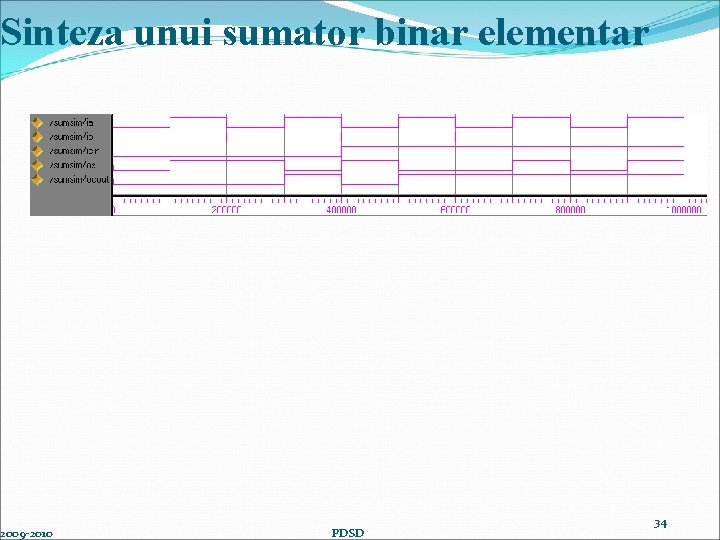

Sinteza unui sumator binar elementar 2009 -2010 PDSD 34

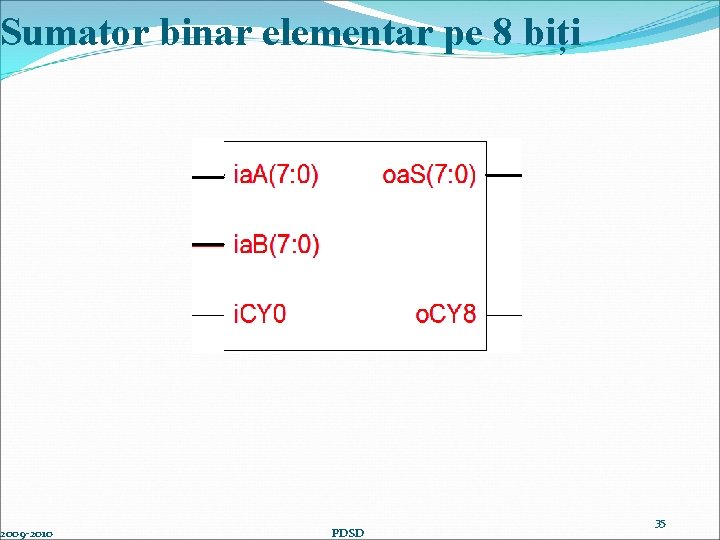

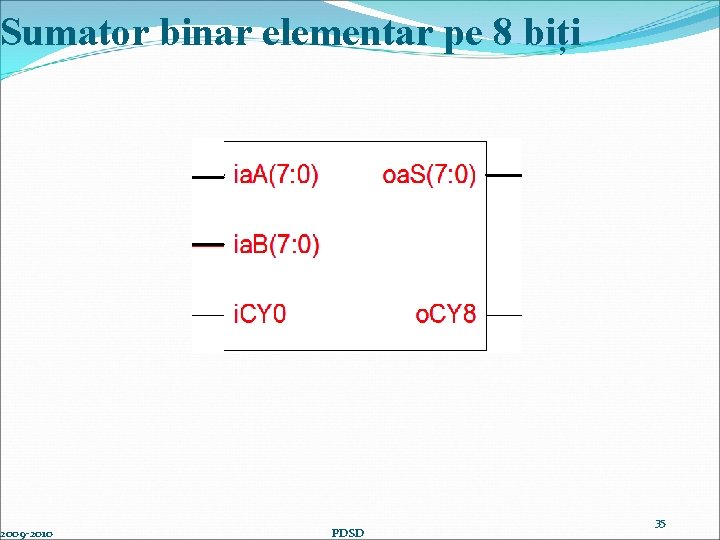

Sumator binar elementar pe 8 biți 2009 -2010 PDSD 35

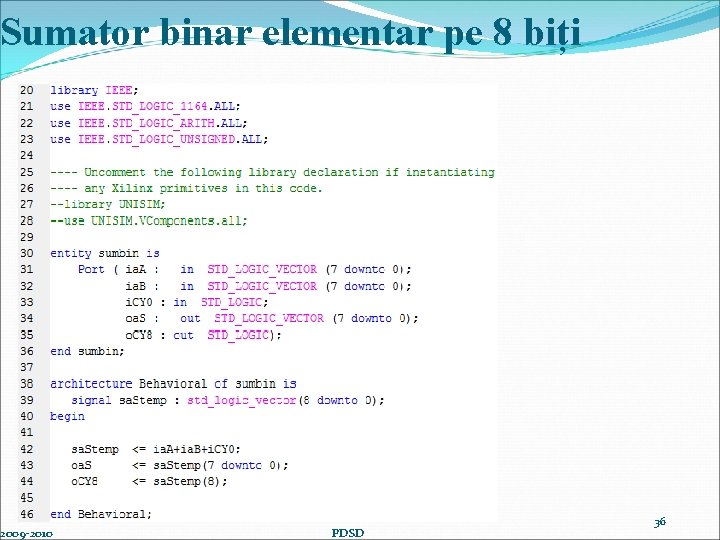

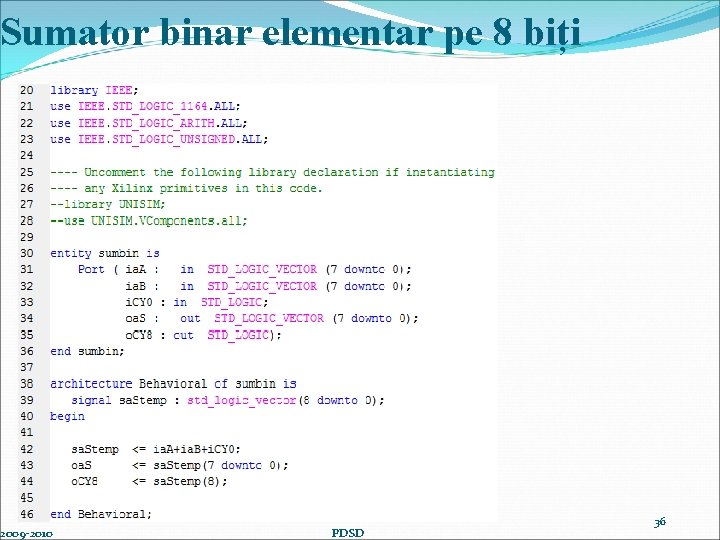

Sumator binar elementar pe 8 biți 2009 -2010 PDSD 36

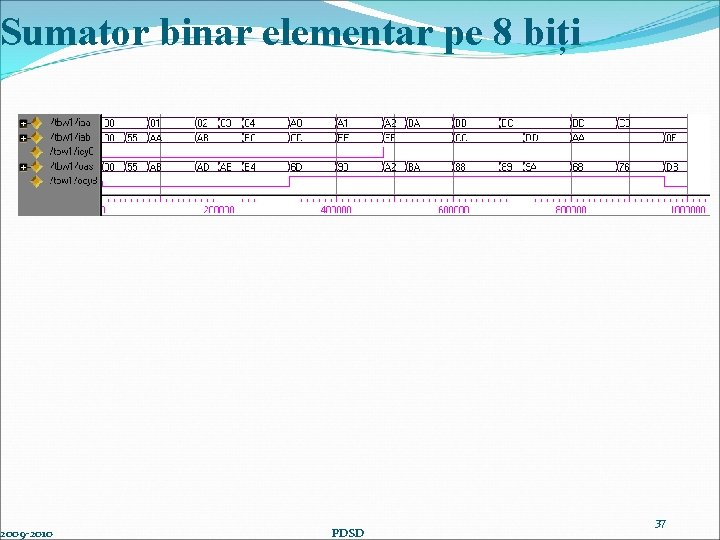

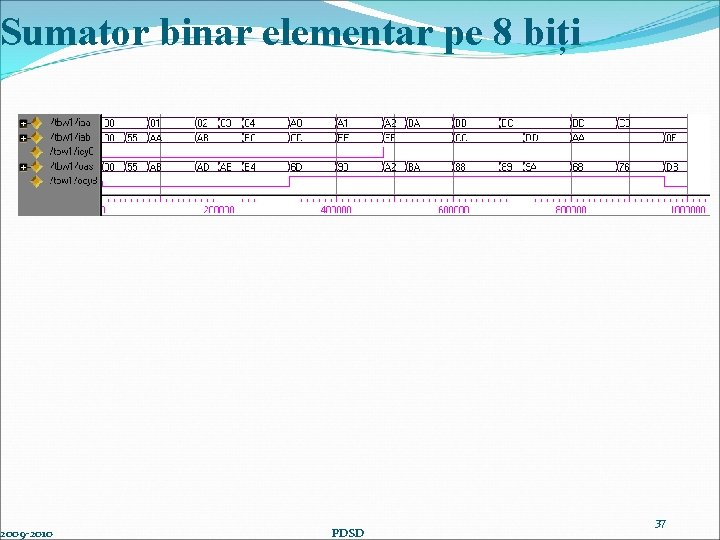

Sumator binar elementar pe 8 biți 2009 -2010 PDSD 37

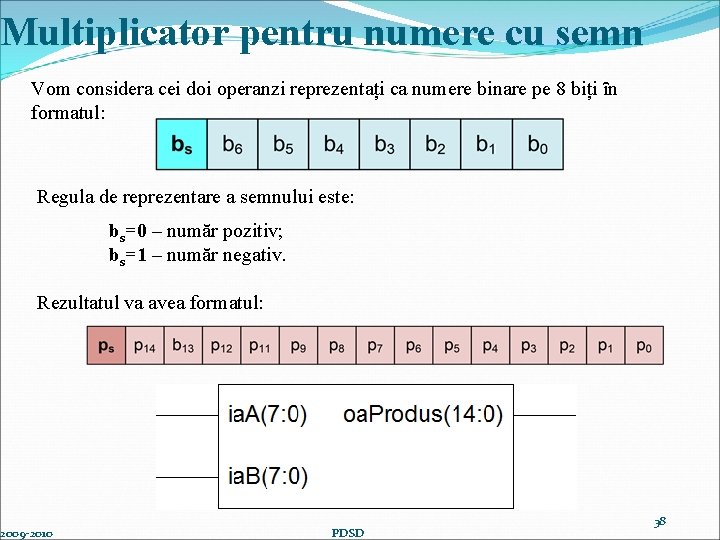

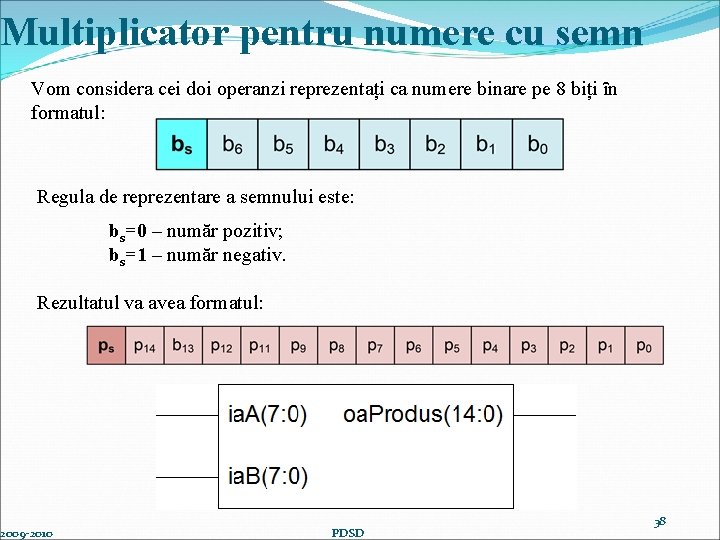

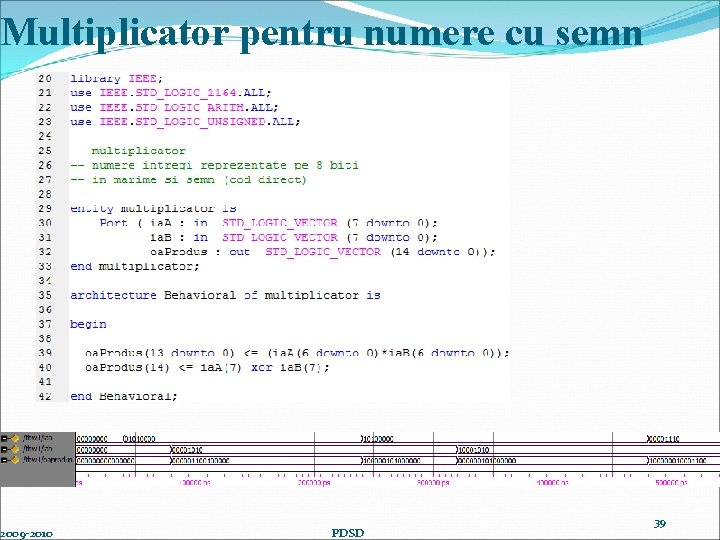

Multiplicator pentru numere cu semn Vom considera cei doi operanzi reprezentați ca numere binare pe 8 biți ȋn formatul: Regula de reprezentare a semnului este: bs=0 – număr pozitiv; bs=1 – număr negativ. Rezultatul va avea formatul: 2009 -2010 PDSD 38

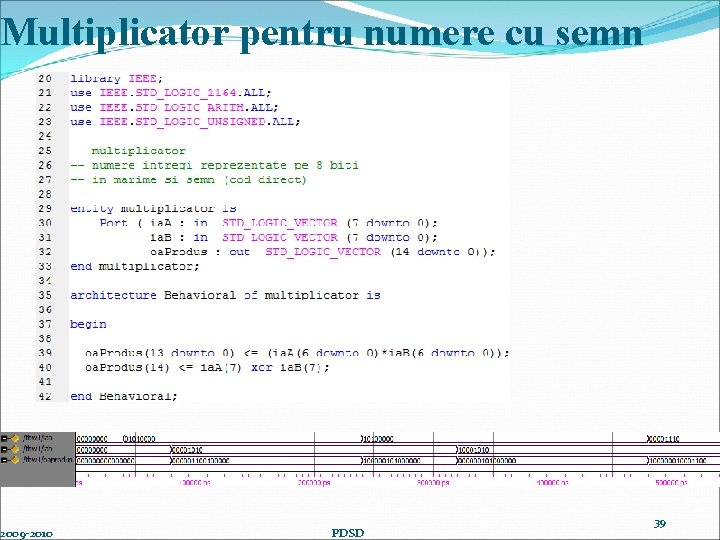

Multiplicator pentru numere cu semn 2009 -2010 PDSD 39

Intrebări ? 2010 Proiectarea sistemelor digitale 40