Analog to Digital Conversion u u Introduction Main

- Slides: 38

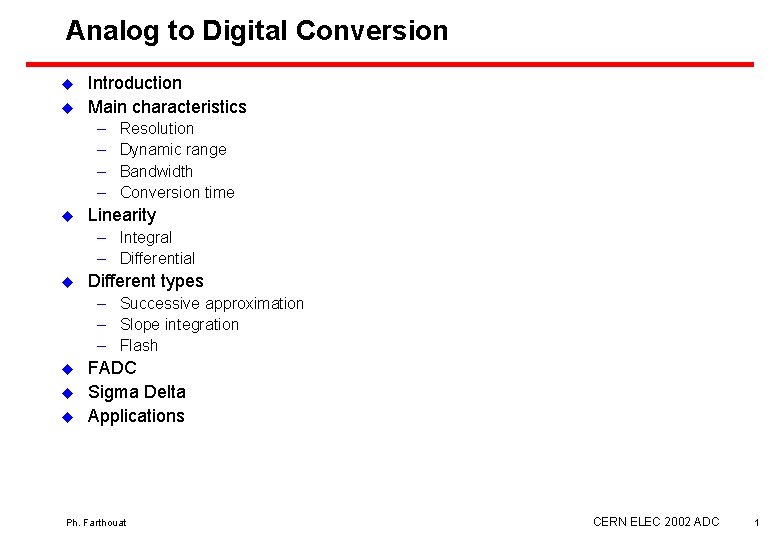

Analog to Digital Conversion u u Introduction Main characteristics – – u Resolution Dynamic range Bandwidth Conversion time Linearity – Integral – Differential u Different types – Successive approximation – Slope integration – Flash u u u FADC Sigma Delta Applications Ph. Farthouat CERN ELEC 2002 ADC 1

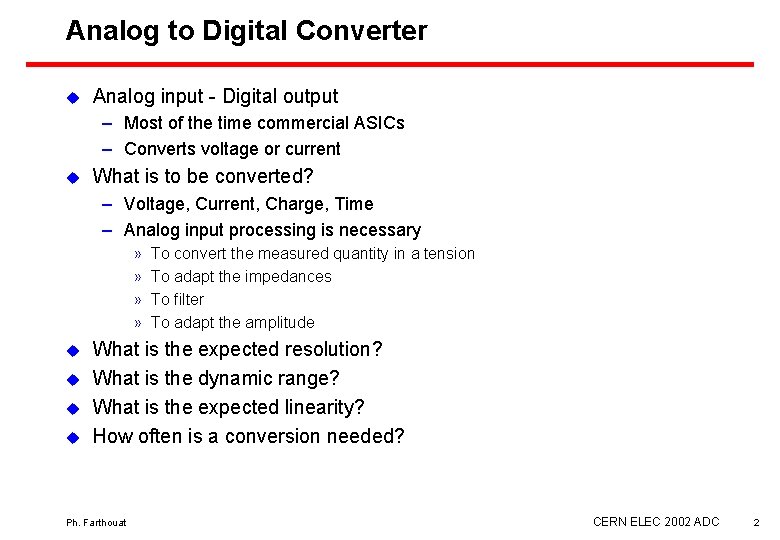

Analog to Digital Converter u Analog input - Digital output – Most of the time commercial ASICs – Converts voltage or current u What is to be converted? – Voltage, Current, Charge, Time – Analog input processing is necessary » » u u To convert the measured quantity in a tension To adapt the impedances To filter To adapt the amplitude What is the expected resolution? What is the dynamic range? What is the expected linearity? How often is a conversion needed? Ph. Farthouat CERN ELEC 2002 ADC 2

Resolution u u u An ADC is given as an n-bit ADC The least significant bit gives the resolution of the ADC Related to full scale if the ADC is linear – LSB = A/2 n – Linear 8 -bit ADC with a 1 V full scale input – Resolution = 1/28 = 3. 9 m. V (0. 39%) Ph. Farthouat CERN ELEC 2002 ADC 3

Dynamic range u Ratio between the minimum and the maximum amplitude to be measured – e. g. calorimeter signal 10 Me. V to 2 Te. V gives a 2 106 dynamic range u In case of linear system the dynamic range is related to the number of bits (and hence the resolution) – an 8 -bit ADC has a 256 dynamic range u In case of large dynamic range (as for a calorimeter) some nonlinearity has to be introduced – linear ADC for the previous example would require 21 bits! u Often used terms in physics: – n-bit resolution – n-bit dynamic range – example: » 8 -bit resolution for a 12 -bit dynamic range means that a signal in the range 14000 is measured with a resolution of 0. 39% Ph. Farthouat CERN ELEC 2002 ADC 4

Conversion time and Bandwidth u How often can a conversion be done – a few ns to a few ms depending on the technology » 100 MHz FADC to slow sigma-delta u Input bandwidth – Maximum input signal bandwidth » Track and hold input circuitry » Conversion frequency (FADC) Ph. Farthouat CERN ELEC 2002 ADC 5

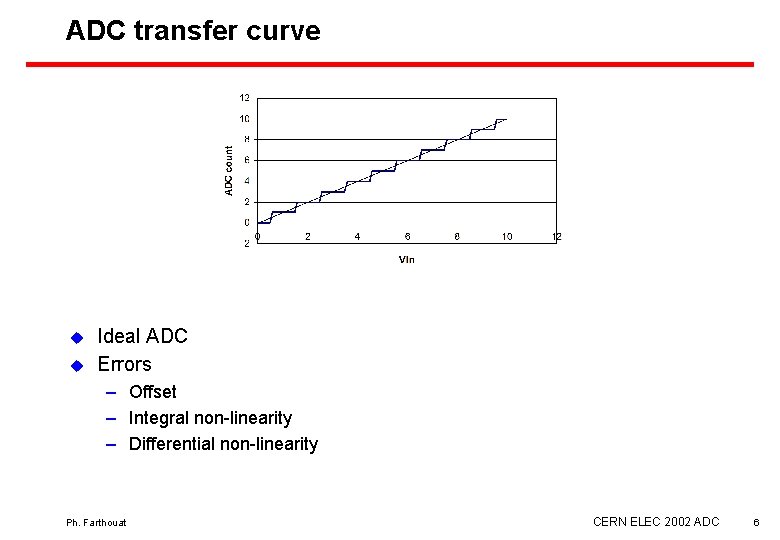

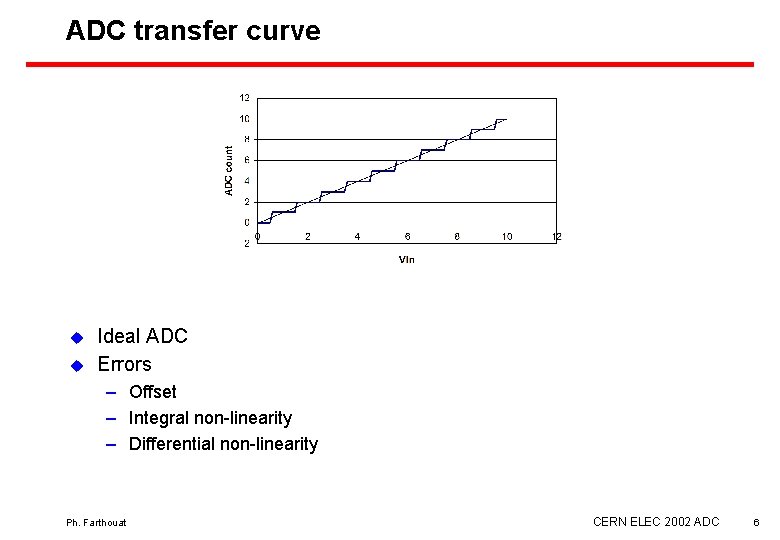

ADC transfer curve u u Ideal ADC Errors – Offset – Integral non-linearity – Differential non-linearity Ph. Farthouat CERN ELEC 2002 ADC 6

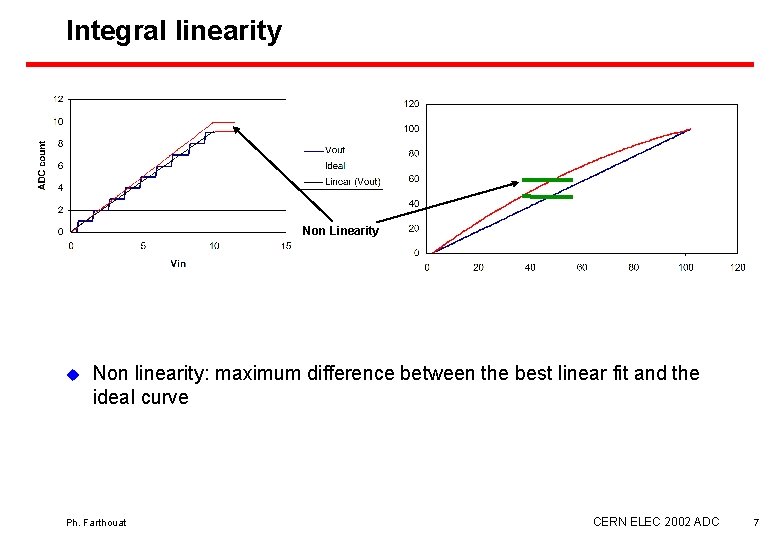

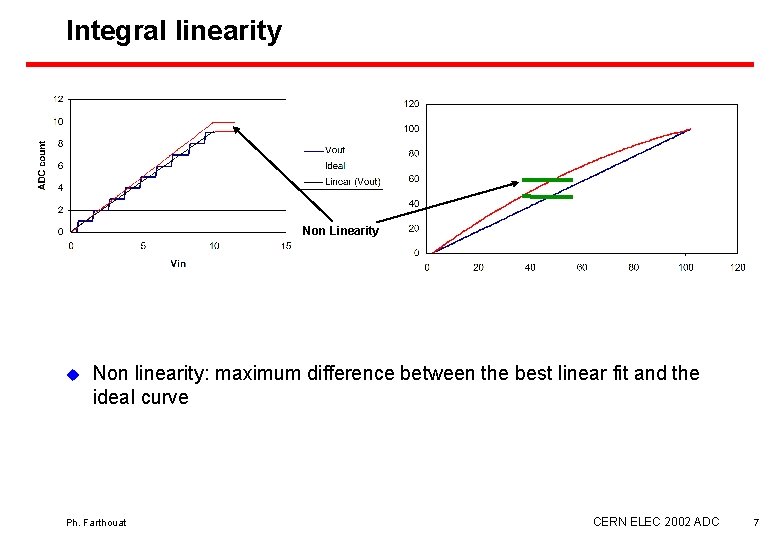

Integral linearity Non Linearity u Non linearity: maximum difference between the best linear fit and the ideal curve Ph. Farthouat CERN ELEC 2002 ADC 7

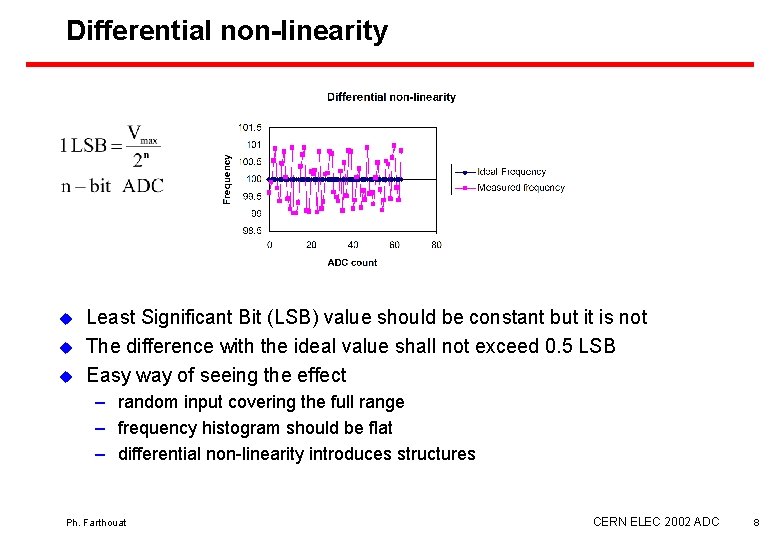

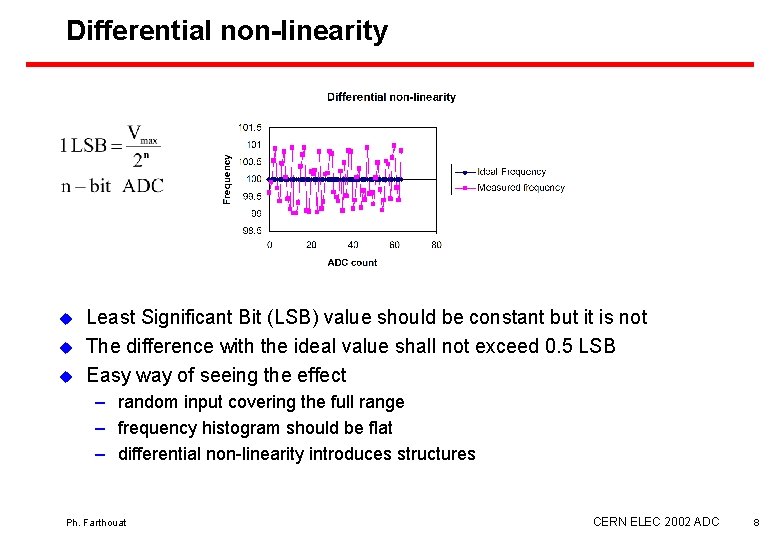

Differential non-linearity u u u Least Significant Bit (LSB) value should be constant but it is not The difference with the ideal value shall not exceed 0. 5 LSB Easy way of seeing the effect – random input covering the full range – frequency histogram should be flat – differential non-linearity introduces structures Ph. Farthouat CERN ELEC 2002 ADC 8

Types of ADC u u u Successive approximation Single slope integration Dual slope integration Flash ADC Sigma-Delta Ph. Farthouat CERN ELEC 2002 ADC 9

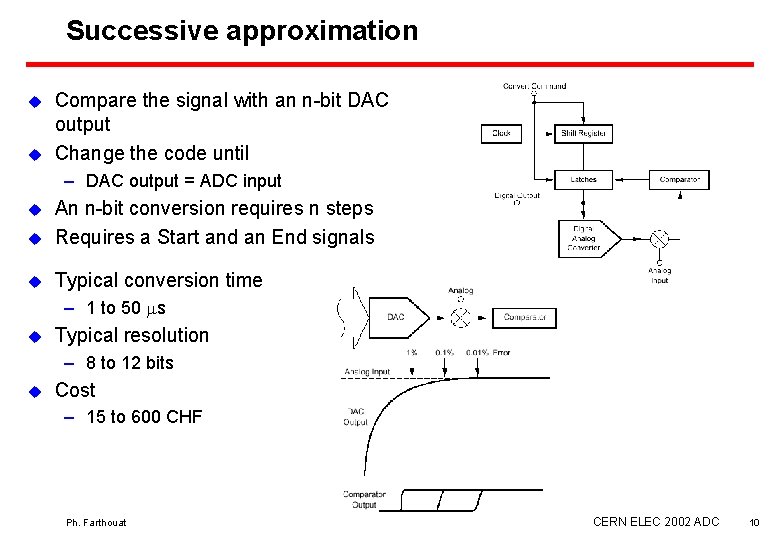

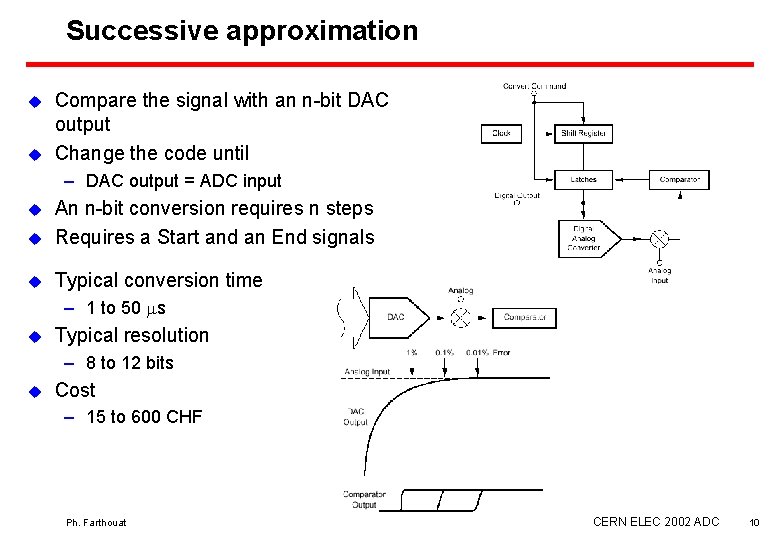

Successive approximation u u Compare the signal with an n-bit DAC output Change the code until – DAC output = ADC input u An n-bit conversion requires n steps Requires a Start and an End signals u Typical conversion time u – 1 to 50 ms u Typical resolution – 8 to 12 bits u Cost – 15 to 600 CHF Ph. Farthouat CERN ELEC 2002 ADC 10

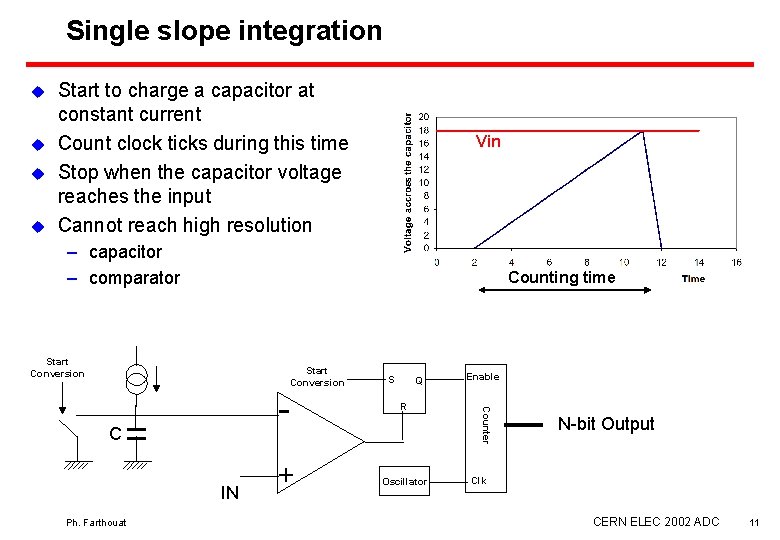

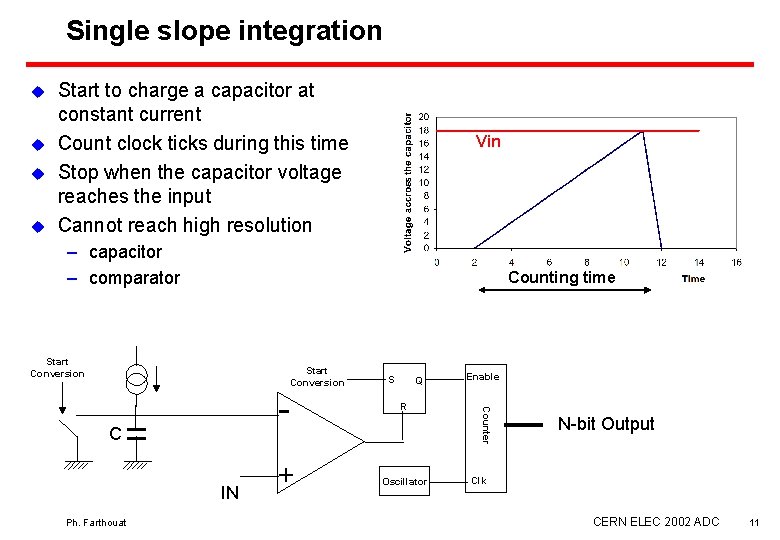

Single slope integration u u Start to charge a capacitor at constant current Count clock ticks during this time Stop when the capacitor voltage reaches the input Cannot reach high resolution Vin – capacitor – comparator Counting time Start Conversion C IN Ph. Farthouat + Q R Oscillator Enable Counter - S N-bit Output Clk CERN ELEC 2002 ADC 11

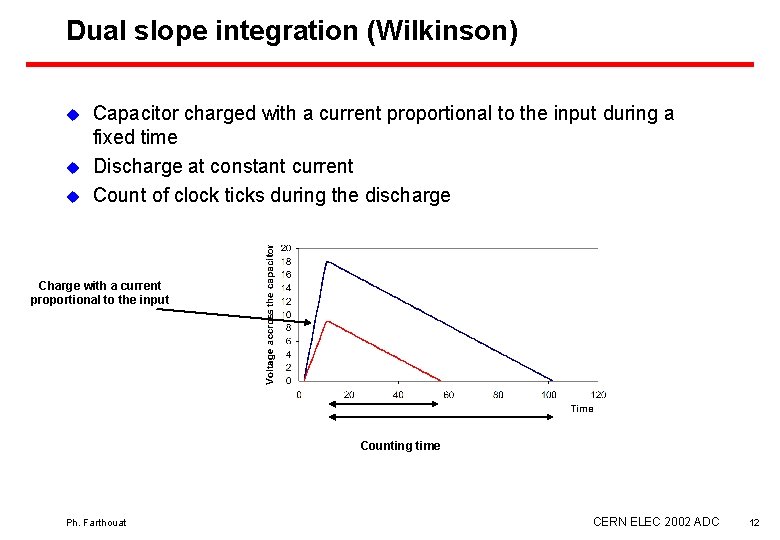

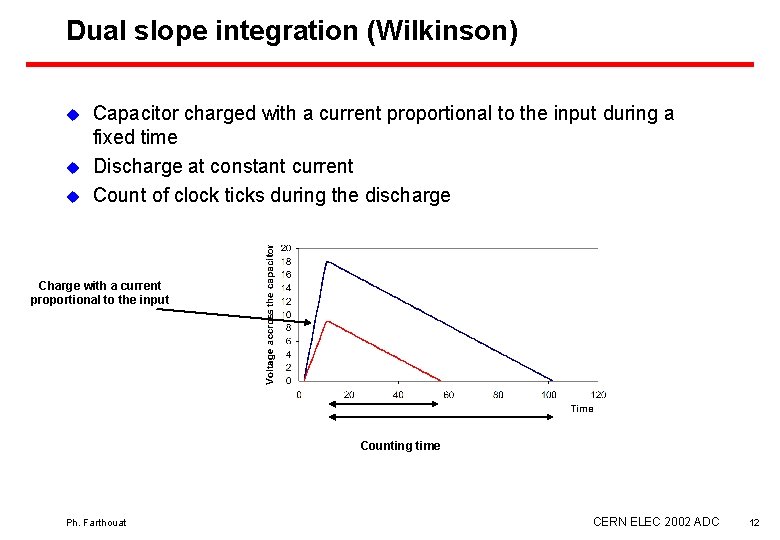

Dual slope integration (Wilkinson) u u u Capacitor charged with a current proportional to the input during a fixed time Discharge at constant current Count of clock ticks during the discharge Charge with a current proportional to the input Counting time Ph. Farthouat CERN ELEC 2002 ADC 12

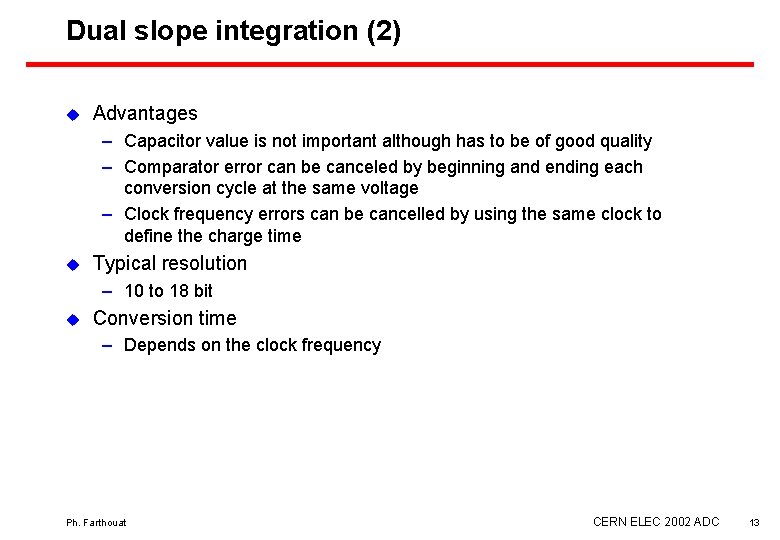

Dual slope integration (2) u Advantages – Capacitor value is not important although has to be of good quality – Comparator error can be canceled by beginning and ending each conversion cycle at the same voltage – Clock frequency errors can be cancelled by using the same clock to define the charge time u Typical resolution – 10 to 18 bit u Conversion time – Depends on the clock frequency Ph. Farthouat CERN ELEC 2002 ADC 13

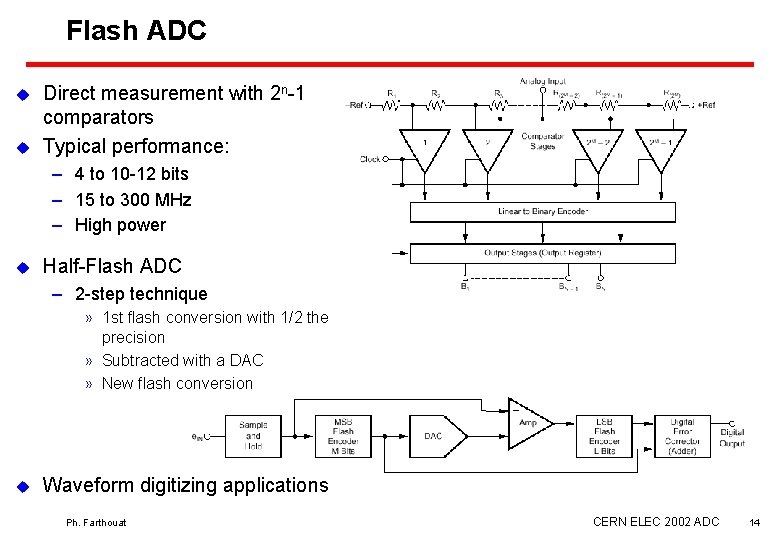

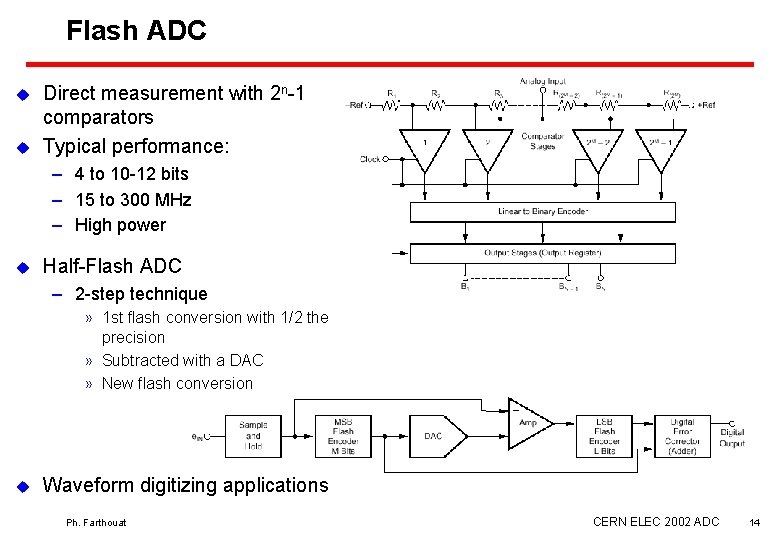

Flash ADC u u Direct measurement with 2 n-1 comparators Typical performance: – 4 to 10 -12 bits – 15 to 300 MHz – High power u Half-Flash ADC – 2 -step technique » 1 st flash conversion with 1/2 the precision » Subtracted with a DAC » New flash conversion u Waveform digitizing applications Ph. Farthouat CERN ELEC 2002 ADC 14

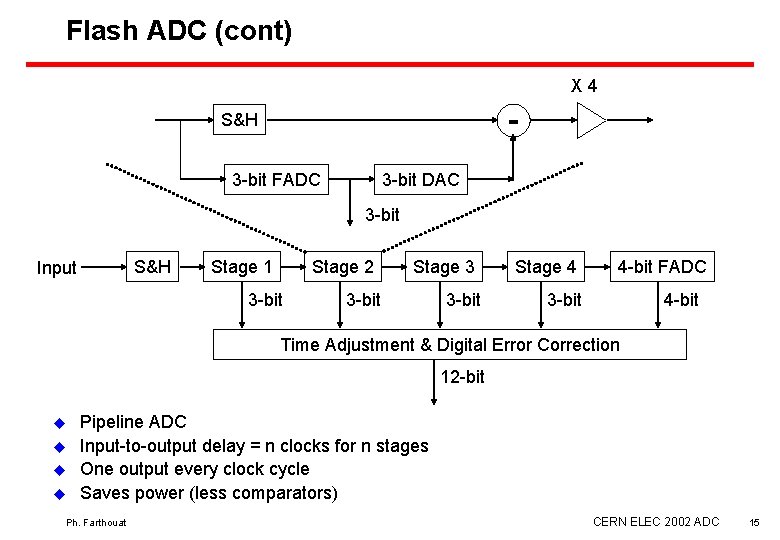

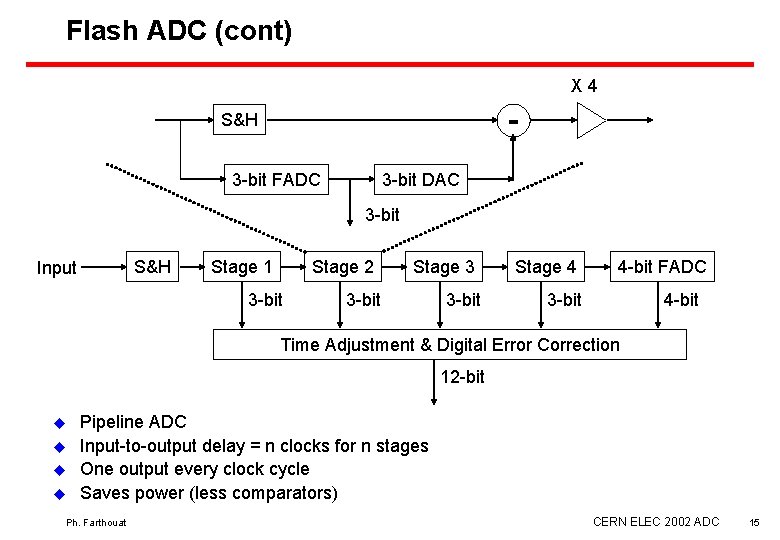

Flash ADC (cont) X 4 - S&H 3 -bit FADC 3 -bit DAC 3 -bit S&H Input Stage 1 Stage 2 3 -bit Stage 3 3 -bit Stage 4 4 -bit FADC 3 -bit 4 -bit Time Adjustment & Digital Error Correction 12 -bit u u Pipeline ADC Input-to-output delay = n clocks for n stages One output every clock cycle Saves power (less comparators) Ph. Farthouat CERN ELEC 2002 ADC 15

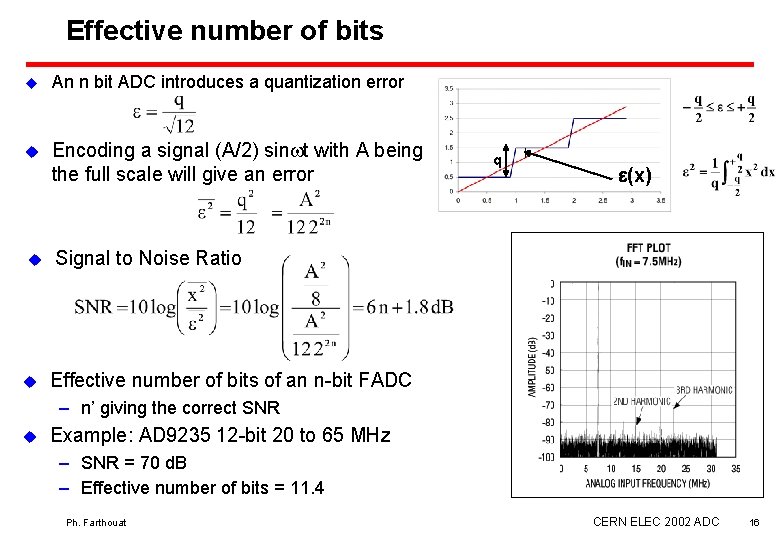

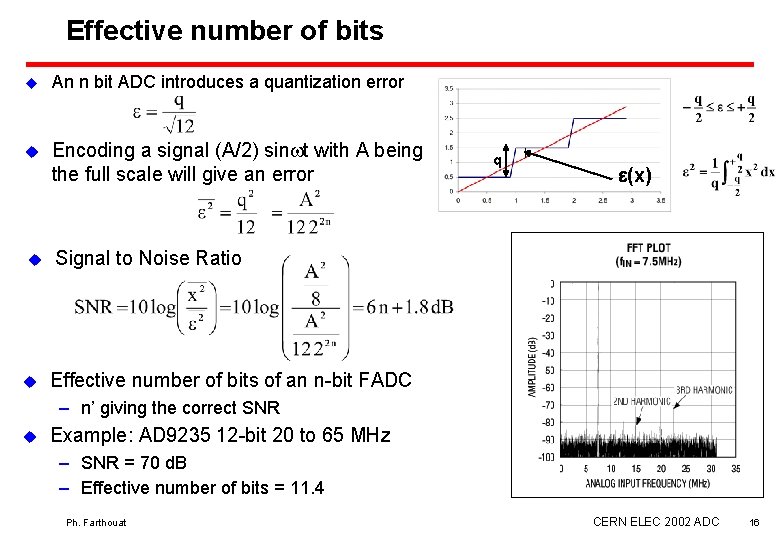

Effective number of bits u An n bit ADC introduces a quantization error u Encoding a signal (A/2) sinwt with A being the full scale will give an error u u q e(x) Signal to Noise Ratio Effective number of bits of an n-bit FADC – n’ giving the correct SNR u Example: AD 9235 12 -bit 20 to 65 MHz – SNR = 70 d. B – Effective number of bits = 11. 4 Ph. Farthouat CERN ELEC 2002 ADC 16

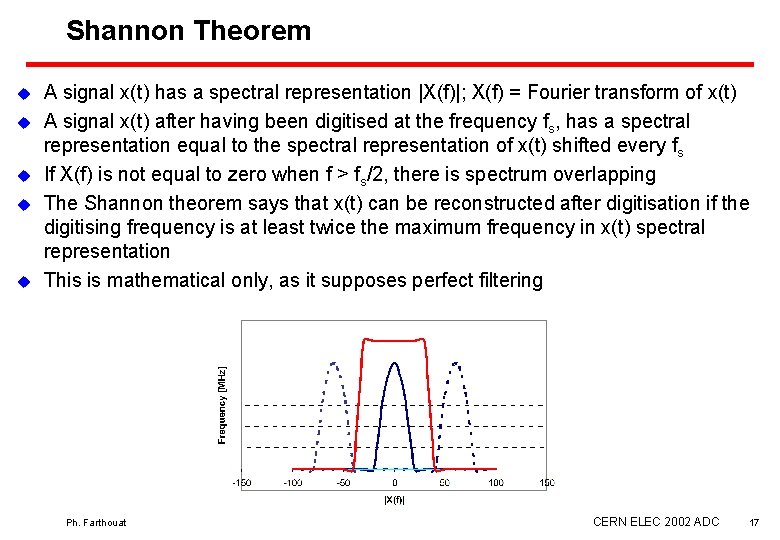

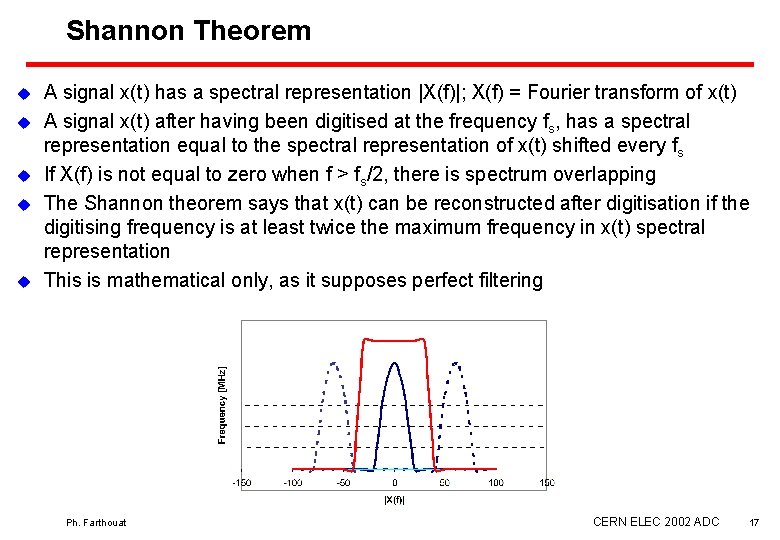

Shannon Theorem u u u A signal x(t) has a spectral representation |X(f)|; X(f) = Fourier transform of x(t) A signal x(t) after having been digitised at the frequency fs, has a spectral representation equal to the spectral representation of x(t) shifted every fs If X(f) is not equal to zero when f > fs/2, there is spectrum overlapping The Shannon theorem says that x(t) can be reconstructed after digitisation if the digitising frequency is at least twice the maximum frequency in x(t) spectral representation This is mathematical only, as it supposes perfect filtering Ph. Farthouat CERN ELEC 2002 ADC 17

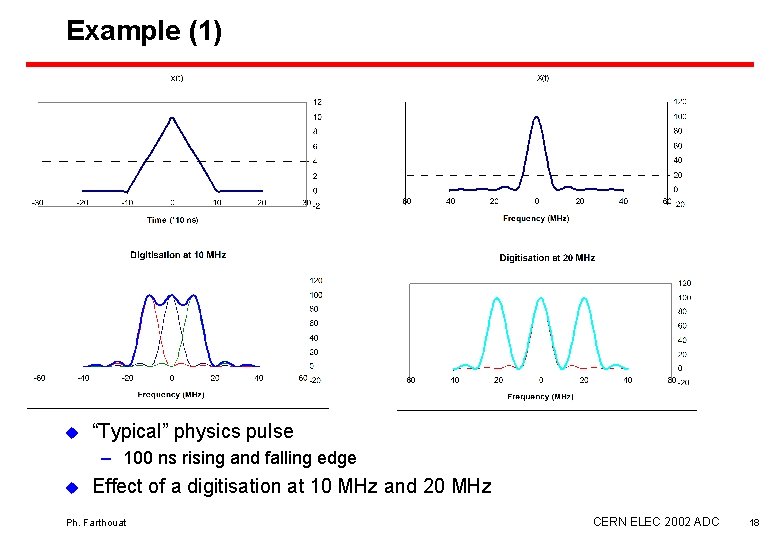

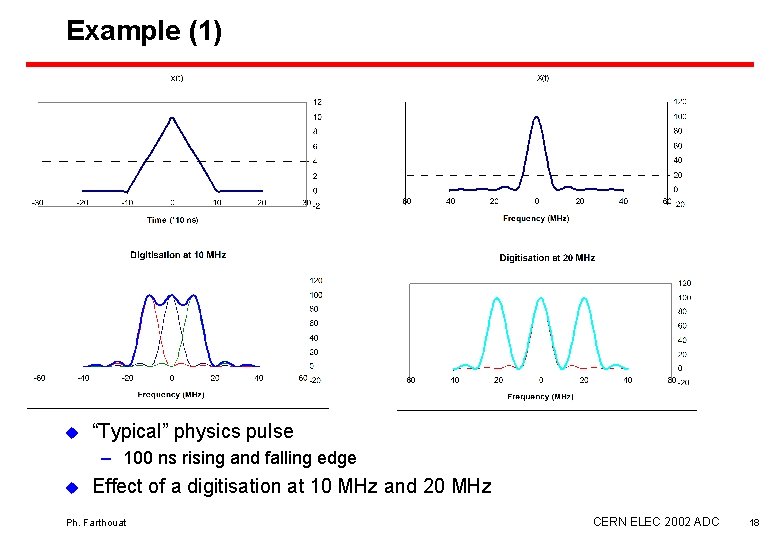

Example (1) u “Typical” physics pulse – 100 ns rising and falling edge u Effect of a digitisation at 10 MHz and 20 MHz Ph. Farthouat CERN ELEC 2002 ADC 18

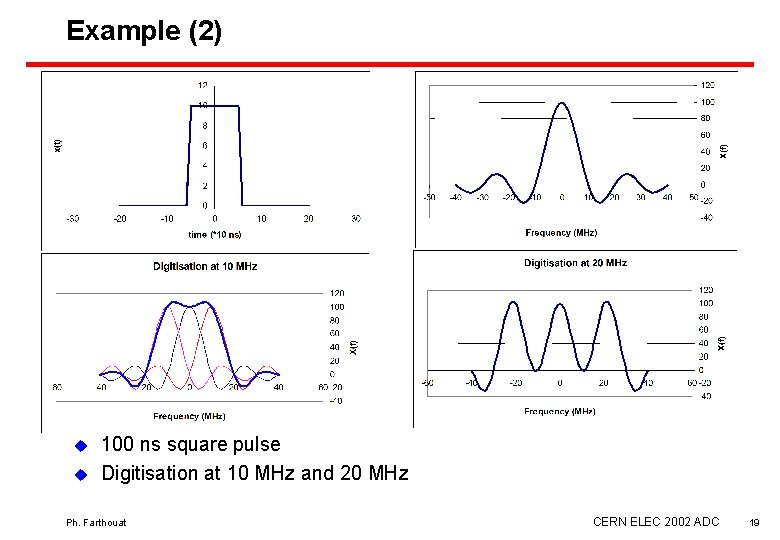

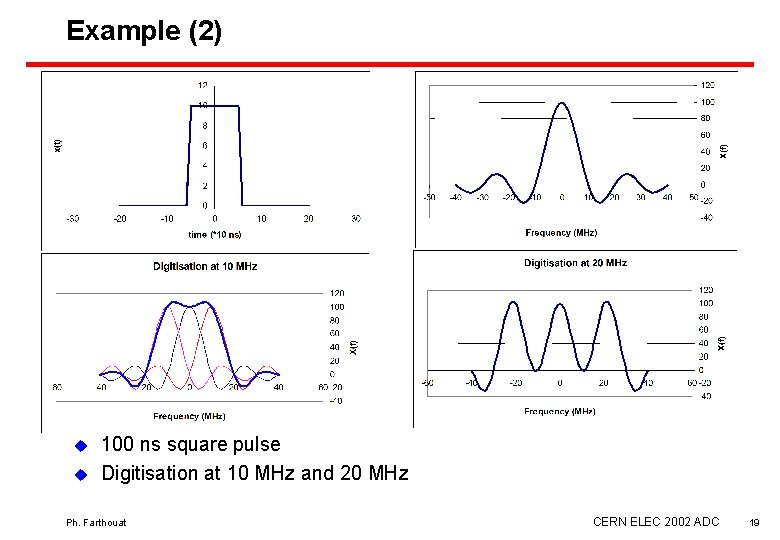

Example (2) u u 100 ns square pulse Digitisation at 10 MHz and 20 MHz Ph. Farthouat CERN ELEC 2002 ADC 19

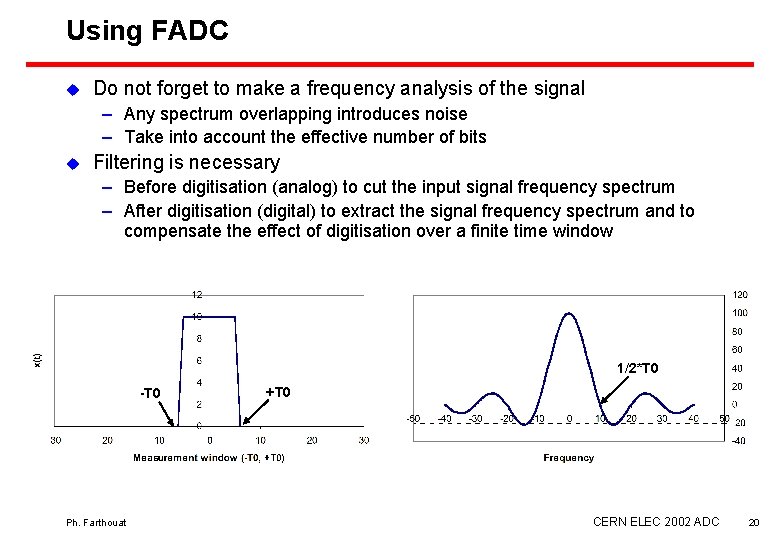

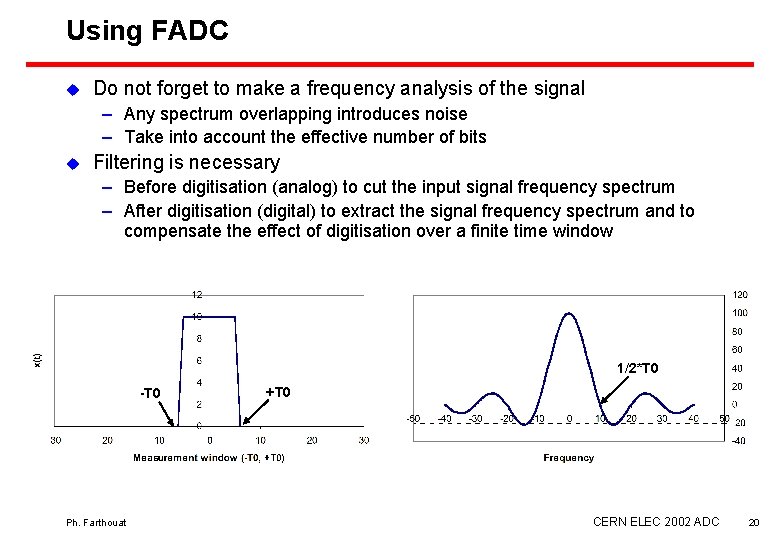

Using FADC u Do not forget to make a frequency analysis of the signal – Any spectrum overlapping introduces noise – Take into account the effective number of bits u Filtering is necessary – Before digitisation (analog) to cut the input signal frequency spectrum – After digitisation (digital) to extract the signal frequency spectrum and to compensate the effect of digitisation over a finite time window 1/2*T 0 -T 0 Ph. Farthouat +T 0 CERN ELEC 2002 ADC 20

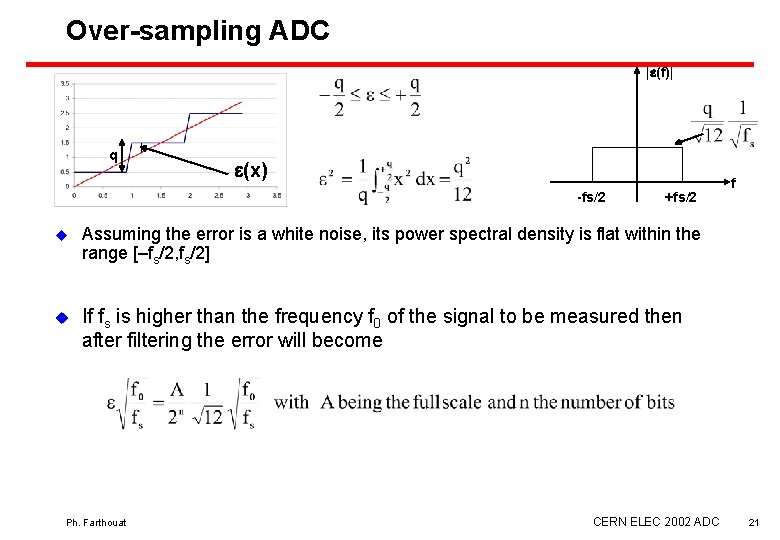

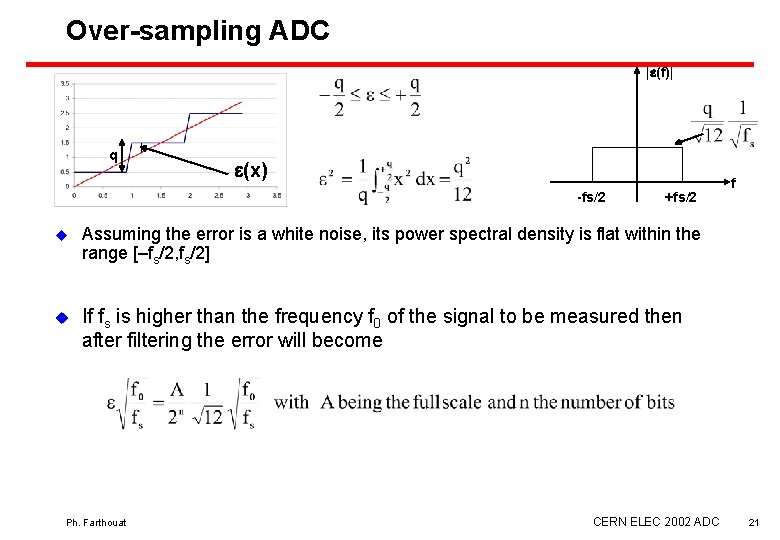

Over-sampling ADC |e(f)| q e(x) -fs/2 +fs/2 u Assuming the error is a white noise, its power spectral density is flat within the range [–fs/2, fs/2] u If fs is higher than the frequency f 0 of the signal to be measured then after filtering the error will become Ph. Farthouat CERN ELEC 2002 ADC f 21

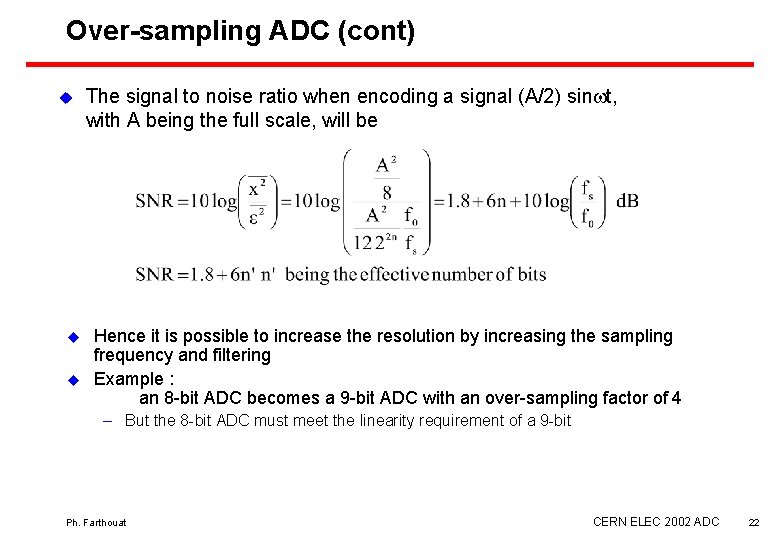

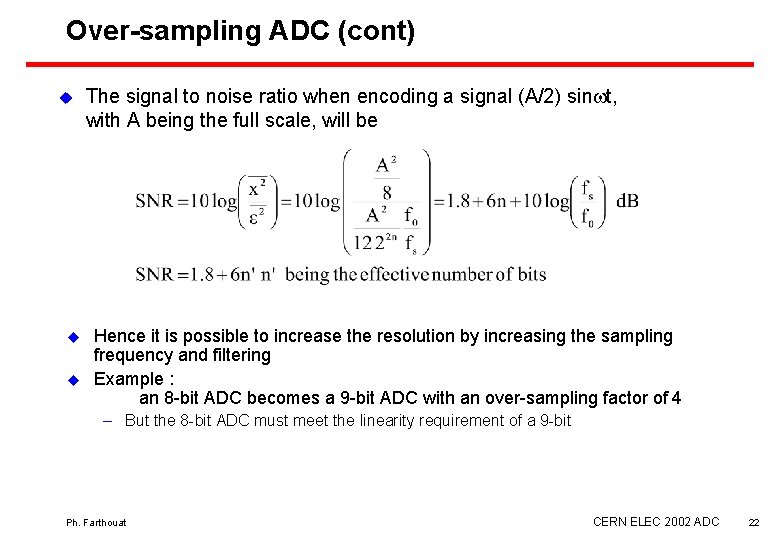

Over-sampling ADC (cont) u u u The signal to noise ratio when encoding a signal (A/2) sinwt, with A being the full scale, will be Hence it is possible to increase the resolution by increasing the sampling frequency and filtering Example : an 8 -bit ADC becomes a 9 -bit ADC with an over-sampling factor of 4 – But the 8 -bit ADC must meet the linearity requirement of a 9 -bit Ph. Farthouat CERN ELEC 2002 ADC 22

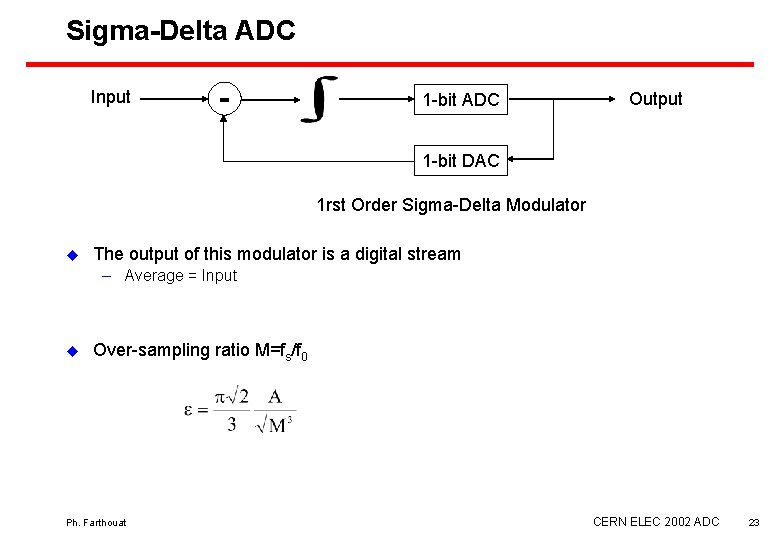

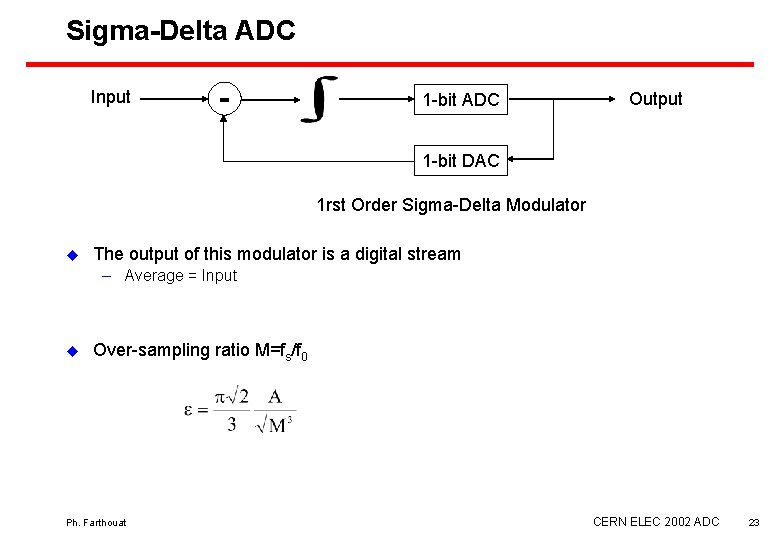

Sigma-Delta ADC Input - 1 -bit ADC Output 1 -bit DAC 1 rst Order Sigma-Delta Modulator u The output of this modulator is a digital stream – Average = Input u Over-sampling ratio M=fs/f 0 Ph. Farthouat CERN ELEC 2002 ADC 23

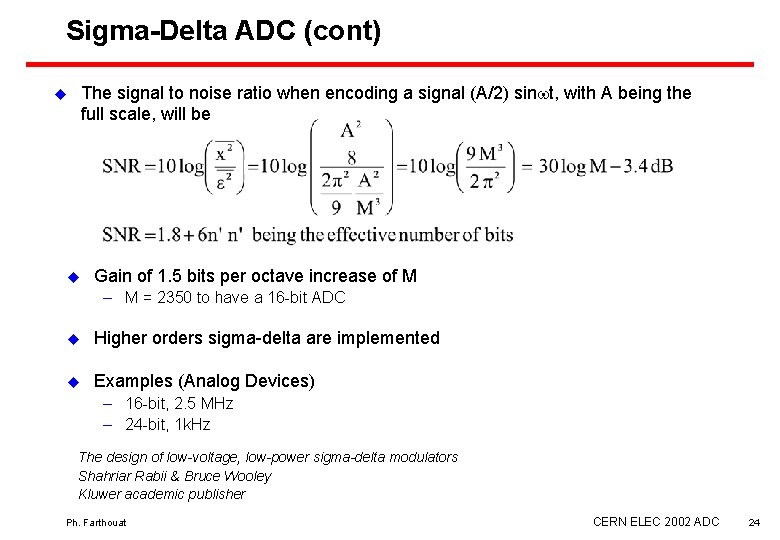

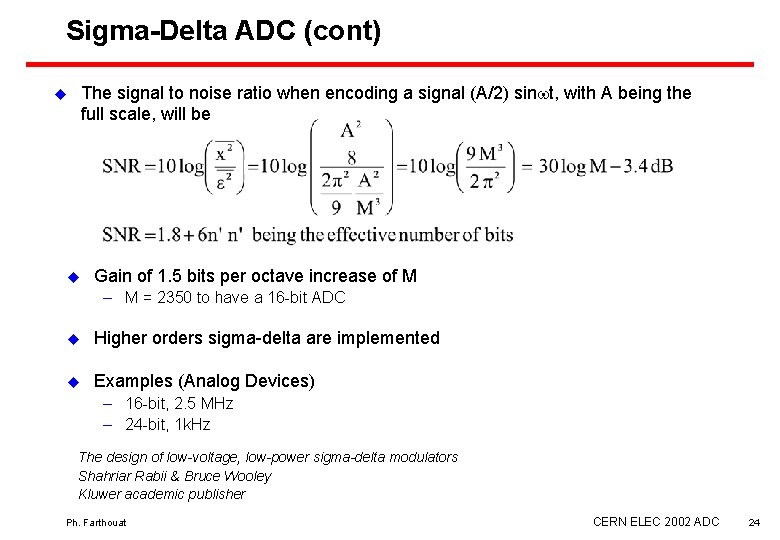

Sigma-Delta ADC (cont) The signal to noise ratio when encoding a signal (A/2) sinwt, with A being the full scale, will be u u Gain of 1. 5 bits per octave increase of M – M = 2350 to have a 16 -bit ADC u Higher orders sigma-delta are implemented u Examples (Analog Devices) – 16 -bit, 2. 5 MHz – 24 -bit, 1 k. Hz The design of low-voltage, low-power sigma-delta modulators Shahriar Rabii & Bruce Wooley Kluwer academic publisher Ph. Farthouat CERN ELEC 2002 ADC 24

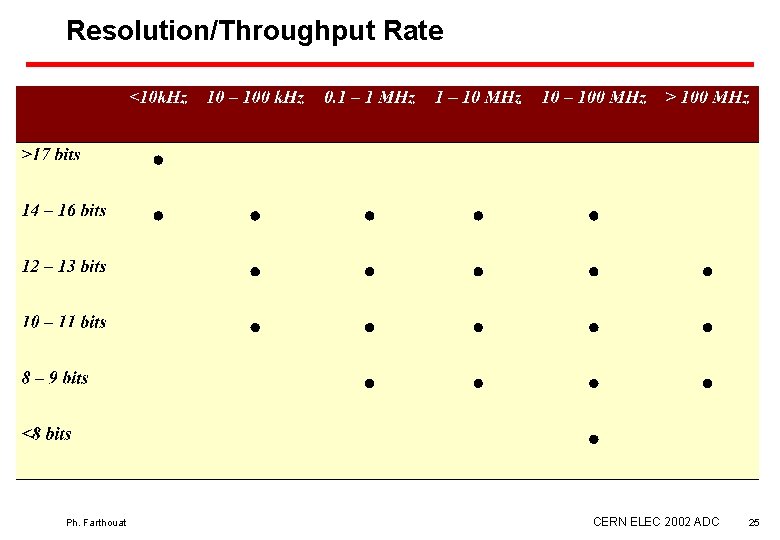

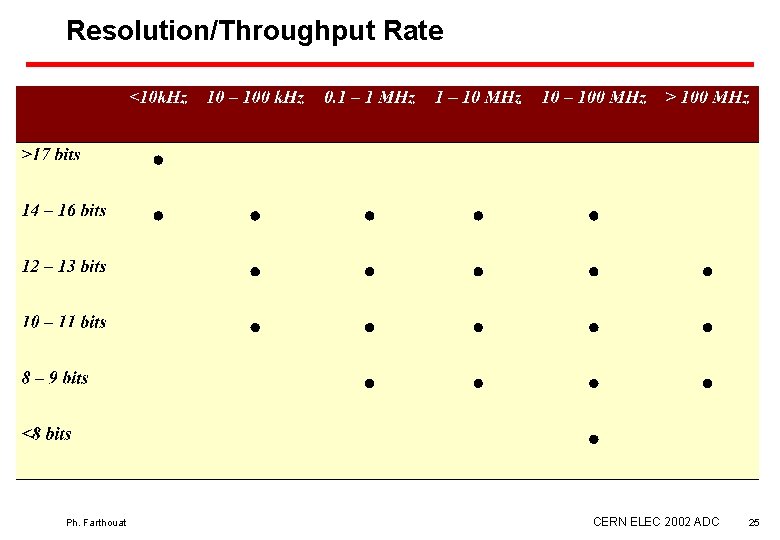

Resolution/Throughput Rate Ph. Farthouat CERN ELEC 2002 ADC 25

Power u u Power is going down Examples – 8 -bit, 200 MSPS: 1. 3 m. W/MSPS – 10 -bit, 10 MSPS core used in ALICE TPC read-out: <20 m. W – 24 -bit, 1 k. SPS: 45 m. W Ph. Farthouat CERN ELEC 2002 ADC 26

Applications u u In HEP we are facing large number of channels The quantity to be measured depends on the type of detector – Charge in the case of a lead glass calorimeter with PM read-out – Voltage in the case of a lead glass calorimeter with triode and preamplifier shaper read-out u u Low cost Charge integrating ADC for a LEP calorimeter High speed peak sensing ADC for a neutrino experiment Non linear ADC for an LHC experiment FADC with numerical filtering for an LHC trigger application Ph. Farthouat CERN ELEC 2002 ADC 27

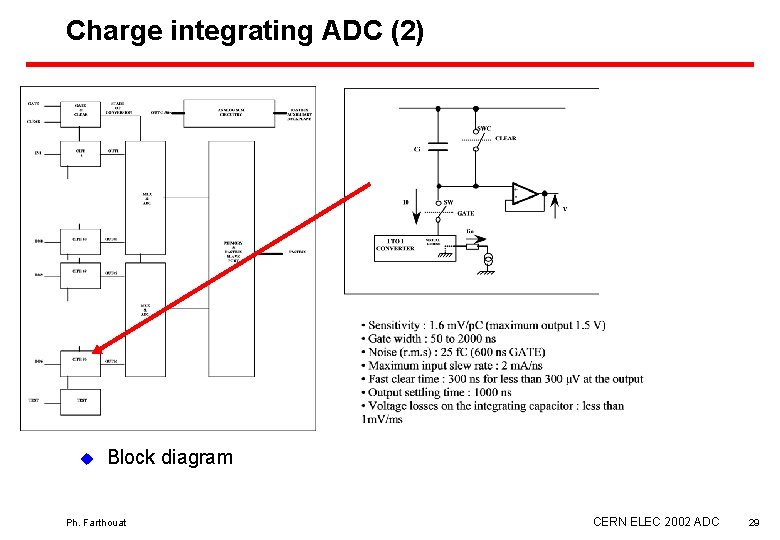

Charge integrating ADC (1) u u u High resolution: 12 -bit High dynamic range: 15 -bit High density: 96 channel per Fastbus board Low speed: 1 ms conversion time Low cost per channel Principle: – Single ADC for 48 channels – Charge input integration and storage Ph. Farthouat CERN ELEC 2002 ADC 28

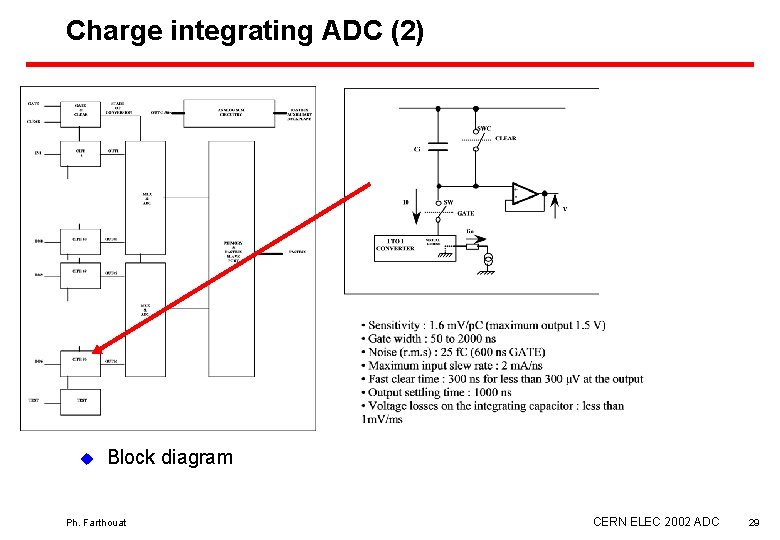

Charge integrating ADC (2) u Block diagram Ph. Farthouat CERN ELEC 2002 ADC 29

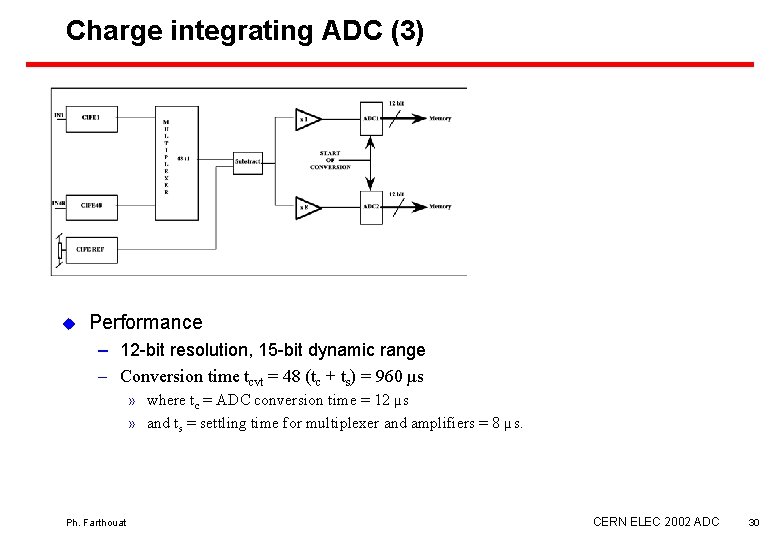

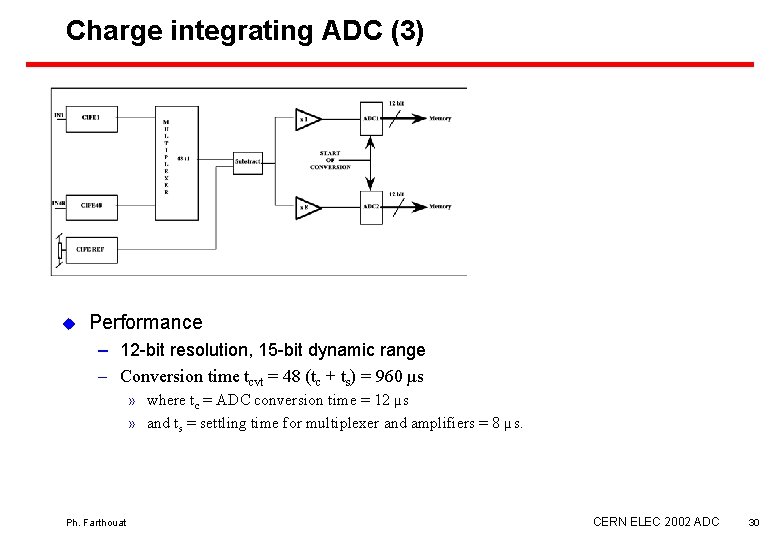

Charge integrating ADC (3) u Performance – 12 -bit resolution, 15 -bit dynamic range – Conversion time tcvt = 48 (tc + ts) = 960 µs » where tc = ADC conversion time = 12 µs » and ts = settling time for multiplexer and amplifiers = 8 µs. Ph. Farthouat CERN ELEC 2002 ADC 30

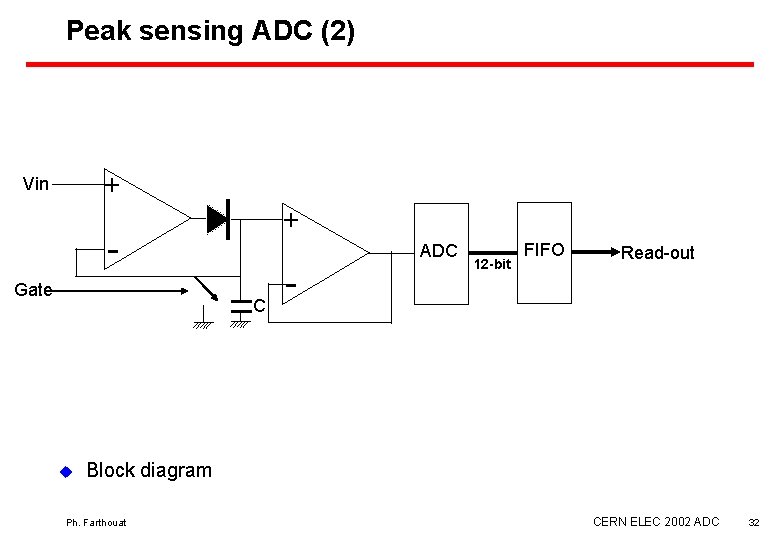

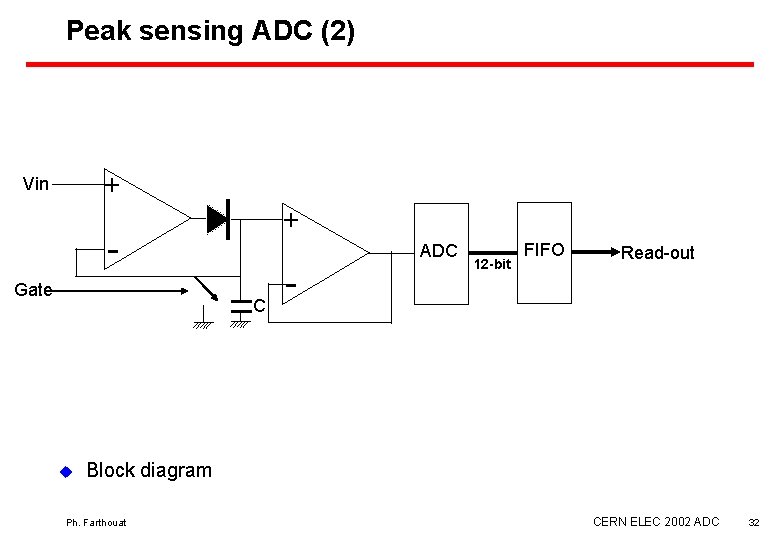

Peak sensing ADC (1) u u u 12 -bit resolution Low dead-time : 8 ms Data buffering Ph. Farthouat CERN ELEC 2002 ADC 31

Peak sensing ADC (2) + Vin + Gate ADC C u - 12 -bit FIFO Read-out Block diagram Ph. Farthouat CERN ELEC 2002 ADC 32

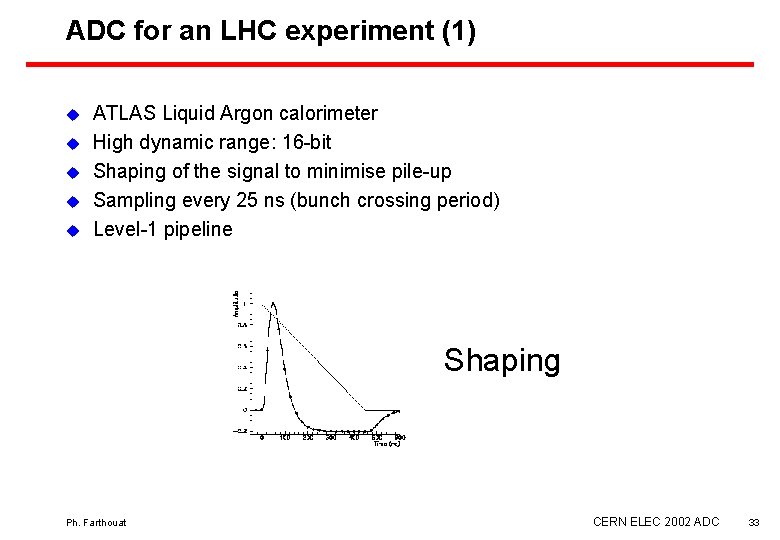

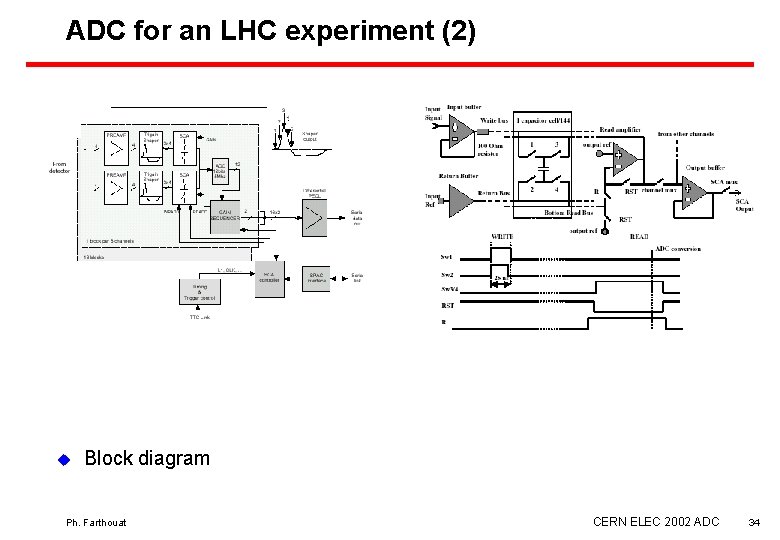

ADC for an LHC experiment (1) u u u ATLAS Liquid Argon calorimeter High dynamic range: 16 -bit Shaping of the signal to minimise pile-up Sampling every 25 ns (bunch crossing period) Level-1 pipeline Shaping Ph. Farthouat CERN ELEC 2002 ADC 33

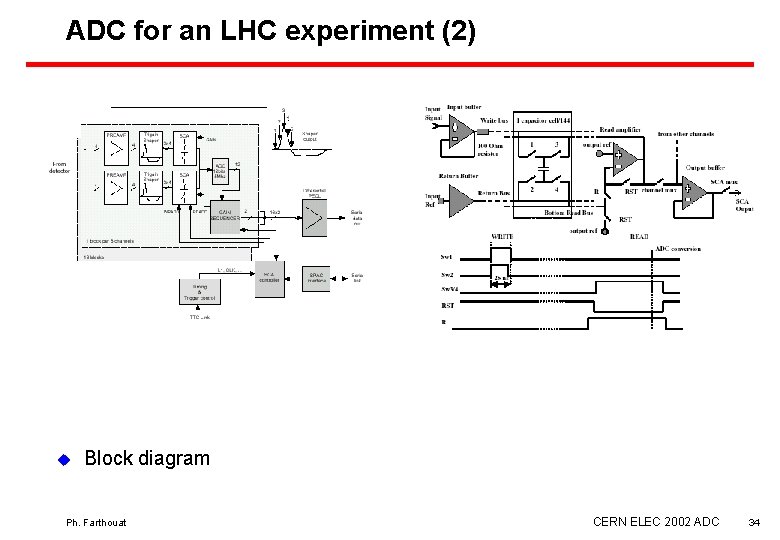

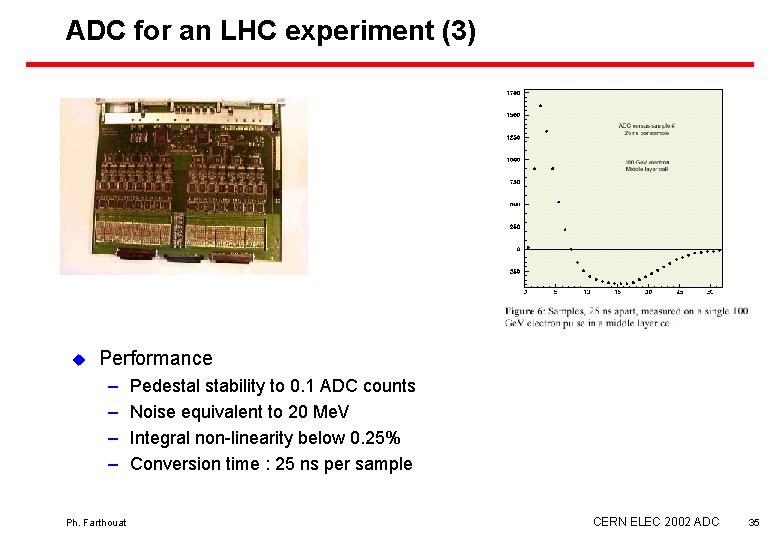

ADC for an LHC experiment (2) u Block diagram Ph. Farthouat CERN ELEC 2002 ADC 34

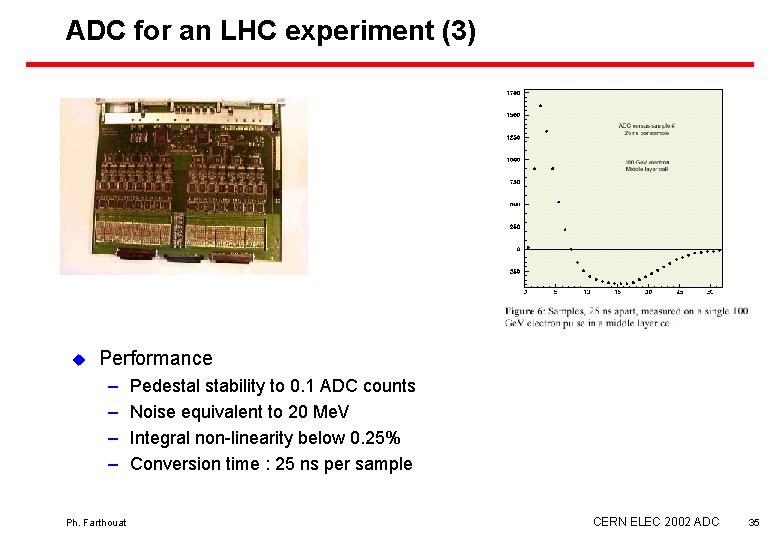

ADC for an LHC experiment (3) u Performance – – Ph. Farthouat Pedestal stability to 0. 1 ADC counts Noise equivalent to 20 Me. V Integral non-linearity below 0. 25% Conversion time : 25 ns per sample CERN ELEC 2002 ADC 35

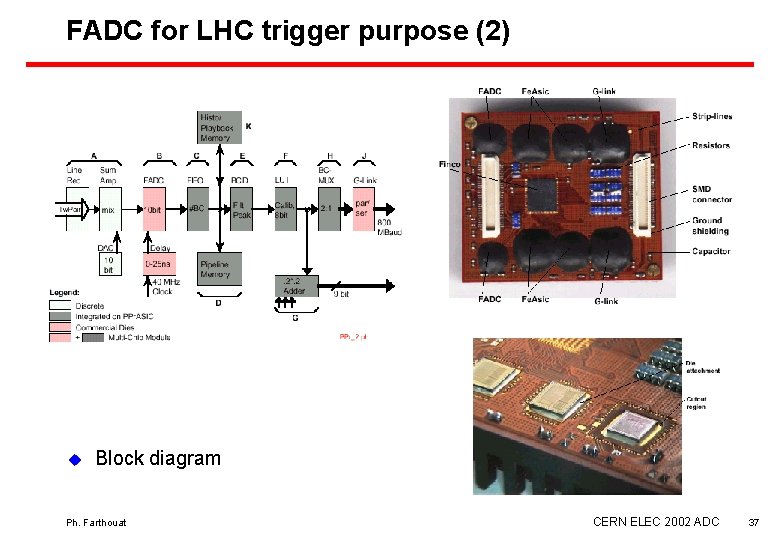

FADC for LHC trigger purpose (1) u u u Analog summation on the detector to form the trigger tower Shaping time covers several bunch crossings FADC and numerical filtering to: – Extract the energy – Extract the bunch crossing responsible for it Ph. Farthouat CERN ELEC 2002 ADC 36

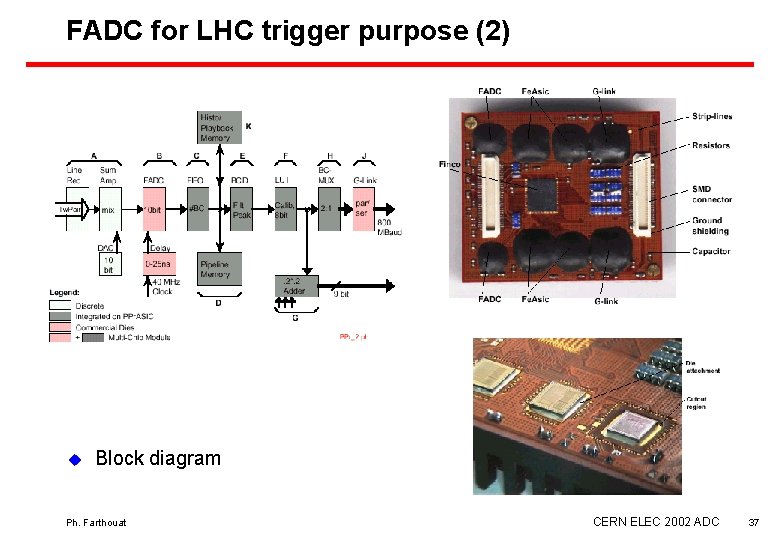

FADC for LHC trigger purpose (2) u Block diagram Ph. Farthouat CERN ELEC 2002 ADC 37

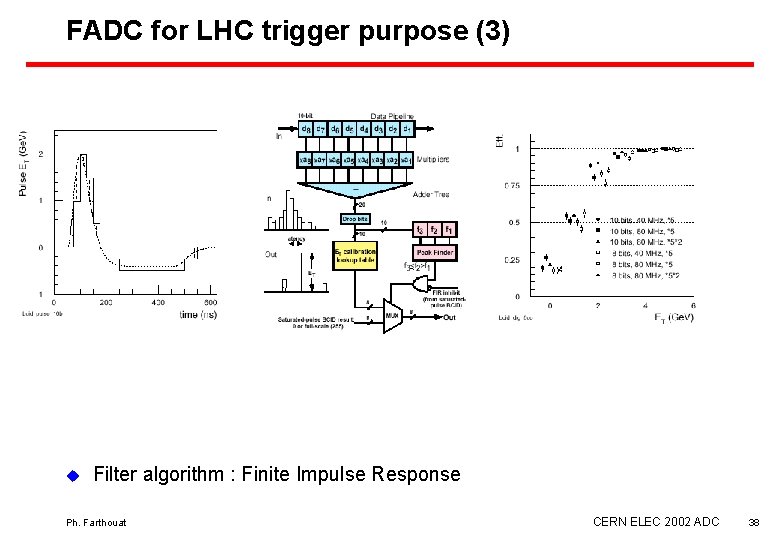

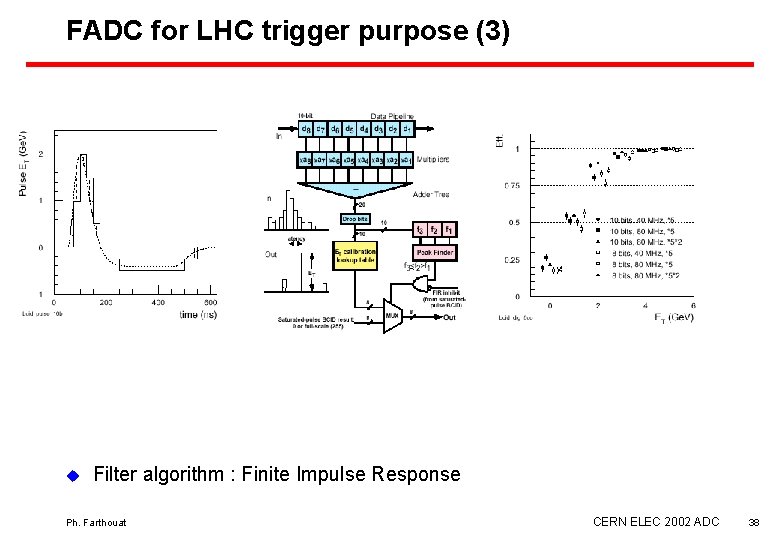

FADC for LHC trigger purpose (3) u Filter algorithm : Finite Impulse Response Ph. Farthouat CERN ELEC 2002 ADC 38