Quiz 2 FLIPFLOP SR Flip Flop Set Reset

- Slides: 18

Quiz 2 FLIP-FLOP

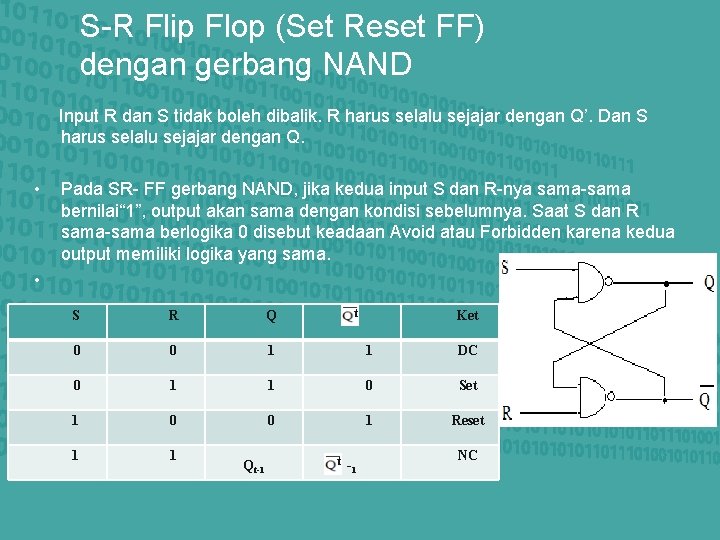

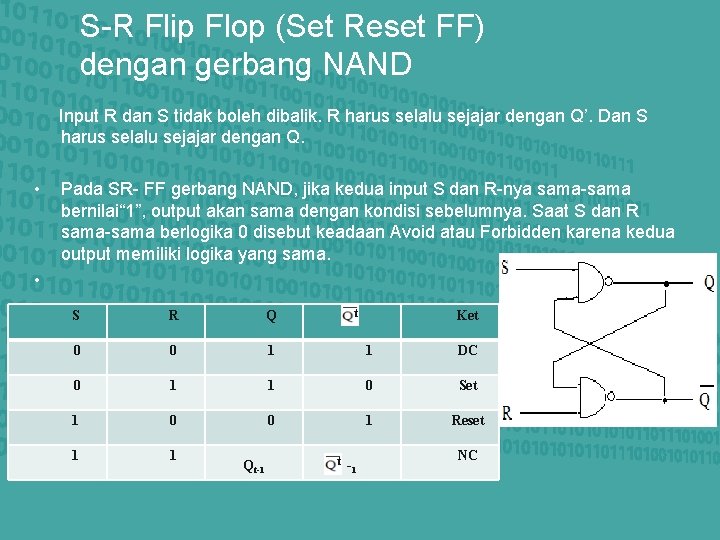

S-R Flip Flop (Set Reset FF) dengan gerbang NAND Input R dan S tidak boleh dibalik. R harus selalu sejajar dengan Q’. Dan S harus selalu sejajar dengan Q. • Pada SR- FF gerbang NAND, jika kedua input S dan R-nya sama-sama bernilai“ 1”, output akan sama dengan kondisi sebelumnya. Saat S dan R sama-sama berlogika 0 disebut keadaan Avoid atau Forbidden karena kedua output memiliki logika yang sama. • t S R Q 0 0 1 1 DC 0 1 1 0 Set 1 0 0 1 Reset 1 1 Qt-1 t 1 Ket NC

Tuliskan persamaannya dan buktikan. . !!!

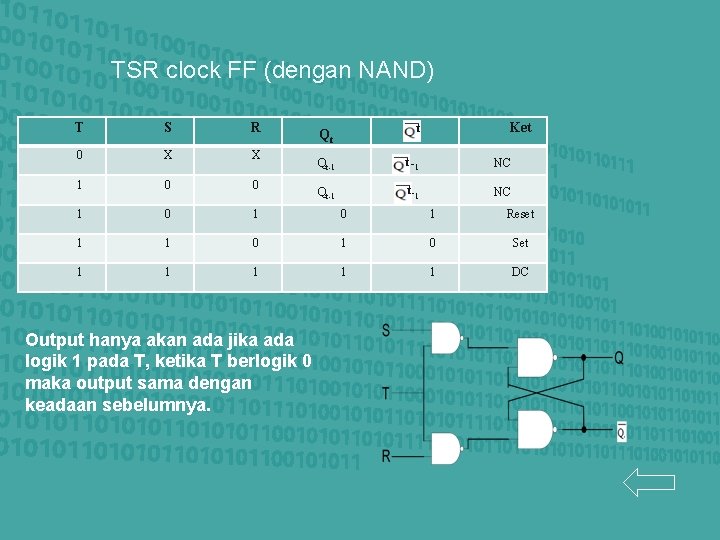

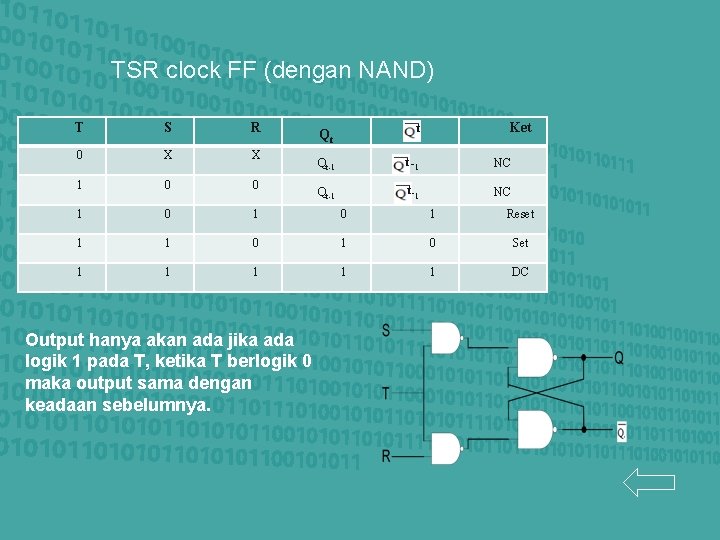

TSR clock FF (dengan NAND) T S R 0 X X 1 0 0 1 0 1 Reset 1 1 0 Set 1 1 1 DC Output hanya akan ada jika ada logik 1 pada T, ketika T berlogik 0 maka output sama dengan keadaan sebelumnya. Ket Qt-1 t -1 NC Qt-1 NC

Tuliskan persamaannya dan buktikan. . !!!

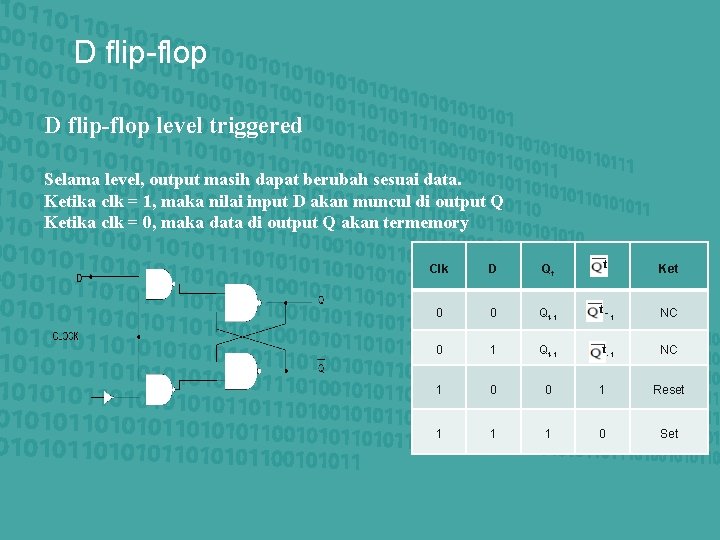

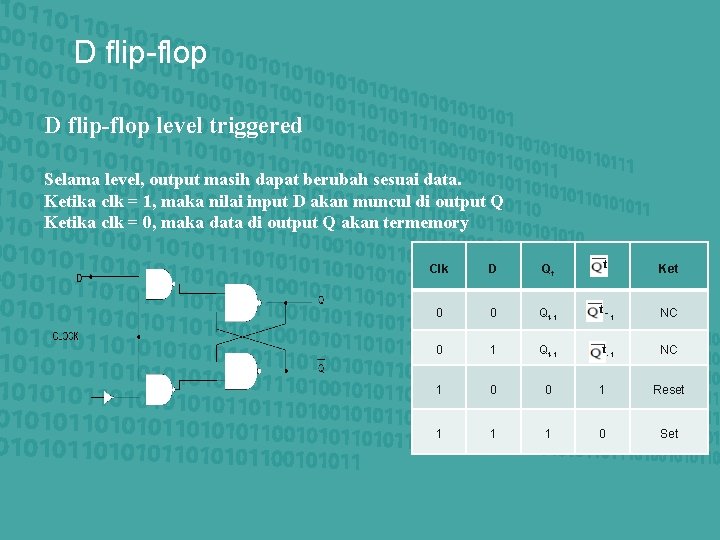

D flip-flop level triggered Selama level, output masih dapat berubah sesuai data. Ketika clk = 1, maka nilai input D akan muncul di output Q Ketika clk = 0, maka data di output Q akan termemory Clk D Qt t Ket 0 0 Qt-1 t-t -1 NC 0 1 Qt-1 t- t -1 NC 1 0 0 1 Reset 1 1 1 0 Set

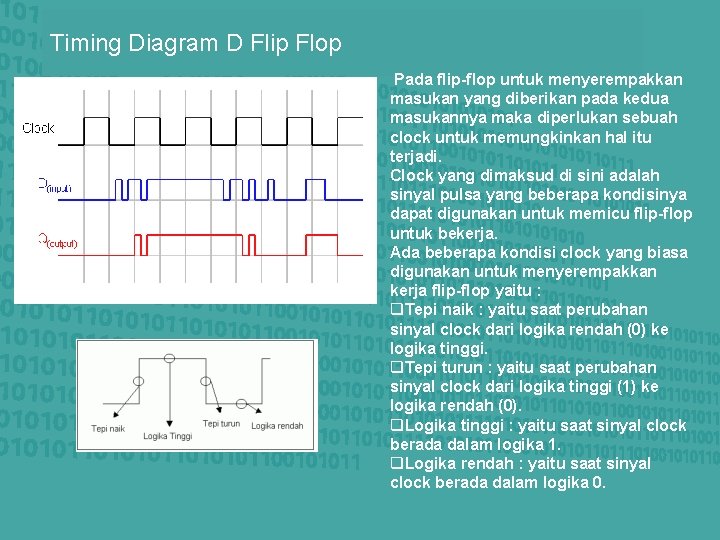

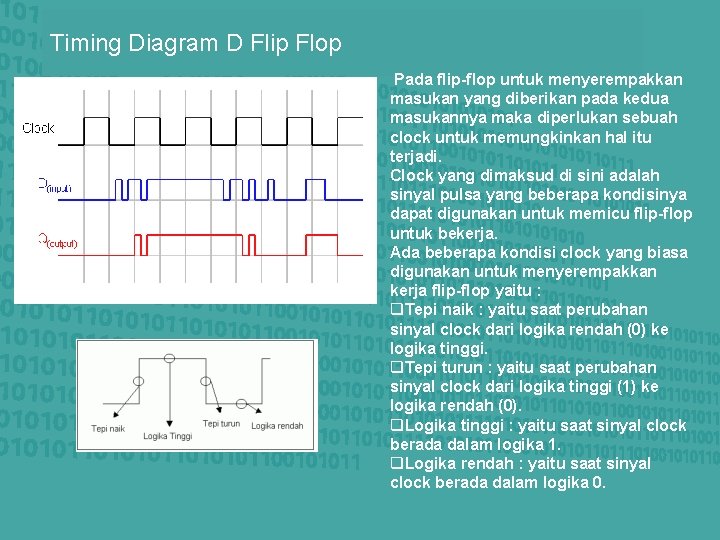

Timing Diagram D Flip Flop Pada flip-flop untuk menyerempakkan masukan yang diberikan pada kedua masukannya maka diperlukan sebuah clock untuk memungkinkan hal itu terjadi. Clock yang dimaksud di sini adalah sinyal pulsa yang beberapa kondisinya dapat digunakan untuk memicu flip-flop untuk bekerja. Ada beberapa kondisi clock yang biasa digunakan untuk menyerempakkan kerja flip-flop yaitu : q. Tepi naik : yaitu saat perubahan sinyal clock dari logika rendah (0) ke logika tinggi. q. Tepi turun : yaitu saat perubahan sinyal clock dari logika tinggi (1) ke logika rendah (0). q. Logika tinggi : yaitu saat sinyal clock berada dalam logika 1. q. Logika rendah : yaitu saat sinyal clock berada dalam logika 0.

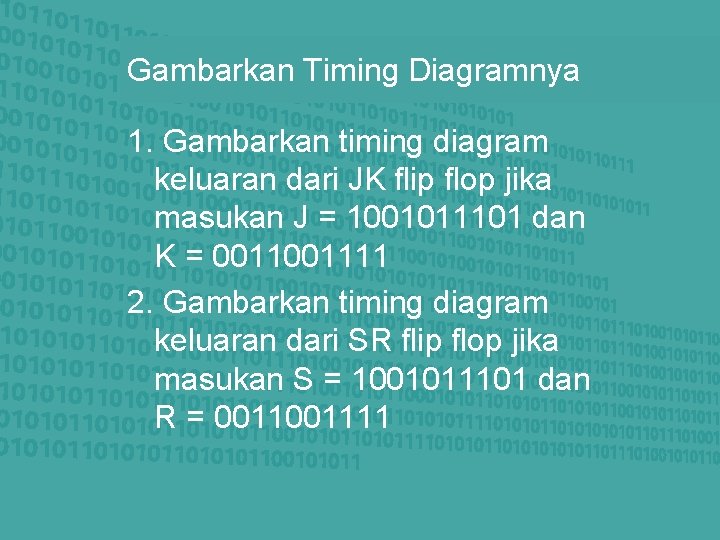

Gambarkan Timing Diagramnya 1. Gambarkan timing diagram keluaran dari JK flip flop jika masukan J = 1001011101 dan K = 001111 2. Gambarkan timing diagram keluaran dari SR flip flop jika masukan S = 1001011101 dan R = 001111

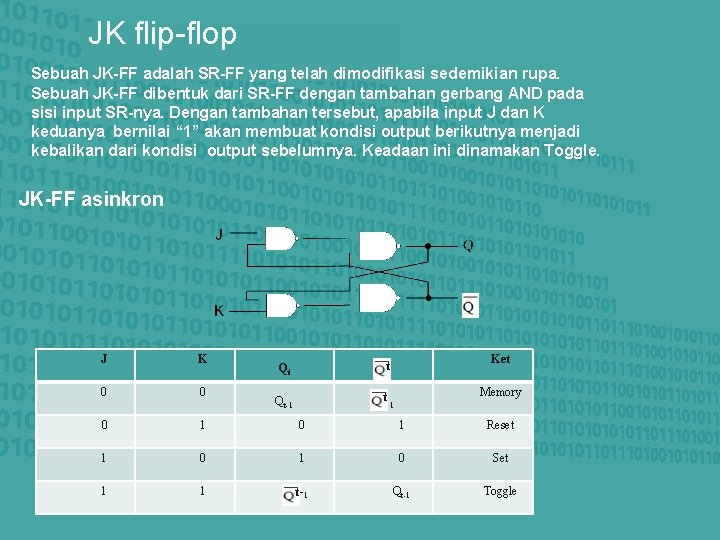

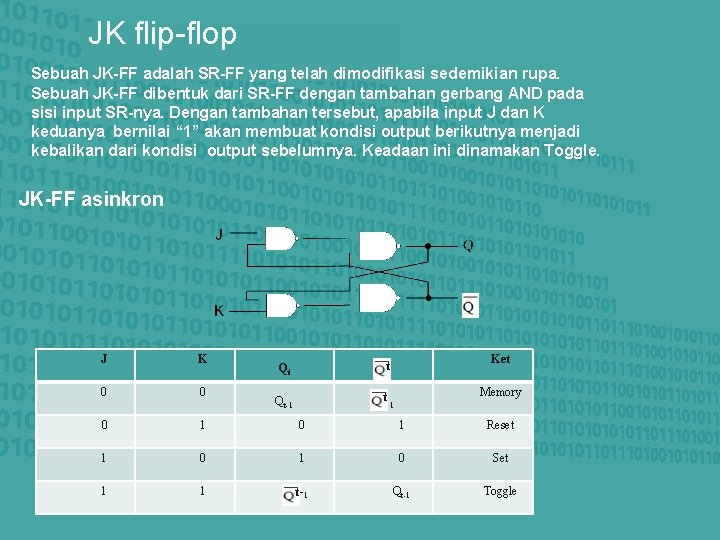

JK flip-flop Sebuah JK-FF adalah SR-FF yang telah dimodifikasi sedemikian rupa. Sebuah JK-FF dibentuk dari SR-FF dengan tambahan gerbang AND pada sisi input SR-nya. Dengan tambahan tersebut, apabila input J dan K keduanya bernilai “ 1” akan membuat kondisi output berikutnya menjadi kebalikan dari kondisi output sebelumnya. Keadaan ini dinamakan Toggle. JK-FF asinkron J K Ket 0 0 0 1 Reset 1 0 Set 1 1 tt-1 Qt-1 Toggle Qt Qt-1 t Qt 1 Memory

Tuliskan persamaannya dan buktikan. . !!!

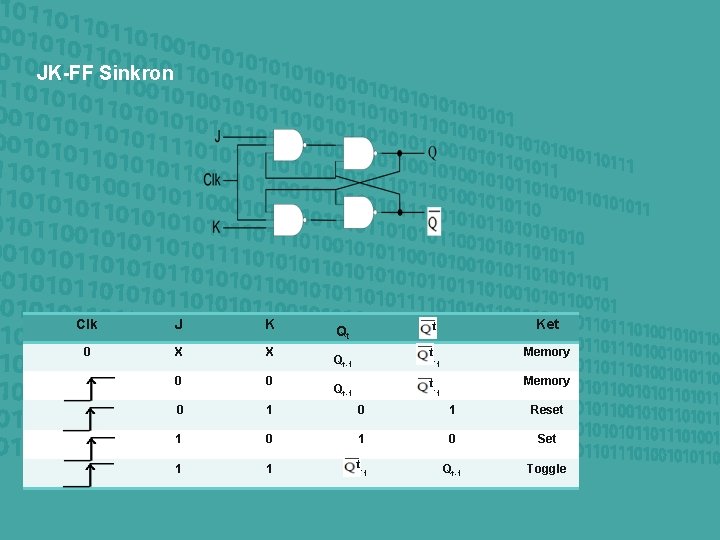

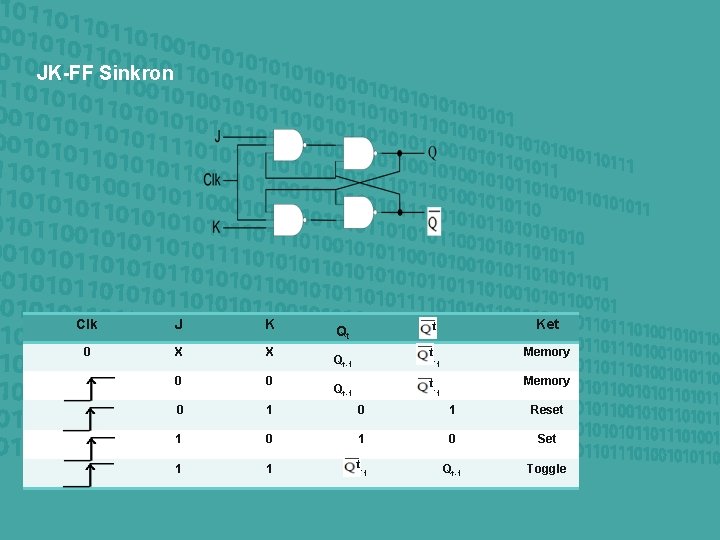

JK-FF Sinkron Clk J K t Ket 0 X X Qt-1 t t-1 Memory 0 0 Qt-1 t t 1 Memory 0 1 Reset 1 0 Set 1 1 t t 1 Qt-1 Toggle Qt

Tuliskan persamaannya dan buktikan. . !!!

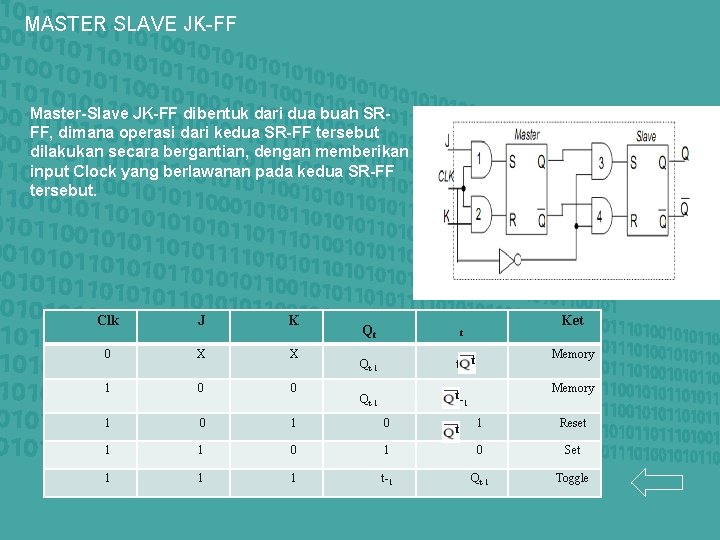

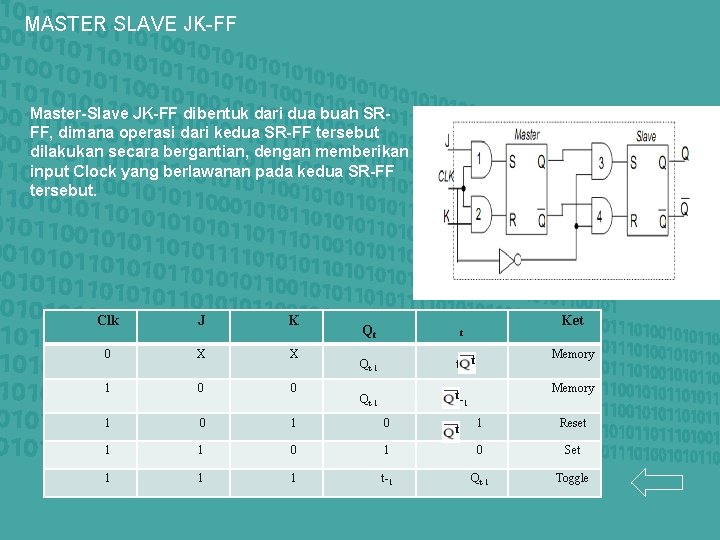

MASTER SLAVE JK-FF Master-Slave JK-FF dibentuk dari dua buah SRFF, dimana operasi dari kedua SR-FF tersebut dilakukan secara bergantian, dengan memberikan input Clock yang berlawanan pada kedua SR-FF tersebut. Clk J K 0 X X 1 0 0 1 0 1 1 1 Qt Ket t Qt-1 tt 1 Memory 1 Reset 1 0 Set t-1 Qt-1 Toggle t

Tuliskan persamaannya dan buktikan. . !!!

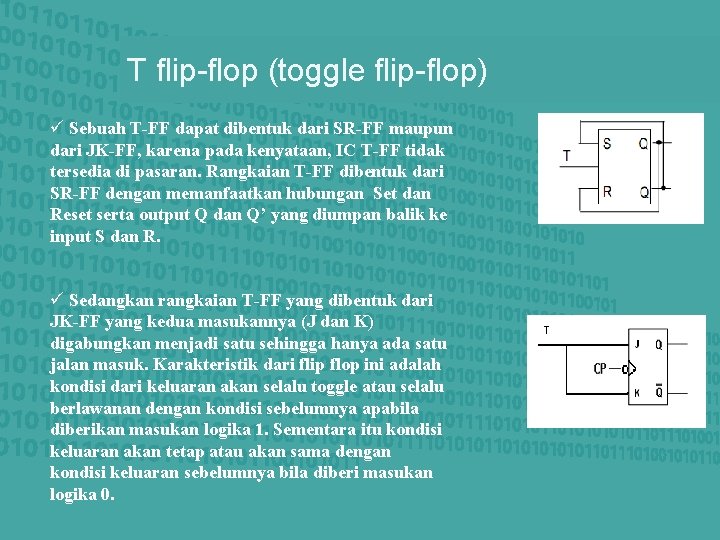

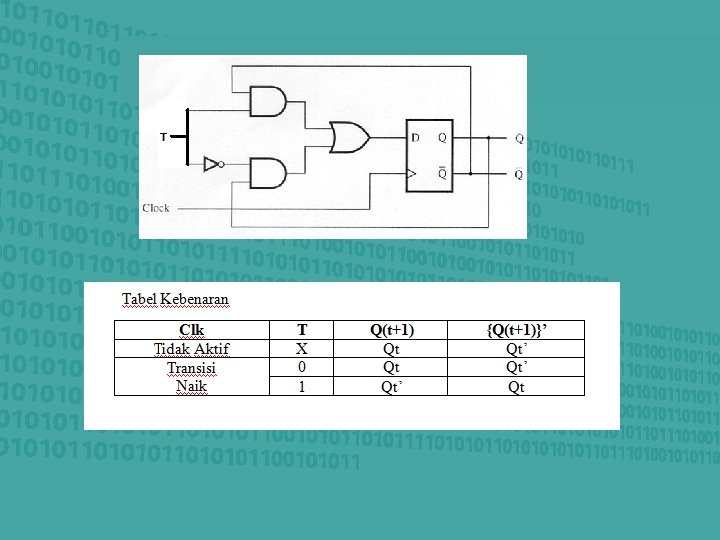

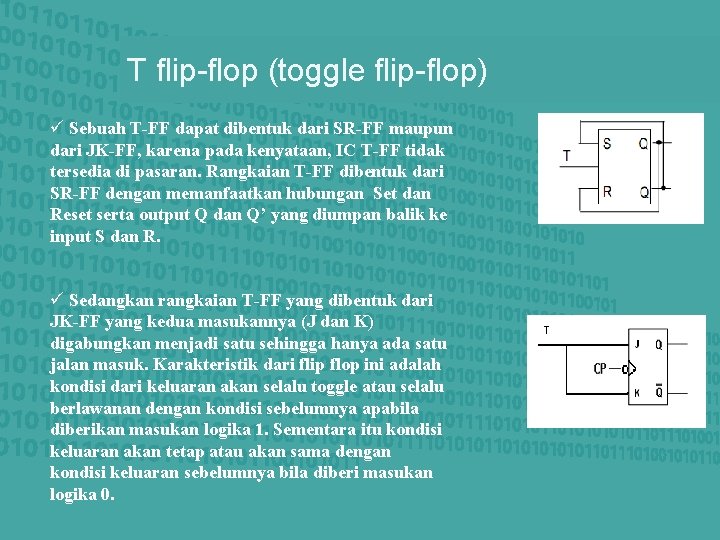

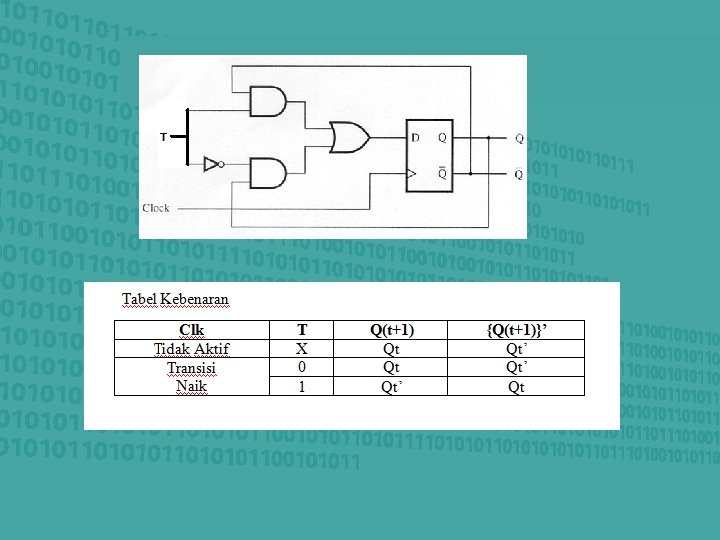

T flip-flop (toggle flip-flop) ü Sebuah T-FF dapat dibentuk dari SR-FF maupun dari JK-FF, karena pada kenyataan, IC T-FF tidak tersedia di pasaran. Rangkaian T-FF dibentuk dari SR-FF dengan memanfaatkan hubungan Set dan Reset serta output Q dan Q’ yang diumpan balik ke input S dan R. ü Sedangkan rangkaian T-FF yang dibentuk dari JK-FF yang kedua masukannya (J dan K) digabungkan menjadi satu sehingga hanya ada satu jalan masuk. Karakteristik dari flip flop ini adalah kondisi dari keluaran akan selalu toggle atau selalu berlawanan dengan kondisi sebelumnya apabila diberikan masukan logika 1. Sementara itu kondisi keluaran akan tetap atau akan sama dengan kondisi keluaran sebelumnya bila diberi masukan logika 0.

Tuliskan persamaannya dan buktikan. . !!!

TERIMA KASIH ATAS PERHATIAN NYA!!!