FLIP FLOP FLIP FLOP Berupa rangkaian elektronika digital

FLIP - FLOP

FLIP FLOP § Berupa rangkaian elektronika digital yang mendasari banyak aplikasi, seperti memori, mikroprosesor, latch dan buffer, dll. § Mempunyai 2 kondisi stabil (Q=1 dan Q=0) § Mampu menyimpan 1 bit memori 2

Klasifikasi Rangkaian digital: R. kombinasi: output hanya fungsi input R. Berurut : output fungsi input sesaat dan output (sekuensial) (jadi juga masukan) sebelumnya → ada ingatan, memori sinkron : perubahan terjadi bersamaan pada waktu ditentukan → ada detak asinkron: perubahan terjadi sembarang waktu 3

FLIP-FLOP v Dasar dari rangk berurut v Disusun dari r. kombinasi dengan umpan balik → ada tundaan waktu (time delay) → tundaan waktu ada pada setiap gerbang v Rangkaian yang mempunyai 2 keluaran saling komplemen (satu komplemen dari yang lain), masukan boleh 1, boleh 2 v Ada 4 bentuk dasar flip flop: Flip flop RS (urut abjad singkatan Set Reset) Flip flop T (Toggle) Flip flop D (Delay) Flip flop JK 4

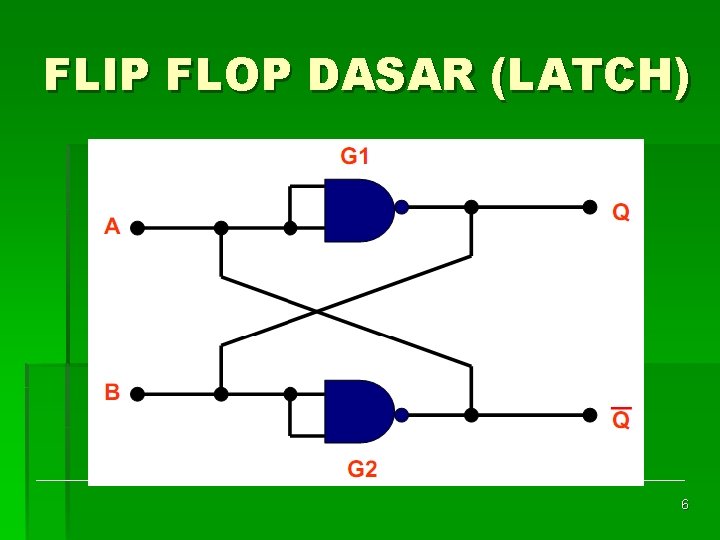

LATCH § Flip flop sederhana § Terdiri dari 2 NAND gates 5

FLIP FLOP DASAR (LATCH) 6

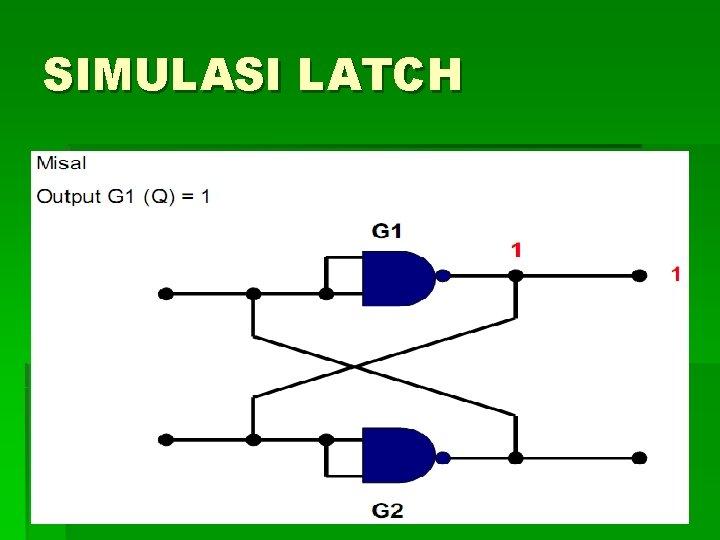

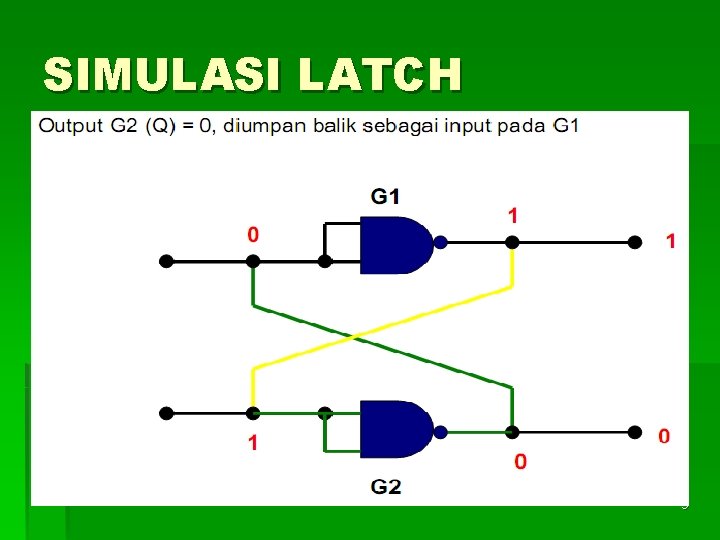

SIMULASI LATCH 7

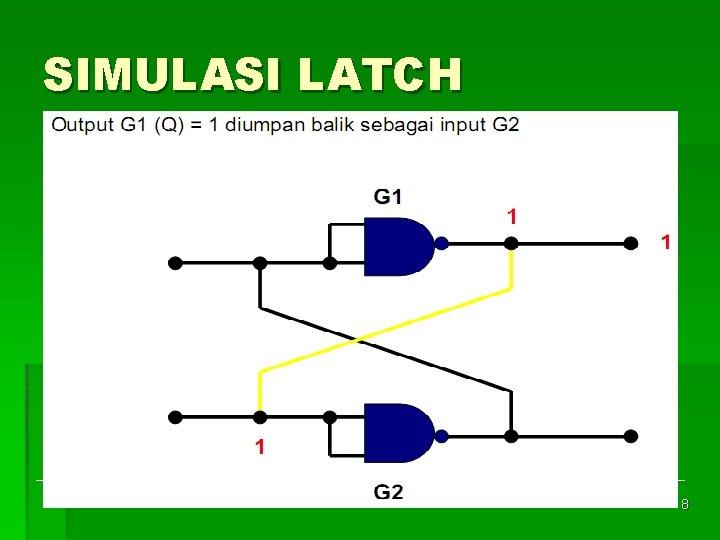

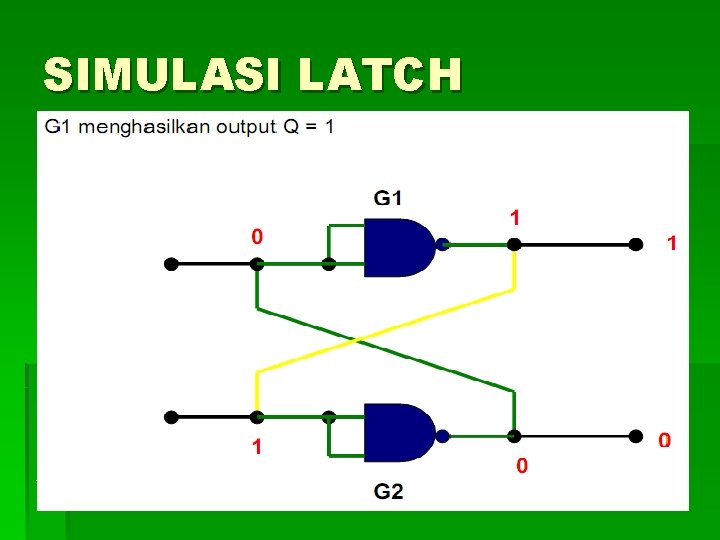

SIMULASI LATCH 8

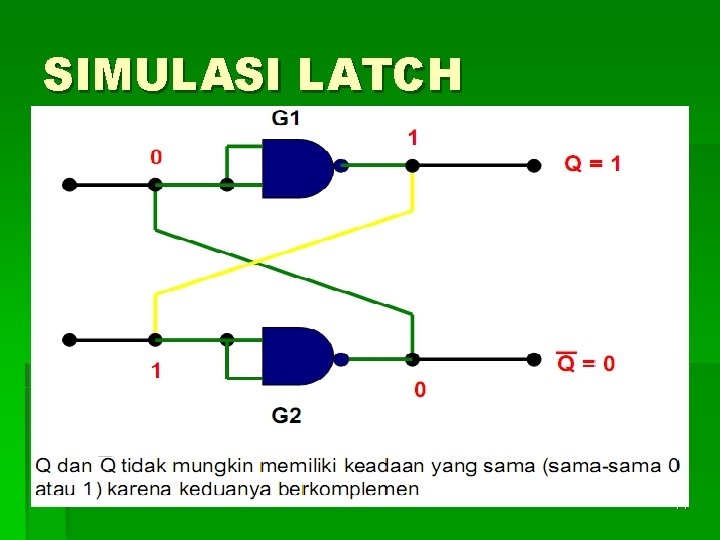

SIMULASI LATCH 9

SIMULASI LATCH 10

SIMULASI LATCH 11

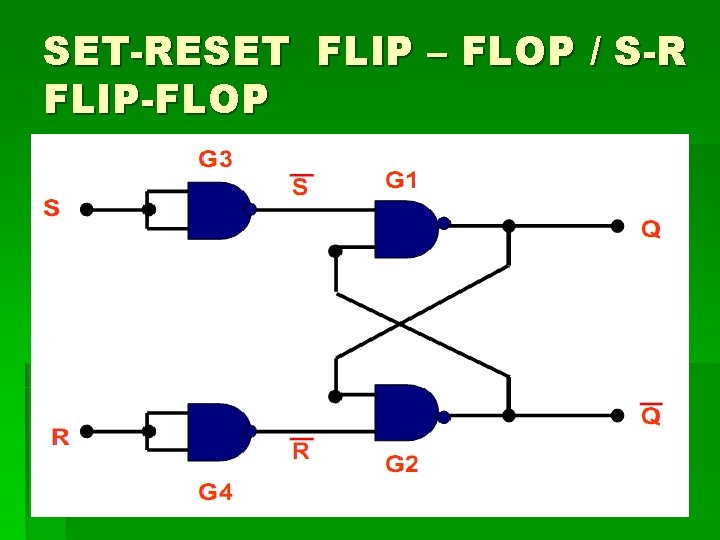

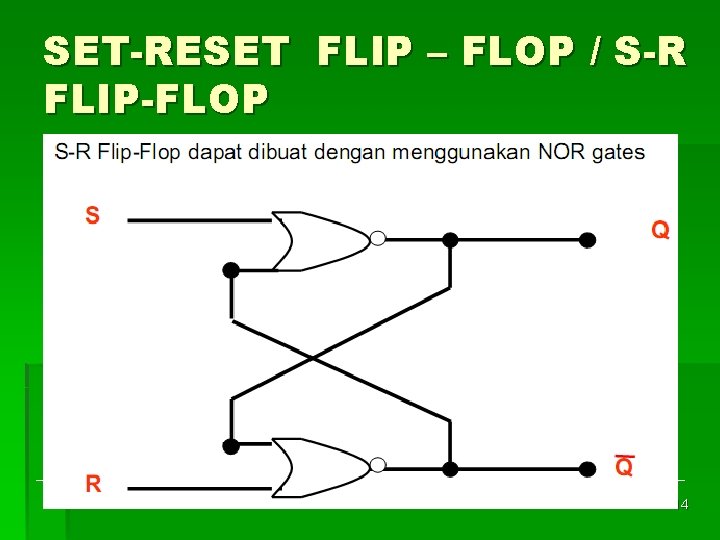

SET-RESET FLIP – FLOP / S-R FLIP-FLOP § Pengembangan dari latch § Dapat diatur untuk mendapatkan nilai output (Q) tertentu 12

SET-RESET FLIP – FLOP / S-R FLIP-FLOP 13

SET-RESET FLIP – FLOP / S-R FLIP-FLOP 14

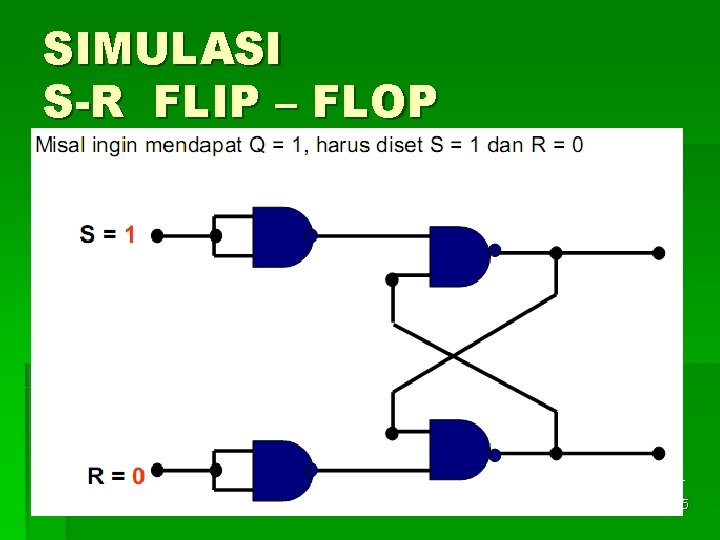

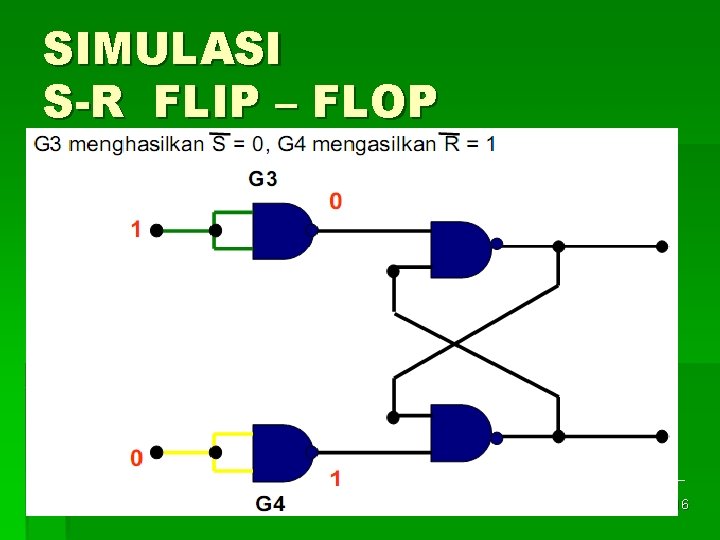

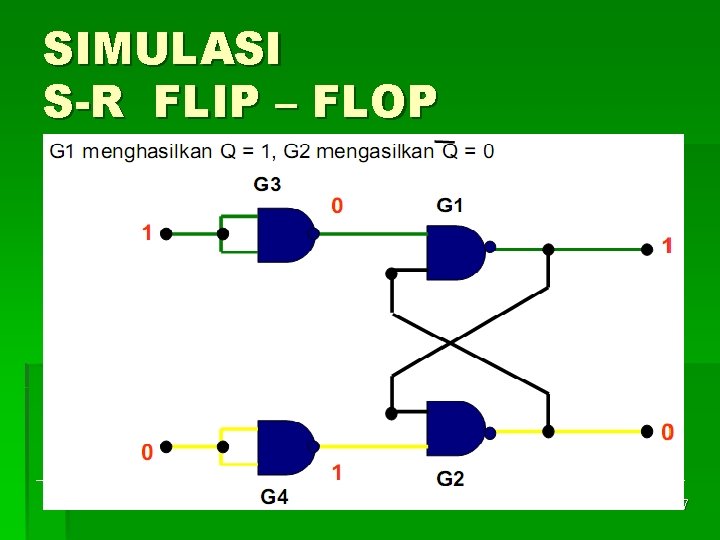

SIMULASI S-R FLIP – FLOP 15

SIMULASI S-R FLIP – FLOP 16

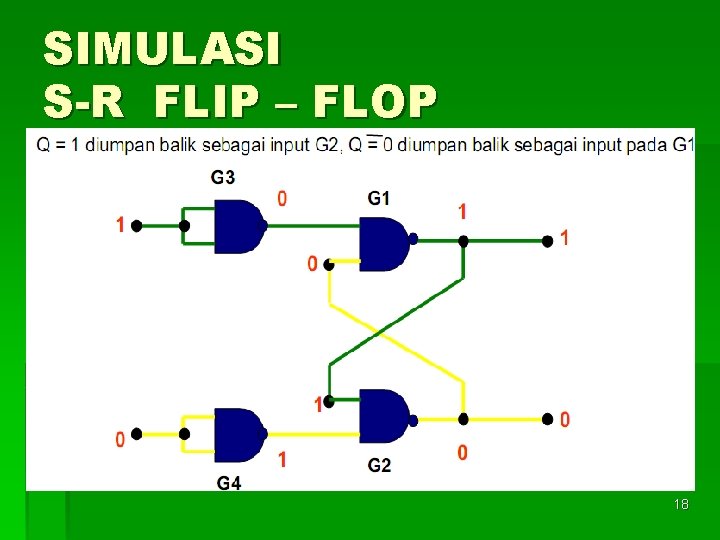

SIMULASI S-R FLIP – FLOP 17

SIMULASI S-R FLIP – FLOP 18

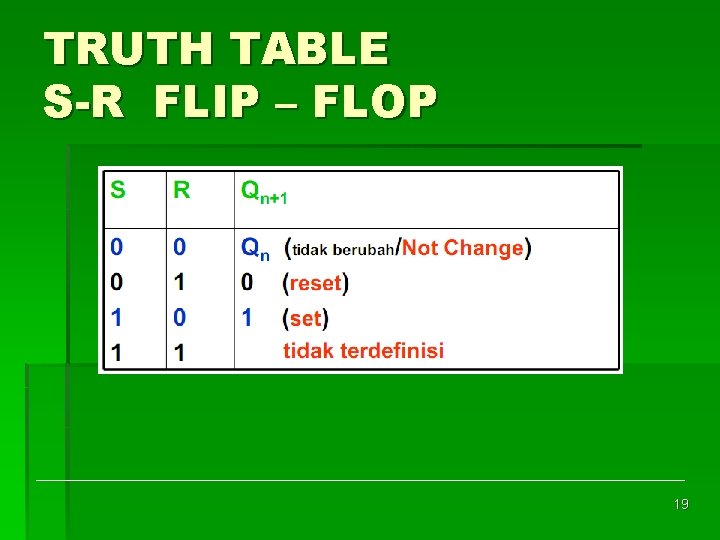

TRUTH TABLE S-R FLIP – FLOP 19

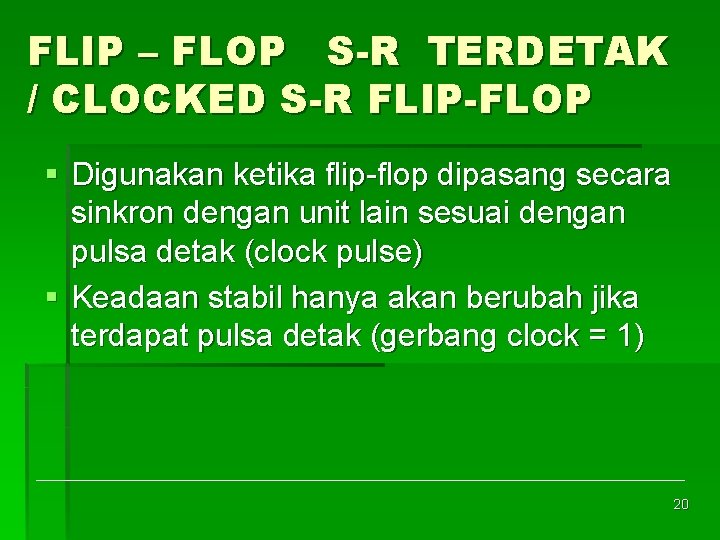

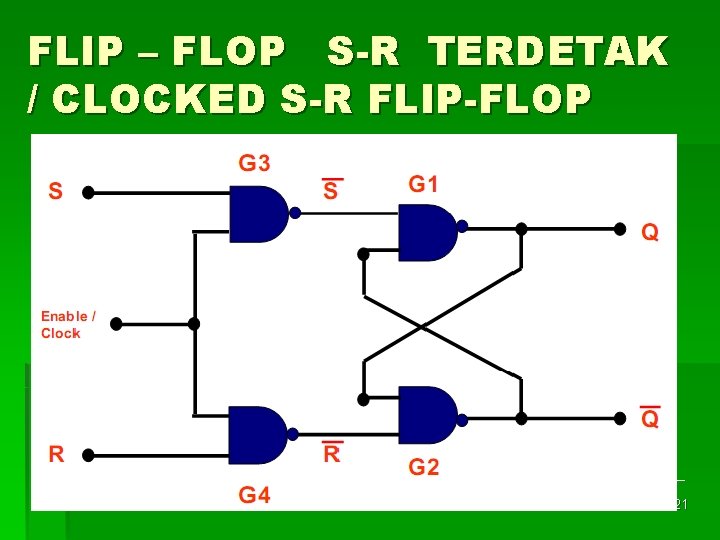

FLIP – FLOP S-R TERDETAK / CLOCKED S-R FLIP-FLOP § Digunakan ketika flip flop dipasang secara sinkron dengan unit lain sesuai dengan pulsa detak (clock pulse) § Keadaan stabil hanya akan berubah jika terdapat pulsa detak (gerbang clock = 1) 20

FLIP – FLOP S-R TERDETAK / CLOCKED S-R FLIP-FLOP 21

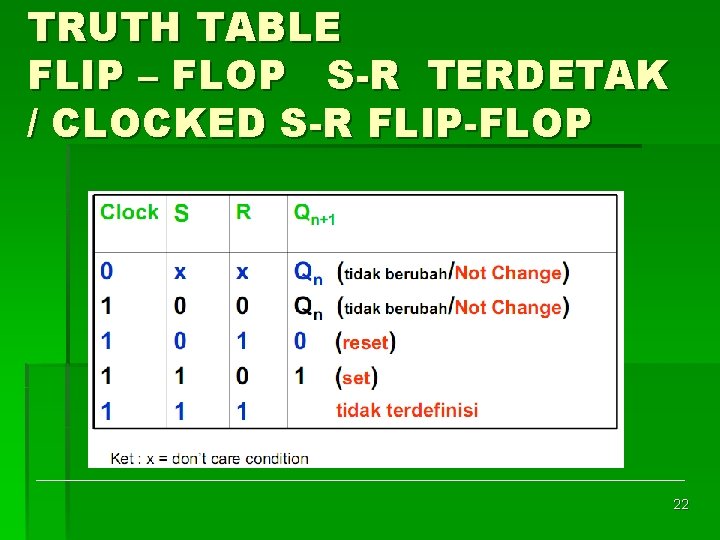

TRUTH TABLE FLIP – FLOP S-R TERDETAK / CLOCKED S-R FLIP-FLOP 22

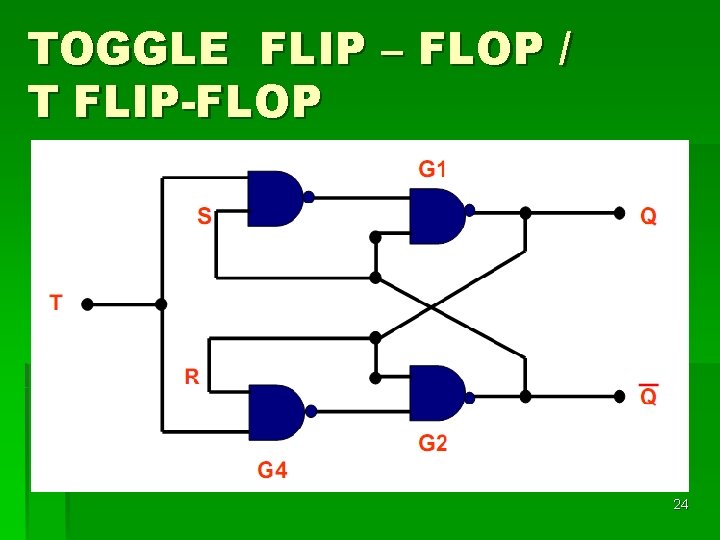

TOGGLE FLIP – FLOP / T FLIP-FLOP § Punya satu masukan T (toggle) § Output pada setiap pulsa masukan berubah 23

TOGGLE FLIP – FLOP / T FLIP-FLOP 24

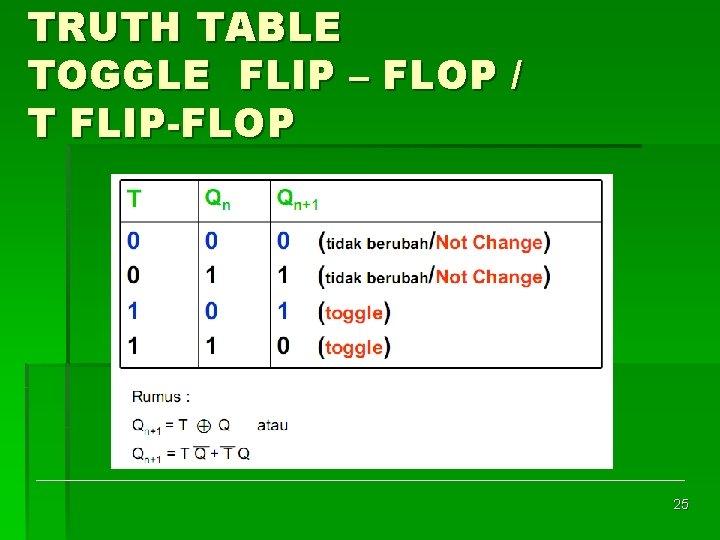

TRUTH TABLE TOGGLE FLIP – FLOP / T FLIP-FLOP 25

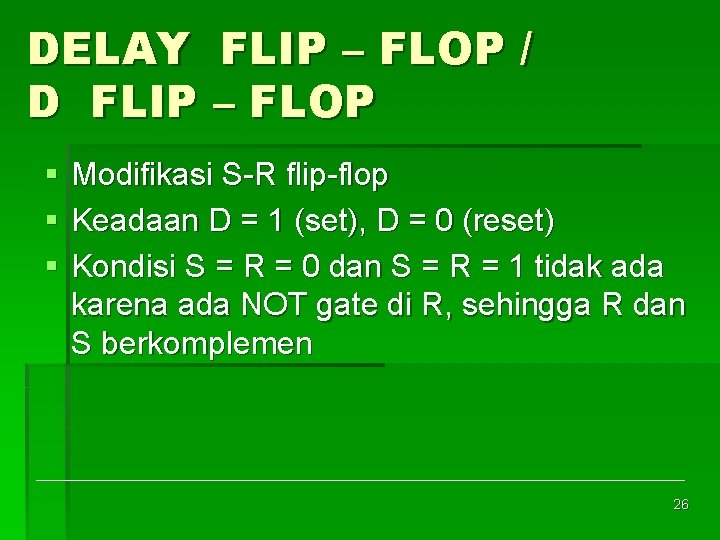

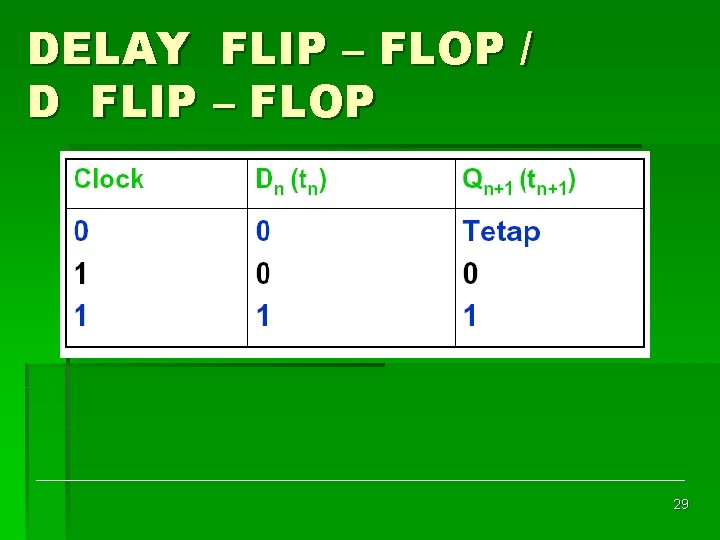

DELAY FLIP – FLOP / D FLIP – FLOP § § § Modifikasi S R flip flop Keadaan D = 1 (set), D = 0 (reset) Kondisi S = R = 0 dan S = R = 1 tidak ada karena ada NOT gate di R, sehingga R dan S berkomplemen 26

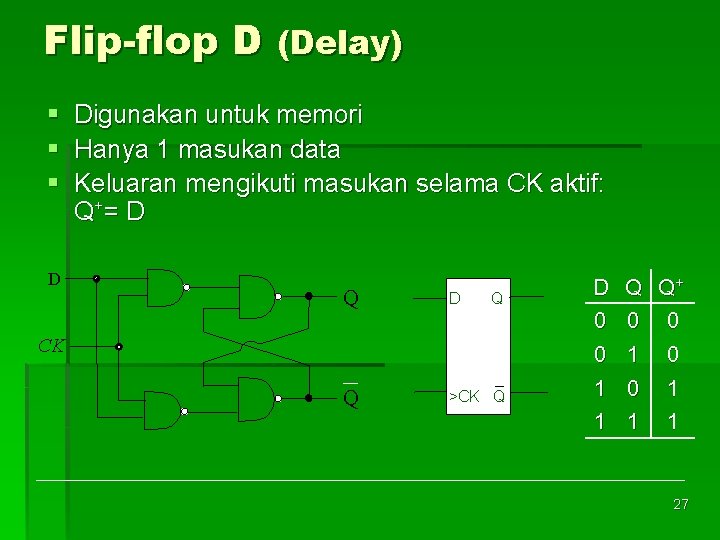

Flip-flop D (Delay) § § § D Digunakan untuk memori Hanya 1 masukan data Keluaran mengikuti masukan selama CK aktif: Q+= D Q >CK Q Q CK D Q Q+ 0 0 1 0 1 1 27

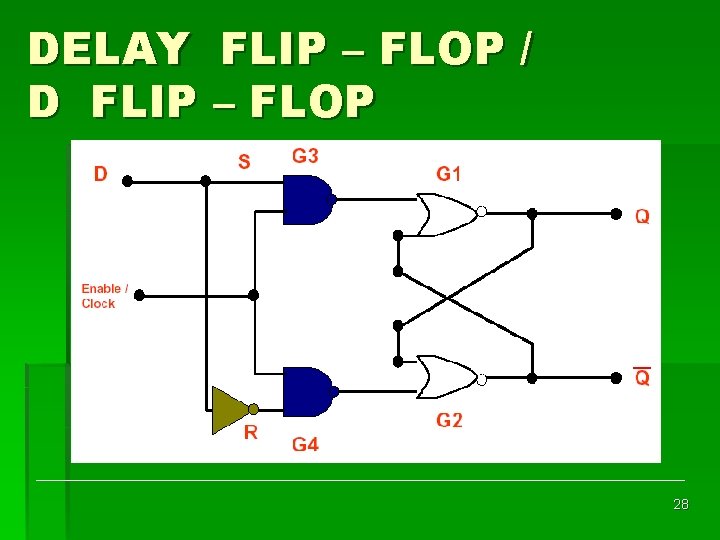

DELAY FLIP – FLOP / D FLIP – FLOP 28

DELAY FLIP – FLOP / D FLIP – FLOP 29

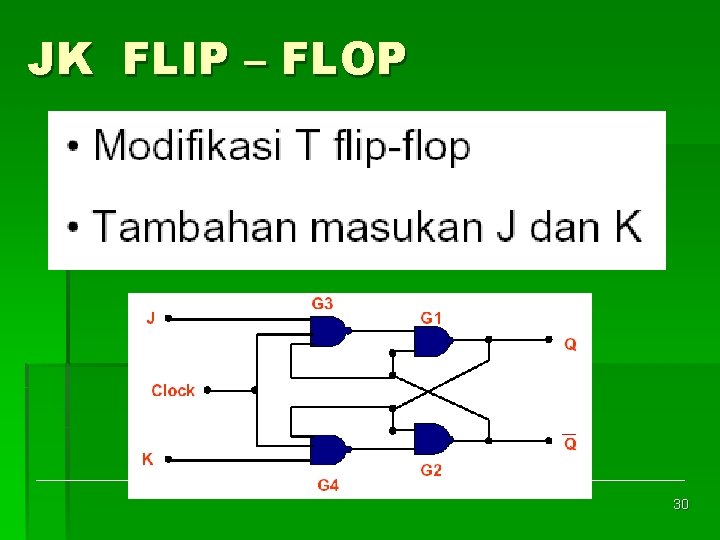

JK FLIP – FLOP 30

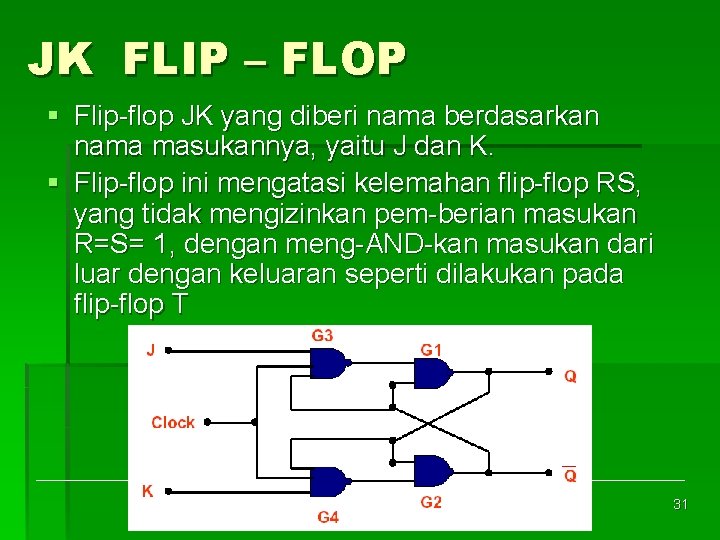

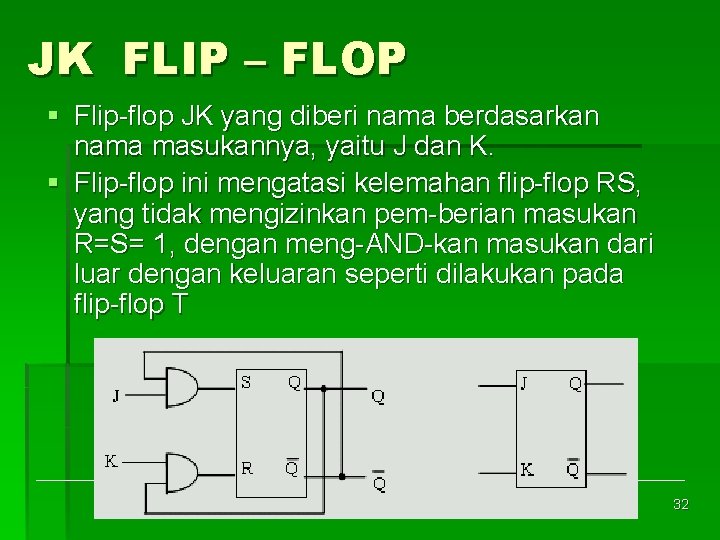

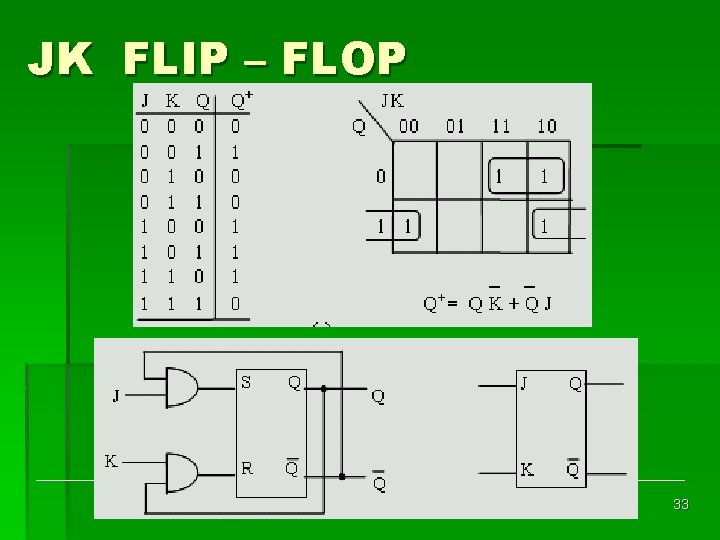

JK FLIP – FLOP § Flip flop JK yang diberi nama berdasarkan nama masukannya, yaitu J dan K. § Flip flop ini mengatasi kelemahan flip flop RS, yang tidak mengizinkan pem berian masukan R=S= 1, dengan meng AND kan masukan dari luar dengan keluaran seperti dilakukan pada flip flop T 31

JK FLIP – FLOP § Flip flop JK yang diberi nama berdasarkan nama masukannya, yaitu J dan K. § Flip flop ini mengatasi kelemahan flip flop RS, yang tidak mengizinkan pem berian masukan R=S= 1, dengan meng AND kan masukan dari luar dengan keluaran seperti dilakukan pada flip flop T 32

JK FLIP – FLOP 33

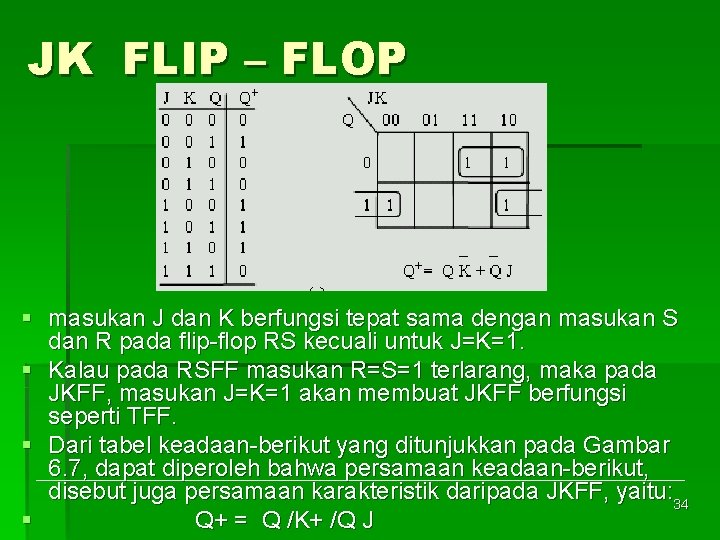

JK FLIP – FLOP § masukan J dan K berfungsi tepat sama dengan masukan S dan R pada flip flop RS kecuali untuk J=K=1. § Kalau pada RSFF masukan R=S=1 terlarang, maka pada JKFF, masukan J=K=1 akan membuat JKFF berfungsi seperti TFF. § Dari tabel keadaan berikut yang ditunjukkan pada Gambar 6. 7, dapat diperoleh bahwa persamaan keadaan berikut, disebut juga persamaan karakteristik daripada JKFF, yaitu: 34 § Q+ = Q /K+ /Q J

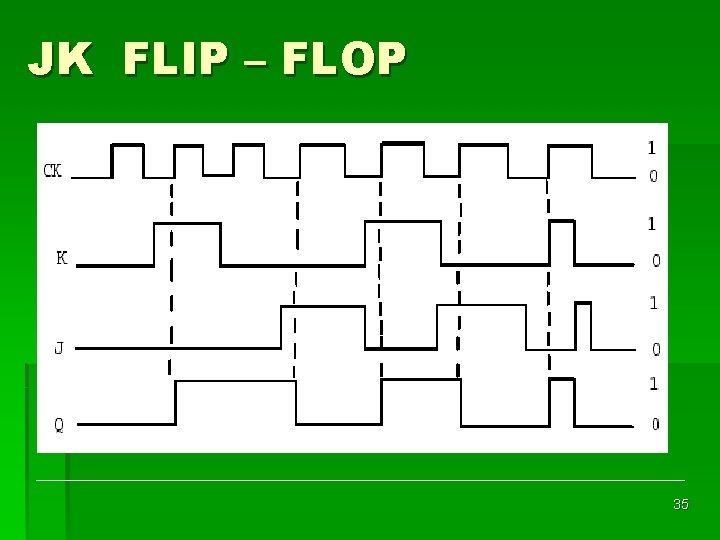

JK FLIP – FLOP 35

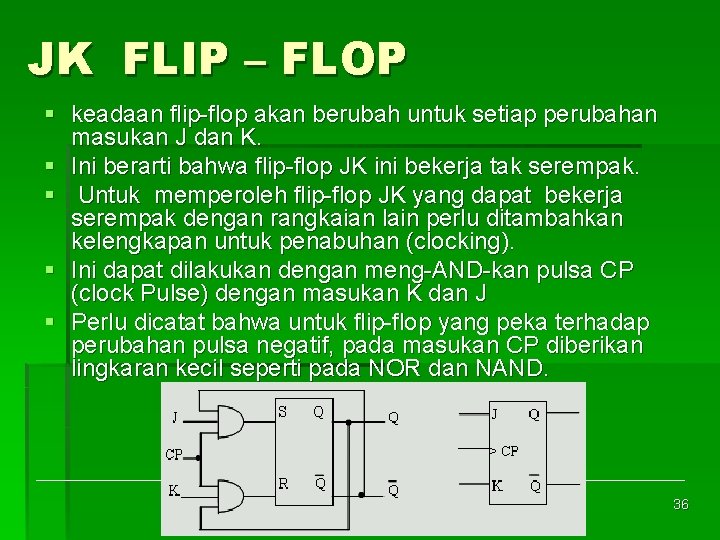

JK FLIP – FLOP § keadaan flip flop akan berubah untuk setiap perubahan masukan J dan K. § Ini berarti bahwa flip flop JK ini bekerja tak serempak. § Untuk memperoleh flip flop JK yang dapat bekerja serempak dengan rangkaian lain perlu ditambahkan kelengkapan untuk penabuhan (clocking). § Ini dapat dilakukan dengan meng AND kan pulsa CP (clock Pulse) dengan masukan K dan J § Perlu dicatat bahwa untuk flip flop yang peka terhadap perubahan pulsa negatif, pada masukan CP diberikan lingkaran kecil seperti pada NOR dan NAND. 36

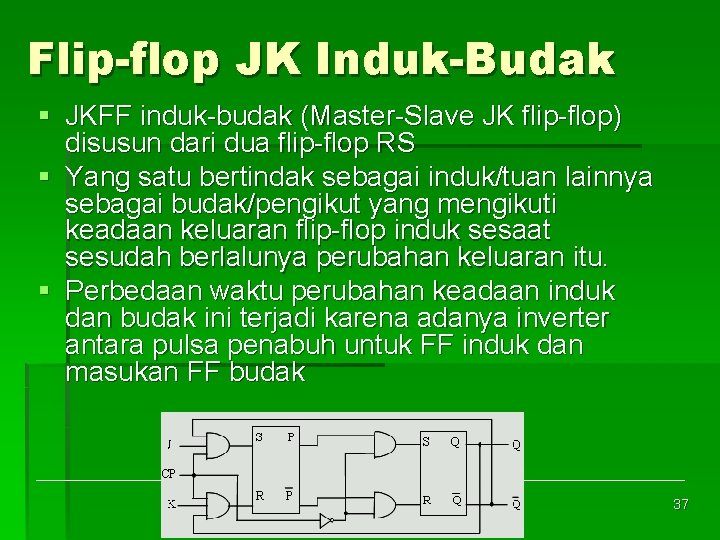

Flip-flop JK Induk-Budak § JKFF induk budak (Master Slave JK flip flop) disusun dari dua flip flop RS § Yang satu bertindak sebagai induk/tuan lainnya sebagai budak/pengikut yang mengikuti keadaan keluaran flip flop induk sesaat sesudah berlalunya perubahan keluaran itu. § Perbedaan waktu perubahan keadaan induk dan budak ini terjadi karena adanya inverter antara pulsa penabuh untuk FF induk dan masukan FF budak 37

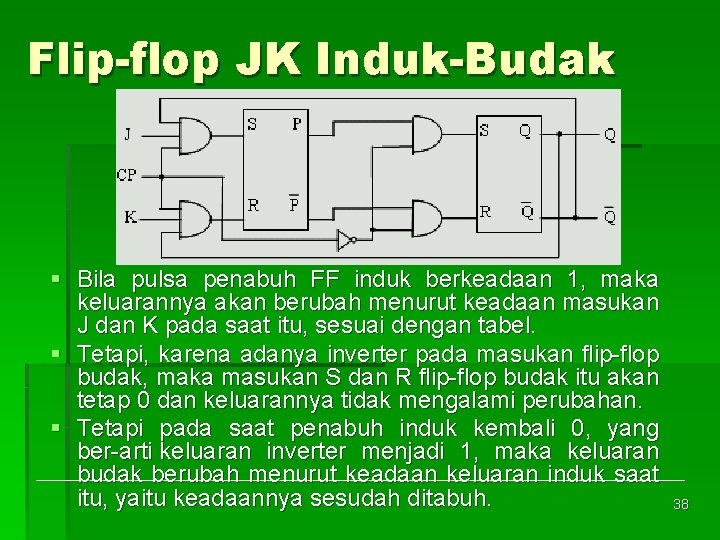

Flip-flop JK Induk-Budak § Bila pulsa penabuh FF induk berkeadaan 1, maka keluarannya akan berubah menurut keadaan masukan J dan K pada saat itu, sesuai dengan tabel. § Tetapi, karena adanya inverter pada masukan flip flop budak, maka masukan S dan R flip flop budak itu akan tetap 0 dan keluarannya tidak mengalami perubahan. § Tetapi pada saat penabuh induk kembali 0, yang ber arti keluaran inverter menjadi 1, maka keluaran budak berubah menurut keadaan keluaran induk saat itu, yaitu keadaannya sesudah ditabuh. 38

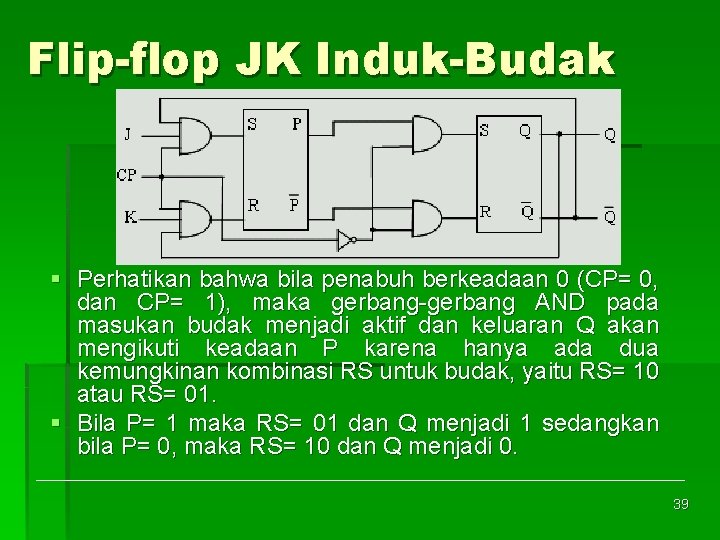

Flip-flop JK Induk-Budak § Perhatikan bahwa bila penabuh berkeadaan 0 (CP= 0, dan CP= 1), maka gerbang AND pada masukan budak menjadi aktif dan keluaran Q akan mengikuti keadaan P karena hanya ada dua kemungkinan kombinasi RS untuk budak, yaitu RS= 10 atau RS= 01. § Bila P= 1 maka RS= 01 dan Q menjadi 1 sedangkan bila P= 0, maka RS= 10 dan Q menjadi 0. 39

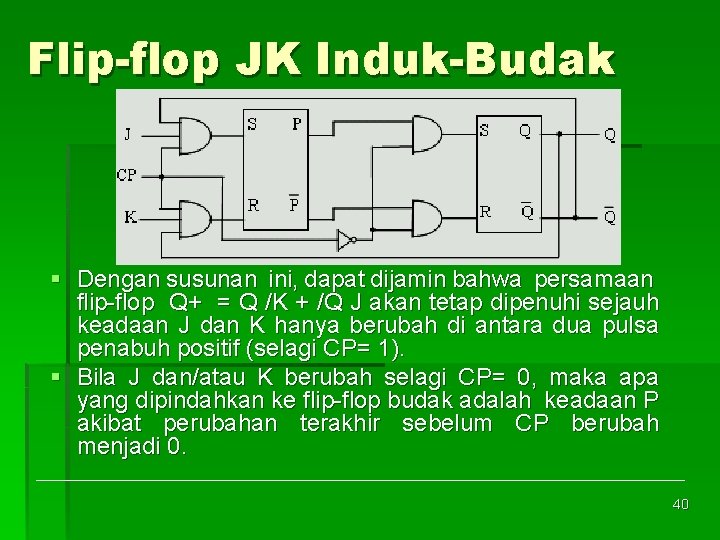

Flip-flop JK Induk-Budak § Dengan susunan ini, dapat dijamin bahwa persamaan flip flop Q+ = Q /K + /Q J akan tetap dipenuhi sejauh keadaan J dan K hanya berubah di antara dua pulsa penabuh positif (selagi CP= 1). § Bila J dan/atau K berubah selagi CP= 0, maka apa yang dipindahkan ke flip flop budak adalah keadaan P akibat perubahan terakhir sebelum CP berubah menjadi 0. 40

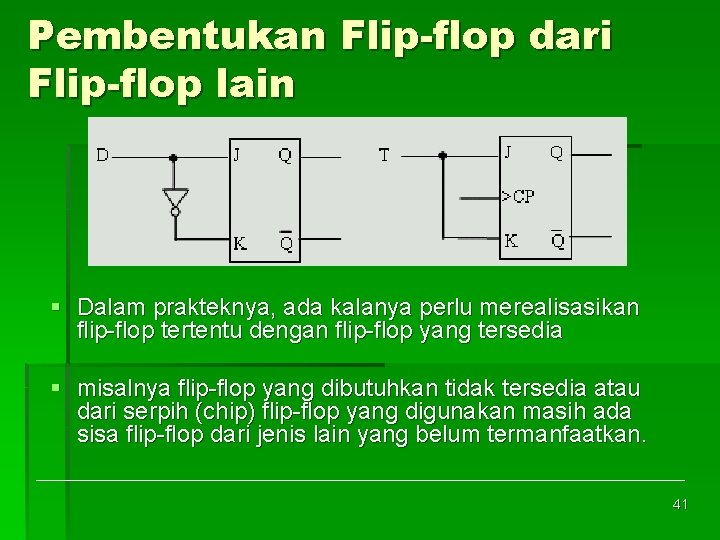

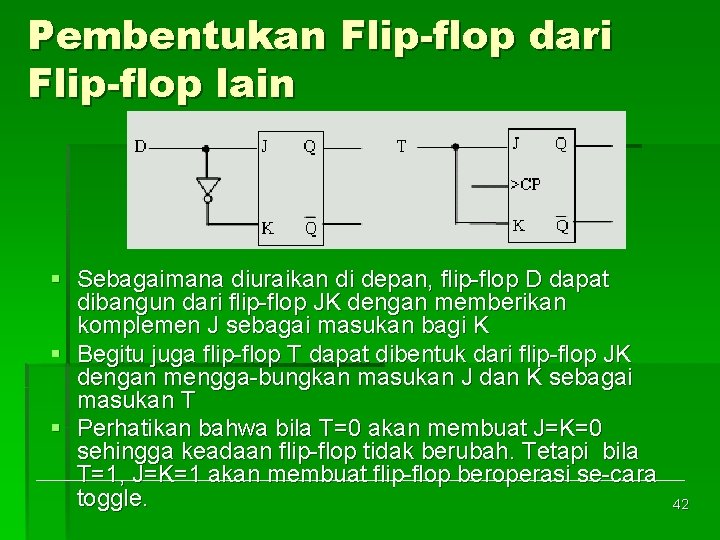

Pembentukan Flip-flop dari Flip-flop lain § Dalam prakteknya, ada kalanya perlu merealisasikan flip flop tertentu dengan flip flop yang tersedia § misalnya flip flop yang dibutuhkan tidak tersedia atau dari serpih (chip) flip flop yang digunakan masih ada sisa flip flop dari jenis lain yang belum termanfaatkan. 41

Pembentukan Flip-flop dari Flip-flop lain § Sebagaimana diuraikan di depan, flip flop D dapat dibangun dari flip flop JK dengan memberikan komplemen J sebagai masukan bagi K § Begitu juga flip flop T dapat dibentuk dari flip flop JK dengan mengga bungkan masukan J dan K sebagai masukan T § Perhatikan bahwa bila T=0 akan membuat J=K=0 sehingga keadaan flip flop tidak berubah. Tetapi bila T=1, J=K=1 akan membuat flip flop beroperasi se cara toggle. 42

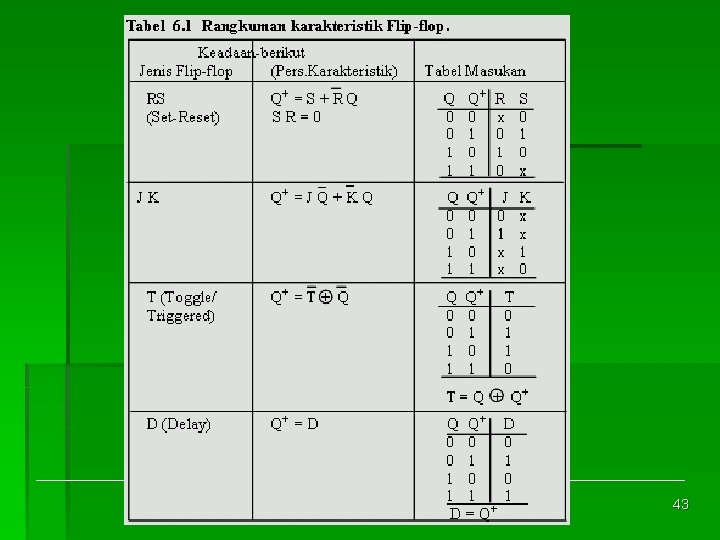

43

- Slides: 43