Programming SuperVGA Graphics Devices Introduction to VESA graphics

- Slides: 24

Programming Super-VGA Graphics Devices Introduction to VESA graphics modes and to organization of the linear frame-buffer memory

Motivation • The impetus for high-quality PC graphics was an early incentive for developing the 32 -bit Intel x 86 processor, since graphics images with realistic color and animation requires efficient access to a much larger memory-segment than can be addressed with the original 20 -bit real-mode scheme

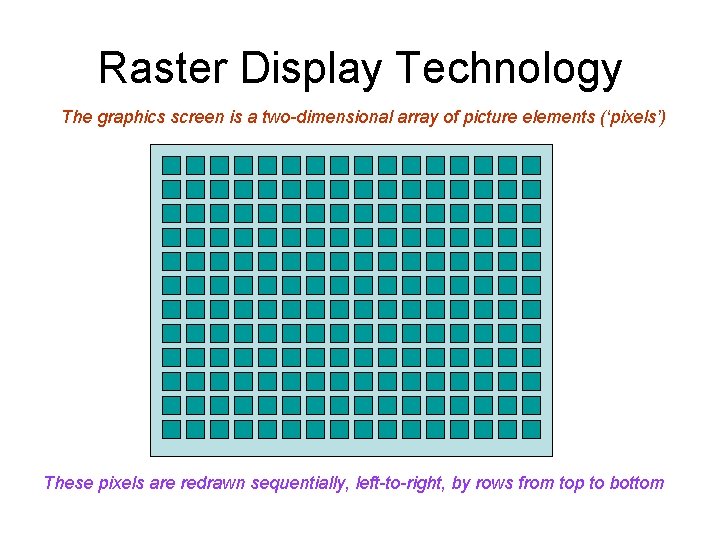

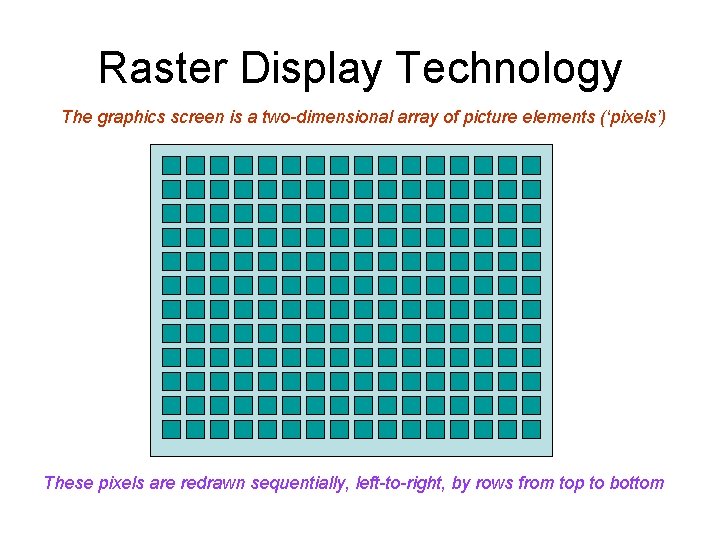

Raster Display Technology The graphics screen is a two-dimensional array of picture elements (‘pixels’) These pixels are redrawn sequentially, left-to-right, by rows from top to bottom

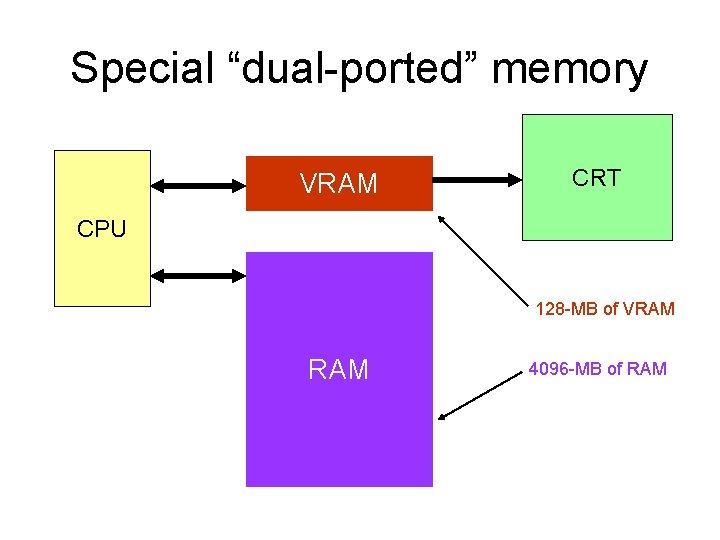

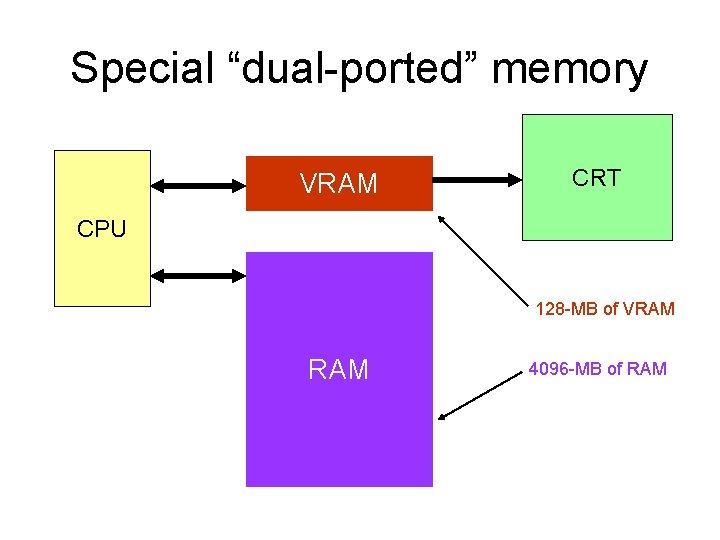

Special “dual-ported” memory VRAM CRT CPU 128 -MB of VRAM 4096 -MB of RAM

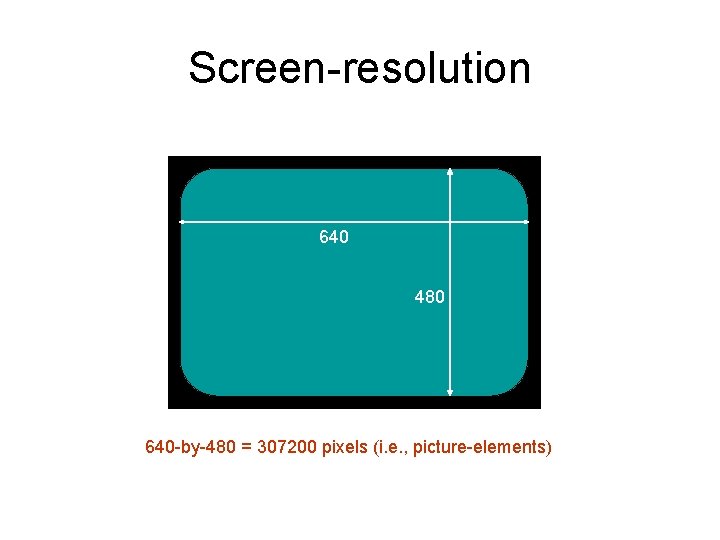

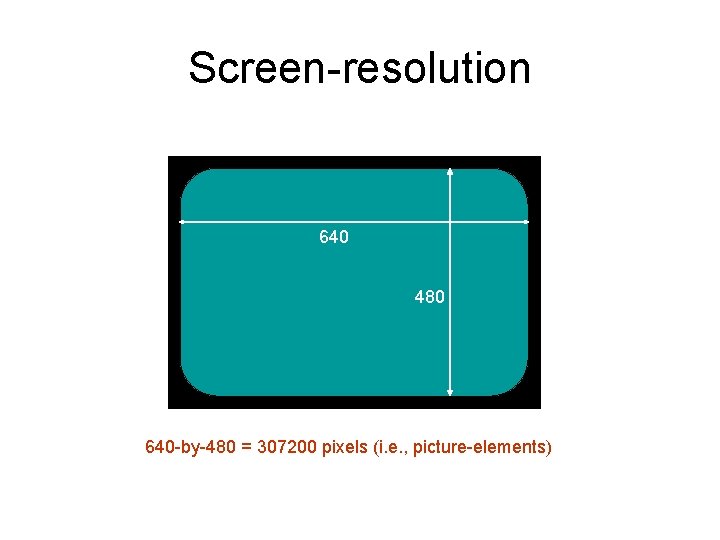

Screen-resolution 640 480 640 -by-480 = 307200 pixels (i. e. , picture-elements)

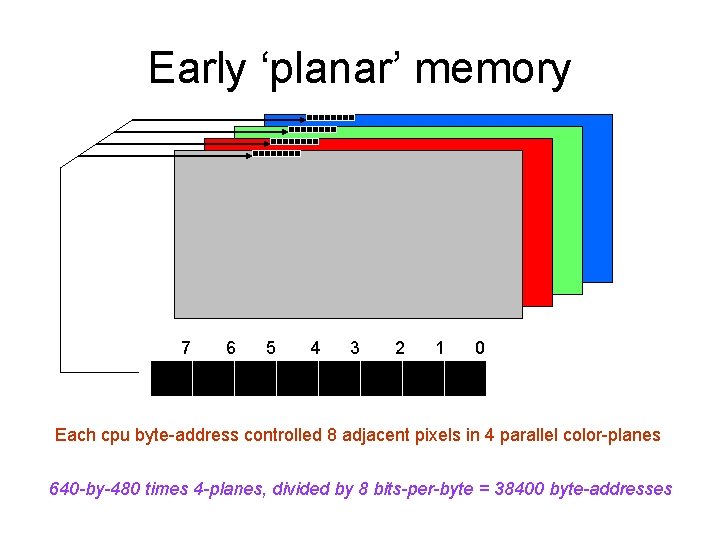

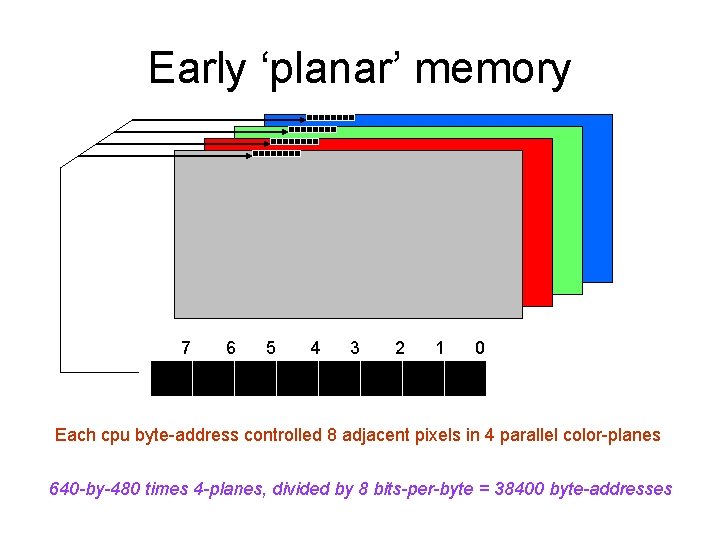

Early ‘planar’ memory 7 6 5 4 3 2 1 0 Each cpu byte-address controlled 8 adjacent pixels in 4 parallel color-planes 640 -by-480 times 4 -planes, divided by 8 bits-per-byte = 38400 byte-addresses

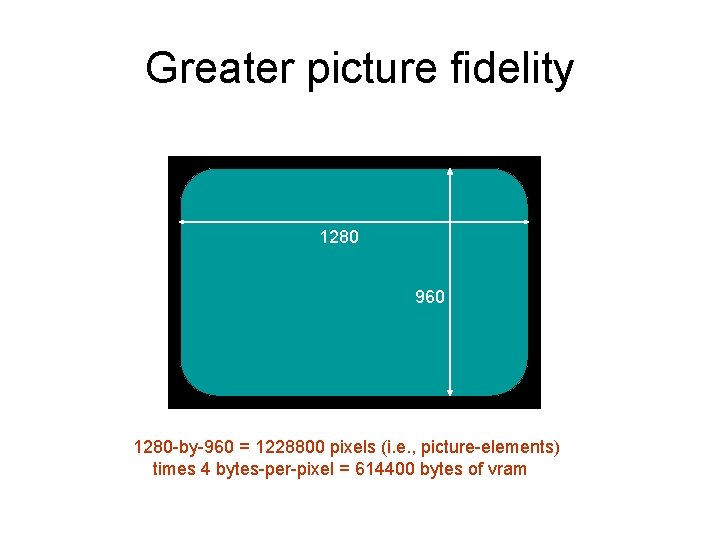

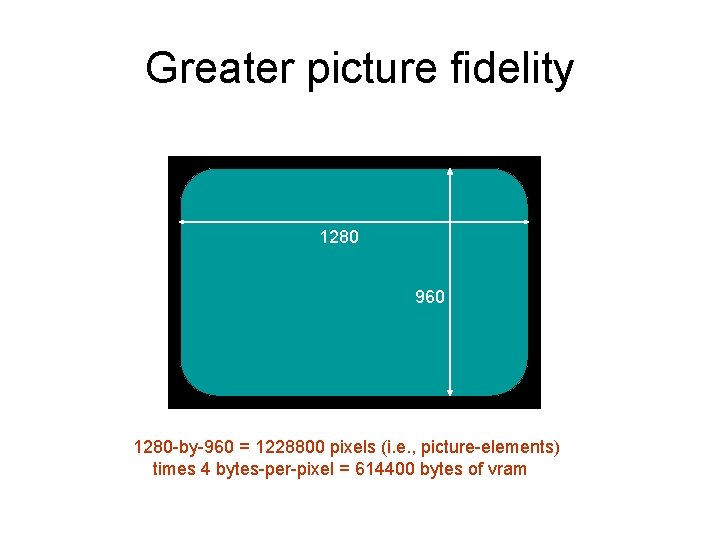

Greater picture fidelity 640 1280 960 480 1280 -by-960 = 1228800 pixels (i. e. , picture-elements) times 4 bytes-per-pixel = 614400 bytes of vram

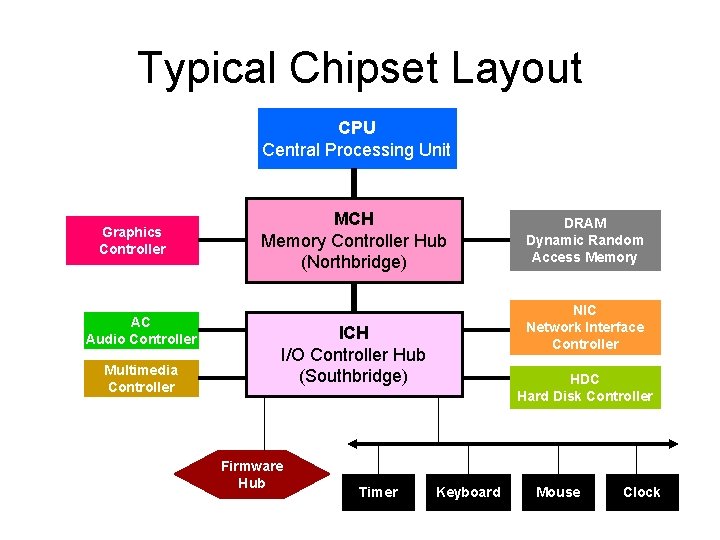

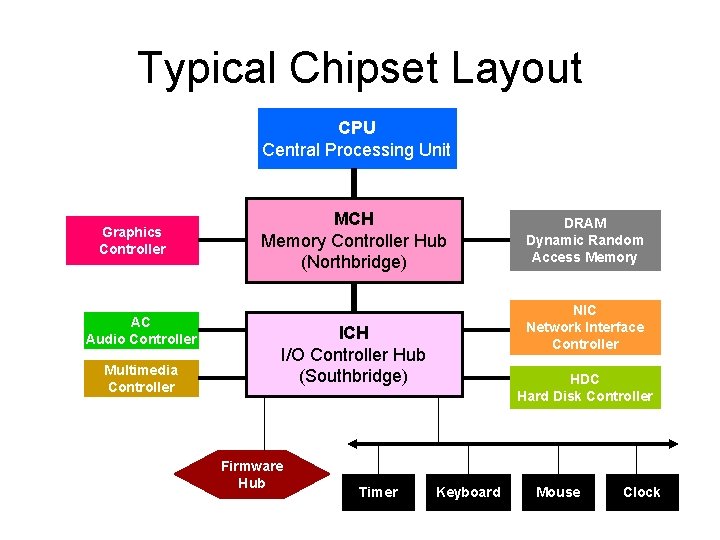

Typical Chipset Layout CPU Central Processing Unit Graphics Controller AC Audio Controller Multimedia Controller MCH Memory Controller Hub (Northbridge) NIC Network Interface Controller ICH I/O Controller Hub (Southbridge) Firmware Hub Timer DRAM Dynamic Random Access Memory HDC Hard Disk Controller Keyboard Mouse Clock

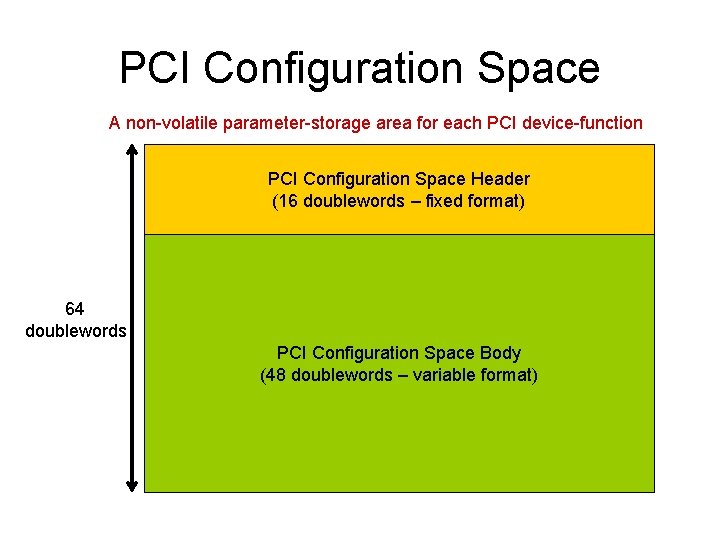

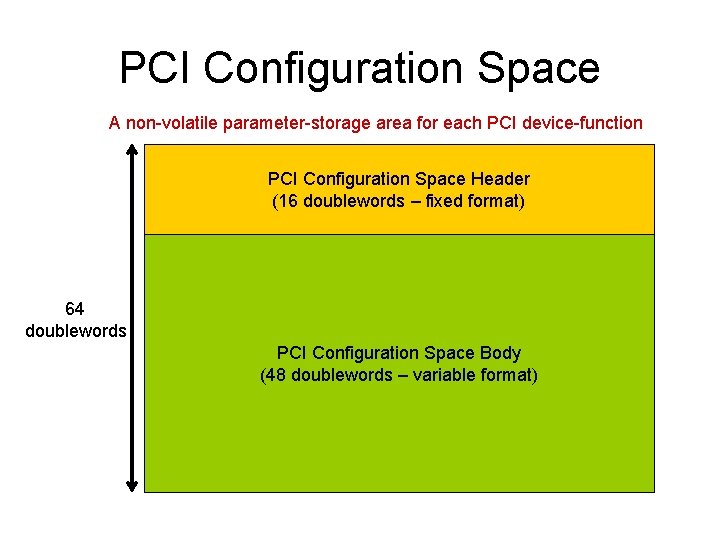

PCI Configuration Space A non-volatile parameter-storage area for each PCI device-function PCI Configuration Space Header (16 doublewords – fixed format) 64 doublewords PCI Configuration Space Body (48 doublewords – variable format)

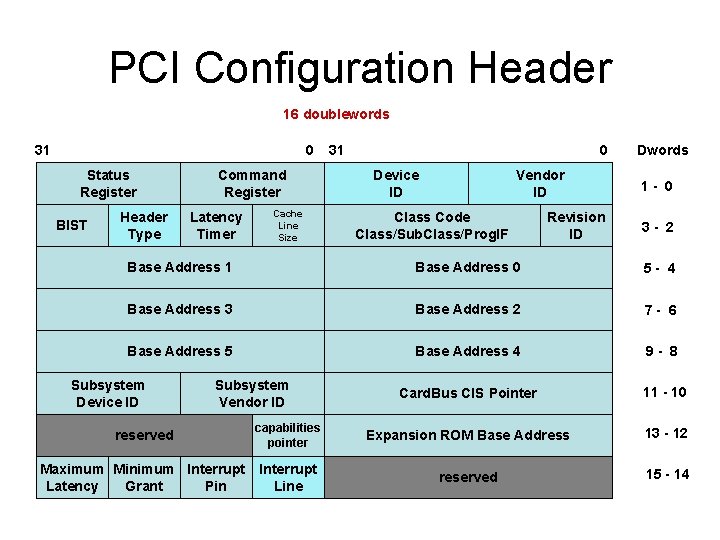

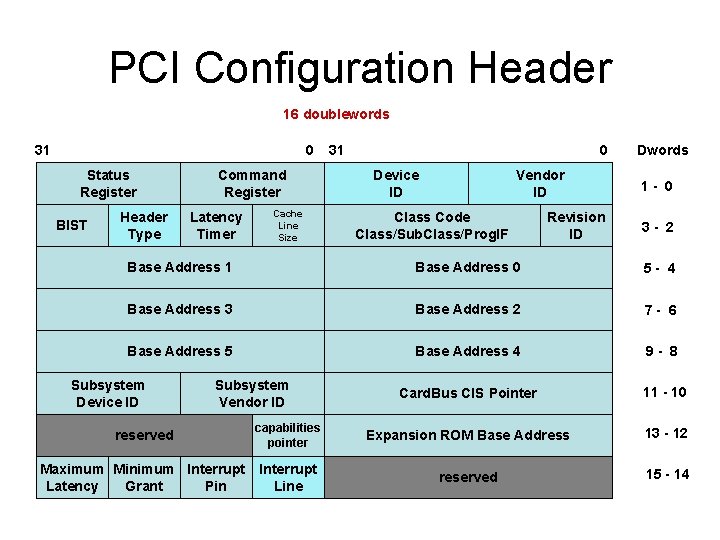

PCI Configuration Header 16 doublewords 31 0 Status Register BIST Header Type Command Register Latency Timer Cache Line Size 31 0 Device ID Vendor ID Class Code Class/Sub. Class/Prog. IF Revision ID Dwords 1 - 0 3 - 2 Base Address 1 Base Address 0 5 - 4 Base Address 3 Base Address 2 7 - 6 Base Address 5 Base Address 4 9 - 8 Card. Bus CIS Pointer 11 - 10 Subsystem Device ID Subsystem Vendor ID reserved capabilities pointer Expansion ROM Base Address 13 - 12 Maximum Minimum Interrupt Latency Grant Pin Interrupt Line reserved 15 - 14

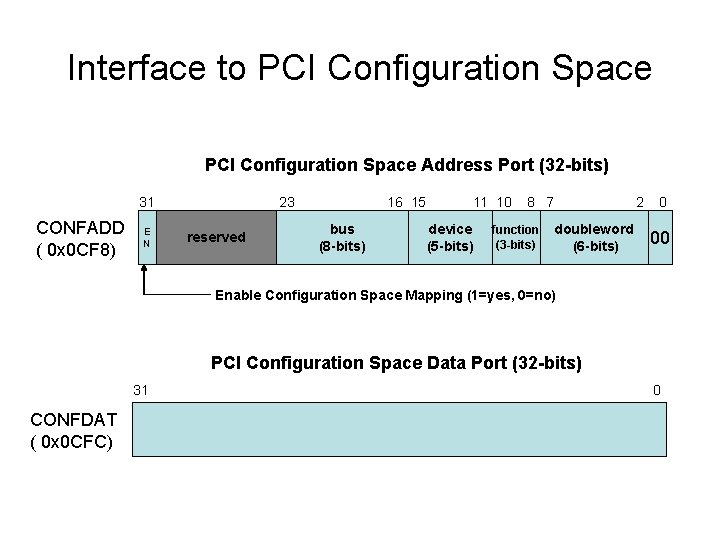

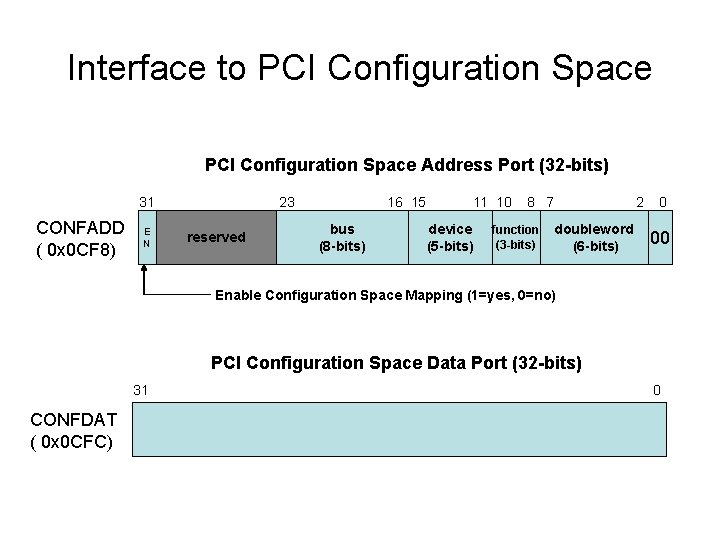

Interface to PCI Configuration Space Address Port (32 -bits) 31 CONFADD ( 0 x 0 CF 8) E N 23 reserved 16 15 bus (8 -bits) 11 10 device (5 -bits) 8 7 function (3 -bits) doubleword (6 -bits) 2 0 00 Enable Configuration Space Mapping (1=yes, 0=no) PCI Configuration Space Data Port (32 -bits) 31 CONFDAT ( 0 x 0 CFC) 0

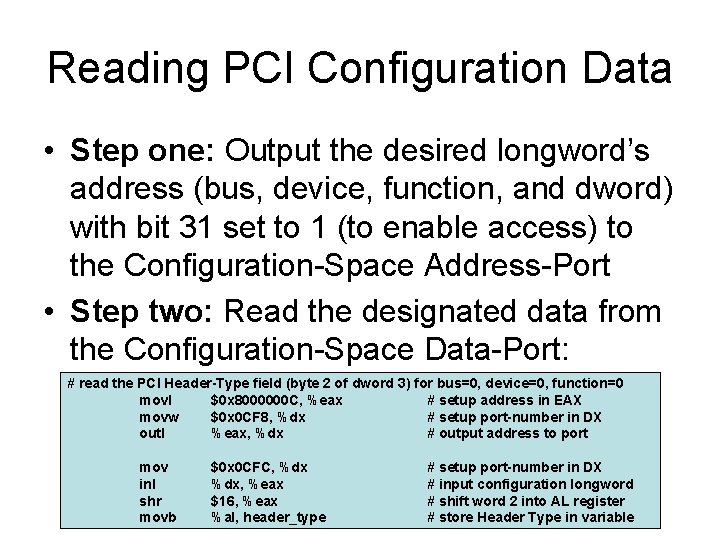

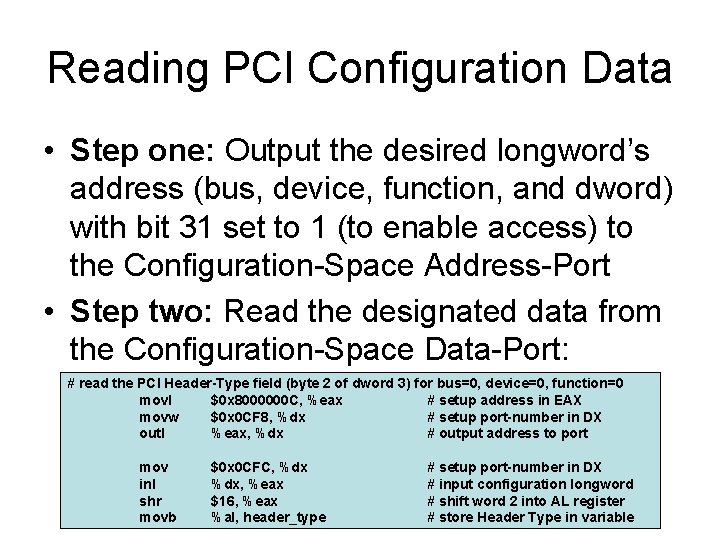

Reading PCI Configuration Data • Step one: Output the desired longword’s address (bus, device, function, and dword) with bit 31 set to 1 (to enable access) to the Configuration-Space Address-Port • Step two: Read the designated data from the Configuration-Space Data-Port: # read the PCI Header-Type field (byte 2 of dword 3) for bus=0, device=0, function=0 movl $0 x 8000000 C, %eax # setup address in EAX movw $0 x 0 CF 8, %dx # setup port-number in DX outl %eax, %dx # output address to port mov inl shr movb $0 x 0 CFC, %dx, %eax $16, %eax %al, header_type # setup port-number in DX # input configuration longword # shift word 2 into AL register # store Header Type in variable

Graphics programs • What a graphics program must do is put appropriate bit-patterns into the correct locations in the VRAM, so that the CRT will show an array of colored dots which in some way is meaningful to the human eye • So the programmer must understand what the CRT will do with the contents of VRAM

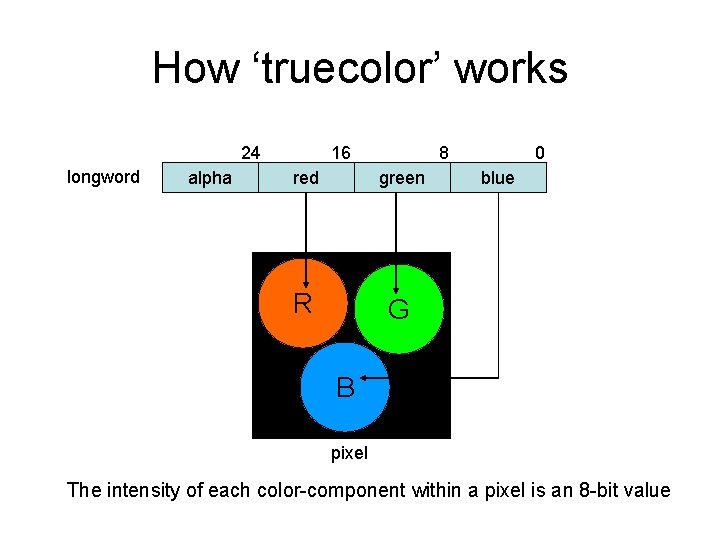

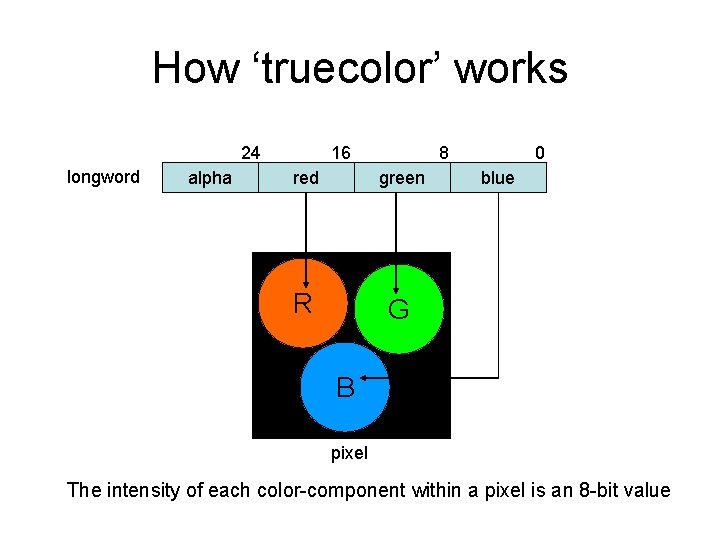

How ‘truecolor’ works 24 longword alpha 16 8 red green R G 0 blue B pixel The intensity of each color-component within a pixel is an 8 -bit value

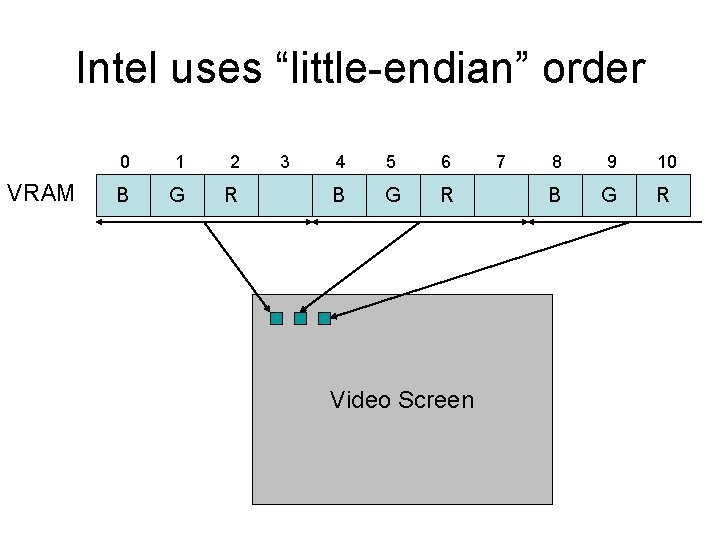

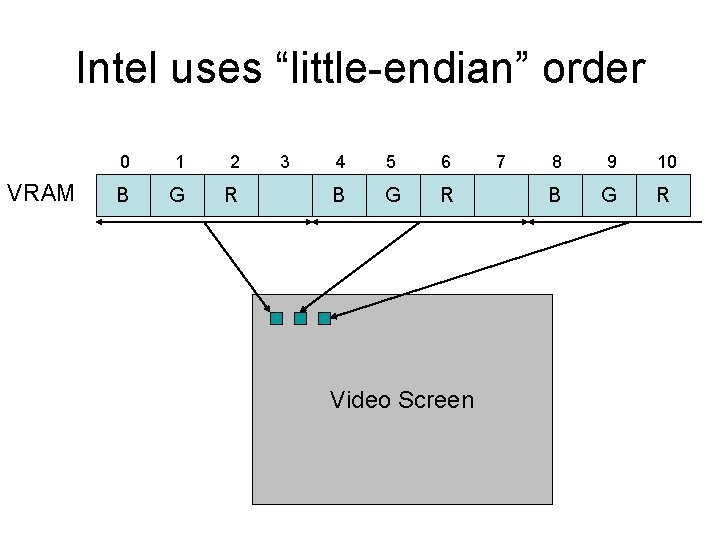

Intel uses “little-endian” order VRAM 0 1 2 B G R 3 4 5 6 B G R Video Screen 7 8 9 10 B G R

Vendor incompatibilities • Several competing vendors manufacture graphics controllers for the PC market • They’re based in various parts of the world (e. g. , United States, Canada, Taiwan, etc. ) • Their hardware designs are not identical • The VESA (Video Electronics Standards Association) organization was created to create a standardized firmware interface

VBE 3. 0 • The VESA BIOS Extensions document is accessible on our CS 630 course website • It implements services in a manner similar to the ROM-BIOS routines we’ve used in our previous boot-time applications (e. g. , via software interrupt-0 x 10) • We’ve created a demo-program (named ‘vesademo. s’) illustrating VESA’s use

Typical ‘program-structure’ Usual steps within a graphics application: – – Initialize video system hardware Display some graphical imagery Wait for a termination condition Restore original hardware state

Hardware Initialization • The SVGA system has over 300 registers which must be individually reprogrammed • It would take us many months to learn how they all work to support a graphics mode • For now, we just ‘reuse’ vendor-supplied routines, built into the SVGA firmware • They usually support quite a few different screen-resolutions and color-depths

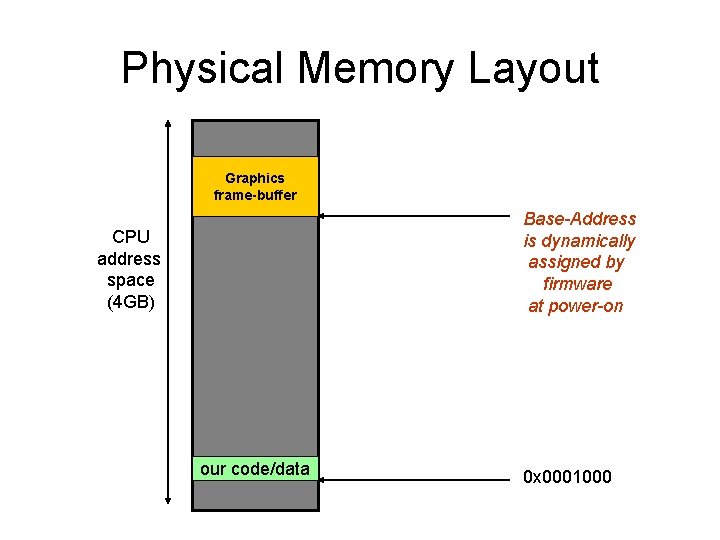

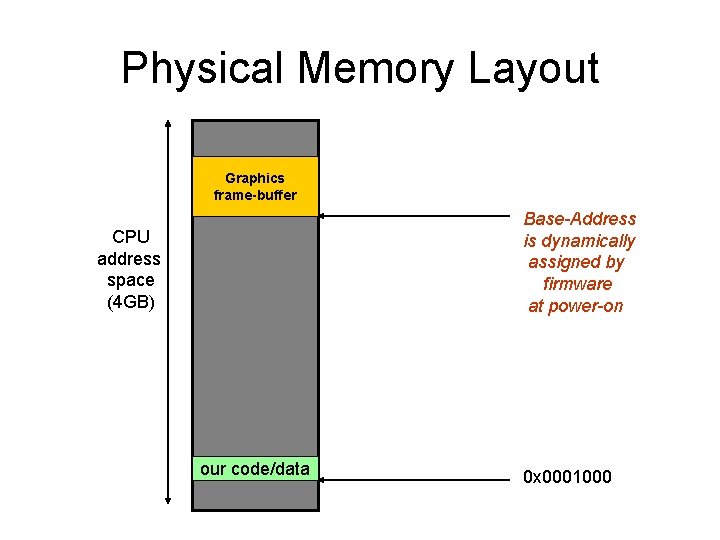

Physical Memory Layout Graphics frame-buffer Base-Address is dynamically assigned by firmware at power-on CPU address space (4 GB) our code/data 0 x 0001000

VESA function 1 • Obtains a block of parameter-values for the desired graphics display-mode: – Scanline-width (in bytes) – Horizontal resolution (in pixels) – Vertical resolution (in pixels) – Pixel-size (in bits-per-pixel) – Frame-buffer’s physical address

VESA function 2 • Reprograms all the graphics controller’s internal device registers for the selected VESA-standard display-mode

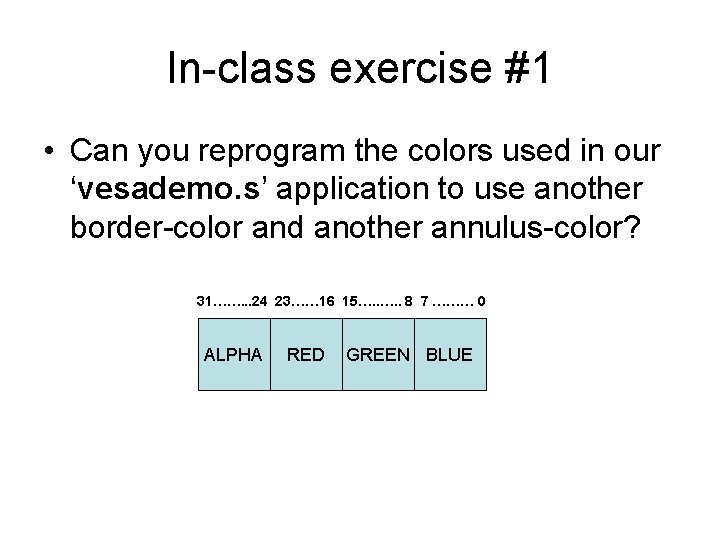

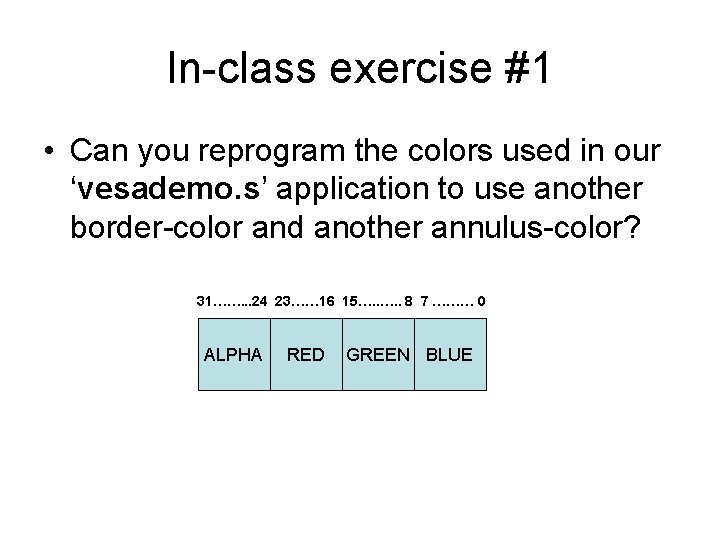

In-class exercise #1 • Can you reprogram the colors used in our ‘vesademo. s’ application to use another border-color and another annulus-color? 31……. . . 24 23…… 16 15…. . 8 7 ……… 0 ALPHA RED GREEN BLUE

In-class exercise #2 • Can you modify our demo-program so as to use a standard VESA graphics mode that has a higher screen-resolution? – Mode 0 x 0115 was for 800 -by-600, 32 bpp – Mode 0 x 0118 is for 1024 -by-768, 32 bpp