PRESPCII VCs used at the CP on Port

- Slides: 18

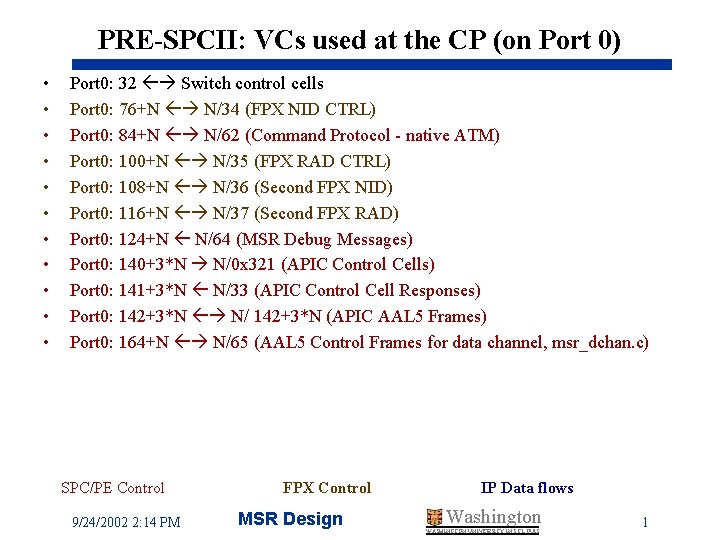

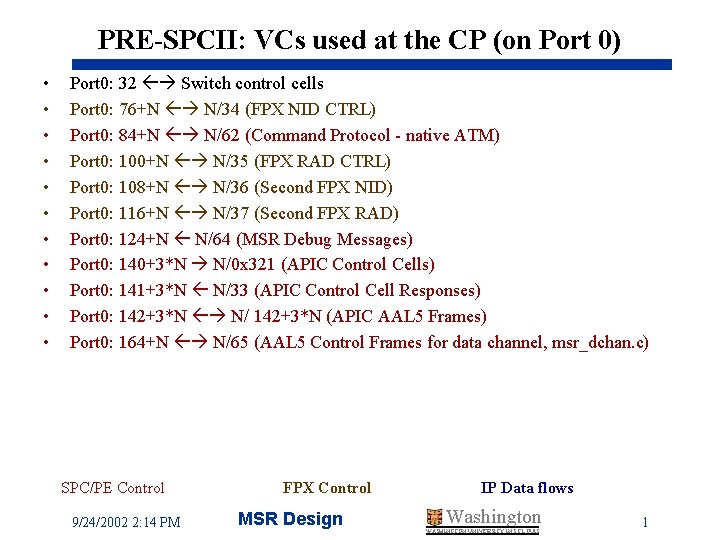

PRE-SPCII: VCs used at the CP (on Port 0) • • • Port 0: 32 Switch control cells Port 0: 76+N N/34 (FPX NID CTRL) Port 0: 84+N N/62 (Command Protocol - native ATM) Port 0: 100+N N/35 (FPX RAD CTRL) Port 0: 108+N N/36 (Second FPX NID) Port 0: 116+N N/37 (Second FPX RAD) Port 0: 124+N N/64 (MSR Debug Messages) Port 0: 140+3*N N/0 x 321 (APIC Control Cells) Port 0: 141+3*N N/33 (APIC Control Cell Responses) Port 0: 142+3*N N/ 142+3*N (APIC AAL 5 Frames) Port 0: 164+N N/65 (AAL 5 Control Frames for data channel, msr_dchan. c) SPC/PE Control 9/24/2002 2: 14 PM FPX Control MSR Design IP Data flows Washington WASHINGTON UNIVERSITY IN ST LOUIS 1

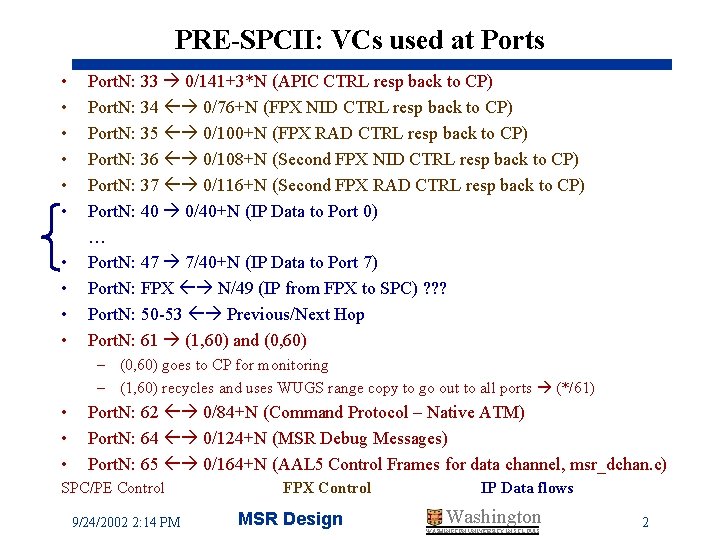

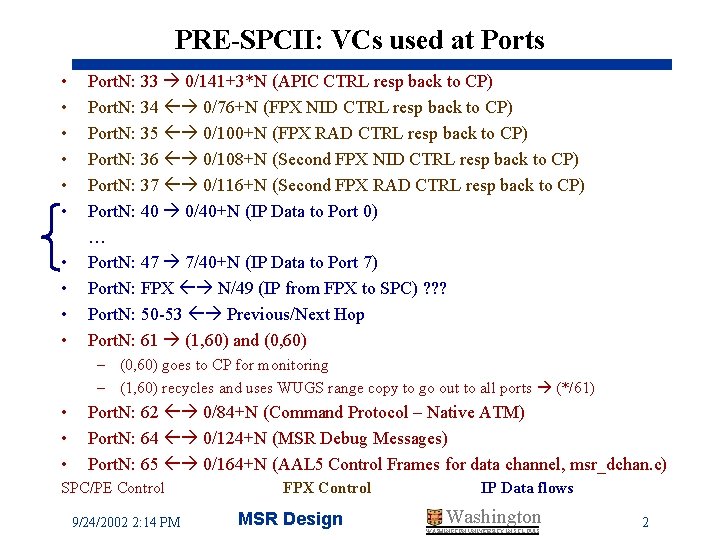

PRE-SPCII: VCs used at Ports • • • Port. N: 33 0/141+3*N (APIC CTRL resp back to CP) Port. N: 34 0/76+N (FPX NID CTRL resp back to CP) Port. N: 35 0/100+N (FPX RAD CTRL resp back to CP) Port. N: 36 0/108+N (Second FPX NID CTRL resp back to CP) Port. N: 37 0/116+N (Second FPX RAD CTRL resp back to CP) Port. N: 40 0/40+N (IP Data to Port 0) … Port. N: 47 7/40+N (IP Data to Port 7) Port. N: FPX N/49 (IP from FPX to SPC) ? ? ? Port. N: 50 -53 Previous/Next Hop Port. N: 61 (1, 60) and (0, 60) – (0, 60) goes to CP for monitoring – (1, 60) recycles and uses WUGS range copy to go out to all ports (*/61) • • • Port. N: 62 0/84+N (Command Protocol – Native ATM) Port. N: 64 0/124+N (MSR Debug Messages) Port. N: 65 0/164+N (AAL 5 Control Frames for data channel, msr_dchan. c) SPC/PE Control 9/24/2002 2: 14 PM FPX Control MSR Design IP Data flows Washington WASHINGTON UNIVERSITY IN ST LOUIS 2

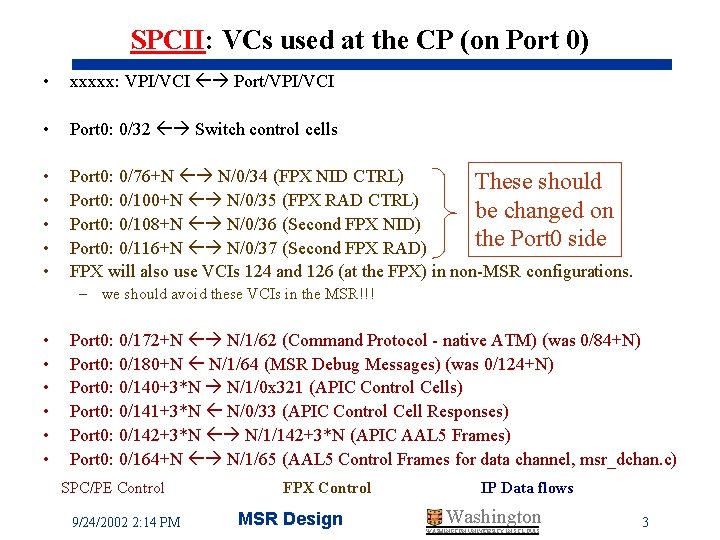

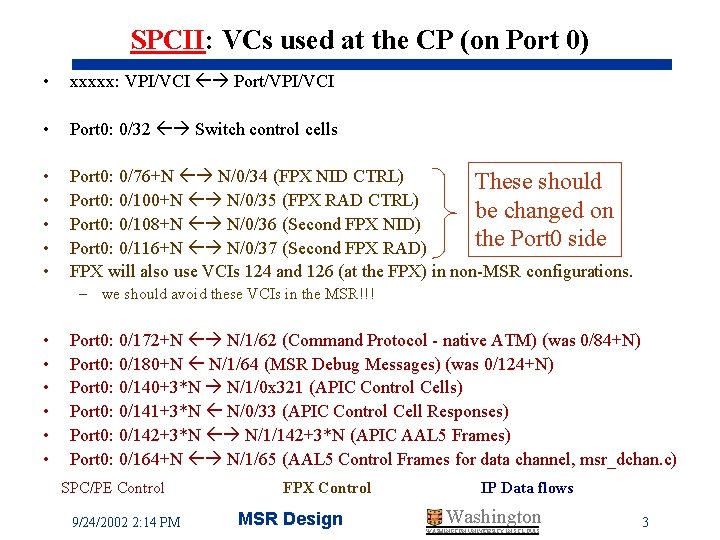

SPCII: VCs used at the CP (on Port 0) • xxxxx: VPI/VCI Port/VPI/VCI • Port 0: 0/32 Switch control cells • • • Port 0: 0/76+N N/0/34 (FPX NID CTRL) These should Port 0: 0/100+N N/0/35 (FPX RAD CTRL) be changed on Port 0: 0/108+N N/0/36 (Second FPX NID) the Port 0 side Port 0: 0/116+N N/0/37 (Second FPX RAD) FPX will also use VCIs 124 and 126 (at the FPX) in non-MSR configurations. – we should avoid these VCIs in the MSR!!! • • • Port 0: 0/172+N N/1/62 (Command Protocol - native ATM) (was 0/84+N) Port 0: 0/180+N N/1/64 (MSR Debug Messages) (was 0/124+N) Port 0: 0/140+3*N N/1/0 x 321 (APIC Control Cells) Port 0: 0/141+3*N N/0/33 (APIC Control Cell Responses) Port 0: 0/142+3*N N/1/142+3*N (APIC AAL 5 Frames) Port 0: 0/164+N N/1/65 (AAL 5 Control Frames for data channel, msr_dchan. c) SPC/PE Control 9/24/2002 2: 14 PM FPX Control MSR Design IP Data flows Washington WASHINGTON UNIVERSITY IN ST LOUIS 3

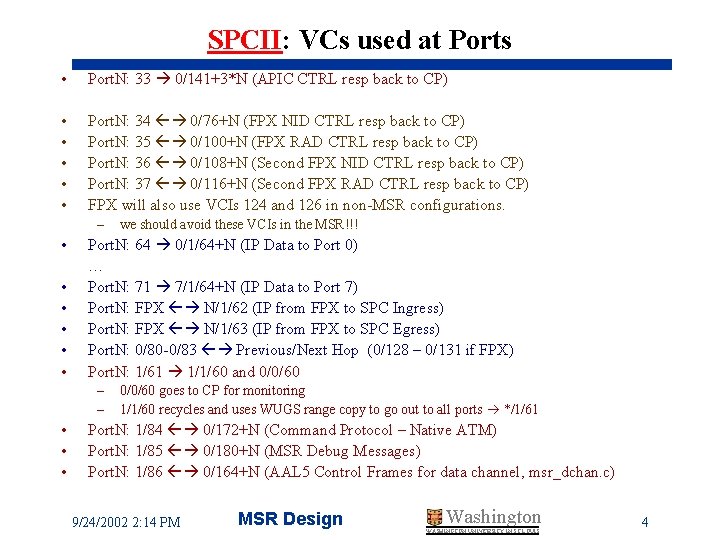

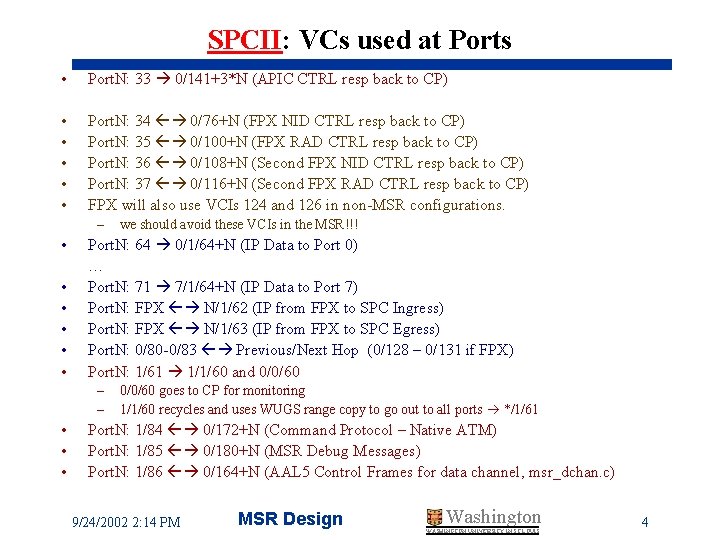

SPCII: VCs used at Ports • Port. N: 33 0/141+3*N (APIC CTRL resp back to CP) • • • Port. N: 34 0/76+N (FPX NID CTRL resp back to CP) Port. N: 35 0/100+N (FPX RAD CTRL resp back to CP) Port. N: 36 0/108+N (Second FPX NID CTRL resp back to CP) Port. N: 37 0/116+N (Second FPX RAD CTRL resp back to CP) FPX will also use VCIs 124 and 126 in non-MSR configurations. – • • • Port. N: 64 0/1/64+N (IP Data to Port 0) … Port. N: 71 7/1/64+N (IP Data to Port 7) Port. N: FPX N/1/62 (IP from FPX to SPC Ingress) Port. N: FPX N/1/63 (IP from FPX to SPC Egress) Port. N: 0/80 -0/83 Previous/Next Hop (0/128 – 0/131 if FPX) Port. N: 1/61 1/1/60 and 0/0/60 – – • • • we should avoid these VCIs in the MSR!!! 0/0/60 goes to CP for monitoring 1/1/60 recycles and uses WUGS range copy to go out to all ports */1/61 Port. N: 1/84 0/172+N (Command Protocol – Native ATM) Port. N: 1/85 0/180+N (MSR Debug Messages) Port. N: 1/86 0/164+N (AAL 5 Control Frames for data channel, msr_dchan. c) 9/24/2002 2: 14 PM MSR Design Washington WASHINGTON UNIVERSITY IN ST LOUIS 4

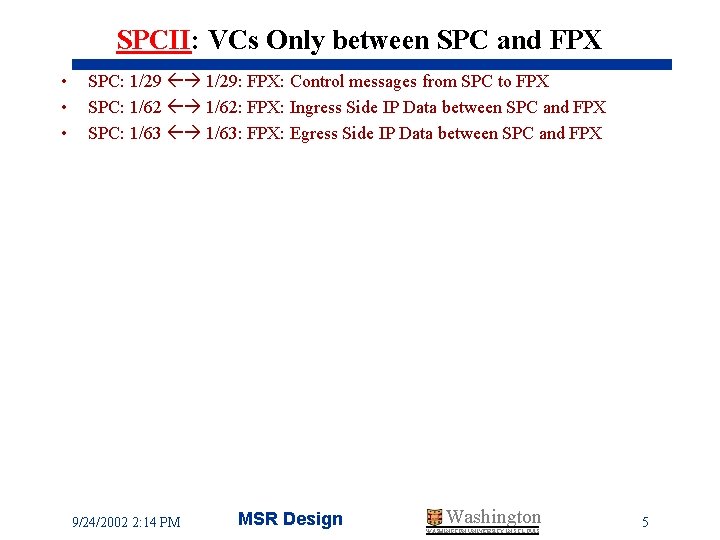

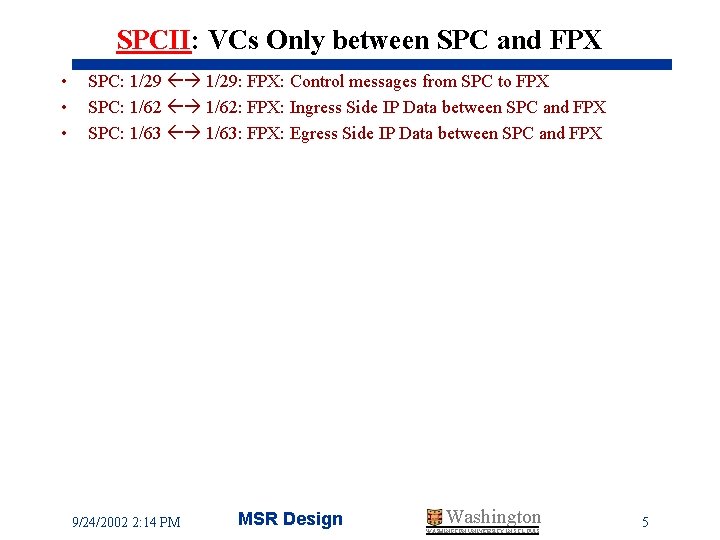

SPCII: VCs Only between SPC and FPX • • • SPC: 1/29: FPX: Control messages from SPC to FPX SPC: 1/62: FPX: Ingress Side IP Data between SPC and FPX SPC: 1/63: FPX: Egress Side IP Data between SPC and FPX 9/24/2002 2: 14 PM MSR Design Washington WASHINGTON UNIVERSITY IN ST LOUIS 5

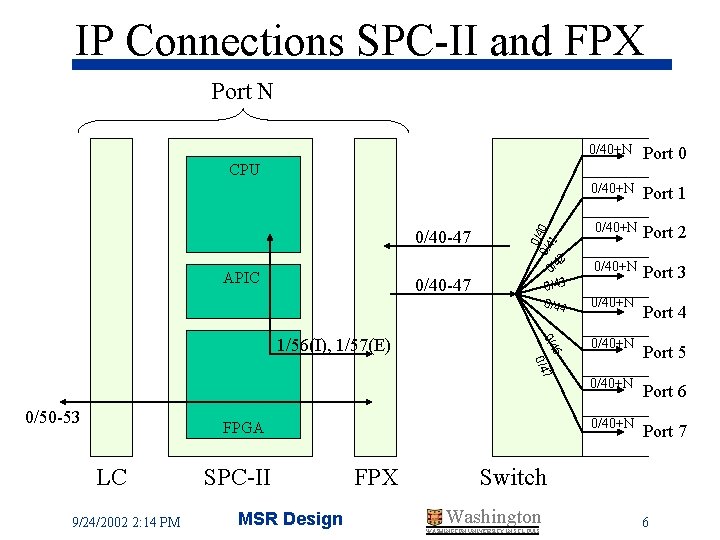

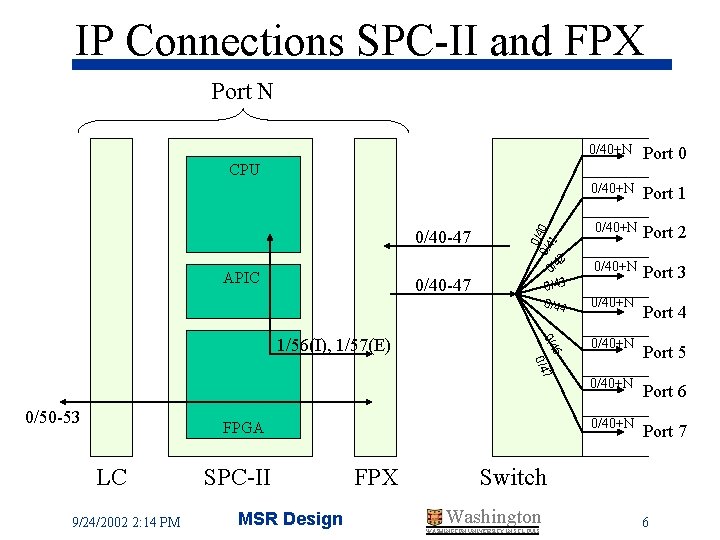

IP Connections SPC-II and FPX Port N 0/40+N Port 0 0/40+N Port 1 0/40+N Port 2 42 0/ 0/43 0/40+N Port 3 0/44 0/40+N Port 5 0/40+N Port 6 0/40+N Port 7 0/40 -47 APIC 0 0/4 /40 1 CPU 0/40 -47 6 1/56(I), 1/57(E) 7 0/4 0/50 -53 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 6

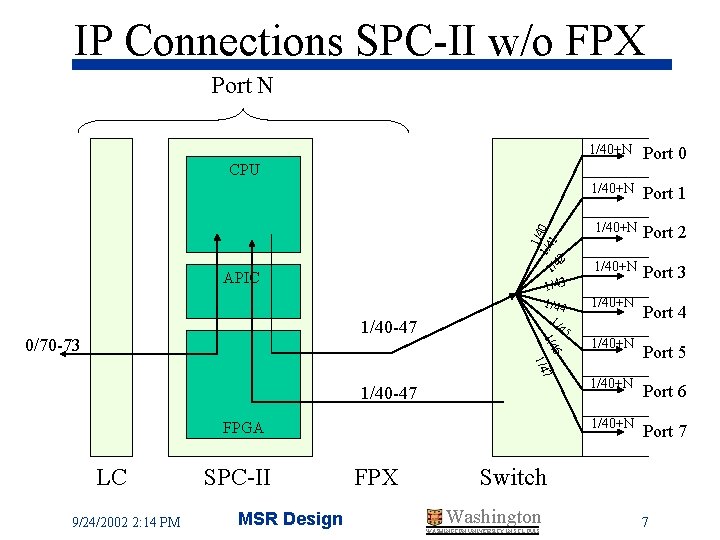

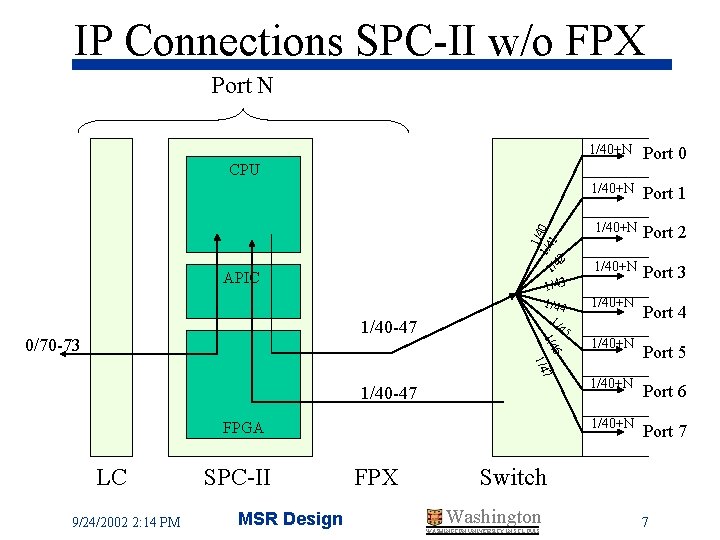

IP Connections SPC-II w/o FPX Port N 1/40+N Port 0 1/40+N Port 1 1/40+N Port 2 1/40+N Port 3 1/40+N Port 4 1/40+N Port 5 1/40+N Port 6 1/40+N Port 7 1 1/4 /40 1 CPU 42 1/ 1/43 APIC 1/44 1/ 45 1/40 -47 6 1/4 0/70 -73 7 1/40 -47 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 7

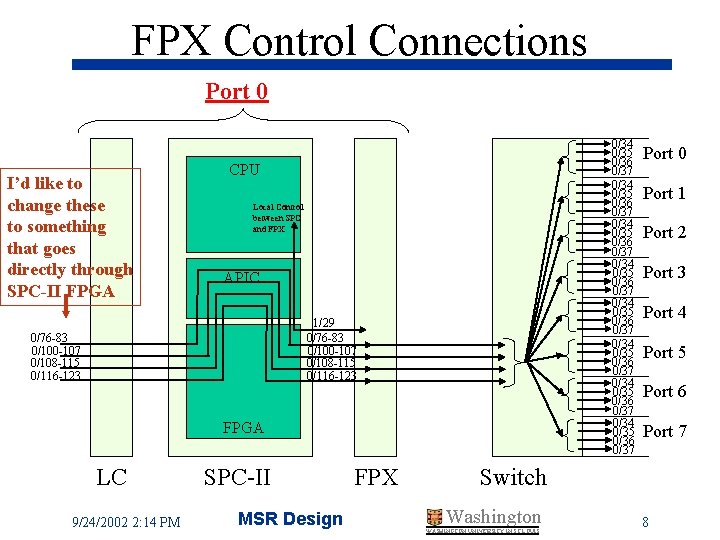

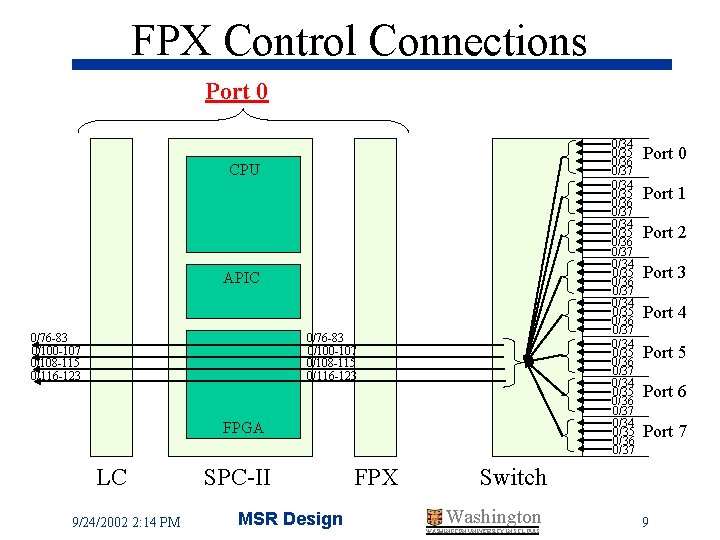

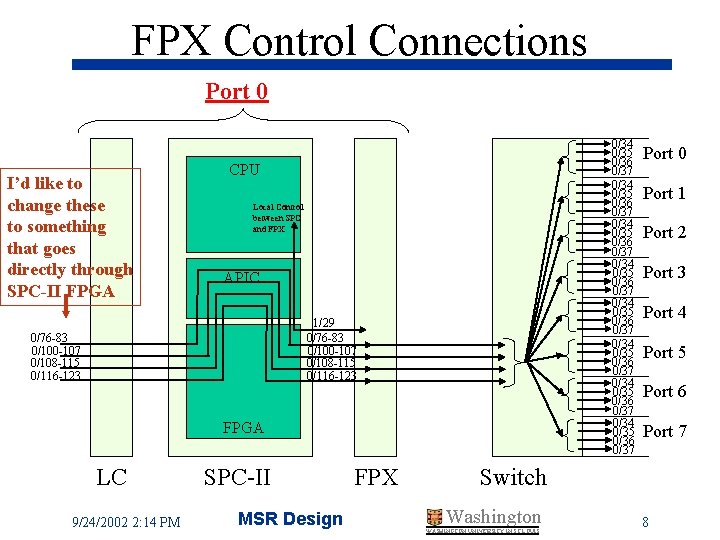

FPX Control Connections Port 0 I’d like to change these to something that goes directly through SPC-II FPGA 0/34 0/35 0/36 0/37 0/34 0/35 0/36 0/37 CPU Local Control between SPC and FPX APIC 1/29 0/76 -83 0/100 -107 0/108 -115 0/116 -123 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX Port 0 Port 1 Port 2 Port 3 Port 4 Port 5 Port 6 Port 7 Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 8

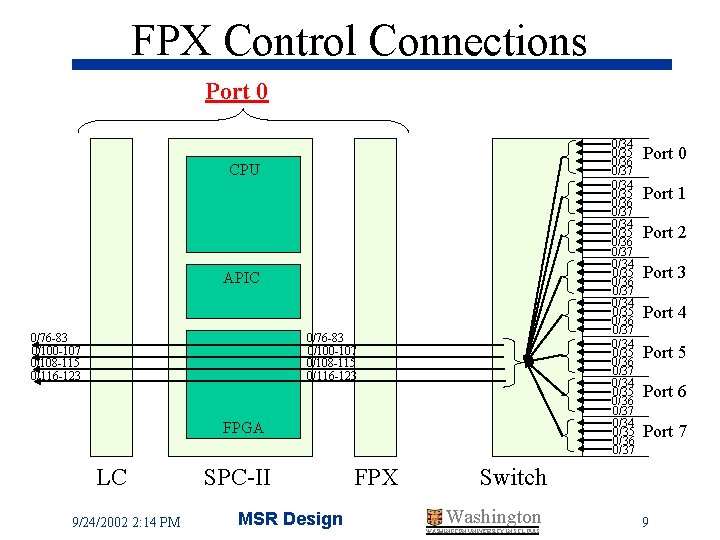

FPX Control Connections Port 0 0/34 0/35 0/36 0/37 0/34 0/35 0/36 0/37 CPU APIC 0/76 -83 0/100 -107 0/108 -115 0/116 -123 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX Port 0 Port 1 Port 2 Port 3 Port 4 Port 5 Port 6 Port 7 Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 9

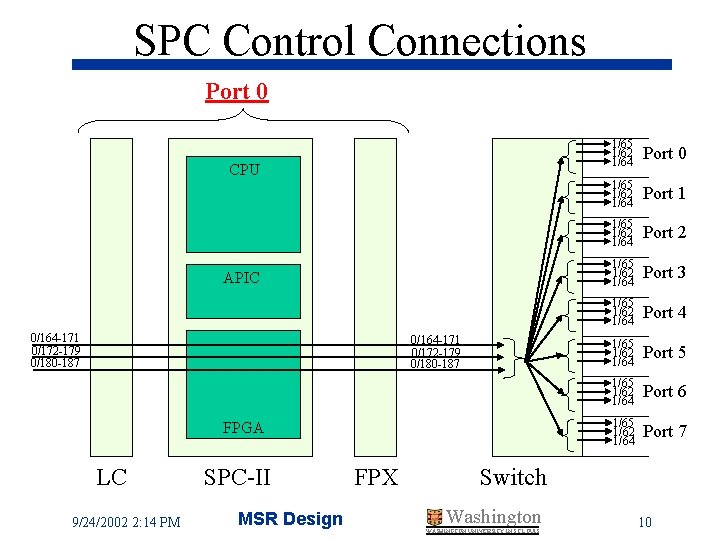

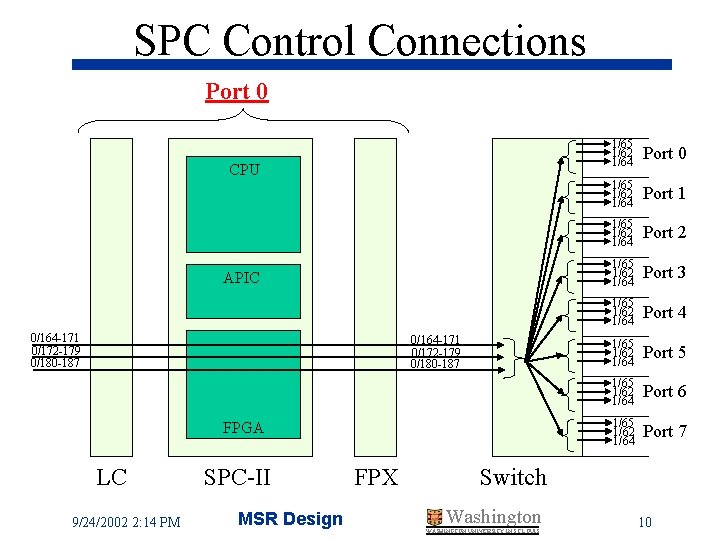

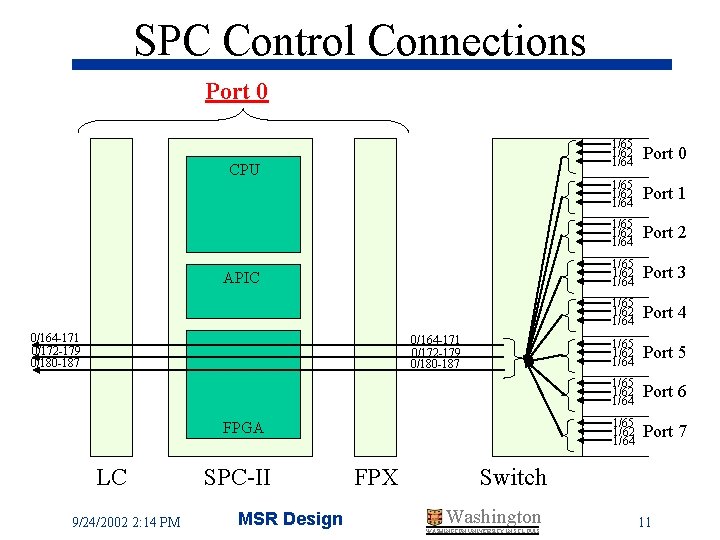

SPC Control Connections Port 0 CPU APIC 0/164 -171 0/172 -179 0/180 -187 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX 1/65 1/62 1/64 Port 0 1/65 1/62 1/64 Port 1 1/65 1/62 1/64 Port 2 1/65 1/62 1/64 Port 3 1/65 1/62 1/64 Port 4 1/65 1/62 1/64 Port 6 1/65 1/62 1/64 Port 7 Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 10

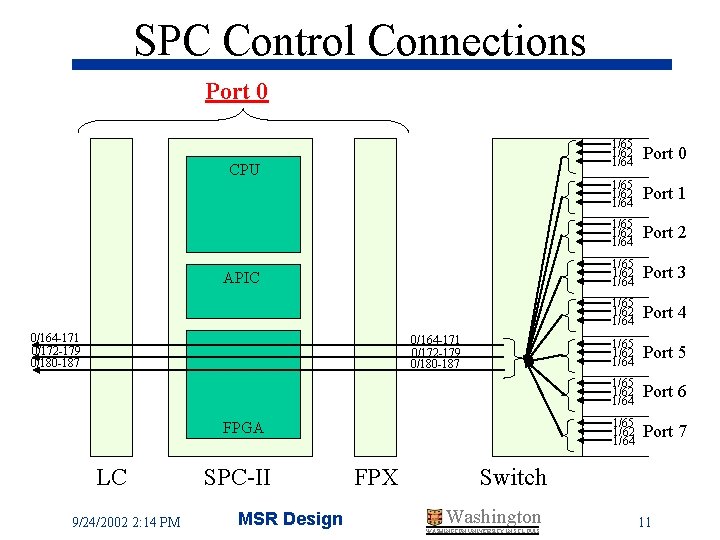

SPC Control Connections Port 0 CPU APIC 0/164 -171 0/172 -179 0/180 -187 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX 1/65 1/62 1/64 Port 0 1/65 1/62 1/64 Port 1 1/65 1/62 1/64 Port 2 1/65 1/62 1/64 Port 3 1/65 1/62 1/64 Port 4 1/65 1/62 1/64 Port 6 1/65 1/62 1/64 Port 7 Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 11

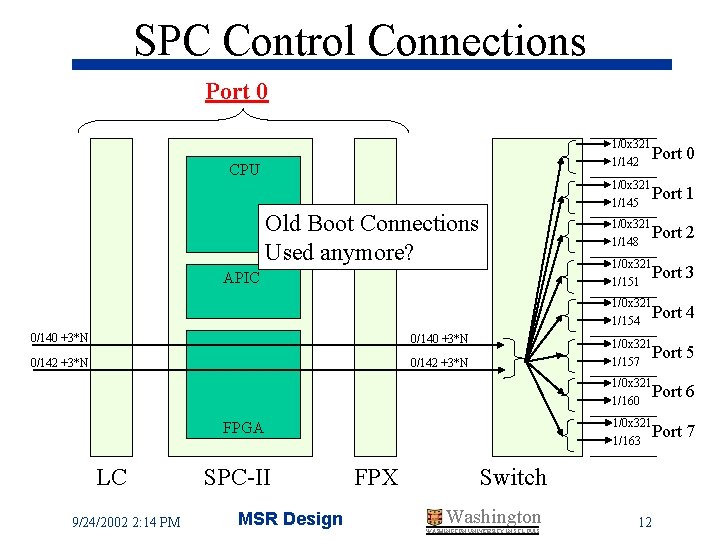

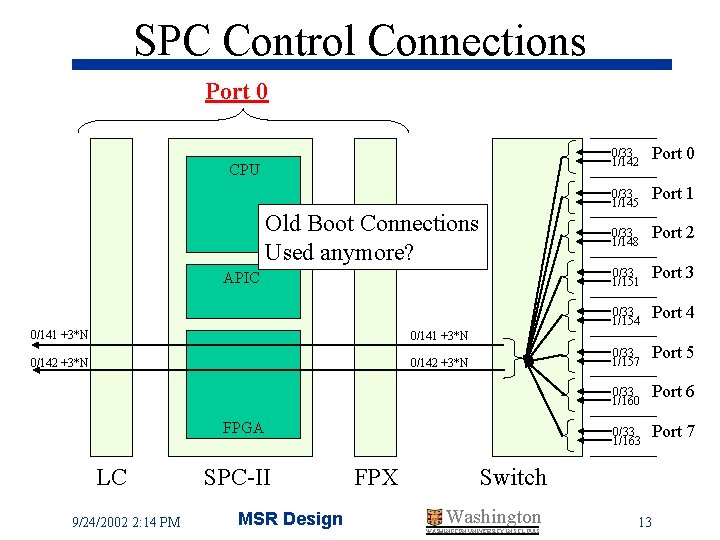

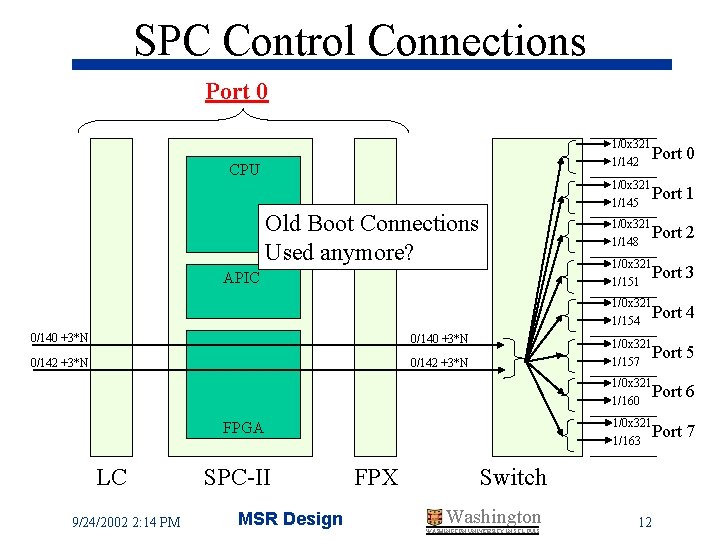

SPC Control Connections Port 0 1/0 x 321 1/142 CPU 1/0 x 321 1/145 Old Boot Connections Used anymore? 1/0 x 321 1/148 1/0 x 321 APIC 1/151 1/0 x 321 1/154 0/140 +3*N 1/0 x 321 0/142 +3*N 1/157 1/0 x 321 1/160 9/24/2002 2: 14 PM SPC-II MSR Design Port 1 Port 2 Port 3 Port 4 Port 5 Port 6 1/0 x 321 FPGA LC Port 0 1/163 FPX Port 7 Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 12

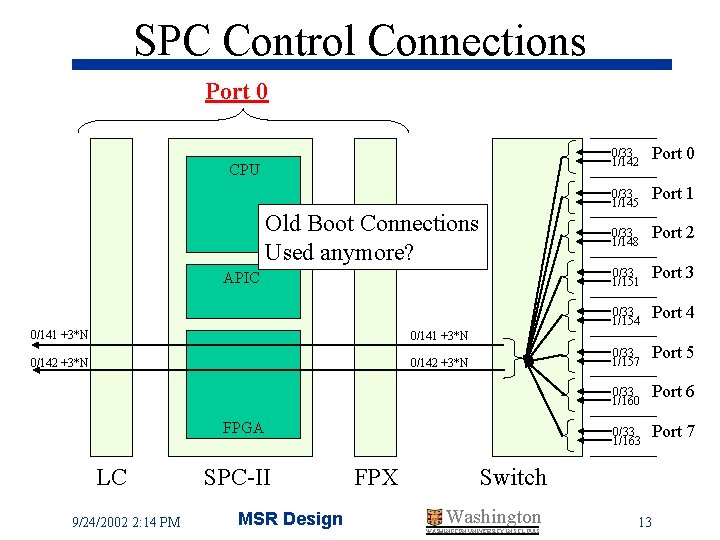

SPC Control Connections Port 0 CPU Old Boot Connections Used anymore? APIC 0/141 +3*N 0/142 +3*N FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX 0/33 1/142 Port 0 0/33 1/145 Port 1 0/33 1/148 Port 2 0/33 1/151 Port 3 0/33 1/154 Port 4 0/33 1/157 Port 5 0/33 1/160 Port 6 0/33 1/163 Port 7 Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 13

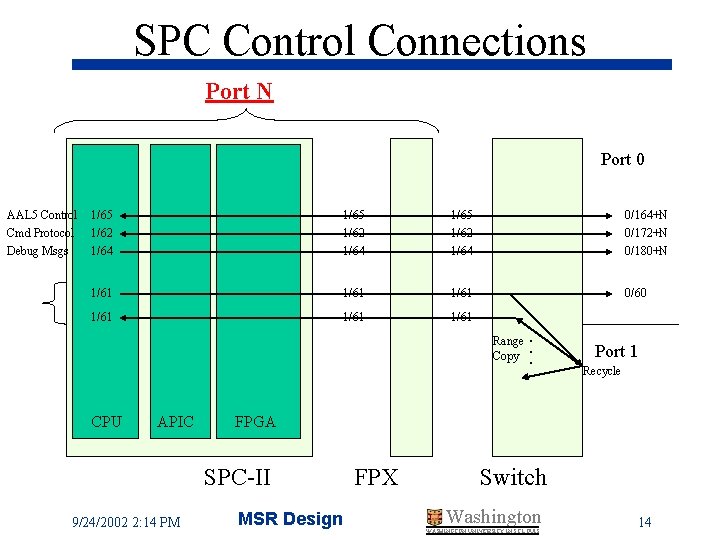

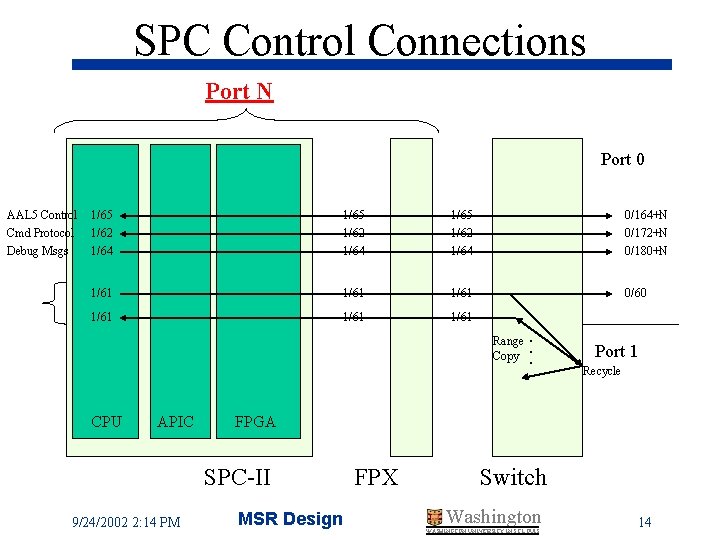

SPC Control Connections Port N Port 0 AAL 5 Control Cmd Protocol Debug Msgs 1/65 1/62 1/64 0/164+N 0/172+N 0/180+N 1/61 0/60 1/61 Range Copy CPU APIC Port 1 Recycle FPGA SPC-II 9/24/2002 2: 14 PM . . . MSR Design FPX Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 14

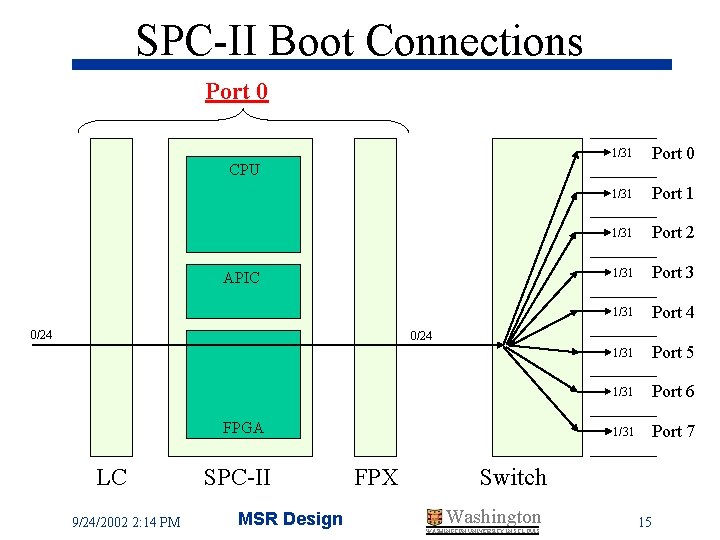

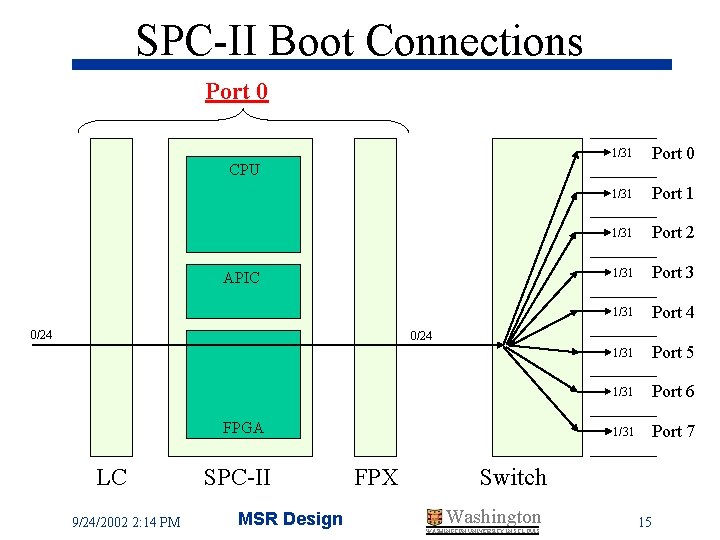

SPC-II Boot Connections Port 0 1/31 Port 1 1/31 Port 2 1/31 Port 3 1/31 Port 4 1/31 Port 5 1/31 Port 6 1/31 Port 7 CPU APIC 0/24 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 15

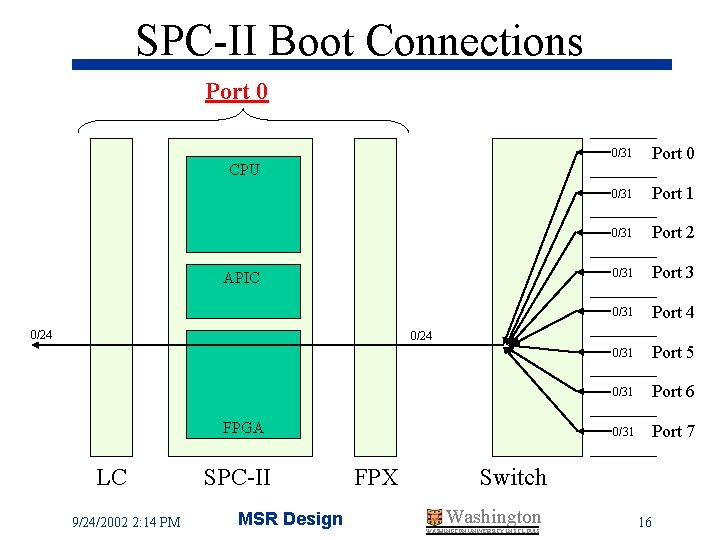

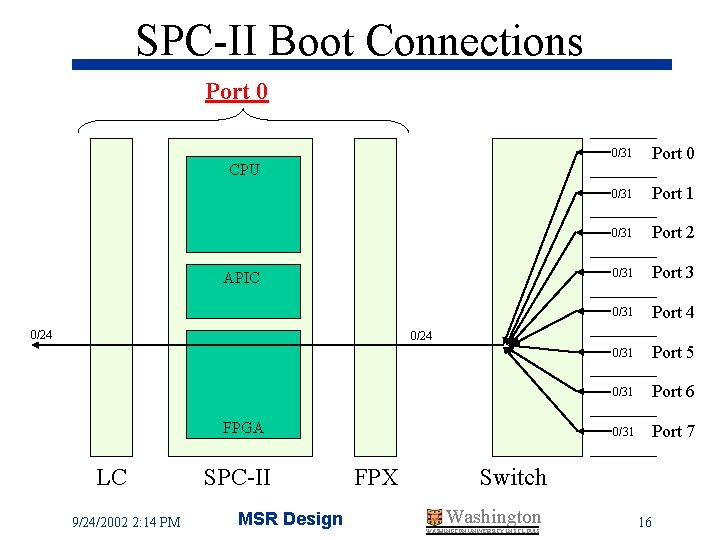

SPC-II Boot Connections Port 0 0/31 Port 1 0/31 Port 2 0/31 Port 3 0/31 Port 4 0/31 Port 5 0/31 Port 6 0/31 Port 7 CPU APIC 0/24 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design FPX Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 16

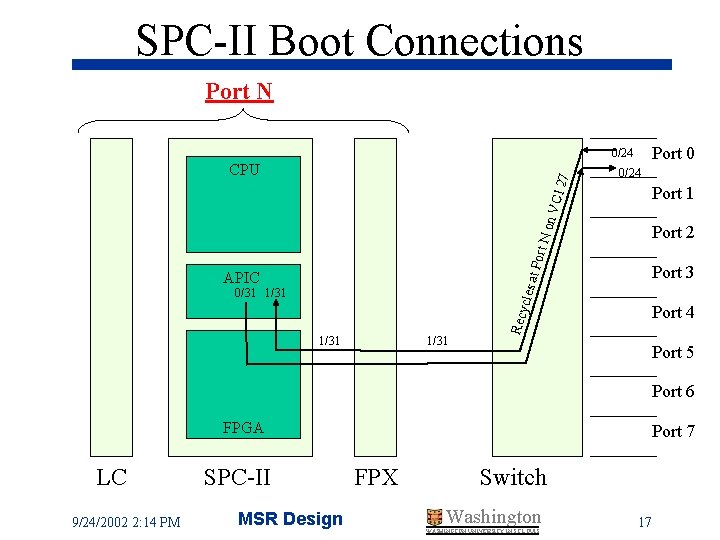

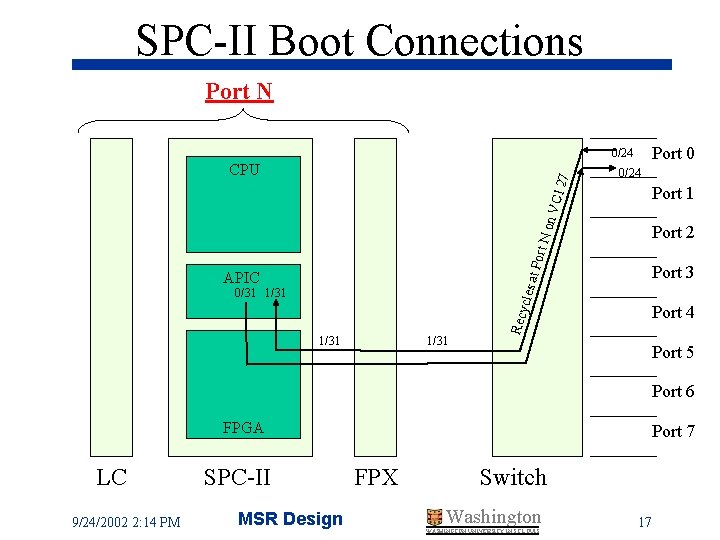

SPC-II Boot Connections Port N Port 0 0/24 at Po rt N on V CI 2 7 CPU 0/31 1/31 Recy cles APIC 0/24 Port 1 Port 2 Port 3 Port 4 Port 5 Port 6 FPGA LC 9/24/2002 2: 14 PM SPC-II MSR Design Port 7 FPX Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 17

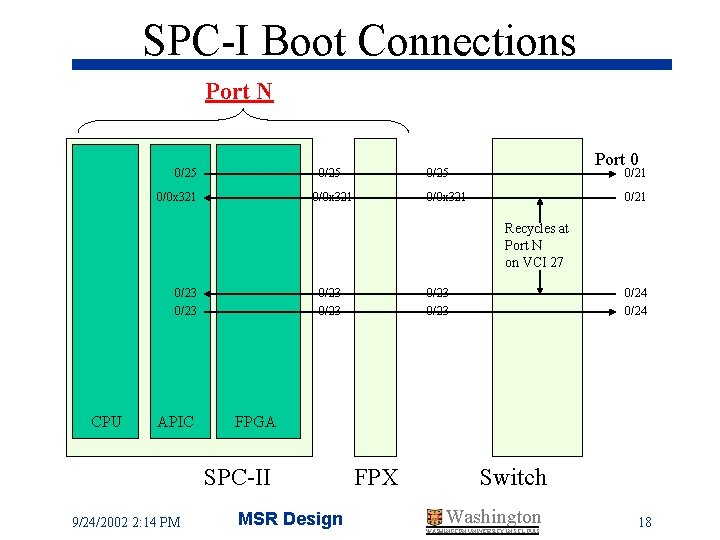

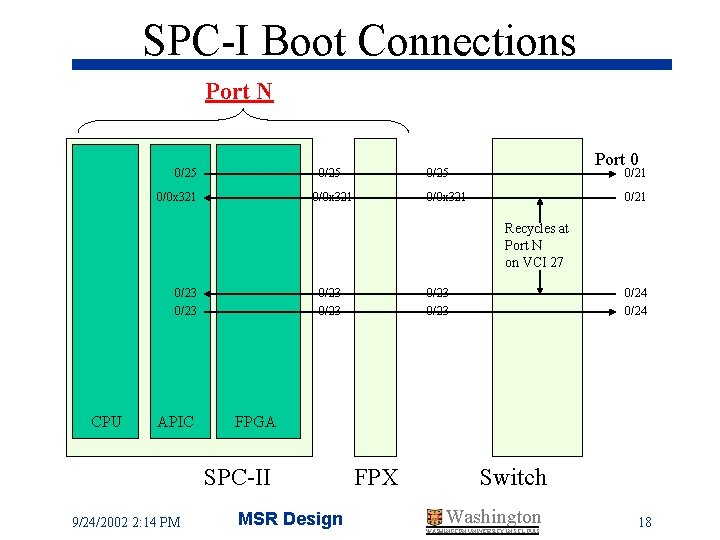

SPC-I Boot Connections Port N 0/25 0/0 x 321 Port 0 0/25 0/0 x 321 0/21 Recycles at Port N on VCI 27 0/23 CPU APIC 0/23 0/24 FPGA SPC-II 9/24/2002 2: 14 PM 0/23 MSR Design FPX Switch Washington WASHINGTON UNIVERSITY IN ST LOUIS 18