Parallel communication interface 8255 Parallel Communication Interface 8255

- Slides: 31

Parallel communication interface 8255 Parallel Communication Interface 8255 1

• • • 8255 Signals Block diagram I/O mode BSR Mode Control word Parallel Communication Interface 8255 2

• The 8255 is a widely used, programmable parallel I/O device. It can be programmed to transfer data under various conditions, from simple I/O to interrupt I/O. It is flexible, versatile and economical (when multiple I/O ports are required). • It is an important general purpose I/O device that can be used with almost any microprocessor. • The 8255 has 24 I/O pins that can be grouped primarily into two 8 bit parallel ports: A and B, with the remaining 8 bits as Port C. Parallel Communication Interface 8255 3

• The 8 bits of port C can be used as individual bits or be grouped into two 4 bit ports: CUpper (CU) and CLower (CL). The functions of these ports are defined by writing a control word in the control register. • 8255 can be used in two modes: Bit set/Reset (BSR) mode and I/O mode. The BSR mode is used to set or reset the bits in port C. The I/O mode is further divided into 3 modes: • mode 0, mode 1 and mode 2. In mode 0, all ports function as simple I/O ports. Parallel Communication Interface 8255 4

Parallel Communication Interface 8255 5

The signal description of 8255 are briefly presented as follows : PA 7 -PA 0: These are eight port A lines that acts as either latched output or buffered input lines depending upon the control word loaded into the control word register. PC 7 -PC 4 : Upper nibble of port C lines. They may act as either output latches or input buffers lines. This port also can be used for generation of handshake lines in mode 1 or mode 2. PC 3 -PC 0 : These are the lower port C lines, other details are the same as PC 7 -PC 4 lines. PB 0 -PB 7 : These are the eight port B lines which are used as latched output lines or buffered input lines in the same way as port A. Parallel Communication Interface 8255 6

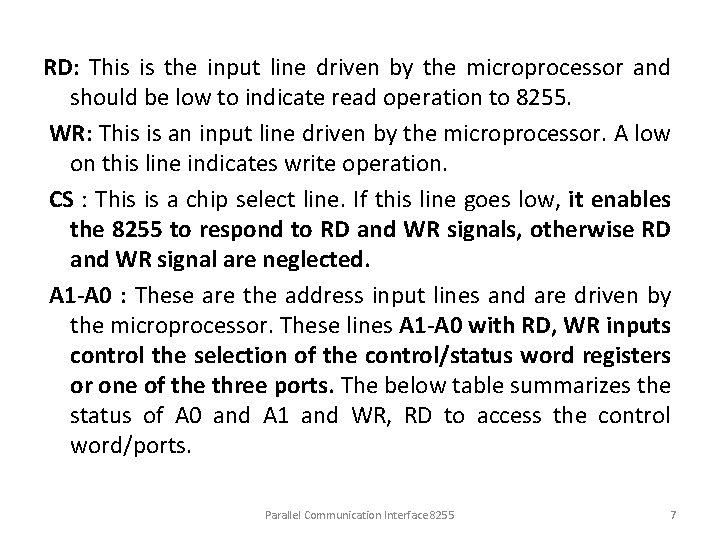

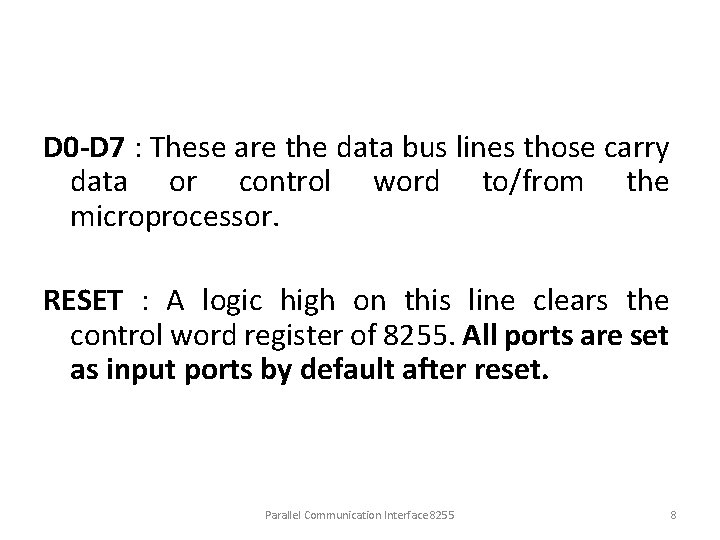

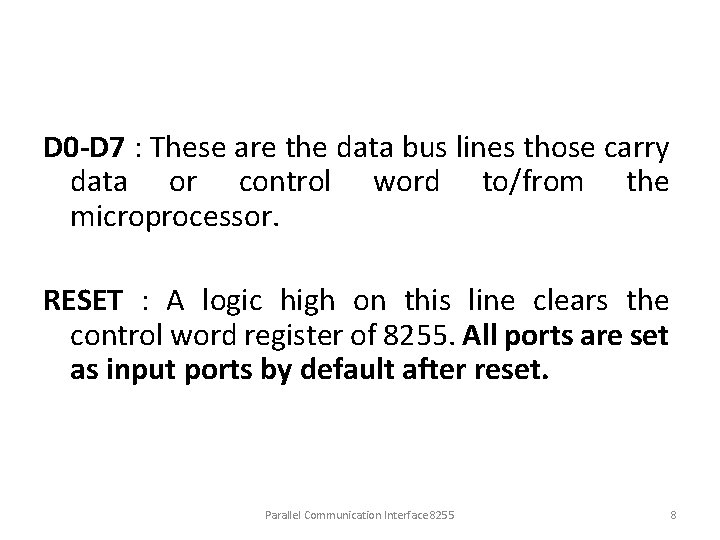

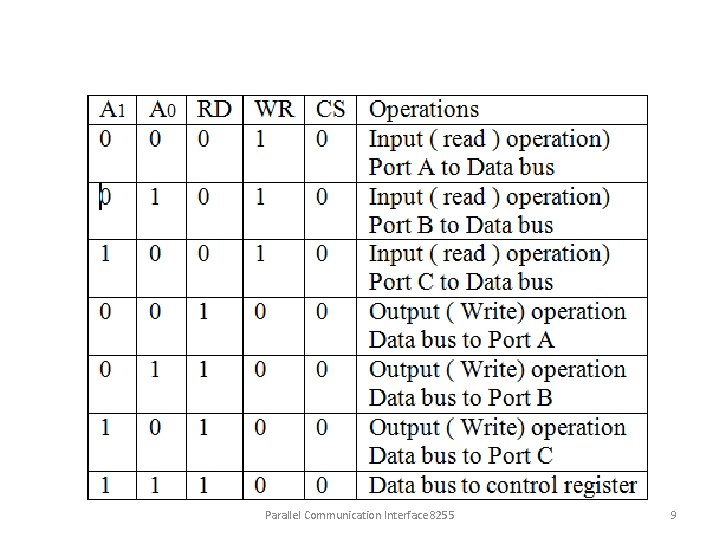

RD: This is the input line driven by the microprocessor and should be low to indicate read operation to 8255. WR: This is an input line driven by the microprocessor. A low on this line indicates write operation. CS : This is a chip select line. If this line goes low, it enables the 8255 to respond to RD and WR signals, otherwise RD and WR signal are neglected. A 1 -A 0 : These are the address input lines and are driven by the microprocessor. These lines A 1 -A 0 with RD, WR inputs control the selection of the control/status word registers or one of the three ports. The below table summarizes the status of A 0 and A 1 and WR, RD to access the control word/ports. Parallel Communication Interface 8255 7

D 0 -D 7 : These are the data bus lines those carry data or control word to/from the microprocessor. RESET : A logic high on this line clears the control word register of 8255. All ports are set as input ports by default after reset. Parallel Communication Interface 8255 8

Parallel Communication Interface 8255 9

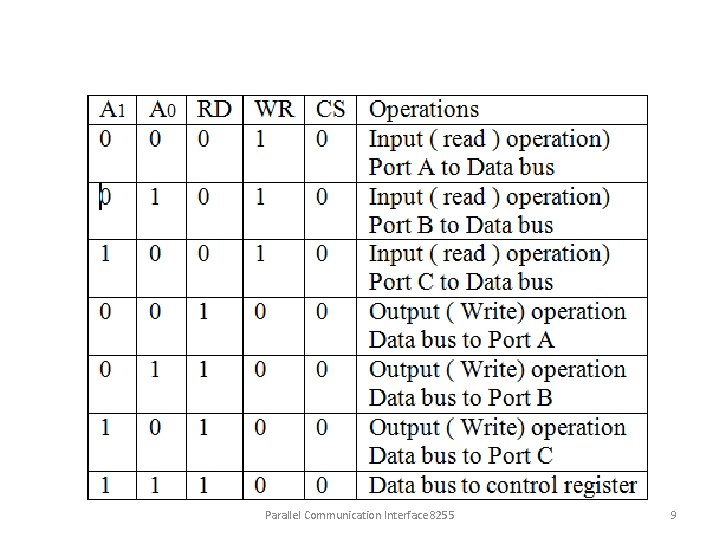

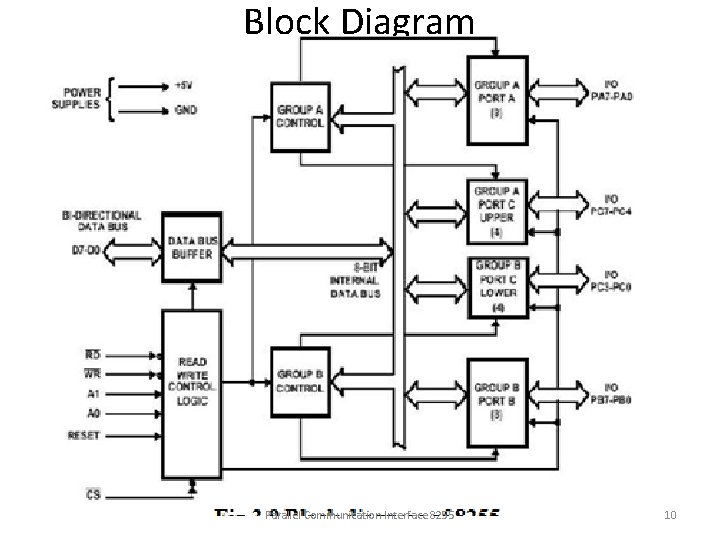

Block Diagram Parallel Communication Interface 8255 10

• Data bus buffer: The tri state buffer is used to interface the internal data bus of 8255 to the system bus. Input data to the CPU or output data from the CPU are all passed through the buffer. • Control logic: The control logic block accepts control signals as well as inputs from the address bus, and sends the commands to the individual control blocks. (Group A and Group B ) Parallel Communication Interface 8255 11

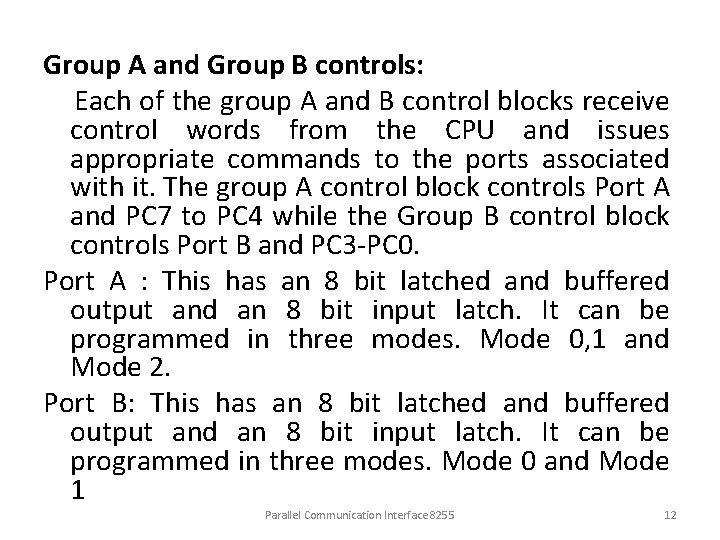

Group A and Group B controls: Each of the group A and B control blocks receive control words from the CPU and issues appropriate commands to the ports associated with it. The group A control block controls Port A and PC 7 to PC 4 while the Group B control block controls Port B and PC 3 -PC 0. Port A : This has an 8 bit latched and buffered output and an 8 bit input latch. It can be programmed in three modes. Mode 0, 1 and Mode 2. Port B: This has an 8 bit latched and buffered output and an 8 bit input latch. It can be programmed in three modes. Mode 0 and Mode 1 Parallel Communication Interface 8255 12

PORT C: This has an 8 bit unlatched input buffer and an 8 bit output latch/buffer. Port C can be separated into two ports and each can be used as control signals for Ports A and B in the handshake mode. It can be programmed for bit set/reset operation. Parallel Communication Interface 8255 13

Operating Modes 1. BSR Mode The individual bits of Port C can be set or reset by sending out a single OUT instruction to the control register. When Port C is used for control/status operation, this feature can be used to set or reset individual bits. Parallel Communication Interface 8255 14

2. I/O Mode 0: Simple Input or Output • In this mode, Port A and Port B are used as two simple 8 -bit I/O ports and Port C as two 4 -bit I/O ports. Each port (or half-port, in case of Port C) can be programmed to function as simply an input port or an output port. The input/output features in mode 0 are: Outputs are latched, Inputs are not latched. Ports do not have handshake or interrupt capability. Parallel Communication Interface 8255 15

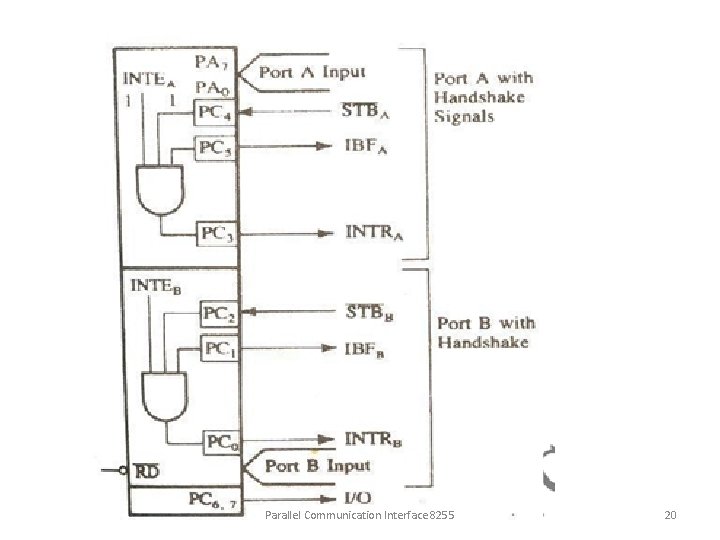

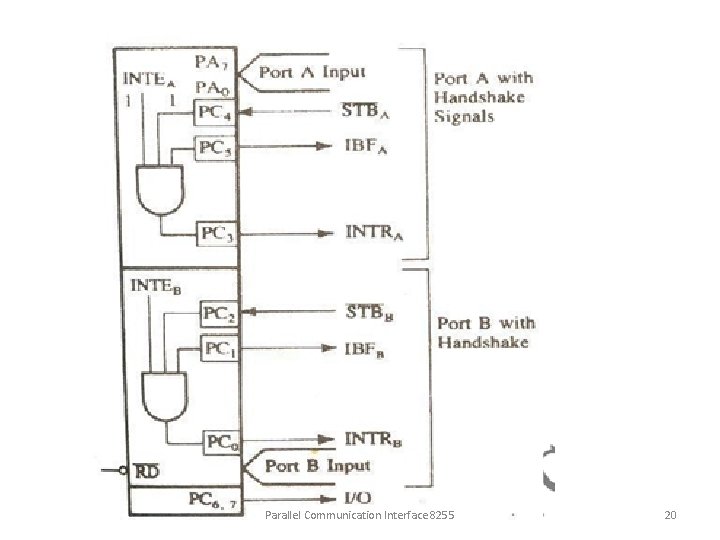

Mode 1: Input or Output with handshake • In mode 1, handshake signals are exchanged between the microprocessor and peripherals prior to data transfer. • The ports (A and B) function as 8 -bit I/O ports. They can be configured either as input or output ports. • Each port (Port A and Port B) uses 3 lines from port C as handshake signals. The remaining two lines of port C can be used for simple I/O functions. Input and output data are latched and Interrupt logic is supported. Parallel Communication Interface 8255 16

Hand shaking signals are used to transfer data between devices whose data transfer speeds are not same. For Example: Computers can send data to the printer with large speed but printer cannot accept data and print data with this rate. So computer has to send data with the speed with which printer can accept. This type of data transfer is achieved by using handshaking signals along with data signals. Parallel Communication Interface 8255 17

Hand Shake Signals Data bus STB Computer Printer ACK Busy Parallel Communication Interface 8255 18

These handshaking signals are used to tell computer whether printer is ready to accept the data or not. If printer is ready to accept the data then after sending data on data bus, computer uses another handshaking signal STB to tell printer that valid data is available on the data bus. Parallel Communication Interface 8255 19

Parallel Communication Interface 8255 20

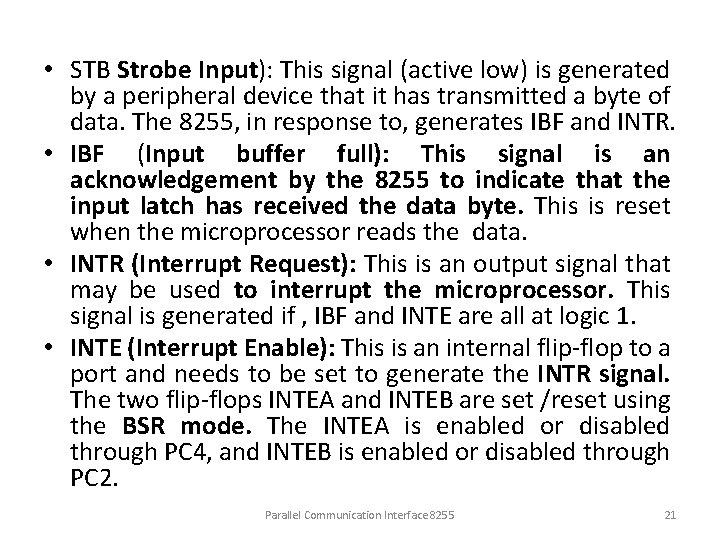

• STB Strobe Input): This signal (active low) is generated by a peripheral device that it has transmitted a byte of data. The 8255, in response to, generates IBF and INTR. • IBF (Input buffer full): This signal is an acknowledgement by the 8255 to indicate that the input latch has received the data byte. This is reset when the microprocessor reads the data. • INTR (Interrupt Request): This is an output signal that may be used to interrupt the microprocessor. This signal is generated if , IBF and INTE are all at logic 1. • INTE (Interrupt Enable): This is an internal flip-flop to a port and needs to be set to generate the INTR signal. The two flip-flops INTEA and INTEB are set /reset using the BSR mode. The INTEA is enabled or disabled through PC 4, and INTEB is enabled or disabled through PC 2. Parallel Communication Interface 8255 21

Mode 2: Bidirectional Data Transfer • This mode is used primarily in applications such as data transfer between the two computers. • Port A can be configured as the bidirectional port and Port B either in mode 0 or mode 1. Port A uses five signals from Port C as handshake signals for data transfer. • The remaining three lines from Port C can be used either as simple I/O or as handshake signals for Port B. Parallel Communication Interface 8255 22

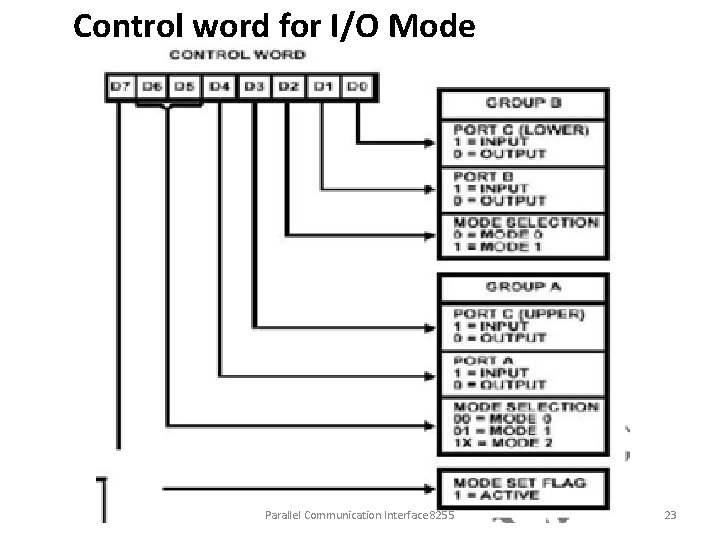

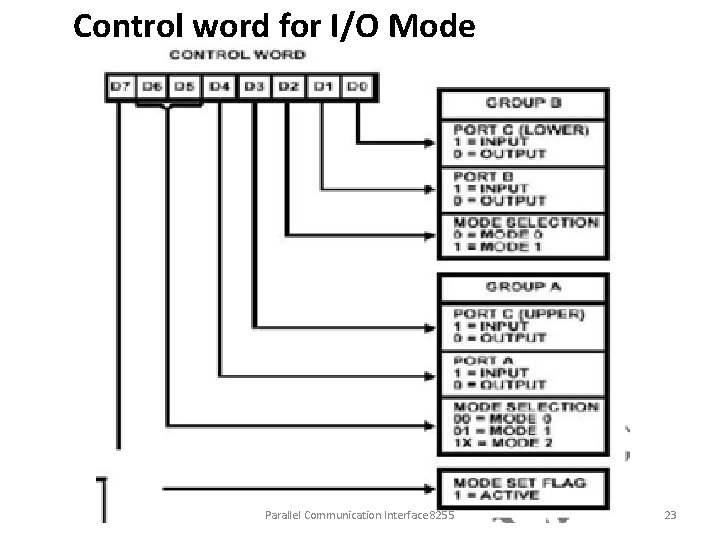

Control word for I/O Mode Parallel Communication Interface 8255 23

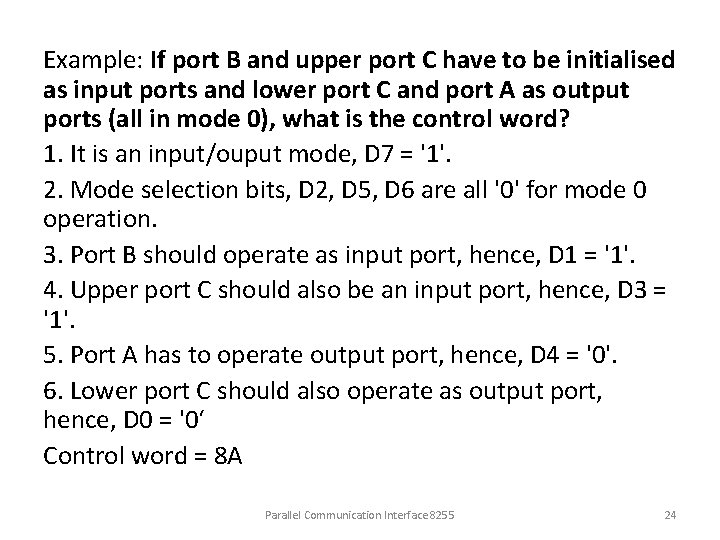

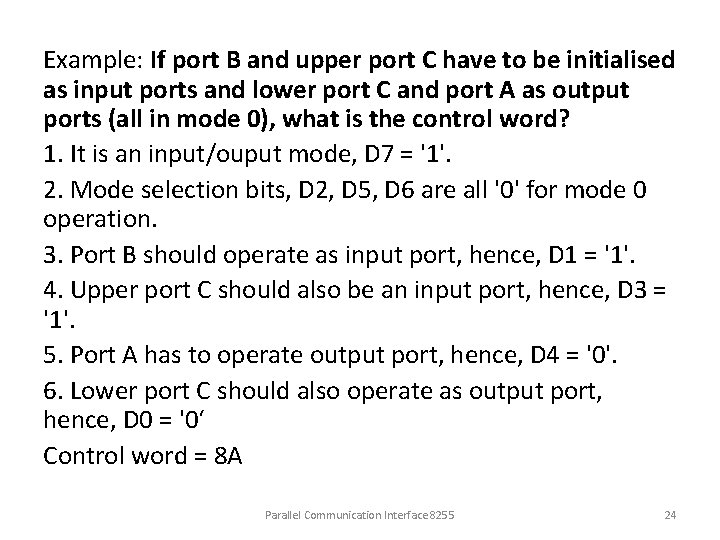

Example: If port B and upper port C have to be initialised as input ports and lower port C and port A as output ports (all in mode 0), what is the control word? 1. It is an input/ouput mode, D 7 = '1'. 2. Mode selection bits, D 2, D 5, D 6 are all '0' for mode 0 operation. 3. Port B should operate as input port, hence, D 1 = '1'. 4. Upper port C should also be an input port, hence, D 3 = '1'. 5. Port A has to operate output port, hence, D 4 = '0'. 6. Lower port C should also operate as output port, hence, D 0 = '0‘ Control word = 8 A Parallel Communication Interface 8255 24

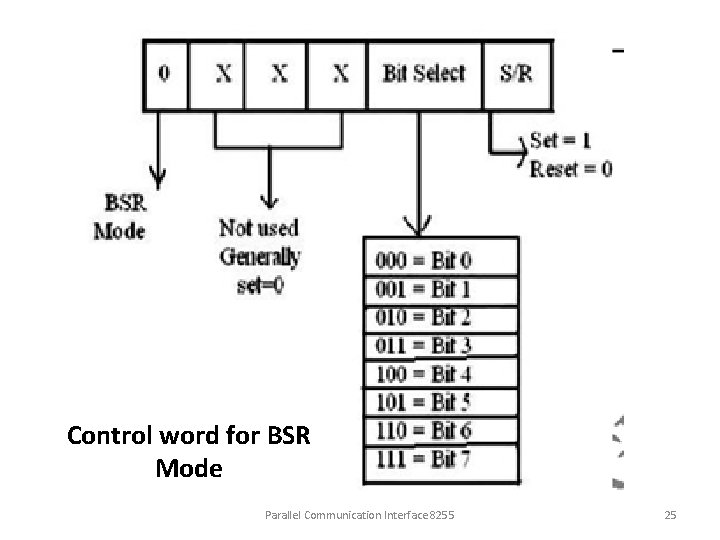

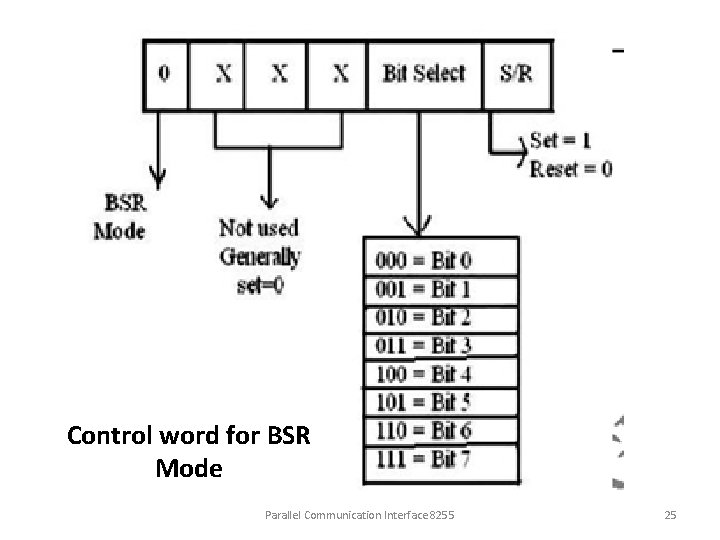

Control word for BSR Mode Parallel Communication Interface 8255 25

The eight possible combinations of the states of bits D 3 –D 1 (B 2 B 1 BO) in the bit set reset format determine particulars bit in PC 0 -PC 7 being set or reset as per the status of bit D 0. Parallel Communication Interface 8255 26

Example: If the 5 th bit (PC 5) of port C has to be "SET", then what is the control word? 1. Since it is BSR mode, D 7 = '0'. 2. Since D 4, D 5, D 6 are not used, assume them to be '0'. 3. PC 5 has to be selected, hence, D 3 = '1', D 2 = '0', D 1 = '1'. 4. PC 5 has to be set, hence, D 0 = '1'. Applying the above values to the format for BSR mode, we get the control word as "0 B (hex)". Parallel Communication Interface 8255 27

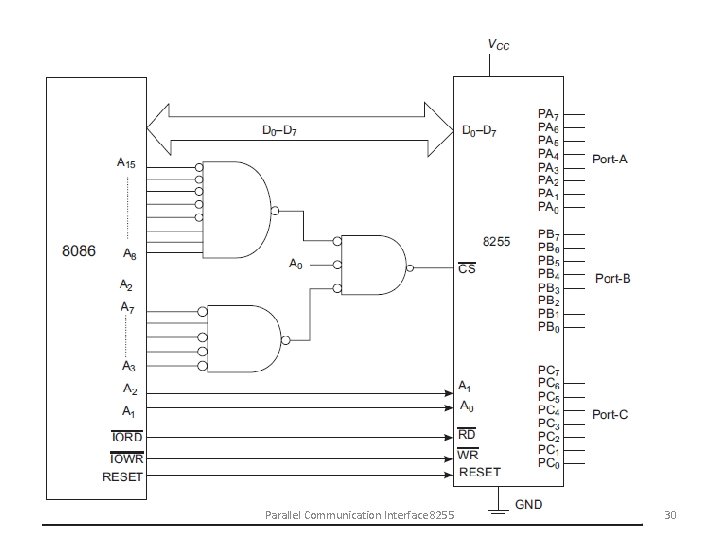

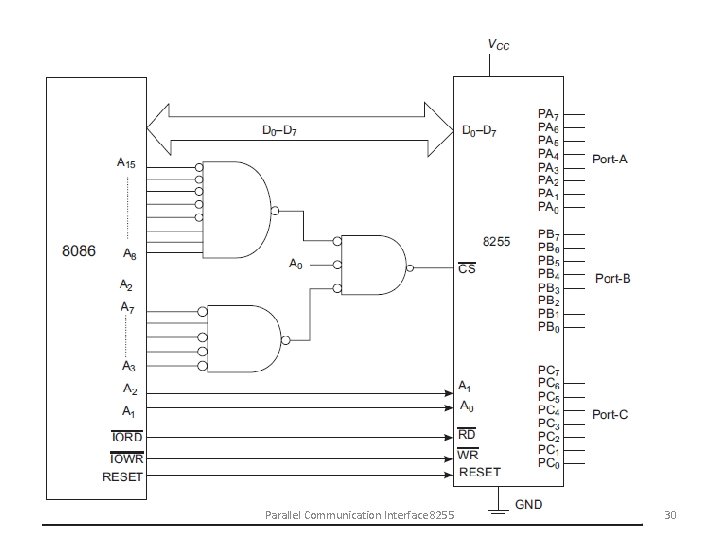

Interfacing 8255 WITH 8086 ( I/O Mapped I/O Mode) • The 8086 has four special instructions IN, INS, OUT and OUTS to transfer data through the input/output ports in I/O mapped I/O system. • M/IO signal is always low when is executing these instructions. • Figure shows the interfacing of 8255 with 8086 • In I/O mapped I/O, RD and WR signals are activated when M/IO signal is low Parallel Communication Interface 8255 28

• In Memory mapped I/O, RD and WR signals are activated when M/IO signal is low. • Depending upon the decoding technique ( Absoluter or Linear ) address lines are used to decode address of 8255. Parallel Communication Interface 8255 29

Parallel Communication Interface 8255 30

Parallel Communication Interface 8255 31