MixedSignal Challenges Solutions for advanced process nodes Cadence

- Slides: 22

Mixed-Signal Challenges & Solutions for advanced process nodes Cadence Design Systems Bruno Dutrey – September 22, 2009 *

Agenda • Introduction on advanced process nodes • Importance of design methodologies in deep submicron technologies • Mixed-Signal Challenges & Solutions • CERN – Cadence partnership highlights *

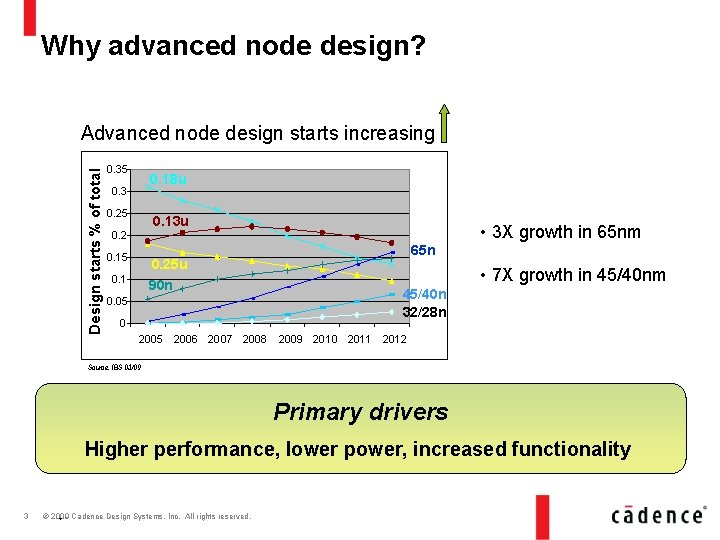

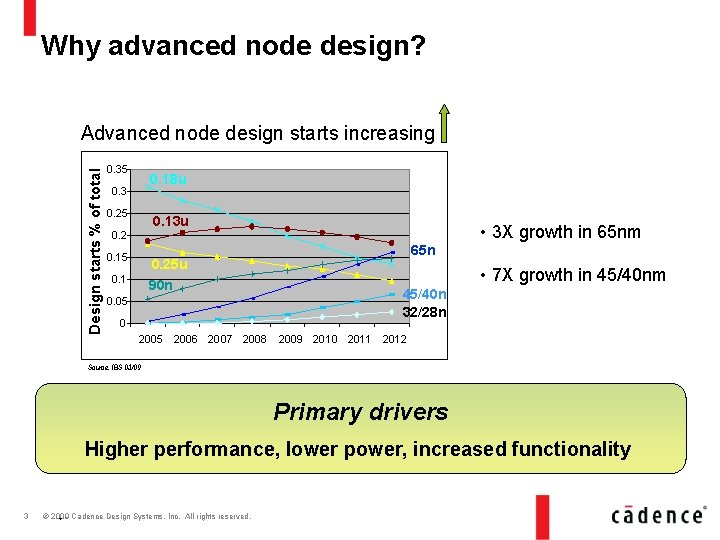

Why advanced node design? Design starts % of total Advanced node design starts increasing 0. 35 0. 18 u 0. 3 0. 25 0. 13 u 0. 2 0. 15 • 3 X growth in 65 nm 65 n 0. 25 u 0. 1 90 n 0. 05 0 2005 2006 2007 2008 • 7 X growth in 45/40 nm 45/40 n 32/28 n 2009 2010 2011 2012 Source: IBS 03/09 Primary drivers Higher performance, lower power, increased functionality 3 © 2009 Cadence Design Systems, Inc. All rights reserved. *

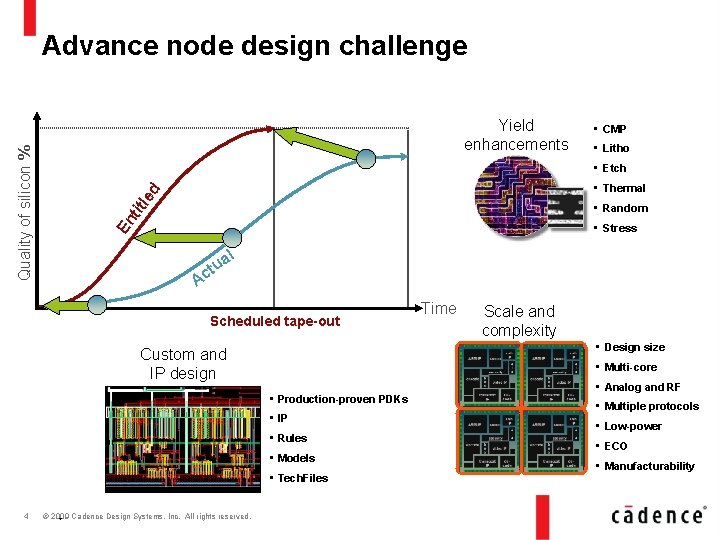

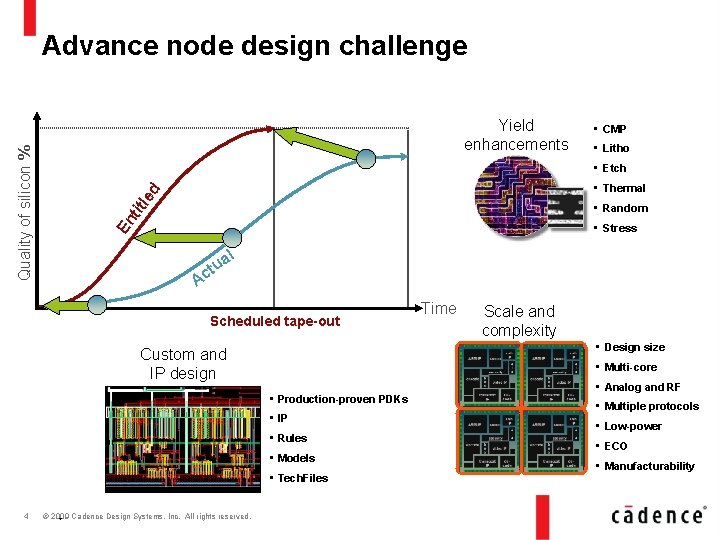

Advance node design challenge Quality of silicon % Yield enhancements • Litho • Etch ed • Thermal En t itl • Random • Stress al tu c A Scheduled tape-out • IP • Rules • Models • Tech. Files * Scale and complexity • Multi-core • Production-proven PDKs © 2009 Cadence Design Systems, Inc. All rights reserved. Time • Design size Custom and IP design 4 • CMP • Analog and RF • Multiple protocols • Low-power • ECO • Manufacturability

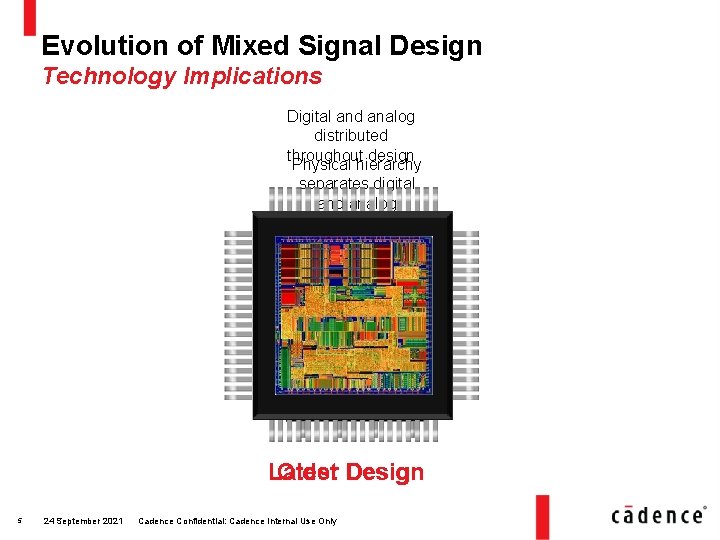

Evolution of Mixed Signal Design Technology Implications Digital and analog distributed throughout design Physical hierarchy separates digital and analog Latest Older Design 5 24 September * 2021 Cadence Confidential: Cadence Internal Use Only

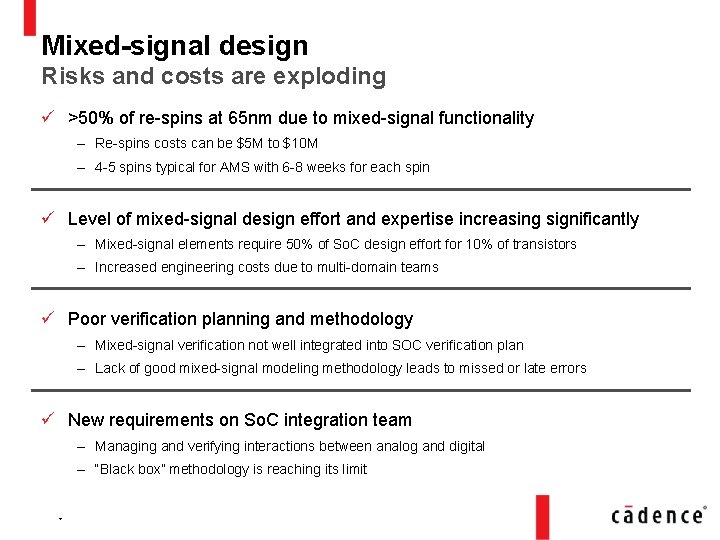

Mixed-signal design Risks and costs are exploding ü >50% of re-spins at 65 nm due to mixed-signal functionality – Re-spins costs can be $5 M to $10 M – 4 -5 spins typical for AMS with 6 -8 weeks for each spin ü Level of mixed-signal design effort and expertise increasing significantly – Mixed-signal elements require 50% of So. C design effort for 10% of transistors – Increased engineering costs due to multi-domain teams ü Poor verification planning and methodology – Mixed-signal verification not well integrated into SOC verification plan – Lack of good mixed-signal modeling methodology leads to missed or late errors ü New requirements on So. C integration team – Managing and verifying interactions between analog and digital – “Black box” methodology is reaching its limit *

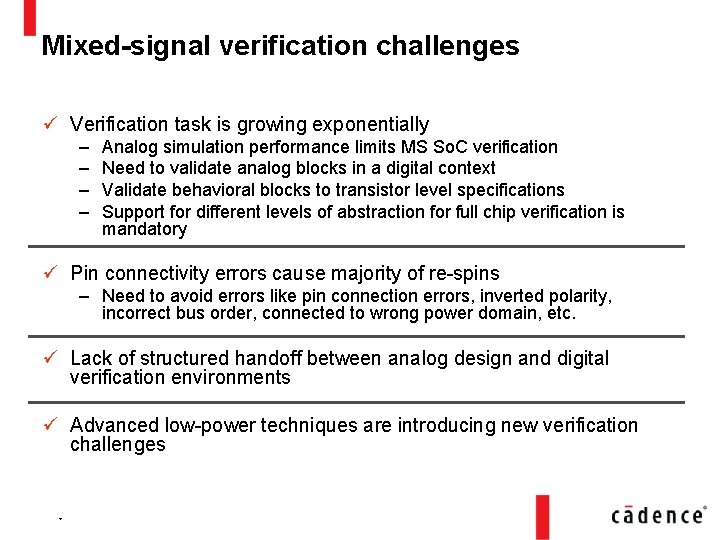

Mixed-signal verification challenges ü Verification task is growing exponentially – – Analog simulation performance limits MS So. C verification Need to validate analog blocks in a digital context Validate behavioral blocks to transistor level specifications Support for different levels of abstraction for full chip verification is mandatory ü Pin connectivity errors cause majority of re-spins – Need to avoid errors like pin connection errors, inverted polarity, incorrect bus order, connected to wrong power domain, etc. ü Lack of structured handoff between analog design and digital verification environments ü Advanced low-power techniques are introducing new verification challenges *

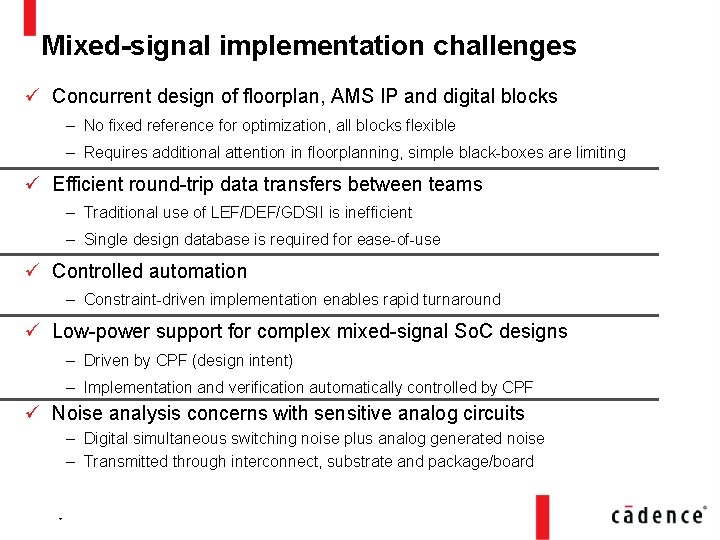

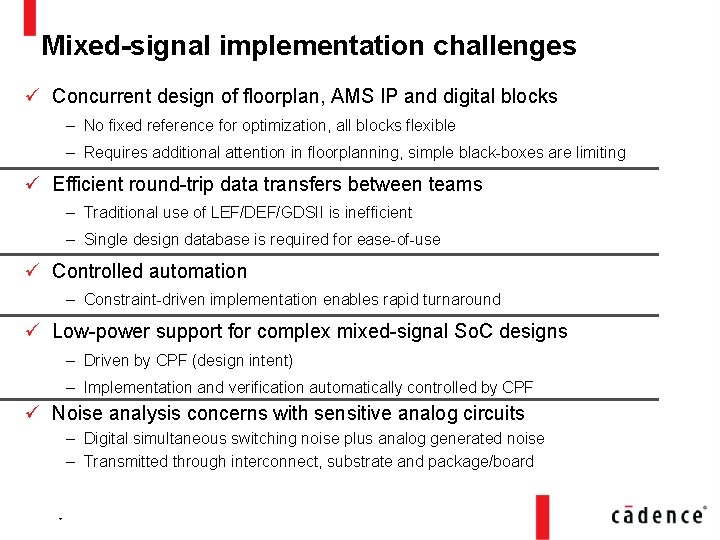

Mixed-signal implementation challenges ü Concurrent design of floorplan, AMS IP and digital blocks – No fixed reference for optimization, all blocks flexible – Requires additional attention in floorplanning, simple black-boxes are limiting ü Efficient round-trip data transfers between teams – Traditional use of LEF/DEF/GDSII is inefficient – Single design database is required for ease-of-use ü Controlled automation – Constraint-driven implementation enables rapid turnaround ü Low-power support for complex mixed-signal So. C designs – Driven by CPF (design intent) – Implementation and verification automatically controlled by CPF ü Noise analysis concerns with sensitive analog circuits – Digital simultaneous switching noise plus analog generated noise – Transmitted through interconnect, substrate and package/board *

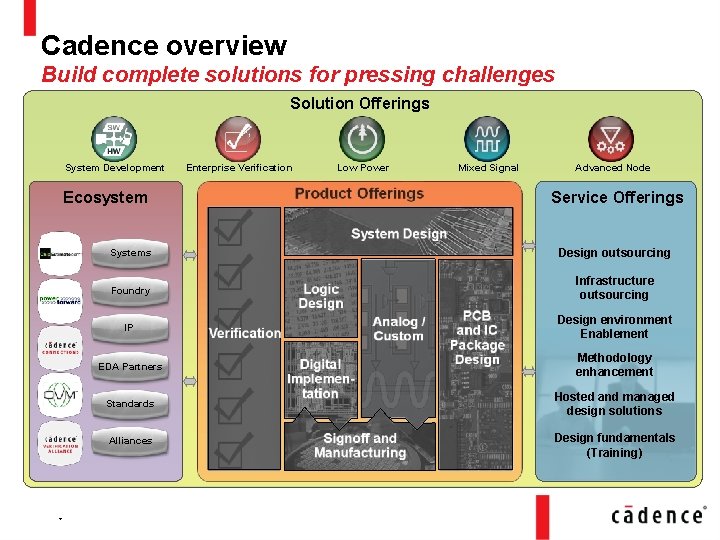

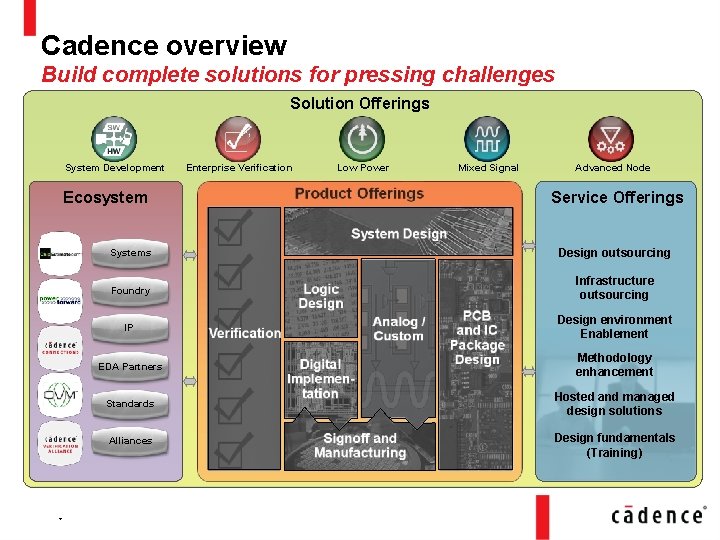

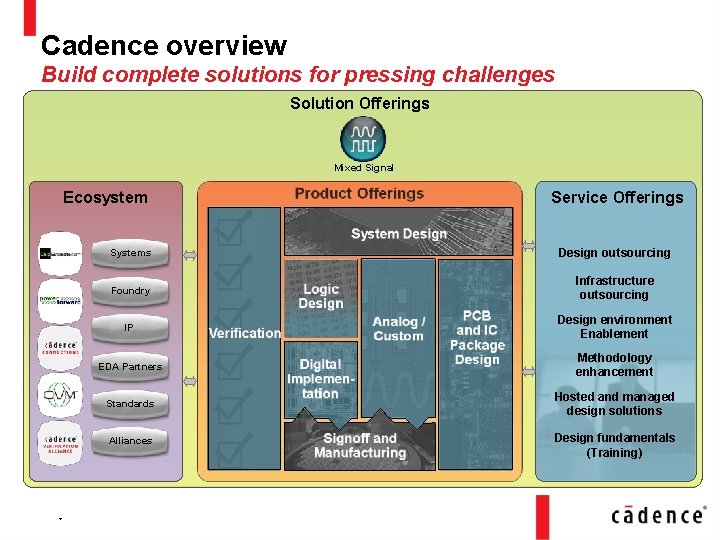

Cadence overview Build complete solutions for pressing challenges Solution Offerings System Development Ecosystem * Enterprise Verification Low Power Mixed Signal Advanced Node Service Offerings Systems Design outsourcing Foundry Infrastructure outsourcing IP Design environment Enablement EDA Partners Methodology enhancement Standards Hosted and managed design solutions Alliances Design fundamentals (Training)

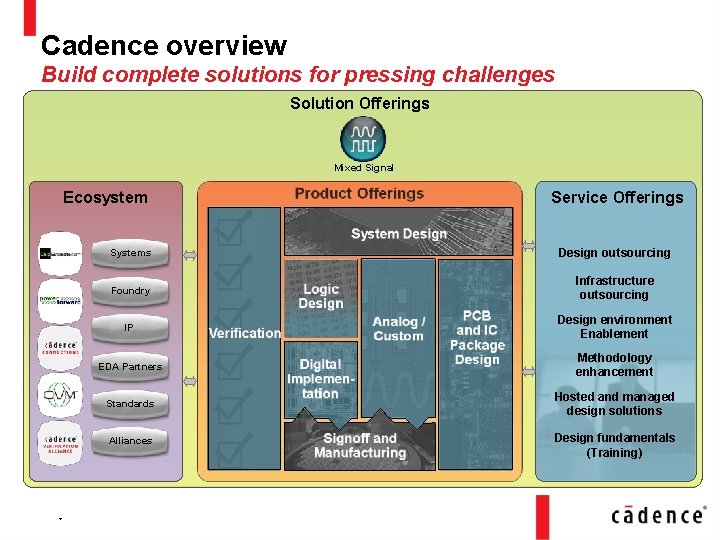

Cadence overview Build complete solutions for pressing challenges Solution Offerings Mixed Signal Ecosystem * Service Offerings Systems Design outsourcing Foundry Infrastructure outsourcing IP Design environment Enablement EDA Partners Methodology enhancement Standards Hosted and managed design solutions Alliances Design fundamentals (Training)

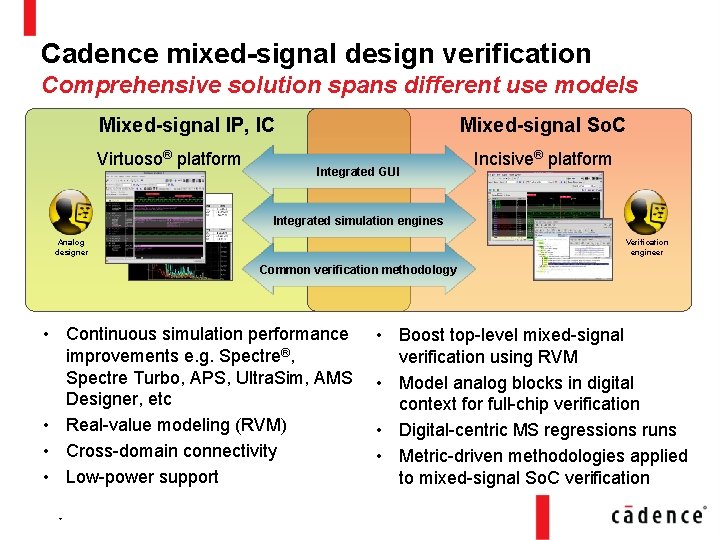

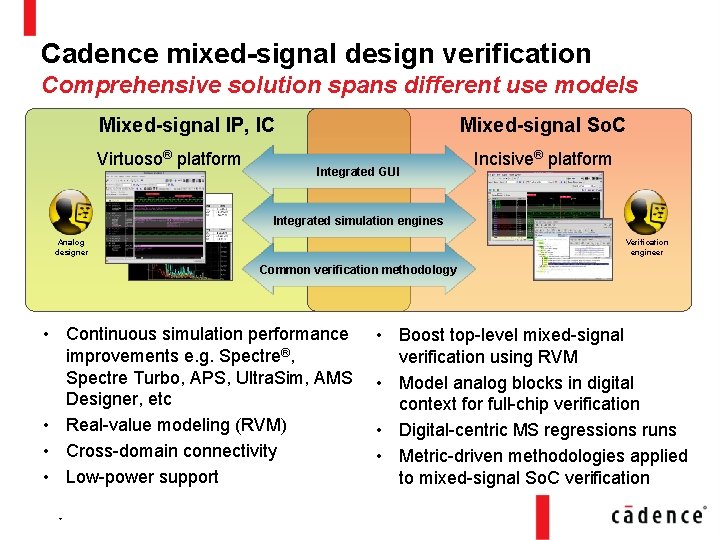

Cadence mixed-signal design verification Comprehensive solution spans different use models Mixed-signal So. C Mixed-signal IP, IC Virtuoso® platform Integrated GUI Incisive® platform Integrated simulation engines Verification engineer Analog designer Common verification methodology • Continuous simulation performance improvements e. g. Spectre®, Spectre Turbo, APS, Ultra. Sim, AMS Designer, etc • Real-value modeling (RVM) • Cross-domain connectivity • Low-power support * • Boost top-level mixed-signal verification using RVM • Model analog blocks in digital context for full-chip verification • Digital-centric MS regressions runs • Metric-driven methodologies applied to mixed-signal So. C verification

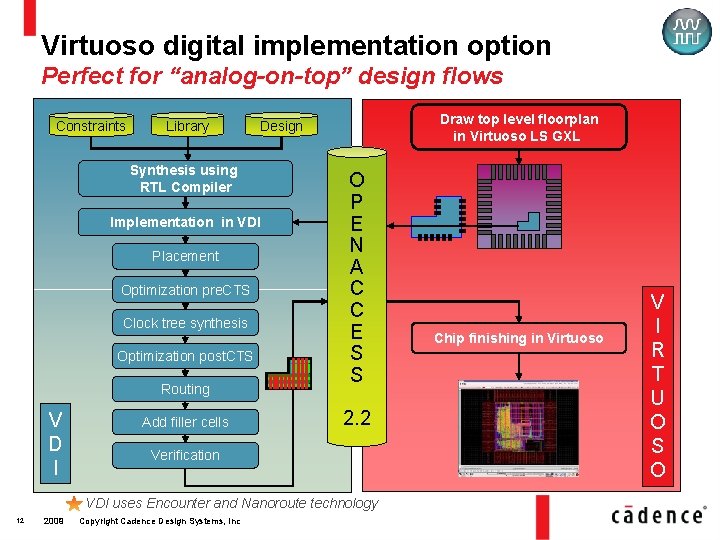

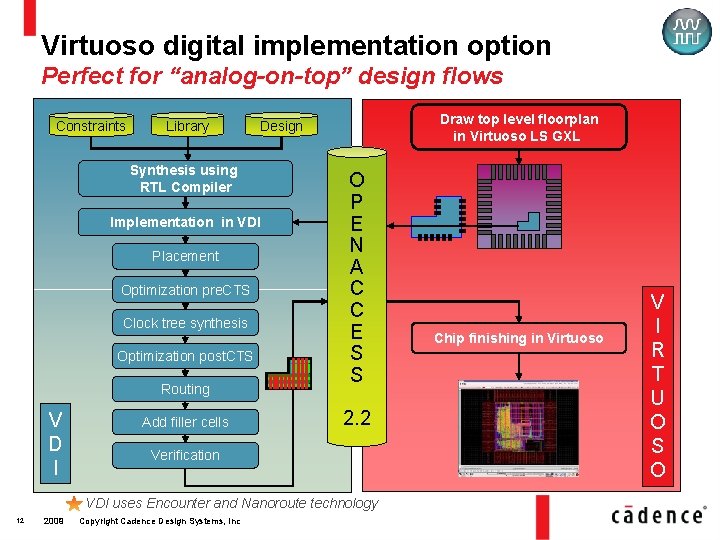

Virtuoso digital implementation option Perfect for “analog-on-top” design flows Constraints Library Synthesis using RTL Compiler Implementation in VDI Placement Optimization pre. CTS Clock tree synthesis Optimization post. CTS Routing V D I Add filler cells Draw top level floorplan in Virtuoso LS GXL Design O P E N A C C E S S 2. 2 Verification VDI uses Encounter and Nanoroute technology 12 2009 * Copyright Cadence Design Systems, Inc Chip finishing in Virtuoso V I R T U O S O

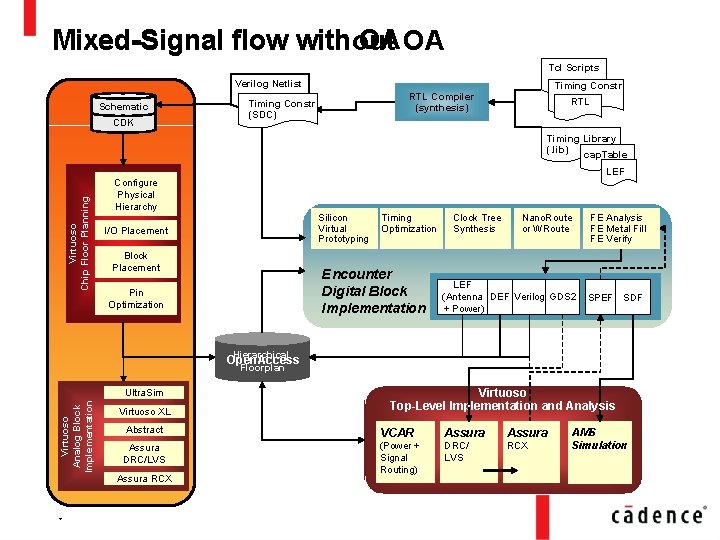

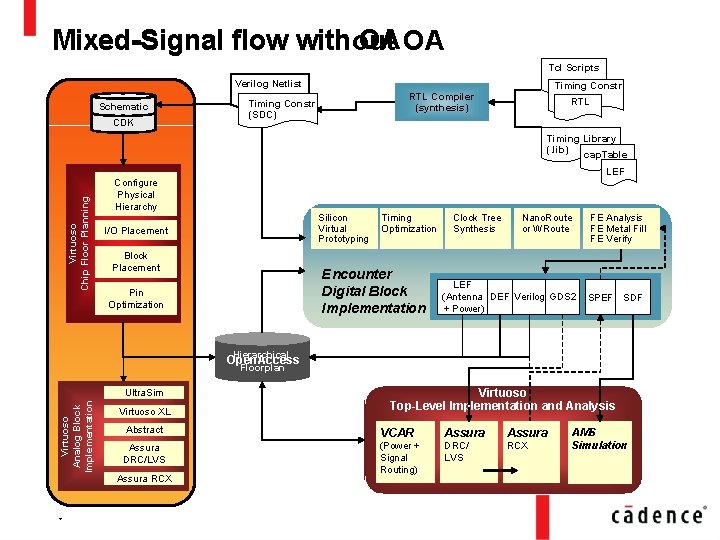

Mixed-Signal flow with OA OA without Tcl Scripts Verilog Netlist Schematic CDK Timing Constr RTL Compiler (synthesis) Timing Constr (SDC) RTL Virtuoso Chip Floor Planning Timing Library (. lib) cap. Table LEF Configure Physical Hierarchy Silicon Virtual Prototyping I/O Placement Block Placement Timing Optimization Encounter Digital Block Implementation Pin Optimization Clock Tree Synthesis Nano. Route or WRoute LEF (Antenna DEF Verilog GDS 2 + Power) FE Analysis FE Metal Fill FE Verify SPEF SDF Hierarchical Floorplan Open. Access Virtuoso Analog Block Implementation Ultra. Sim * Virtuoso XL Abstract Assura DRC/LVS Assura RCX Virtuoso Top-Level Implementation and Analysis VCAR Assura (Power + Signal Routing) DRC/ LVS RCX AMS Simulation

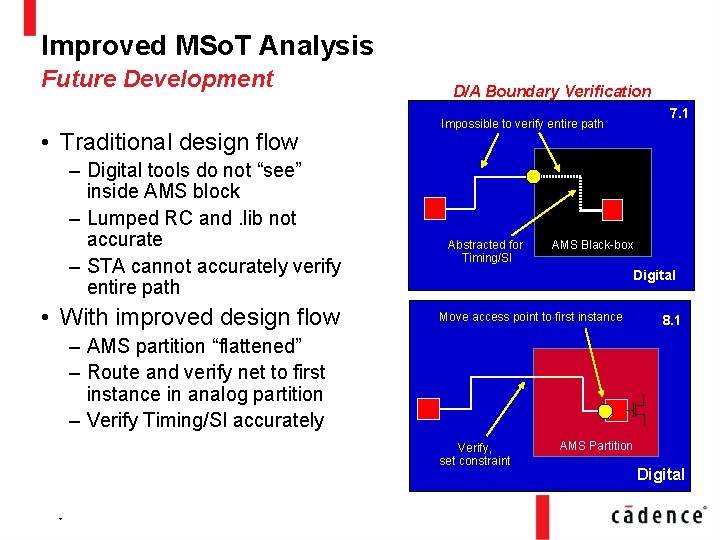

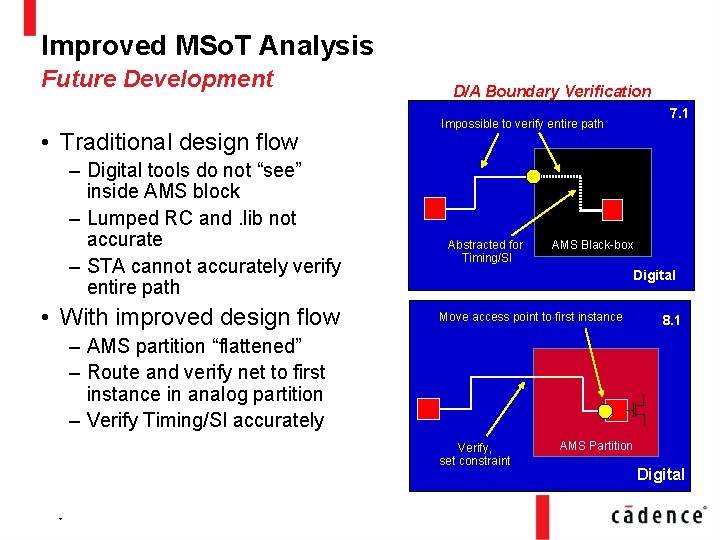

Improved MSo. T Analysis Future Development • Traditional design flow – Digital tools do not “see” inside AMS block – Lumped RC and. lib not accurate – STA cannot accurately verify entire path • With improved design flow D/A Boundary Verification 7. 1 Impossible to verify entire path Abstracted for Timing/SI AMS Black-box Digital Move access point to first instance 8. 1 – AMS partition “flattened” – Route and verify net to first instance in analog partition – Verify Timing/SI accurately Verify, set constraint * AMS Partition Digital

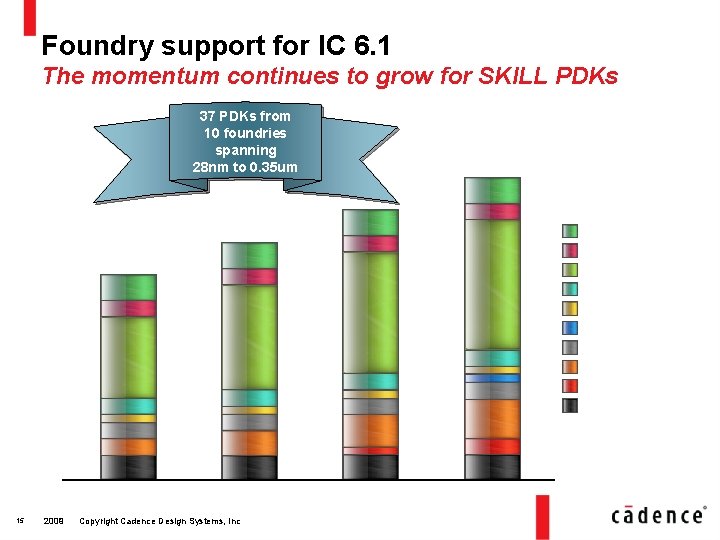

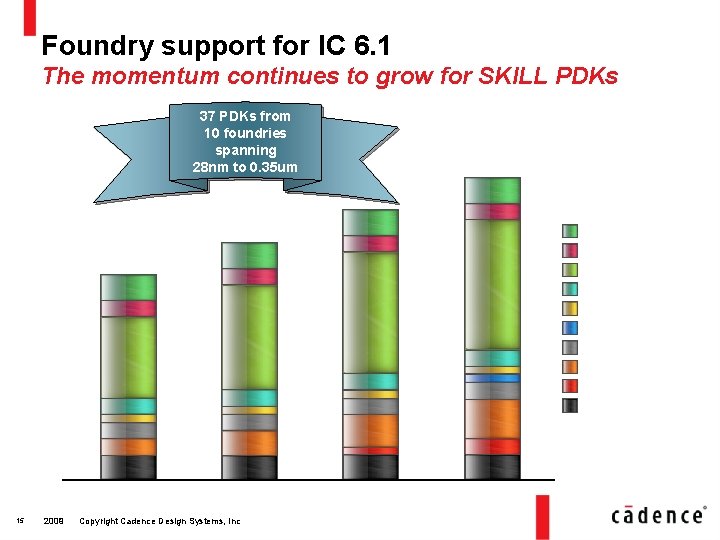

Foundry support for IC 6. 1 The momentum continues to grow for SKILL PDKs 37 PDKs from 10 foundries spanning 28 nm to 0. 35 um 15 2009 * Copyright Cadence Design Systems, Inc

PDK migration – CDBA to Open Access The Five Biggest Challenges • • • Technology File Vias SKILL Pcells Tool Interoperability *

CERN – Cadence partnership Needs and challenges • Formalize & Automate Cern Mixed-Signal design flow based on IBM open access PDK – Build Open Access PDK supporting advanced features – Productivity enhancement • Focused on Client’s Design Team Productivity through VCAD IPs – IP packaging – Design environment • Interoperability based on IBM pdk – Currently implementing a CERN design on the developed • Training Services *

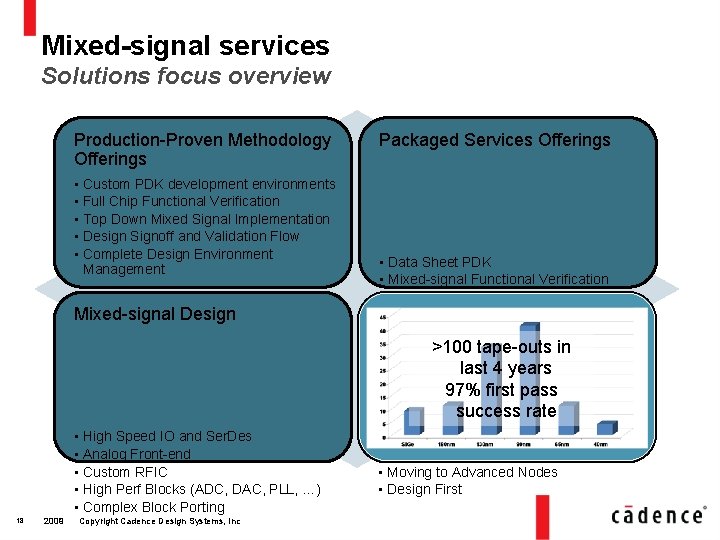

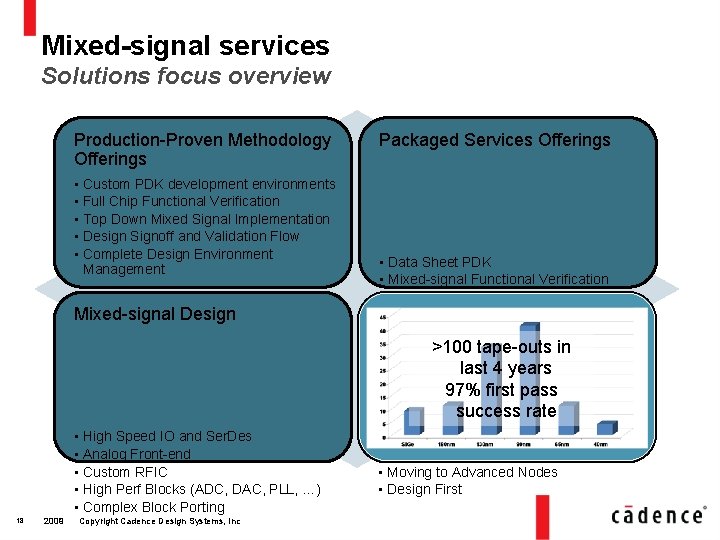

Mixed-signal services Solutions focus overview Production-Proven Methodology Offerings • Custom PDK development environments • Full Chip Functional Verification • Top Down Mixed Signal Implementation • Design Signoff and Validation Flow • Complete Design Environment Management Mixed-signal Design Packaged Services Offerings • Data Sheet PDK • Mixed-signal Functional Verification • Custom Library Characterization • Design IP Technology Transition Offerings >100 tape-outs in last 4 years 97% first pass success rate • High Speed IO and Ser. Des • Analog Front-end • Custom RFIC • High Perf Blocks (ADC, DAC, PLL, …) • Complex Block Porting 18 2009 * Copyright Cadence Design Systems, Inc • Competitive replacement • 6. 1 feature adoption • Moving to Advanced Nodes • Design First

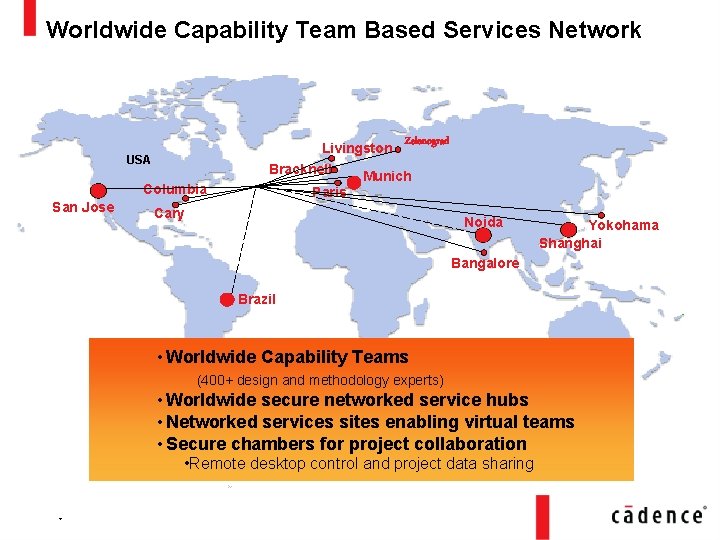

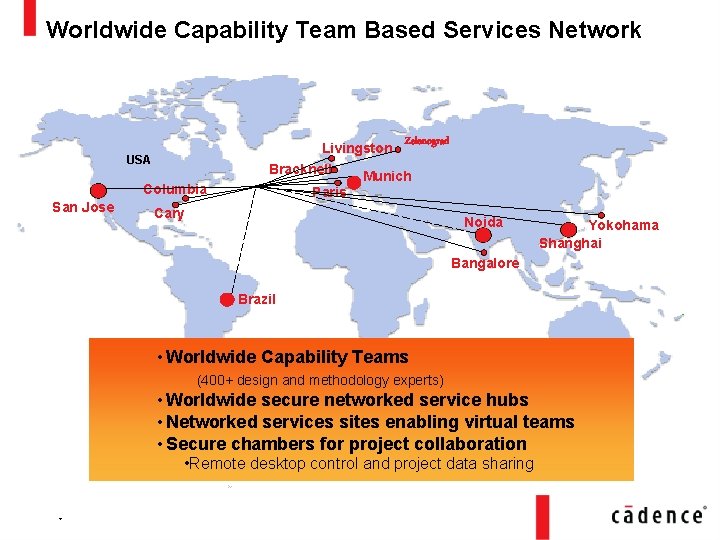

Worldwide Capability Team Based Services Network Livingston USA Bracknell Columbia San Jose Zelenograd Munich Paris Cary Noida Yokohama Shanghai Bangalore Brazil • Worldwide Capability Teams Collaboration Hub Hosting Hub (400+ design and methodology experts) • Worldwide secure networked service hubs • Networked services sites enabling virtual teams • Secure chambers for project collaboration • Remote desktop control and project data sharing *

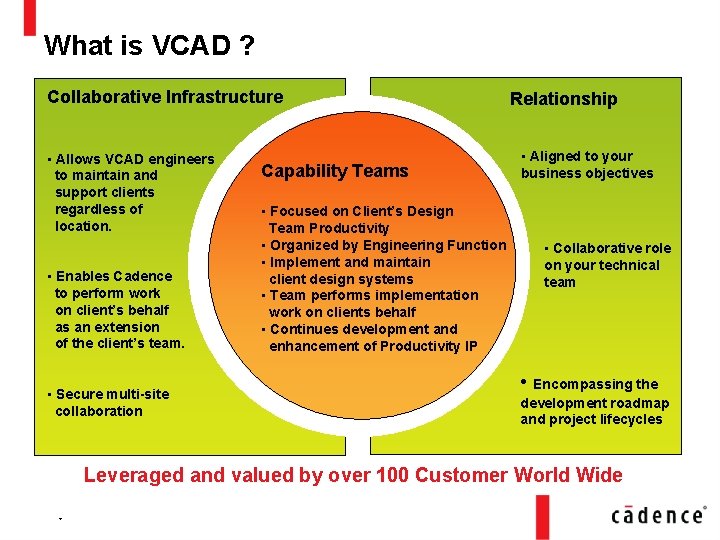

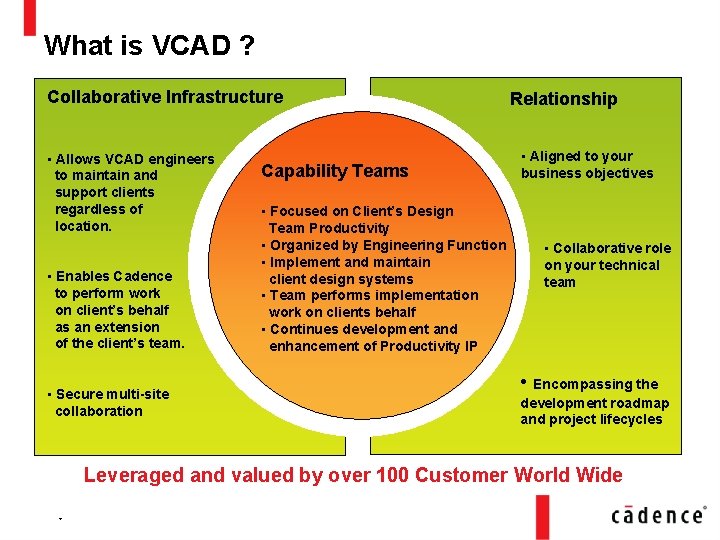

What is VCAD ? Collaborative Infrastructure At its core are the Relationship Global: • Allows VCAD engineers to maintain and support clients regardless of location. • Enables Cadence to perform work on client’s behalf as an extension of the client’s team. • Secure multi-site collaboration Capability Teams • Focused on Client’s Design Team Productivity • Organized by Engineering Function • Implement and maintain client design systems • Team performs implementation work on clients behalf • Continues development and enhancement of Productivity IP • Aligned to your business objectives • Collaborative role on your technical team • Encompassing the development roadmap and project lifecycles Leveraged and valued by over 100 Customer World Wide *

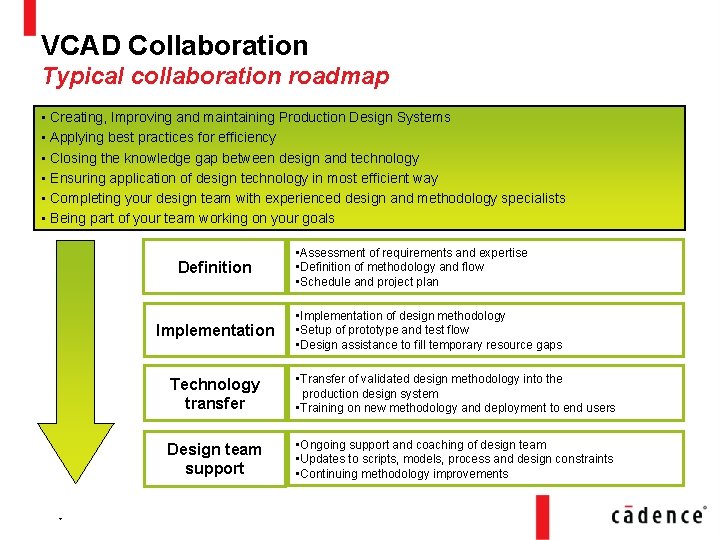

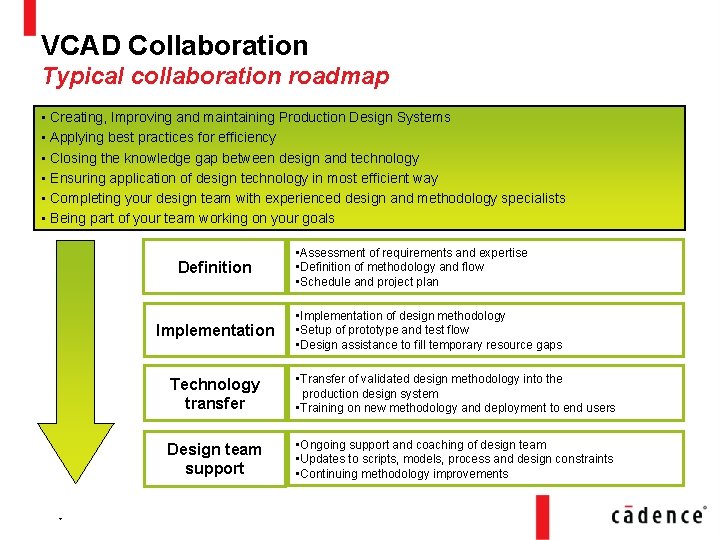

VCAD Collaboration Typical collaboration roadmap • Creating, Improving and maintaining Production Design Systems • Applying best practices for efficiency • Closing the knowledge gap between design and technology • Ensuring application of design technology in most efficient way • Completing your design team with experienced design and methodology specialists • Being part of your team working on your goals Definition Implementation * • Assessment of requirements and expertise • Definition of methodology and flow • Schedule and project plan • Implementation of design methodology • Setup of prototype and test flow • Design assistance to fill temporary resource gaps Technology transfer • Transfer of validated design methodology into the production design system • Training on new methodology and deployment to end users Design team support • Ongoing support and coaching of design team • Updates to scripts, models, process and design constraints • Continuing methodology improvements