Chapter 3 Cadence layout editor IC CAD Analog

![Cadence layout editor Example> NMOS의 layout [ICCAD@train##]/user 1/train##/ > mkdir cadence [ICCAD@train##]/user 1/train##/ > Cadence layout editor Example> NMOS의 layout [ICCAD@train##]/user 1/train##/ > mkdir cadence [ICCAD@train##]/user 1/train##/ >](https://slidetodoc.com/presentation_image_h2/fef709212a33ae96af829d6f16341469/image-3.jpg)

- Slides: 29

Chapter 3. Cadence layout editor IC CAD 실험 Analog part

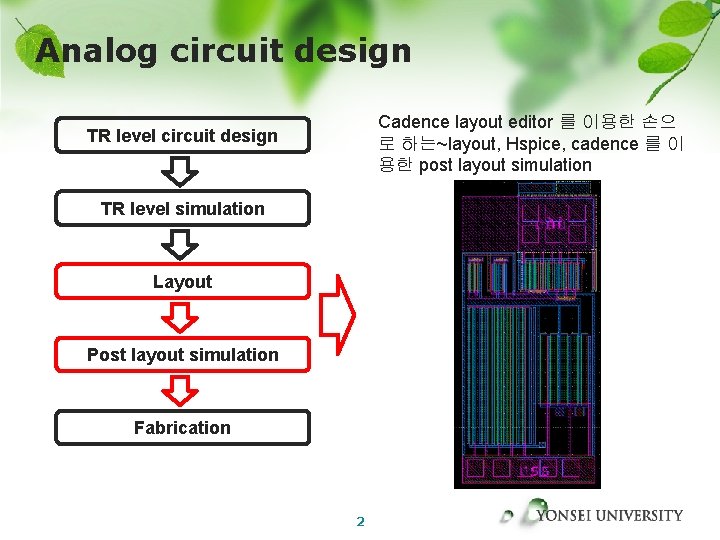

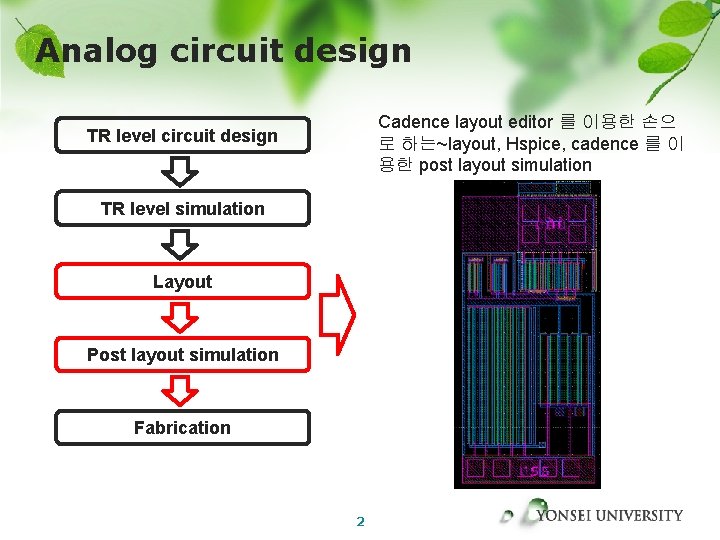

Analog circuit design Cadence layout editor 를 이용한 손으 로 하는~layout, Hspice, cadence 를 이 용한 post layout simulation TR level circuit design TR level simulation Layout Post layout simulation Fabrication 2

![Cadence layout editor Example NMOS의 layout ICCADtrainuser 1train mkdir cadence ICCADtrainuser 1train Cadence layout editor Example> NMOS의 layout [ICCAD@train##]/user 1/train##/ > mkdir cadence [ICCAD@train##]/user 1/train##/ >](https://slidetodoc.com/presentation_image_h2/fef709212a33ae96af829d6f16341469/image-3.jpg)

Cadence layout editor Example> NMOS의 layout [ICCAD@train##]/user 1/train##/ > mkdir cadence [ICCAD@train##]/user 1/train##/ > cd cadence [ICCAD@train##]/user 1/train##/ cadence> sourceic [ICCAD@train##]/user 1/train##/ hspice> icfb & 3

Cadence layout editor Example> NMOS의 layout Tools Library manager 4

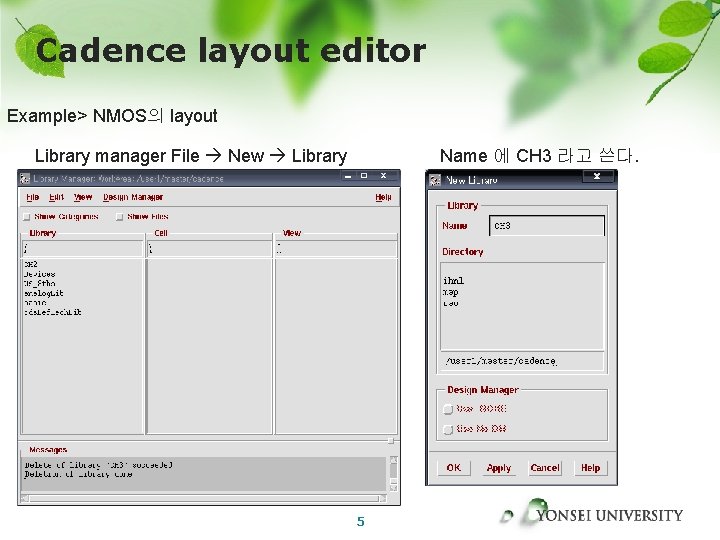

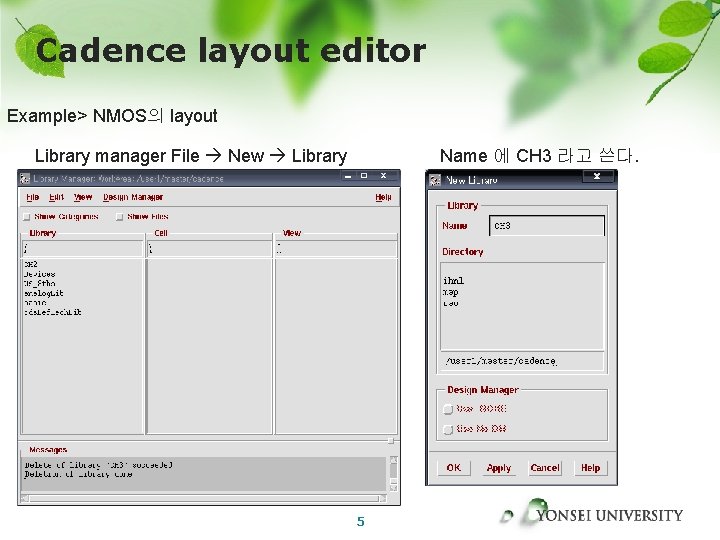

Cadence layout editor Example> NMOS의 layout Library manager File New Library Name 에 CH 3 라고 쓴다. 5

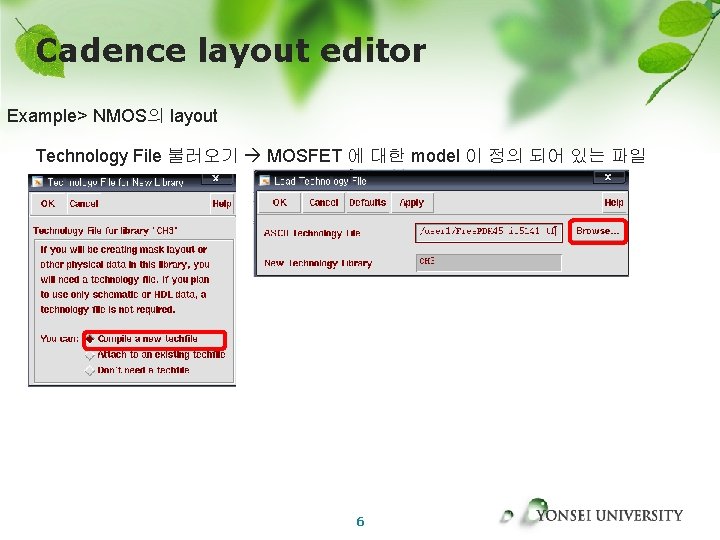

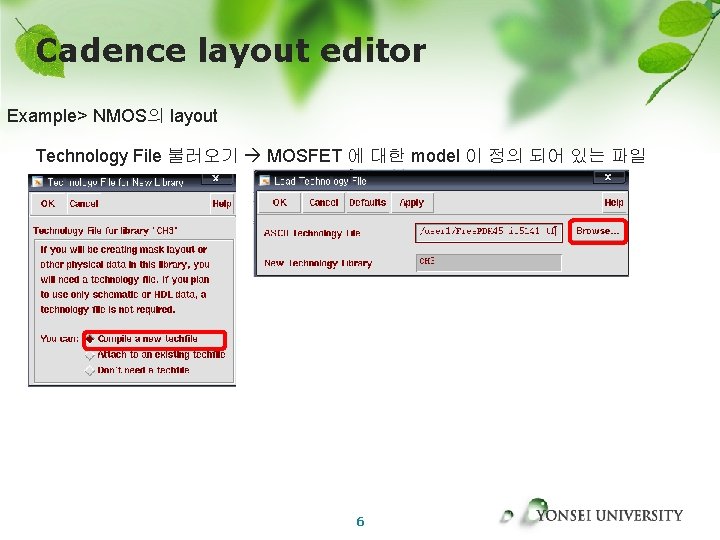

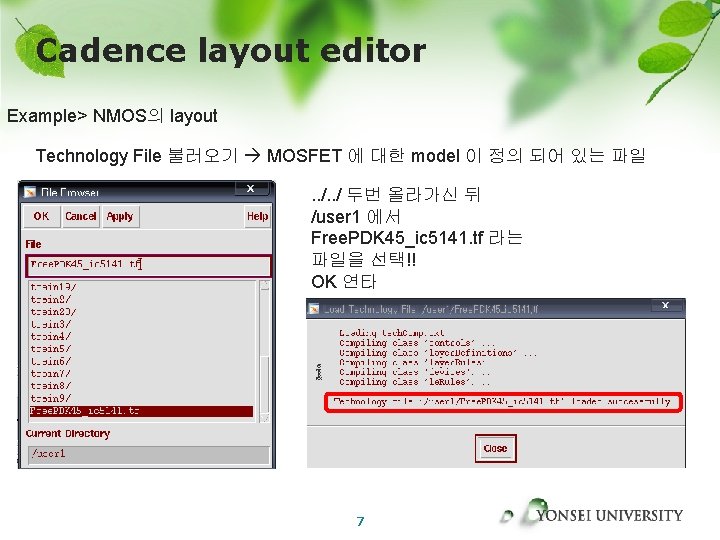

Cadence layout editor Example> NMOS의 layout Technology File 불러오기 MOSFET 에 대한 model 이 정의 되어 있는 파일 6

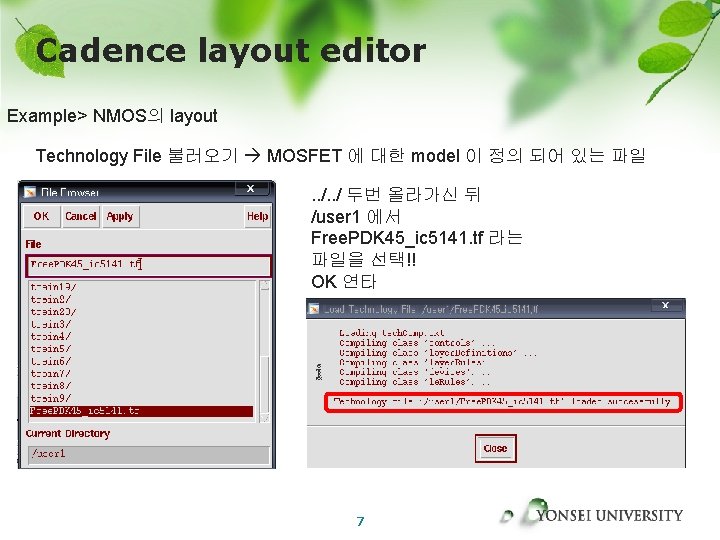

Cadence layout editor Example> NMOS의 layout Technology File 불러오기 MOSFET 에 대한 model 이 정의 되어 있는 파일. . / 두번 올라가신 뒤 /user 1 에서 Free. PDK 45_ic 5141. tf 라는 파일을 선택!! OK 연타 7

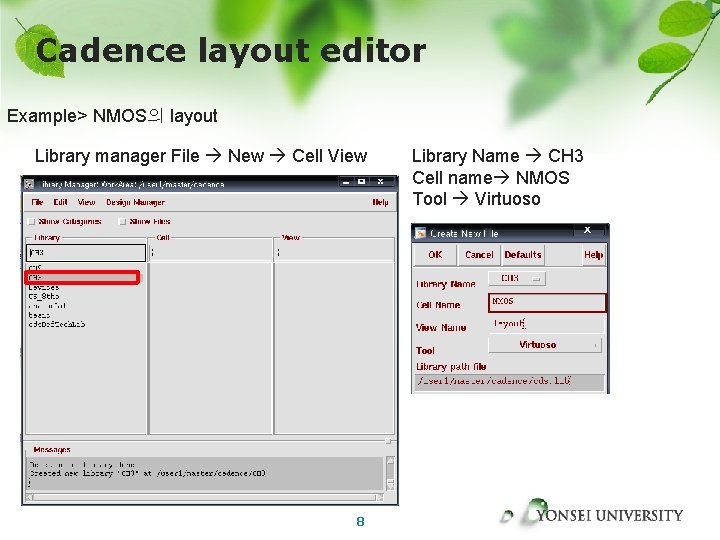

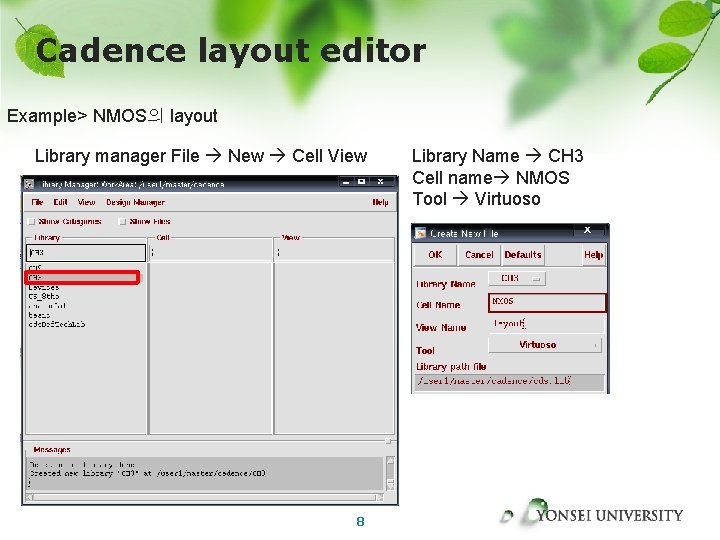

Cadence layout editor Example> NMOS의 layout Library manager File New Cell View 8 Library Name CH 3 Cell name NMOS Tool Virtuoso

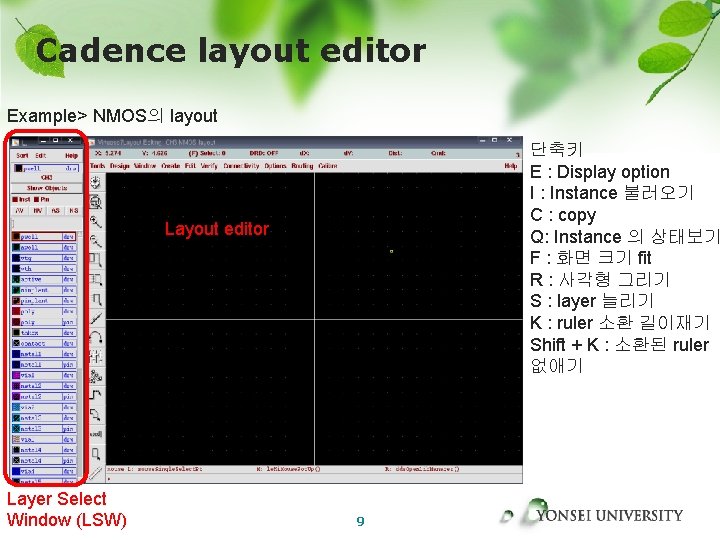

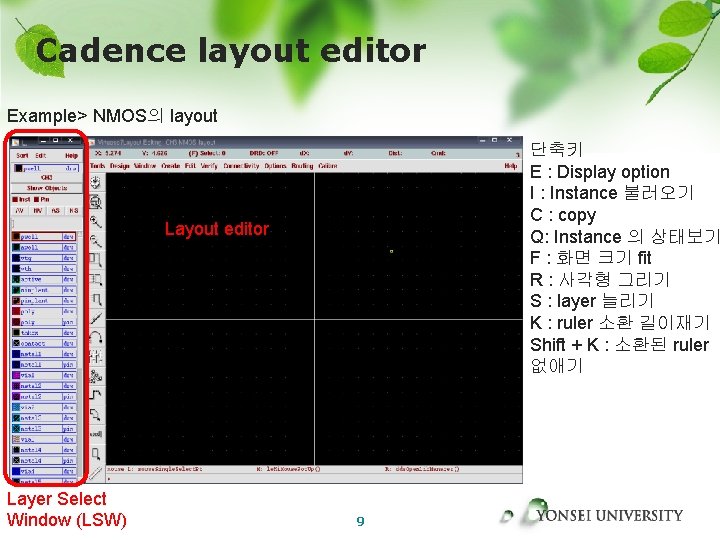

Cadence layout editor Example> NMOS의 layout 단축키 E : Display option I : Instance 불러오기 C : copy Q: Instance 의 상태보기 F : 화면 크기 fit R : 사각형 그리기 S : layer 늘리기 K : ruler 소환 길이재기 Shift + K : 소환된 ruler 없애기 Layout editor Layer Select Window (LSW) 9

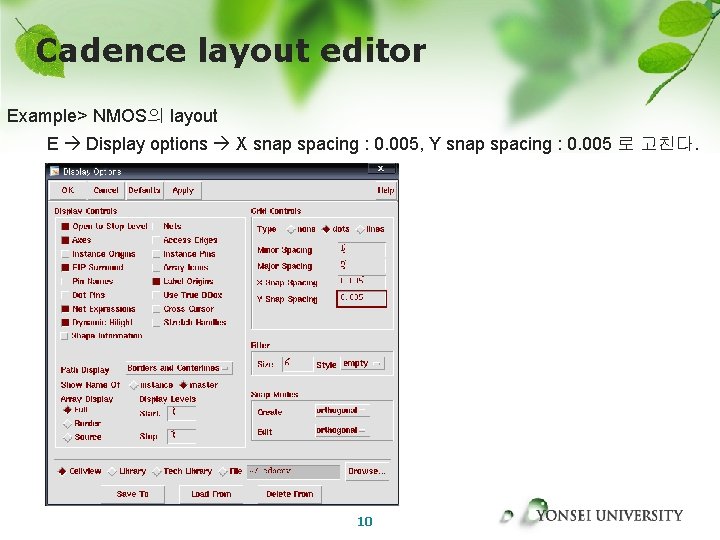

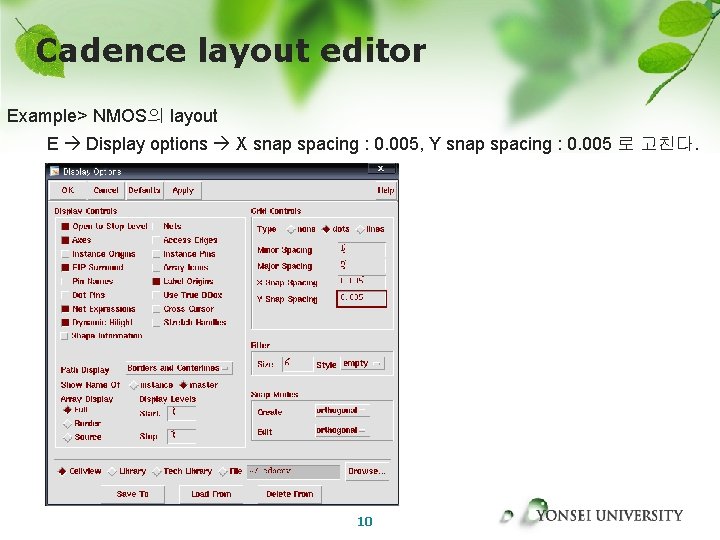

Cadence layout editor Example> NMOS의 layout E Display options X snap spacing : 0. 005, Y snap spacing : 0. 005 로 고친다. 10

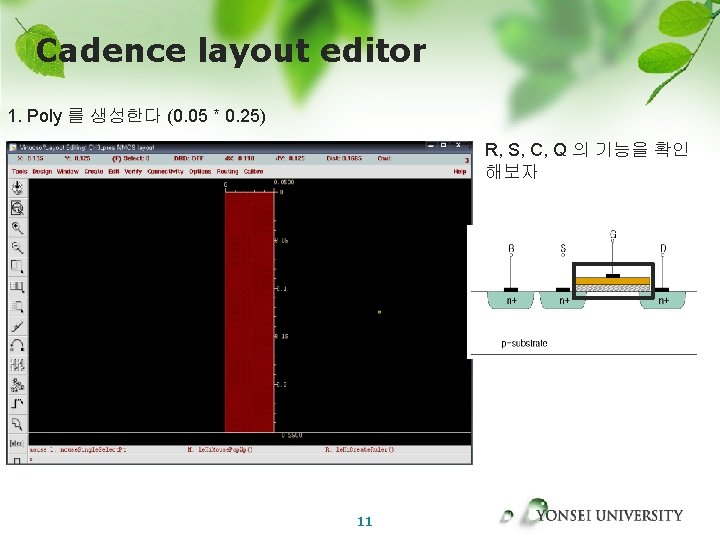

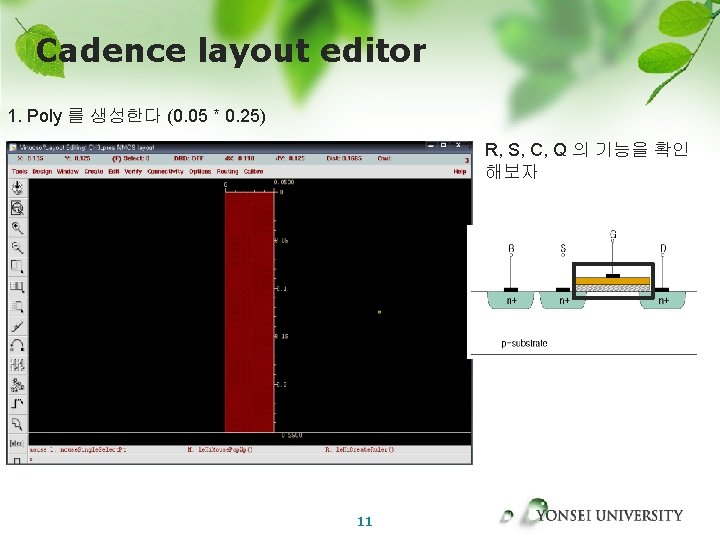

Cadence layout editor 1. Poly 를 생성한다 (0. 05 * 0. 25) R, S, C, Q 의 기능을 확인 해보자 11

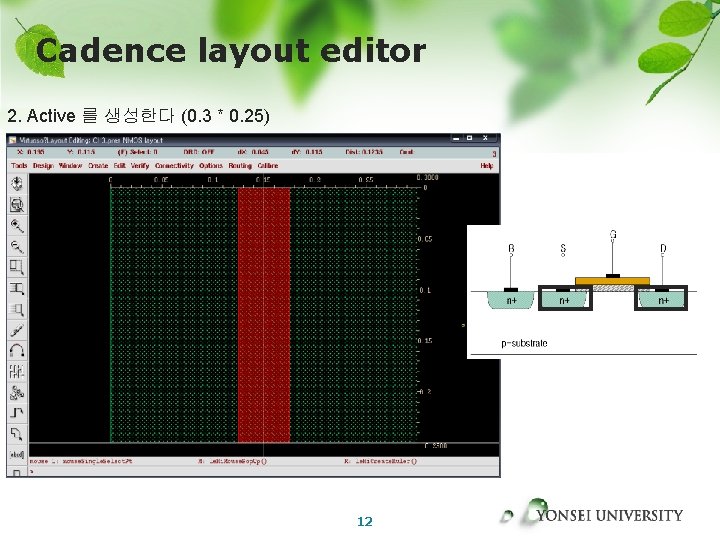

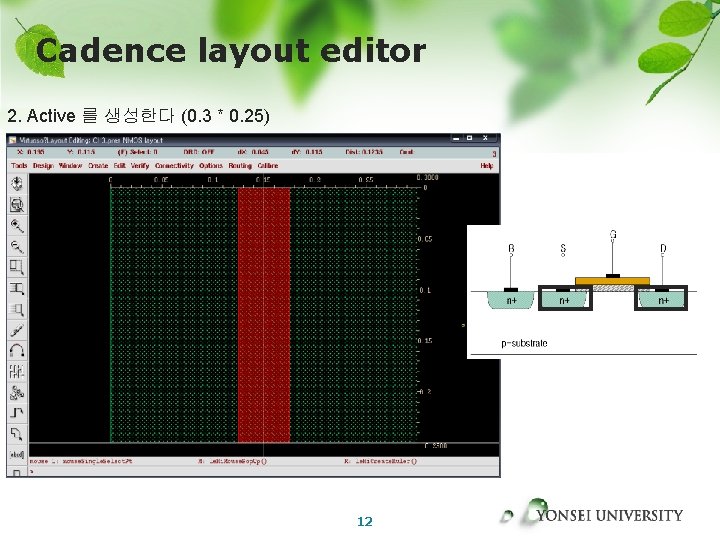

Cadence layout editor 2. Active 를 생성한다 (0. 3 * 0. 25) 12

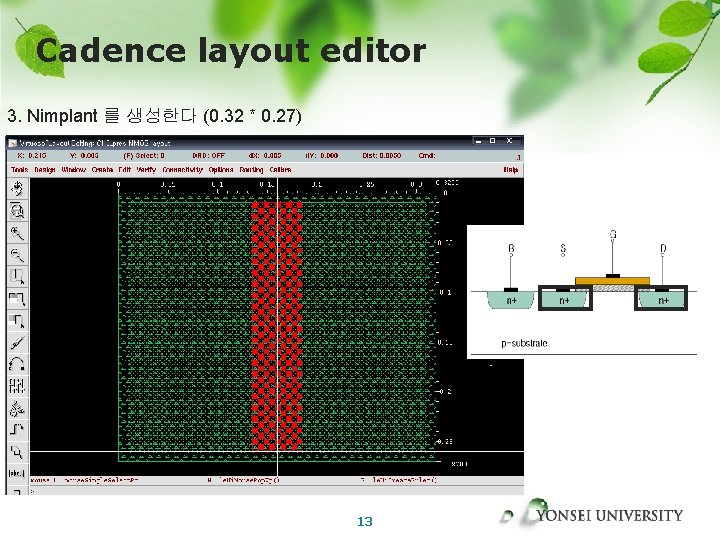

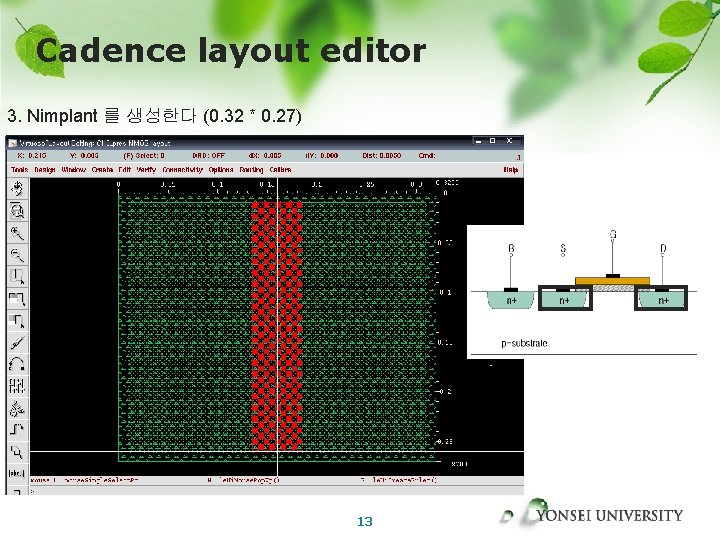

Cadence layout editor 3. Nimplant 를 생성한다 (0. 32 * 0. 27) 13

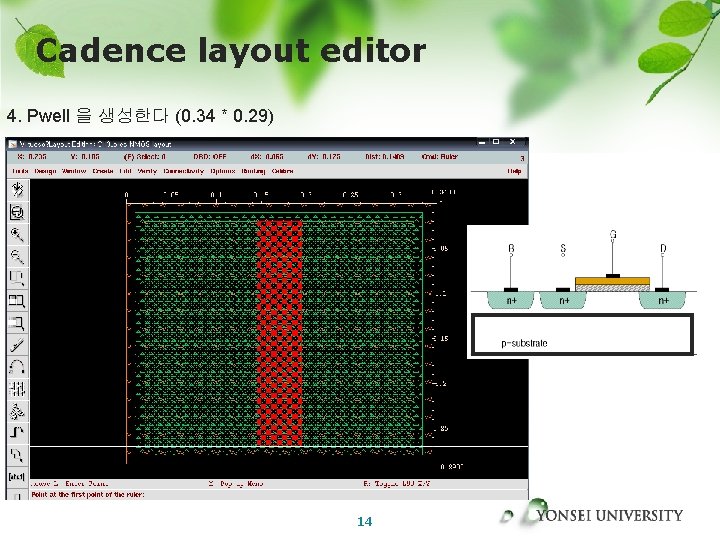

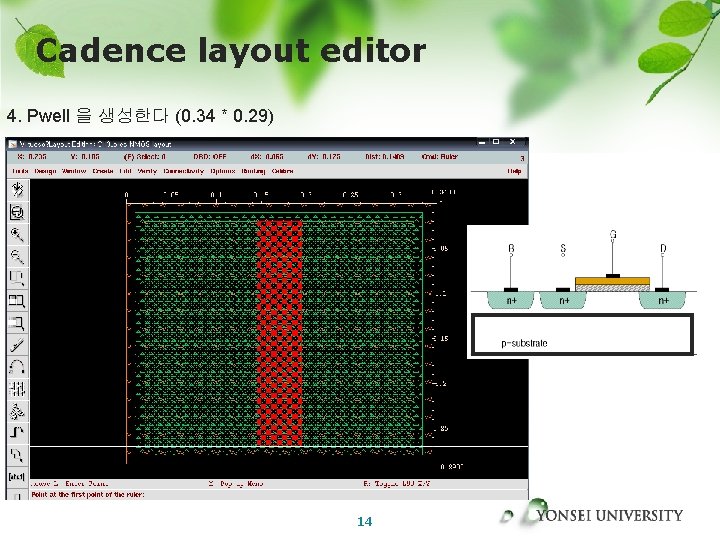

Cadence layout editor 4. Pwell 을 생성한다 (0. 34 * 0. 29) 14

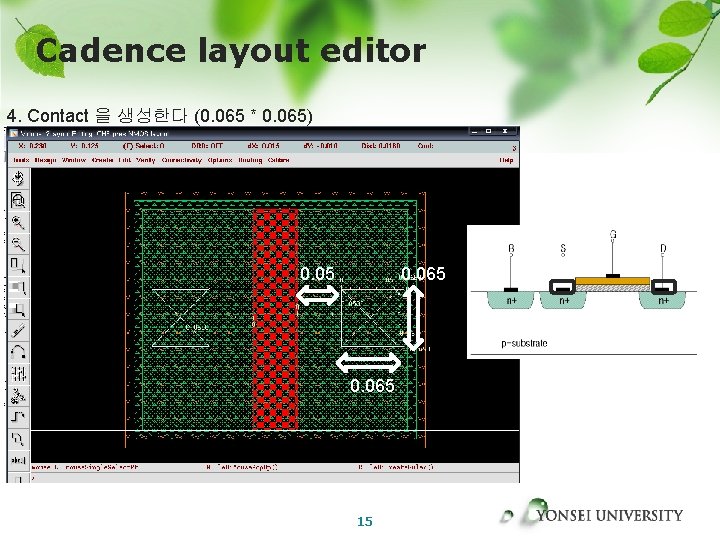

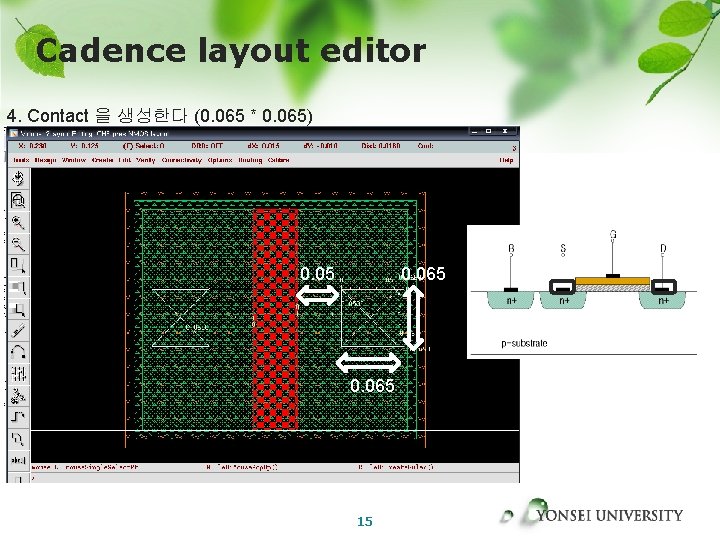

Cadence layout editor 4. Contact 을 생성한다 (0. 065 * 0. 065) 0. 05 0. 065 15

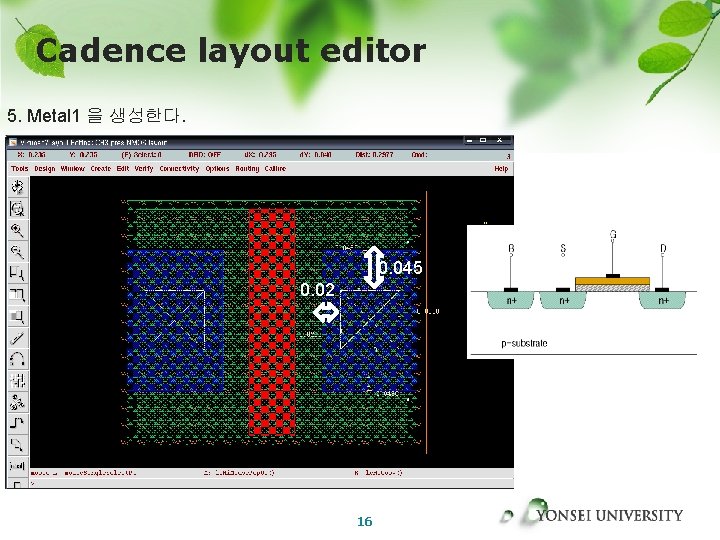

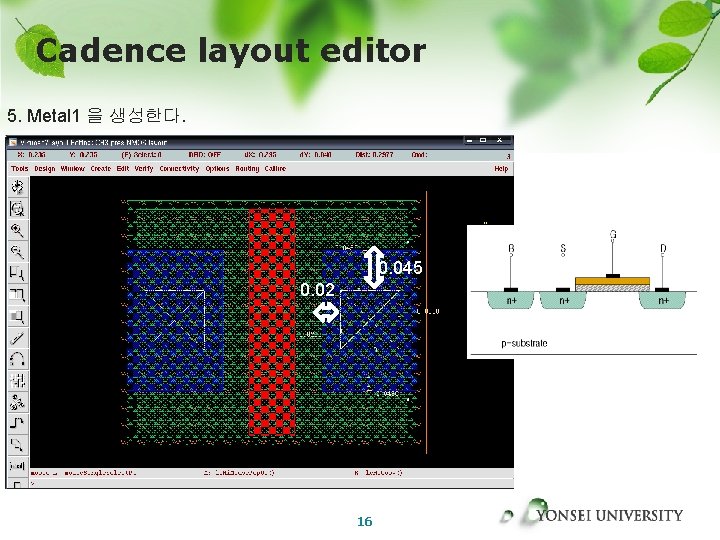

Cadence layout editor 5. Metal 1 을 생성한다. 0. 045 0. 02 16

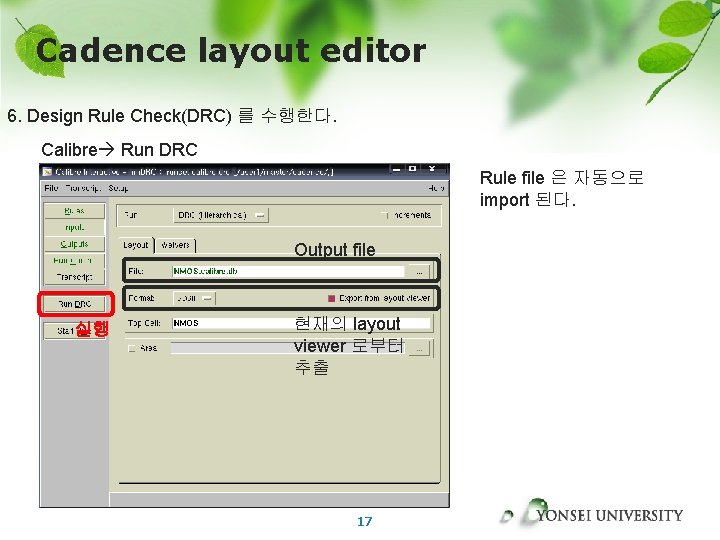

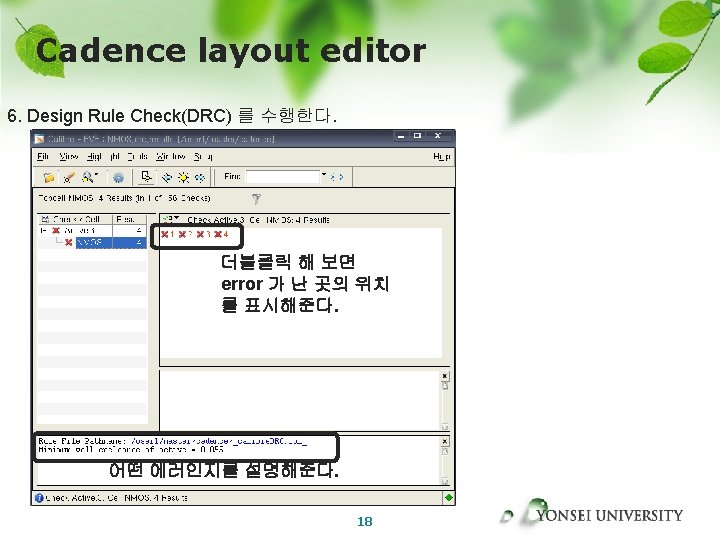

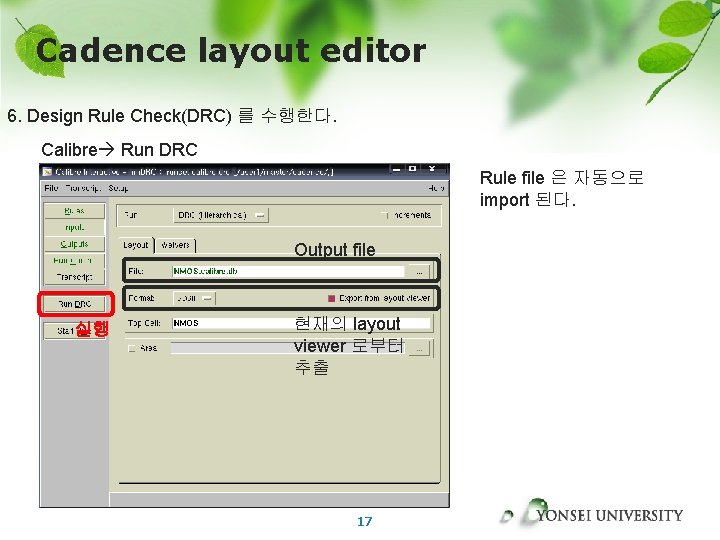

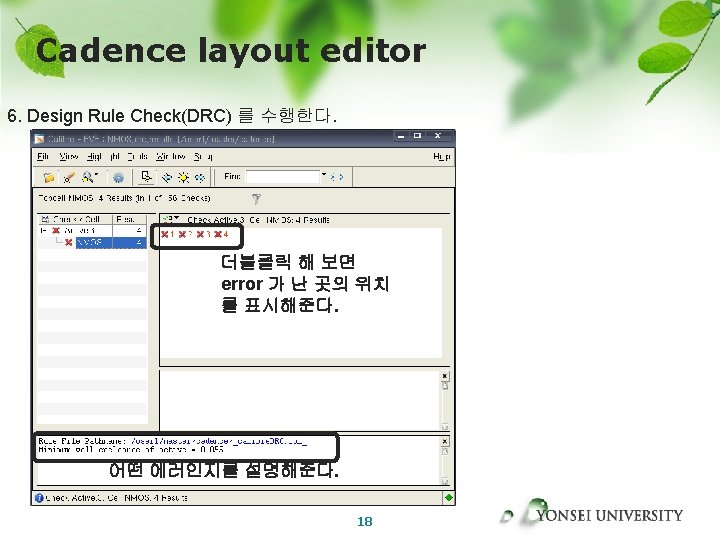

Cadence layout editor 6. Design Rule Check(DRC) 를 수행한다. Calibre Run DRC Rule file 은 자동으로 import 된다. Output file 실행 현재의 layout viewer 로부터 추출 17

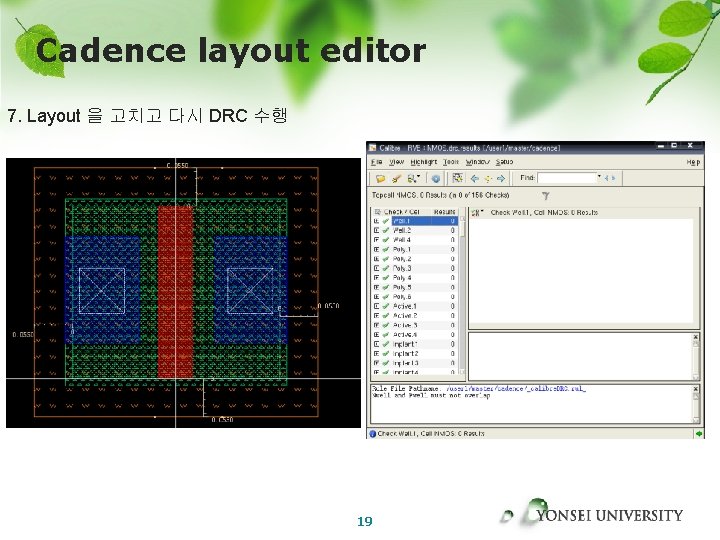

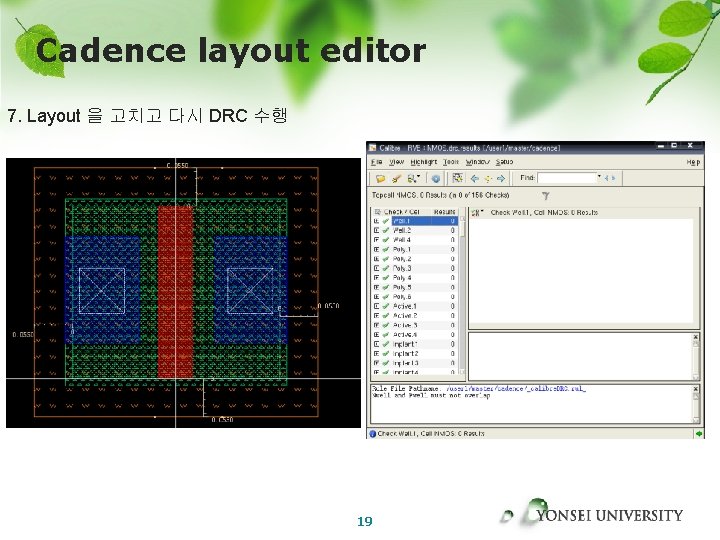

Cadence layout editor 7. Layout 을 고치고 다시 DRC 수행 19

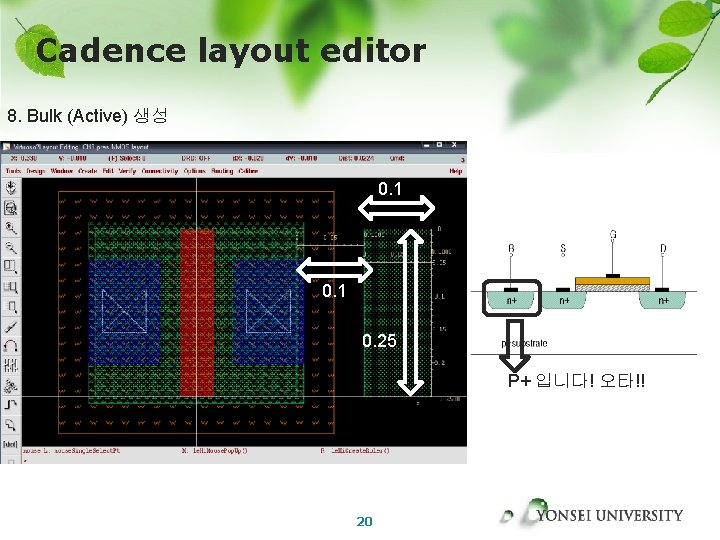

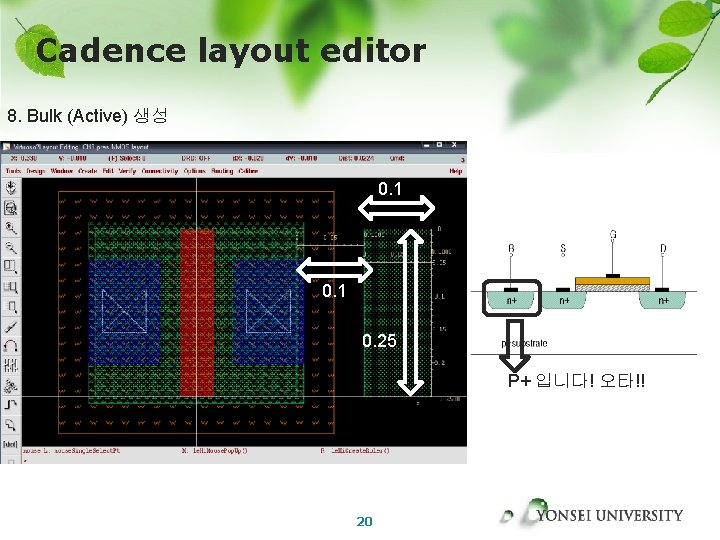

Cadence layout editor 8. Bulk (Active) 생성 0. 1 0. 25 P+ 입니다! 오타!! 20

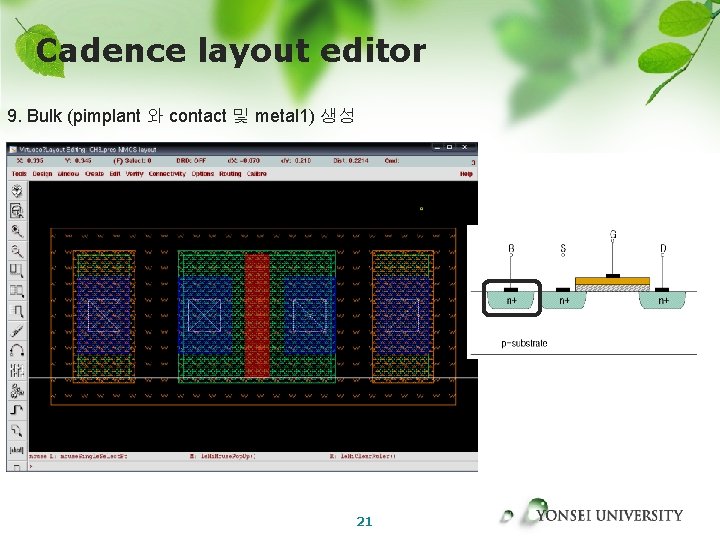

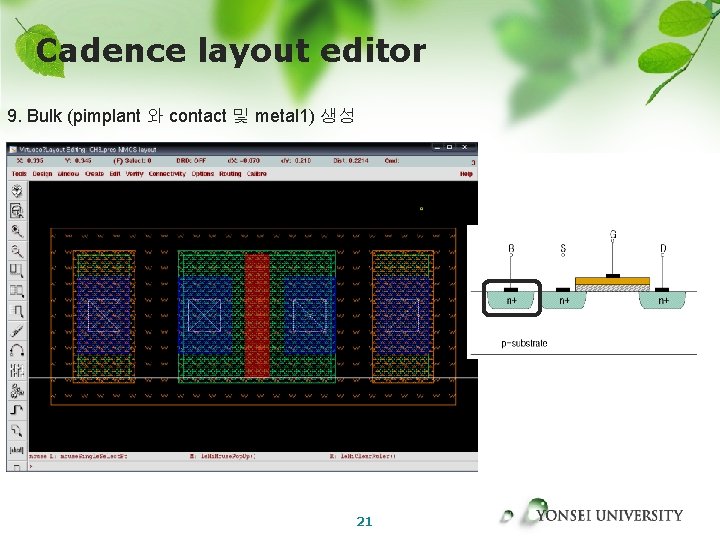

Cadence layout editor 9. Bulk (pimplant 와 contact 및 metal 1) 생성 21

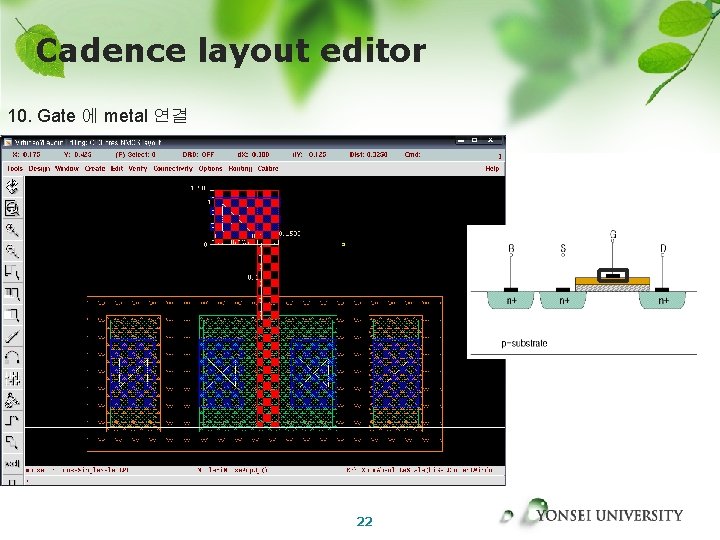

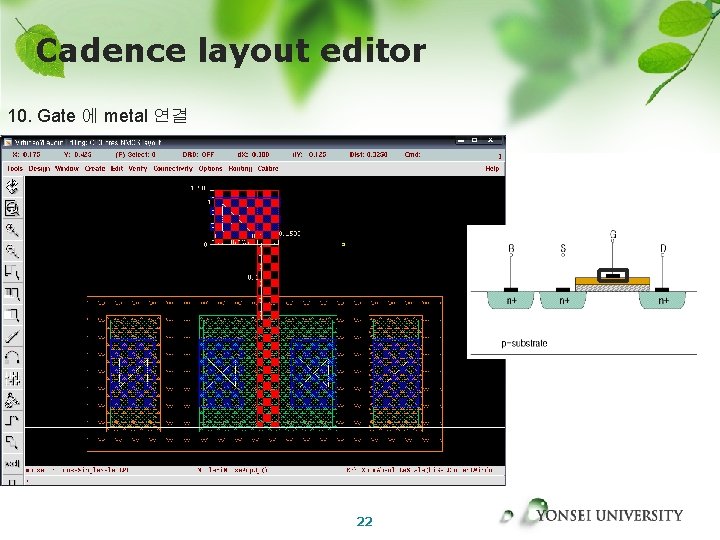

Cadence layout editor 10. Gate 에 metal 연결 22

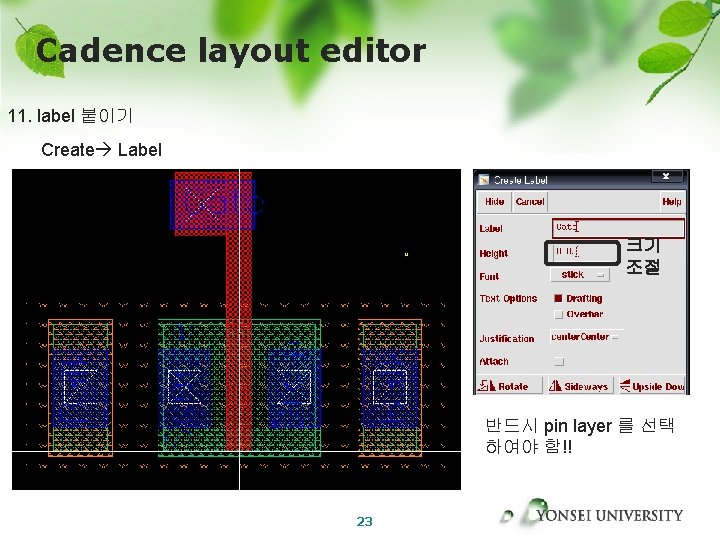

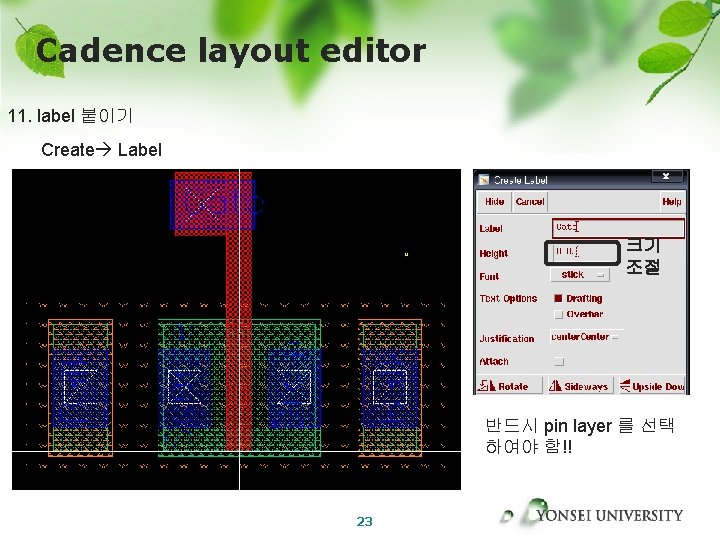

Cadence layout editor 11. label 붙이기 Create Label 크기 조절 반드시 pin layer 를 선택 하여야 함!! 23

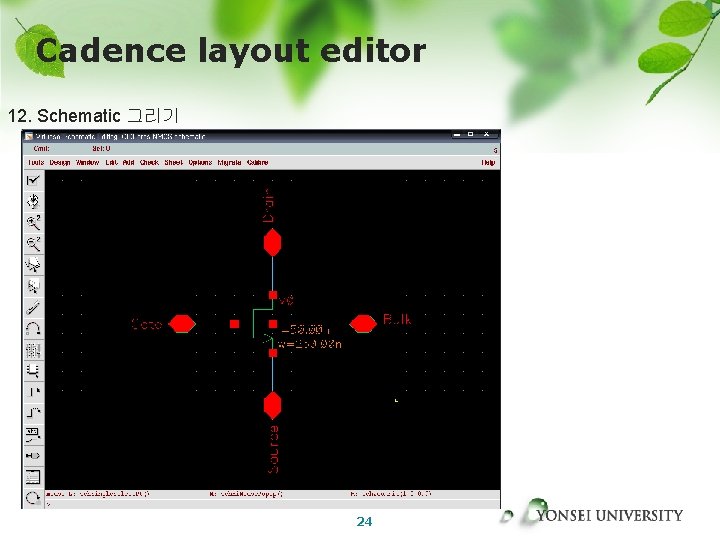

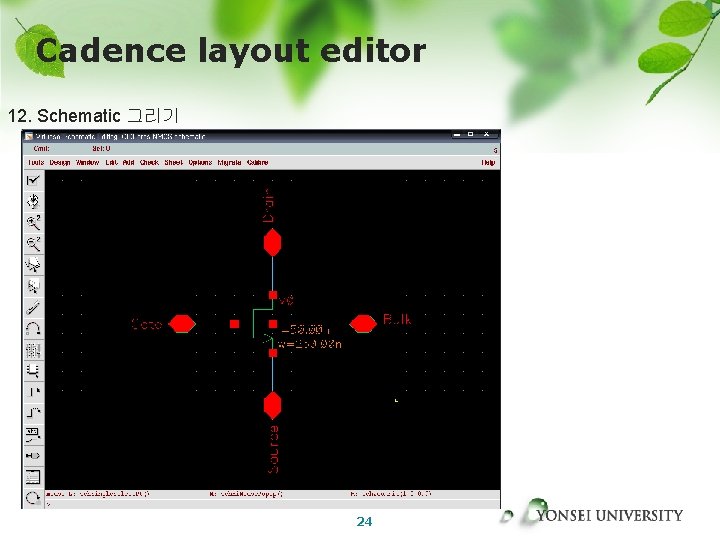

Cadence layout editor 12. Schematic 그리기 24

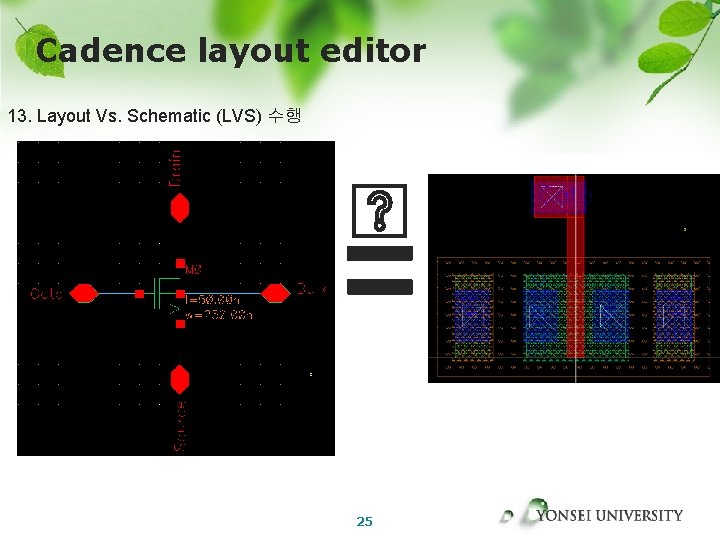

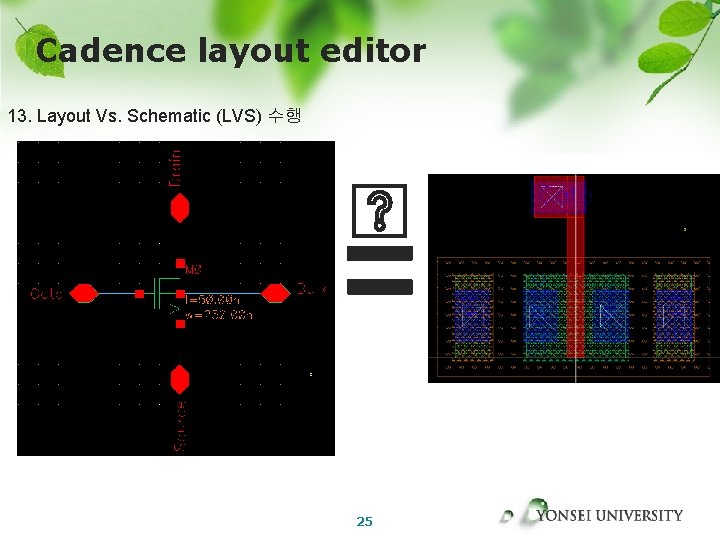

Cadence layout editor 13. Layout Vs. Schematic (LVS) 수행 25

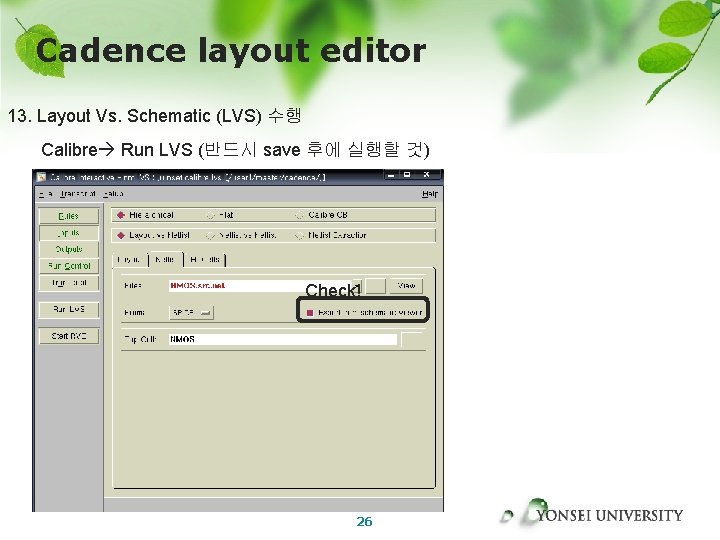

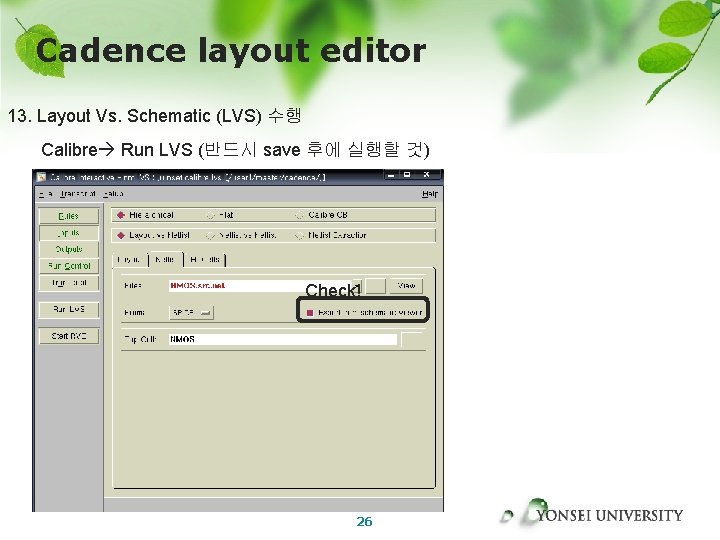

Cadence layout editor 13. Layout Vs. Schematic (LVS) 수행 Calibre Run LVS (반드시 save 후에 실행할 것) Check! 26

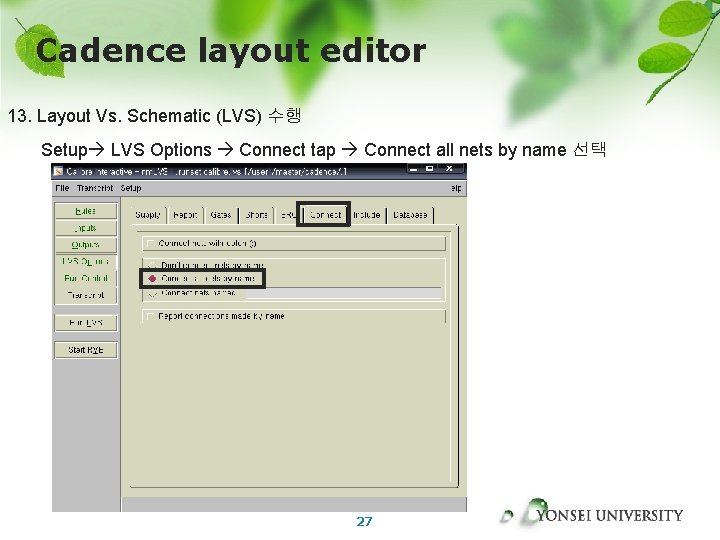

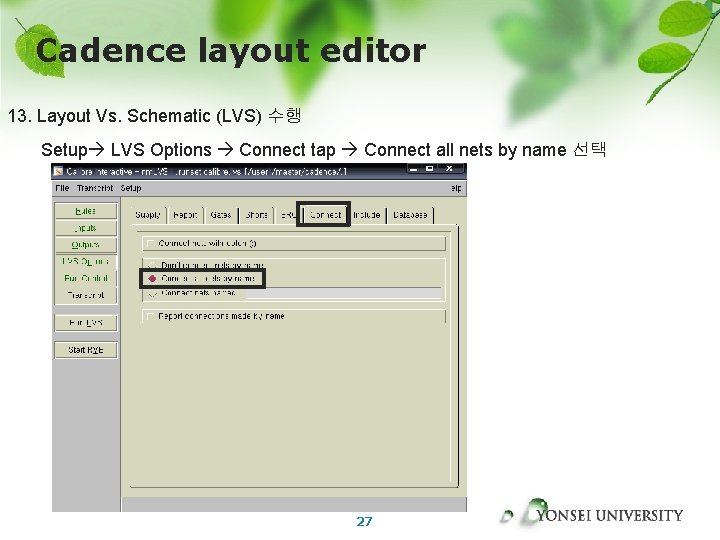

Cadence layout editor 13. Layout Vs. Schematic (LVS) 수행 Setup LVS Options Connect tap Connect all nets by name 선택 27

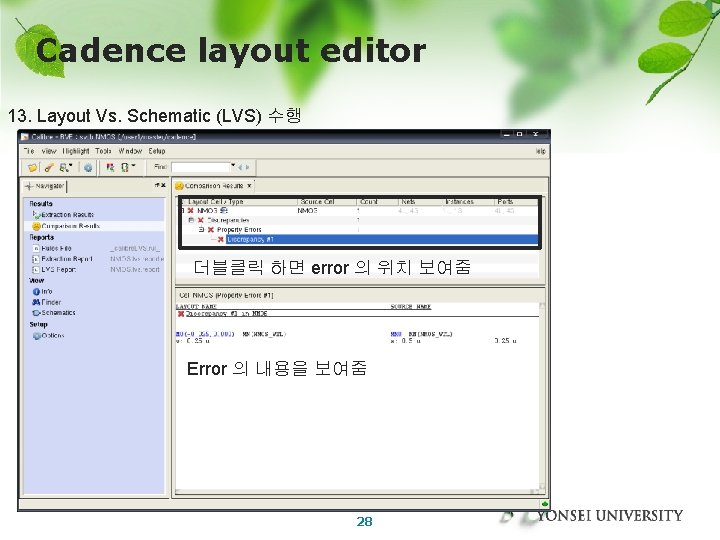

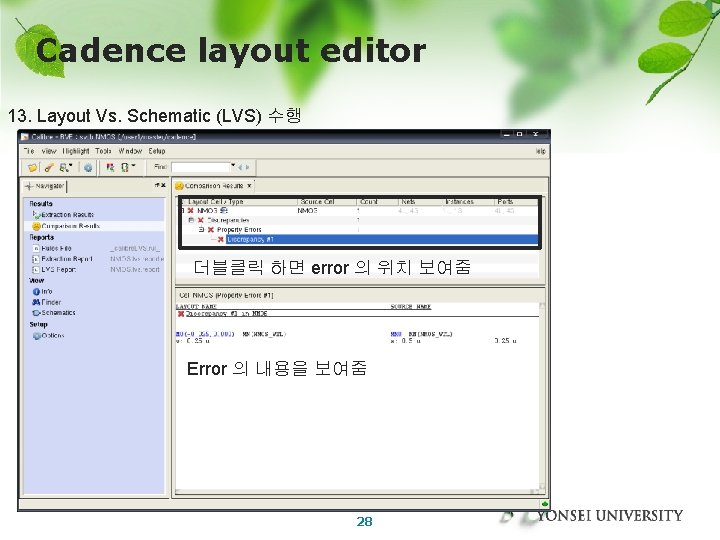

Cadence layout editor 13. Layout Vs. Schematic (LVS) 수행 더블클릭 하면 error 의 위치 보여줌 Error 의 내용을 보여줌 28

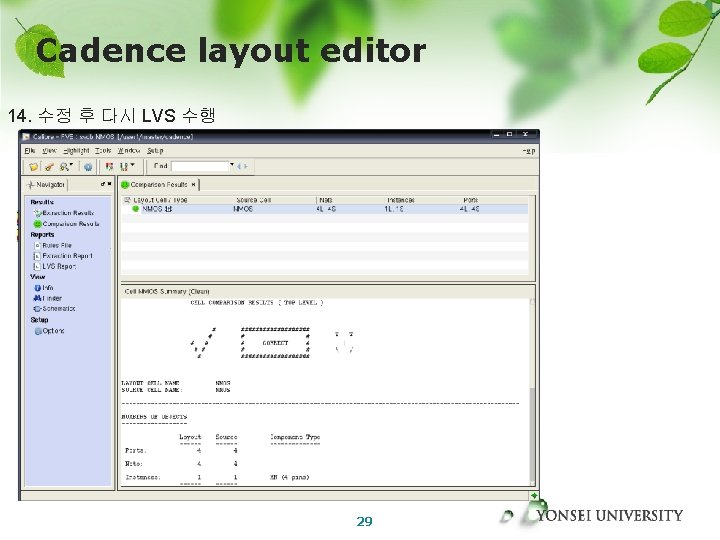

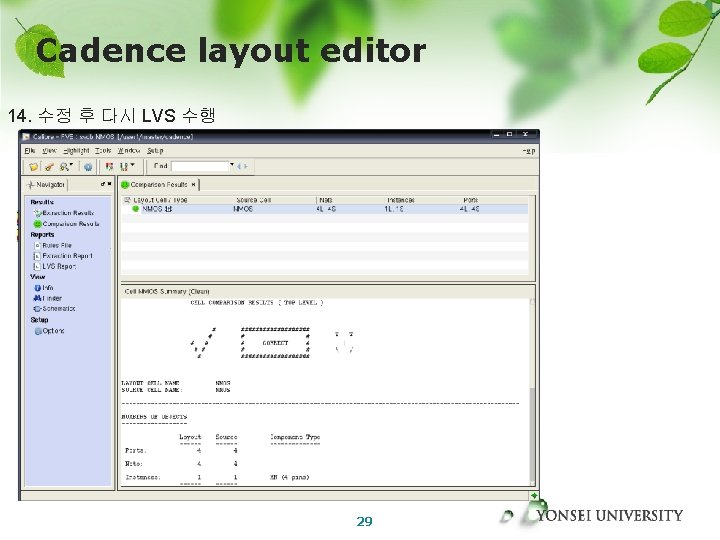

Cadence layout editor 14. 수정 후 다시 LVS 수행 29