Chapter 11 Analog and MixedSignal Testing EE 141

![Histogram – Code Bins Code Bin T[6] 7 245 W[7] T[6] 6 543 W[6] Histogram – Code Bins Code Bin T[6] 7 245 W[7] T[6] 6 543 W[6]](https://slidetodoc.com/presentation_image_h/904b52feafa99458cd7f28daa7af5486/image-102.jpg)

![Test Methods - Nonlinearity Differential Nonlinearity T[6] 7 203 T[6] 6 443 5 440 Test Methods - Nonlinearity Differential Nonlinearity T[6] 7 203 T[6] 6 443 5 440](https://slidetodoc.com/presentation_image_h/904b52feafa99458cd7f28daa7af5486/image-107.jpg)

- Slides: 139

Chapter 11 Analog and Mixed-Signal Testing EE 141 VLSI Test Principles and Architectures 1 Chap. 11 - Analog and Mixed-Signal

What is this chapter about? q Introduces AMS circuits, failure modes and fault models. q Addresses analog testing, including DC and AC parametric testing. q Discusses mixed-signal circuits, ADC and DAC, and their testing approaches. q Studies IEEE Std. 1149. 4, the standard for mixed-signal test buses EE 141 VLSI Test Principles and Architectures 2 Chap. 11 - Analog and Mixed-Signal

Chapter 11 Analog and Mixed-Signal Testing q Introduction q Analog Circuit Testing q Mixed-Signal Testing q IEEE Std. 1149. 4 Standard for Mixed. Signal Test Bus q Concluding Remarks EE 141 VLSI Test Principles and Architectures 3 Chap. 11 - Analog and Mixed-Signal

11. 1 Introduction q Analog Circuit Properties q Analog Defect Mechanism and Fault Models EE 141 VLSI Test Principles and Architectures 4 Chap. 11 - Analog and Mixed-Signal

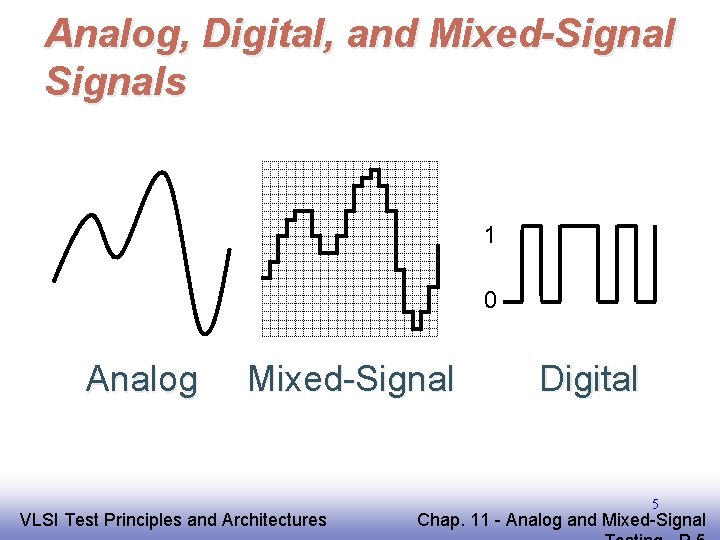

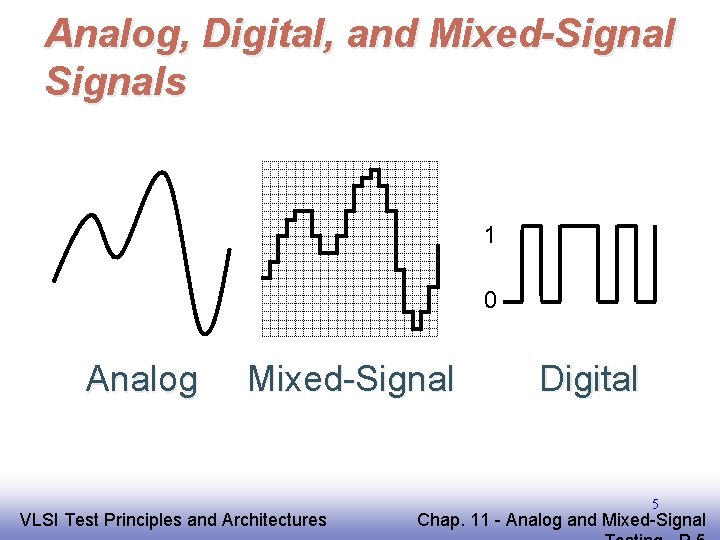

Analog, Digital, and Mixed-Signals 1 0 Analog Mixed-Signal EE 141 VLSI Test Principles and Architectures Digital 5 Chap. 11 - Analog and Mixed-Signal

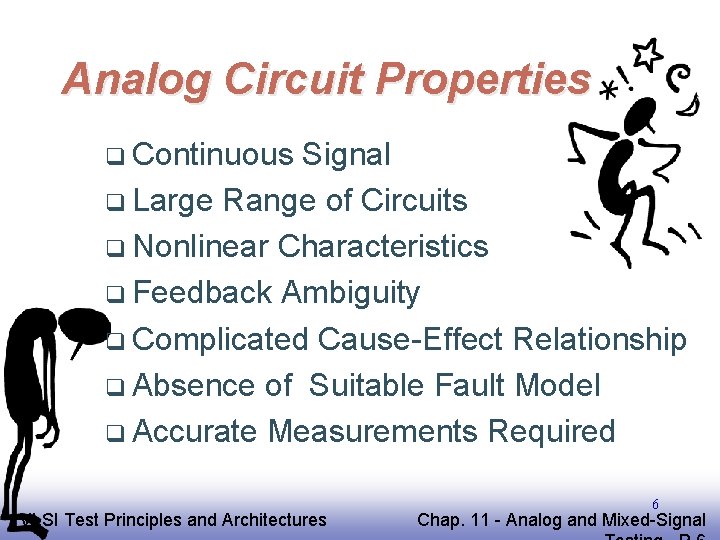

Analog Circuit Properties q Continuous Signal q Large Range of Circuits q Nonlinear Characteristics q Feedback Ambiguity q Complicated Cause-Effect Relationship q Absence of Suitable Fault Model q Accurate Measurements Required EE 141 VLSI Test Principles and Architectures 6 Chap. 11 - Analog and Mixed-Signal

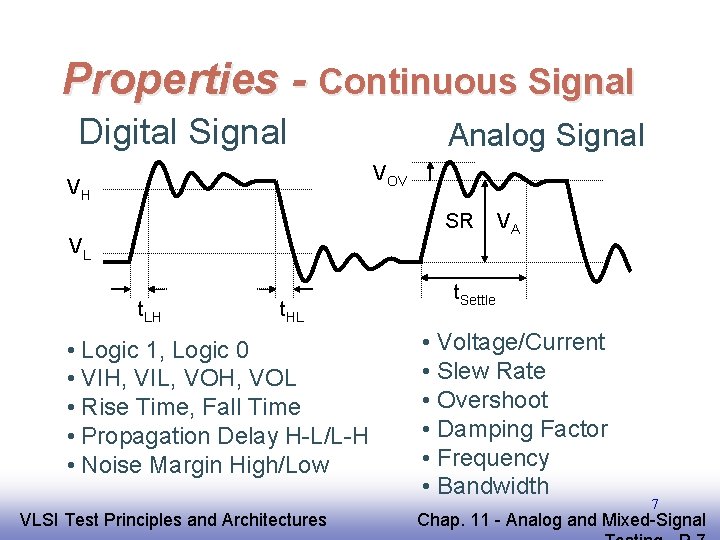

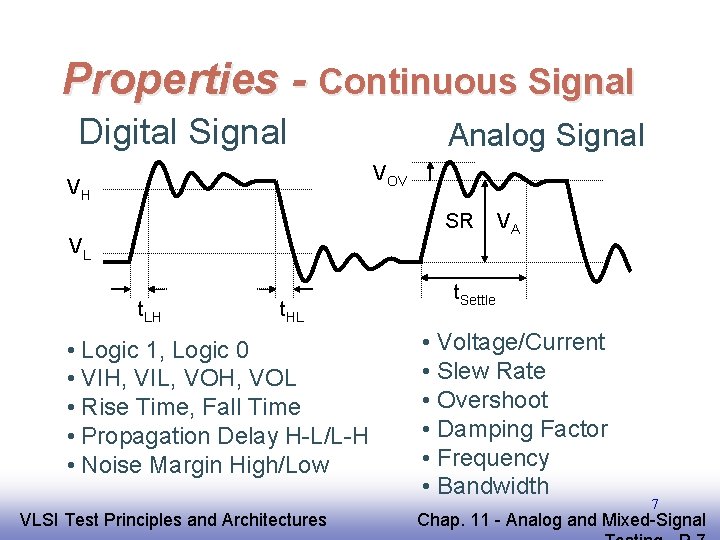

Properties - Continuous Signal Digital Signal Analog Signal VOV VH SR VL t. LH t. HL • Logic 1, Logic 0 • VIH, VIL, VOH, VOL • Rise Time, Fall Time • Propagation Delay H-L/L-H • Noise Margin High/Low EE 141 VLSI Test Principles and Architectures VA t. Settle • Voltage/Current • Slew Rate • Overshoot • Damping Factor • Frequency • Bandwidth 7 Chap. 11 - Analog and Mixed-Signal

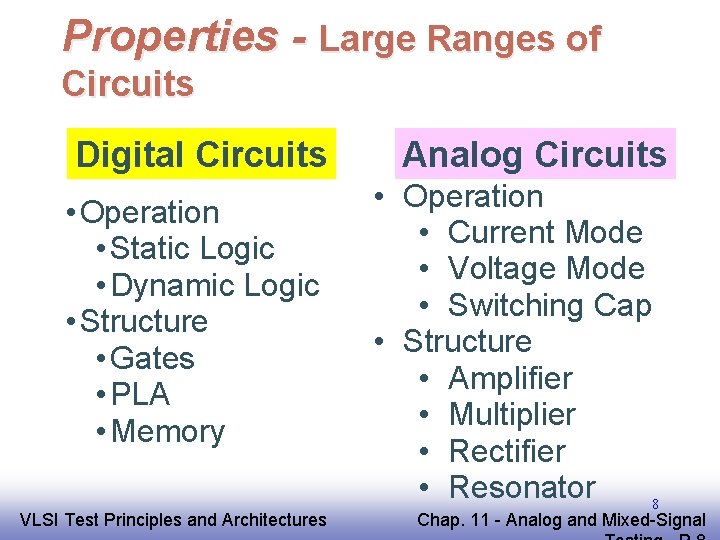

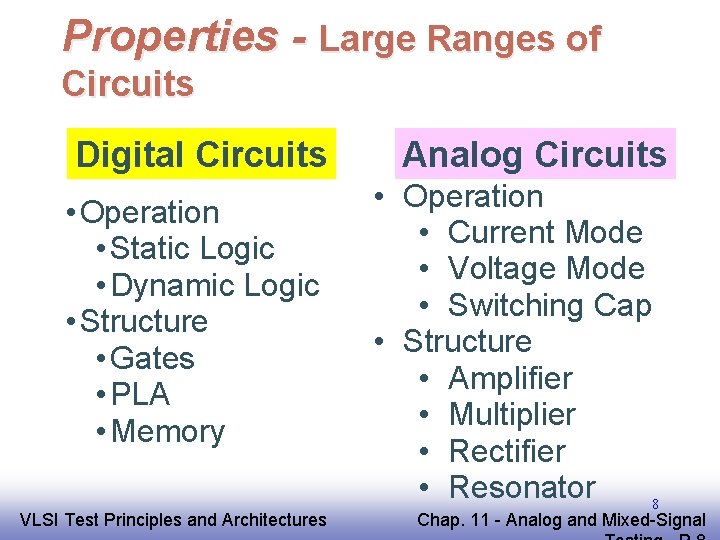

Properties - Large Ranges of Circuits Digital Circuits • Operation • Static Logic • Dynamic Logic • Structure • Gates • PLA • Memory EE 141 VLSI Test Principles and Architectures Analog Circuits • Operation • Current Mode • Voltage Mode • Switching Cap • Structure • Amplifier • Multiplier • Rectifier • Resonator 8 Chap. 11 - Analog and Mixed-Signal

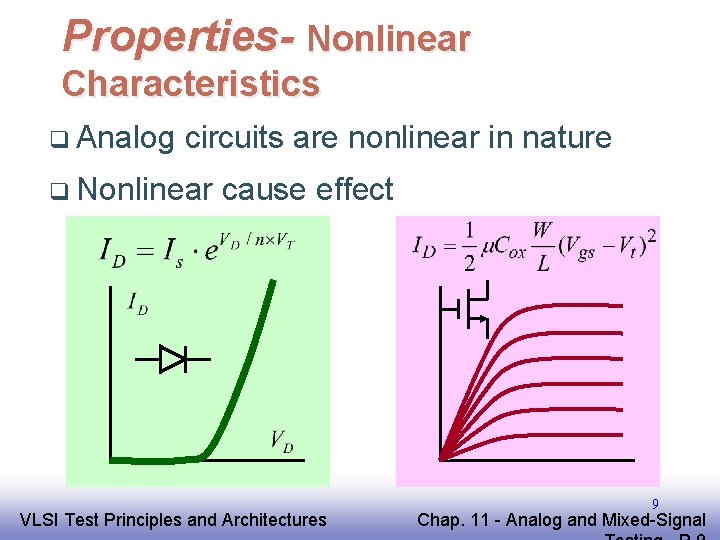

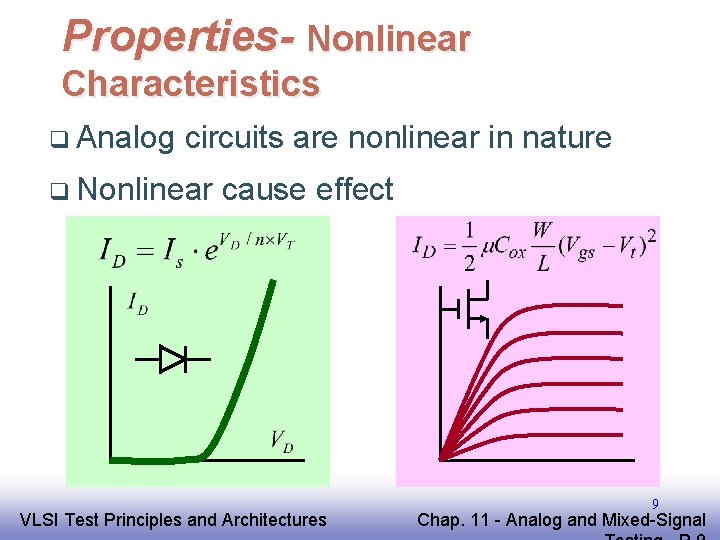

Properties- Nonlinear Characteristics q Analog circuits are nonlinear in nature q Nonlinear cause effect EE 141 VLSI Test Principles and Architectures 9 Chap. 11 - Analog and Mixed-Signal

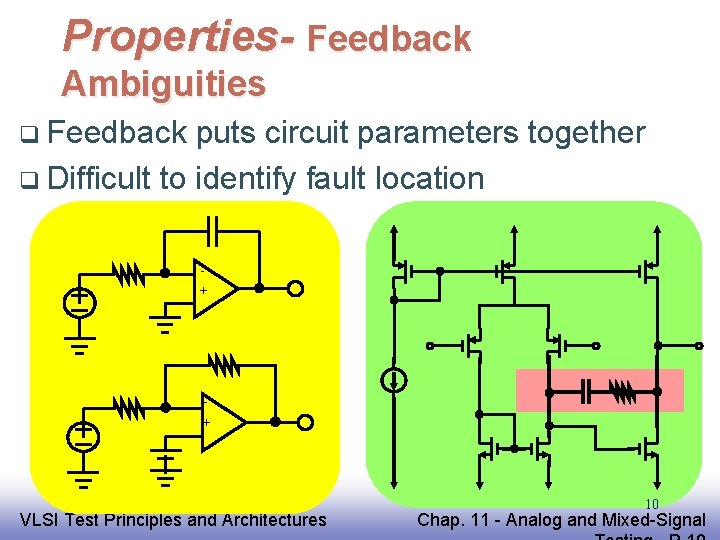

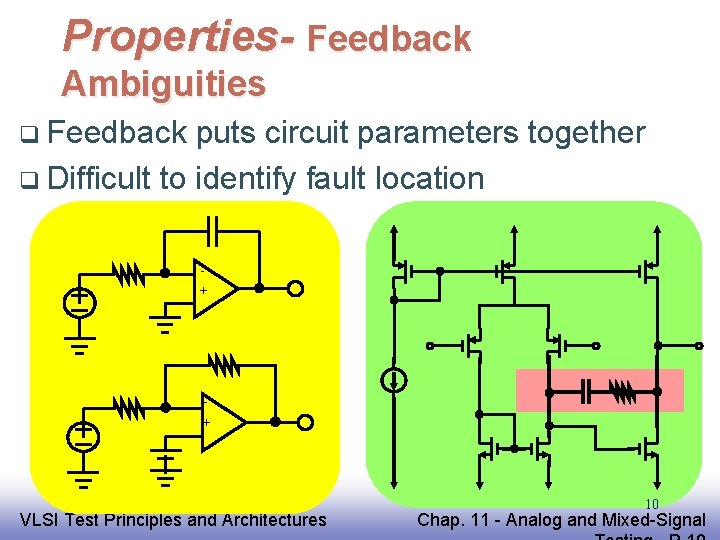

Properties- Feedback Ambiguities q Feedback puts circuit parameters together q Difficult to identify fault location + + EE 141 VLSI Test Principles and Architectures 10 Chap. 11 - Analog and Mixed-Signal

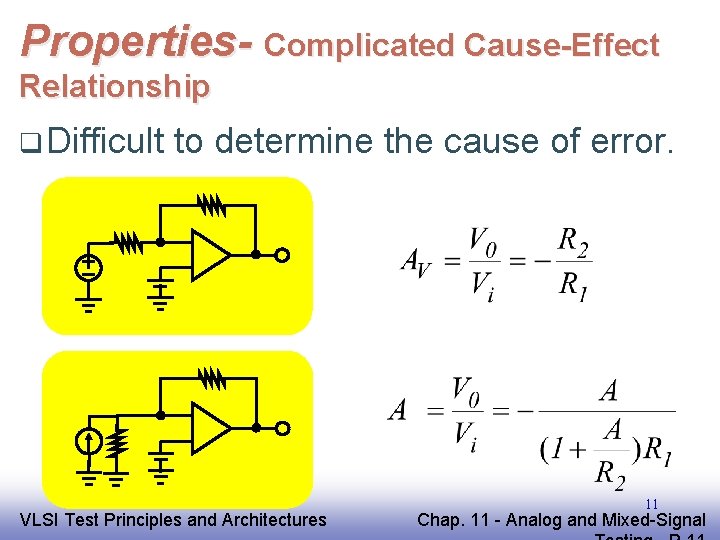

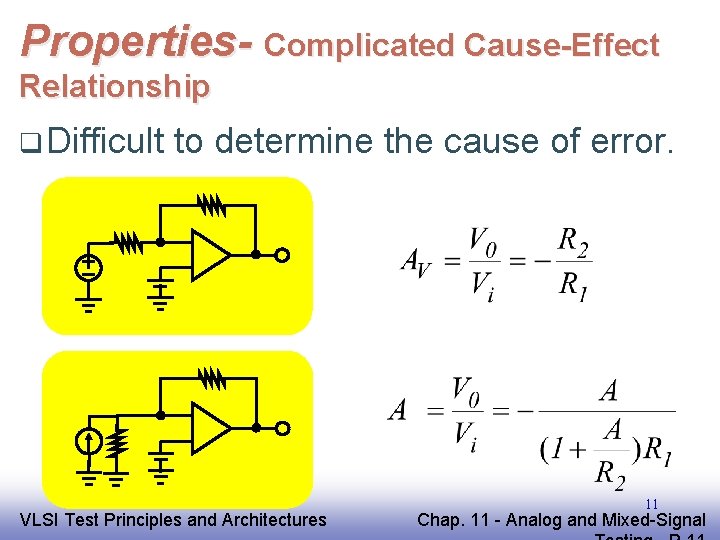

Properties- Complicated Cause-Effect Relationship q Difficult to determine the cause of error. EE 141 VLSI Test Principles and Architectures 11 Chap. 11 - Analog and Mixed-Signal

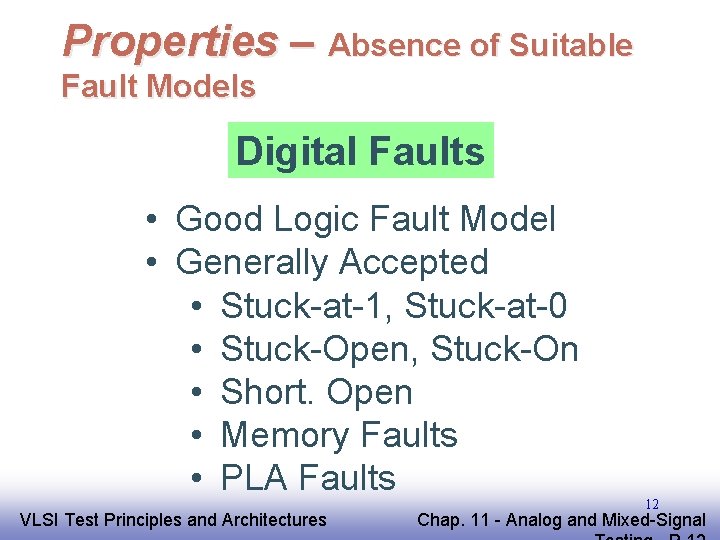

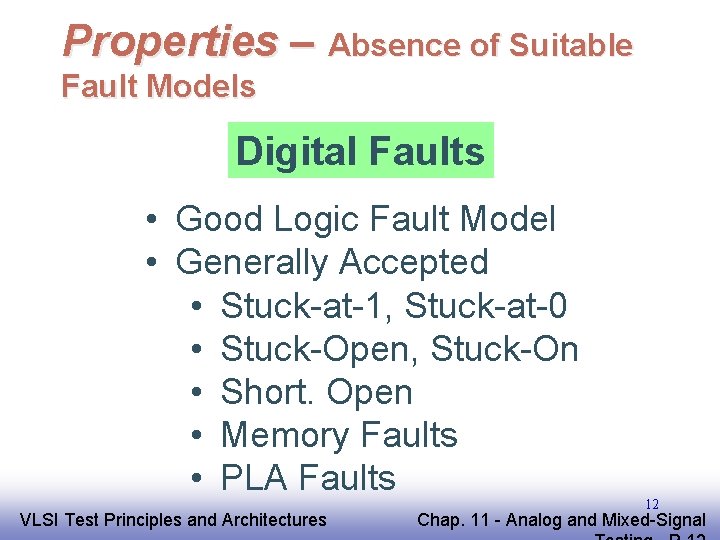

Properties – Absence of Suitable Fault Models Digital Faults • Good Logic Fault Model • Generally Accepted • Stuck-at-1, Stuck-at-0 • Stuck-Open, Stuck-On • Short. Open • Memory Faults • PLA Faults EE 141 VLSI Test Principles and Architectures 12 Chap. 11 - Analog and Mixed-Signal

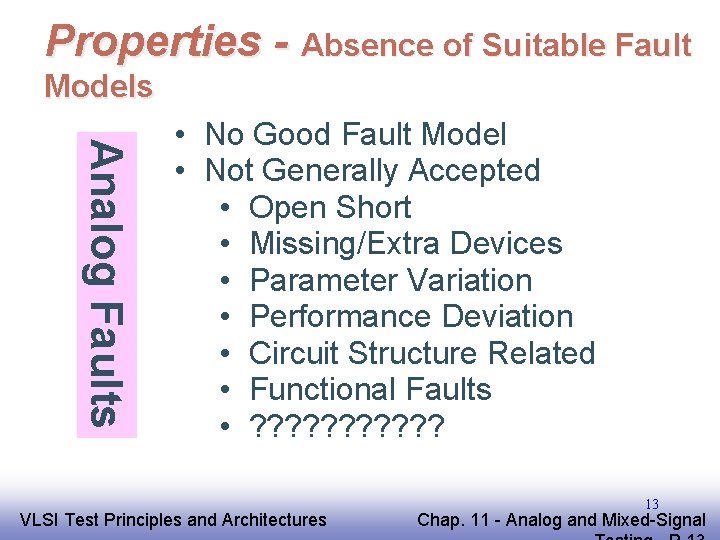

Properties - Absence of Suitable Fault Models Analog Faults • No Good Fault Model • Not Generally Accepted • Open Short • Missing/Extra Devices • Parameter Variation • Performance Deviation • Circuit Structure Related • Functional Faults • ? ? ? EE 141 VLSI Test Principles and Architectures 13 Chap. 11 - Analog and Mixed-Signal

Properties – Accurate Measurements Required Digital Instrument • Oscilloscope • Function Generator • Logic Analyzer • Frequency Counter EE 141 VLSI Test Principles and Architectures 14 Chap. 11 - Analog and Mixed-Signal

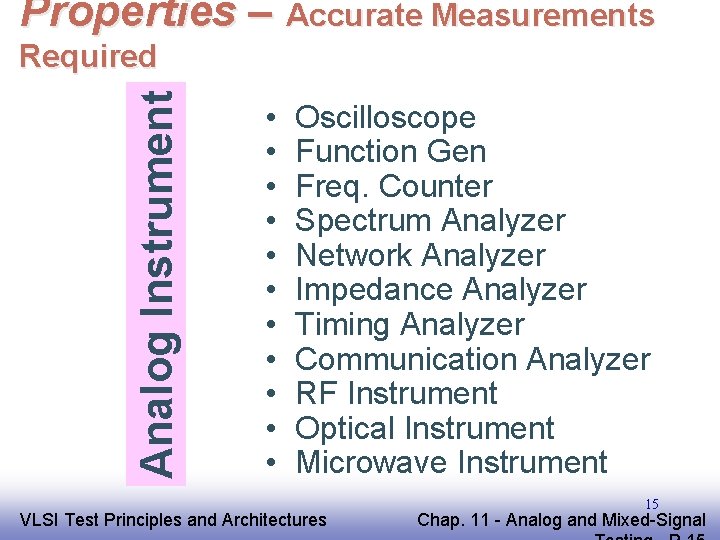

Properties – Accurate Measurements Analog Instrument Required • • • Oscilloscope Function Gen Freq. Counter Spectrum Analyzer Network Analyzer Impedance Analyzer Timing Analyzer Communication Analyzer RF Instrument Optical Instrument Microwave Instrument EE 141 VLSI Test Principles and Architectures 15 Chap. 11 - Analog and Mixed-Signal

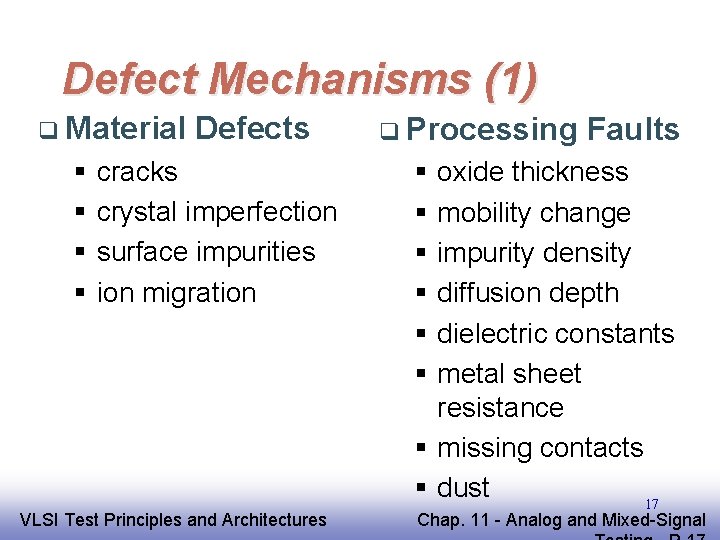

11. 1 Introduction q Analog Circuit Properties q Analog Defect Mechanism and Fault Models EE 141 VLSI Test Principles and Architectures 16 Chap. 11 - Analog and Mixed-Signal

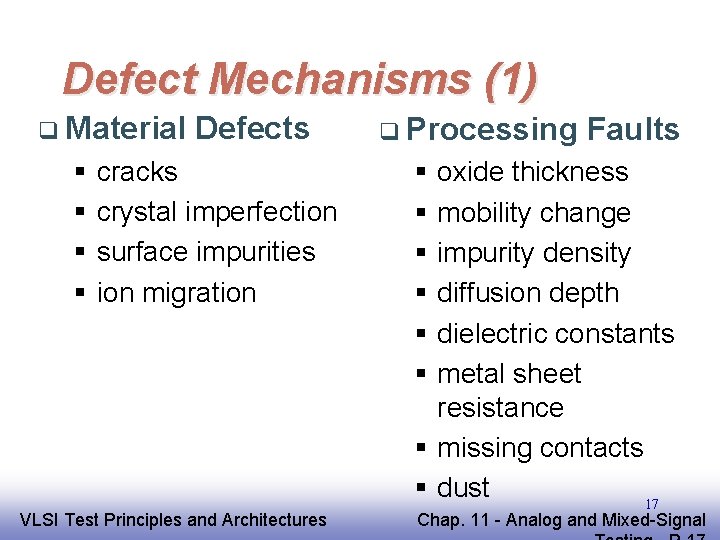

Defect Mechanisms (1) q Material § § Defects cracks crystal imperfection surface impurities ion migration EE 141 VLSI Test Principles and Architectures q Processing Faults § § § oxide thickness mobility change impurity density diffusion depth dielectric constants metal sheet resistance § missing contacts § dust 17 Chap. 11 - Analog and Mixed-Signal

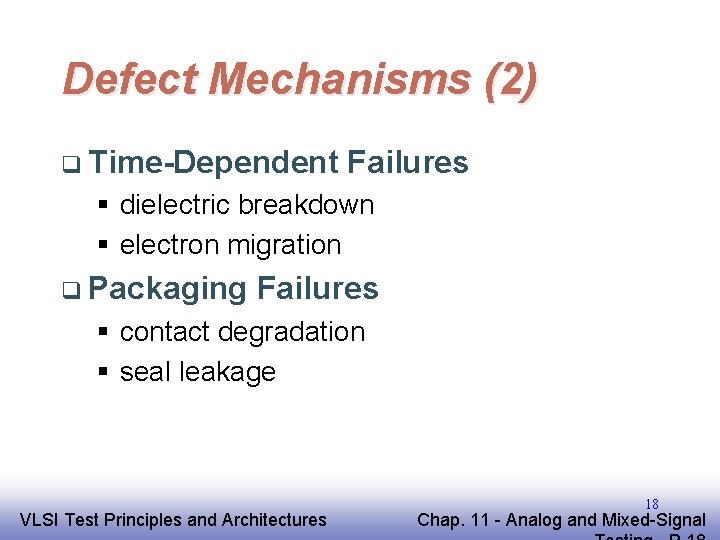

Defect Mechanisms (2) q Time-Dependent Failures § dielectric breakdown § electron migration q Packaging Failures § contact degradation § seal leakage EE 141 VLSI Test Principles and Architectures 18 Chap. 11 - Analog and Mixed-Signal

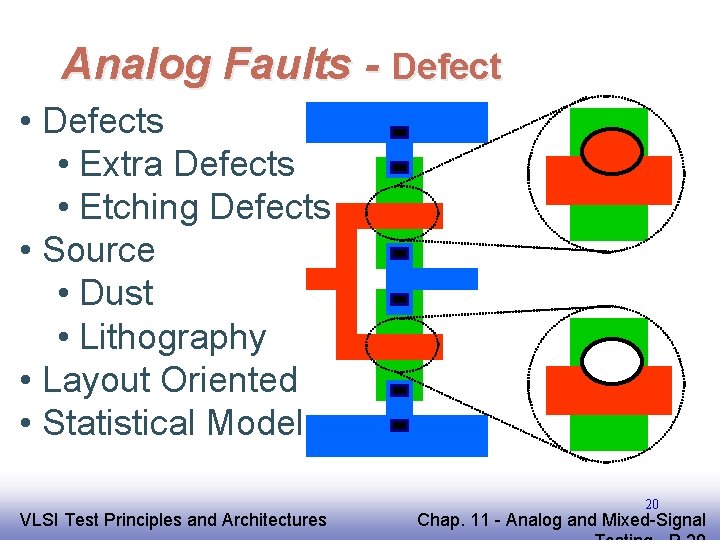

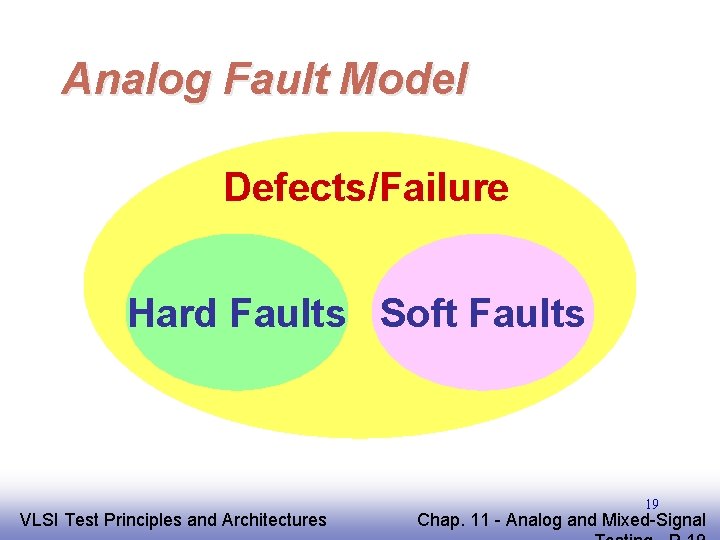

Analog Fault Model Defects/Failure Hard Faults Soft Faults EE 141 VLSI Test Principles and Architectures 19 Chap. 11 - Analog and Mixed-Signal

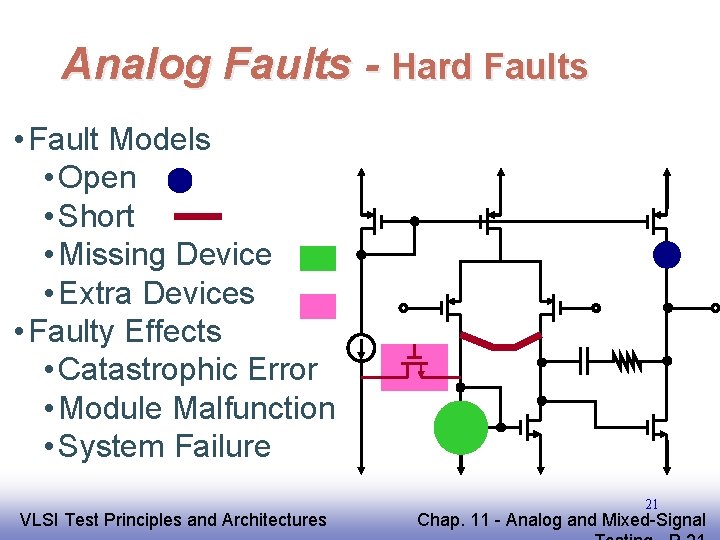

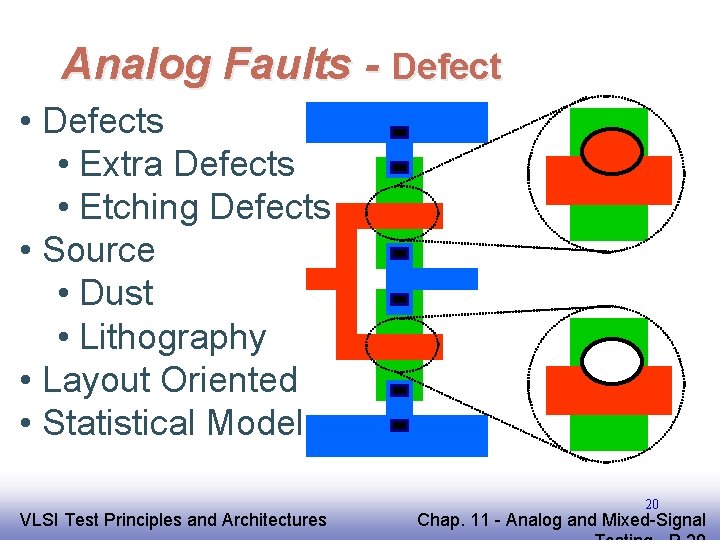

Analog Faults - Defect • Defects • Extra Defects • Etching Defects • Source • Dust • Lithography • Layout Oriented • Statistical Model EE 141 VLSI Test Principles and Architectures 20 Chap. 11 - Analog and Mixed-Signal

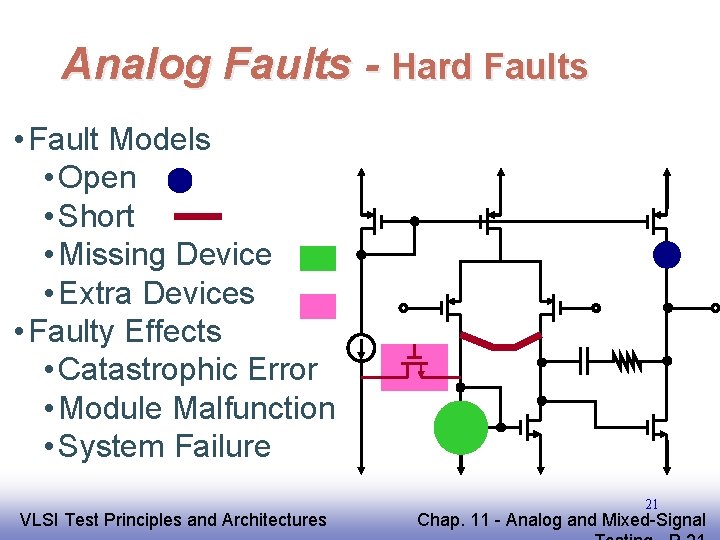

Analog Faults - Hard Faults • Fault Models • Open • Short • Missing Device • Extra Devices • Faulty Effects • Catastrophic Error • Module Malfunction • System Failure EE 141 VLSI Test Principles and Architectures 21 Chap. 11 - Analog and Mixed-Signal

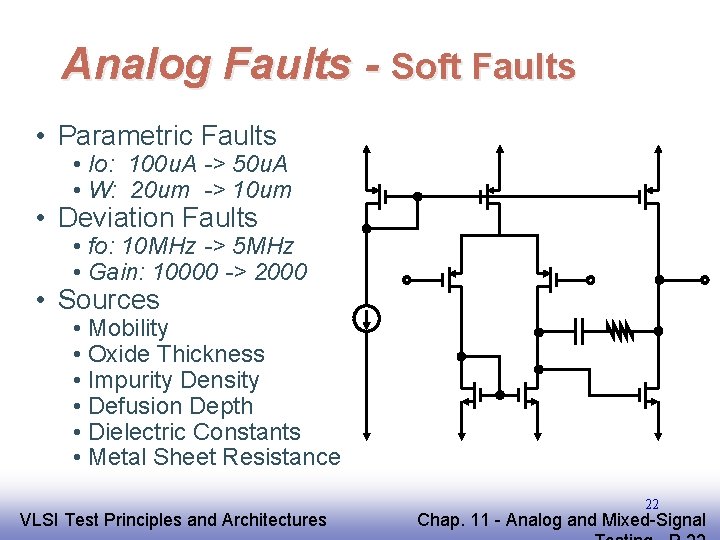

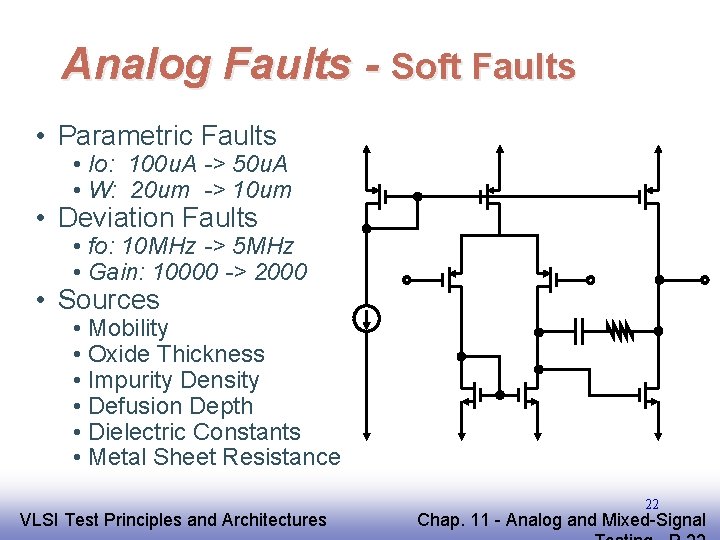

Analog Faults - Soft Faults • Parametric Faults • Io: 100 u. A -> 50 u. A • W: 20 um -> 10 um • Deviation Faults • fo: 10 MHz -> 5 MHz • Gain: 10000 -> 2000 • Sources • Mobility • Oxide Thickness • Impurity Density • Defusion Depth • Dielectric Constants • Metal Sheet Resistance EE 141 VLSI Test Principles and Architectures 22 Chap. 11 - Analog and Mixed-Signal

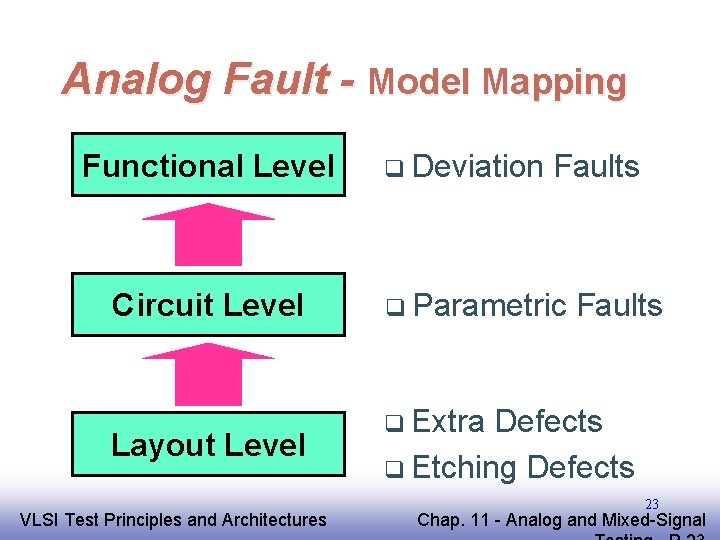

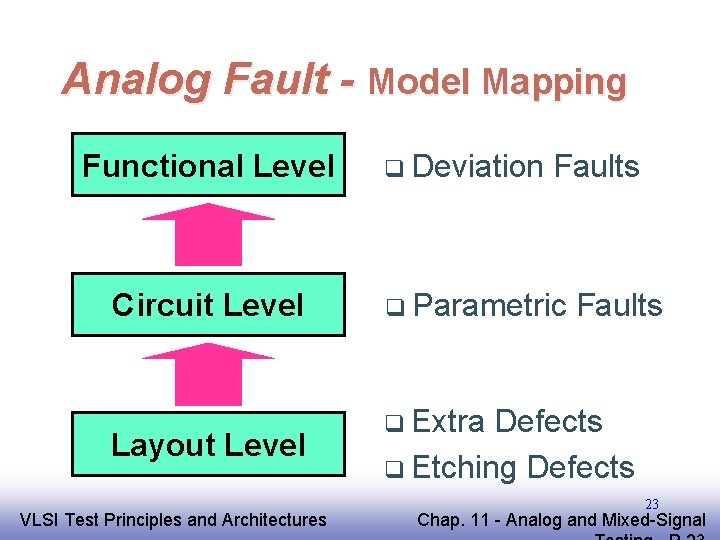

Analog Fault - Model Mapping Functional Level Circuit Level Layout Level EE 141 VLSI Test Principles and Architectures q Deviation Faults q Parametric Faults q Extra Defects q Etching Defects 23 Chap. 11 - Analog and Mixed-Signal

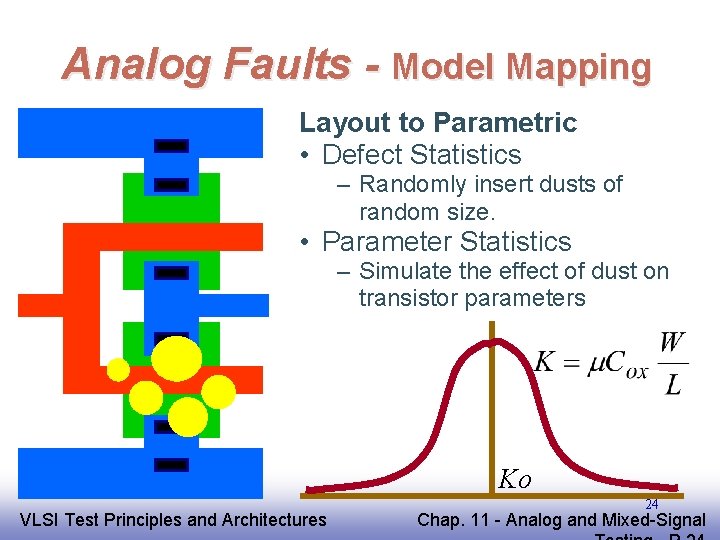

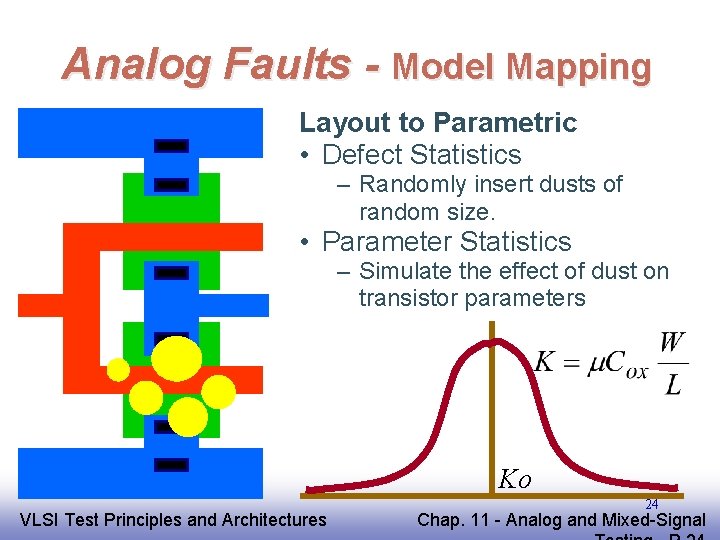

Analog Faults - Model Mapping Layout to Parametric • Defect Statistics – Randomly insert dusts of random size. • Parameter Statistics – Simulate the effect of dust on transistor parameters Ko EE 141 VLSI Test Principles and Architectures 24 Chap. 11 - Analog and Mixed-Signal

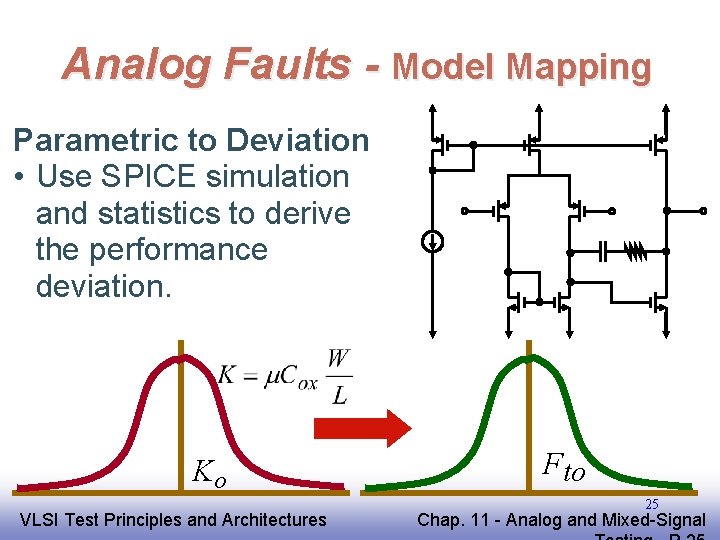

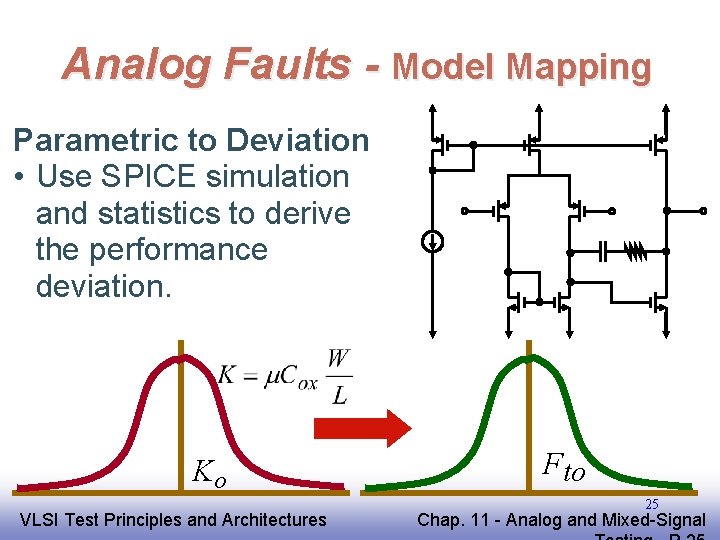

Analog Faults - Model Mapping Parametric to Deviation • Use SPICE simulation and statistics to derive the performance deviation. Ko EE 141 VLSI Test Principles and Architectures Fto 25 Chap. 11 - Analog and Mixed-Signal

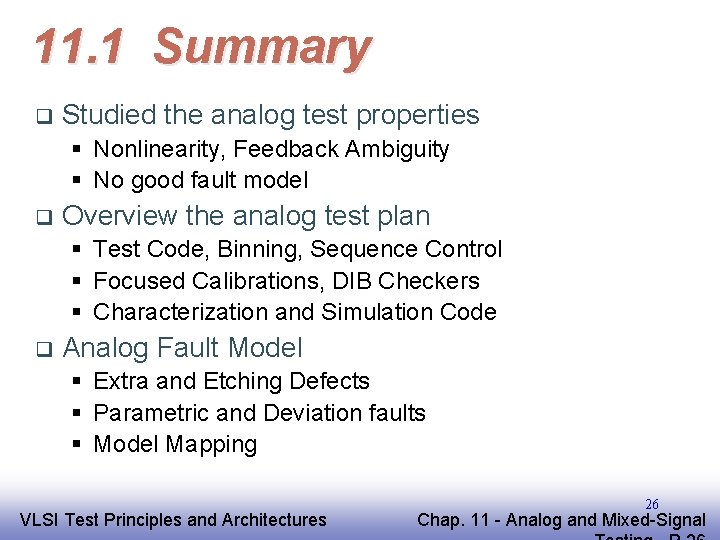

11. 1 Summary q Studied the analog test properties § Nonlinearity, Feedback Ambiguity § No good fault model q Overview the analog test plan § Test Code, Binning, Sequence Control § Focused Calibrations, DIB Checkers § Characterization and Simulation Code q Analog Fault Model § Extra and Etching Defects § Parametric and Deviation faults § Model Mapping EE 141 VLSI Test Principles and Architectures 26 Chap. 11 - Analog and Mixed-Signal

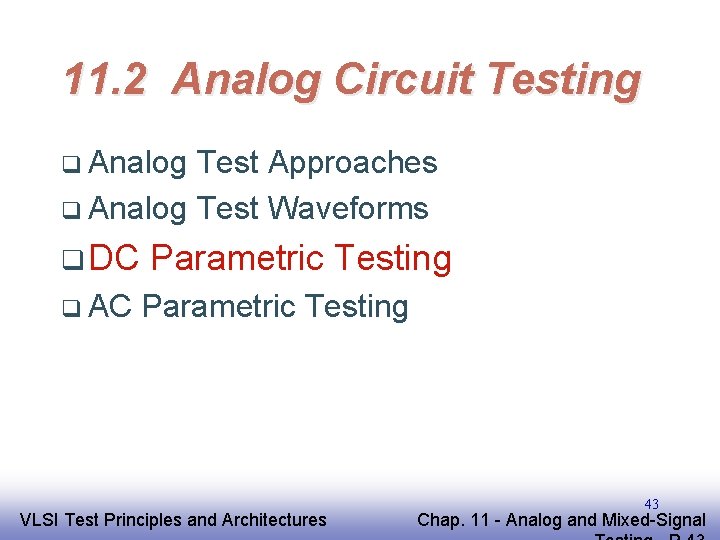

11. 2 Analog Circuit Testing q Analog Test Approaches q Analog Test Waveforms q DC Parametric Testing q AC Parametric Testing EE 141 VLSI Test Principles and Architectures 27 Chap. 11 - Analog and Mixed-Signal

Analog Testing Spec Oriented Waveform Oriented EE 141 VLSI Test Principles and Architectures 28 Chap. 11 - Analog and Mixed-Signal

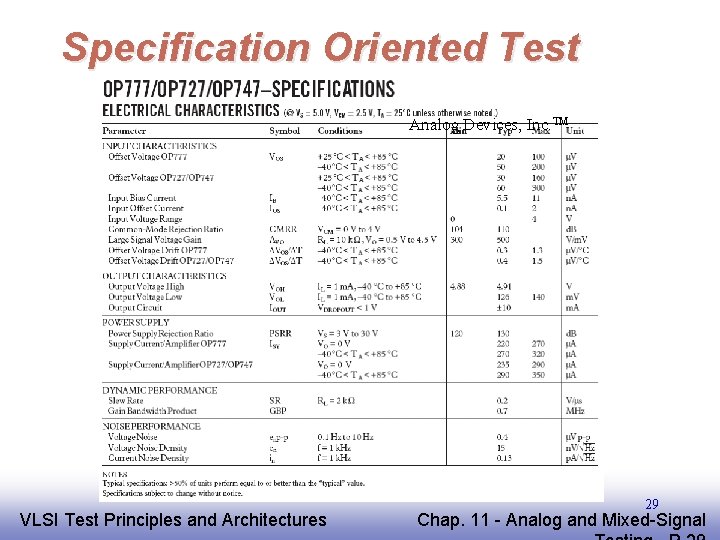

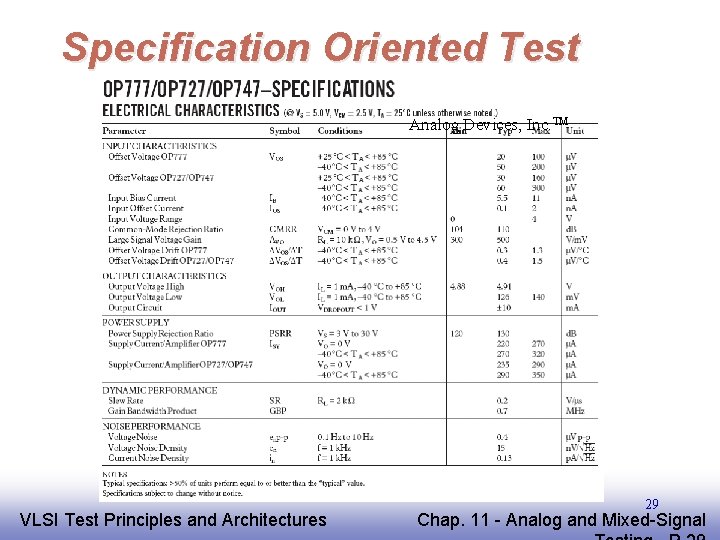

Specification Oriented Test Analog Devices, Inc. TM EE 141 VLSI Test Principles and Architectures 29 Chap. 11 - Analog and Mixed-Signal

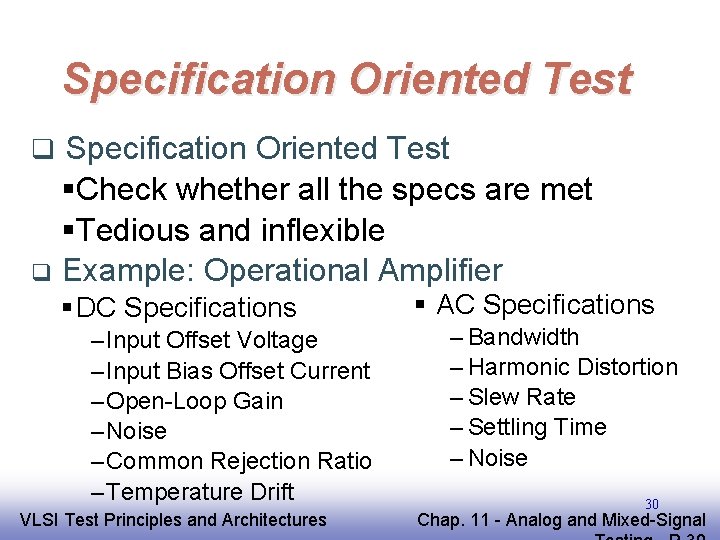

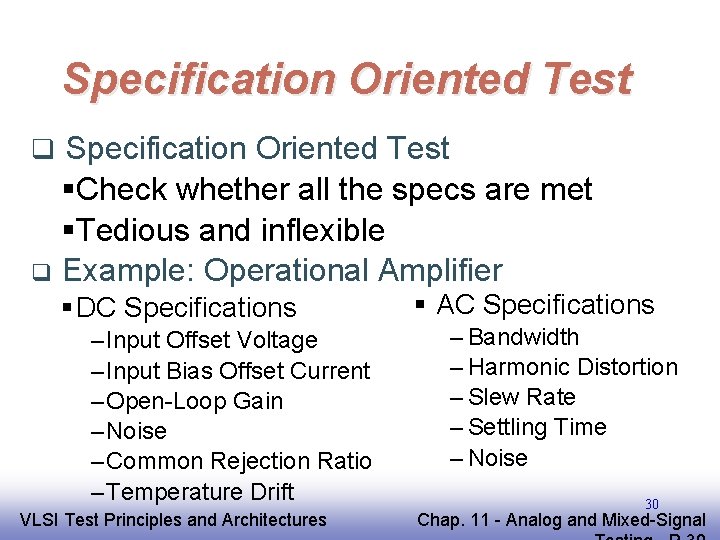

Specification Oriented Test q Specification Oriented Test §Check whether all the specs are met §Tedious and inflexible q Example: Operational Amplifier § DC Specifications – Input Offset Voltage – Input Bias Offset Current – Open-Loop Gain – Noise – Common Rejection Ratio – Temperature Drift EE 141 VLSI Test Principles and Architectures § AC Specifications – Bandwidth – Harmonic Distortion – Slew Rate – Settling Time – Noise 30 Chap. 11 - Analog and Mixed-Signal

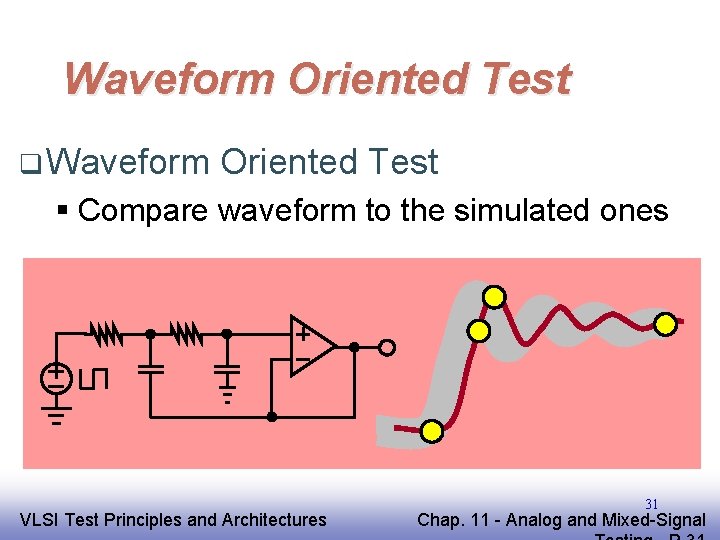

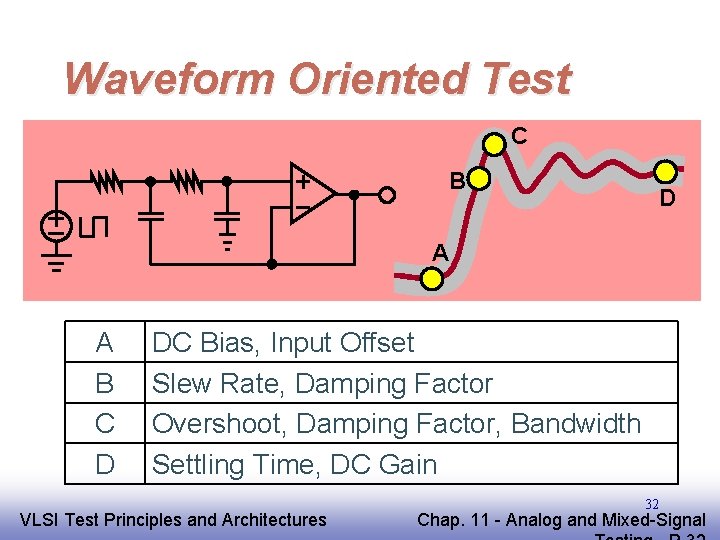

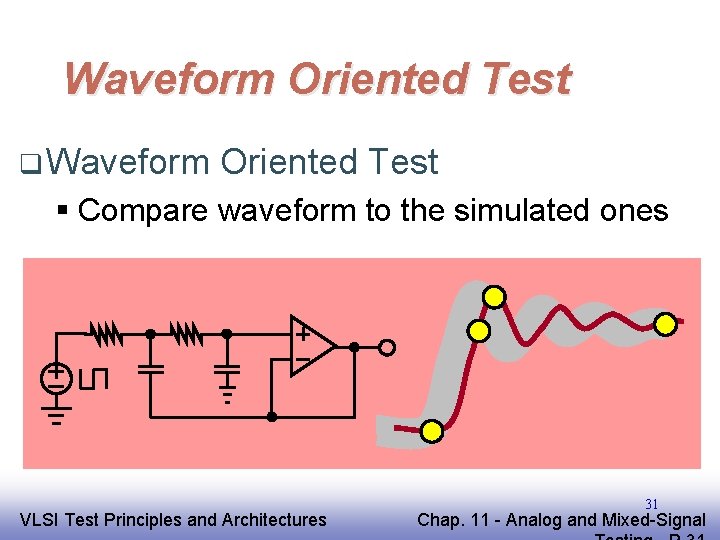

Waveform Oriented Test q Waveform Oriented Test § Compare waveform to the simulated ones EE 141 VLSI Test Principles and Architectures 31 Chap. 11 - Analog and Mixed-Signal

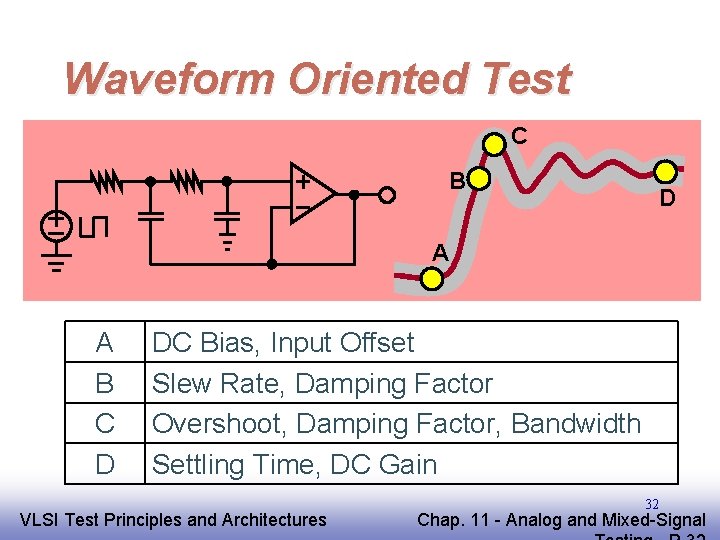

Waveform Oriented Test C B D A A B C D DC Bias, Input Offset Slew Rate, Damping Factor Overshoot, Damping Factor, Bandwidth Settling Time, DC Gain EE 141 VLSI Test Principles and Architectures 32 Chap. 11 - Analog and Mixed-Signal

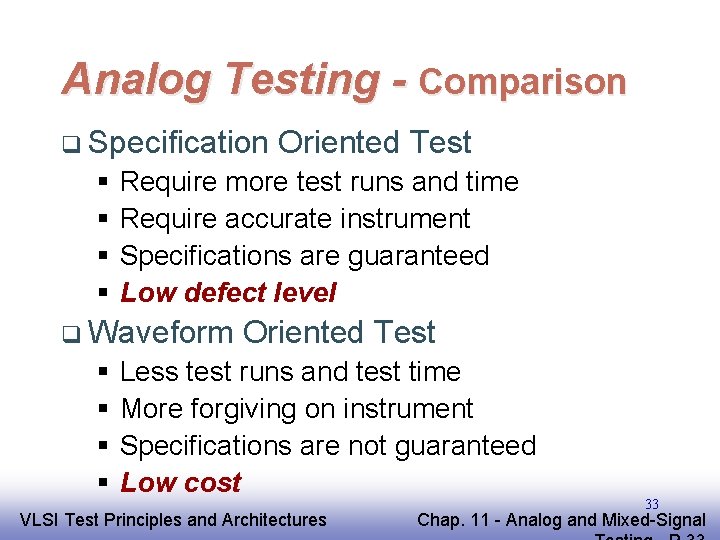

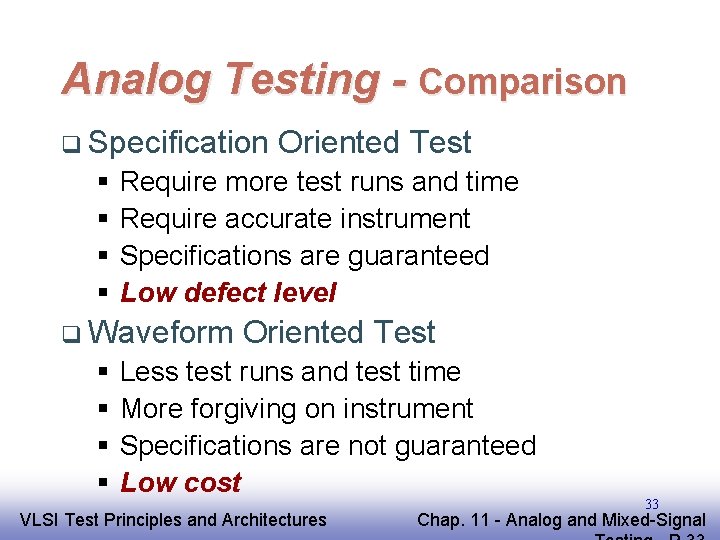

Analog Testing - Comparison q Specification § § Require more test runs and time Require accurate instrument Specifications are guaranteed Low defect level q Waveform § § Oriented Test Less test runs and test time More forgiving on instrument Specifications are not guaranteed Low cost EE 141 VLSI Test Principles and Architectures 33 Chap. 11 - Analog and Mixed-Signal

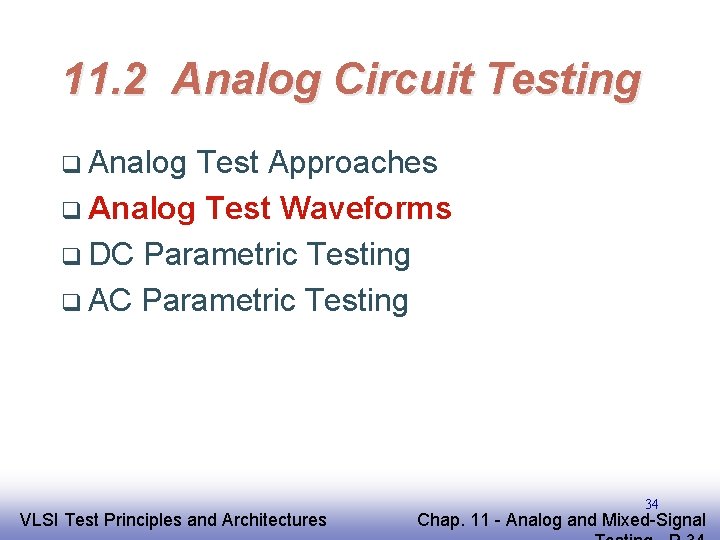

11. 2 Analog Circuit Testing q Analog Test Approaches q Analog Test Waveforms q DC Parametric Testing q AC Parametric Testing EE 141 VLSI Test Principles and Architectures 34 Chap. 11 - Analog and Mixed-Signal

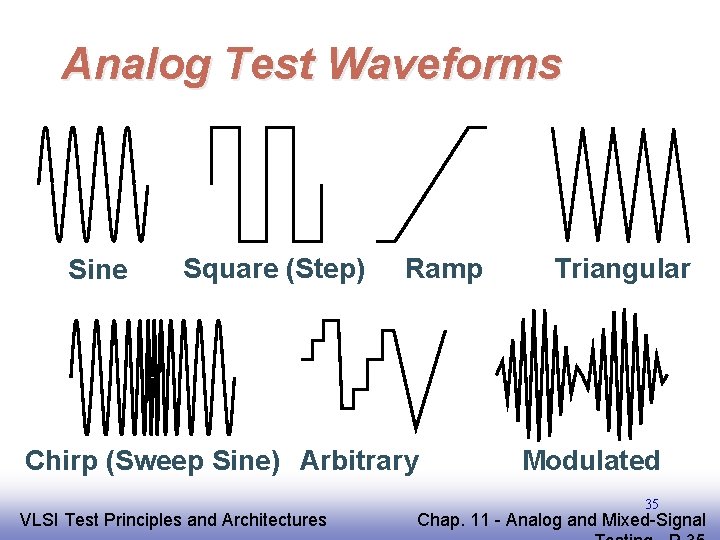

Analog Test Waveforms Sine Square (Step) Ramp Chirp (Sweep Sine) Arbitrary EE 141 VLSI Test Principles and Architectures Triangular Modulated 35 Chap. 11 - Analog and Mixed-Signal

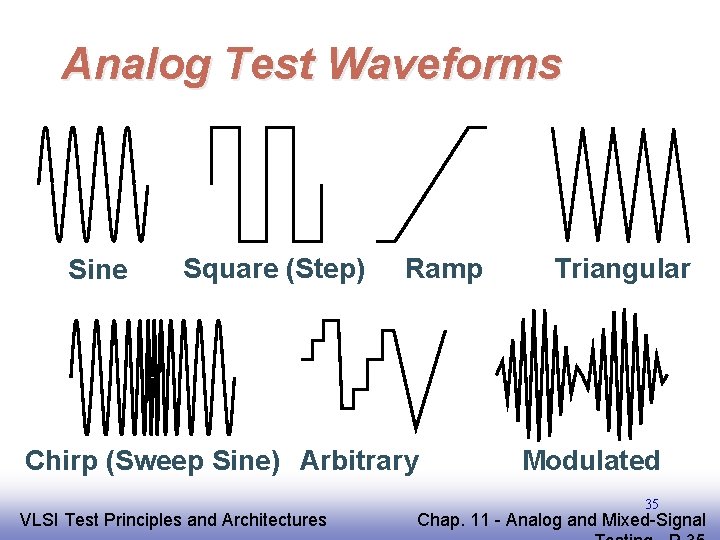

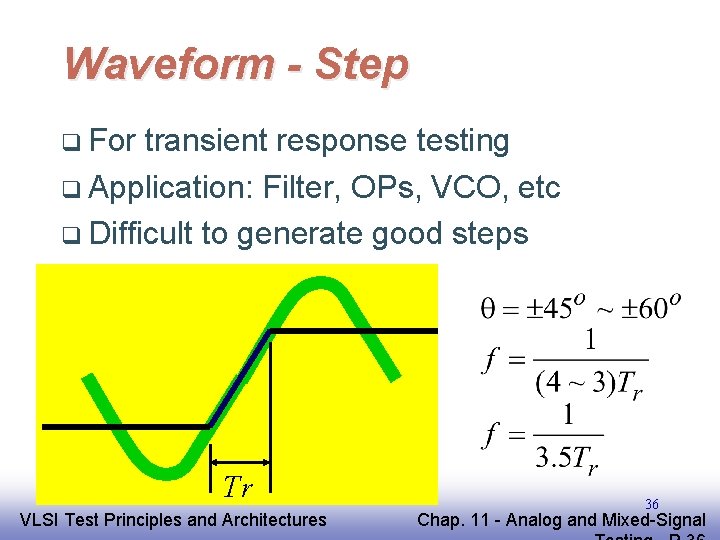

Waveform - Step q For transient response testing q Application: Filter, OPs, VCO, etc q Difficult to generate good steps Tr EE 141 VLSI Test Principles and Architectures 36 Chap. 11 - Analog and Mixed-Signal

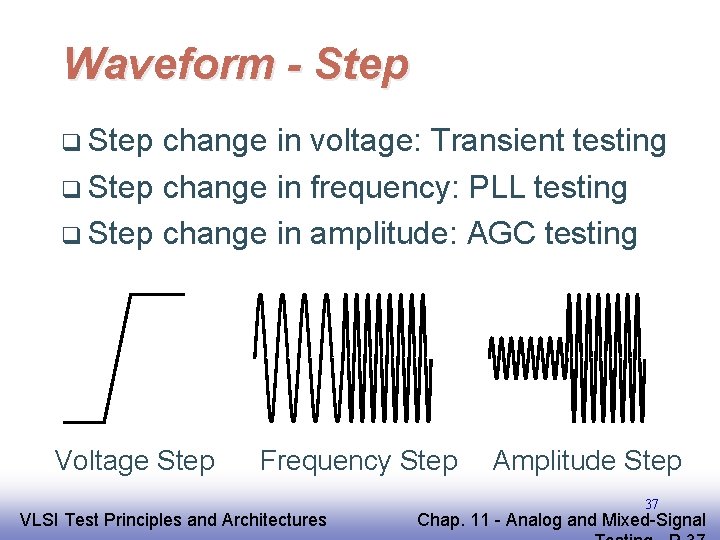

Waveform - Step q Step change in voltage: Transient testing q Step change in frequency: PLL testing q Step change in amplitude: AGC testing Voltage Step Frequency Step EE 141 VLSI Test Principles and Architectures Amplitude Step 37 Chap. 11 - Analog and Mixed-Signal

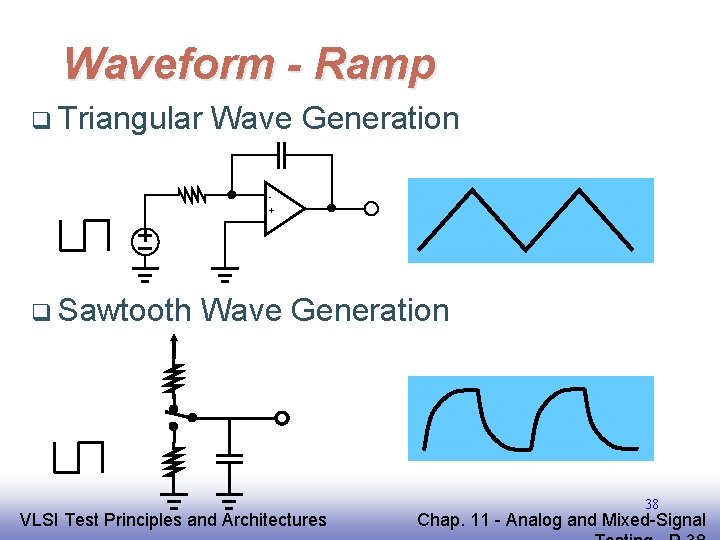

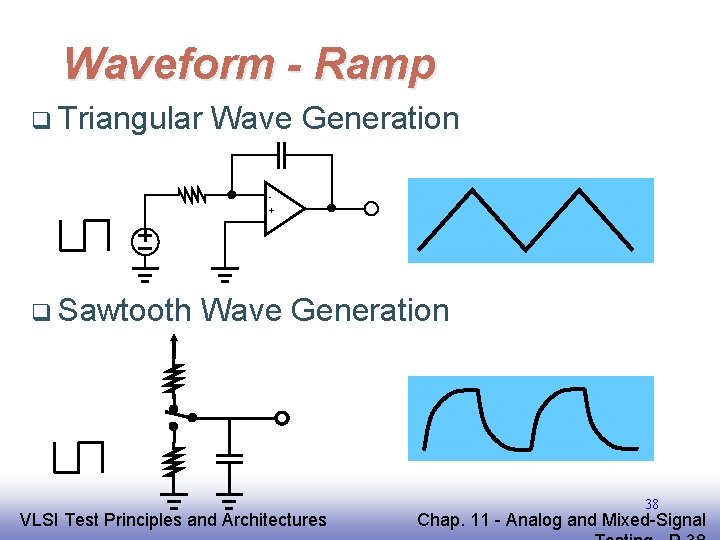

Waveform - Ramp q Triangular Wave Generation + q Sawtooth Wave Generation EE 141 VLSI Test Principles and Architectures 38 Chap. 11 - Analog and Mixed-Signal

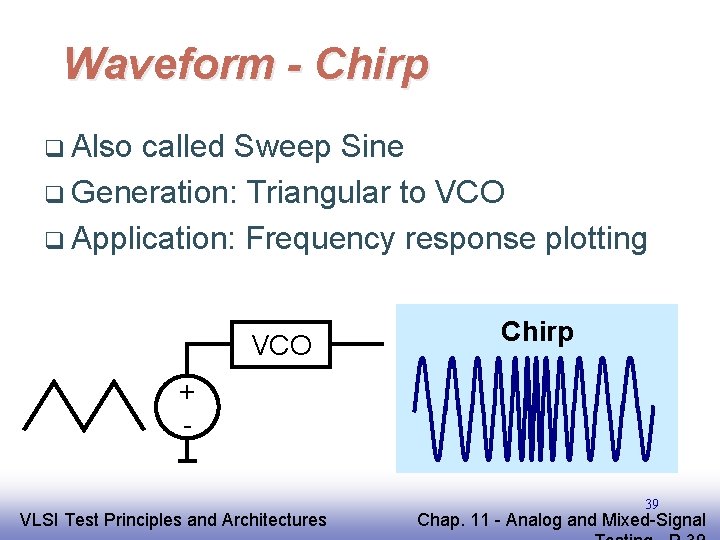

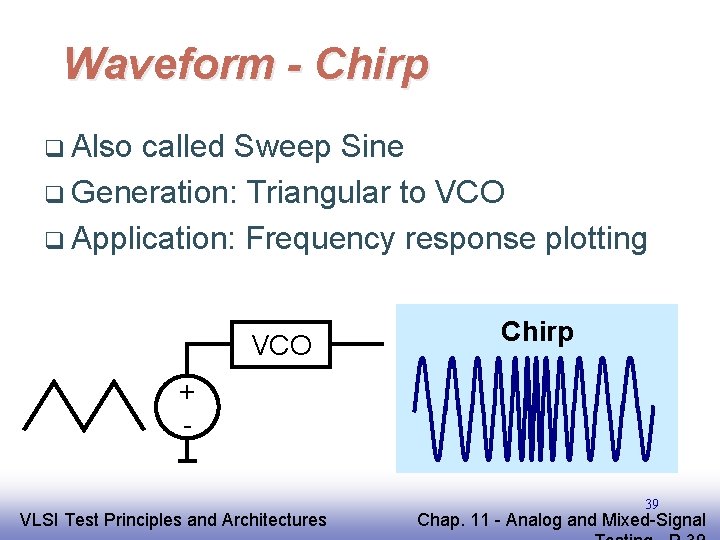

Waveform - Chirp q Also called Sweep Sine q Generation: Triangular to VCO q Application: Frequency response plotting VCO Chirp + EE 141 VLSI Test Principles and Architectures 39 Chap. 11 - Analog and Mixed-Signal

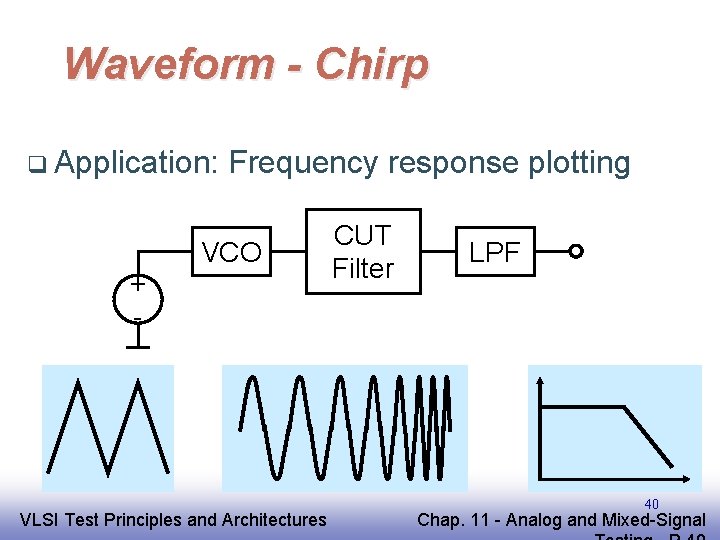

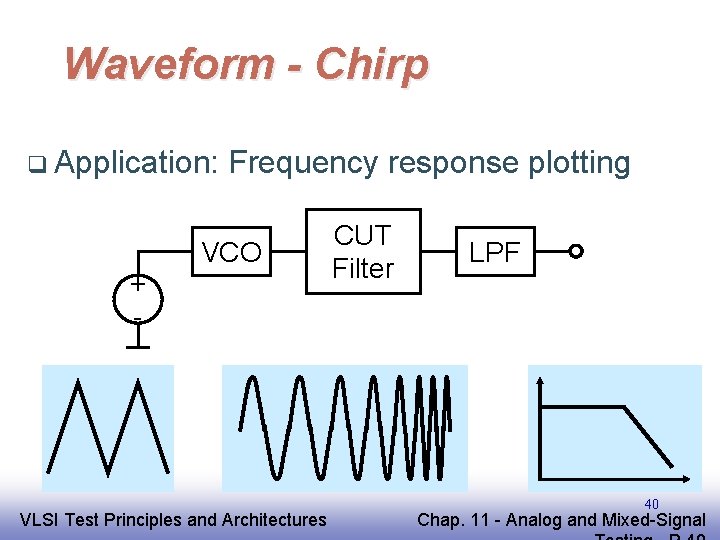

Waveform - Chirp q Application: + - Frequency response plotting VCO EE 141 VLSI Test Principles and Architectures CUT Filter LPF 40 Chap. 11 - Analog and Mixed-Signal

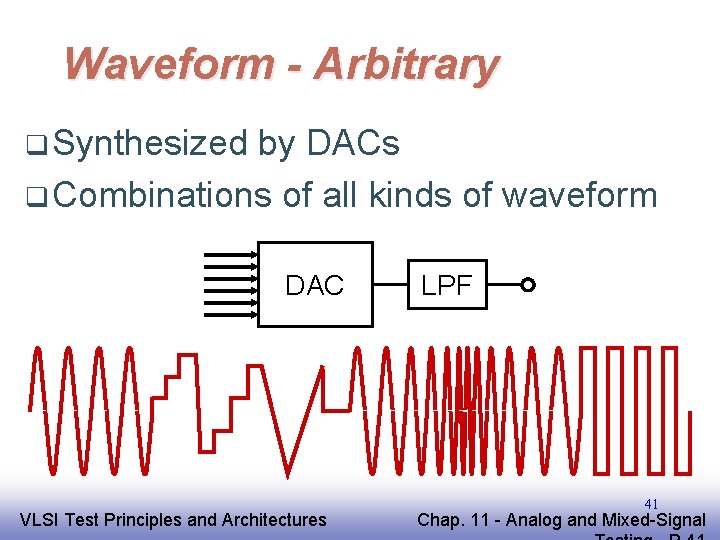

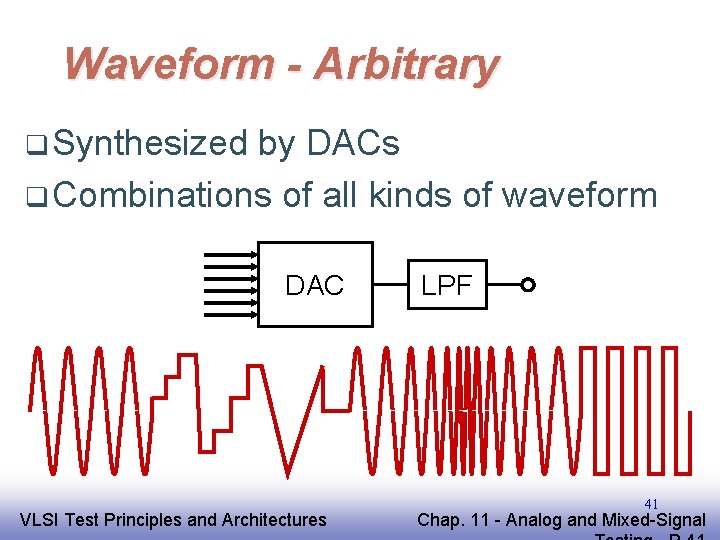

Waveform - Arbitrary q Synthesized by DACs q Combinations of all kinds of waveform DAC EE 141 VLSI Test Principles and Architectures LPF 41 Chap. 11 - Analog and Mixed-Signal

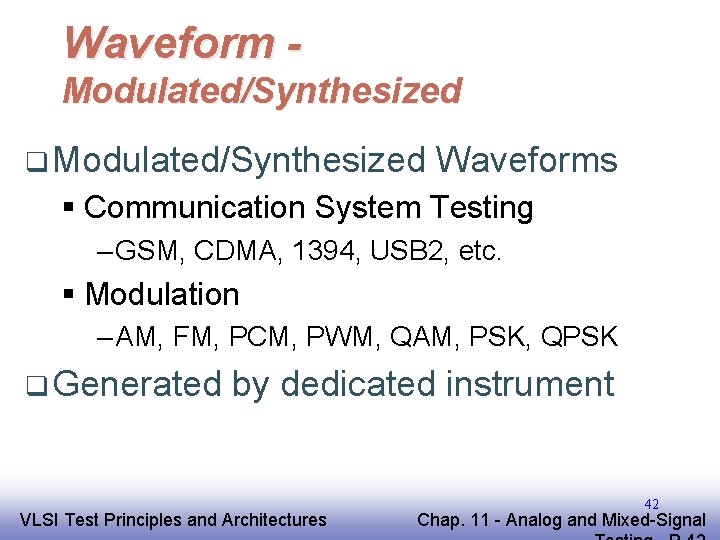

Waveform Modulated/Synthesized q Modulated/Synthesized Waveforms § Communication System Testing – GSM, CDMA, 1394, USB 2, etc. § Modulation – AM, FM, PCM, PWM, QAM, PSK, QPSK q Generated by dedicated instrument EE 141 VLSI Test Principles and Architectures 42 Chap. 11 - Analog and Mixed-Signal

11. 2 Analog Circuit Testing q Analog Test Approaches q Analog Test Waveforms q DC q AC Parametric Testing EE 141 VLSI Test Principles and Architectures 43 Chap. 11 - Analog and Mixed-Signal

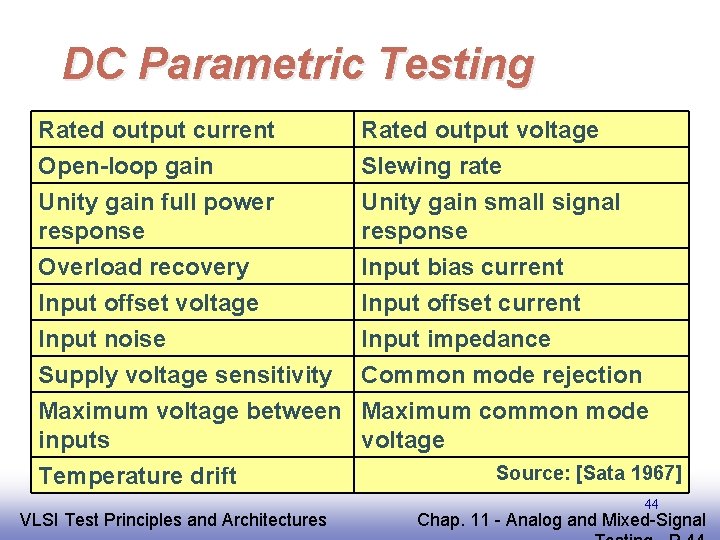

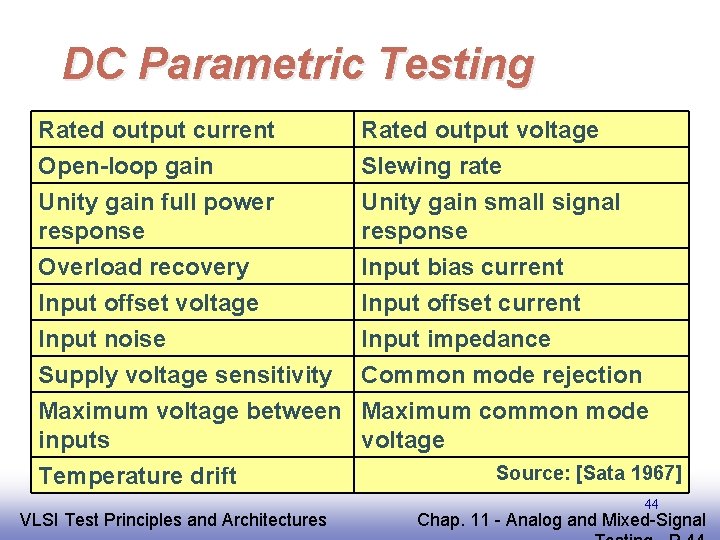

DC Parametric Testing Rated output current Open-loop gain Unity gain full power response Rated output voltage Slewing rate Unity gain small signal response Overload recovery Input bias current Input offset voltage Input noise Supply voltage sensitivity Maximum voltage between inputs Input offset current Input impedance Common mode rejection Maximum common mode voltage Temperature drift EE 141 VLSI Test Principles and Architectures Source: [Sata 1967] 44 Chap. 11 - Analog and Mixed-Signal

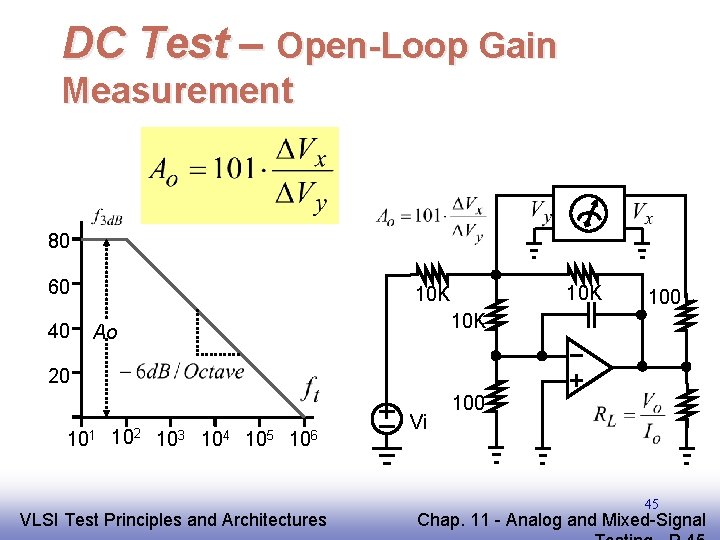

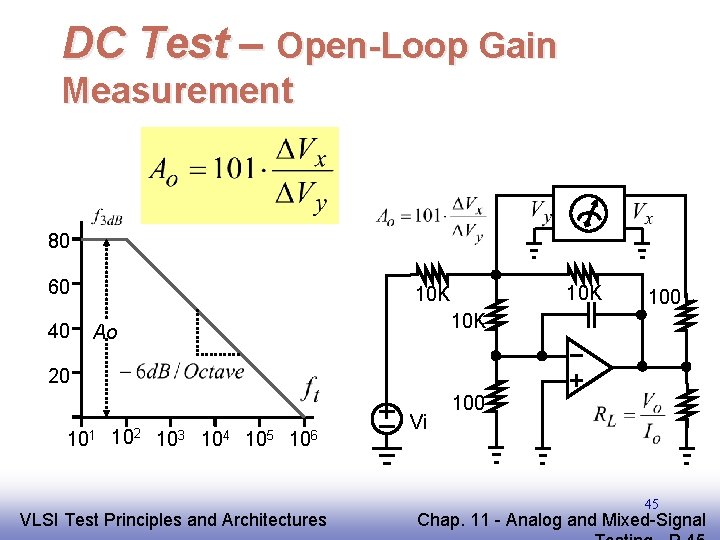

DC Test – Open-Loop Gain Measurement 80 60 40 10 K 100 10 K Ao 20 101 102 103 104 105 106 EE 141 VLSI Test Principles and Architectures Vi 100 45 Chap. 11 - Analog and Mixed-Signal

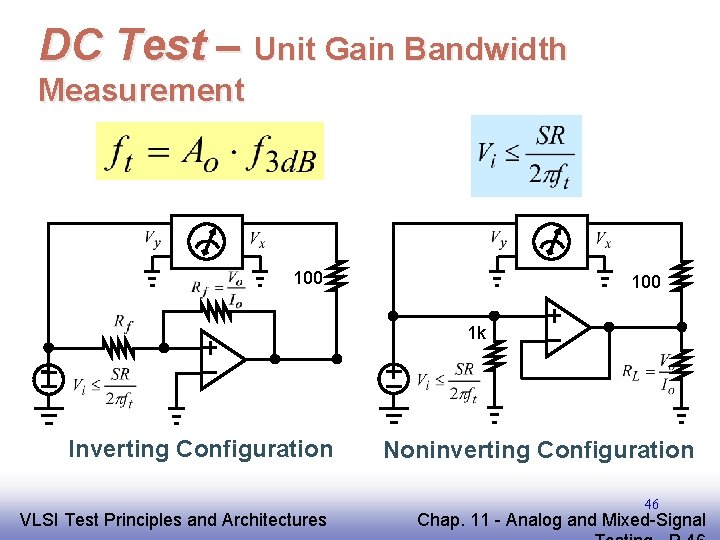

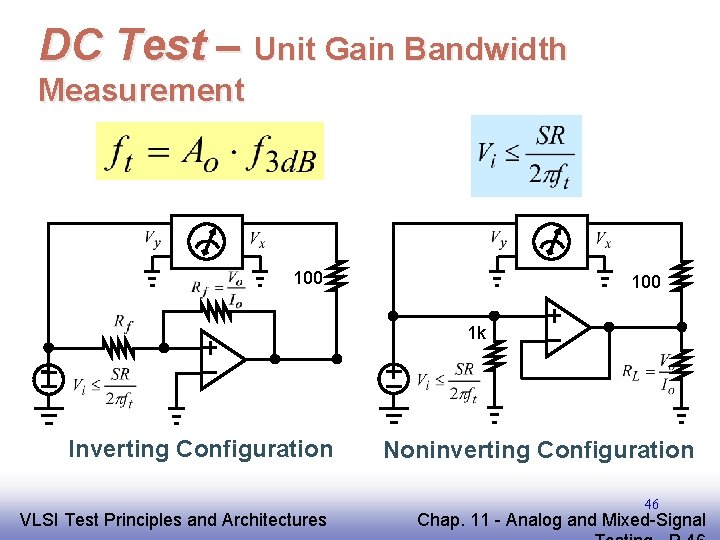

DC Test – Unit Gain Bandwidth Measurement 100 1 k Inverting Configuration EE 141 VLSI Test Principles and Architectures Noninverting Configuration 46 Chap. 11 - Analog and Mixed-Signal

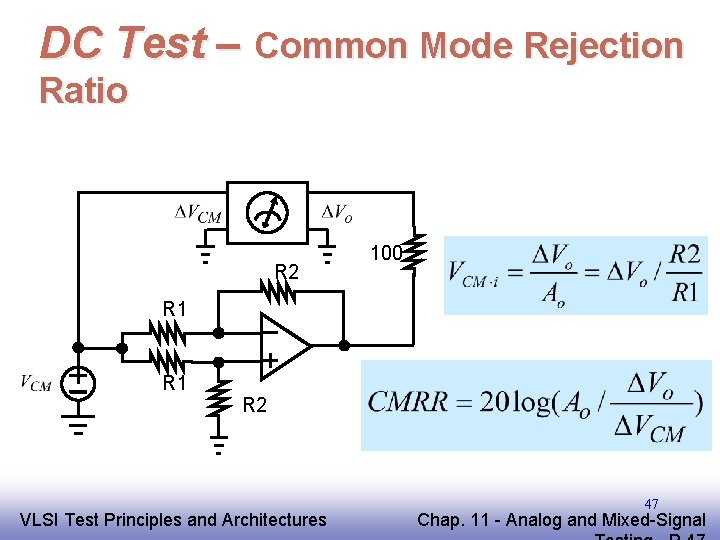

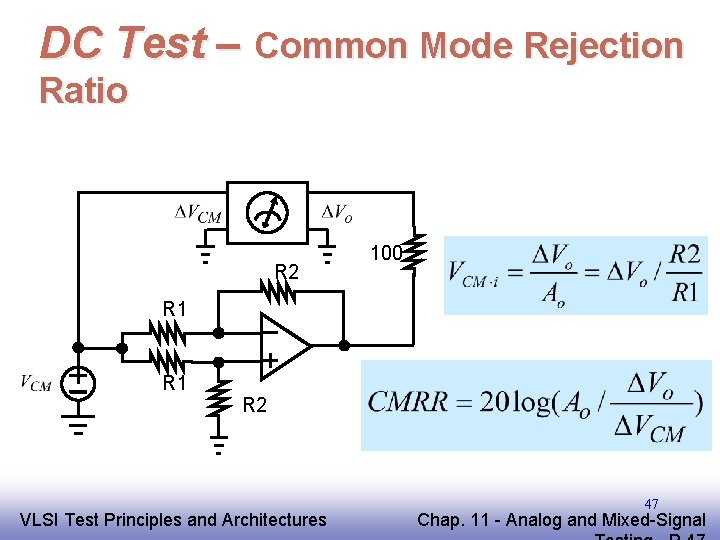

DC Test – Common Mode Rejection Ratio R 2 100 R 1 R 2 EE 141 VLSI Test Principles and Architectures 47 Chap. 11 - Analog and Mixed-Signal

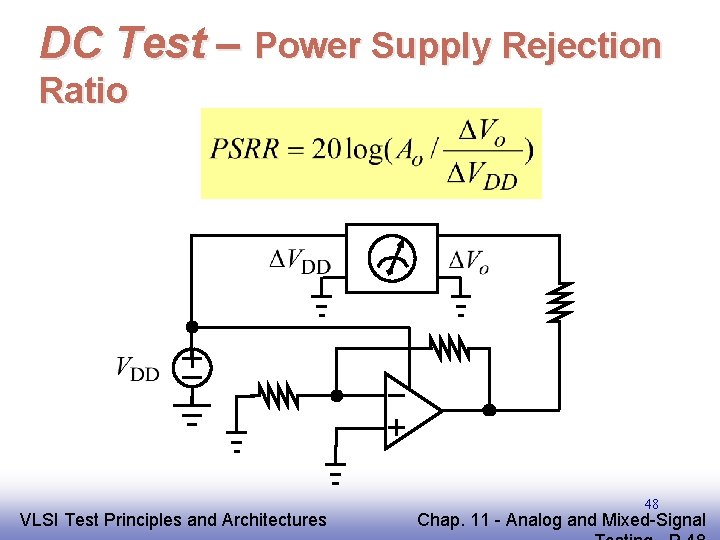

DC Test – Power Supply Rejection Ratio EE 141 VLSI Test Principles and Architectures 48 Chap. 11 - Analog and Mixed-Signal

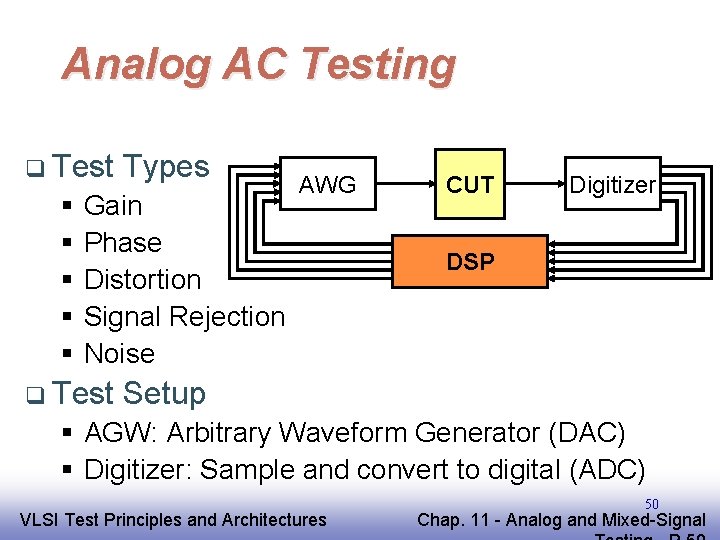

11. 2 Analog Circuit Testing q Analog Test Approaches q Analog Test Waveforms q DC Parametric Testing q AC Parametric Testing EE 141 VLSI Test Principles and Architectures 49 Chap. 11 - Analog and Mixed-Signal

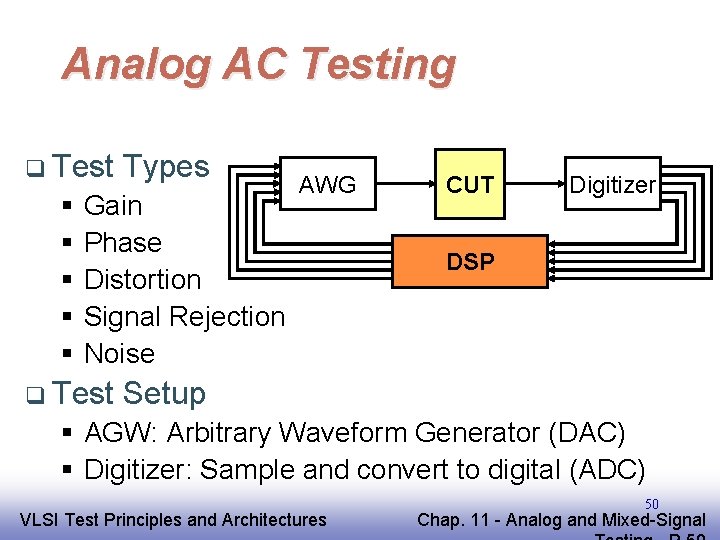

Analog AC Testing q Test § § § Types Gain Phase Distortion Signal Rejection Noise q Test AWG CUT Digitizer DSP Setup § AGW: Arbitrary Waveform Generator (DAC) § Digitizer: Sample and convert to digital (ADC) EE 141 VLSI Test Principles and Architectures 50 Chap. 11 - Analog and Mixed-Signal

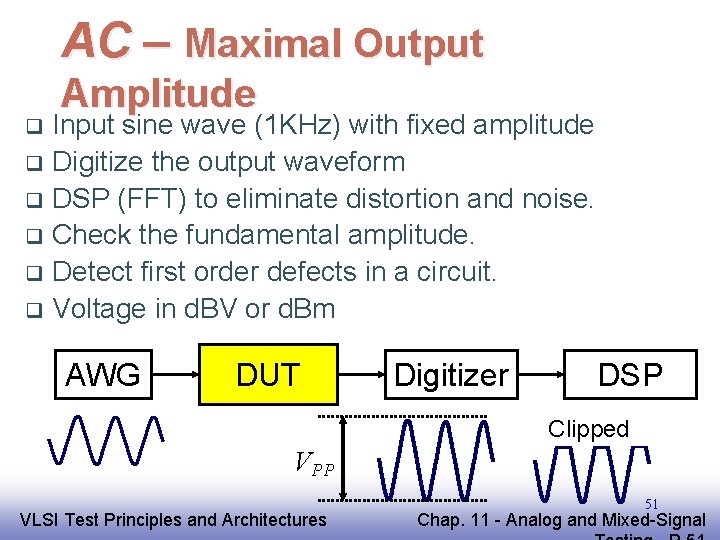

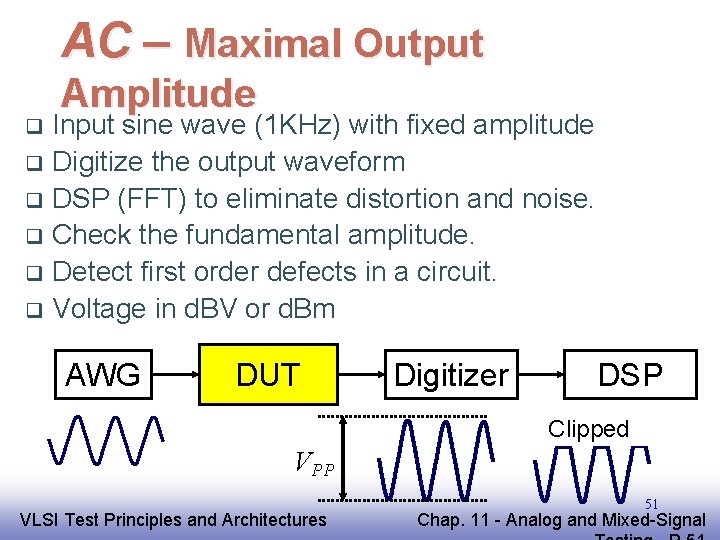

AC – Maximal Output Amplitude Input sine wave (1 KHz) with fixed amplitude q Digitize the output waveform q DSP (FFT) to eliminate distortion and noise. q Check the fundamental amplitude. q Detect first order defects in a circuit. q Voltage in d. BV or d. Bm q AWG DUT Digitizer DSP Clipped VPP EE 141 VLSI Test Principles and Architectures 51 Chap. 11 - Analog and Mixed-Signal

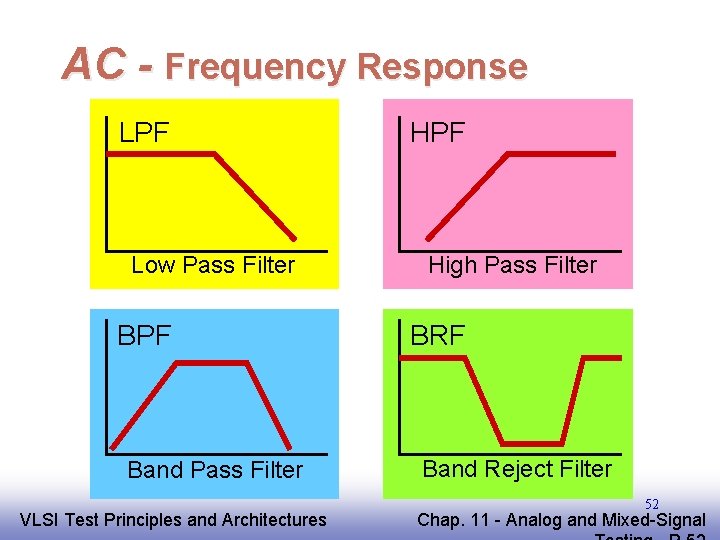

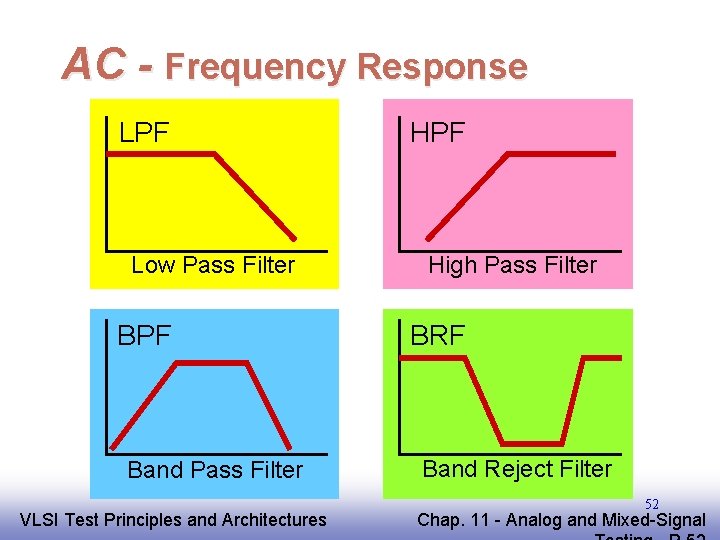

AC - Frequency Response LPF Low Pass Filter BPF Band Pass Filter EE 141 VLSI Test Principles and Architectures HPF High Pass Filter BRF Band Reject Filter 52 Chap. 11 - Analog and Mixed-Signal

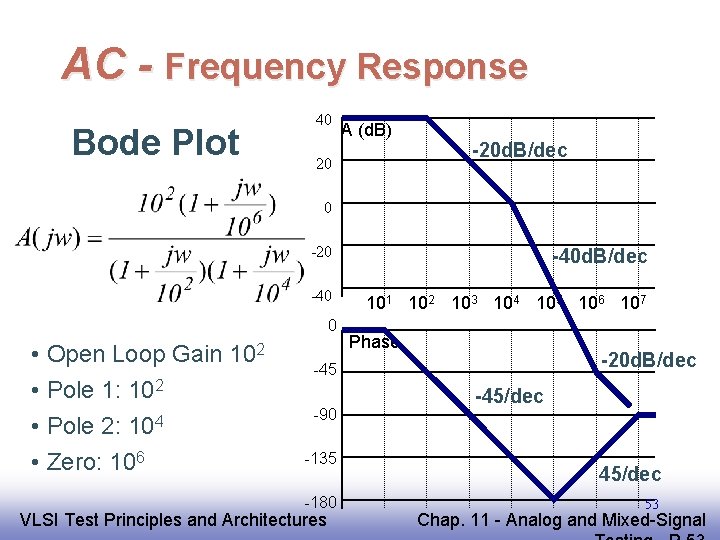

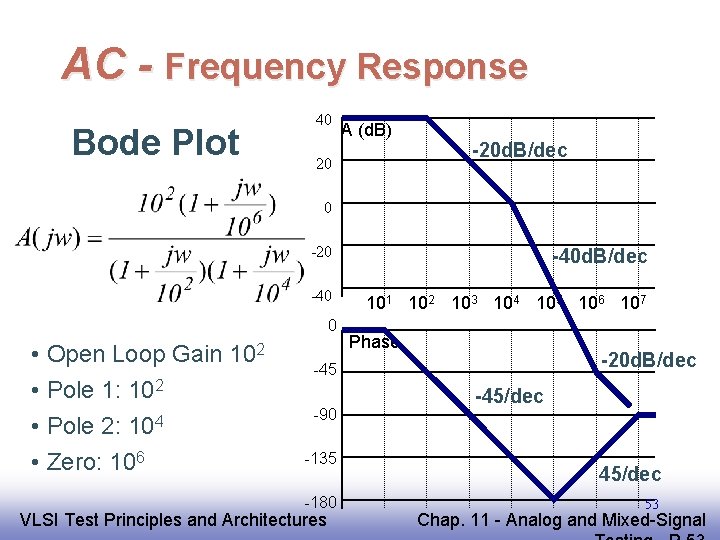

AC - Frequency Response Bode Plot 40 A (d. B) 20 -20 d. B/dec 0 -20 -40 d. B/dec -40 101 102 103 104 105 106 107 0 • Open Loop Gain • Pole 1: 102 • Pole 2: 104 • Zero: 106 102 Phase -20 d. B/dec -45 -90 -135 -180 EE 141 VLSI Test Principles and Architectures -45/dec 53 Chap. 11 - Analog and Mixed-Signal

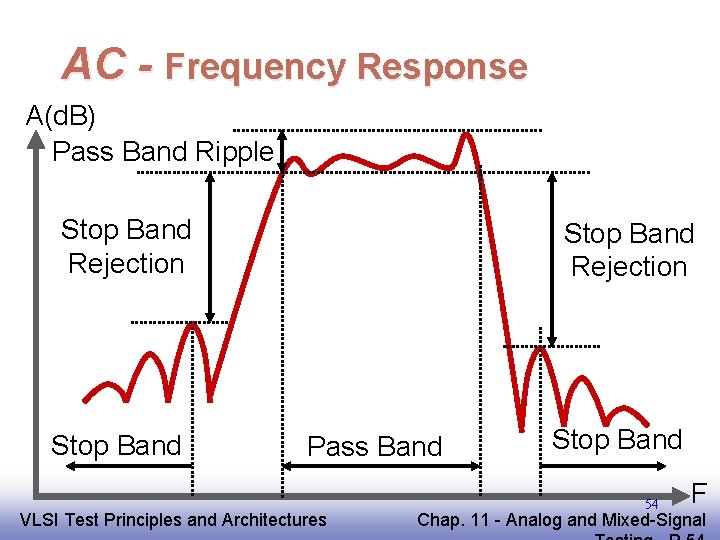

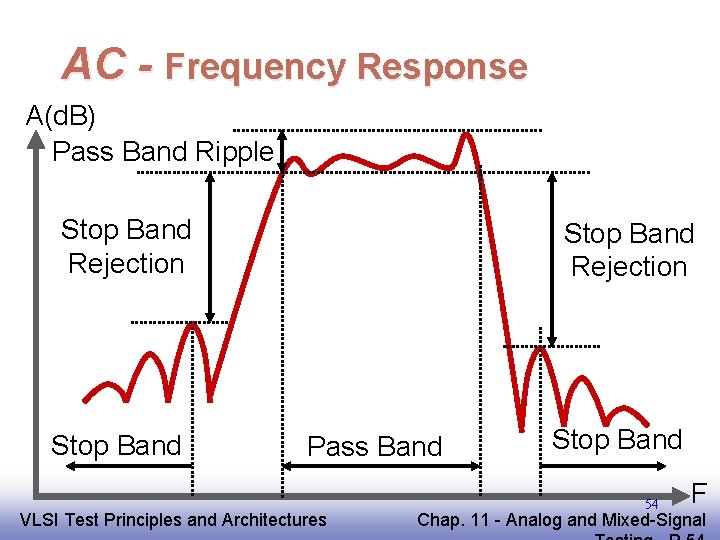

AC - Frequency Response A(d. B) Pass Band Ripple Stop Band Rejection Pass Band EE 141 VLSI Test Principles and Architectures Stop Band 54 F Chap. 11 - Analog and Mixed-Signal

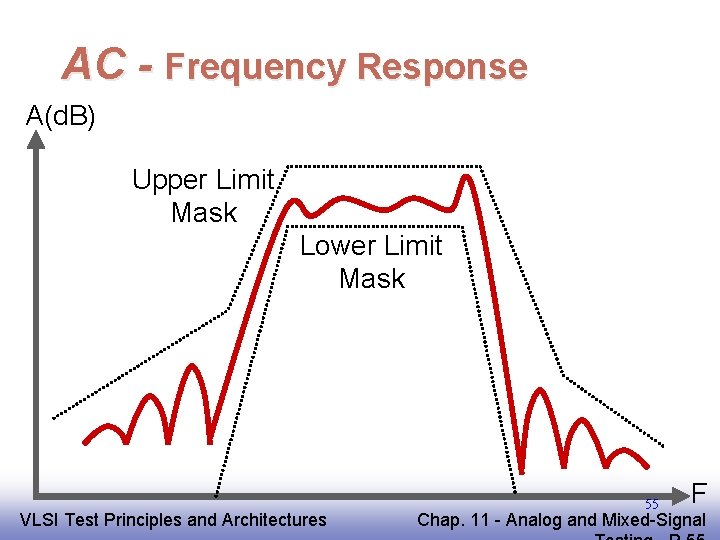

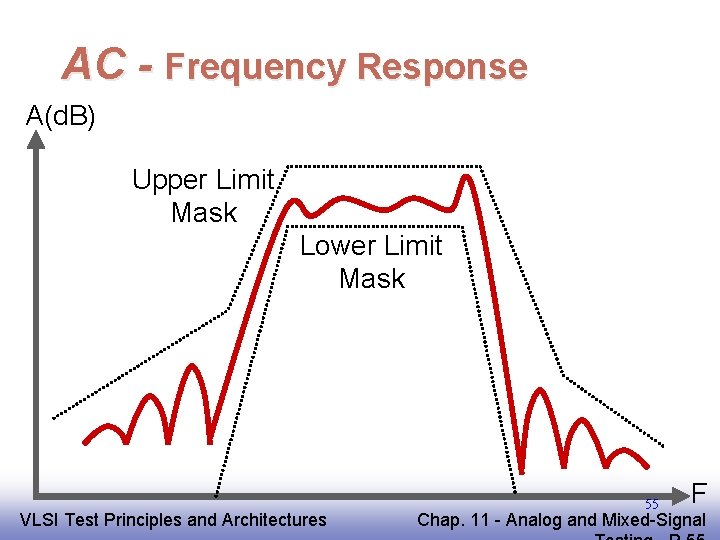

AC - Frequency Response A(d. B) Upper Limit Mask Lower Limit Mask EE 141 VLSI Test Principles and Architectures 55 F Chap. 11 - Analog and Mixed-Signal

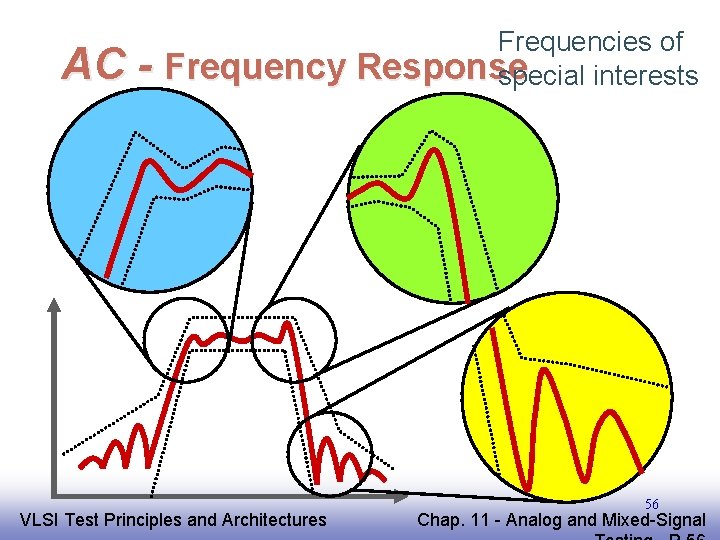

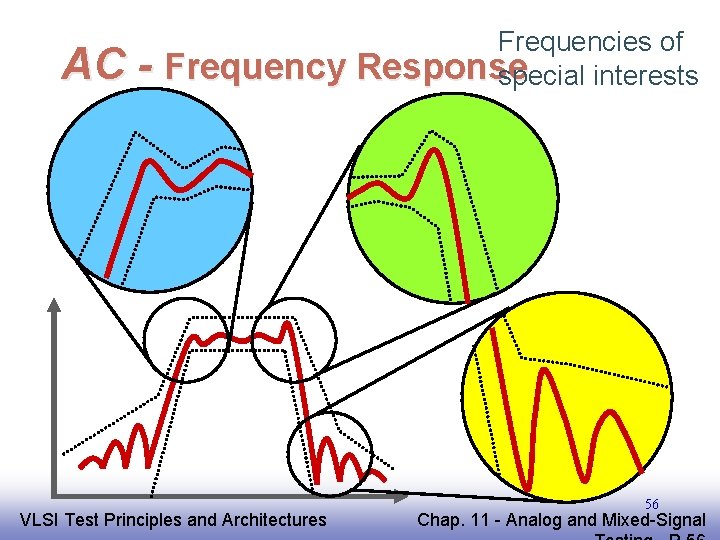

AC - Frequency EE 141 VLSI Test Principles and Architectures Frequencies of Response special interests 56 Chap. 11 - Analog and Mixed-Signal

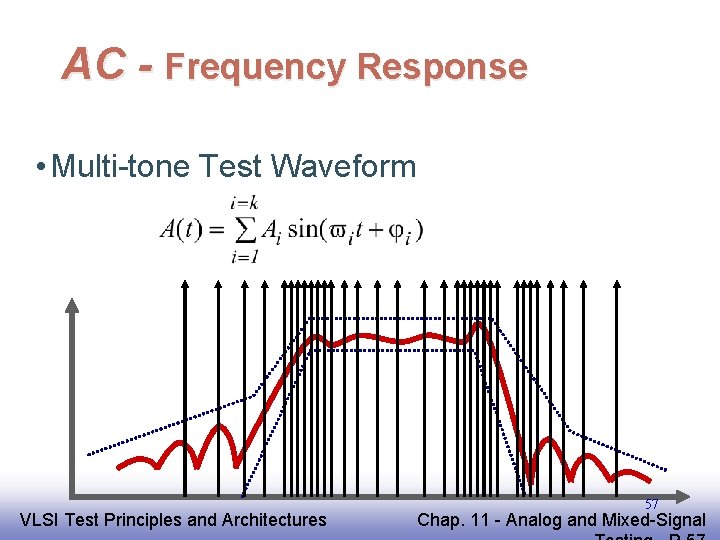

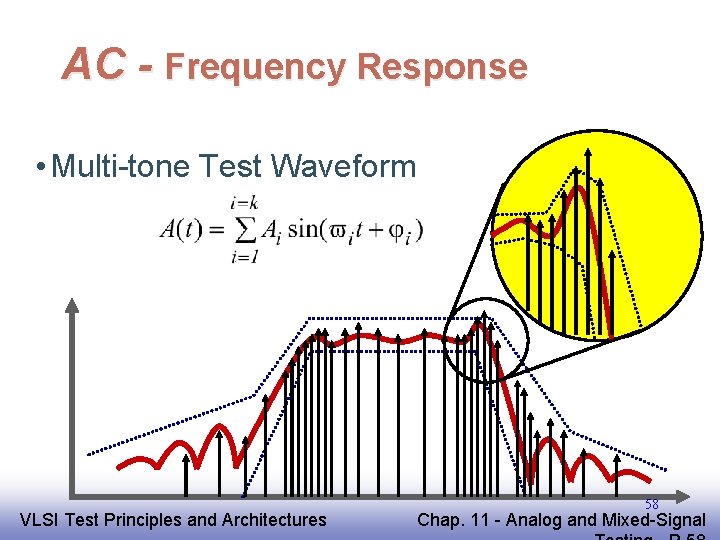

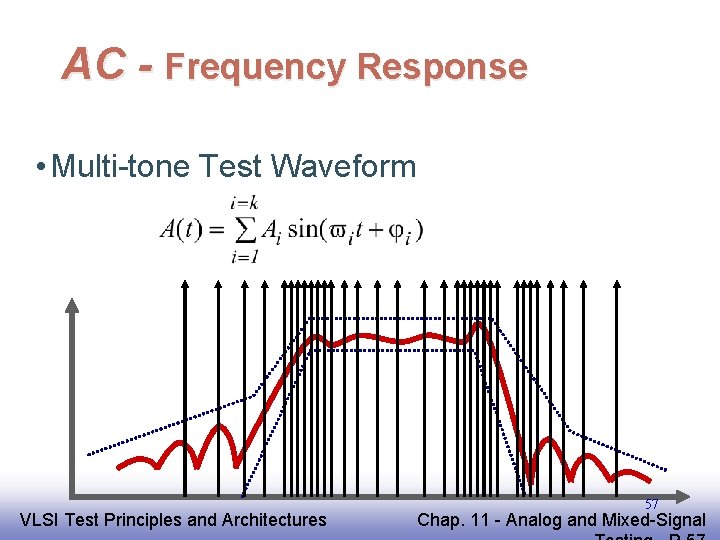

AC - Frequency Response • Multi-tone Test Waveform EE 141 VLSI Test Principles and Architectures 57 Chap. 11 - Analog and Mixed-Signal

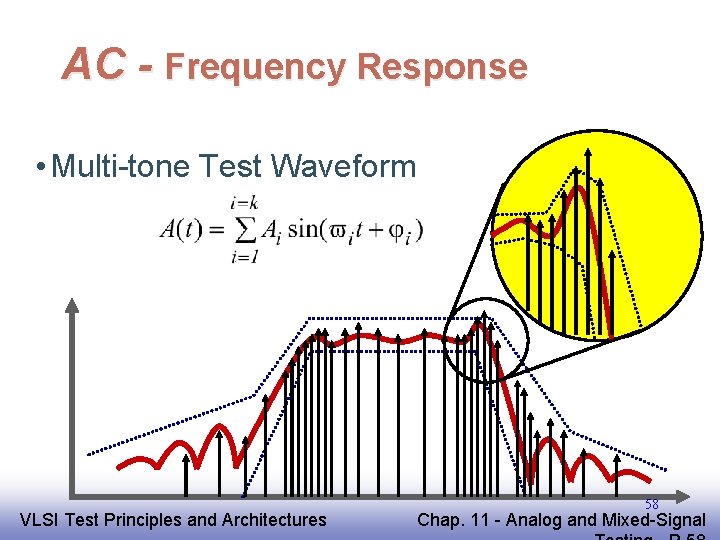

AC - Frequency Response • Multi-tone Test Waveform EE 141 VLSI Test Principles and Architectures 58 Chap. 11 - Analog and Mixed-Signal

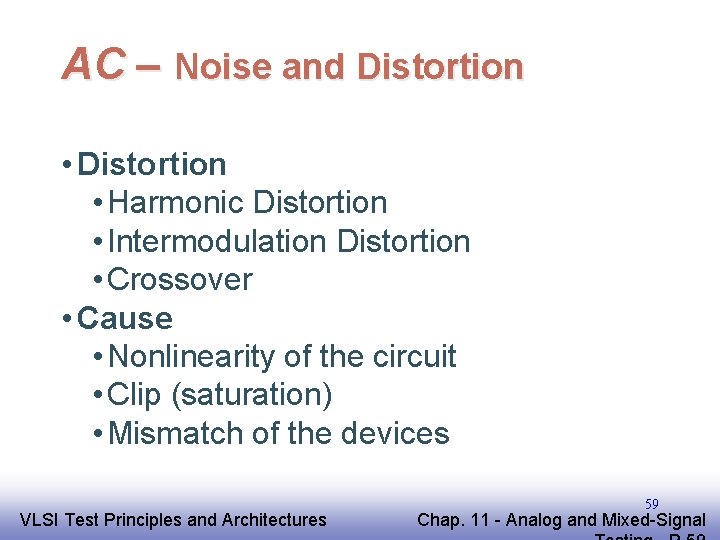

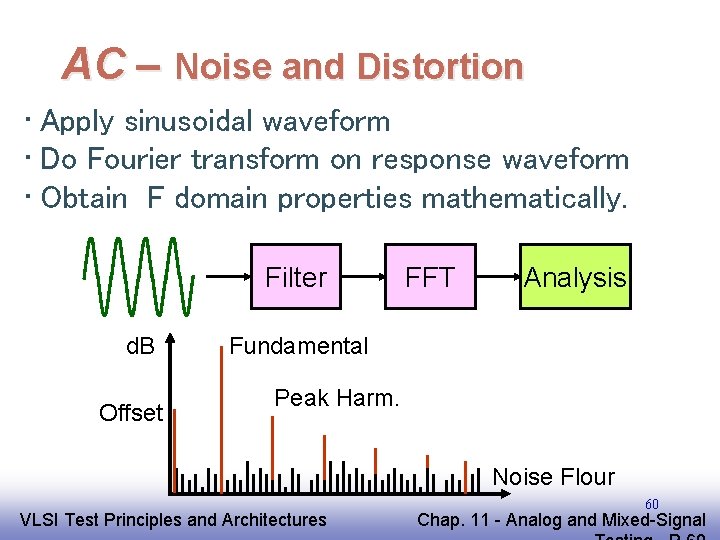

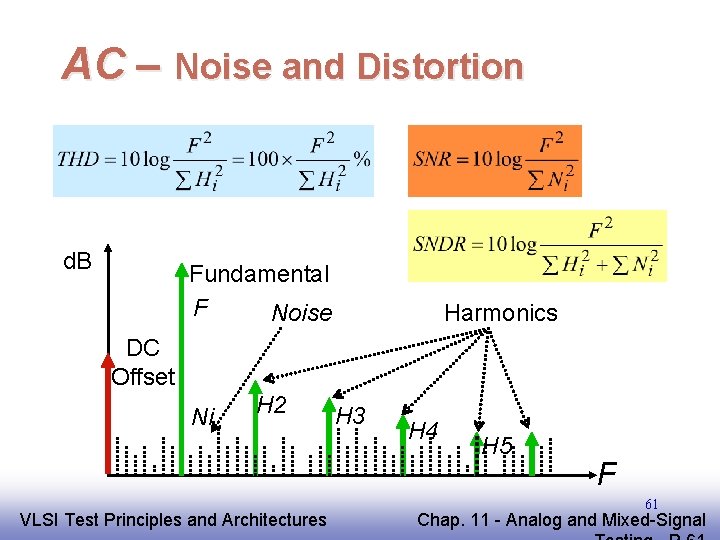

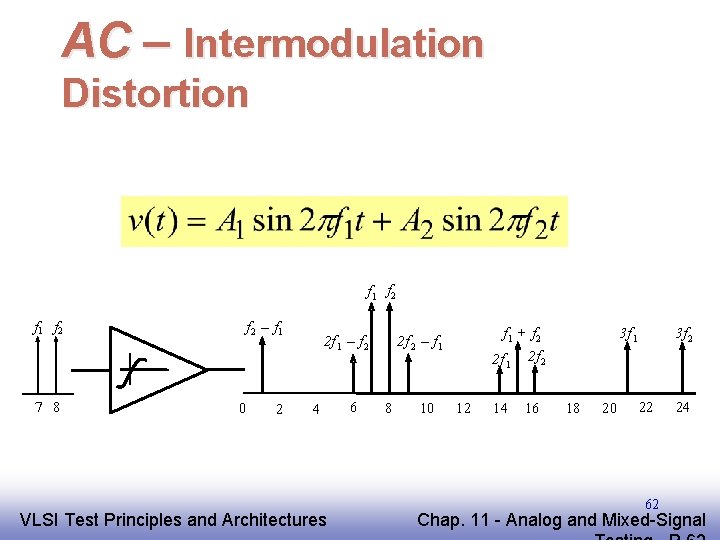

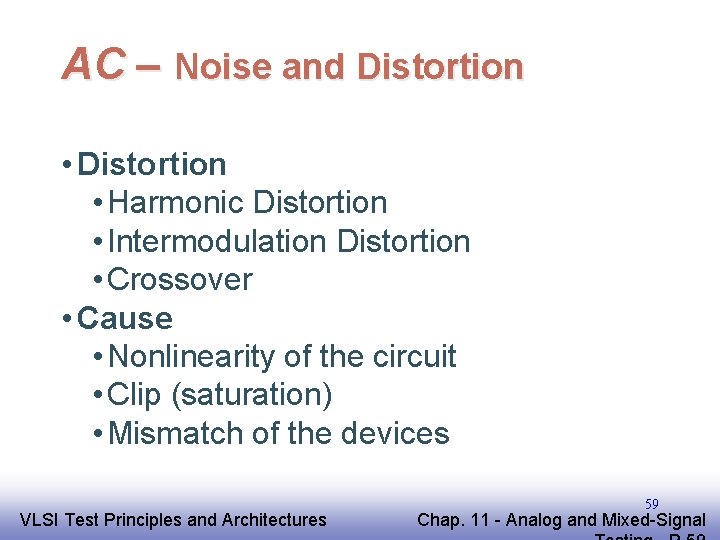

AC – Noise and Distortion • Harmonic Distortion • Intermodulation Distortion • Crossover • Cause • Nonlinearity of the circuit • Clip (saturation) • Mismatch of the devices EE 141 VLSI Test Principles and Architectures 59 Chap. 11 - Analog and Mixed-Signal

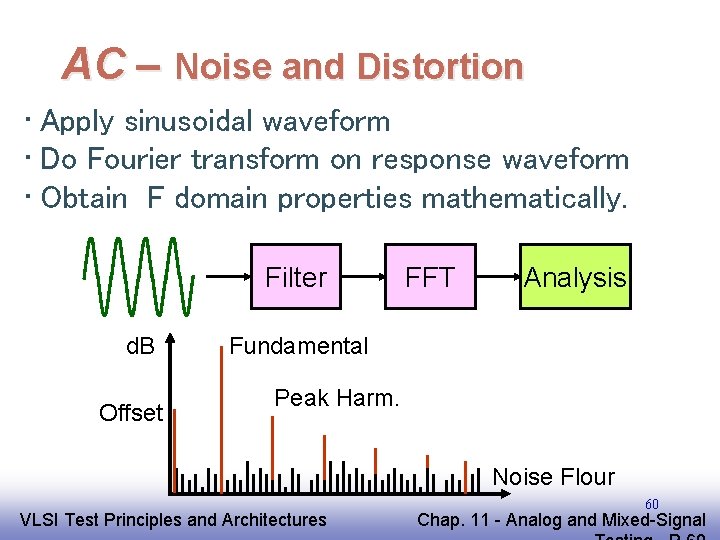

AC – Noise and Distortion • Apply sinusoidal waveform • Do Fourier transform on response waveform • Obtain F domain properties mathematically. Filter d. B Offset FFT Analysis Fundamental Peak Harm. Noise Flour EE 141 VLSI Test Principles and Architectures 60 Chap. 11 - Analog and Mixed-Signal

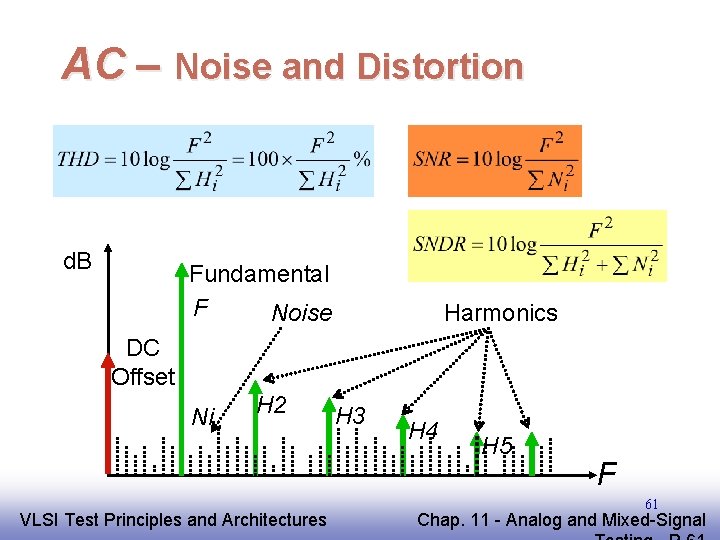

AC – Noise and Distortion d. B Fundamental F Noise Harmonics DC Offset Ni H 2 EE 141 VLSI Test Principles and Architectures H 3 H 4 H 5 F 61 Chap. 11 - Analog and Mixed-Signal

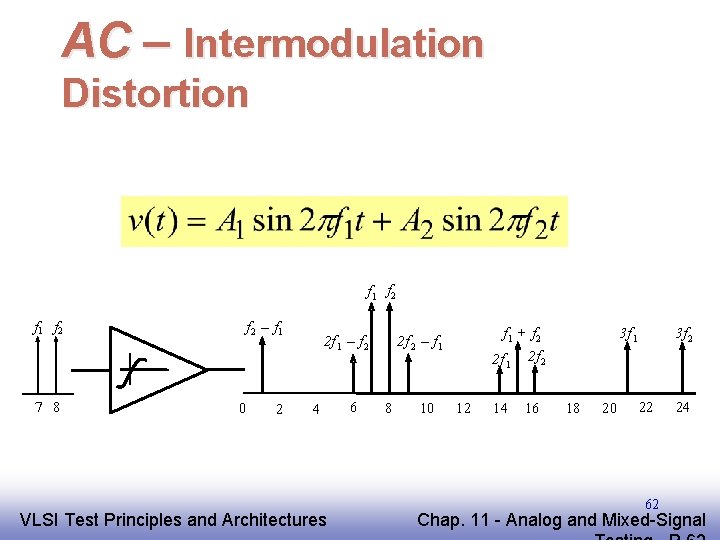

AC – Intermodulation Distortion f 1 f 2 7 8 f 2 – f 1 0 2 4 EE 141 VLSI Test Principles and Architectures 6 f 1 + f 2 2 f 2 – f 1 2 f 1 – f 2 8 10 12 2 f 1 2 f 2 14 16 3 f 1 18 20 3 f 2 22 62 24 Chap. 11 - Analog and Mixed-Signal

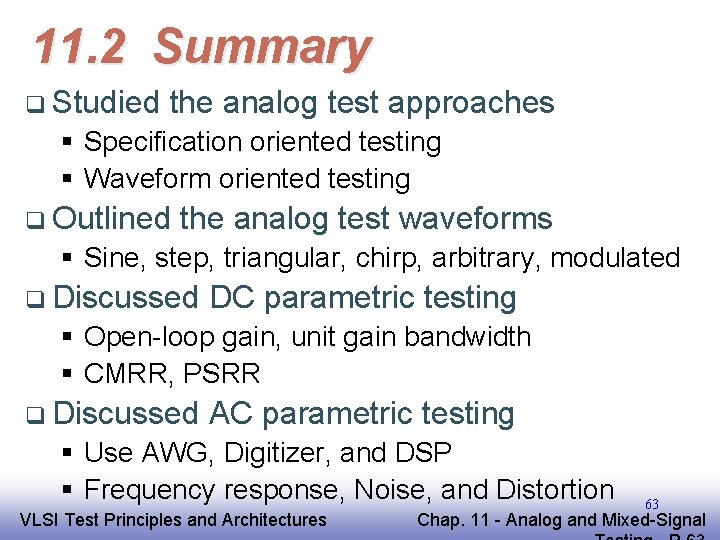

11. 2 Summary q Studied the analog test approaches § Specification oriented testing § Waveform oriented testing q Outlined the analog test waveforms § Sine, step, triangular, chirp, arbitrary, modulated q Discussed DC parametric testing § Open-loop gain, unit gain bandwidth § CMRR, PSRR q Discussed AC parametric testing § Use AWG, Digitizer, and DSP § Frequency response, Noise, and Distortion EE 141 VLSI Test Principles and Architectures 63 Chap. 11 - Analog and Mixed-Signal

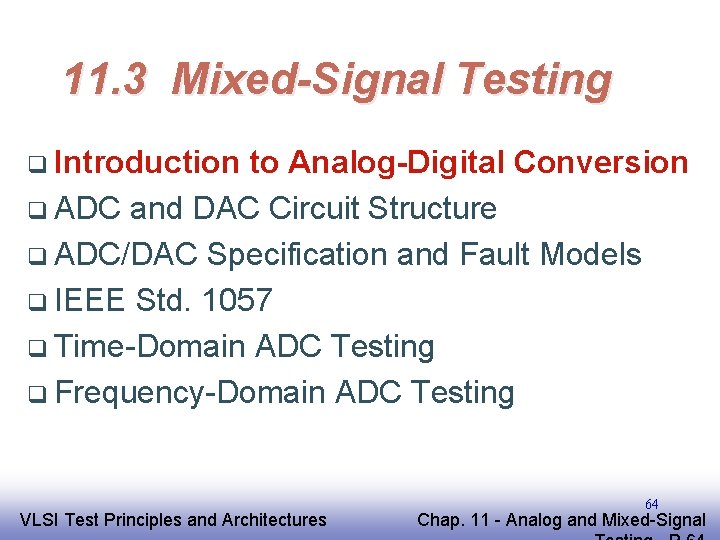

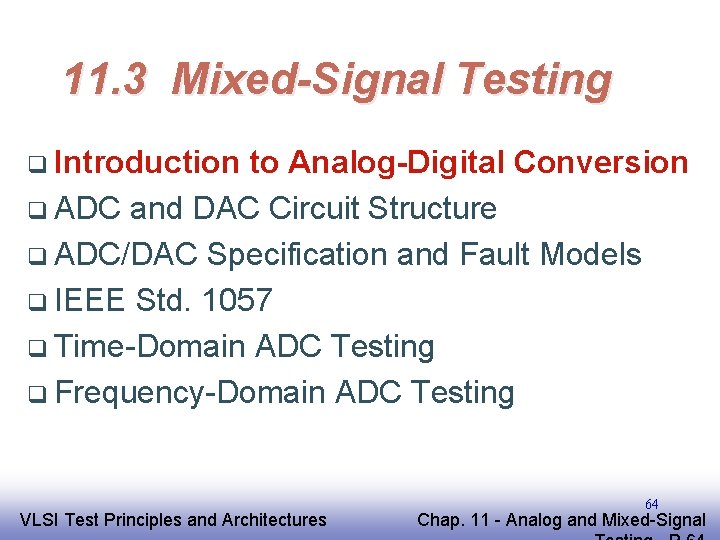

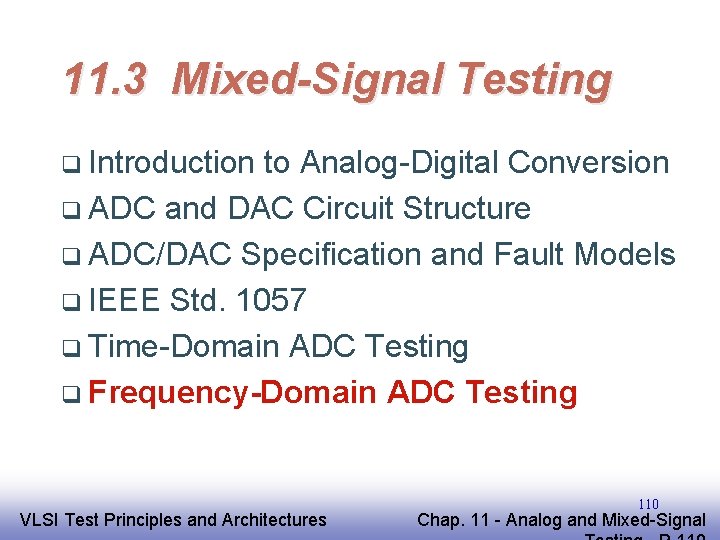

11. 3 Mixed-Signal Testing q Introduction to Analog-Digital Conversion q ADC and DAC Circuit Structure q ADC/DAC Specification and Fault Models q IEEE Std. 1057 q Time-Domain ADC Testing q Frequency-Domain ADC Testing EE 141 VLSI Test Principles and Architectures 64 Chap. 11 - Analog and Mixed-Signal

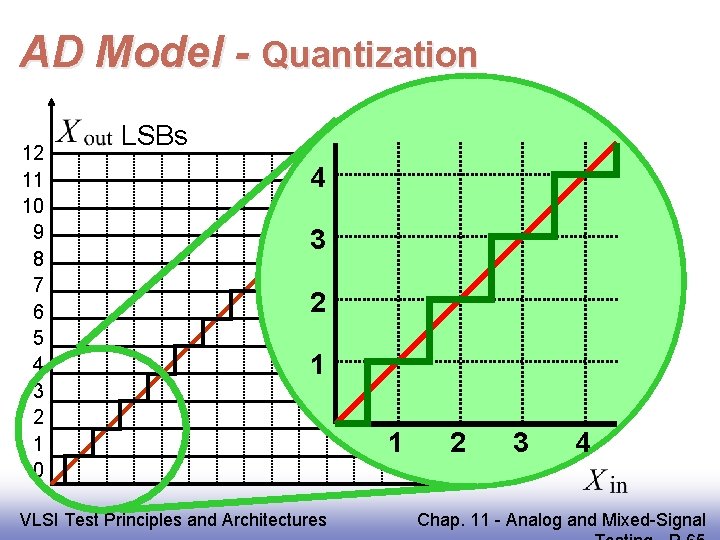

AD Model - Quantization 12 11 10 9 8 7 6 5 4 3 2 1 0 LSBs 4 3 2 1 EE 141 VLSI Test Principles and Architectures 1 2 3 4 Chap. 11 - Analog and Mixed-Signal

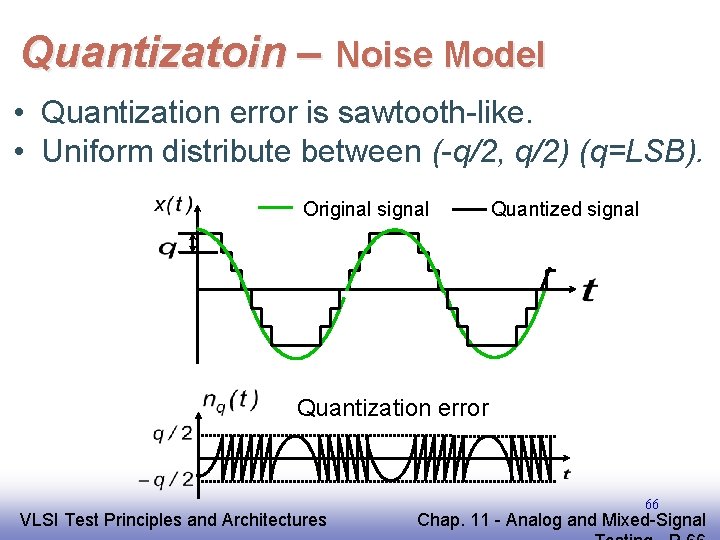

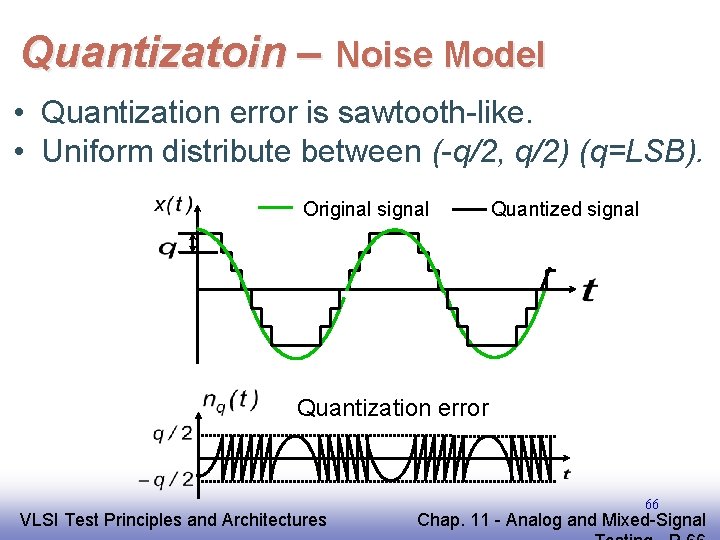

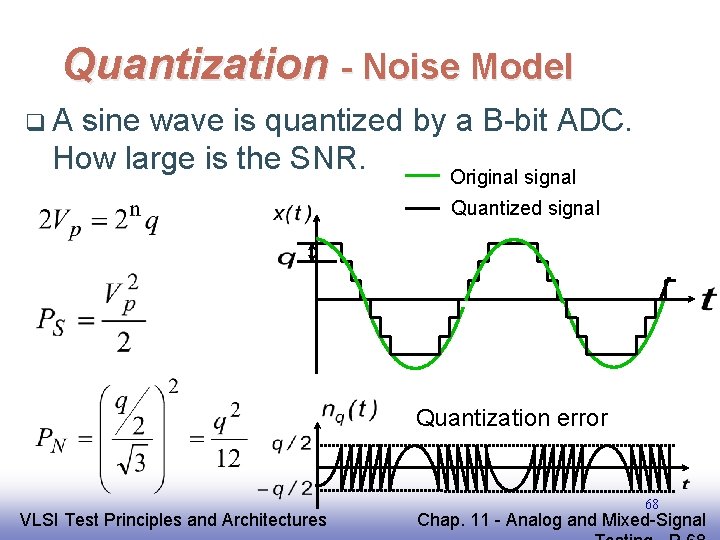

Quantizatoin – Noise Model • Quantization error is sawtooth-like. • Uniform distribute between (-q/2, q/2) (q=LSB). Original signal Quantized signal Quantization error EE 141 VLSI Test Principles and Architectures 66 Chap. 11 - Analog and Mixed-Signal

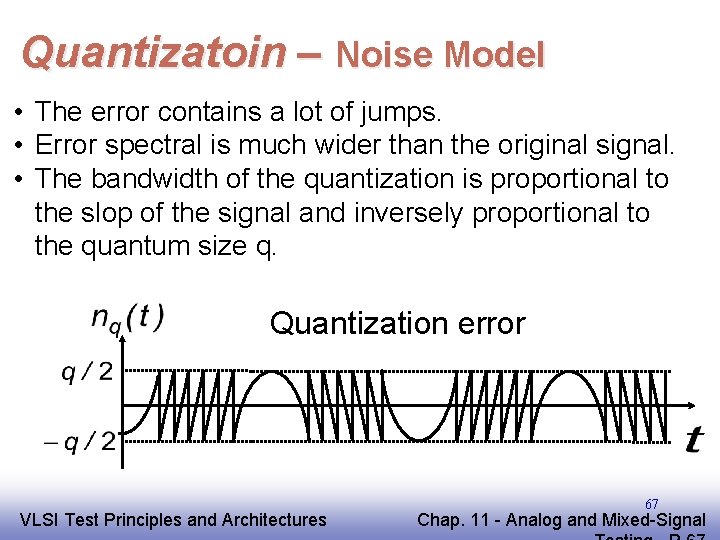

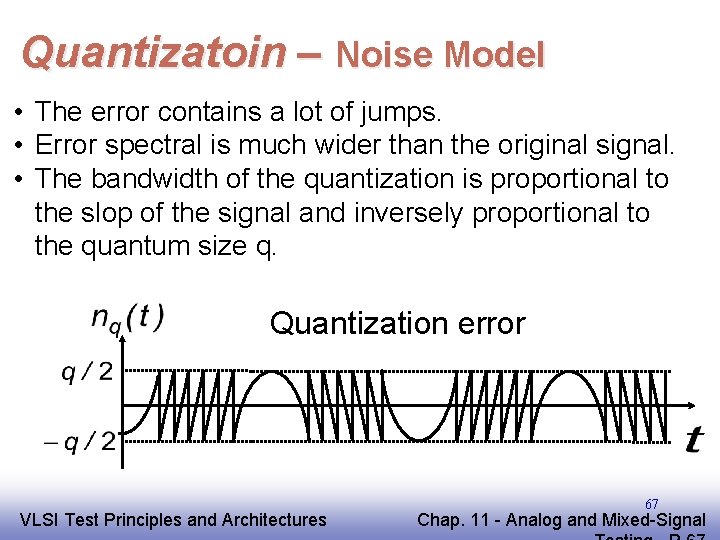

Quantizatoin – Noise Model • The error contains a lot of jumps. • Error spectral is much wider than the original signal. • The bandwidth of the quantization is proportional to the slop of the signal and inversely proportional to the quantum size q. Quantization error EE 141 VLSI Test Principles and Architectures 67 Chap. 11 - Analog and Mixed-Signal

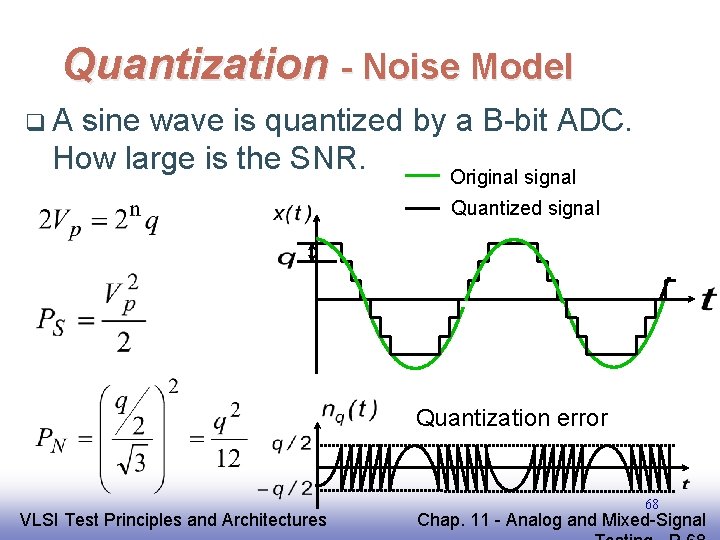

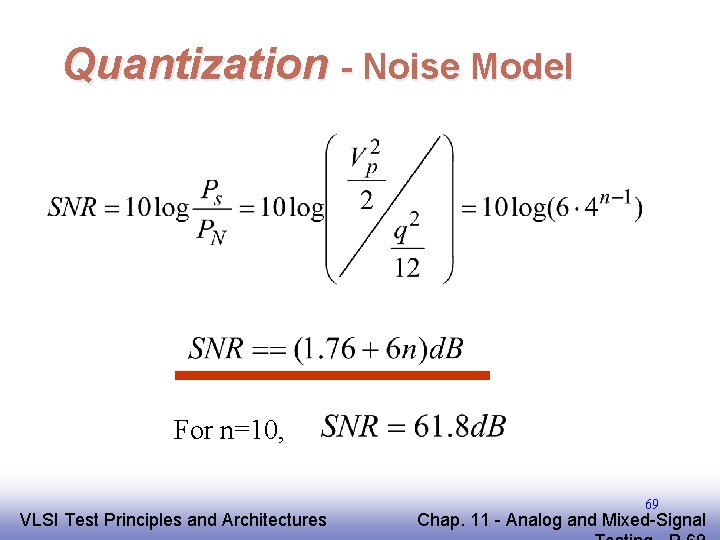

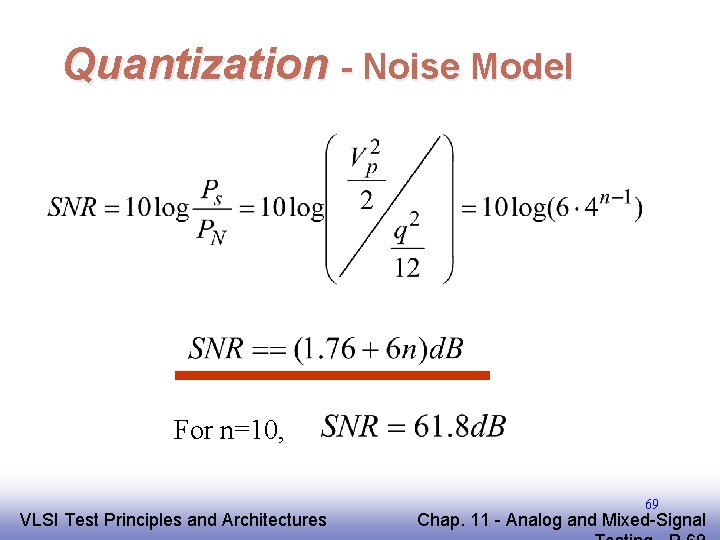

Quantization - Noise Model q. A sine wave is quantized by a B-bit ADC. How large is the SNR. Original signal Quantized signal Quantization error EE 141 VLSI Test Principles and Architectures 68 Chap. 11 - Analog and Mixed-Signal

Quantization - Noise Model For n=10, EE 141 VLSI Test Principles and Architectures 69 Chap. 11 - Analog and Mixed-Signal

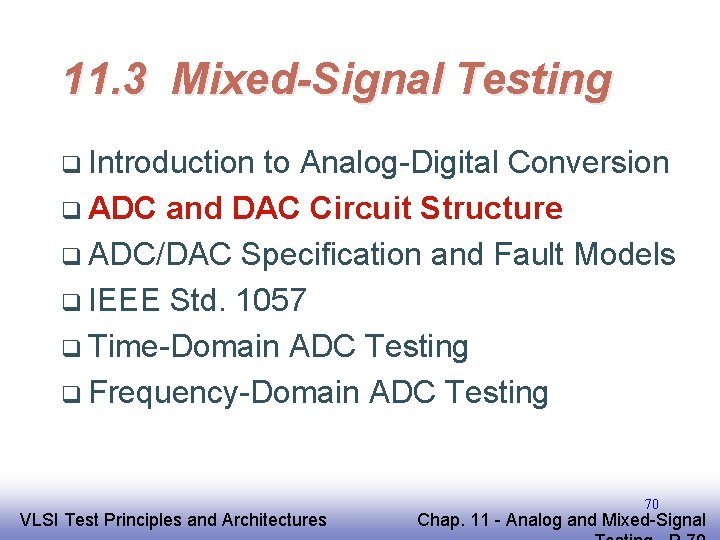

11. 3 Mixed-Signal Testing q Introduction to Analog-Digital Conversion q ADC and DAC Circuit Structure q ADC/DAC Specification and Fault Models q IEEE Std. 1057 q Time-Domain ADC Testing q Frequency-Domain ADC Testing EE 141 VLSI Test Principles and Architectures 70 Chap. 11 - Analog and Mixed-Signal

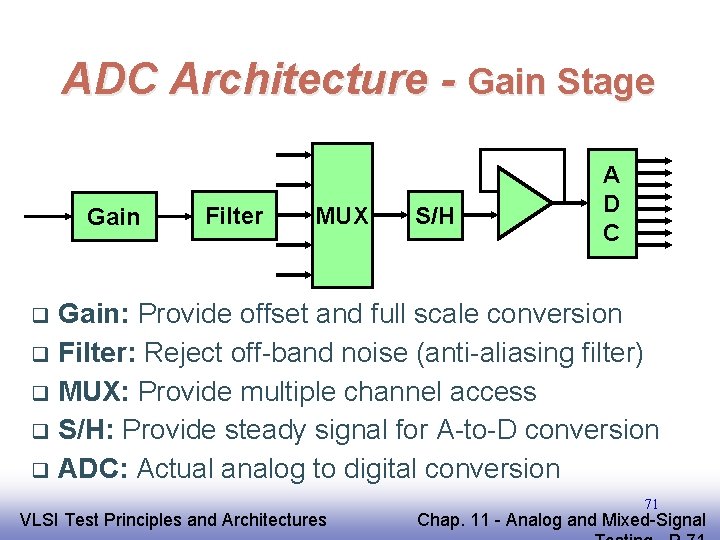

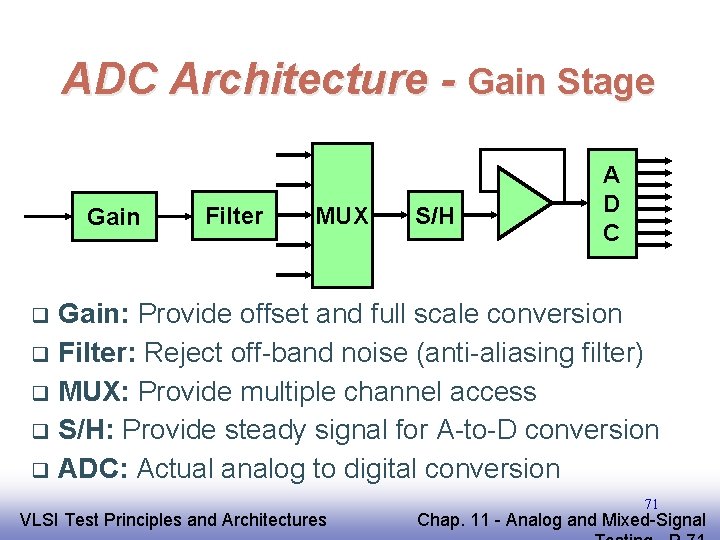

ADC Architecture - Gain Stage Gain Filter MUX S/H A D C Gain: Provide offset and full scale conversion q Filter: Reject off-band noise (anti-aliasing filter) q MUX: Provide multiple channel access q S/H: Provide steady signal for A-to-D conversion q ADC: Actual analog to digital conversion q EE 141 VLSI Test Principles and Architectures 71 Chap. 11 - Analog and Mixed-Signal

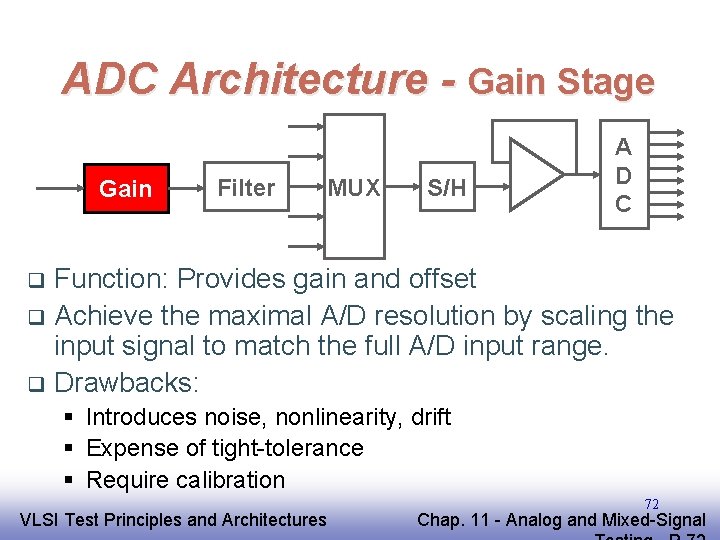

ADC Architecture - Gain Stage Gain Filter MUX S/H A D C Function: Provides gain and offset q Achieve the maximal A/D resolution by scaling the input signal to match the full A/D input range. q Drawbacks: q § Introduces noise, nonlinearity, drift § Expense of tight-tolerance § Require calibration EE 141 VLSI Test Principles and Architectures 72 Chap. 11 - Analog and Mixed-Signal

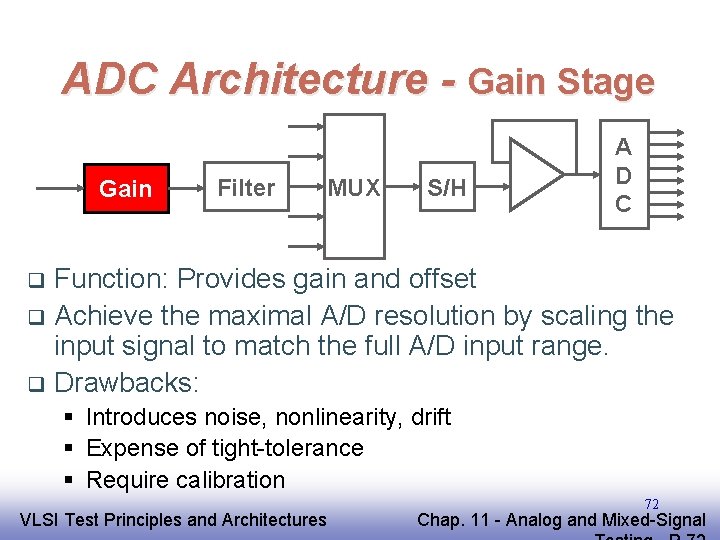

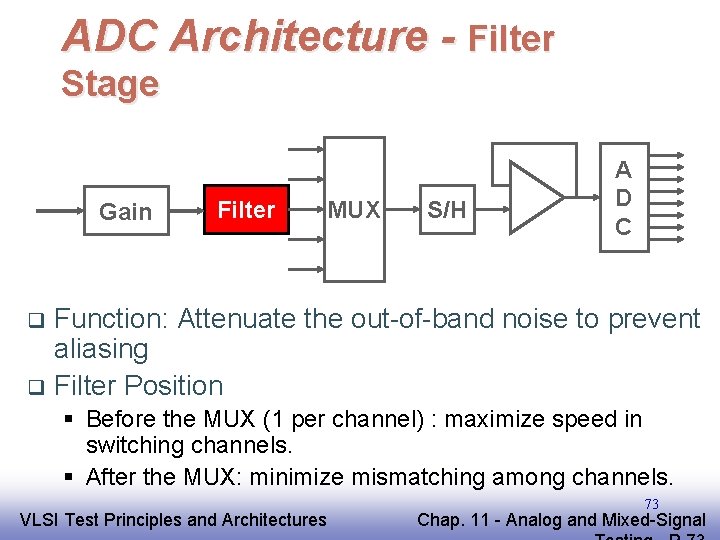

ADC Architecture - Filter Stage Gain Filter MUX S/H A D C Function: Attenuate the out-of-band noise to prevent aliasing q Filter Position q § Before the MUX (1 per channel) : maximize speed in switching channels. § After the MUX: minimize mismatching among channels. EE 141 VLSI Test Principles and Architectures 73 Chap. 11 - Analog and Mixed-Signal

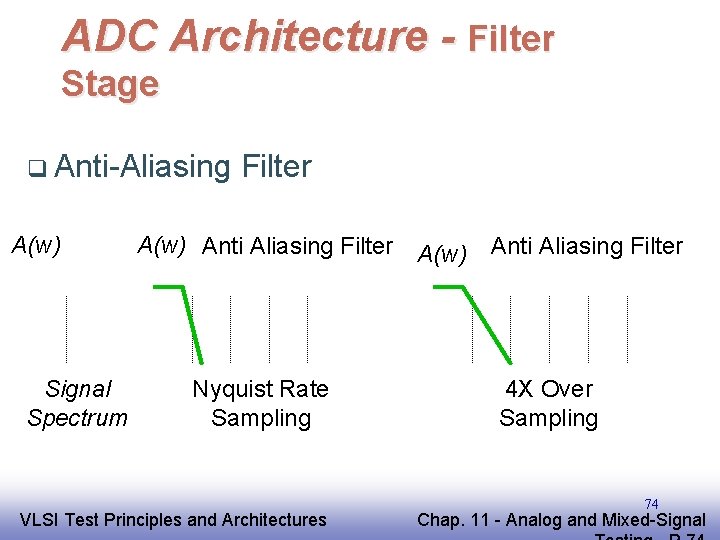

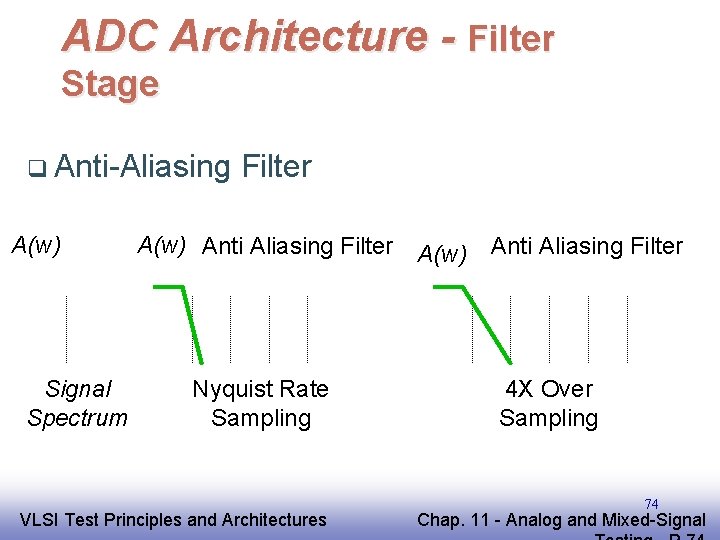

ADC Architecture - Filter Stage q Anti-Aliasing A(w) Signal Spectrum Filter A(w) Anti Aliasing Filter A(w) Nyquist Rate Sampling EE 141 VLSI Test Principles and Architectures Anti Aliasing Filter 4 X Over Sampling 74 Chap. 11 - Analog and Mixed-Signal

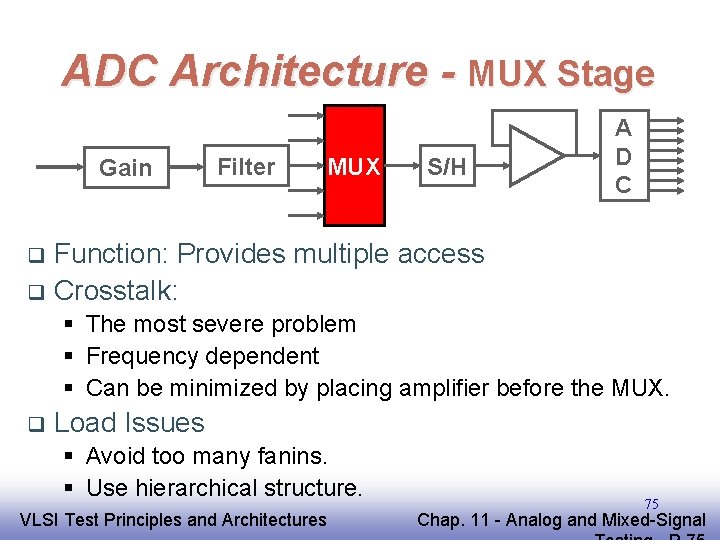

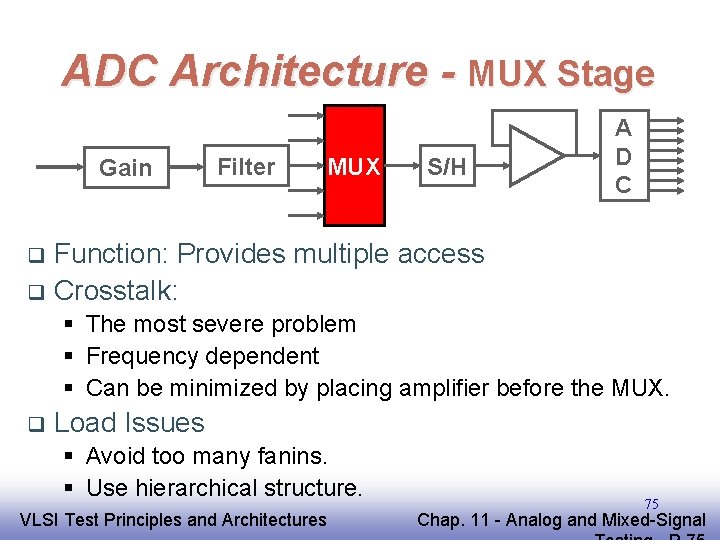

ADC Architecture - MUX Stage Gain Filter MUX S/H A D C Function: Provides multiple access q Crosstalk: q § The most severe problem § Frequency dependent § Can be minimized by placing amplifier before the MUX. q Load Issues § Avoid too many fanins. § Use hierarchical structure. EE 141 VLSI Test Principles and Architectures 75 Chap. 11 - Analog and Mixed-Signal

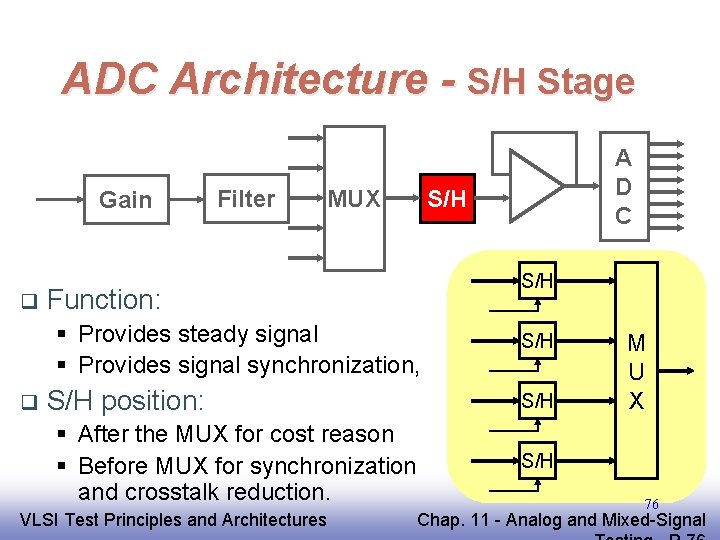

ADC Architecture - S/H Stage Gain q Filter S/H MUX S/H Function: § Provides steady signal § Provides signal synchronization, q S/H position: § After the MUX for cost reason § Before MUX for synchronization and crosstalk reduction. EE 141 VLSI Test Principles and Architectures A D C S/H M U X S/H 76 Chap. 11 - Analog and Mixed-Signal

ADC Architecture - S/H Check List Aperture Time: The time aperture (t 3) q Acquisition Time: The total time for the S/H to acquire a full-scale step input signal. (t 3 - t 1) q Aperture Jitter: The uncertainty of aperture time due to noise or jitter in clock. (t 4 -t 2) q Vin S R Vc Sample EE 141 VLSI Test Principles and Architectures Hold 77 Chap. 11 - Analog and Mixed-Signal

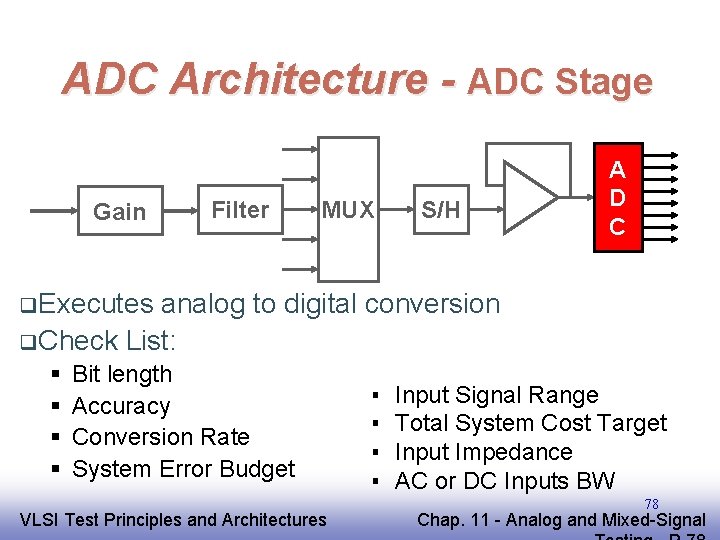

ADC Architecture - ADC Stage Gain Filter MUX S/H A D C q. Executes analog to digital conversion q. Check List: § § Bit length Accuracy Conversion Rate System Error Budget EE 141 VLSI Test Principles and Architectures ▪ ▪ Input Signal Range Total System Cost Target Input Impedance AC or DC Inputs BW 78 Chap. 11 - Analog and Mixed-Signal

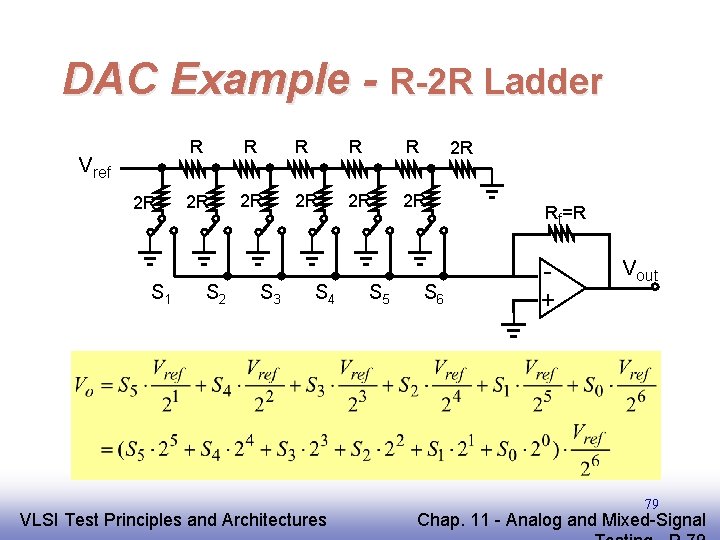

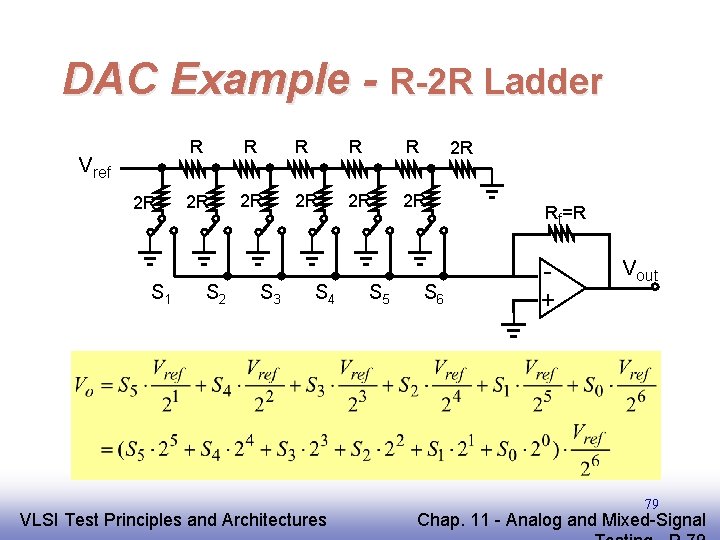

DAC Example - R-2 R Ladder Vref 2 R S 1 R R R 2 R 2 R 2 R S 2 S 3 S 4 EE 141 VLSI Test Principles and Architectures S 5 2 R S 6 Rf=R + Vout 79 Chap. 11 - Analog and Mixed-Signal

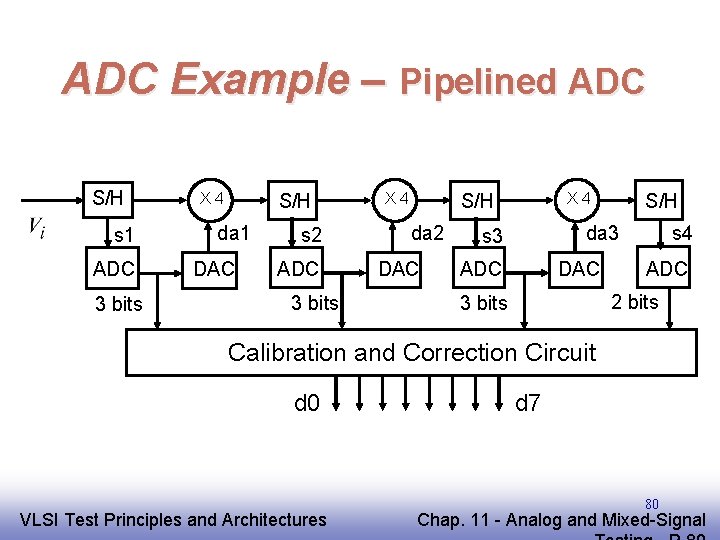

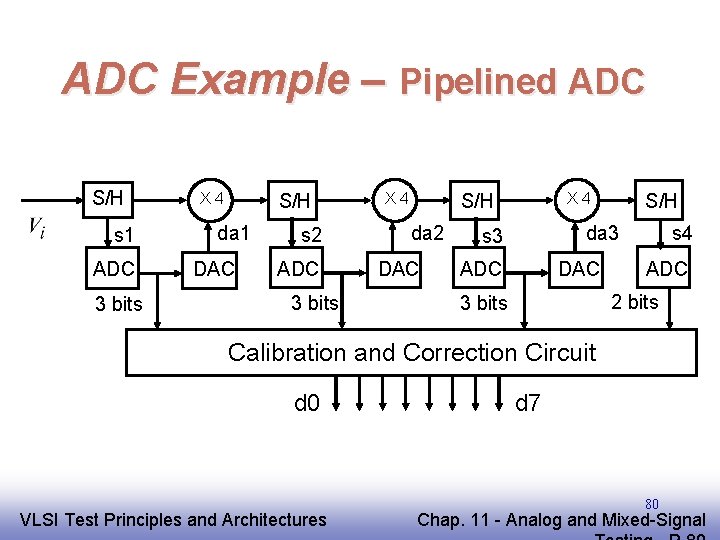

ADC Example – Pipelined ADC S/H s 1 ADC 3 bits X 4 S/H da 1 DAC s 2 ADC 3 bits X 4 S/H da 2 DAC S/H s 4 da 3 s 3 ADC DAC ADC 2 bits 3 bits Calibration and Correction Circuit d 0 EE 141 VLSI Test Principles and Architectures d 7 80 Chap. 11 - Analog and Mixed-Signal

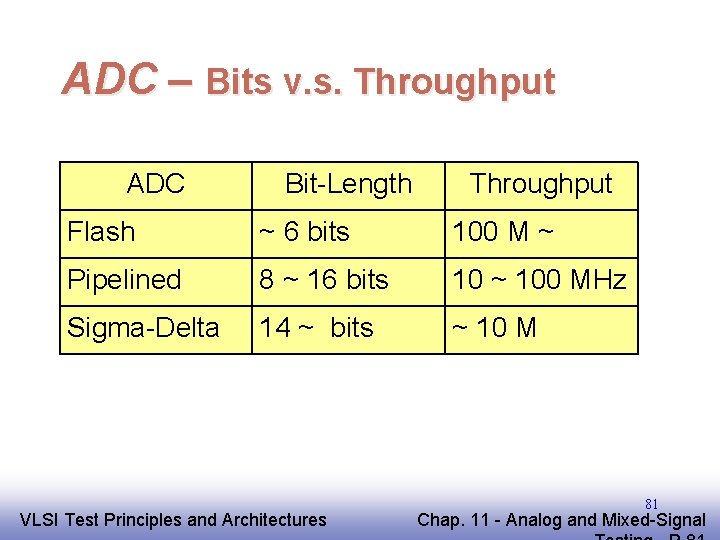

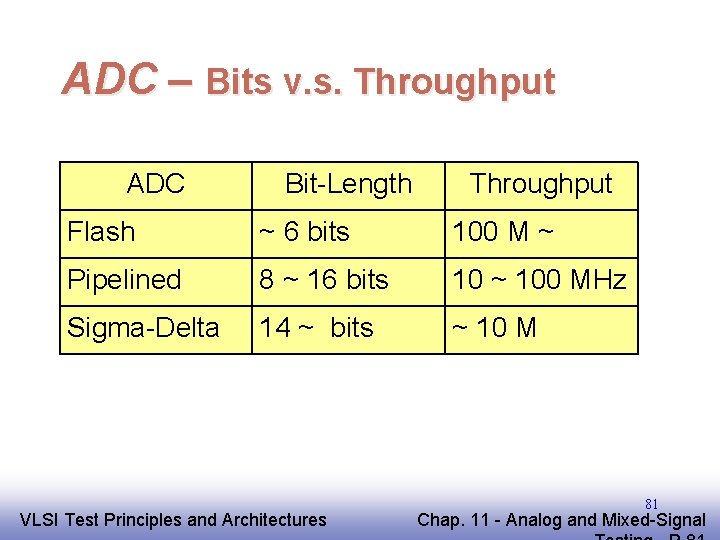

ADC – Bits v. s. Throughput ADC Bit-Length Throughput Flash ~ 6 bits 100 M ~ Pipelined 8 ~ 16 bits 10 ~ 100 MHz Sigma-Delta 14 ~ bits ~ 10 M EE 141 VLSI Test Principles and Architectures 81 Chap. 11 - Analog and Mixed-Signal

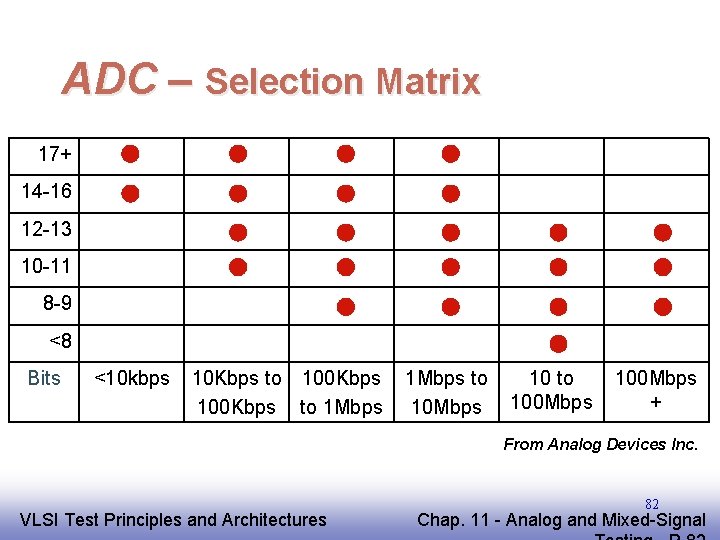

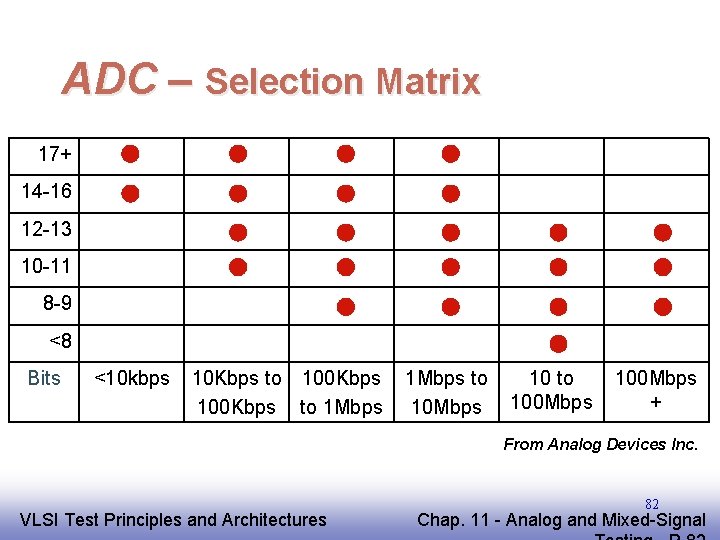

ADC – Selection Matrix 17+ 14 -16 12 -13 10 -11 8 -9 <8 Bits <10 kbps 10 Kbps to 100 Kbps to 1 Mbps to 10 Mbps 10 to 100 Mbps + From Analog Devices Inc. EE 141 VLSI Test Principles and Architectures 82 Chap. 11 - Analog and Mixed-Signal

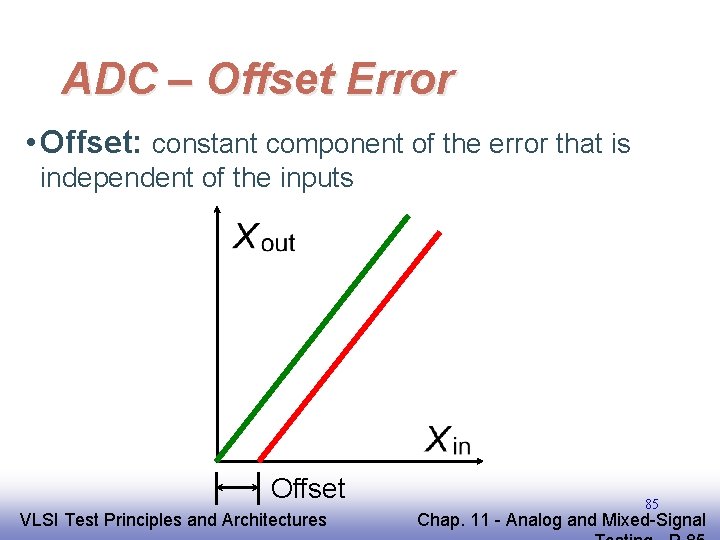

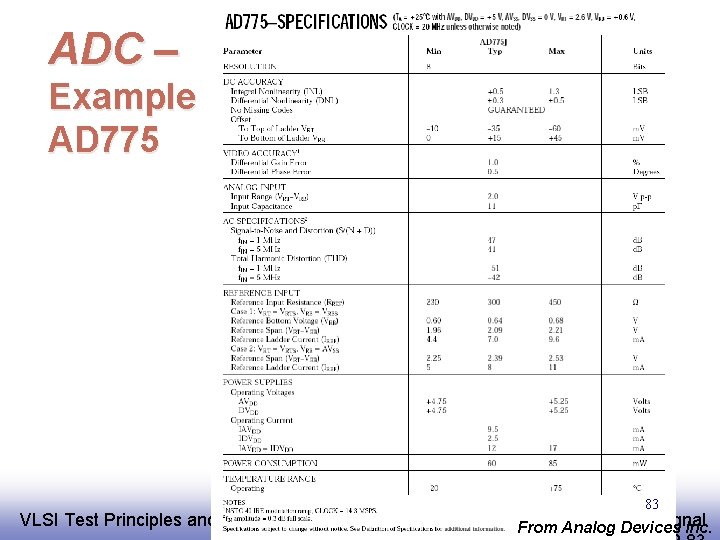

ADC – Example AD 775 EE 141 VLSI Test Principles and Architectures 83 Chap. 11 - Analog and Mixed-Signal From Analog Devices Inc.

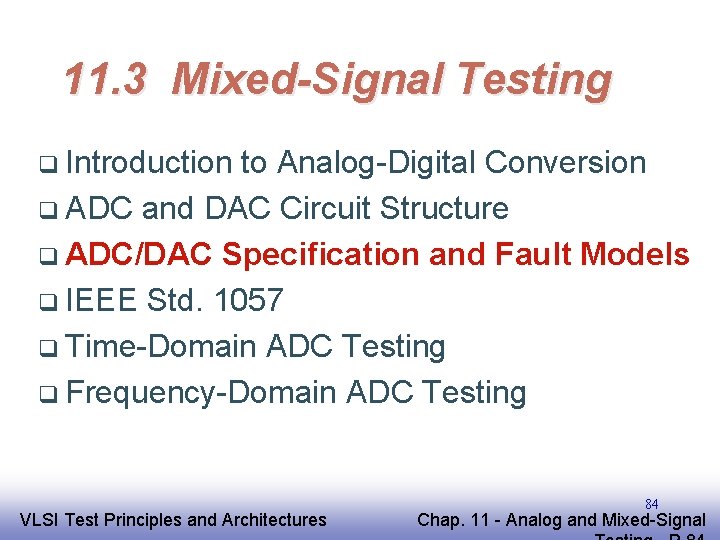

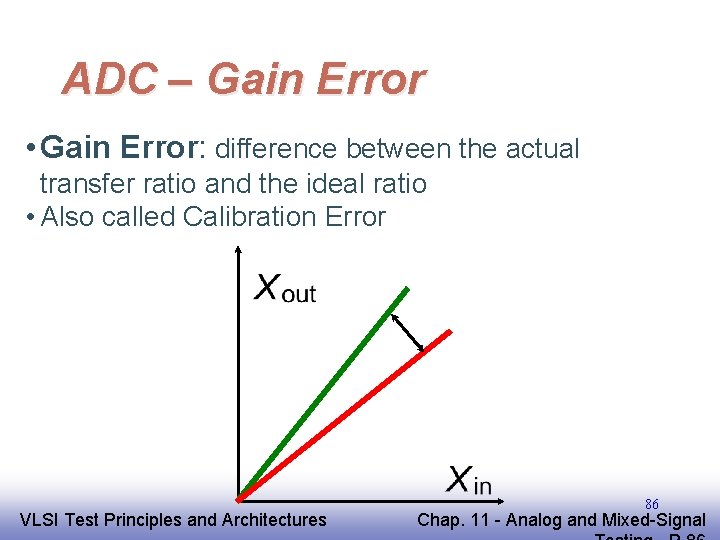

11. 3 Mixed-Signal Testing q Introduction to Analog-Digital Conversion q ADC and DAC Circuit Structure q ADC/DAC Specification and Fault Models q IEEE Std. 1057 q Time-Domain ADC Testing q Frequency-Domain ADC Testing EE 141 VLSI Test Principles and Architectures 84 Chap. 11 - Analog and Mixed-Signal

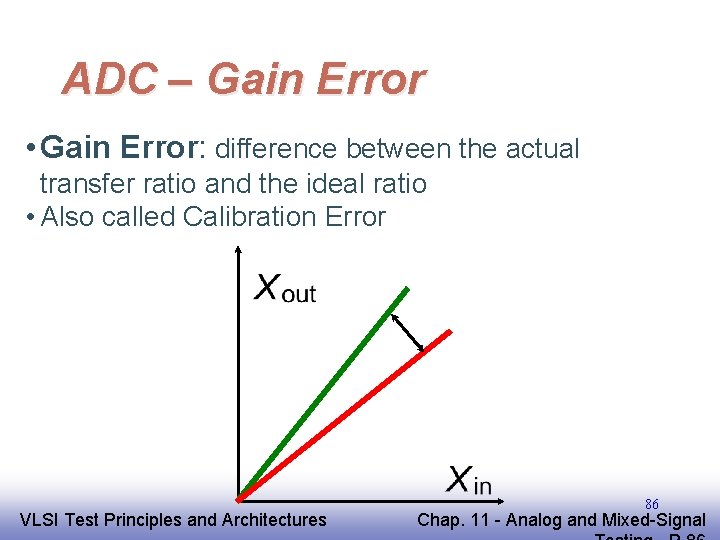

ADC – Offset Error • Offset: constant component of the error that is independent of the inputs Offset EE 141 VLSI Test Principles and Architectures 85 Chap. 11 - Analog and Mixed-Signal

ADC – Gain Error • Gain Error: difference between the actual transfer ratio and the ideal ratio • Also called Calibration Error EE 141 VLSI Test Principles and Architectures 86 Chap. 11 - Analog and Mixed-Signal

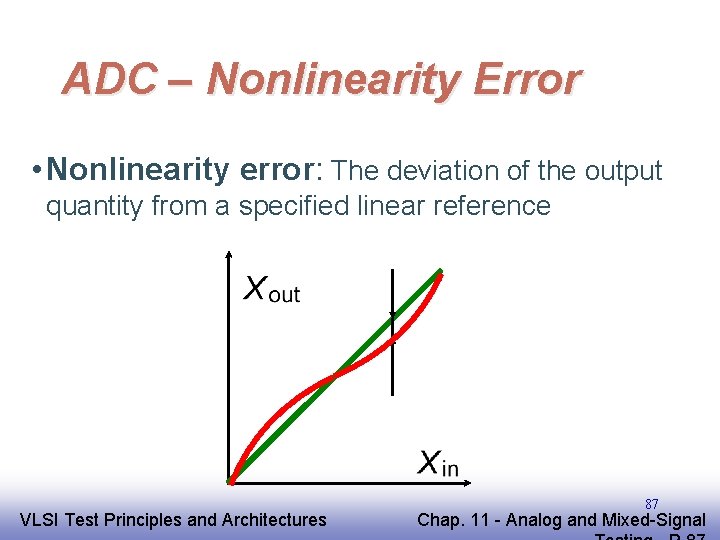

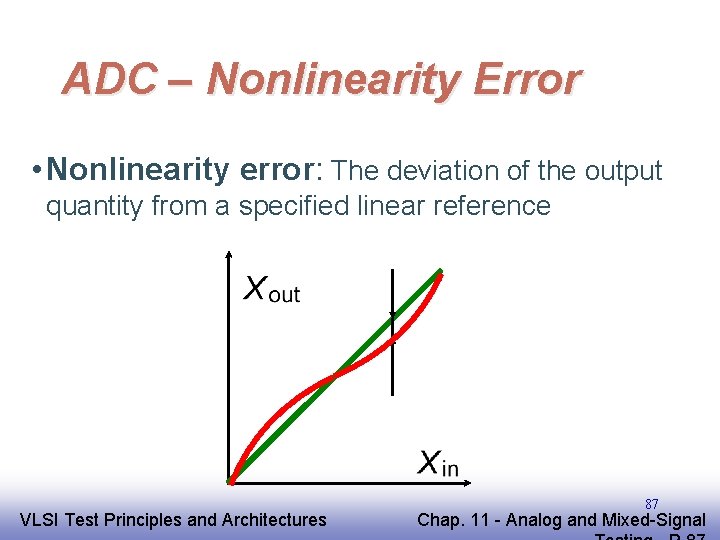

ADC – Nonlinearity Error • Nonlinearity error: The deviation of the output quantity from a specified linear reference EE 141 VLSI Test Principles and Architectures 87 Chap. 11 - Analog and Mixed-Signal

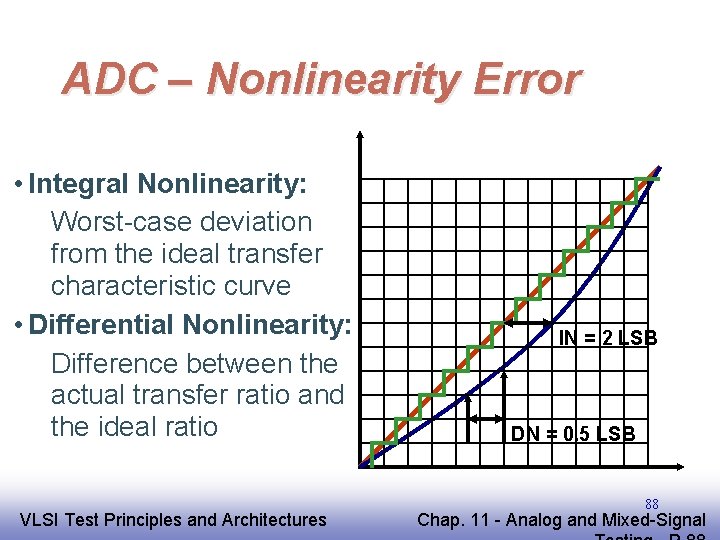

ADC – Nonlinearity Error • Integral Nonlinearity: Worst-case deviation from the ideal transfer characteristic curve • Differential Nonlinearity: Difference between the actual transfer ratio and the ideal ratio EE 141 VLSI Test Principles and Architectures IN = 2 LSB DN = 0. 5 LSB 88 Chap. 11 - Analog and Mixed-Signal

ADC – Temperature-Dependent Error • Temperature-Dependent Error: Due to the change in ambient temperature or temperature variation due to self-heating (temperature stability, temperature coefficient) EE 141 VLSI Test Principles and Architectures 89 Chap. 11 - Analog and Mixed-Signal

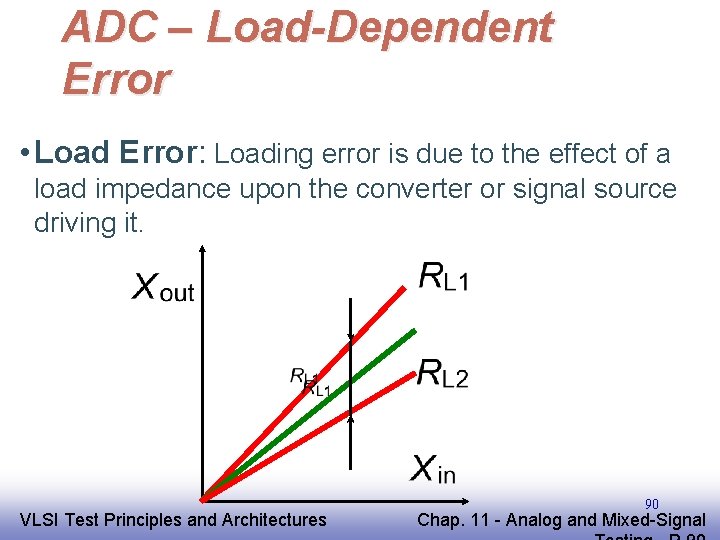

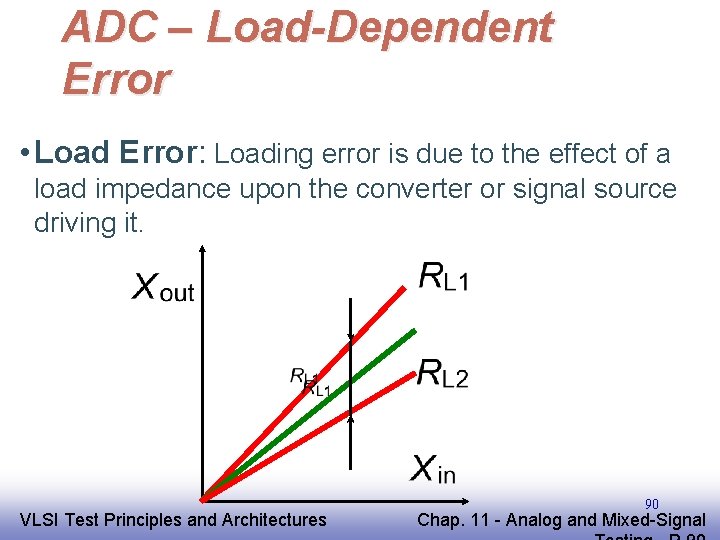

ADC – Load-Dependent Error • Load Error: Loading error is due to the effect of a load impedance upon the converter or signal source driving it. EE 141 VLSI Test Principles and Architectures 90 Chap. 11 - Analog and Mixed-Signal

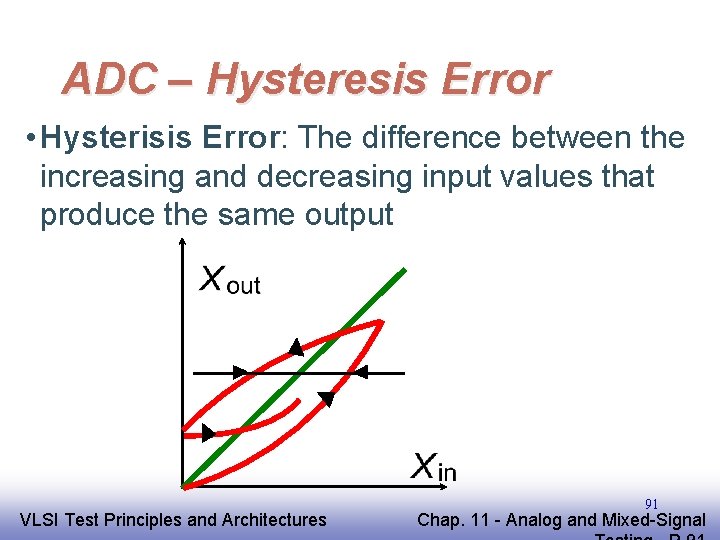

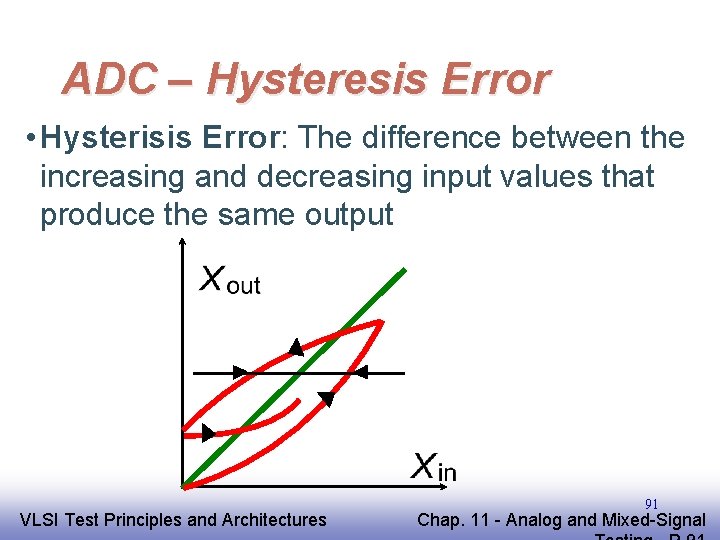

ADC – Hysteresis Error • Hysterisis Error: The difference between the increasing and decreasing input values that produce the same output EE 141 VLSI Test Principles and Architectures 91 Chap. 11 - Analog and Mixed-Signal

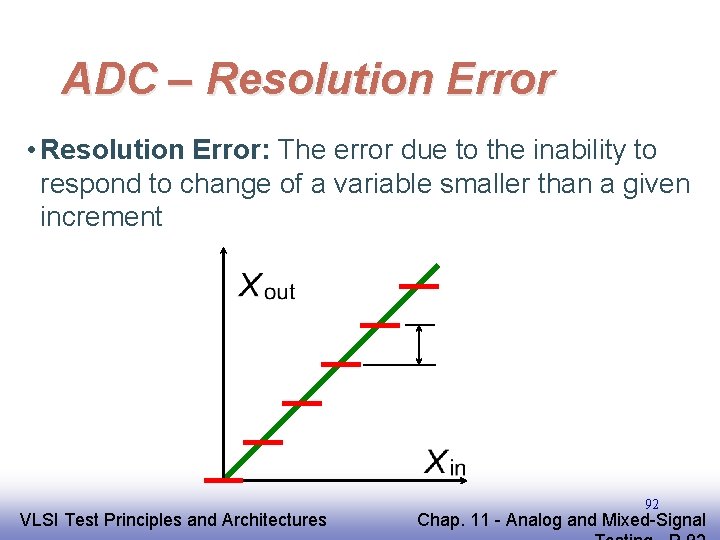

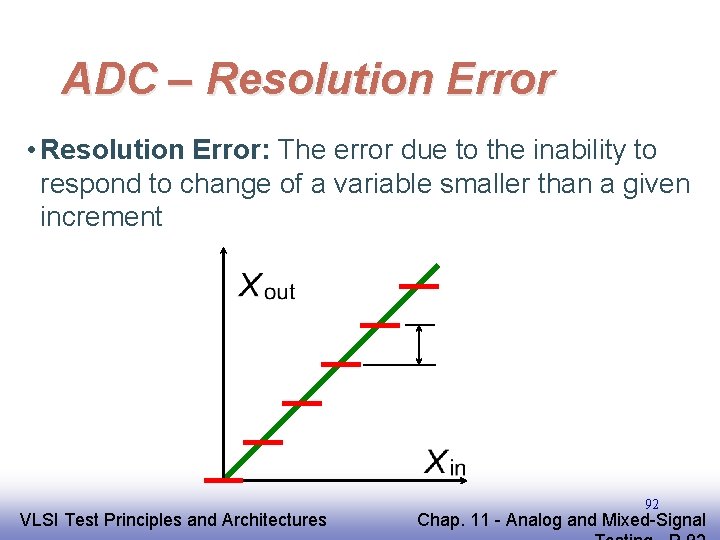

ADC – Resolution Error • Resolution Error: The error due to the inability to respond to change of a variable smaller than a given increment EE 141 VLSI Test Principles and Architectures 92 Chap. 11 - Analog and Mixed-Signal

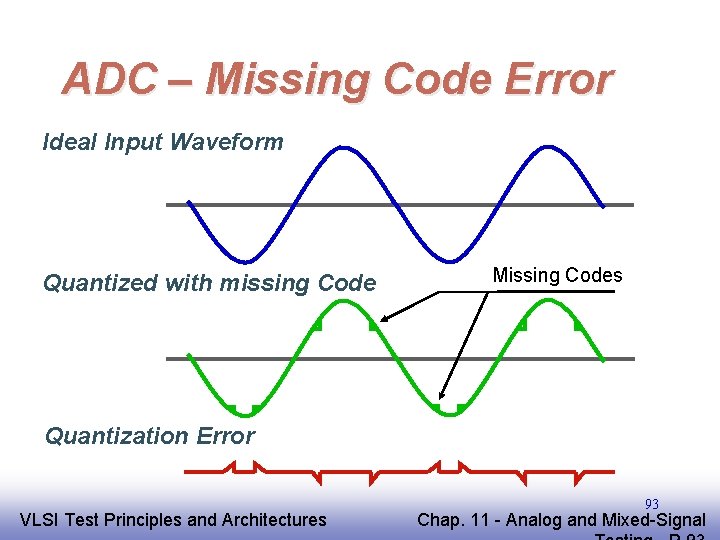

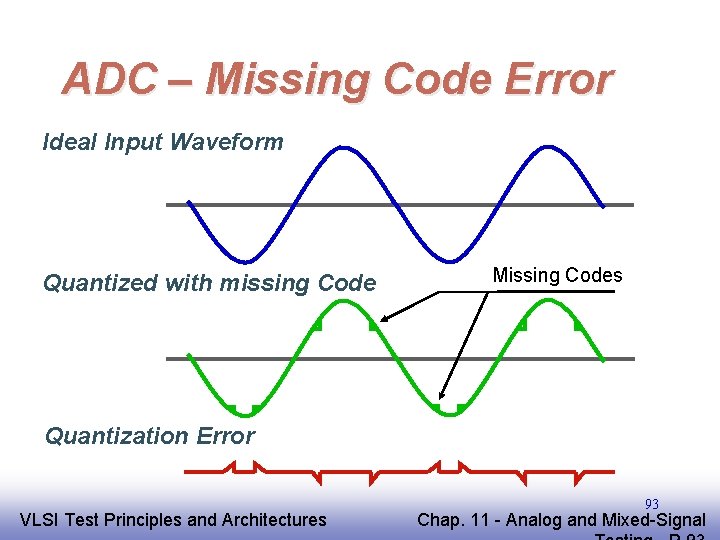

ADC – Missing Code Error Ideal Input Waveform Quantized with missing Code Missing Codes Quantization Error EE 141 VLSI Test Principles and Architectures 93 Chap. 11 - Analog and Mixed-Signal

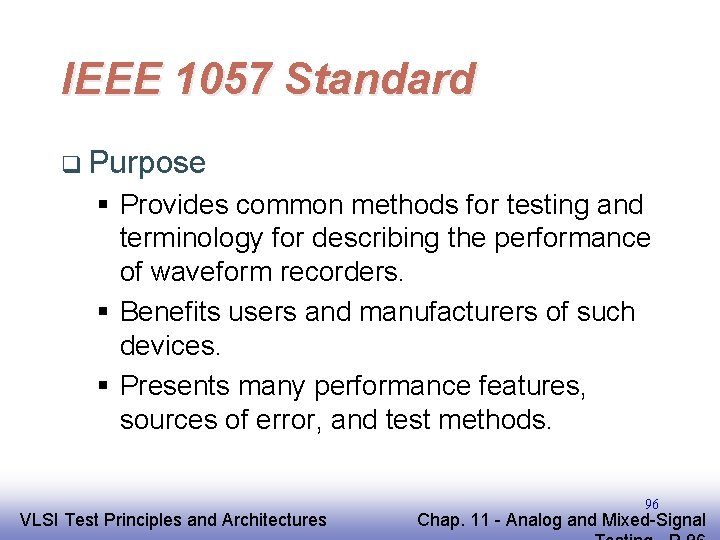

11. 3 Mixed-Signal Testing q Introduction to Analog-Digital Conversion q ADC and DAC Circuit Structure q ADC/DAC Specification and Fault Models q IEEE Std. 1057 q Time-Domain ADC Testing q Frequency-Domain ADC Testing EE 141 VLSI Test Principles and Architectures 94 Chap. 11 - Analog and Mixed-Signal

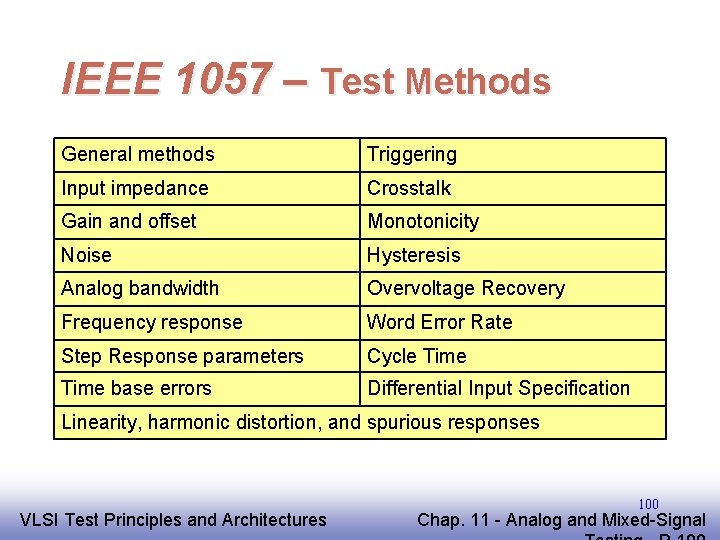

IEEE 1057 Standard q Scope § Covers electronic digitizing waveform recorders, waveform analyzers and digitizing oscilloscopes with digital outputs. § Applies to, but is not restricted to, generalpurpose waveform recorders and analyzers. EE 141 VLSI Test Principles and Architectures 95 Chap. 11 - Analog and Mixed-Signal

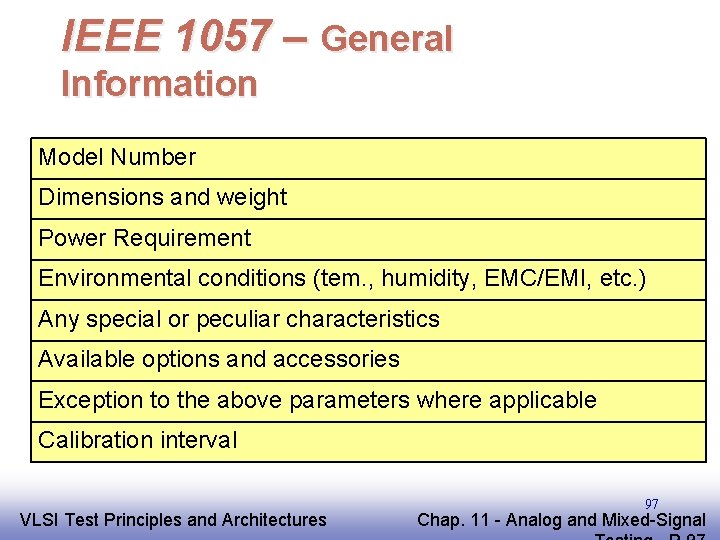

IEEE 1057 Standard q Purpose § Provides common methods for testing and terminology for describing the performance of waveform recorders. § Benefits users and manufacturers of such devices. § Presents many performance features, sources of error, and test methods. EE 141 VLSI Test Principles and Architectures 96 Chap. 11 - Analog and Mixed-Signal

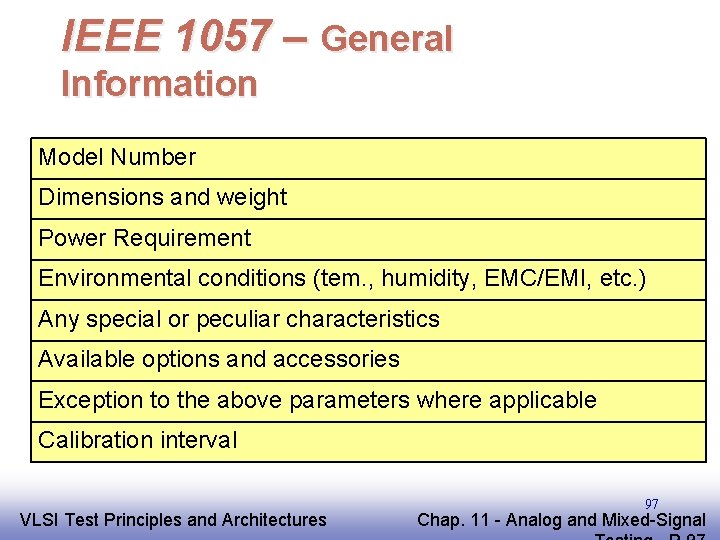

IEEE 1057 – General Information Model Number Dimensions and weight Power Requirement Environmental conditions (tem. , humidity, EMC/EMI, etc. ) Any special or peculiar characteristics Available options and accessories Exception to the above parameters where applicable Calibration interval EE 141 VLSI Test Principles and Architectures 97 Chap. 11 - Analog and Mixed-Signal

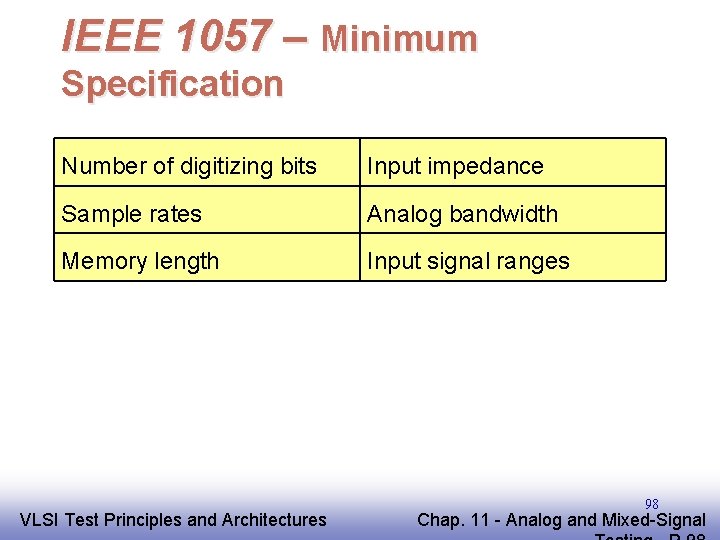

IEEE 1057 – Minimum Specification Number of digitizing bits Input impedance Sample rates Analog bandwidth Memory length Input signal ranges EE 141 VLSI Test Principles and Architectures 98 Chap. 11 - Analog and Mixed-Signal

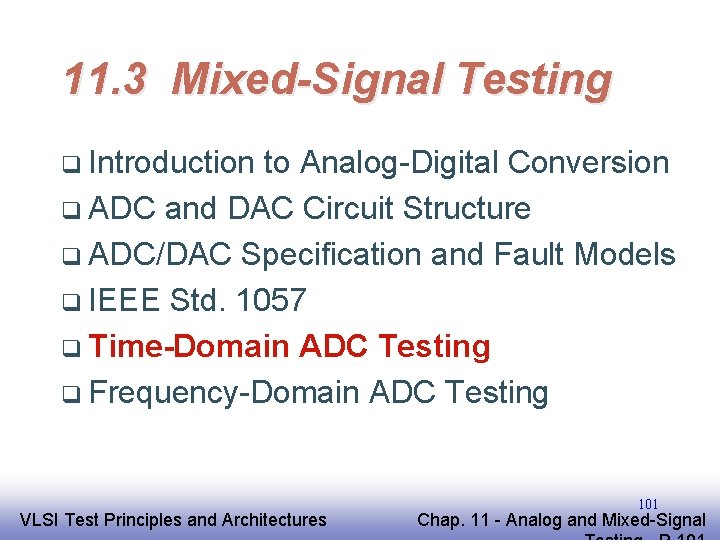

IEEE 1057 – Additional Specifications Gain Fixed error in sample time Offset Trigger delay and jitter Differential nonlinearity Trigger sensitivity Integral nonlinearity Trigger minimum rate of change Harmonic distortion Trigger hysteresis band Spurious response Trigger coupling to signal Maximal static error Crosstalk Signal to noise ratio Monotonicity Effective bits Hystersis Peak error Over voltage recovery Random noise Word error rate Frequency response Cycle time Settling time Common mode rejection ratio Slew limit Differential input impedance Overshoot and precursors Maximum operating common Aperture uncertainty mode signal level Long-term stability Transition duration of step response Maximum common mode signal level EE 141 VLSI Test Principles and Architectures 99 Chap. 11 - Analog and Mixed-Signal

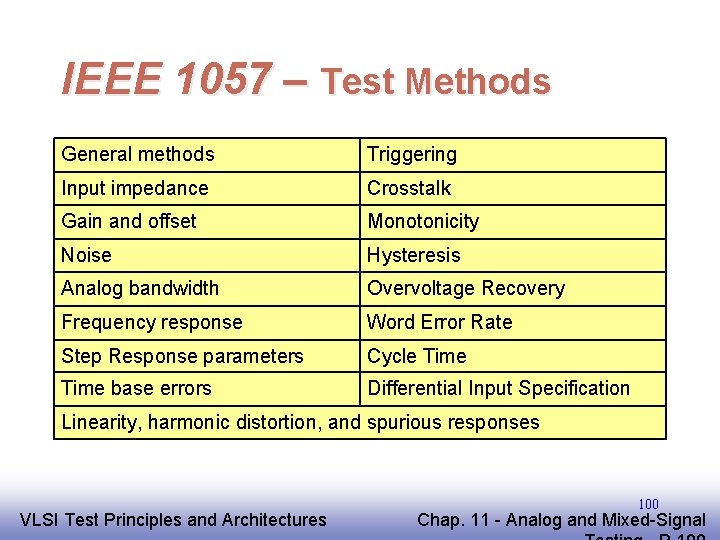

IEEE 1057 – Test Methods General methods Triggering Input impedance Crosstalk Gain and offset Monotonicity Noise Hysteresis Analog bandwidth Overvoltage Recovery Frequency response Word Error Rate Step Response parameters Cycle Time base errors Differential Input Specification Linearity, harmonic distortion, and spurious responses EE 141 VLSI Test Principles and Architectures 100 Chap. 11 - Analog and Mixed-Signal

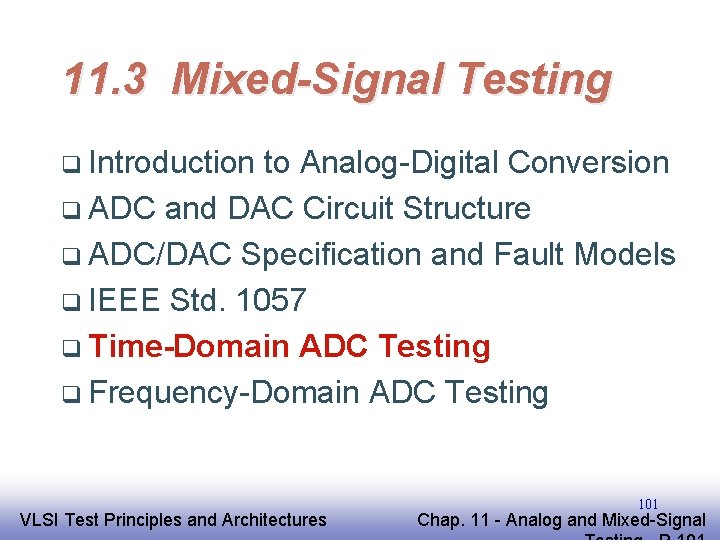

11. 3 Mixed-Signal Testing q Introduction to Analog-Digital Conversion q ADC and DAC Circuit Structure q ADC/DAC Specification and Fault Models q IEEE Std. 1057 q Time-Domain ADC Testing q Frequency-Domain ADC Testing EE 141 VLSI Test Principles and Architectures 101 Chap. 11 - Analog and Mixed-Signal

![Histogram Code Bins Code Bin T6 7 245 W7 T6 6 543 W6 Histogram – Code Bins Code Bin T[6] 7 245 W[7] T[6] 6 543 W[6]](https://slidetodoc.com/presentation_image_h/904b52feafa99458cd7f28daa7af5486/image-102.jpg)

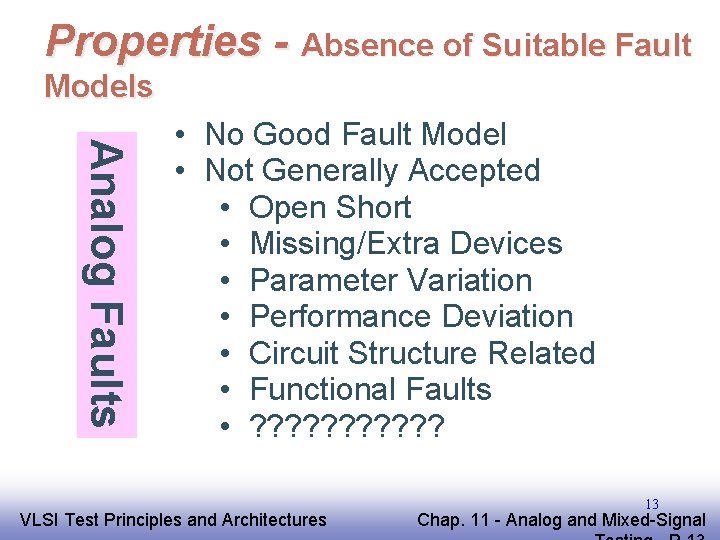

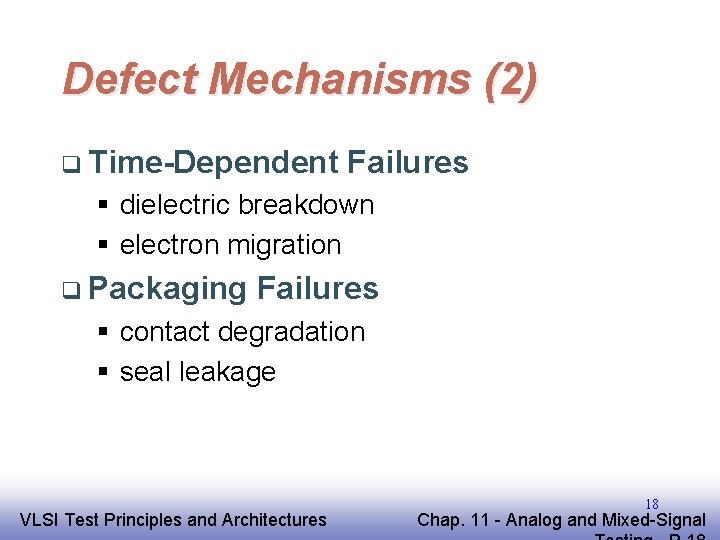

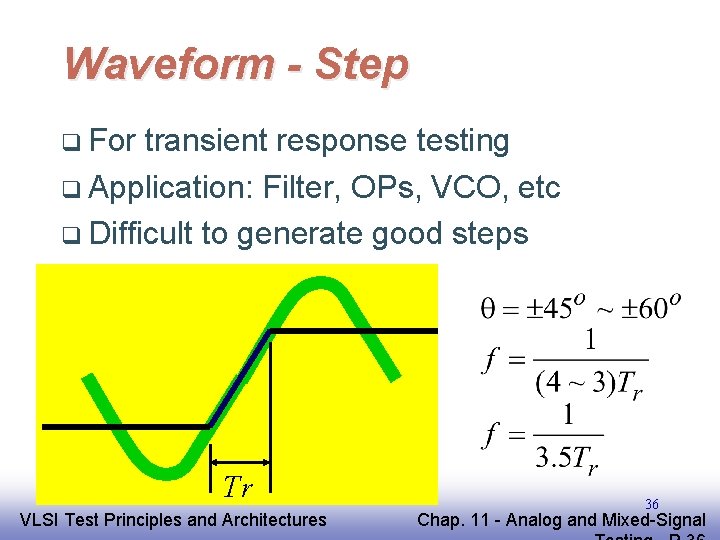

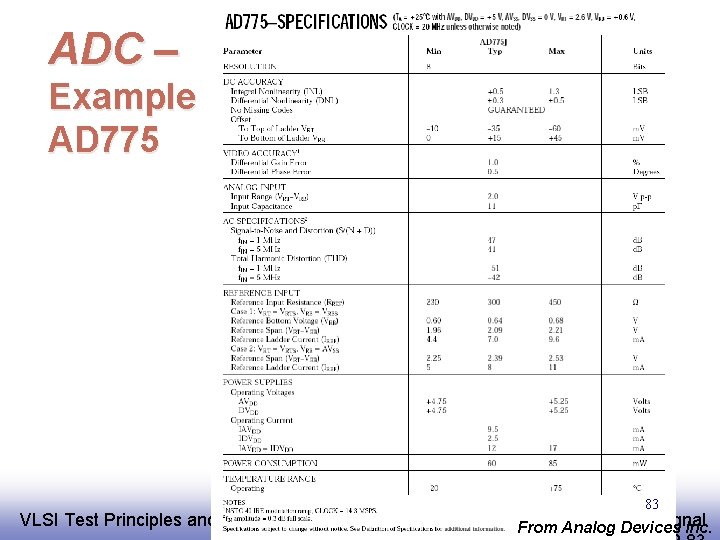

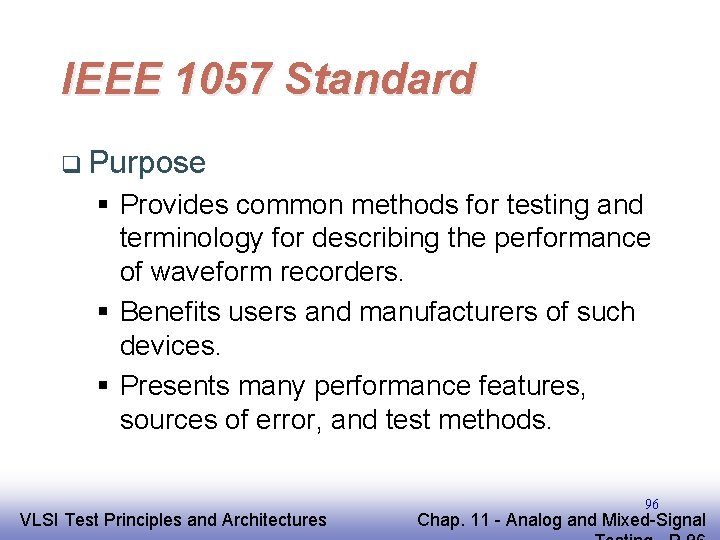

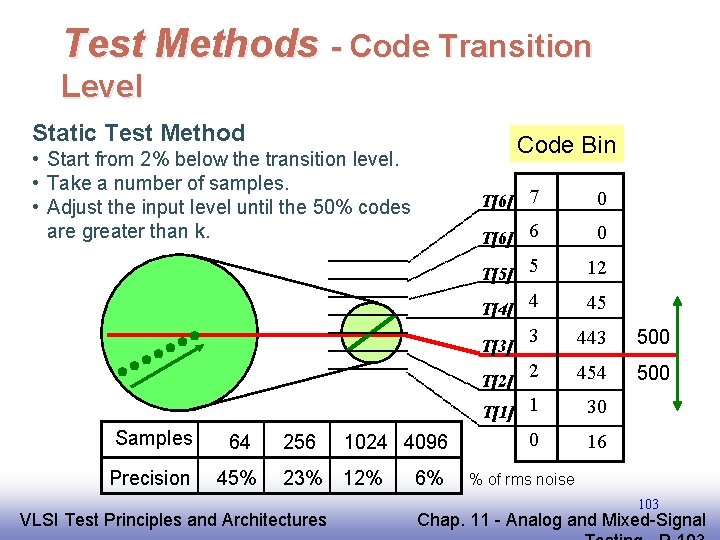

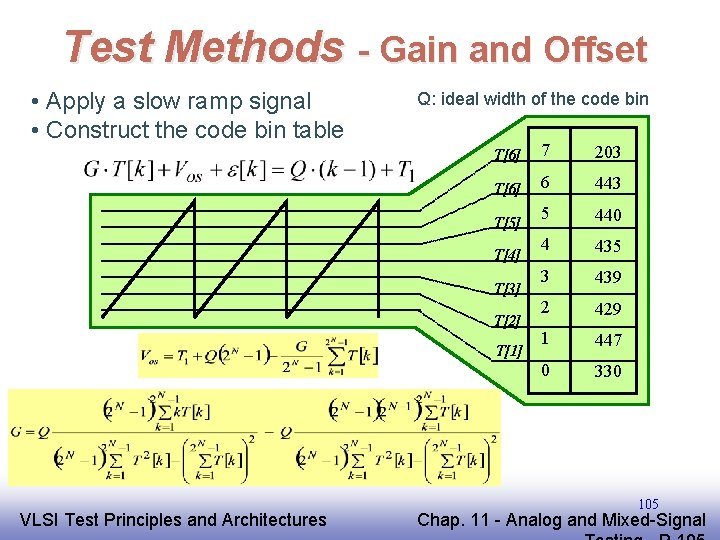

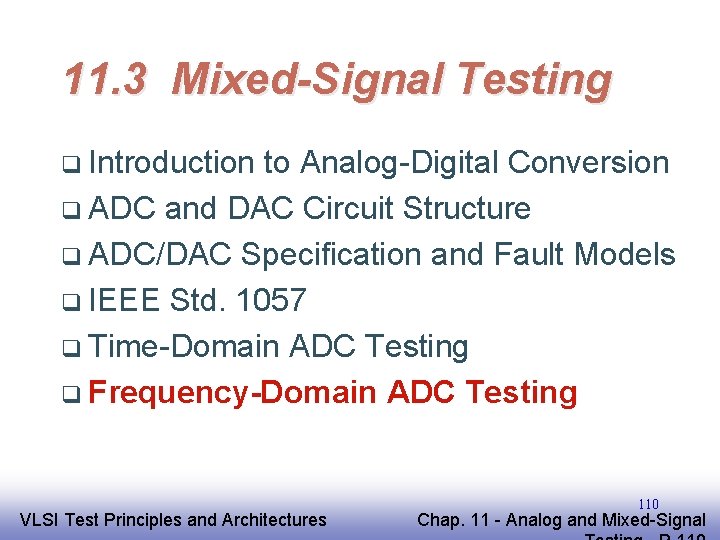

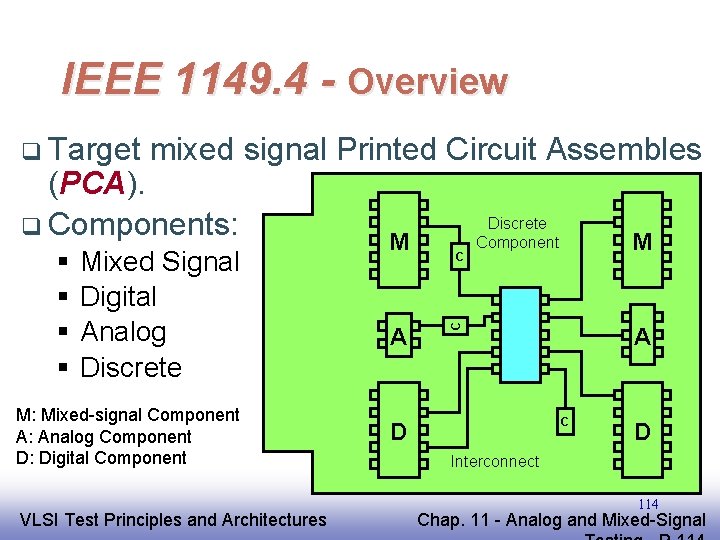

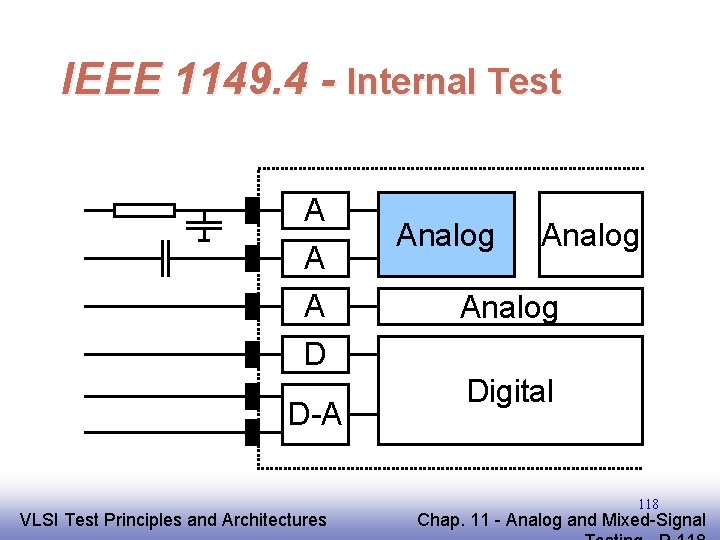

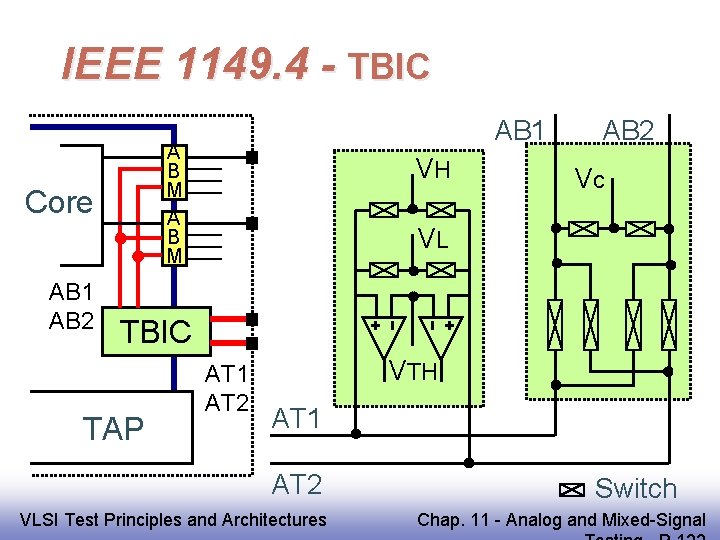

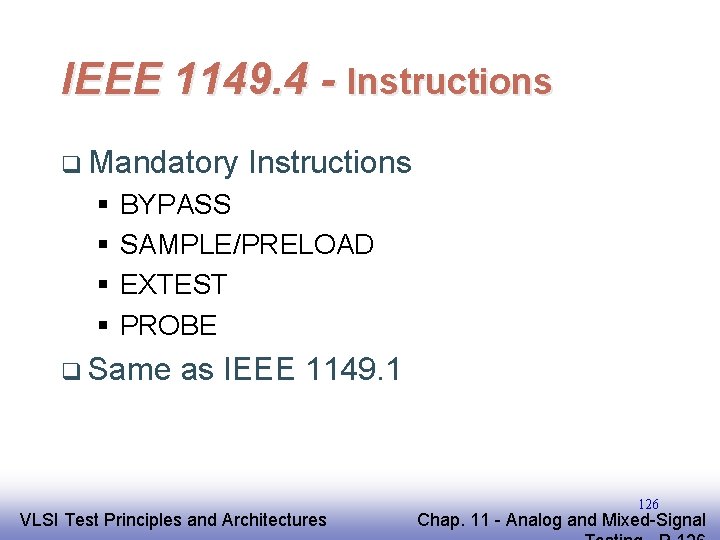

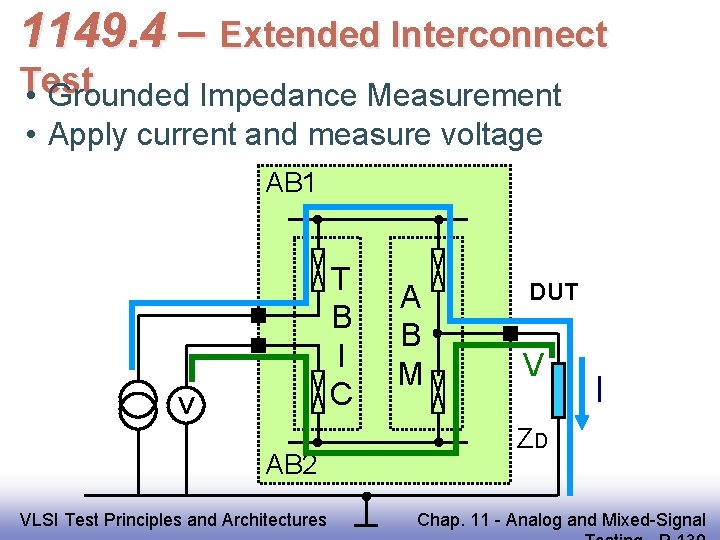

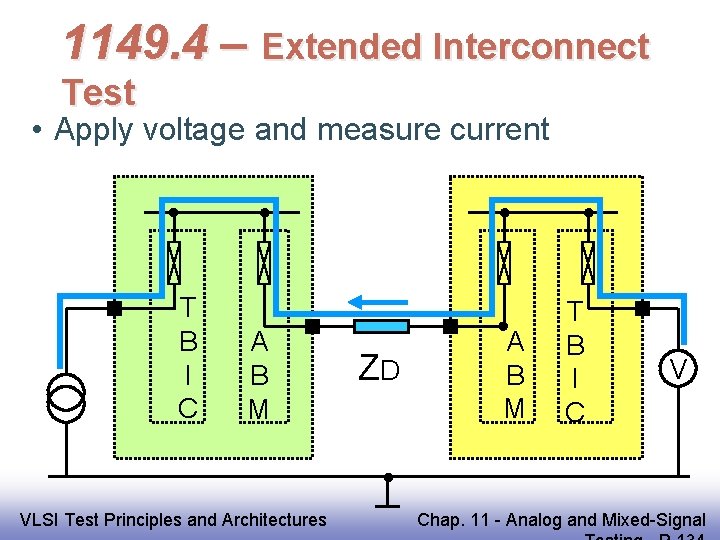

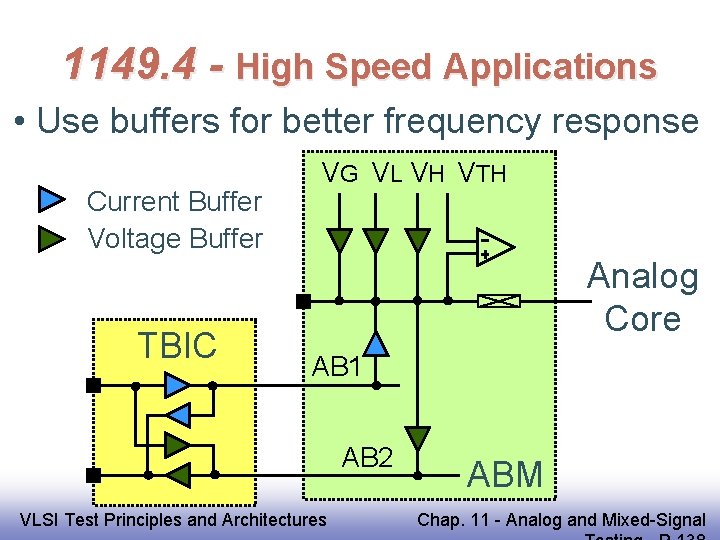

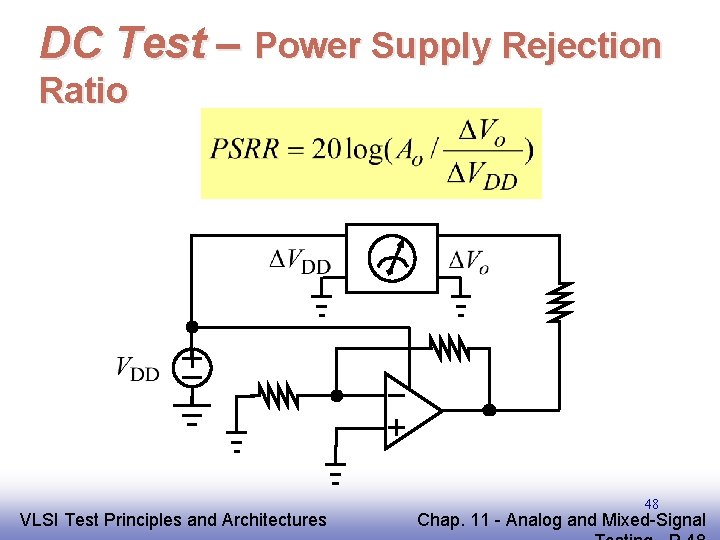

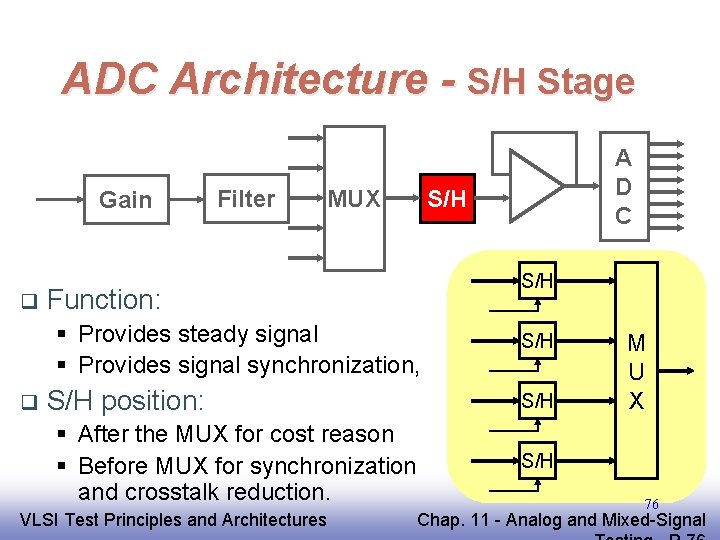

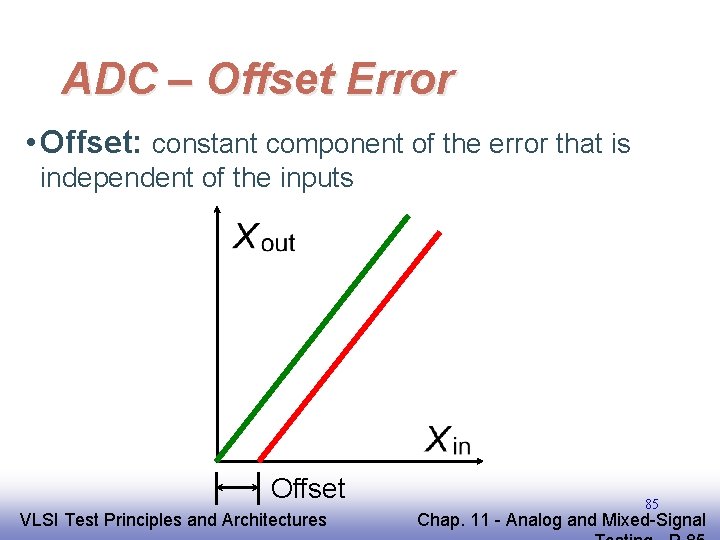

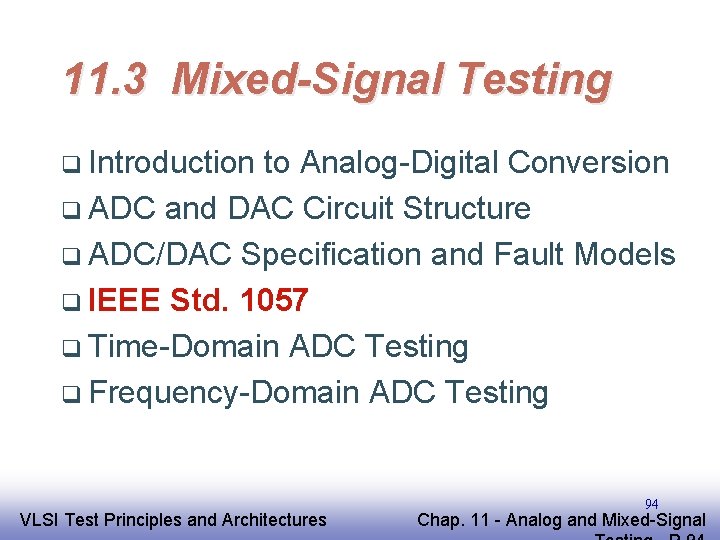

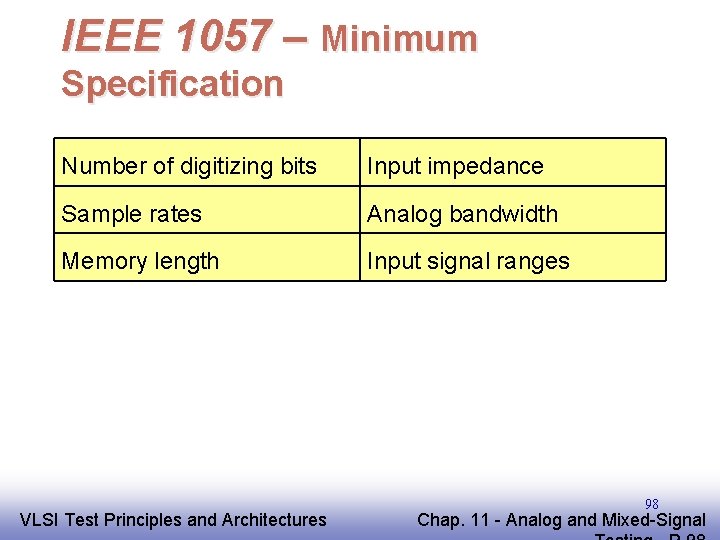

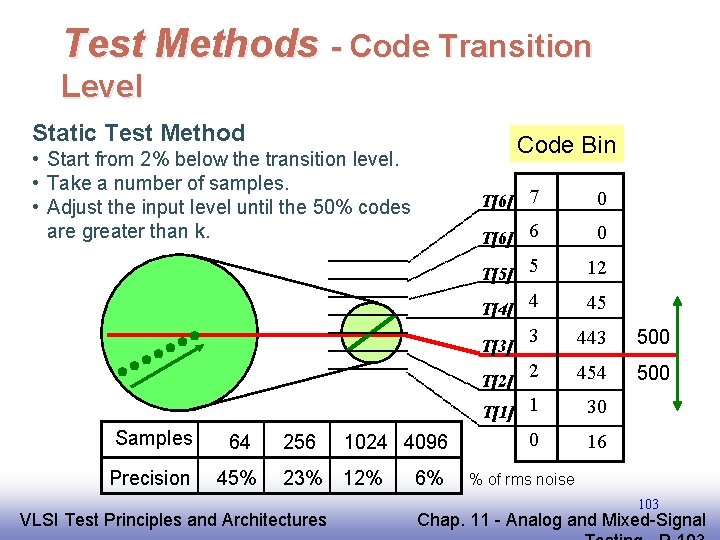

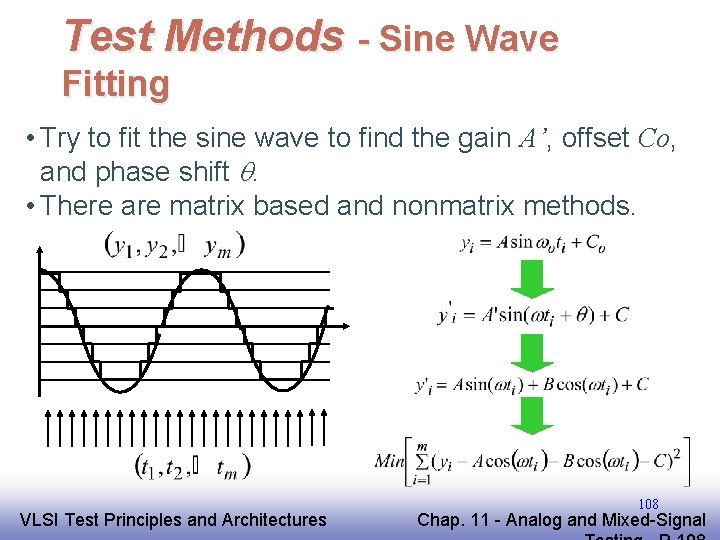

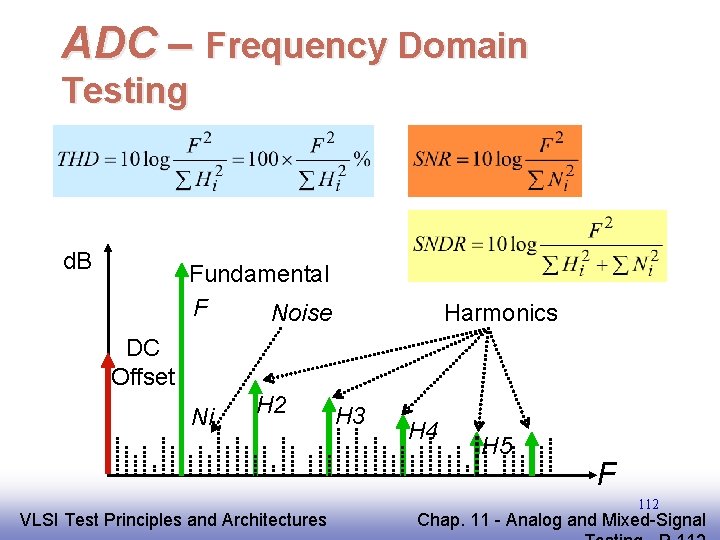

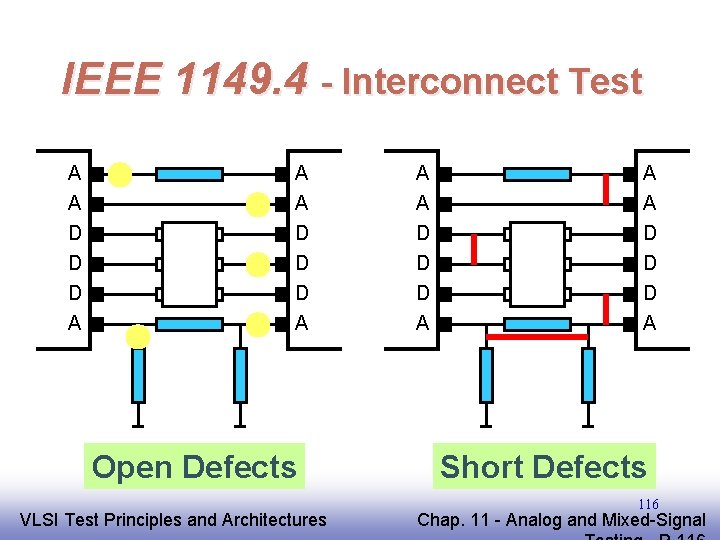

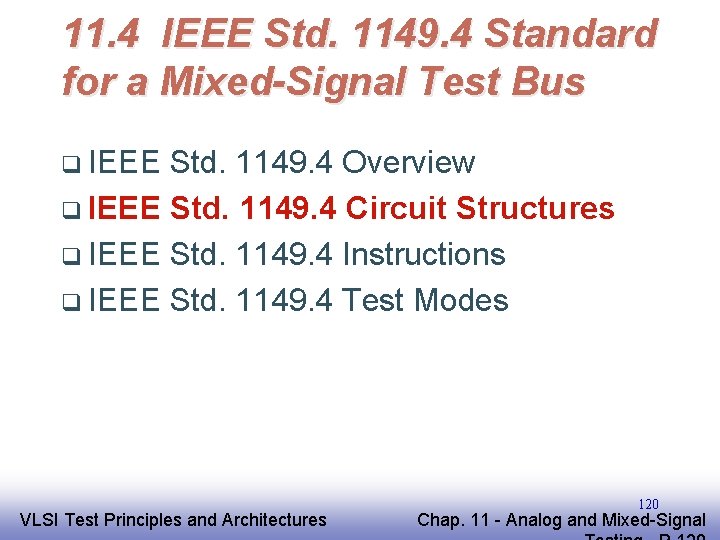

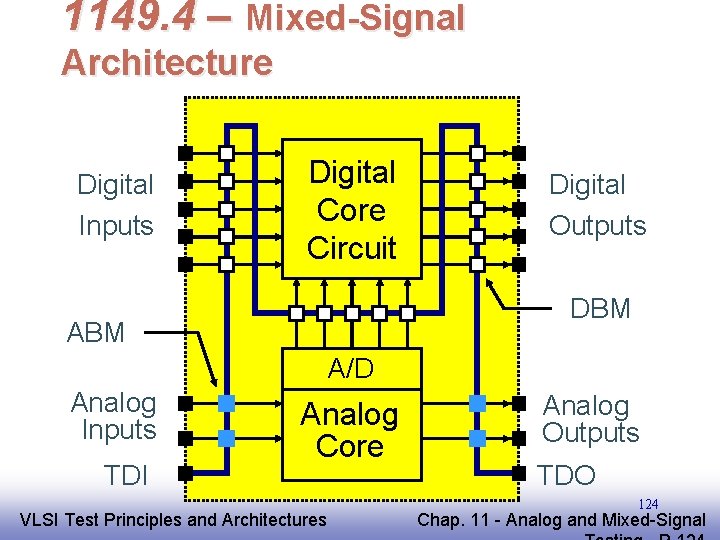

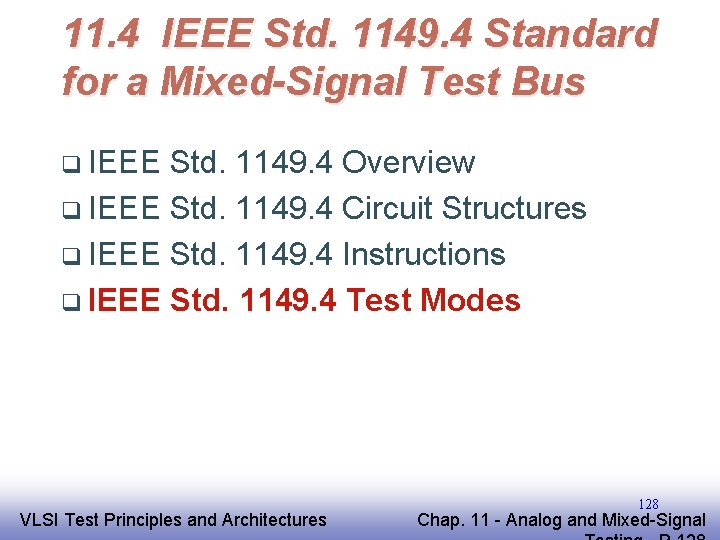

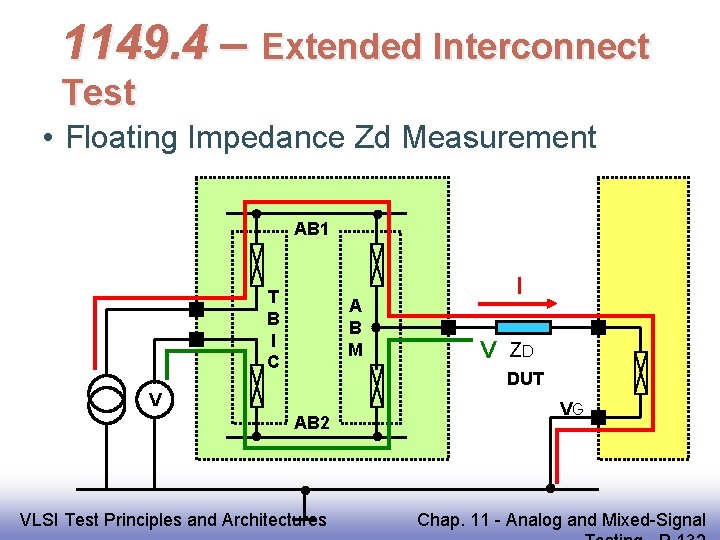

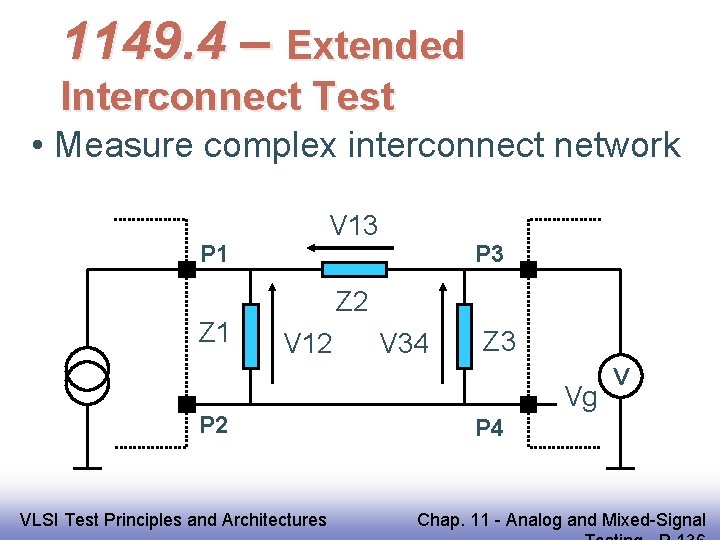

Histogram – Code Bins Code Bin T[6] 7 245 W[7] T[6] 6 543 W[6] T[5] 5 456 W[5] T[4] 4 372 W[4] 3 345 W[3] 2 472 W[2] T[1] 1 529 W[1] 0 302 W[0] T[3] T[2] Code Level Bin Count H[k] Code Width W[k] EE 141 VLSI Test Principles and Architectures 102 Chap. 11 - Analog and Mixed-Signal

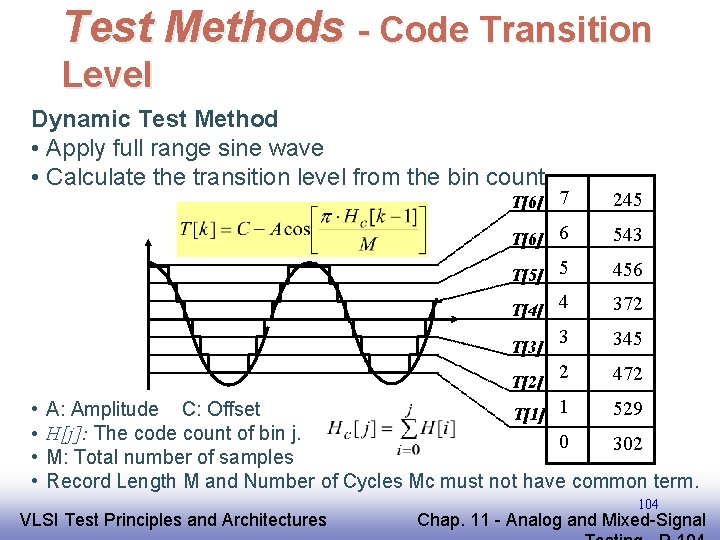

Test Methods - Code Transition Level Static Test Method Code Bin • Start from 2% below the transition level. • Take a number of samples. • Adjust the input level until the 50% codes are greater than k. T[6] 7 0 T[6] 6 0 T[5] 5 12 T[4] 4 45 3 443 500 2 454 500 T[1] 1 30 0 16 T[3] T[2] Samples 64 Precision 45% 256 1024 4096 23% 12% EE 141 VLSI Test Principles and Architectures 6% % of rms noise 103 Chap. 11 - Analog and Mixed-Signal

Test Methods - Code Transition Level Dynamic Test Method • Apply full range sine wave • Calculate the transition level from the bin count T[6] 7 245 T[6] 6 543 T[5] 5 456 T[4] 4 372 3 345 2 472 T[3] T[2] • • 529 A: Amplitude C: Offset T[1] 1 H[j]: The code count of bin j. 0 302 M: Total number of samples Record Length M and Number of Cycles Mc must not have common term. EE 141 VLSI Test Principles and Architectures 104 Chap. 11 - Analog and Mixed-Signal

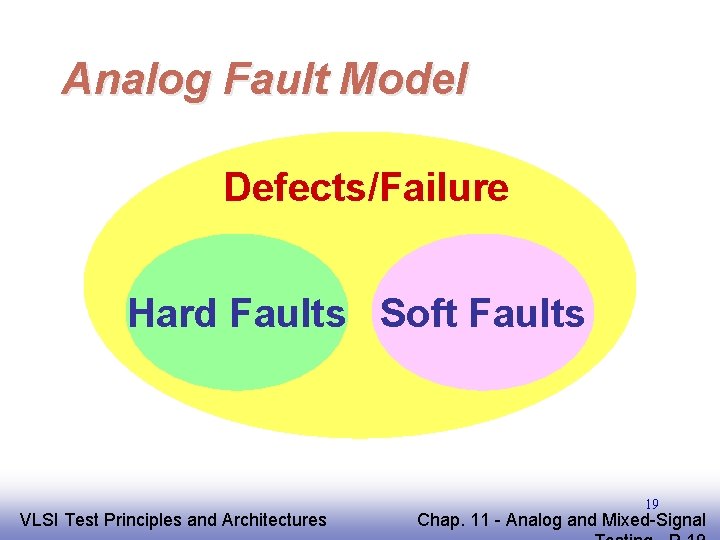

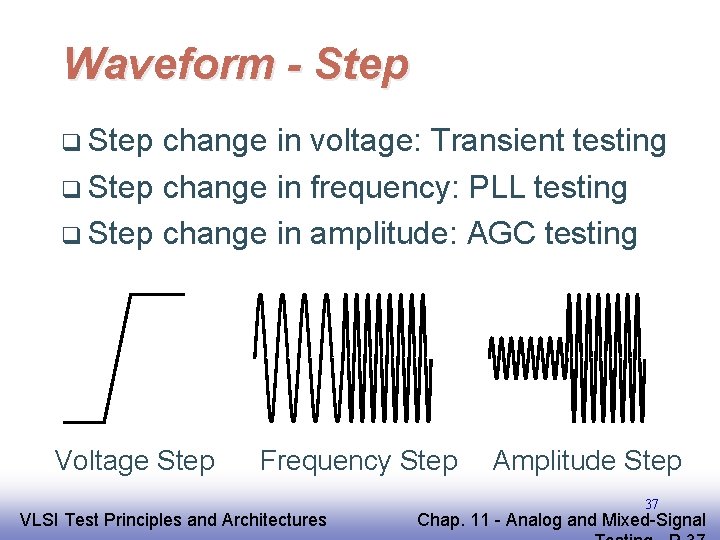

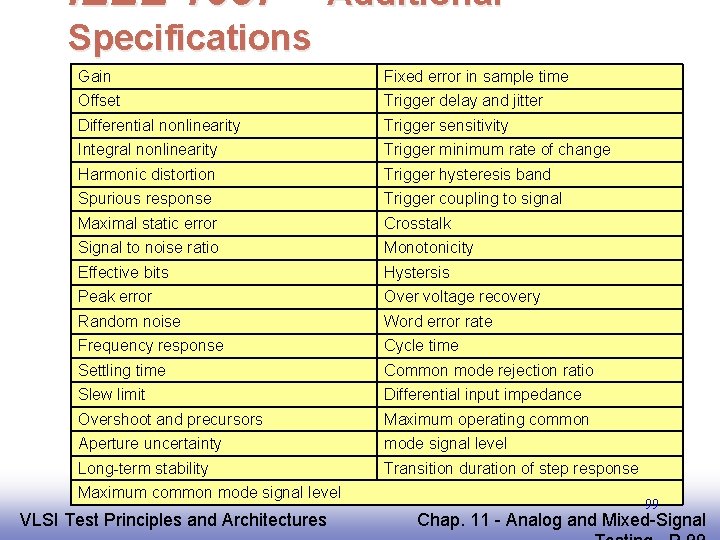

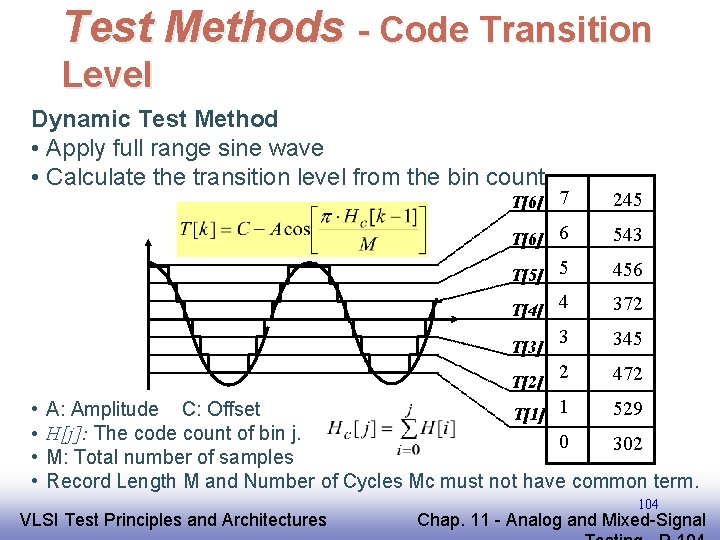

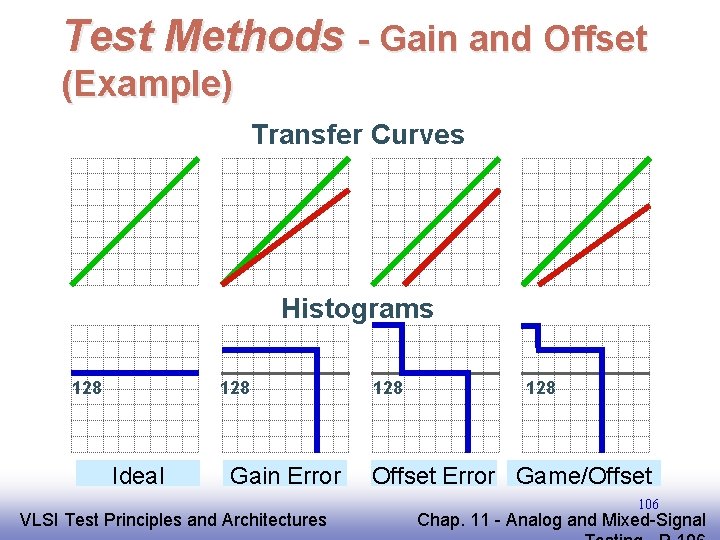

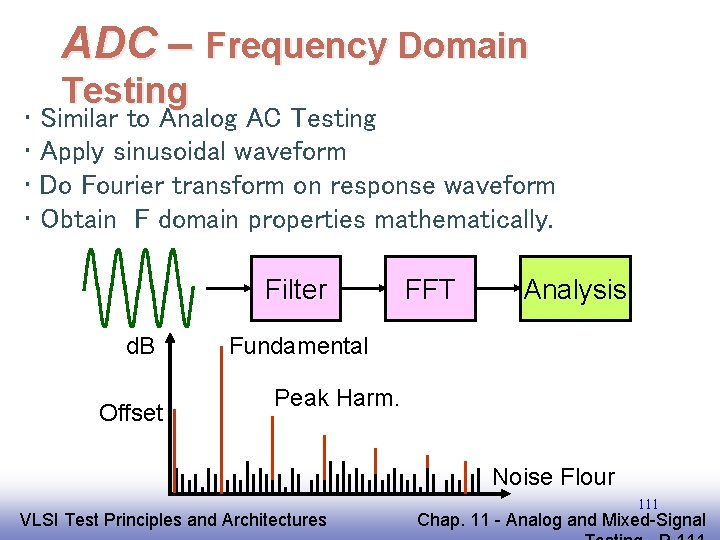

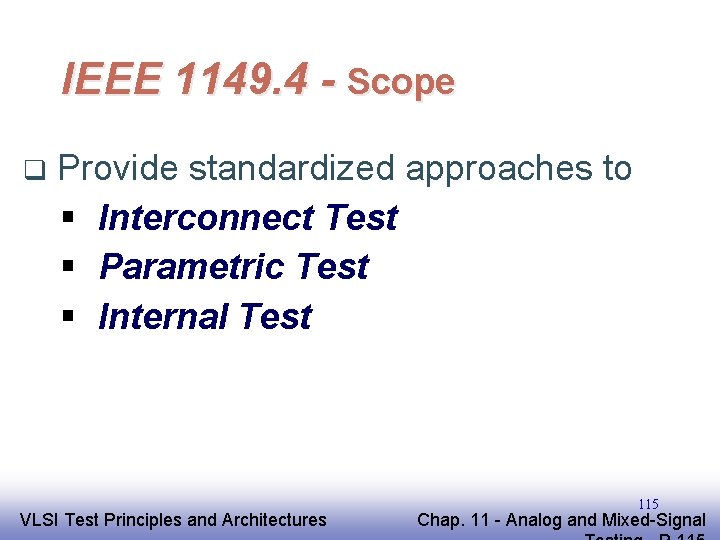

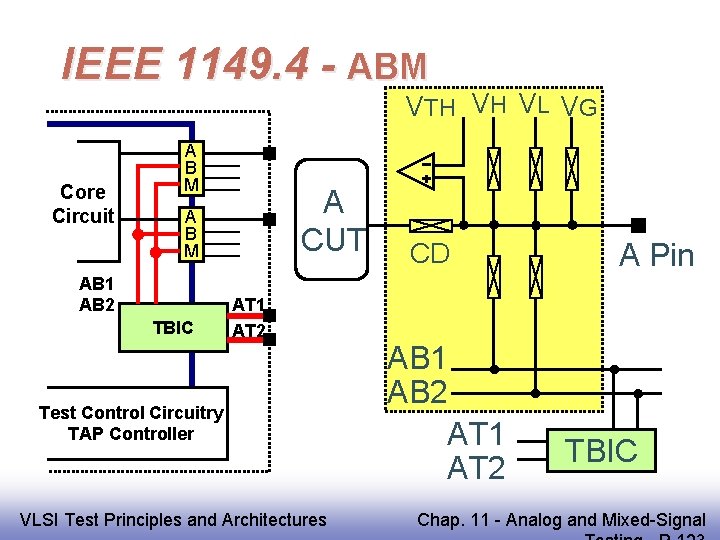

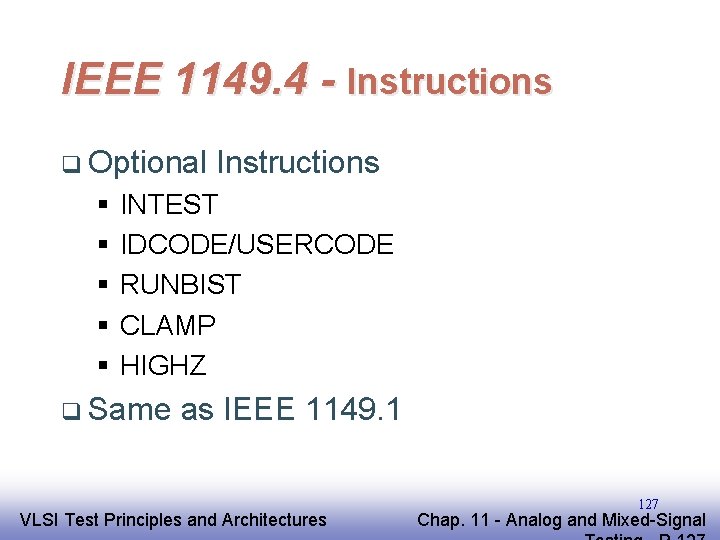

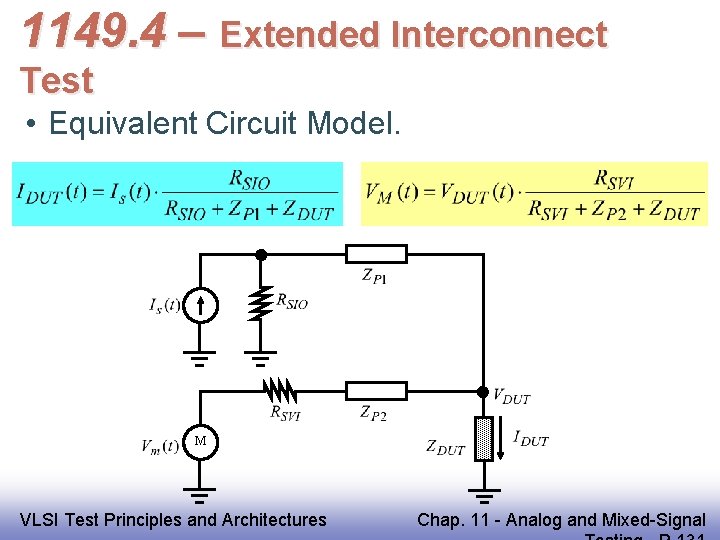

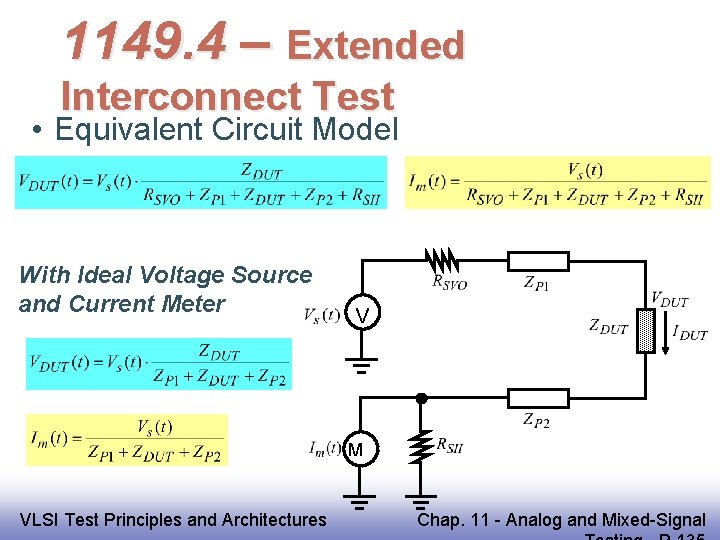

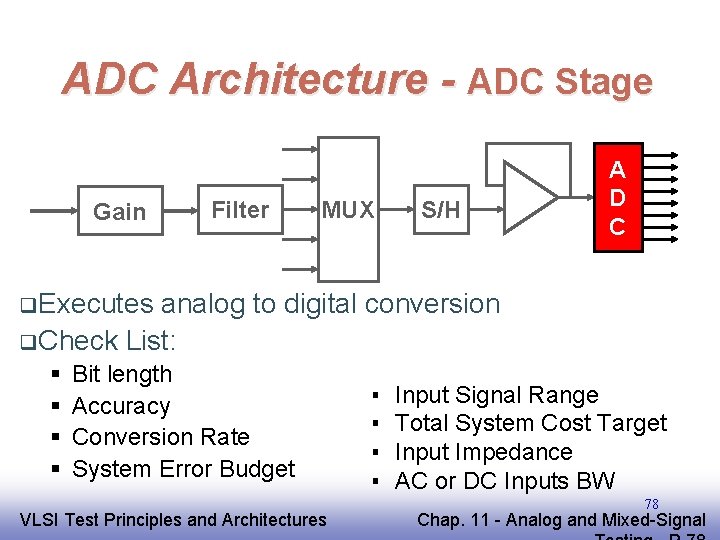

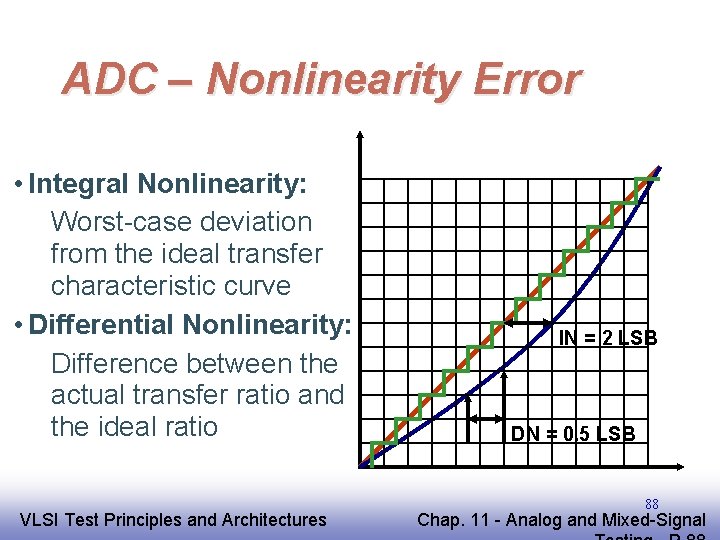

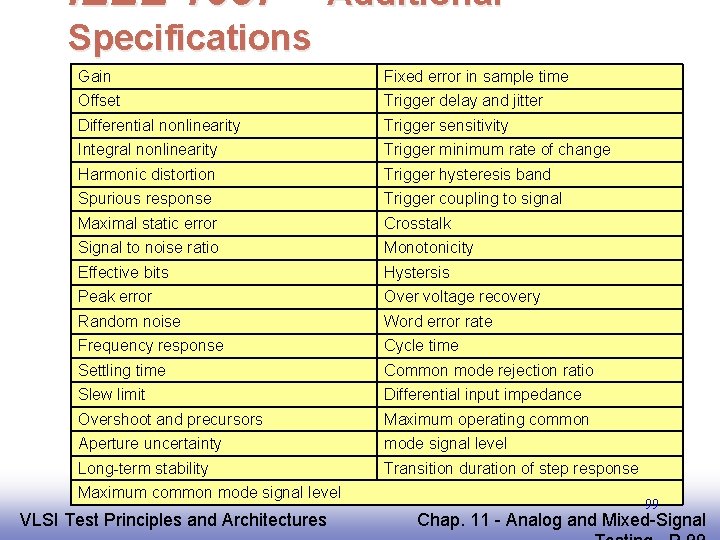

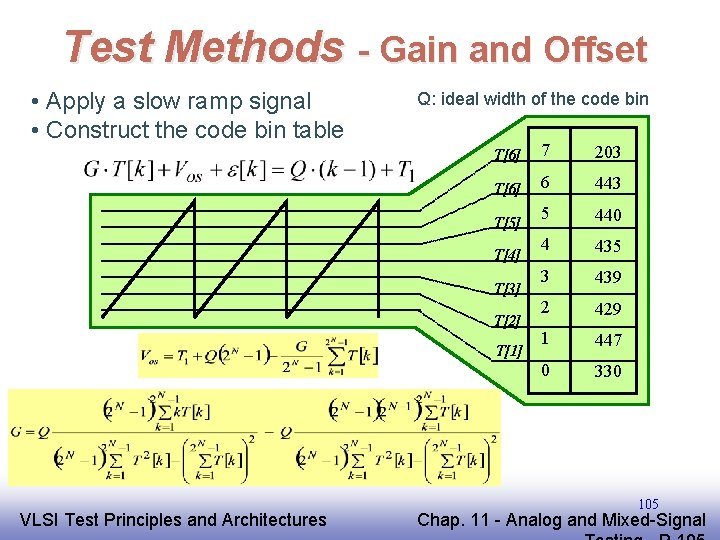

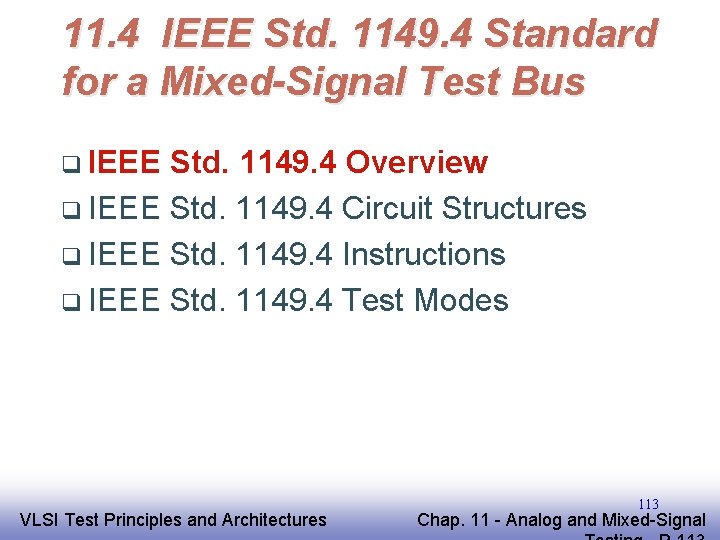

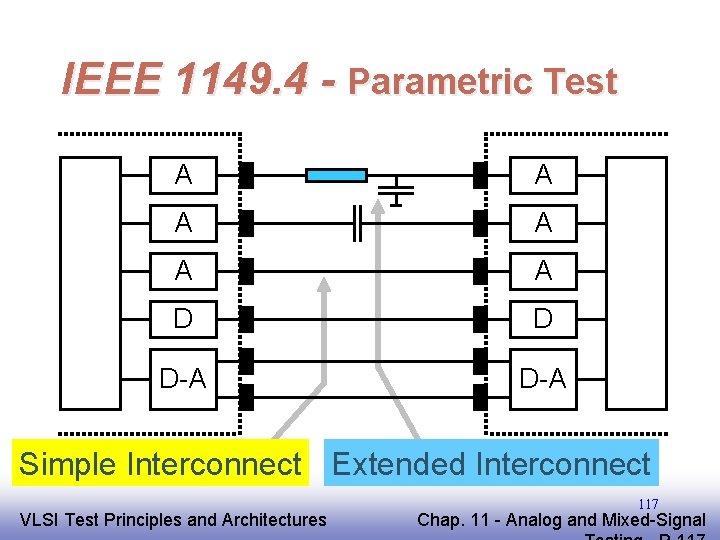

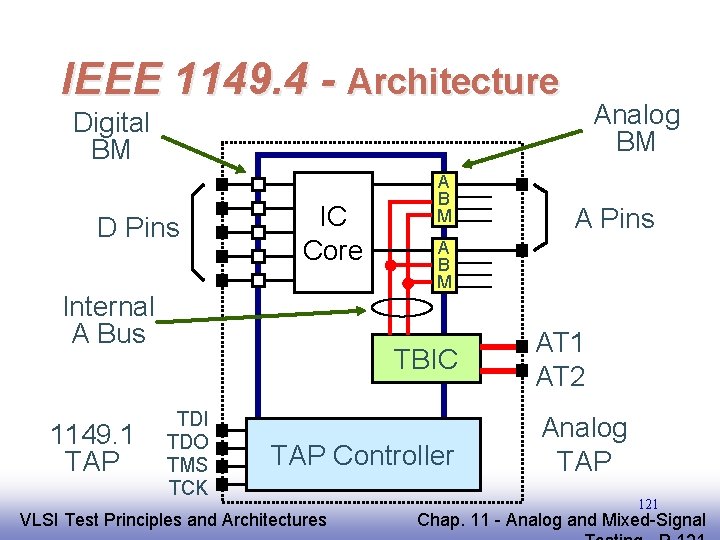

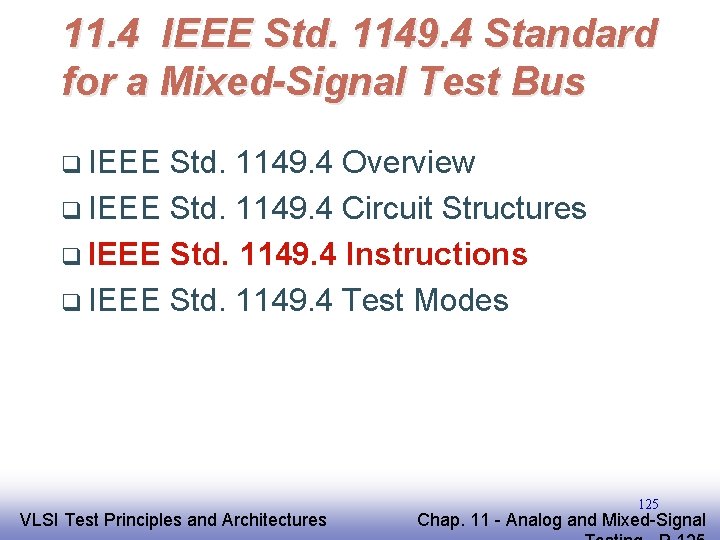

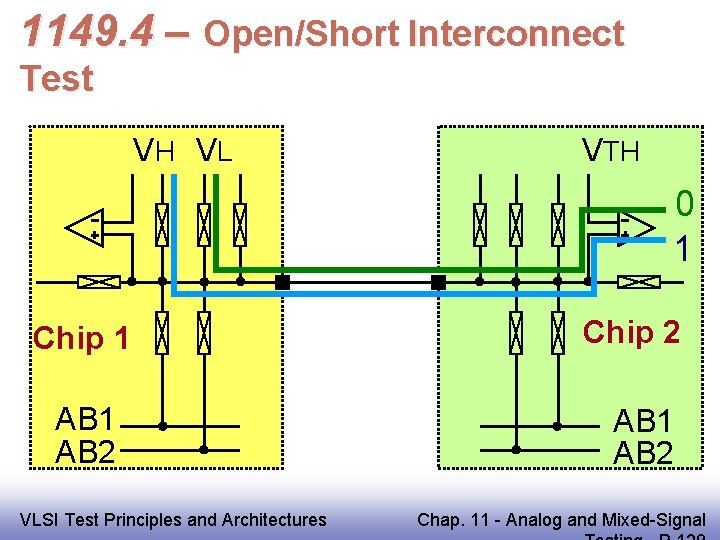

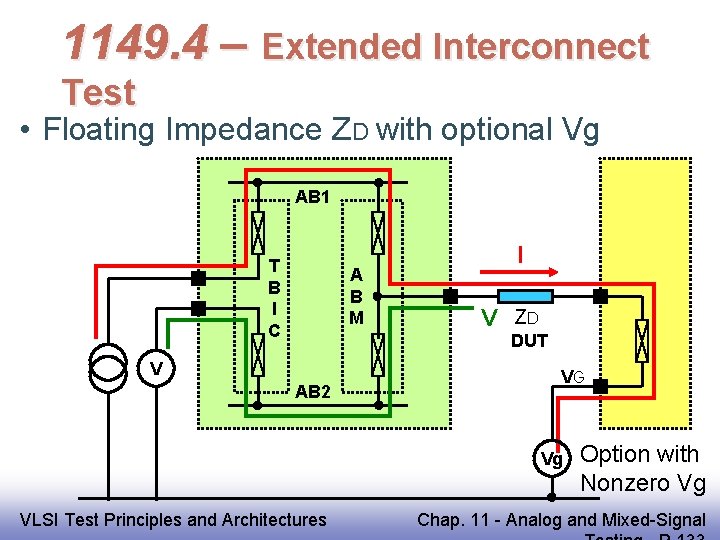

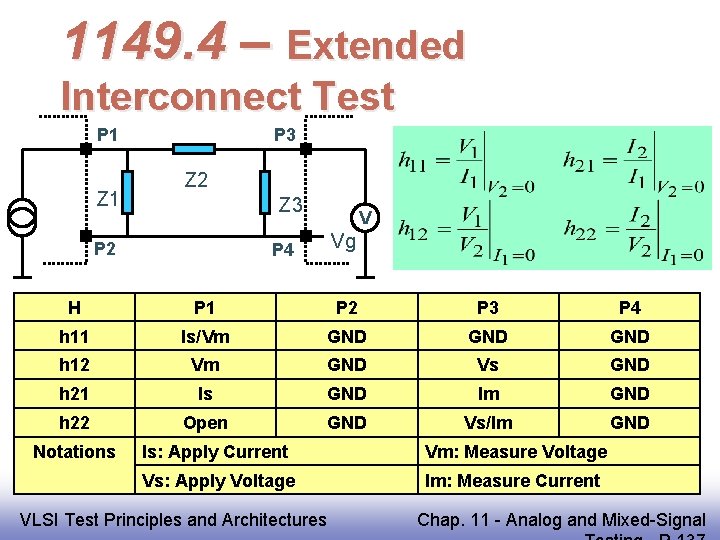

Test Methods - Gain and Offset • Apply a slow ramp signal • Construct the code bin table Q: ideal width of the code bin T[6] 7 203 T[6] 6 443 5 440 4 435 3 439 2 429 1 447 0 330 T[5] T[4] T[3] T[2] T[1] EE 141 VLSI Test Principles and Architectures 105 Chap. 11 - Analog and Mixed-Signal

Test Methods - Gain and Offset (Example) Transfer Curves Histograms 128 Ideal Gain Error EE 141 VLSI Test Principles and Architectures 128 Offset Error Game/Offset 106 Chap. 11 - Analog and Mixed-Signal

![Test Methods Nonlinearity Differential Nonlinearity T6 7 203 T6 6 443 5 440 Test Methods - Nonlinearity Differential Nonlinearity T[6] 7 203 T[6] 6 443 5 440](https://slidetodoc.com/presentation_image_h/904b52feafa99458cd7f28daa7af5486/image-107.jpg)

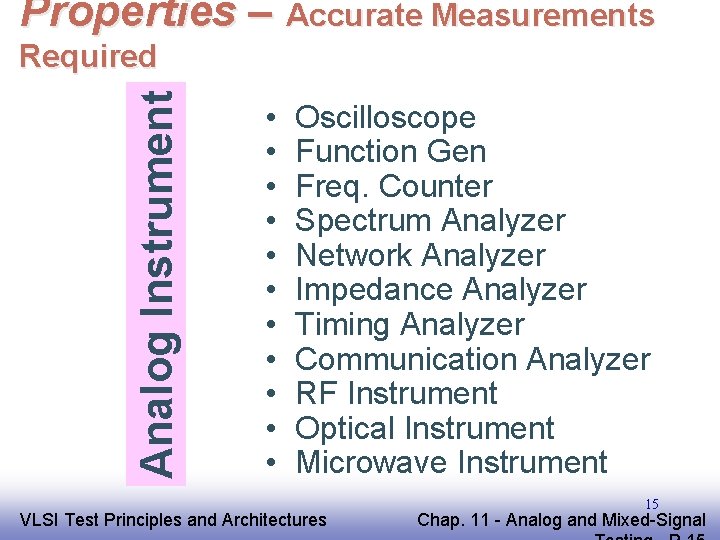

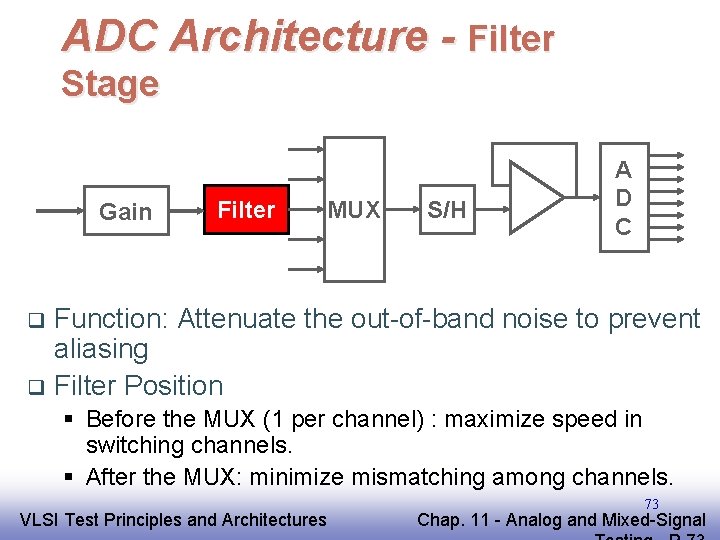

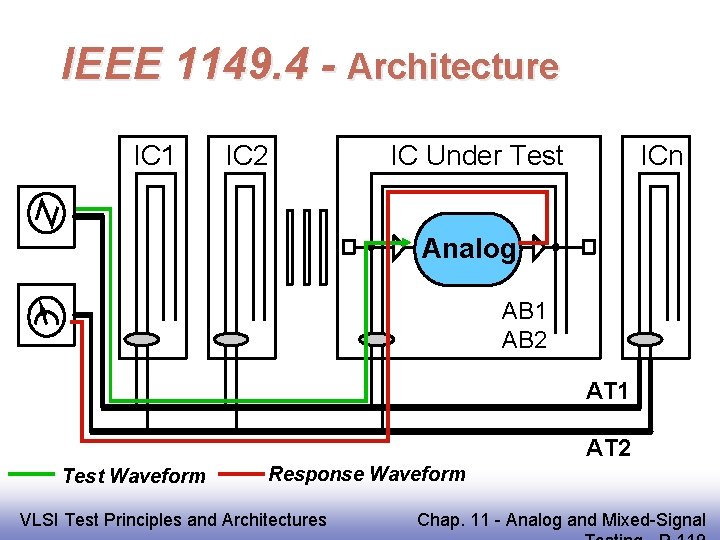

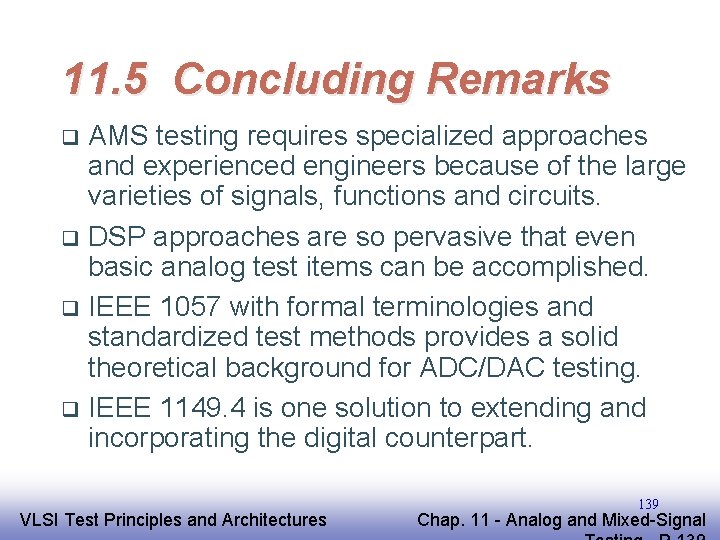

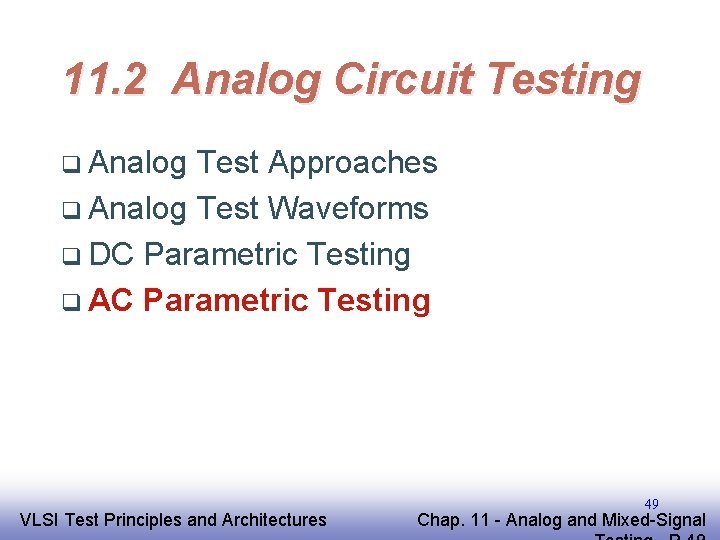

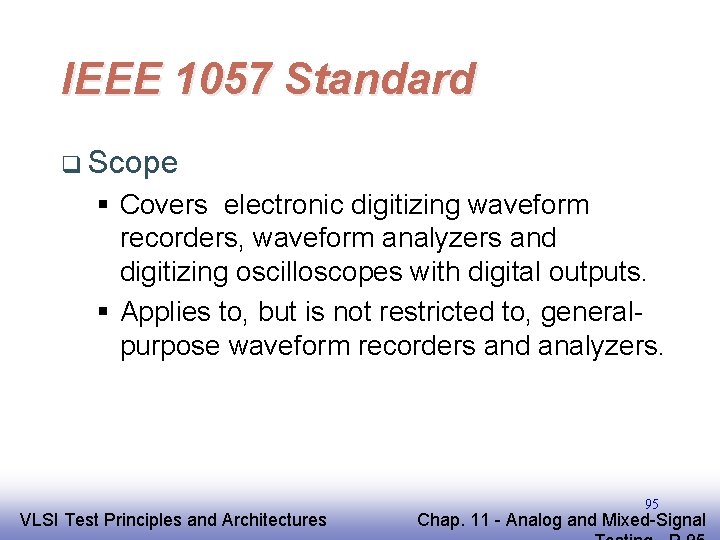

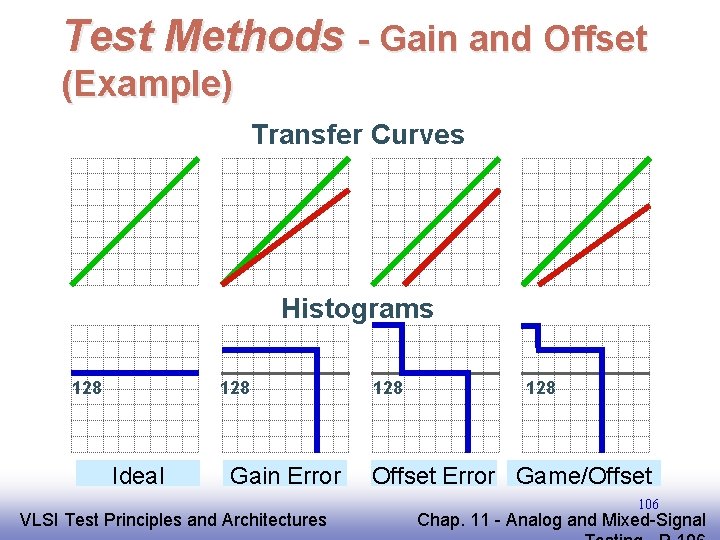

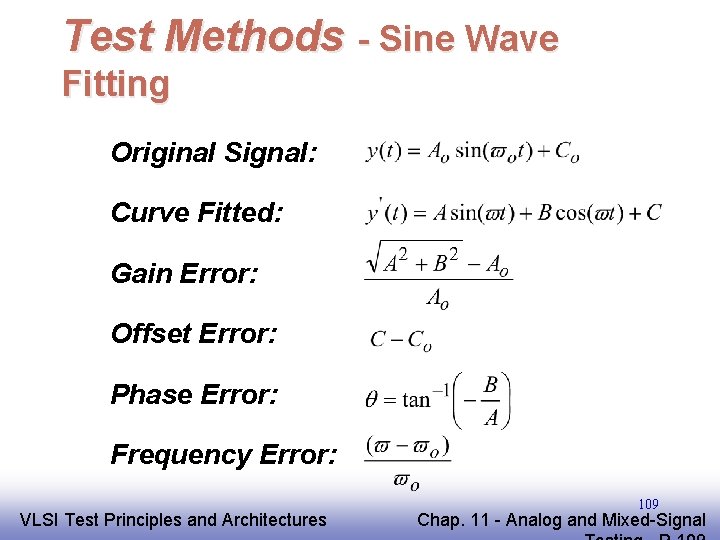

Test Methods - Nonlinearity Differential Nonlinearity T[6] 7 203 T[6] 6 443 5 440 4 435 3 439 2 429 1 447 0 330 T[5] T[4] T[3] T[2] Integral Nonlinearity T[1] Maximal Static Error EE 141 VLSI Test Principles and Architectures 107 Chap. 11 - Analog and Mixed-Signal

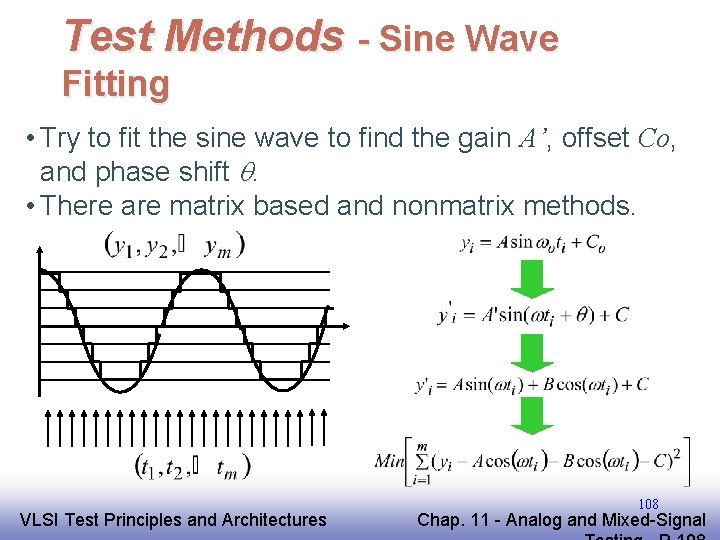

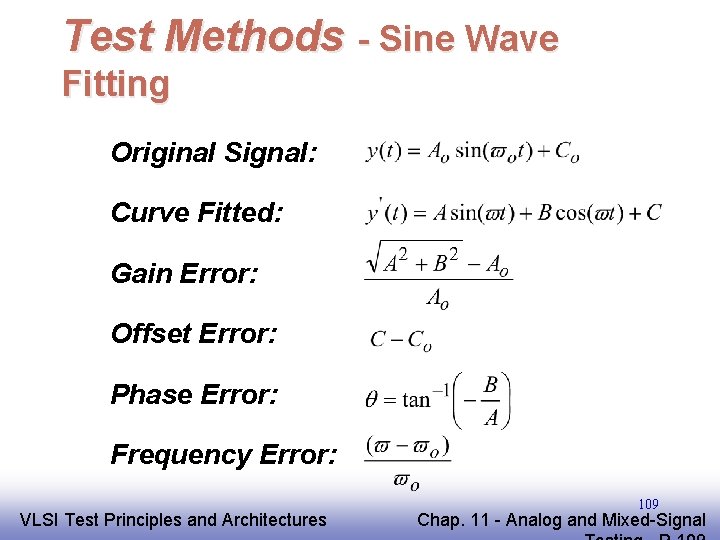

Test Methods - Sine Wave Fitting • Try to fit the sine wave to find the gain A’, offset Co, and phase shift q. • There are matrix based and nonmatrix methods. EE 141 VLSI Test Principles and Architectures 108 Chap. 11 - Analog and Mixed-Signal

Test Methods - Sine Wave Fitting Original Signal: Curve Fitted: Gain Error: Offset Error: Phase Error: Frequency Error: EE 141 VLSI Test Principles and Architectures 109 Chap. 11 - Analog and Mixed-Signal

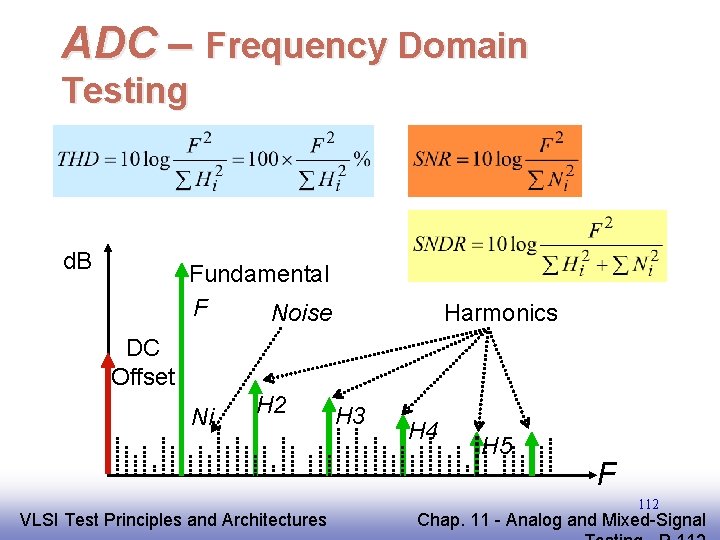

11. 3 Mixed-Signal Testing q Introduction to Analog-Digital Conversion q ADC and DAC Circuit Structure q ADC/DAC Specification and Fault Models q IEEE Std. 1057 q Time-Domain ADC Testing q Frequency-Domain ADC Testing EE 141 VLSI Test Principles and Architectures 110 Chap. 11 - Analog and Mixed-Signal

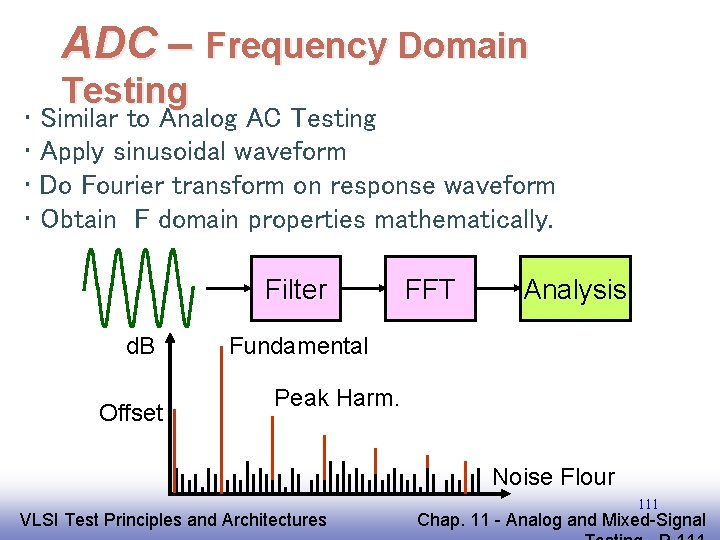

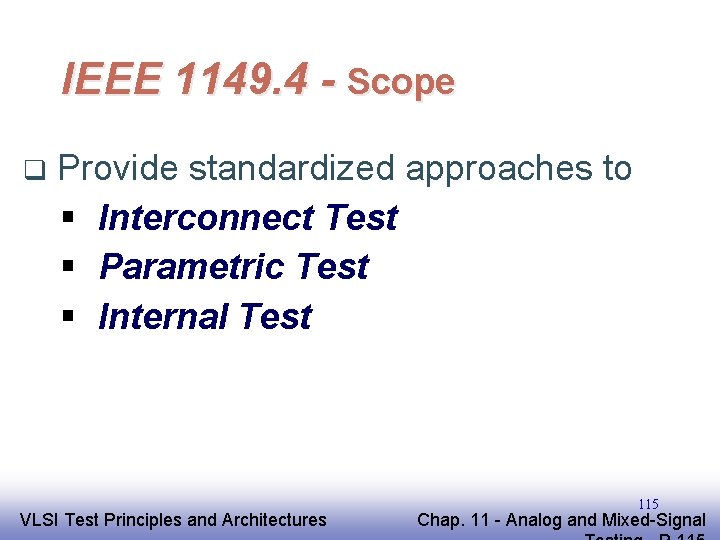

ADC – Frequency Domain • • Testing Similar to Analog AC Testing Apply sinusoidal waveform Do Fourier transform on response waveform Obtain F domain properties mathematically. Filter d. B Offset FFT Analysis Fundamental Peak Harm. Noise Flour EE 141 VLSI Test Principles and Architectures 111 Chap. 11 - Analog and Mixed-Signal

ADC – Frequency Domain Testing d. B Fundamental F Noise Harmonics DC Offset Ni H 2 EE 141 VLSI Test Principles and Architectures H 3 H 4 H 5 F 112 Chap. 11 - Analog and Mixed-Signal

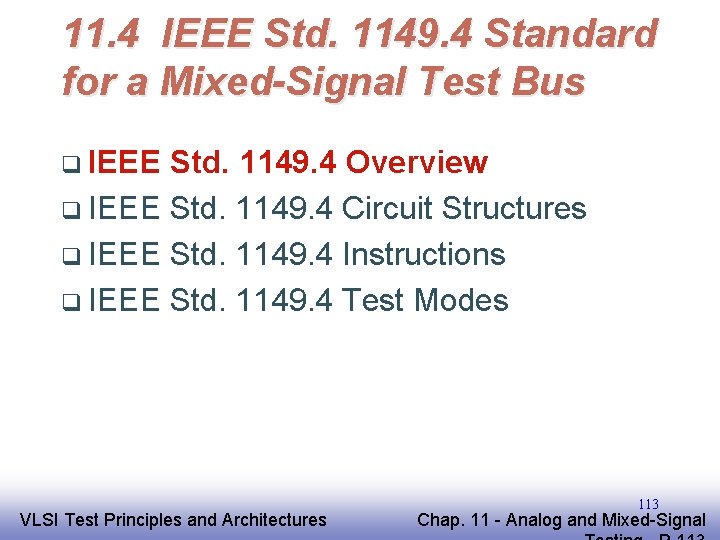

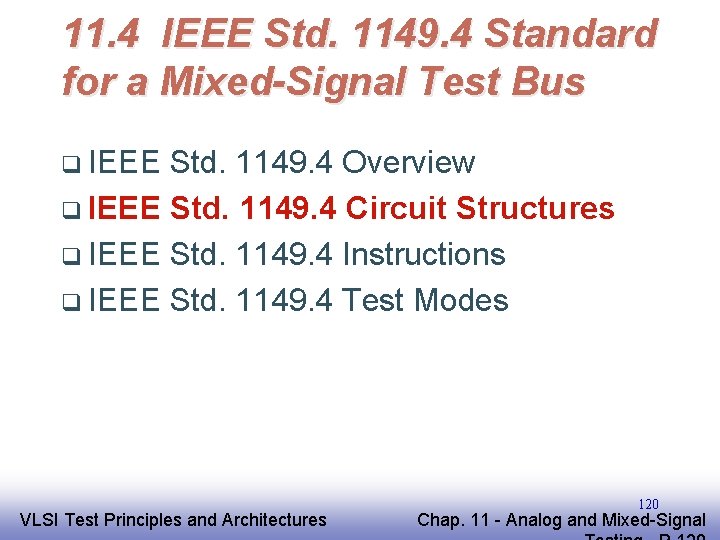

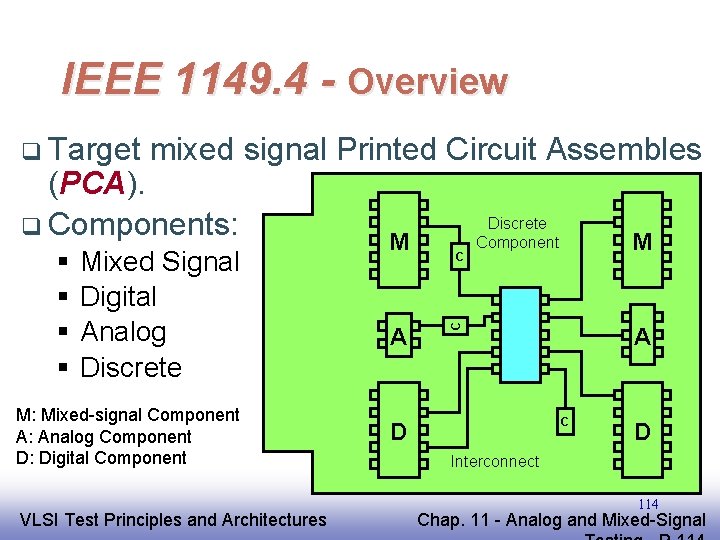

11. 4 IEEE Std. 1149. 4 Standard for a Mixed-Signal Test Bus q IEEE Std. 1149. 4 Overview q IEEE Std. 1149. 4 Circuit Structures q IEEE Std. 1149. 4 Instructions q IEEE Std. 1149. 4 Test Modes EE 141 VLSI Test Principles and Architectures 113 Chap. 11 - Analog and Mixed-Signal

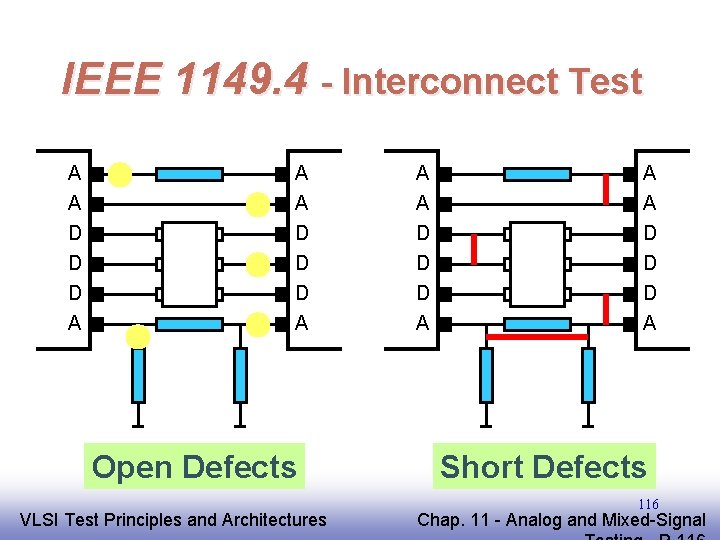

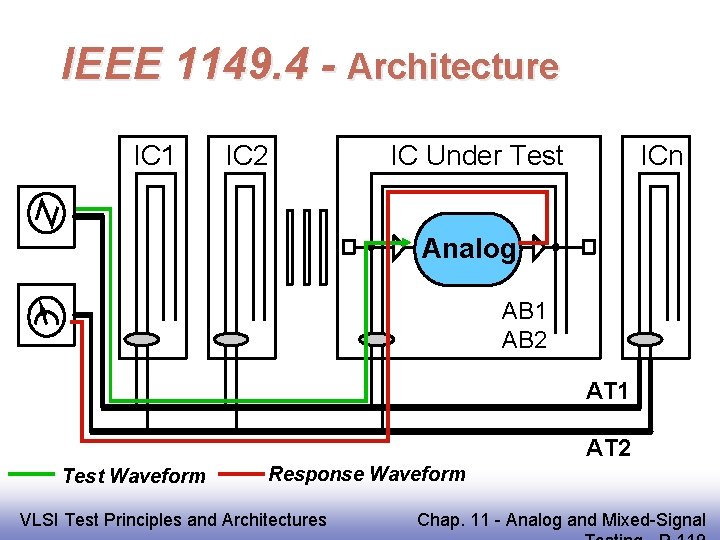

IEEE 1149. 4 - Overview mixed signal Printed Circuit Assembles (PCA). q Components: § § Mixed Signal Digital Analog Discrete M: Mixed-signal Component A: Analog Component D: Digital Component EE 141 VLSI Test Principles and Architectures M A C Discrete Component M C q Target A C D D Interconnect 114 Chap. 11 - Analog and Mixed-Signal

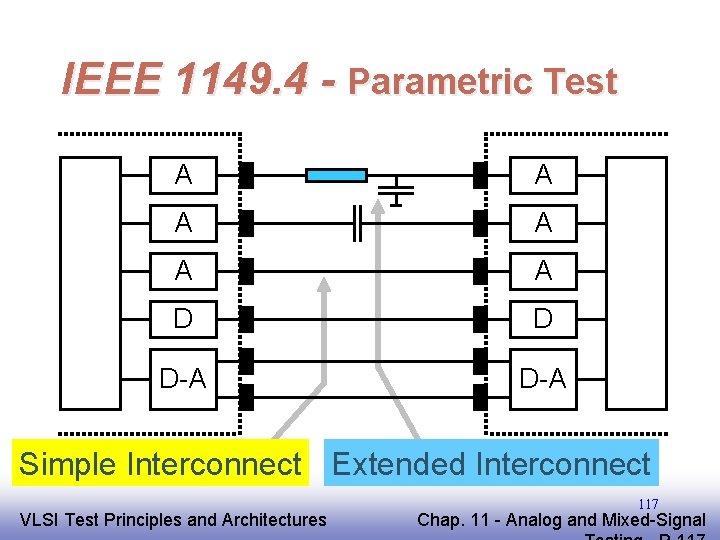

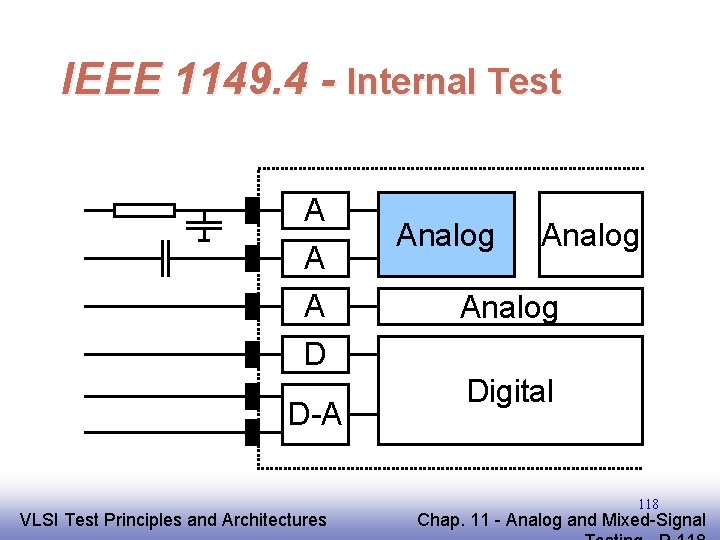

IEEE 1149. 4 - Scope q Provide standardized approaches to § Interconnect Test § Parametric Test § Internal Test EE 141 VLSI Test Principles and Architectures 115 Chap. 11 - Analog and Mixed-Signal

IEEE 1149. 4 - Interconnect Test A A A A D D D A Open Defects EE 141 VLSI Test Principles and Architectures Short Defects 116 Chap. 11 - Analog and Mixed-Signal

IEEE 1149. 4 - Parametric Test A A A D D D-A Simple Interconnect Extended Interconnect EE 141 VLSI Test Principles and Architectures 117 Chap. 11 - Analog and Mixed-Signal

IEEE 1149. 4 - Internal Test A A A D D-A EE 141 VLSI Test Principles and Architectures Analog Digital 118 Chap. 11 - Analog and Mixed-Signal

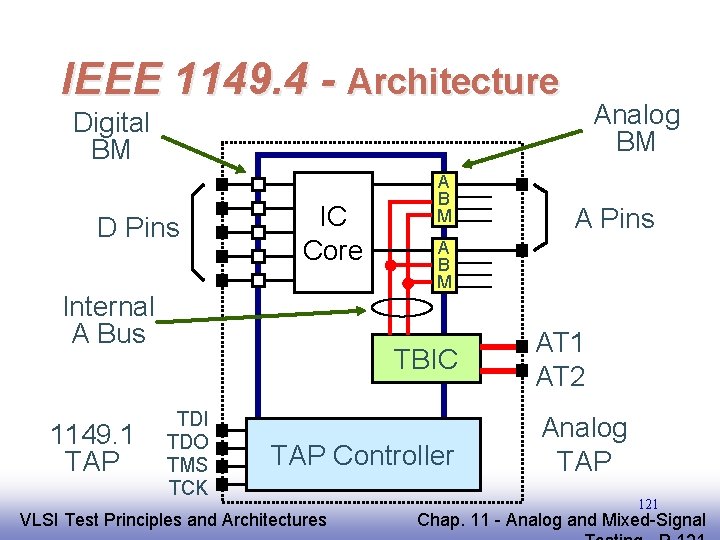

IEEE 1149. 4 - Architecture IC 1 IC 2 IC Under Test ICn Analog AB 1 AB 2 AT 1 AT 2 Test Waveform Response Waveform EE 141 VLSI Test Principles and Architectures Chap. 11 - Analog and Mixed-Signal

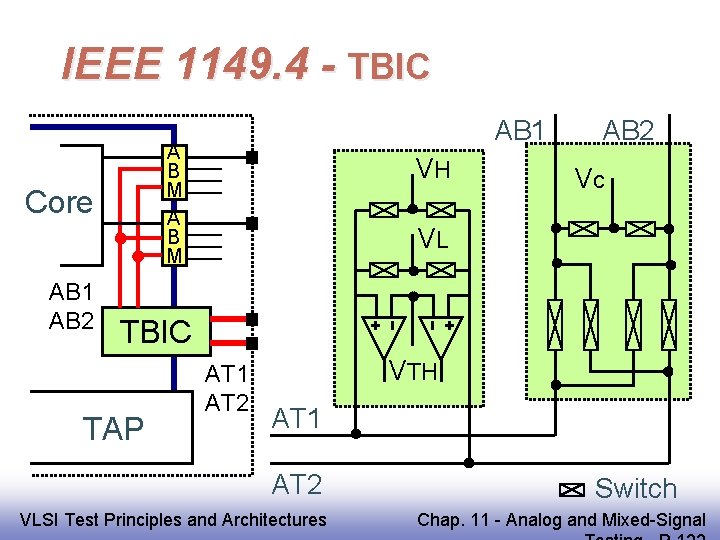

11. 4 IEEE Std. 1149. 4 Standard for a Mixed-Signal Test Bus q IEEE Std. 1149. 4 Overview q IEEE Std. 1149. 4 Circuit Structures q IEEE Std. 1149. 4 Instructions q IEEE Std. 1149. 4 Test Modes EE 141 VLSI Test Principles and Architectures 120 Chap. 11 - Analog and Mixed-Signal

IEEE 1149. 4 - Architecture Analog BM Digital BM D Pins IC Core Internal A Bus 1149. 1 TAP A B M TBIC TDI TDO TMS TCK TAP Controller EE 141 VLSI Test Principles and Architectures A Pins AT 1 AT 2 Analog TAP 121 Chap. 11 - Analog and Mixed-Signal

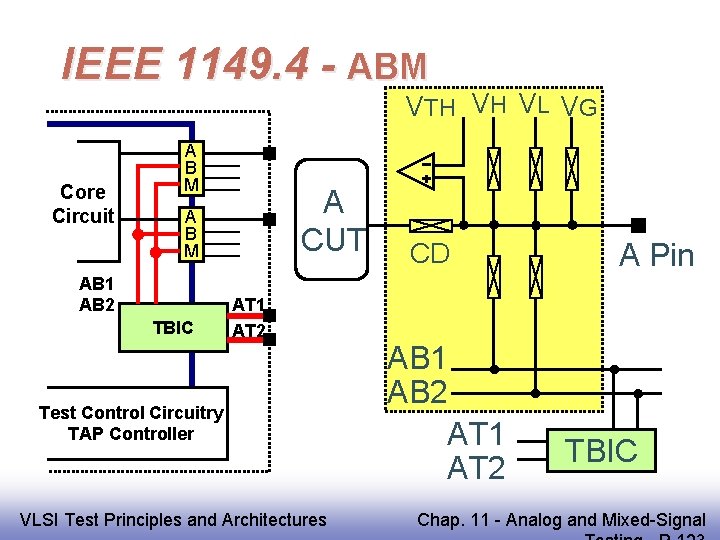

IEEE 1149. 4 - TBIC A B M Core AB 1 AB 2 AB 1 VH AB 2 Vc VL TBIC TAP AT 1 AT 2 VTH AT 1 AT 2 EE 141 VLSI Test Principles and Architectures Switch Chap. 11 - Analog and Mixed-Signal

IEEE 1149. 4 - ABM VTH VH VL VG Core Circuit A B M A CUT A B M AB 1 AB 2 TBIC AT 1 AT 2 Test Control Circuitry TAP Controller EE 141 VLSI Test Principles and Architectures CD AB 1 AB 2 AT 1 AT 2 A Pin TBIC Chap. 11 - Analog and Mixed-Signal

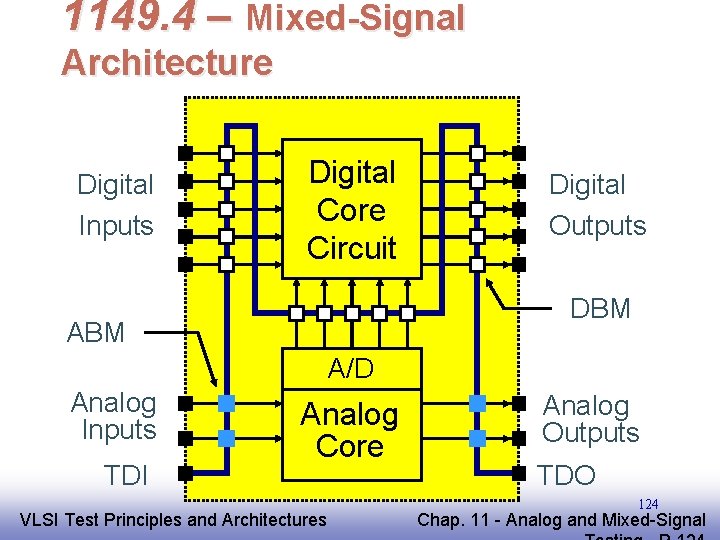

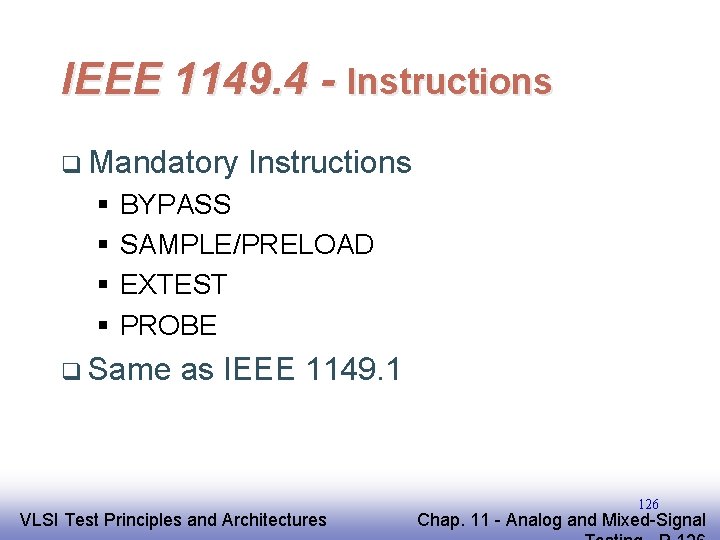

1149. 4 – Mixed-Signal Architecture Digital Inputs Digital Core Circuit Digital Outputs DBM A/D Analog Inputs TDI Analog Core EE 141 VLSI Test Principles and Architectures Analog Outputs TDO 124 Chap. 11 - Analog and Mixed-Signal

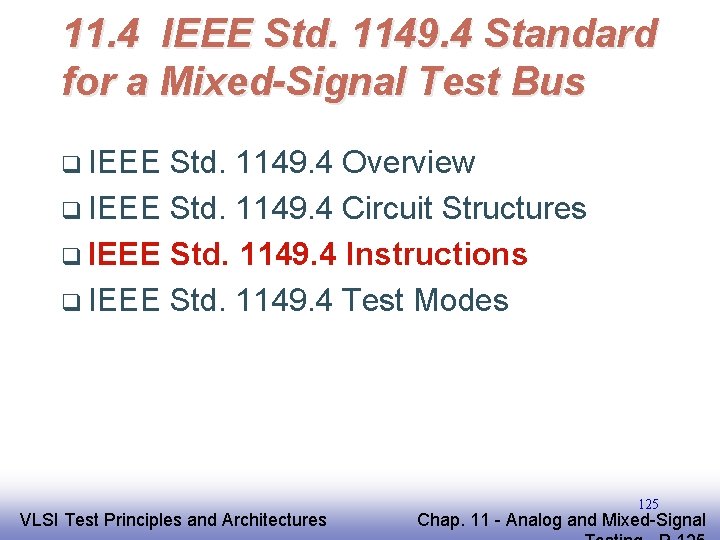

11. 4 IEEE Std. 1149. 4 Standard for a Mixed-Signal Test Bus q IEEE Std. 1149. 4 Overview q IEEE Std. 1149. 4 Circuit Structures q IEEE Std. 1149. 4 Instructions q IEEE Std. 1149. 4 Test Modes EE 141 VLSI Test Principles and Architectures 125 Chap. 11 - Analog and Mixed-Signal

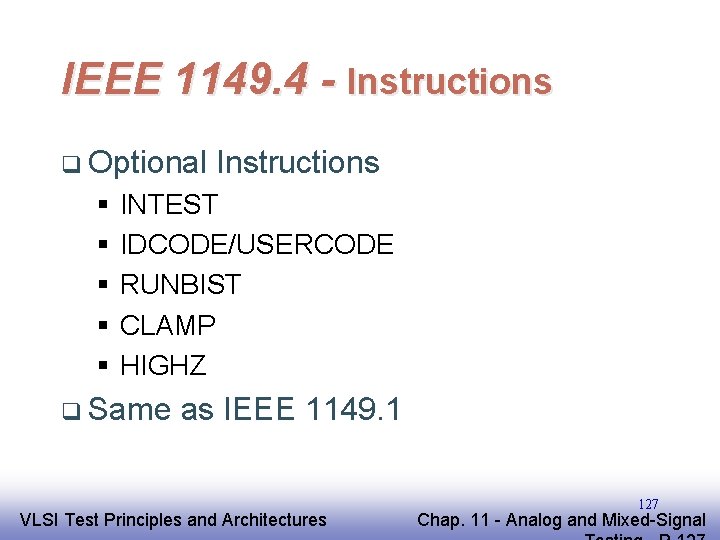

IEEE 1149. 4 - Instructions q Mandatory § § Instructions BYPASS SAMPLE/PRELOAD EXTEST PROBE q Same as IEEE 1149. 1 EE 141 VLSI Test Principles and Architectures 126 Chap. 11 - Analog and Mixed-Signal

IEEE 1149. 4 - Instructions q Optional § § § Instructions INTEST IDCODE/USERCODE RUNBIST CLAMP HIGHZ q Same as IEEE 1149. 1 EE 141 VLSI Test Principles and Architectures 127 Chap. 11 - Analog and Mixed-Signal

11. 4 IEEE Std. 1149. 4 Standard for a Mixed-Signal Test Bus q IEEE Std. 1149. 4 Overview q IEEE Std. 1149. 4 Circuit Structures q IEEE Std. 1149. 4 Instructions q IEEE Std. 1149. 4 Test Modes EE 141 VLSI Test Principles and Architectures 128 Chap. 11 - Analog and Mixed-Signal

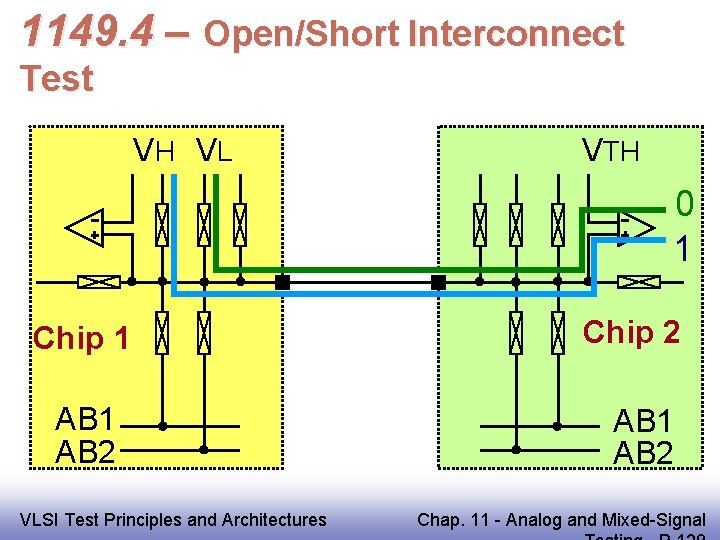

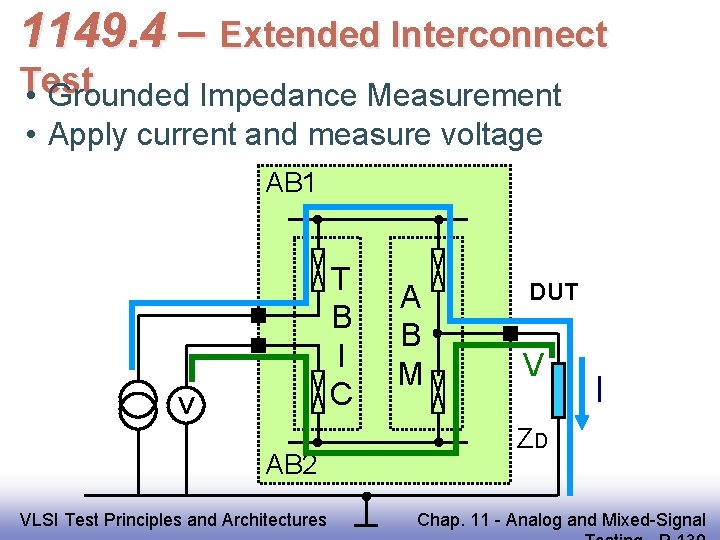

1149. 4 – Open/Short Interconnect Test VH VL VTH 0 1 Chip 1 AB 2 EE 141 VLSI Test Principles and Architectures Chip 2 AB 1 AB 2 Chap. 11 - Analog and Mixed-Signal

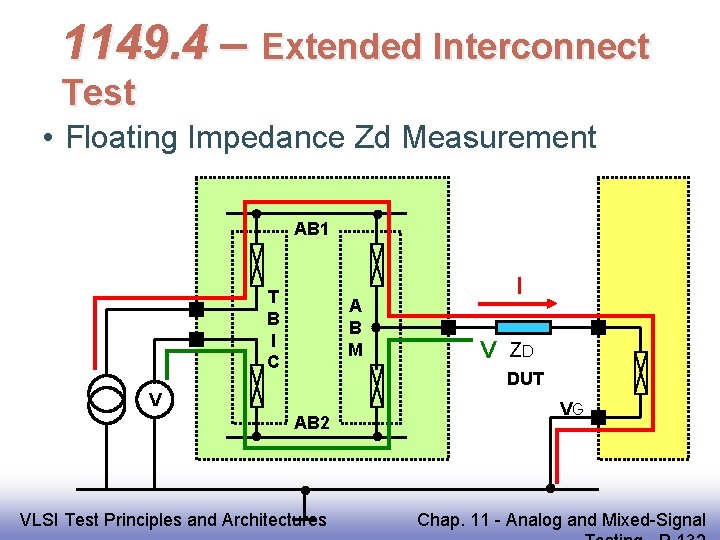

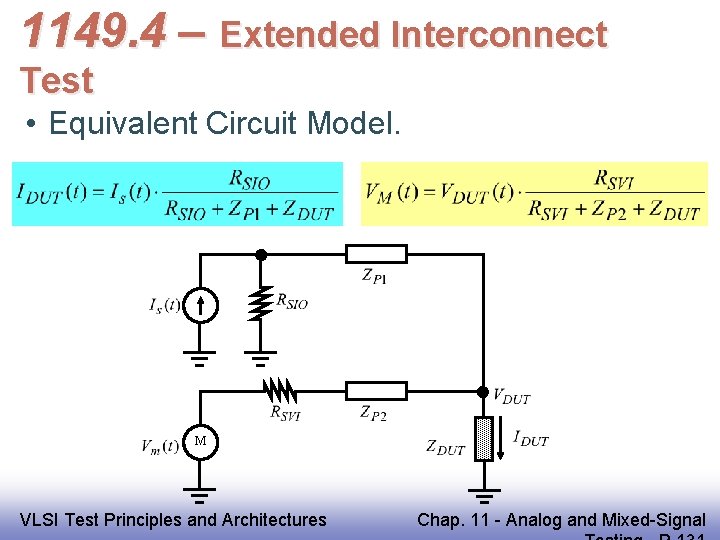

1149. 4 – Extended Interconnect Test • Grounded Impedance Measurement • Apply current and measure voltage AB 1 T B I C V AB 2 EE 141 VLSI Test Principles and Architectures A B M DUT V I ZD Chap. 11 - Analog and Mixed-Signal

1149. 4 – Extended Interconnect Test • Equivalent Circuit Model. M EE 141 VLSI Test Principles and Architectures Chap. 11 - Analog and Mixed-Signal

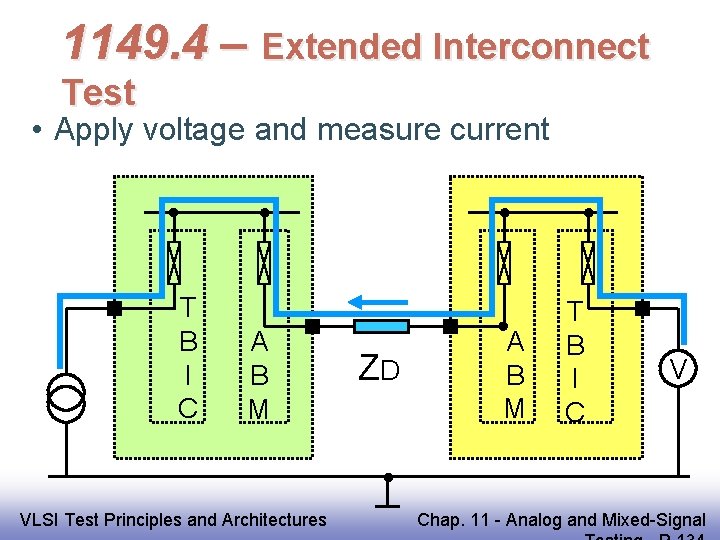

1149. 4 – Extended Interconnect Test • Floating Impedance Zd Measurement AB 1 T B I C A B M I V ZD DUT V AB 2 EE 141 VLSI Test Principles and Architectures VG Chap. 11 - Analog and Mixed-Signal

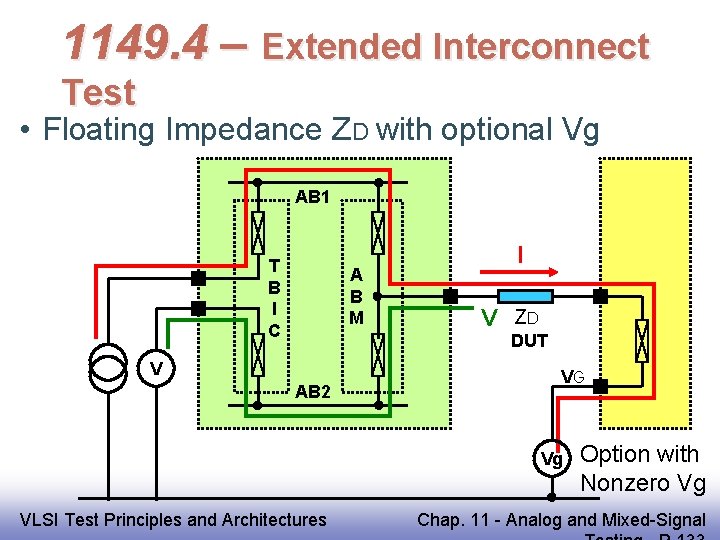

1149. 4 – Extended Interconnect Test • Floating Impedance ZD with optional Vg AB 1 T B I C A B M I V ZD DUT V AB 2 VG Vg EE 141 VLSI Test Principles and Architectures Option with Nonzero Vg Chap. 11 - Analog and Mixed-Signal

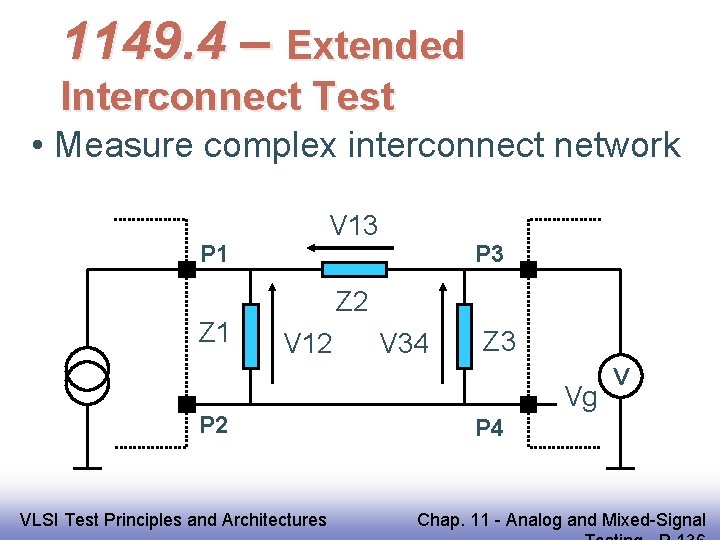

1149. 4 – Extended Interconnect Test • Apply voltage and measure current T B I C A B M EE 141 VLSI Test Principles and Architectures ZD A B M T B I C V Chap. 11 - Analog and Mixed-Signal

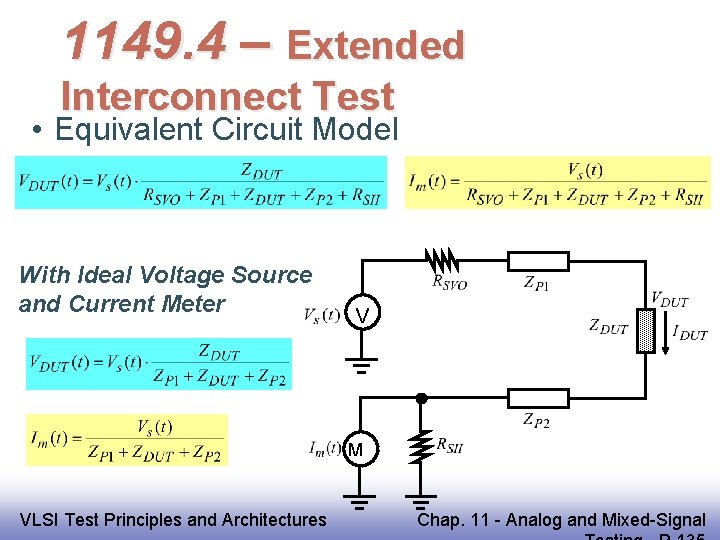

1149. 4 – Extended Interconnect Test • Equivalent Circuit Model With Ideal Voltage Source and Current Meter V M EE 141 VLSI Test Principles and Architectures Chap. 11 - Analog and Mixed-Signal

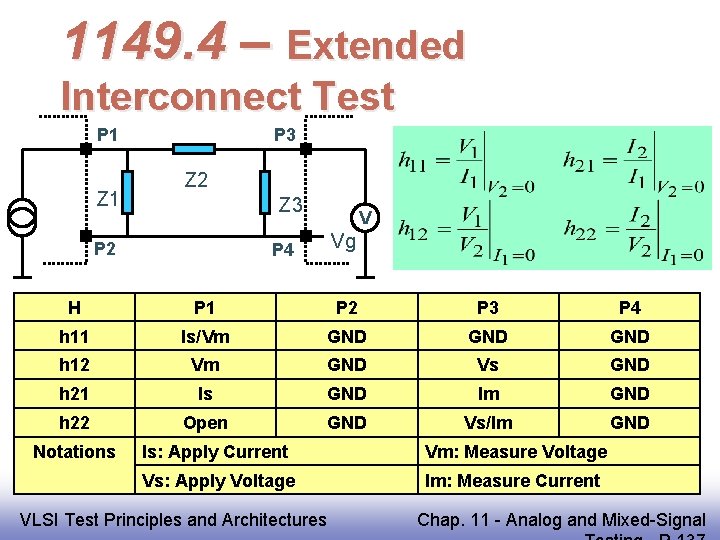

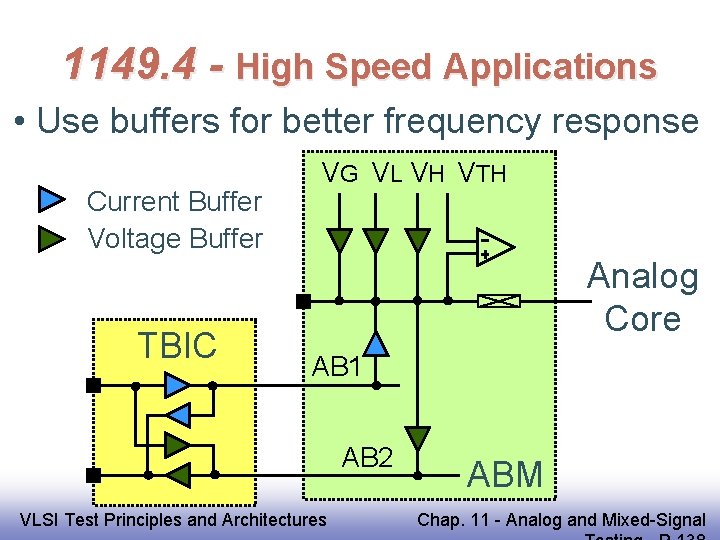

1149. 4 – Extended Interconnect Test • Measure complex interconnect network V 13 P 1 Z 1 P 3 Z 2 V 12 V 34 Z 3 Vg P 2 EE 141 VLSI Test Principles and Architectures V P 4 Chap. 11 - Analog and Mixed-Signal

1149. 4 – Extended Interconnect Test P 1 Z 1 P 3 Z 2 Z 3 P 2 P 4 V Vg H P 1 P 2 P 3 P 4 h 11 Is/Vm GND GND h 12 Vm GND Vs GND h 21 Is GND Im GND h 22 Open GND Vs/Im GND Notations Is: Apply Current Vm: Measure Voltage Vs: Apply Voltage Im: Measure Current EE 141 VLSI Test Principles and Architectures Chap. 11 - Analog and Mixed-Signal

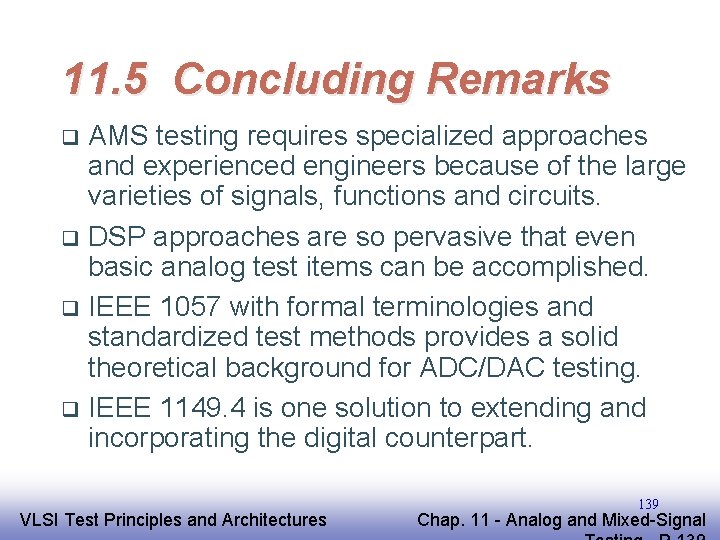

1149. 4 - High Speed Applications • Use buffers for better frequency response Current Buffer Voltage Buffer TBIC VG VL VH VTH Analog Core AB 1 AB 2 EE 141 VLSI Test Principles and Architectures ABM Chap. 11 - Analog and Mixed-Signal

11. 5 Concluding Remarks AMS testing requires specialized approaches and experienced engineers because of the large varieties of signals, functions and circuits. q DSP approaches are so pervasive that even basic analog test items can be accomplished. q IEEE 1057 with formal terminologies and standardized test methods provides a solid theoretical background for ADC/DAC testing. q IEEE 1149. 4 is one solution to extending and incorporating the digital counterpart. q EE 141 VLSI Test Principles and Architectures 139 Chap. 11 - Analog and Mixed-Signal