DARE SET SIMULATION FLOW INTEGRATED IN VIRTUOSO ADE

- Slides: 26

DARE SET SIMULATION FLOW INTEGRATED IN VIRTUOSO ADE L/XL DESIGN ENVIRONMENT STAF VERHAEGEN AMICSA 2018, LEUVEN PUBLIC

DARE SET SIMULATION FLOW INTEGRATED IN VIRTUOSO ADE L/XL DESIGN ENVIRONMENT STAFwith VERHAEGEN Also compatible ADE Explorer/Assembler AMICSA 2018, LEUVEN PUBLIC

OVERVIEW § SET § Wish List § History § Wrap-Up 3 AMICSA 2018

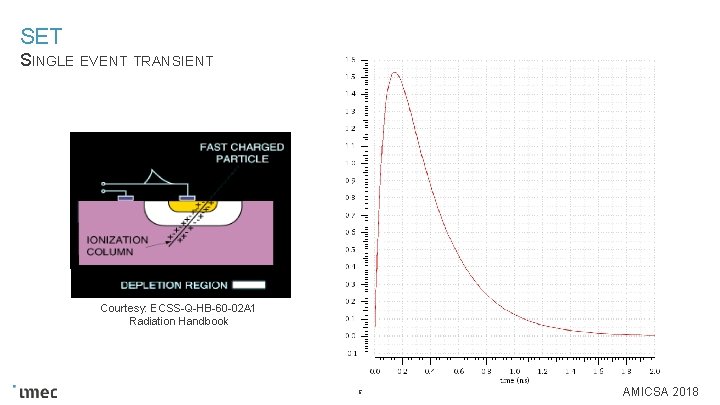

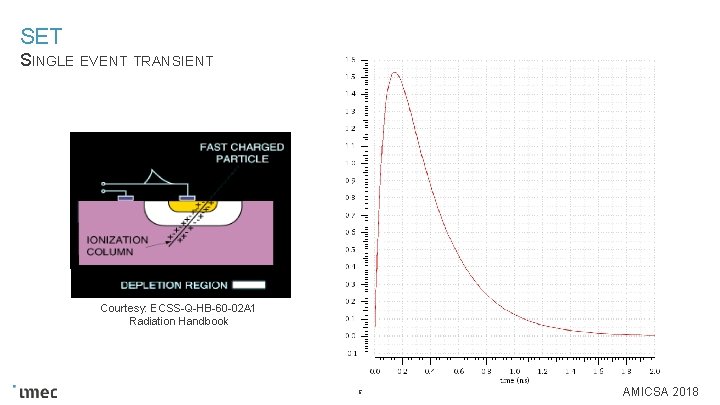

SET

SET SINGLE EVENT TRANSIENT Courtesy: ECSS-Q-HB-60 -02 A 1 Radiation Handbook 5 AMICSA 2018

WISH LIST

WISH LIST § Easy SET injection on nodes in a circuit § Integrated in analog design flow § No changes needed on circuit to investigate § Flexible timing of generated events § Fit in design exploration, SET screening phase § Fit in circuit SET hardening phase 7 AMICSA 2018

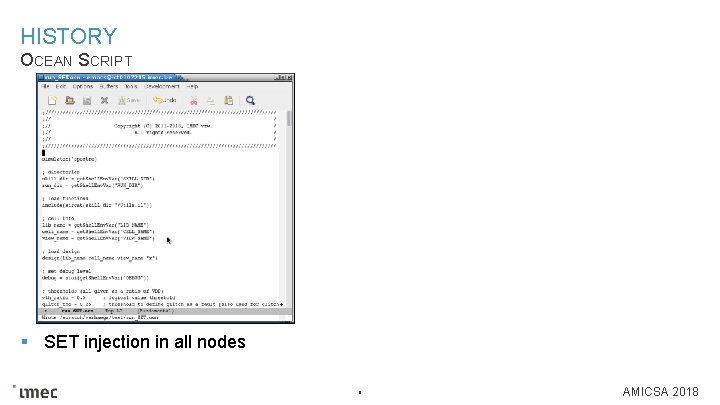

HISTORY

HISTORY OCEAN SCRIPT § SET injection in all nodes 9 AMICSA 2018

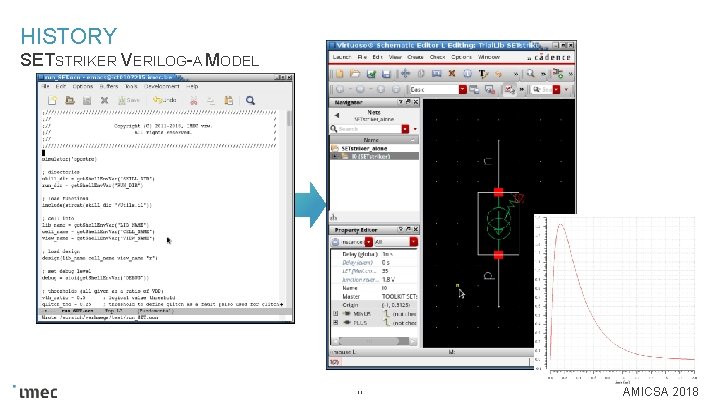

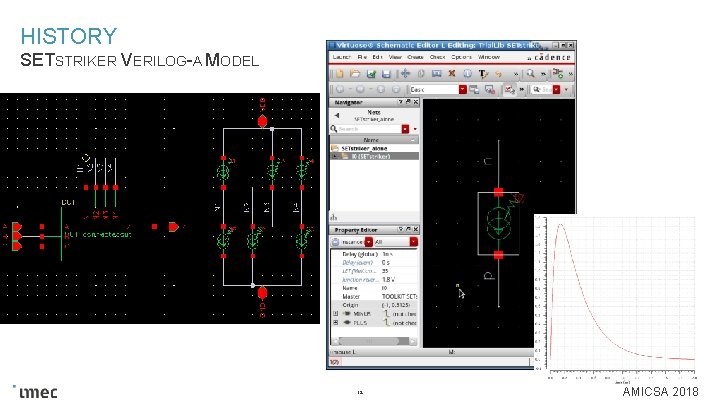

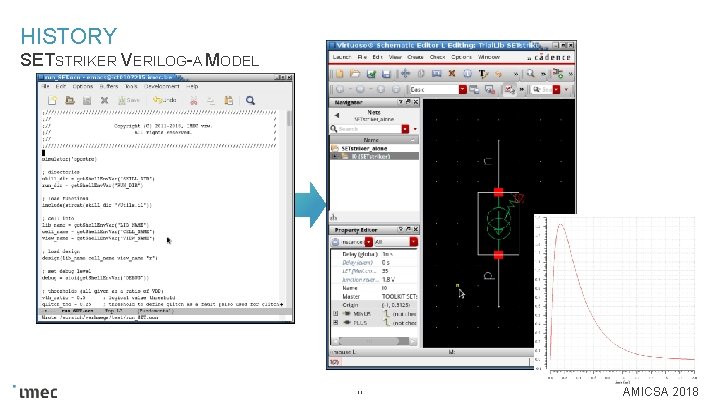

HISTORY SETSTRIKER VERILOG-A MODEL • Not integrated in Virtuoso ADE flow 10 AMICSA 2018

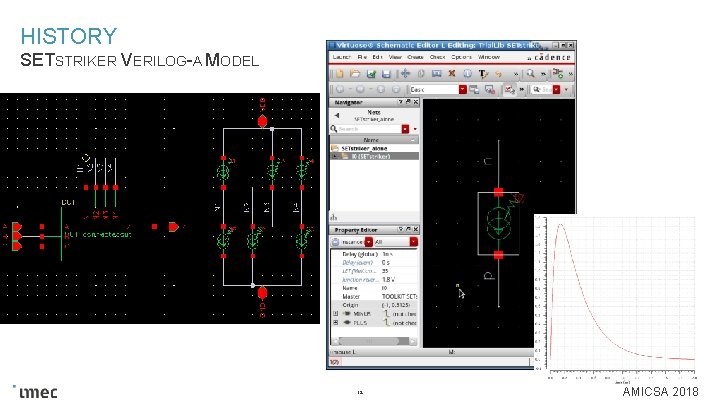

HISTORY SETSTRIKER VERILOG-A MODEL 11 AMICSA 2018

HISTORY SETSTRIKER VERILOG-A MODEL 12 AMICSA 2018

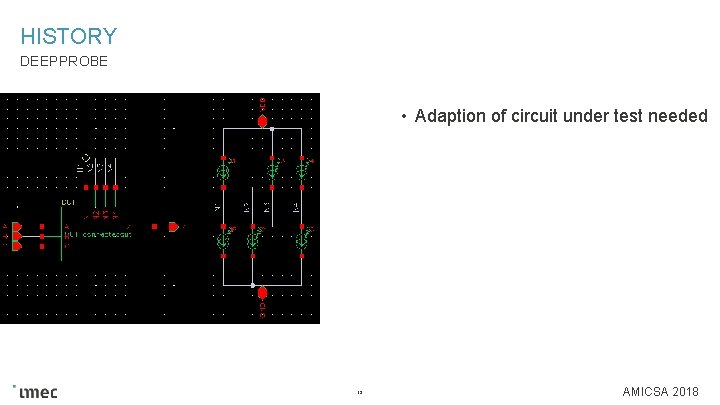

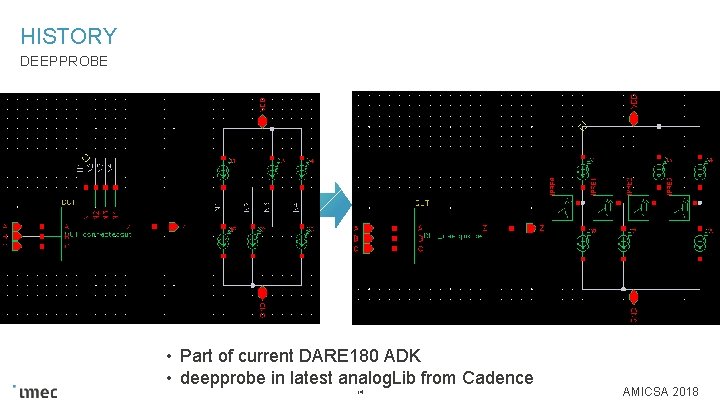

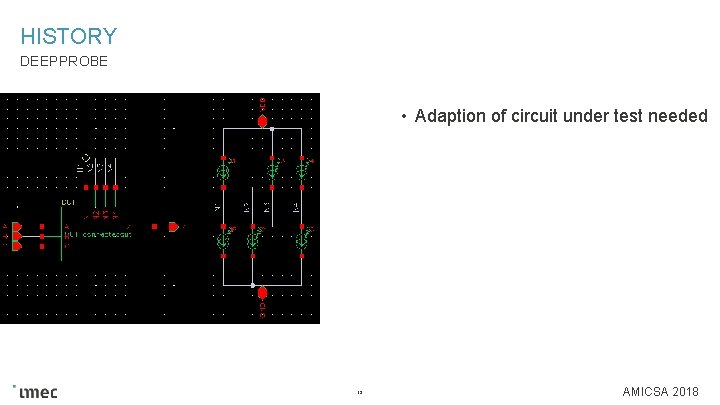

HISTORY DEEPPROBE • Adaption of circuit under test needed 13 AMICSA 2018

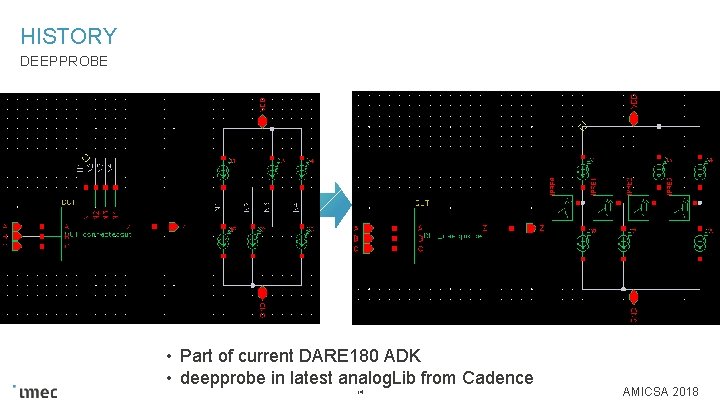

HISTORY DEEPPROBE • Part of current DARE 180 ADK • deepprobe in latest analog. Lib from Cadence 14 AMICSA 2018

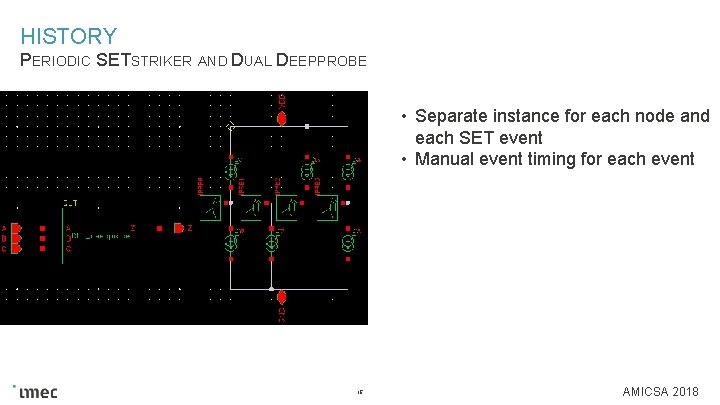

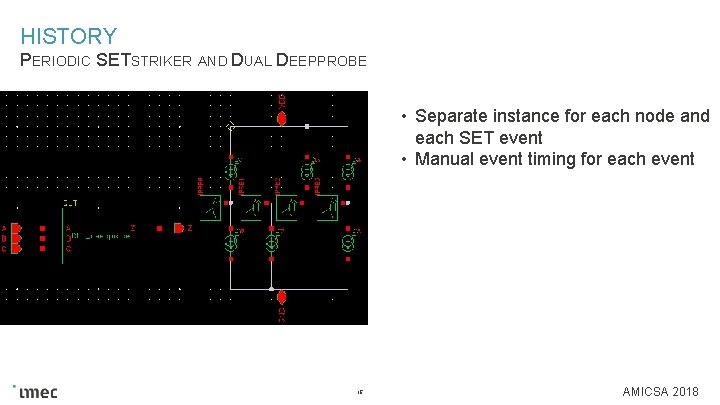

HISTORY PERIODIC SETSTRIKER AND DUAL DEEPPROBE • Separate instance for each node and each SET event • Manual event timing for each event 15 AMICSA 2018

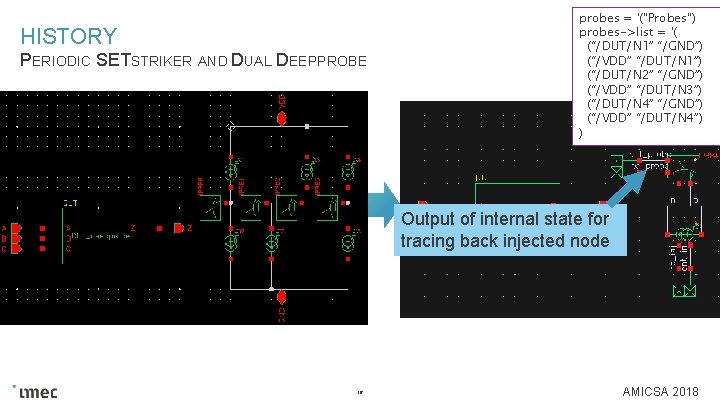

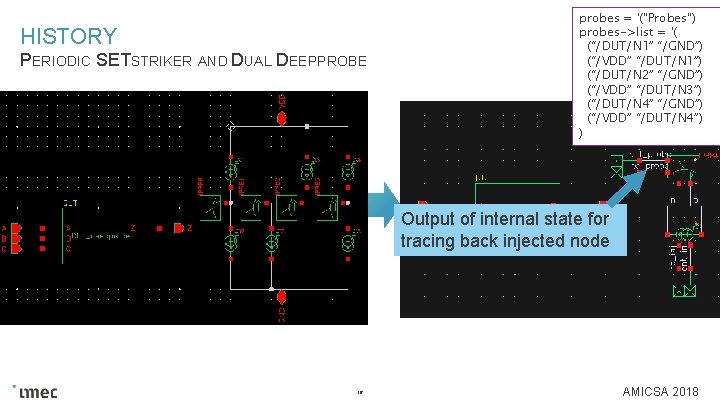

HISTORY PERIODIC SETSTRIKER AND DUAL DEEPPROBE probes = '("Probes") probes->list = '( (“/DUT/N 1” “/GND”) (“/VDD” “/DUT/N 1”) (“/DUT/N 2” “/GND”) (“/VDD” “/DUT/N 3”) (“/DUT/N 4” “/GND”) (“/VDD” “/DUT/N 4”) ) Output of internal state for tracing back injected node 16 AMICSA 2018

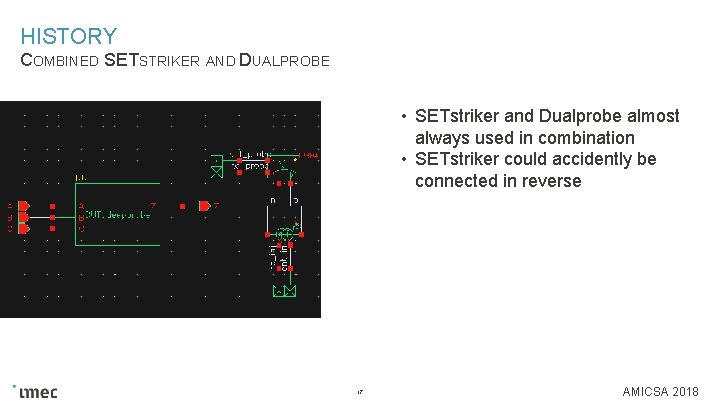

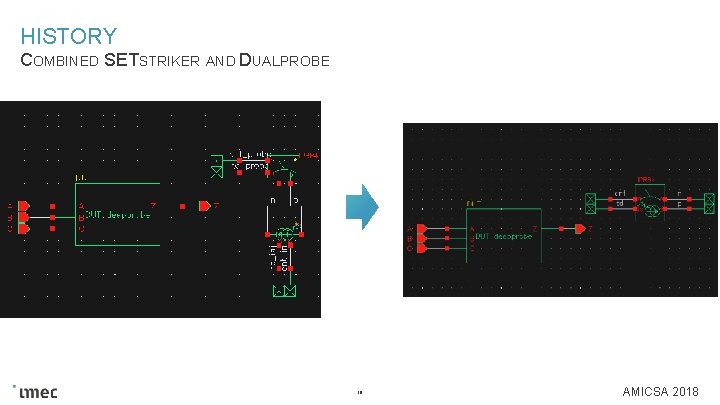

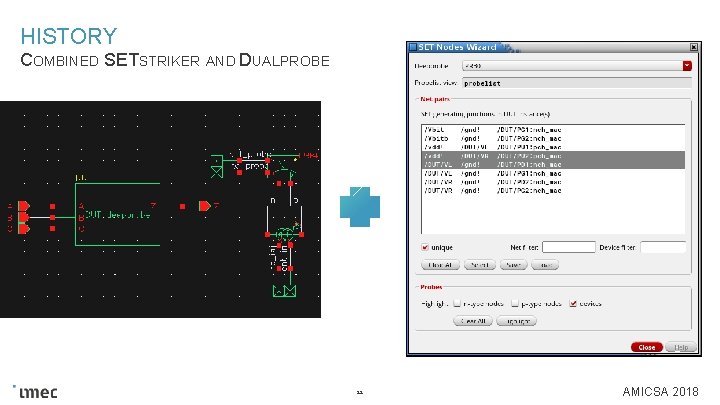

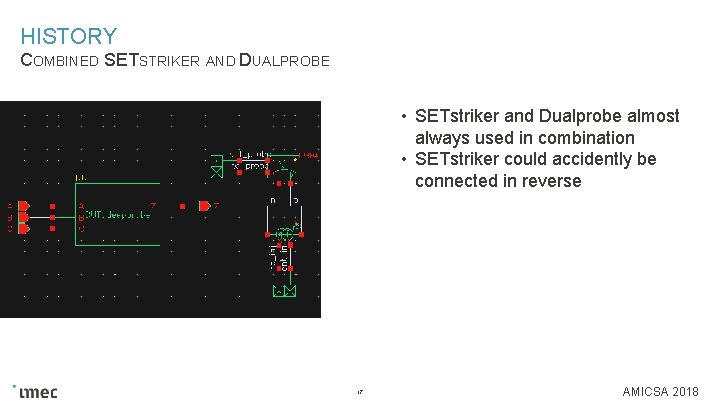

HISTORY COMBINED SETSTRIKER AND DUALPROBE • SETstriker and Dualprobe almost always used in combination • SETstriker could accidently be connected in reverse 17 AMICSA 2018

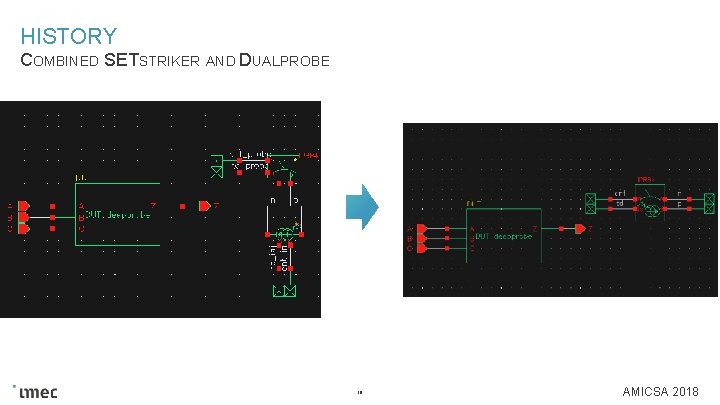

HISTORY COMBINED SETSTRIKER AND DUALPROBE 18 AMICSA 2018

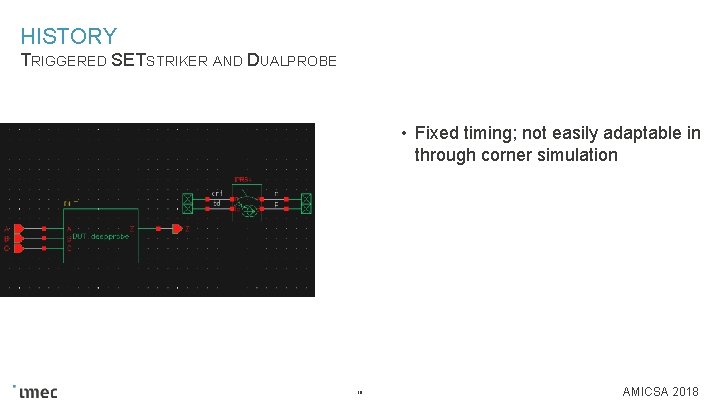

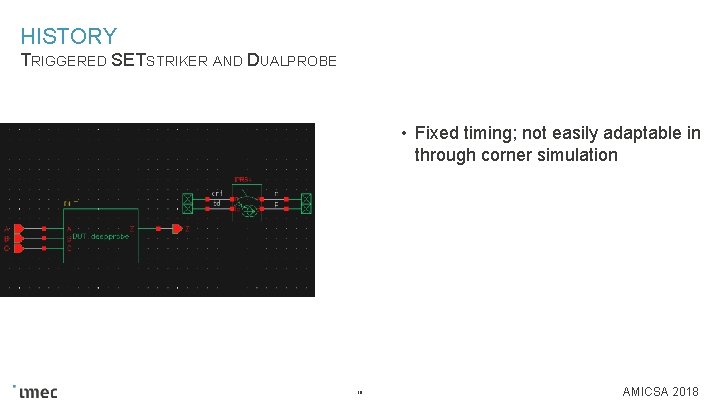

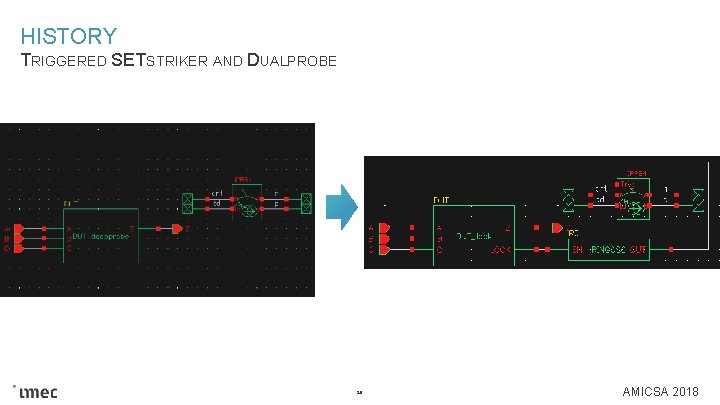

HISTORY TRIGGERED SETSTRIKER AND DUALPROBE • Fixed timing; not easily adaptable in through corner simulation 19 AMICSA 2018

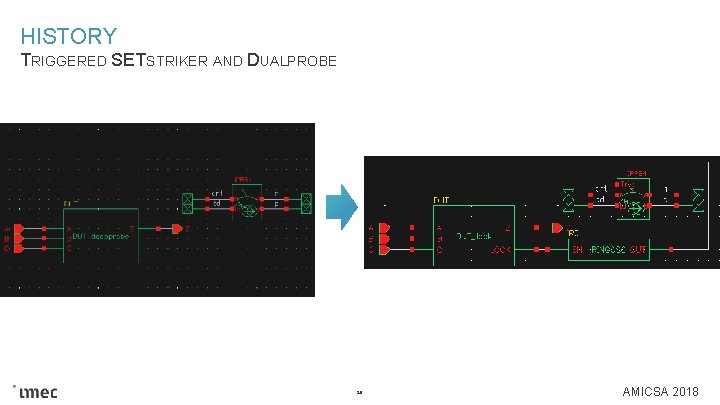

HISTORY TRIGGERED SETSTRIKER AND DUALPROBE 20 AMICSA 2018

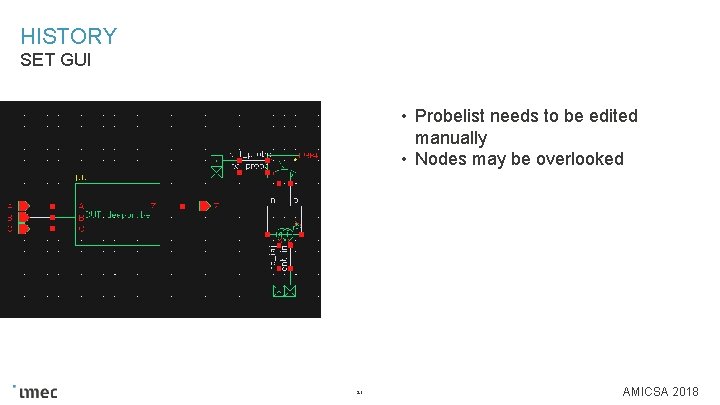

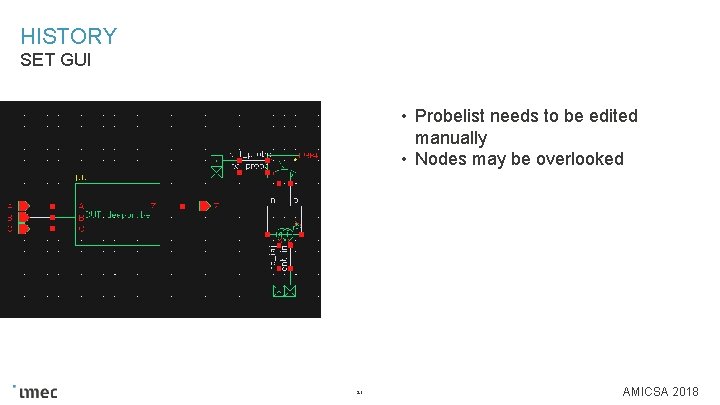

HISTORY SET GUI • Probelist needs to be edited manually • Nodes may be overlooked 21 AMICSA 2018

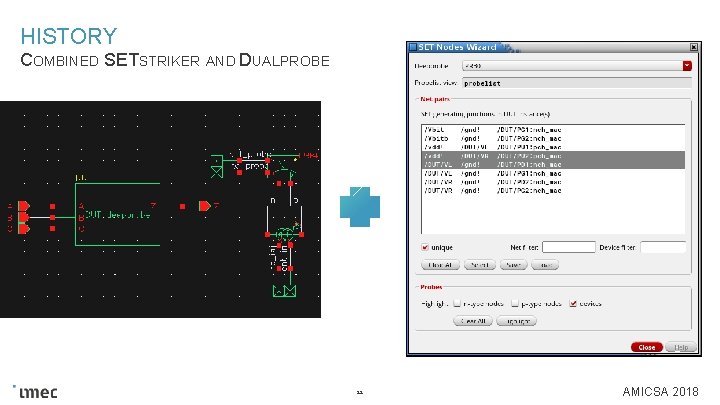

HISTORY COMBINED SETSTRIKER AND DUALPROBE 22 AMICSA 2018

WRAP-UP

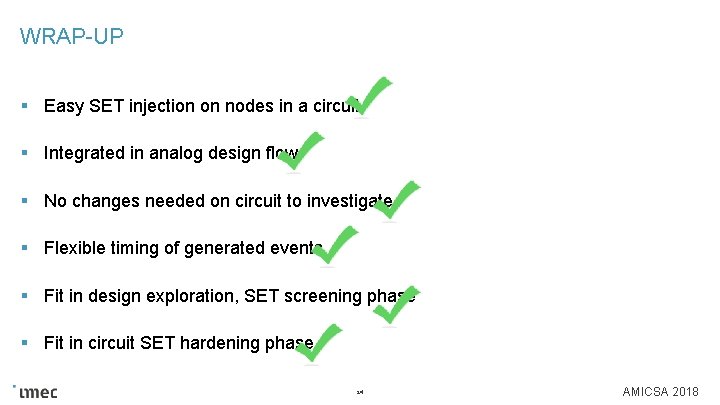

WRAP-UP § Easy SET injection on nodes in a circuit § Integrated in analog design flow § No changes needed on circuit to investigate § Flexible timing of generated events § Fit in design exploration, SET screening phase § Fit in circuit SET hardening phase 24 AMICSA 2018

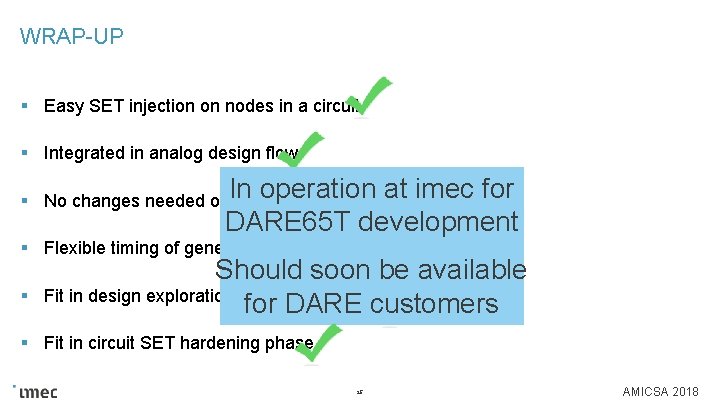

WRAP-UP § Easy SET injection on nodes in a circuit § Integrated in analog design flow operation at § No changes needed on. In circuit to investigate imec for DARE 65 T development § Flexible timing of generated events § Should soon be available Fit in design exploration, SET screening phase for DARE customers § Fit in circuit SET hardening phase 25 AMICSA 2018

PUBLIC