Microprocessors And Microcontrollers Semester 4 th 5 th

- Slides: 34

Microprocessors And Microcontrollers Semester : 4 th , 5 th (TL, ES) Course Code : ES 256 , ES 313 By: Dr. Attiya Baqai Assistant Professor, Department of Electronics, MUET.

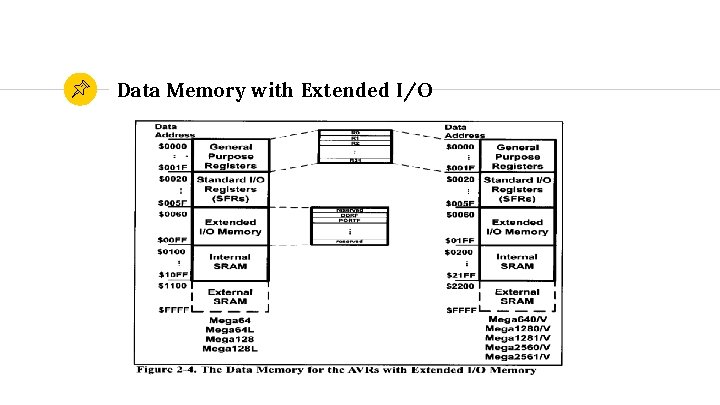

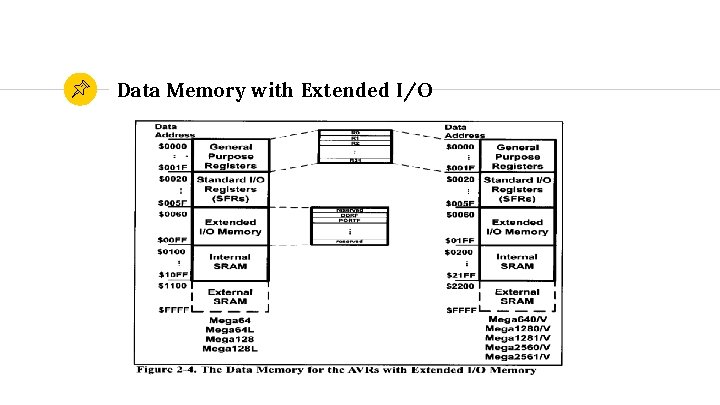

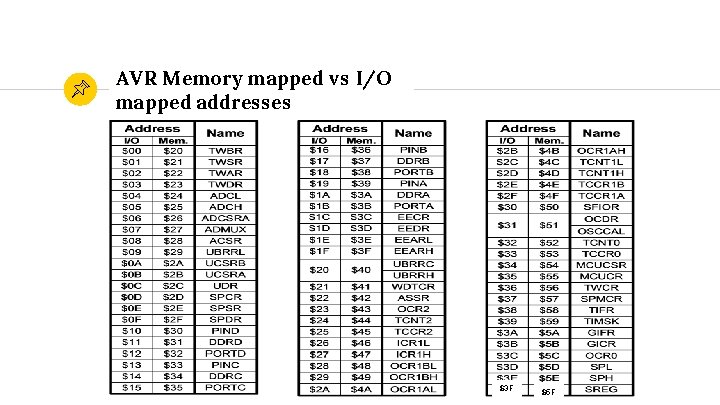

IO memory (SFR) ◉ Dedicated to Specific Functions ◉ All AVRs have at least 64, 8 bit I/O locations. ◉ 64 byte section is called Standard I/O memory. ◉ AVRs of more than 32 IO pins (ATmega 64, ATmega 128, ATmega 256) have extended I/O for controlling extra ports and extra peripherals

Data Memory with Extended I/O

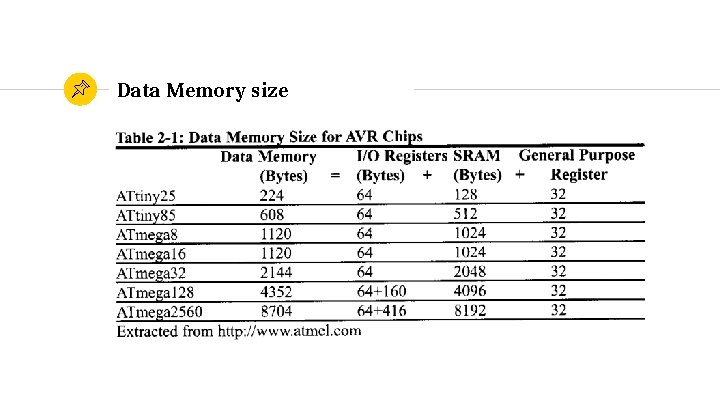

SRAM vs EEPROM ◉ SRAM is 8 bit RAM ◉ SRAM also called scratch pad RAM ◉ EEPROM does not lose data while SRAM does when power is off. ◉EEPROM is used when data is rarely changed like settings, options etc. ◉SRAM is used when data or parameters are frequently changed. ◉Data Memory= GPRs+ SFR(I/O Reg)+ SRAM

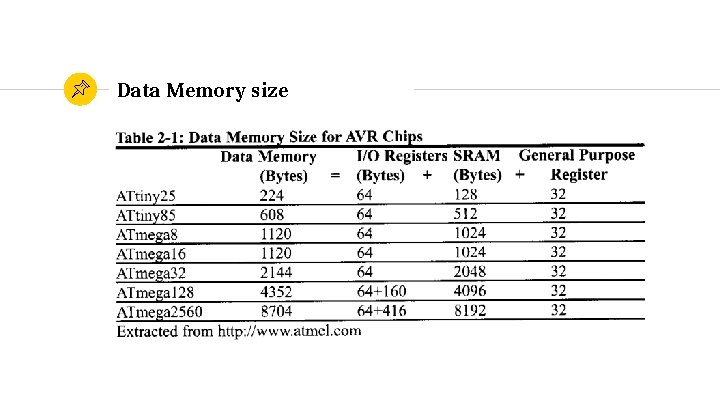

Data Memory size

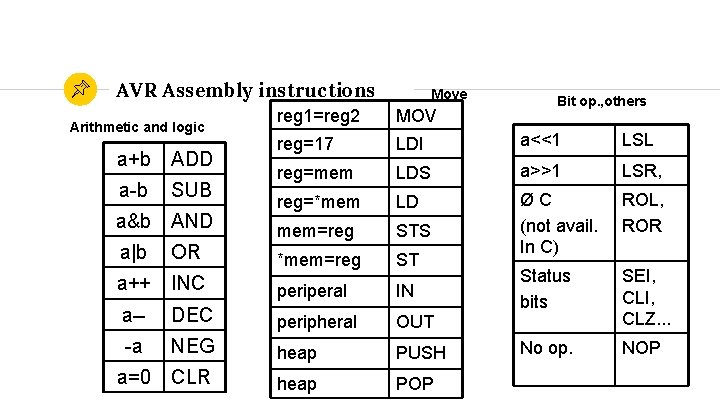

AVR Assembly instructions ◉ Arithmetic and logic ◉Branch, jump ◉Data movement ◉Bit manipulation, bit test

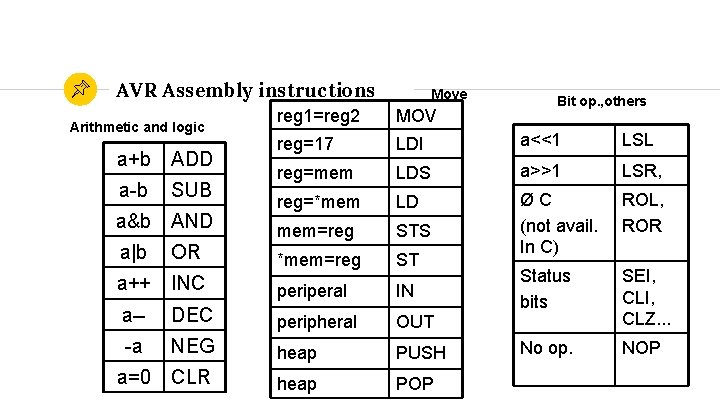

AVR Assembly instructions Arithmetic and logic a+b ADD a-b SUB a&b AND Move Bit op. , others reg 1=reg 2 MOV reg=17 LDI a<<1 LSL reg=mem LDS a>>1 LSR, reg=*mem LD mem=reg STS ROL, ROR *mem=reg ST ØC (not avail. In C) Status bits SEI, CLZ. . . No op. NOP a|b OR a++ INC periperal IN a-- DEC peripheral OUT -a NEG heap PUSH a=0 CLR heap POP

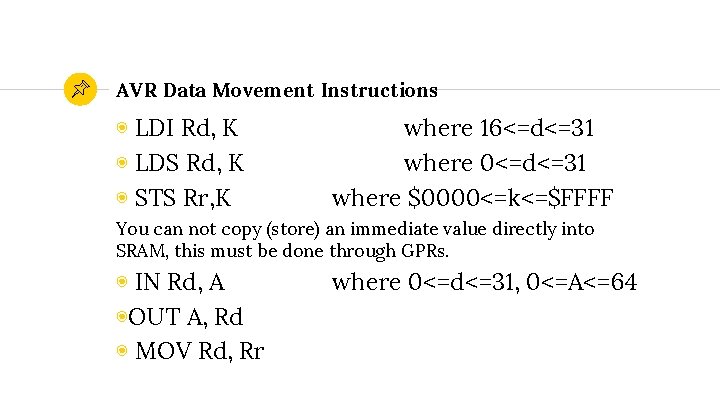

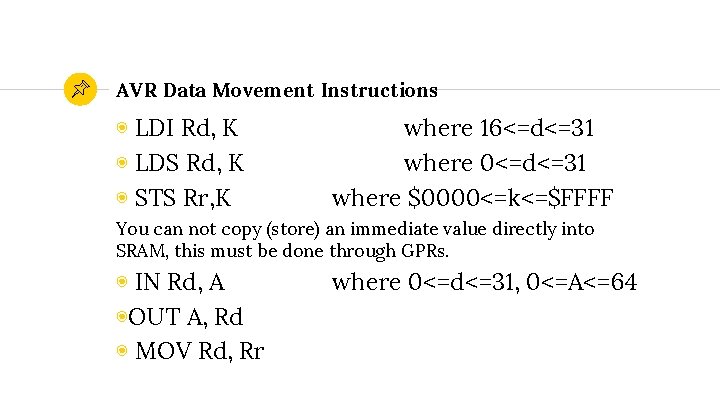

AVR Data Movement Instructions ◉ LDI Rd, K ◉ LDS Rd, K ◉ STS Rr, K where 16<=d<=31 where 0<=d<=31 where $0000<=k<=$FFFF You can not copy (store) an immediate value directly into SRAM, this must be done through GPRs. ◉ IN Rd, A ◉OUT A, Rd ◉ MOV Rd, Rr where 0<=d<=31, 0<=A<=64

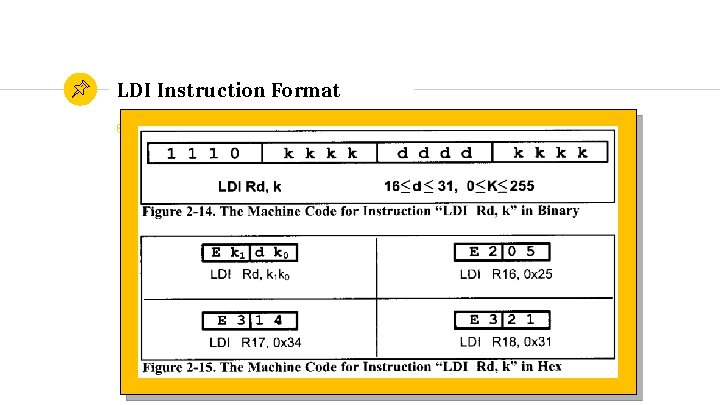

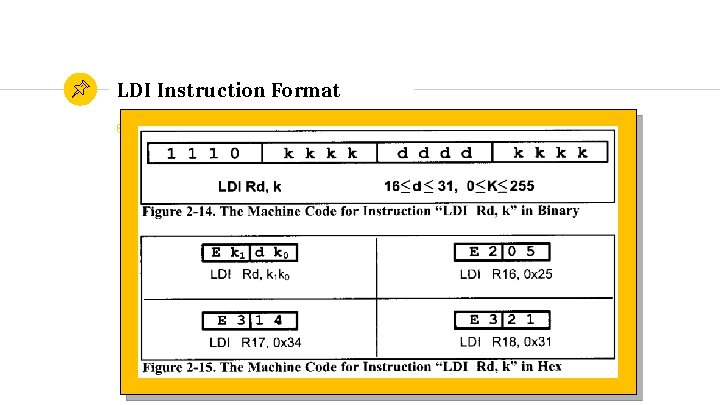

LDI Instruction Format ◉

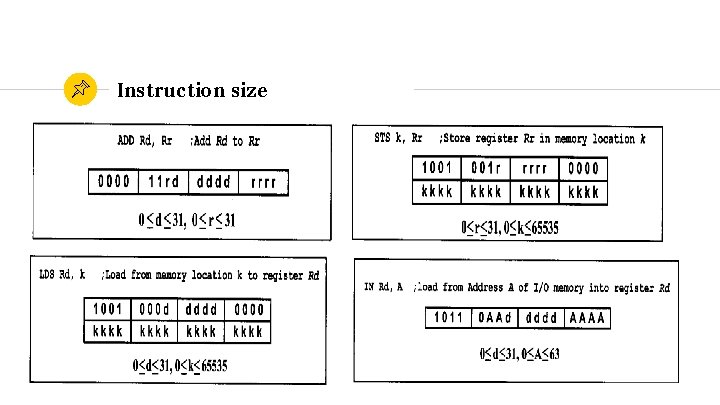

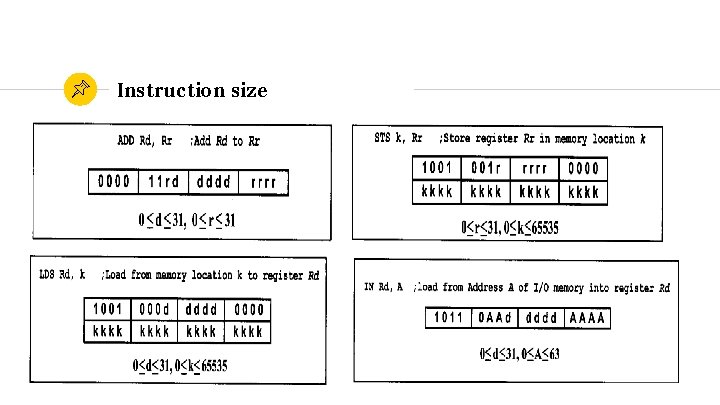

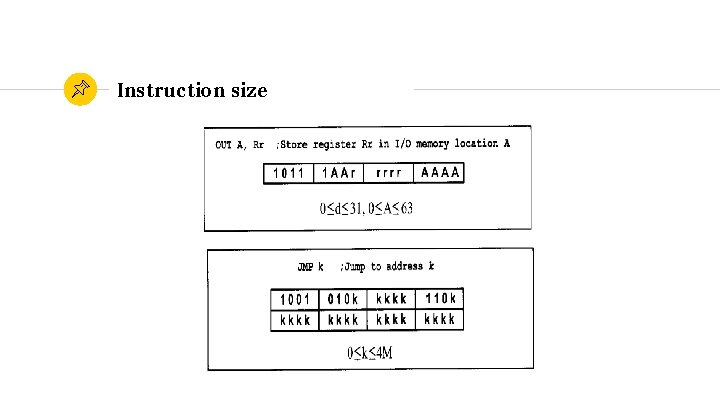

Instruction size

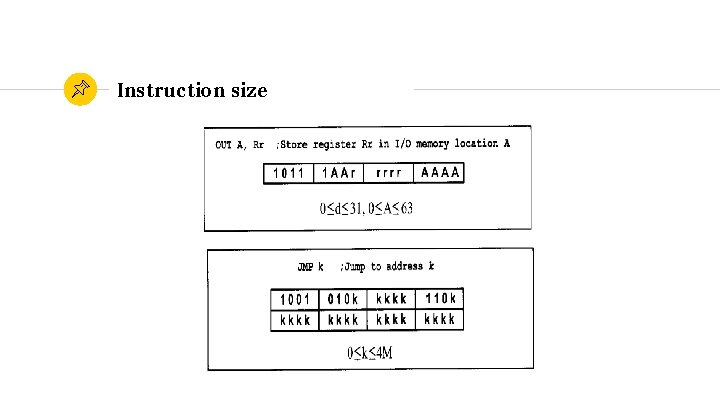

Instruction size

Data Format Representation ◉ Hex----- 0 x 0 F, $0 F ◉ Binary----0 b 00001111 ◉ Decimal-------15 ◉ ASCII----- ‘ 2’

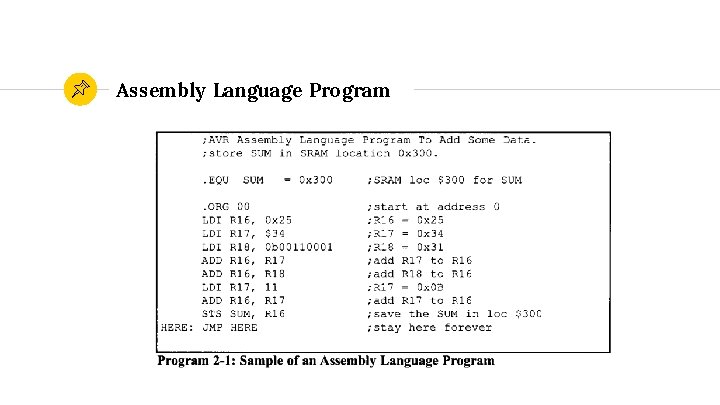

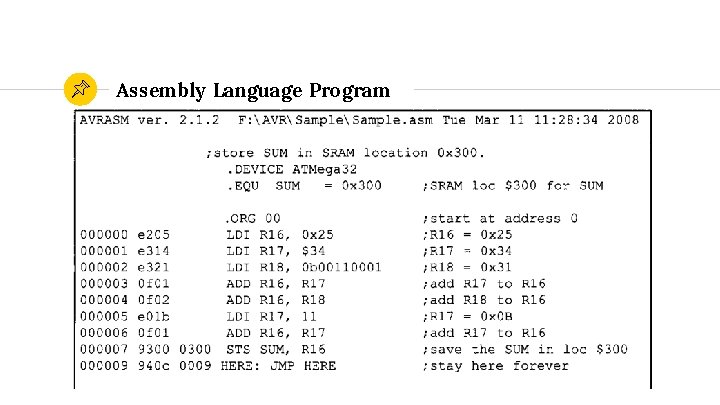

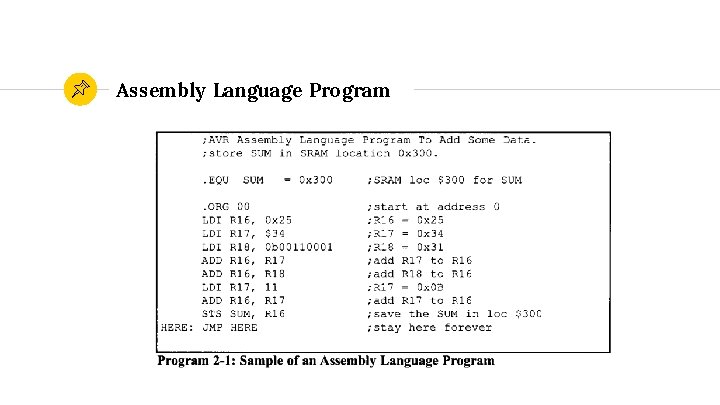

Assembly Language Program

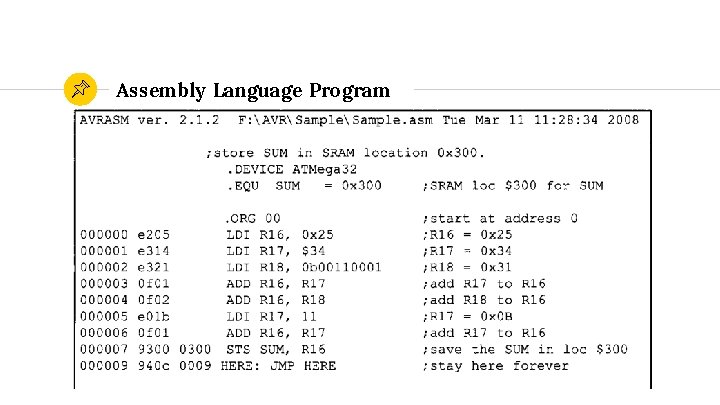

Assembly Language Program

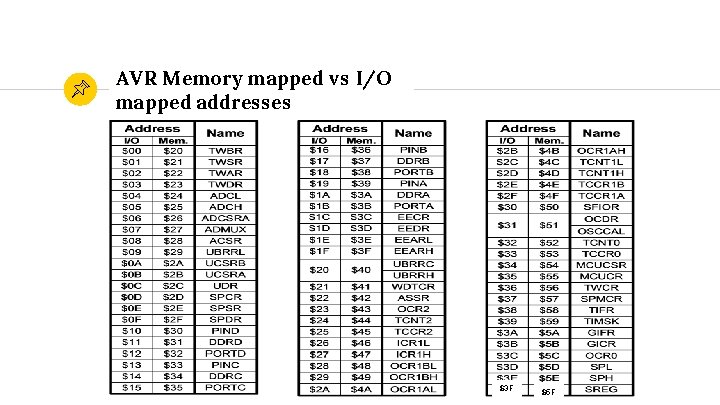

AVR Memory mapped vs I/O mapped addresses $3 F $5 F

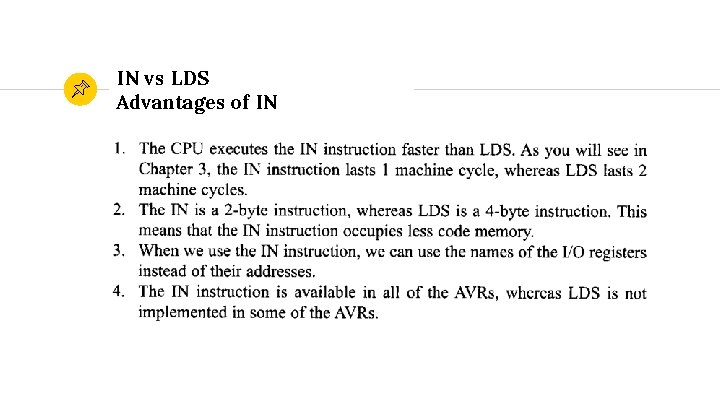

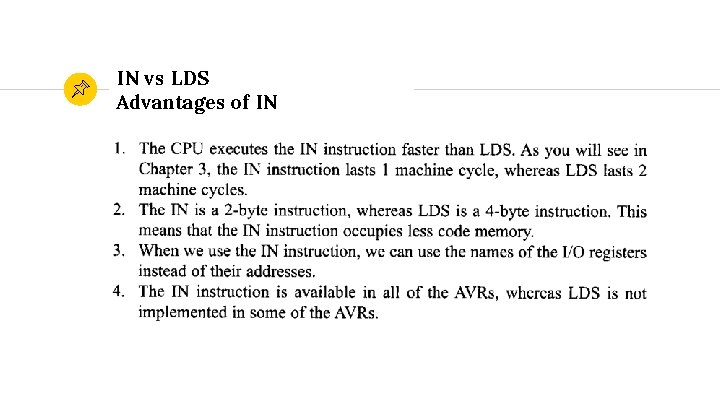

IN vs LDS Advantages of IN

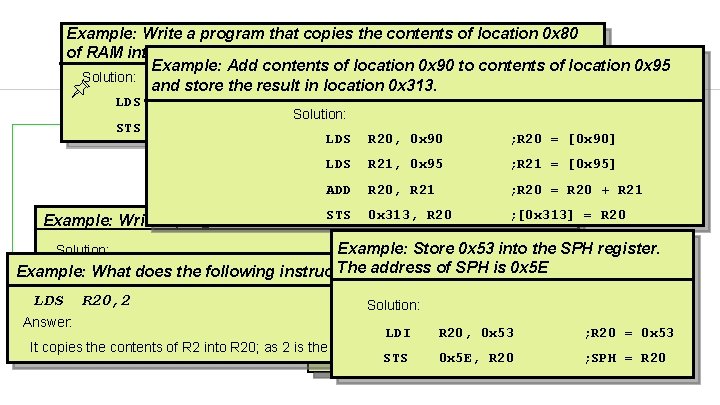

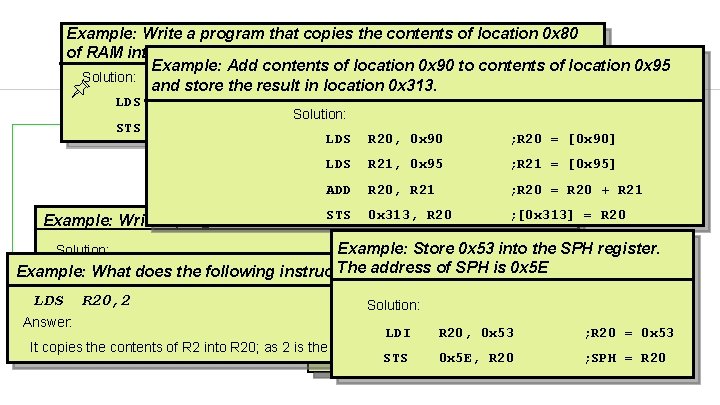

Example: Write a program that copies the contents of location 0 x 80 of RAM into location 0 x 81. Example: Add contents of location 0 x 90 to contents of location 0 x 95 Solution: store the. Space result in location 0 x 313. Dataand Address LDS R 20, 0 x 80 STS 0 x 81, R 20 ; R 20 = [0 x 80] Solution: ; [0 x 81] = R 20 = [0 x 80] LDS R 20, 0 x 90 ; R 20 = [0 x 90] LDS R 21, 0 x 95 ; R 21 = [0 x 95] ADD R 20, R 21 ; R 20 = R 20 + R 21 0 x 313, R 20 = R 20 Example: Write a program that stores. STS 55 into location 0 x 80 of ; [0 x 313] RAM. Example: Store 0 x 53 into the SPH register. LDS (Load from dataspace) STS (Storedirect to The address of SPH is data 0 x 5 E Example: LDI What R 20, does 55 the following do? ; R 20 = instruction 55 Solution: LDS Answer: STS 0 x 80, R 20, 2 LDS addr STS Rd, addr, Rd ; [0 x 80] = R 20 = 55 Solution: ; Rd = [addr] ; [addr]=Rd Example: LDI R 20, 0 x 53 ; R 20 = 0 x 53 It copies the contents of R 2 into R 20; as 2 is the address of R 2. LDS 0 x 60 STS R 1, 0 x 60, R 15 ; [0 x 60] = R 15 STS 0 x 5 E, R 20 ; SPH = R 20

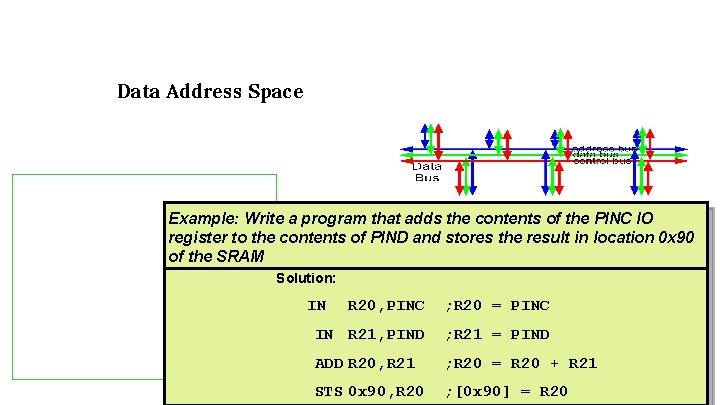

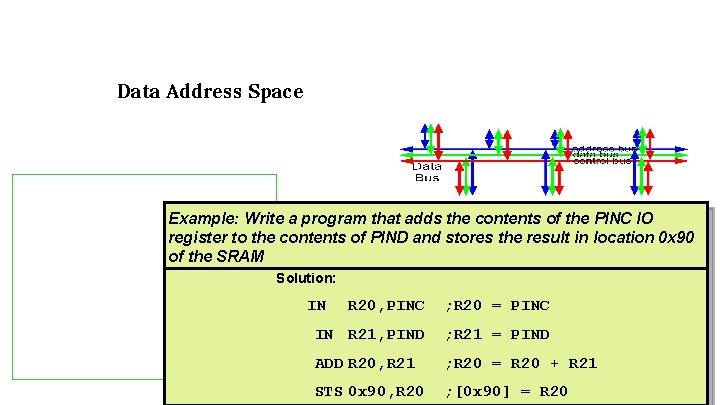

Data Address Space Example: Write a program that adds the contents of the PINC IO OUT (OUT to. IO IOlocation) IN (IN from register to the contents of PIND and stores the result in location 0 x 90 OUT IOAddr, Rd ; [addr]=Rd IN Rd, IOaddress = [addr] of the SRAM Using Names of IO registers Solution: Example: ; R 20 = PINC R 20, PINC OUT 0 x 3 F, R 12 ; SREG R 120 x 3 E, R 12 IN R 1, 0 x 3 F ; R 1 ==SREG OUT SPH, R 12 ; OUT IN R 21, PIND ; R 21 = PIND 0 x 3 E, R 15 ; SPH = R 15 IN R 17, 0 x 3 E ; R 17 = SPH INOUT R 15, SREG ; IN R 15, 0 x 3 F ADD R 20, R 21 ; R 20 = R 20 + R 21 IN STS 0 x 90, R 20 ; [0 x 90] = R 20

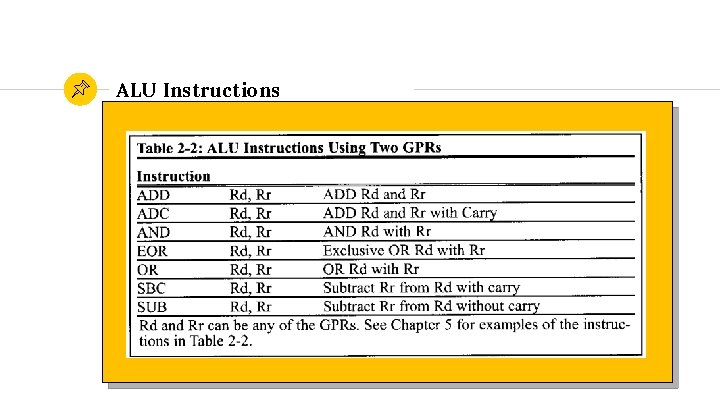

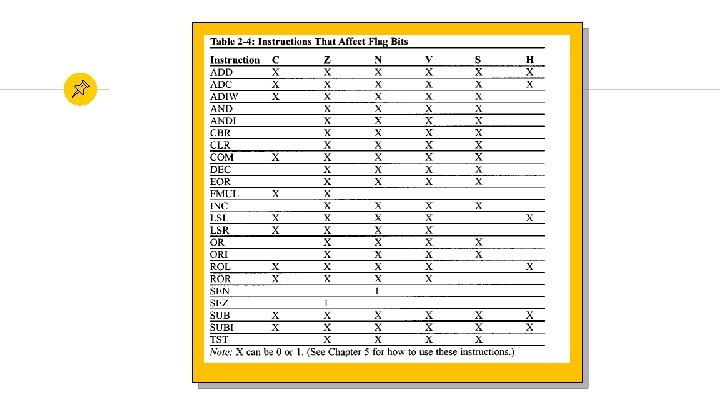

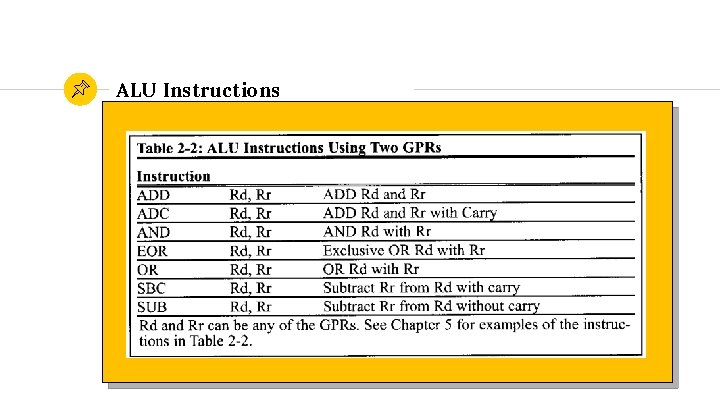

ALU Instructions

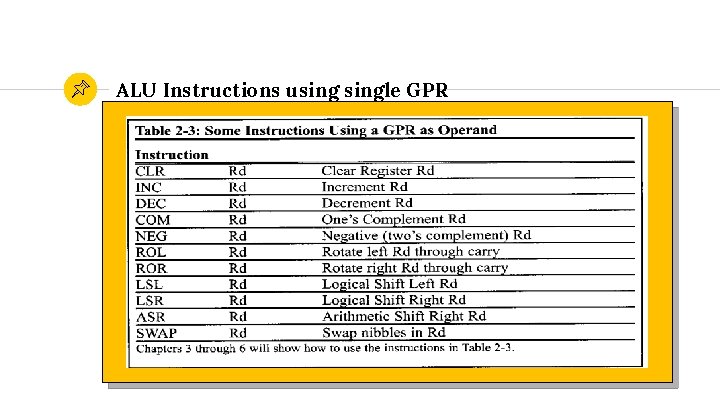

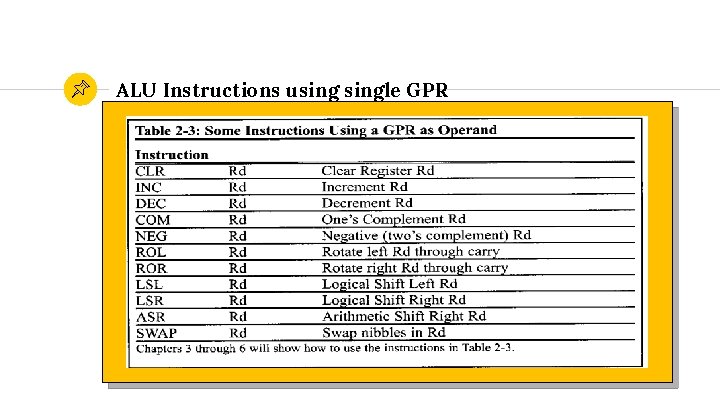

ALU Instructions usingle GPR

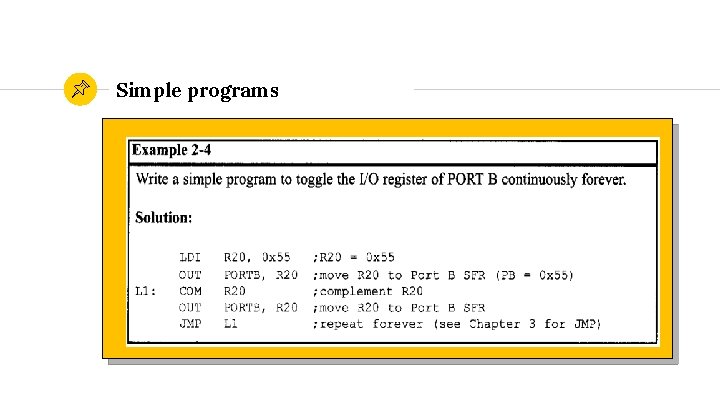

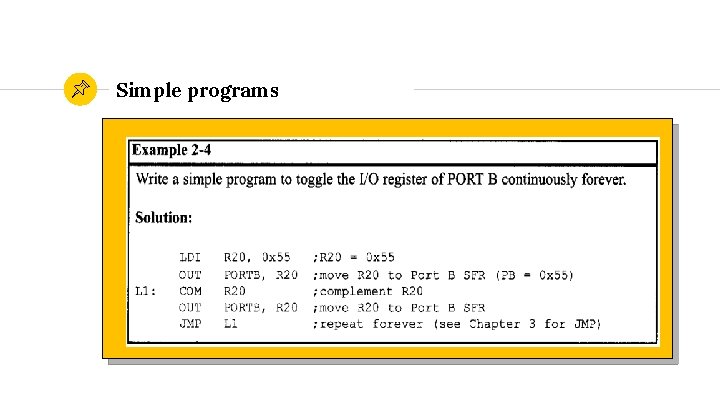

Simple programs

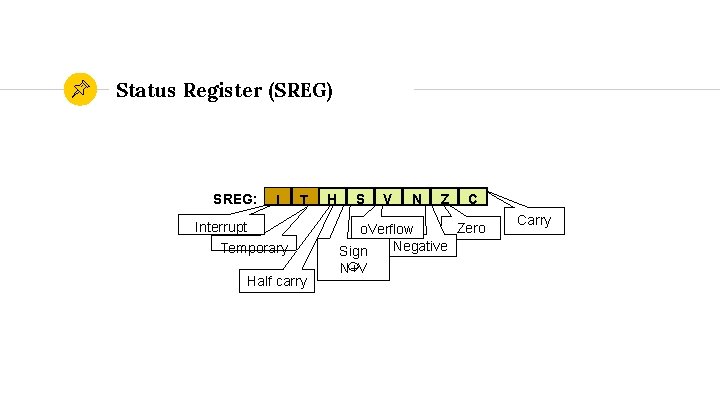

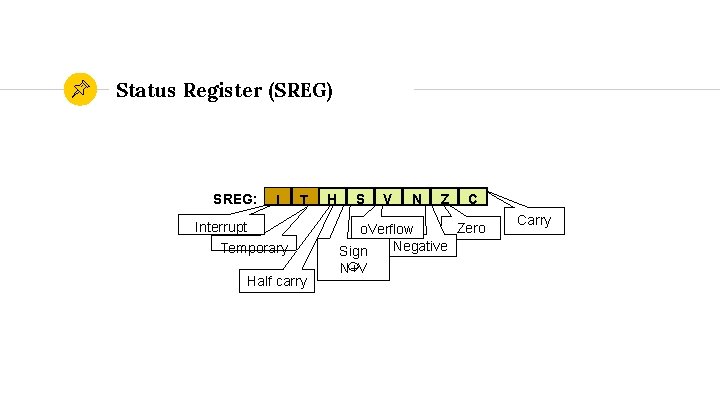

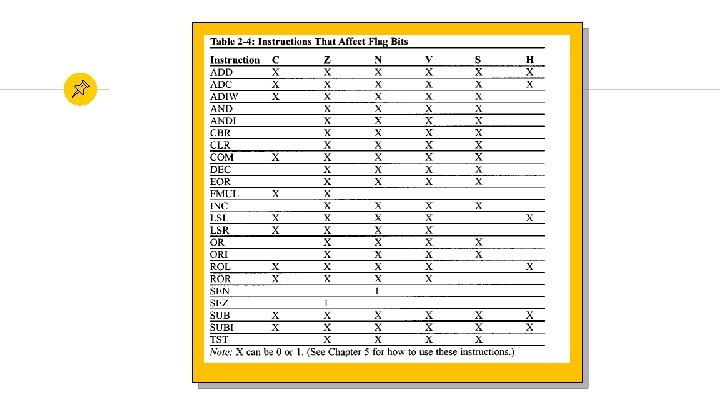

Status Register (SREG) SREG: I T Interrupt Temporary Half carry H S V N Z C Zero o. Verflow Negative Sign N+V Carry

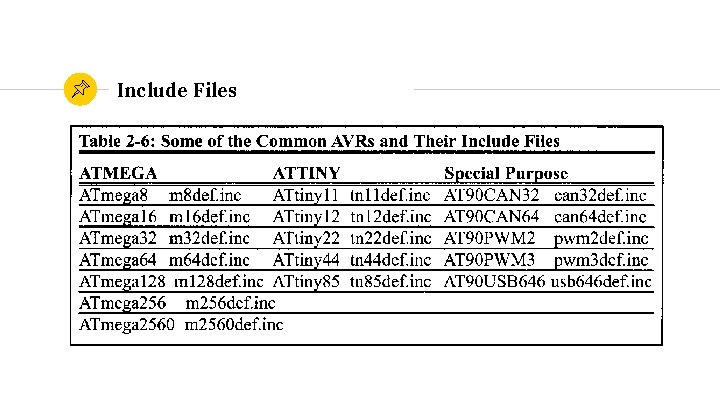

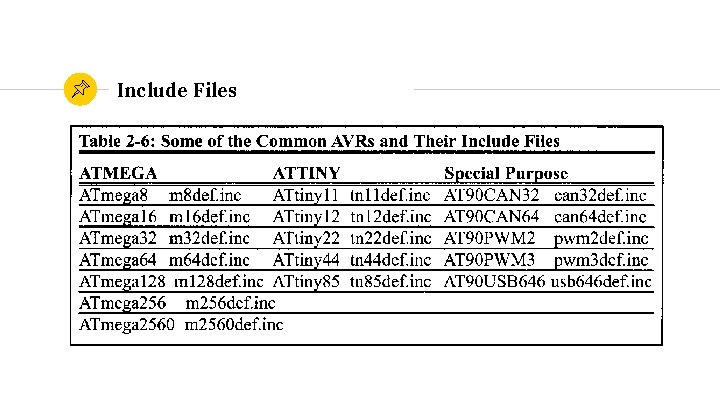

Include Files

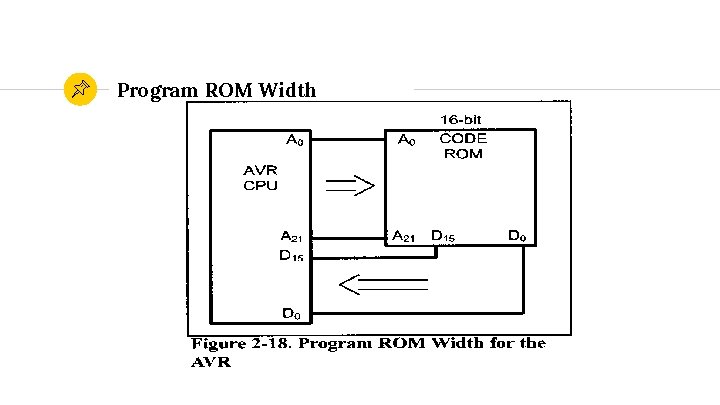

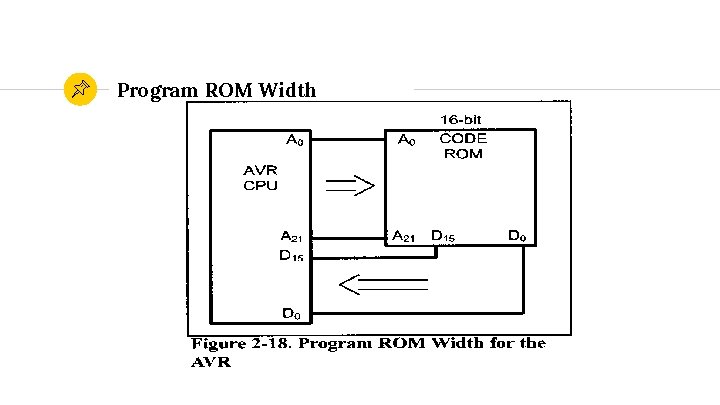

Program ROM Width

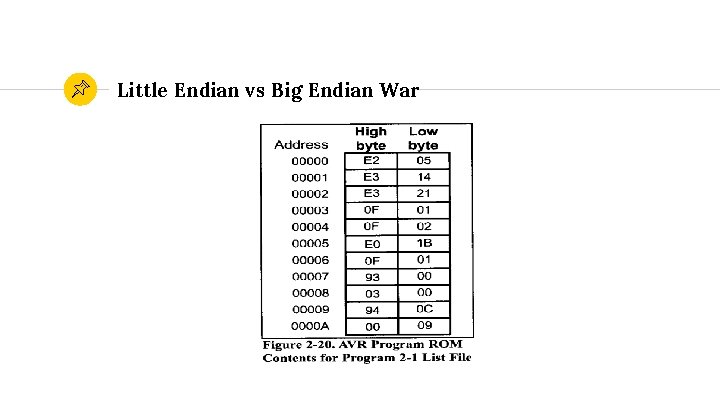

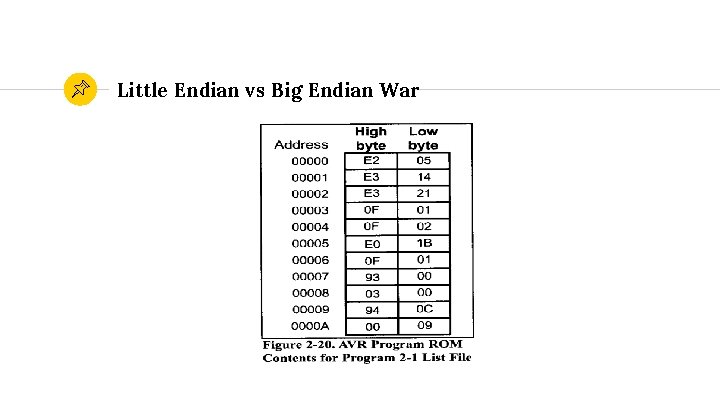

Little Endian vs Big Endian War

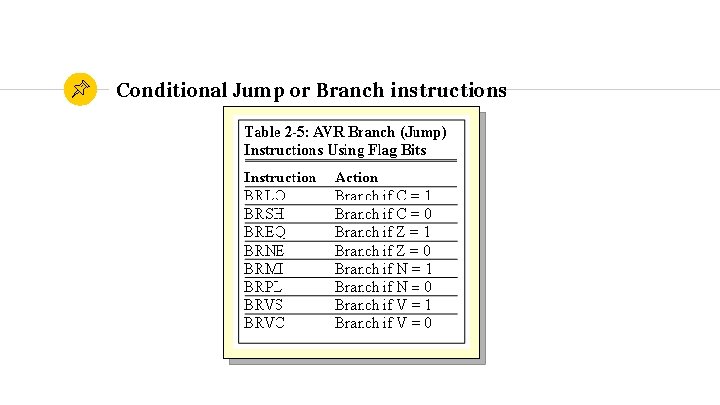

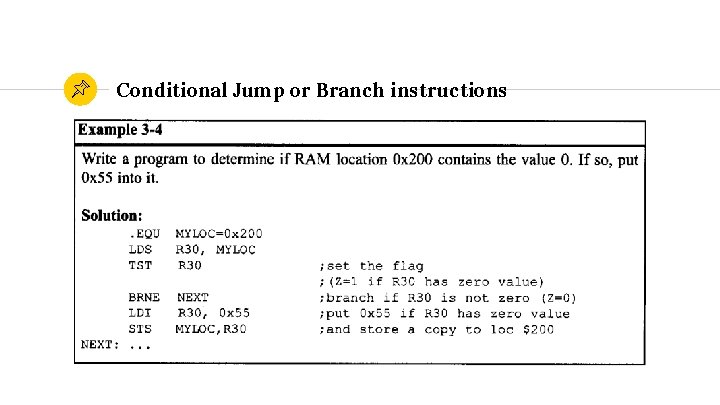

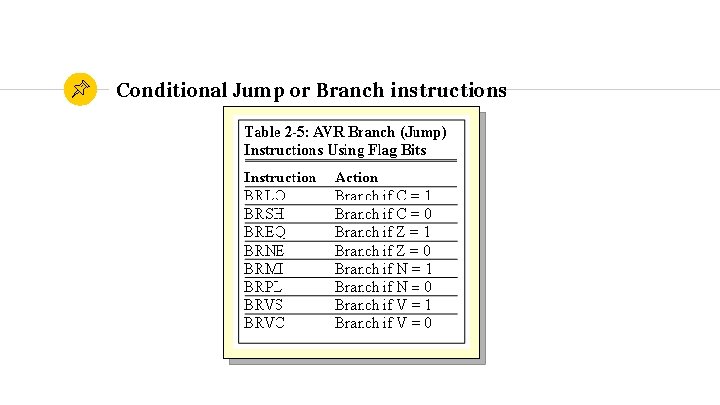

Conditional Jump or Branch instructions

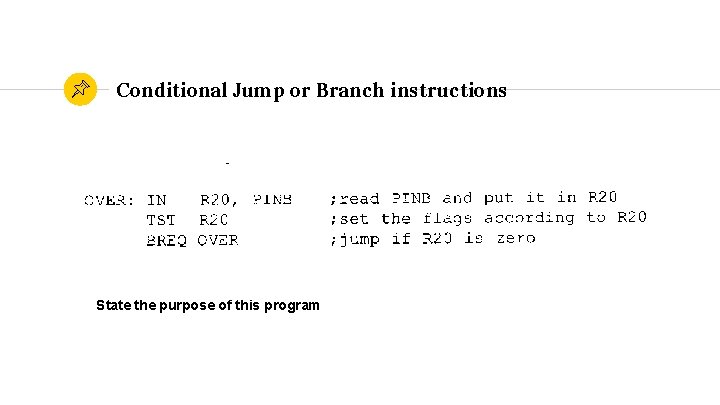

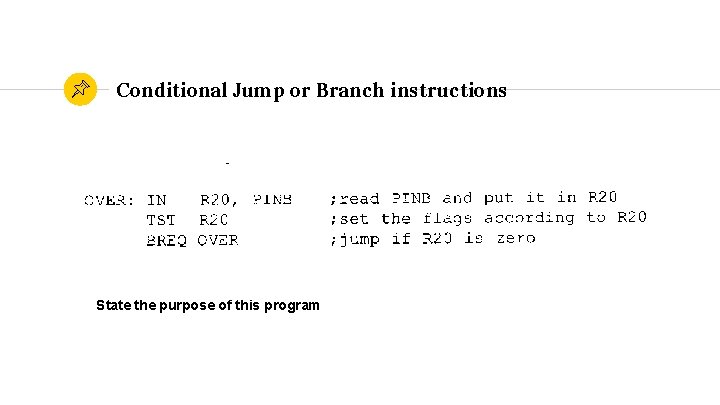

Conditional Jump or Branch instructions State the purpose of this program

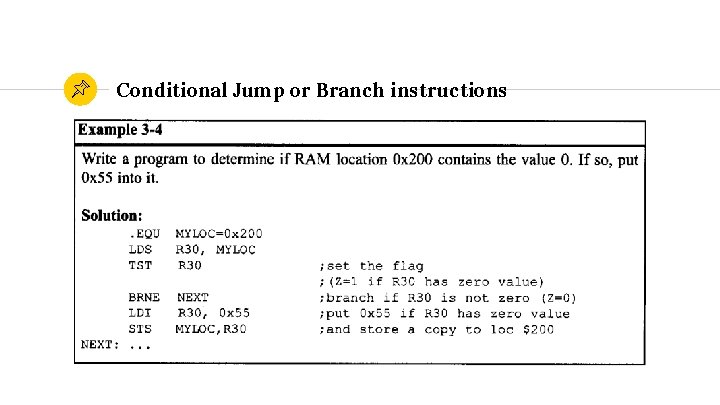

Conditional Jump or Branch instructions

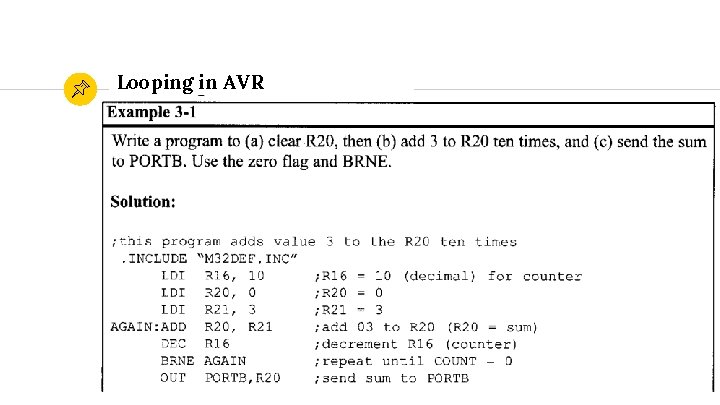

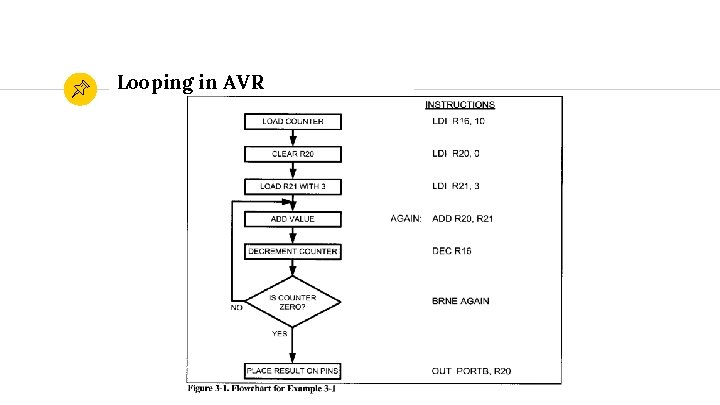

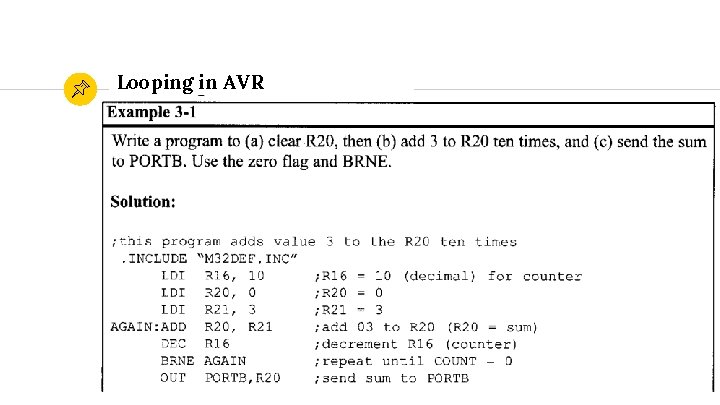

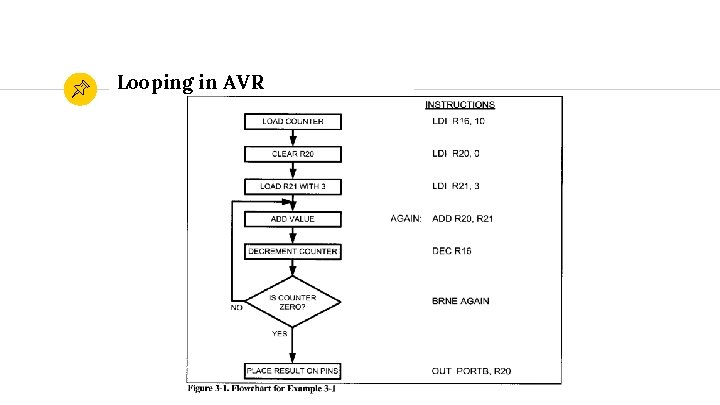

Looping in AVR

Looping in AVR

Looping in AVR

Looping in AVR

Thanks! Any questions ?