make Utility A Unix utility to create and

![The description file and its Components ������� %make [ -f make_name] [other options] [targets[ The description file and its Components ������� %make [ -f make_name] [other options] [targets[](https://slidetodoc.com/presentation_image_h2/6164e2467f836b911b7edc5478b338c6/image-13.jpg)

![The description file and its Components 2. ����� ��� �� word ���������� location parameter)$]MACRO/location/string[( The description file and its Components 2. ����� ��� �� word ���������� location parameter)$]MACRO/location/string[(](https://slidetodoc.com/presentation_image_h2/6164e2467f836b911b7edc5478b338c6/image-30.jpg)

![The description file and its Components . 3 ���������� )$]MACRO? string 1: string 2[( The description file and its Components . 3 ���������� )$]MACRO? string 1: string 2[(](https://slidetodoc.com/presentation_image_h2/6164e2467f836b911b7edc5478b338c6/image-35.jpg)

- Slides: 57

make Utility A Unix utility to create and maintain program Present by …. Noppamas Pukkhem make 1

Overview • • • Compiling multi-part programs Overview of the make Utility The Description file and its Components Operation of the make Utility Running make 2

Compiling Multi-part programs make 3

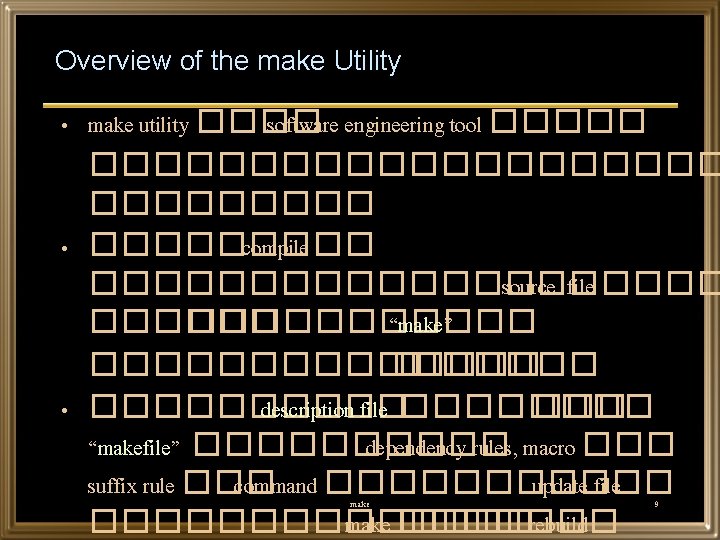

Compiling multi-part programs • ��� compile ��������� source file �������� 2 ������� : – compile ����� module �������� object file – link ��� object file ������ executable program make 4

Compiling multi-part programs ���������� 1: Compile mod 1. o cc -c ��������� mod 1. c �object file mod 2. o mod 3. o cc -c mod 2. c cc -c mod 3. c ����� Link ��� object file ������ � 2 : cc -o final mod 1. o mod 2. o mod 3. o make 5

Overview of make Utility make 8

Overview of the make Utility • make utility ���� software engineering tool ������������� • ����� compile ���������� source file ����������� “make” �������� • ����� description file ���� ��� “makefile” ����� dependency rules, macro ��� suffix rule ��� command ������ update file 9 make ������� rebuild

Overview of the make Utility • “make” can be used with any programming language (including C/C++) whose compiler can be run with a unix shell command. make 10

The Description file and its Components make 11

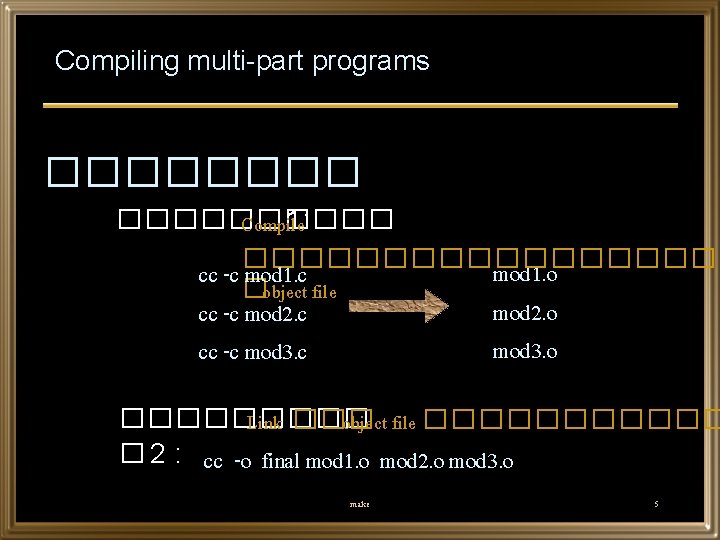

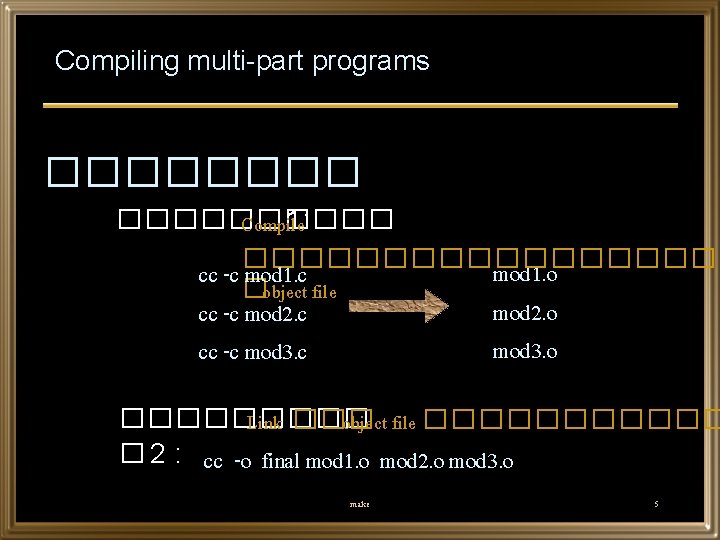

The description file and its Components • Description file • ���������� make ����� target ������� dependent ���� dependency file �������� Make ���� description file ��� default ��� file ���� procedure ���� ‘makefile’ ���� ‘Makefile’ make 12

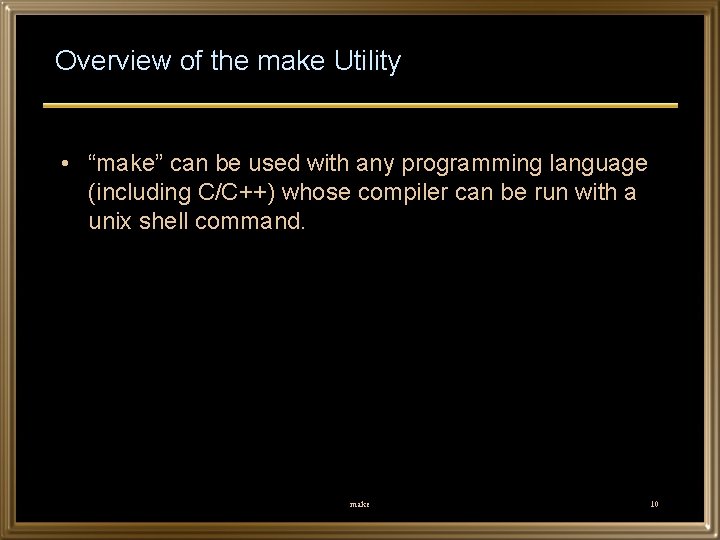

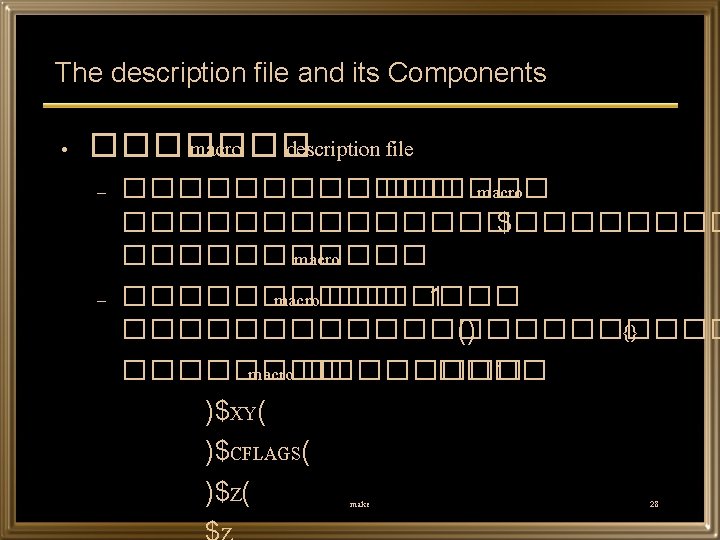

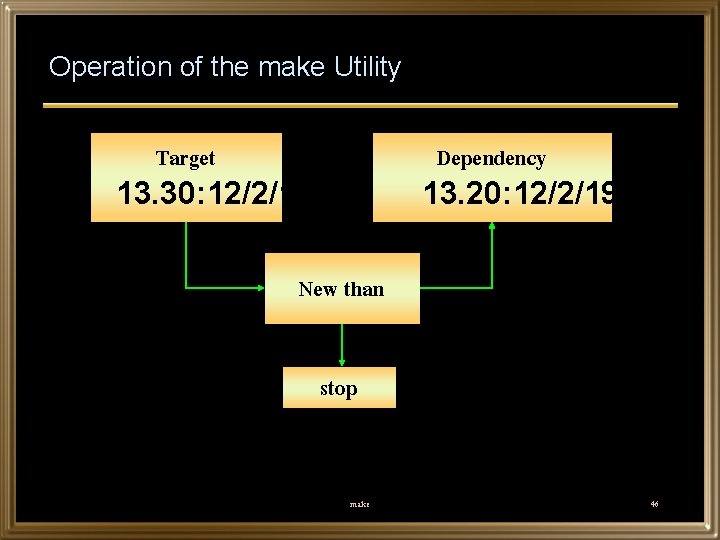

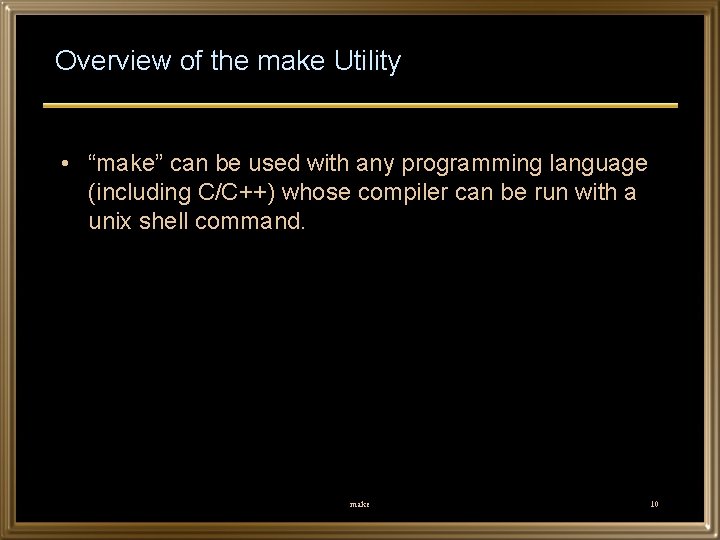

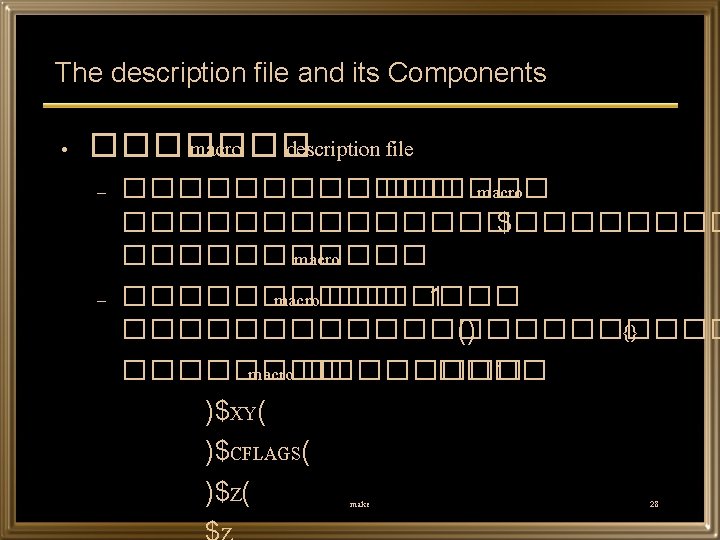

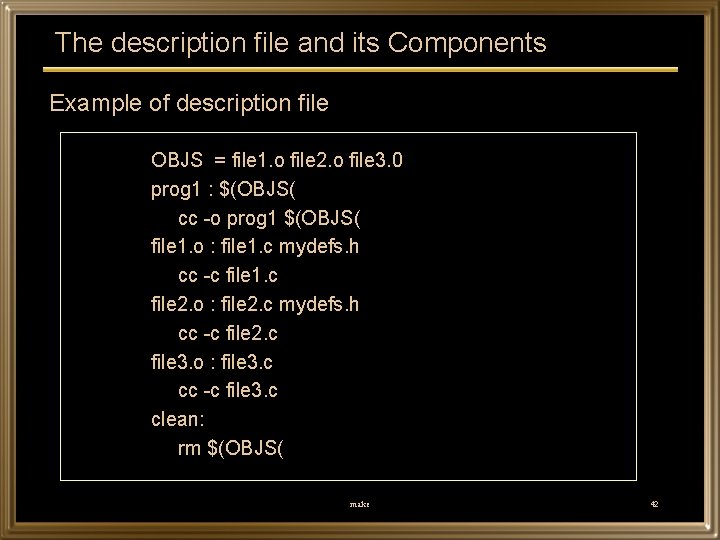

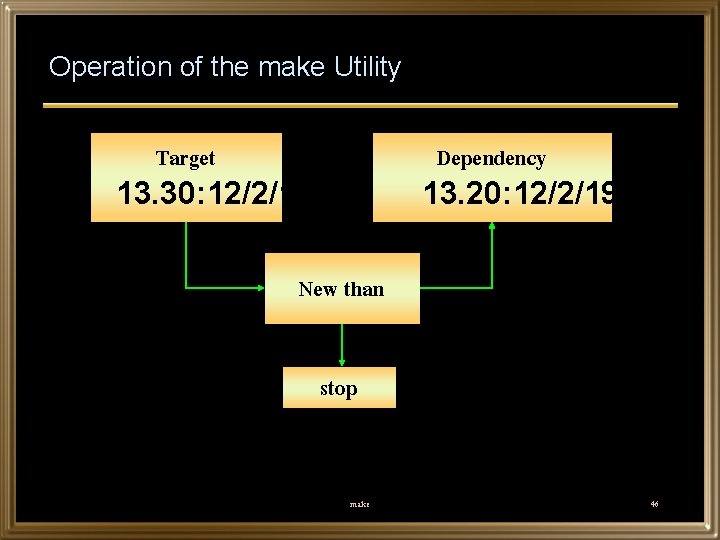

![The description file and its Components make f makename other options targets The description file and its Components ������� %make [ -f make_name] [other options] [targets[](https://slidetodoc.com/presentation_image_h2/6164e2467f836b911b7edc5478b338c6/image-13.jpg)

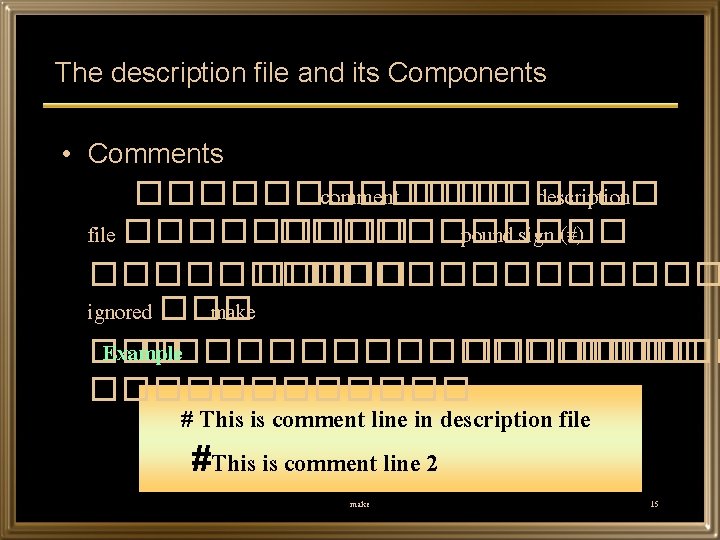

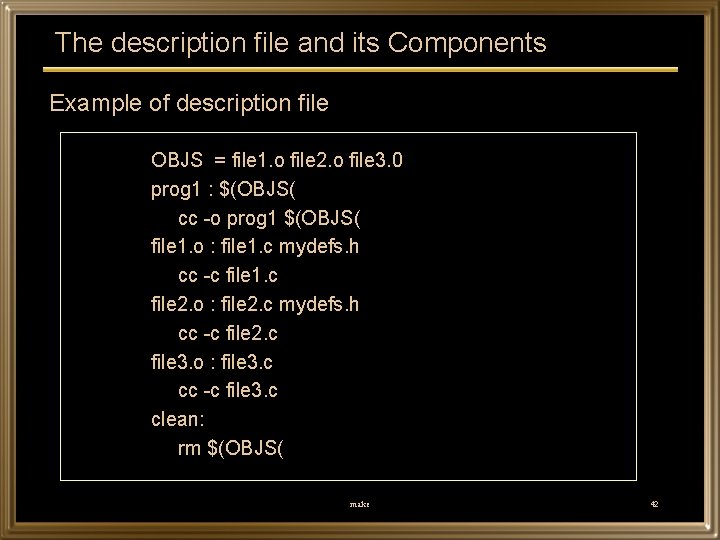

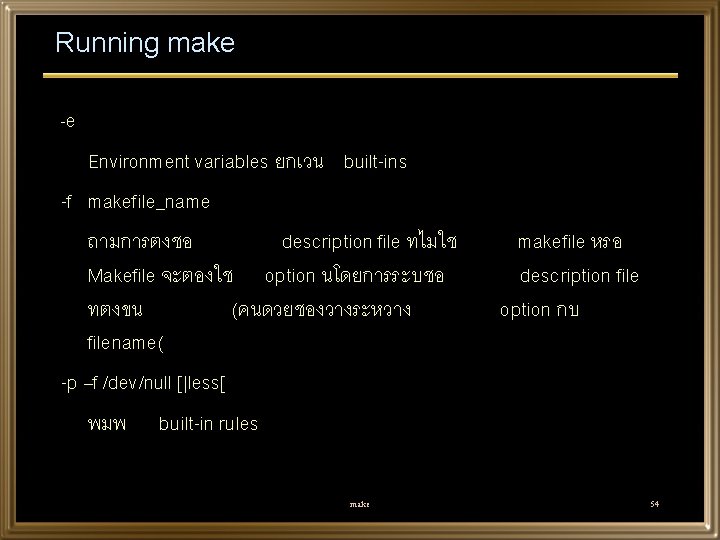

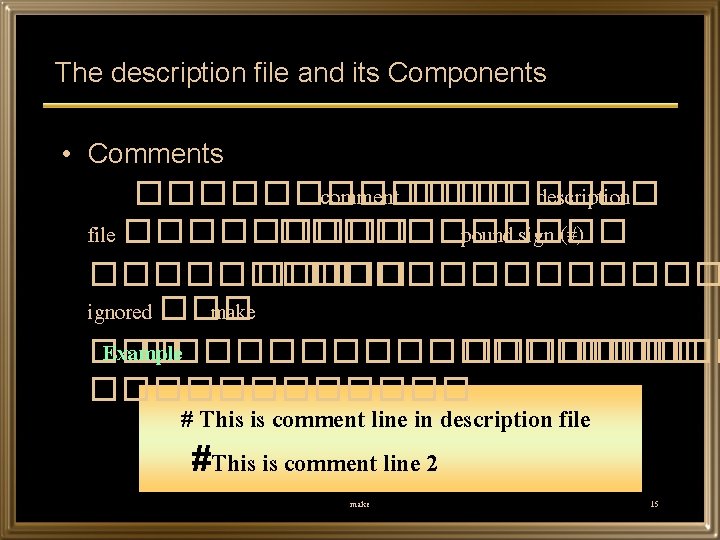

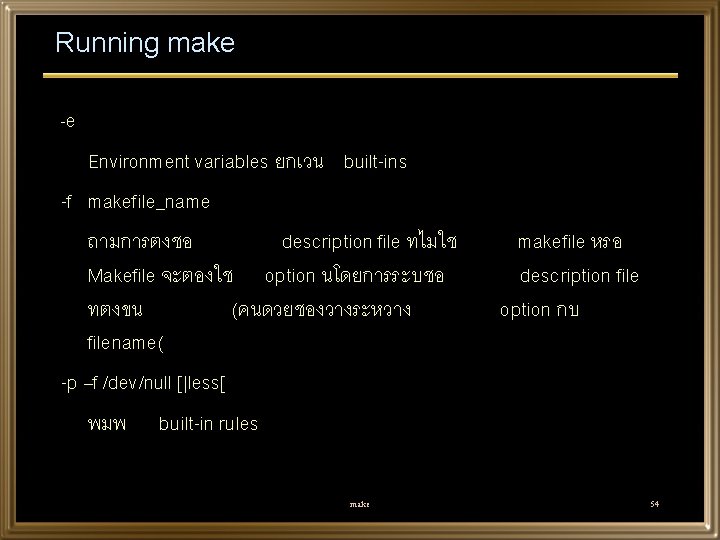

The description file and its Components ������� %make [ -f make_name] [other options] [targets[ make 13

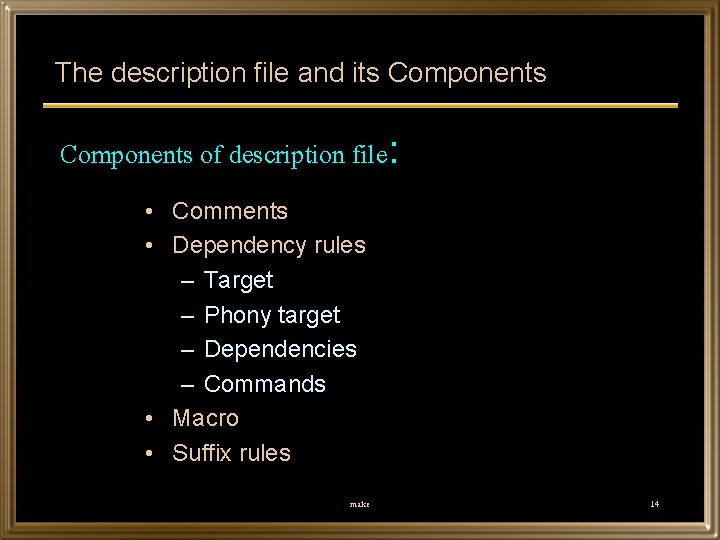

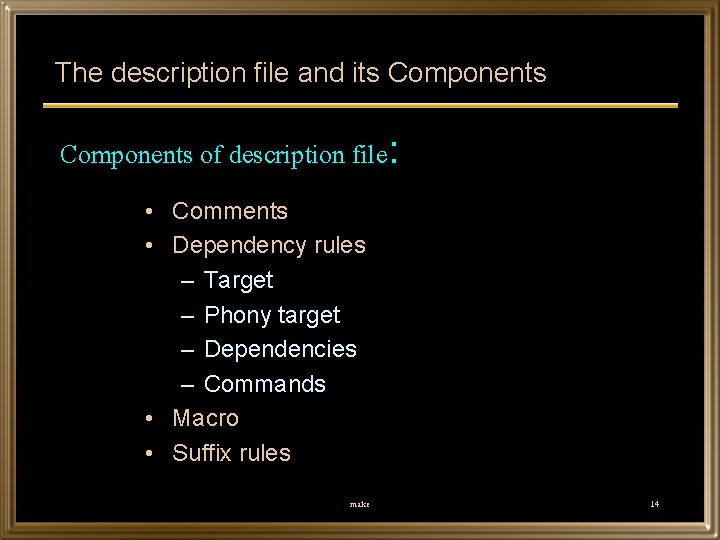

The description file and its Components of description file: • Comments • Dependency rules – Target – Phony target – Dependencies – Commands • Macro • Suffix rules make 14

The description file and its Components • Comments ������ comment ���� description file ����������� pound sign (#) �������� ignored ��� make Example ����������� ������ # This is comment line in description file #This is comment line 2 make 15

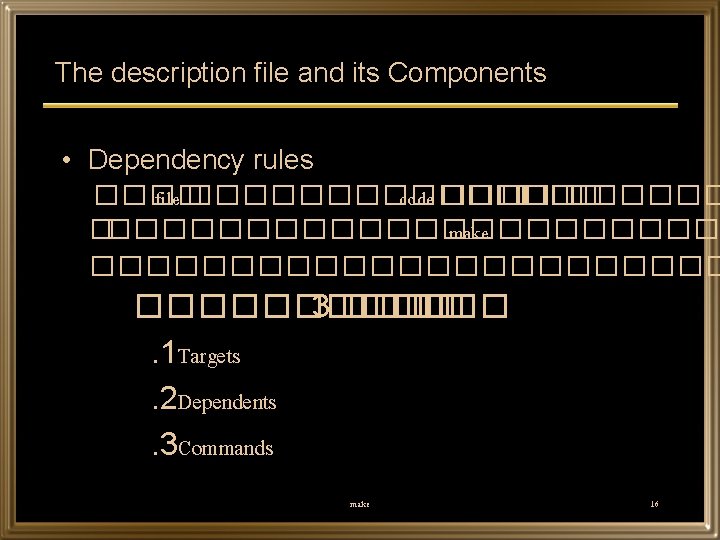

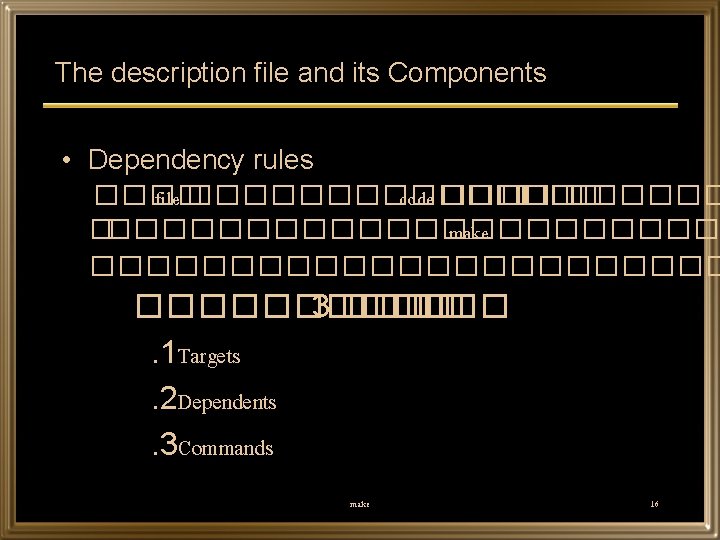

The description file and its Components • Dependency rules ���� file ������� code ��������������� make ������������ 3 ���� ���. 1 Targets. 2 Dependents. 3 Commands make 16

The description file and its Components • �������� dependency rule target 1[ target 2 …] : [dependency 1 …][; commands[ >]tab> command[ ���� target mod 1. o : mod 1. c dependency cc -c mod 1. c tab command make 17

The description file and its Components • ����� � target_1 : dependency_1…. dependency_n dependency_n+1; … command_1 ; command_2 ; command_3; …; … ; …command_m make 18

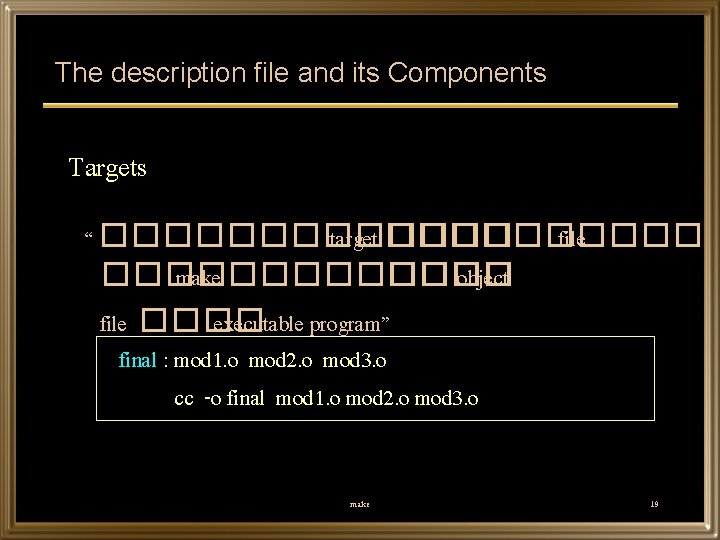

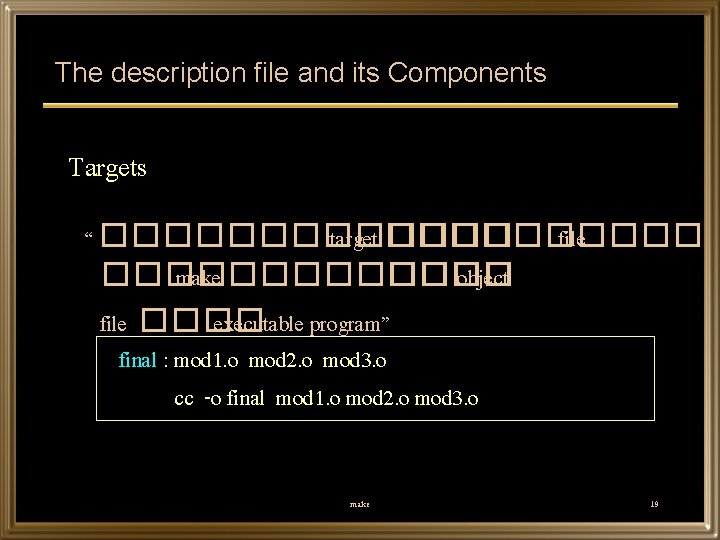

The description file and its Components Targets “ ������� target ����� file ���� make ����� object file ���� executable program” final : mod 1. o mod 2. o mod 3. o cc -o final mod 1. o mod 2. o mod 3. o make 19

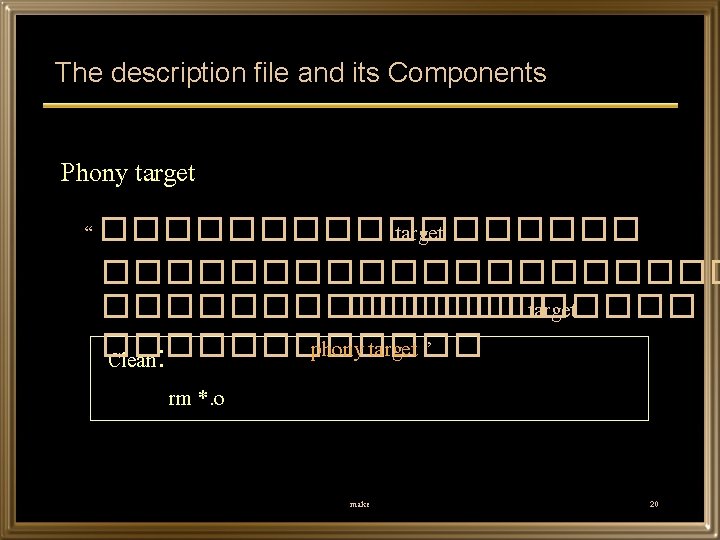

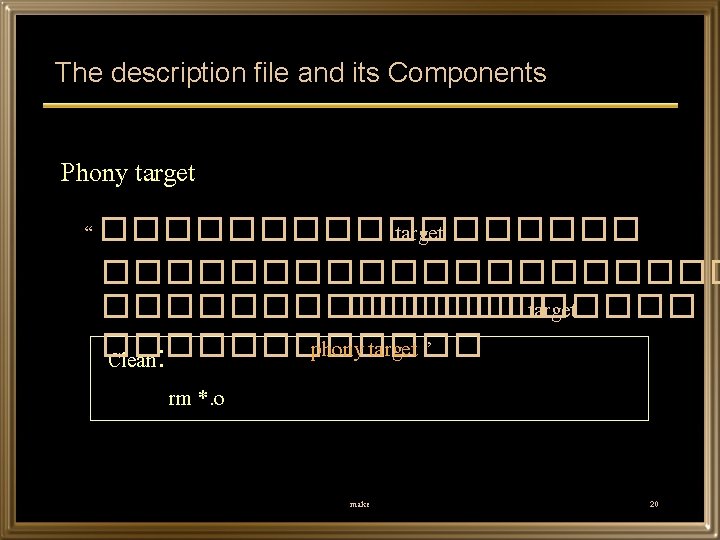

The description file and its Components Phony target “ ��������� target ���������� ������ target ������ phony target ” Clean: rm *. o make 20

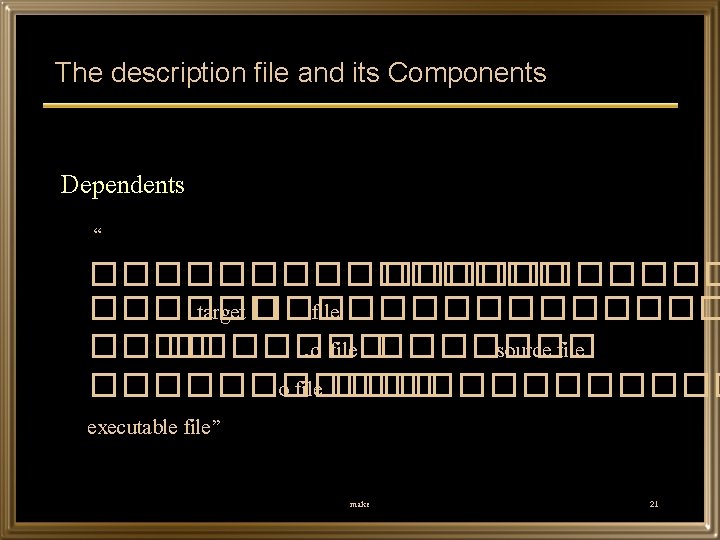

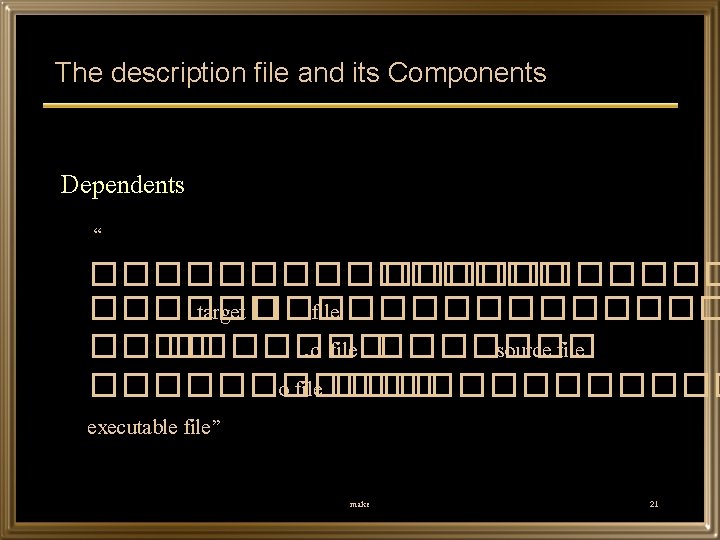

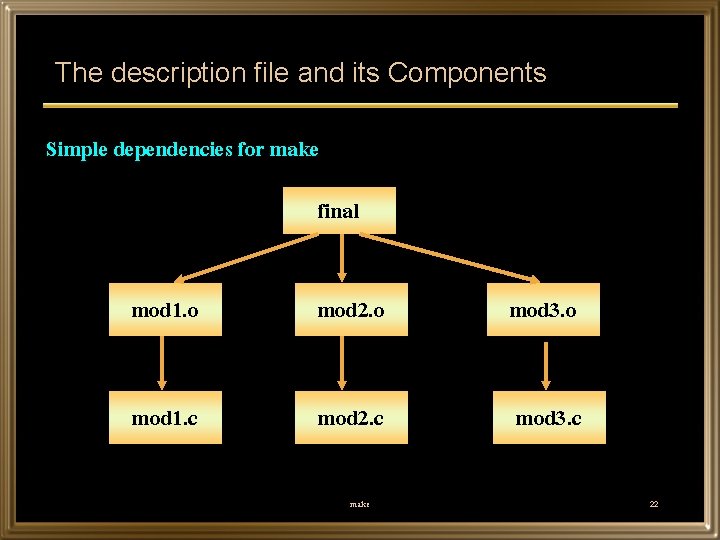

The description file and its Components Dependents “ �������� ������ target ��� file �������. c file ������� source file ������. o file ������� executable file” make 21

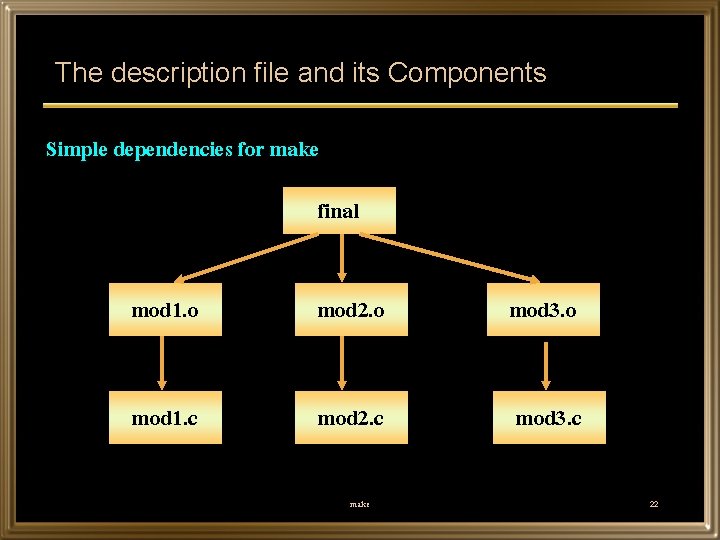

The description file and its Components Simple dependencies for make final mod 1. o mod 2. o mod 3. o mod 1. c mod 2. c mod 3. c make 22

The description file and its Components commands “����� command ������� shell ���������� ��� default ���� make ����� /bin/sh shell ��� default ���������� macro SHELL= /bin/sh �� description file” make 23

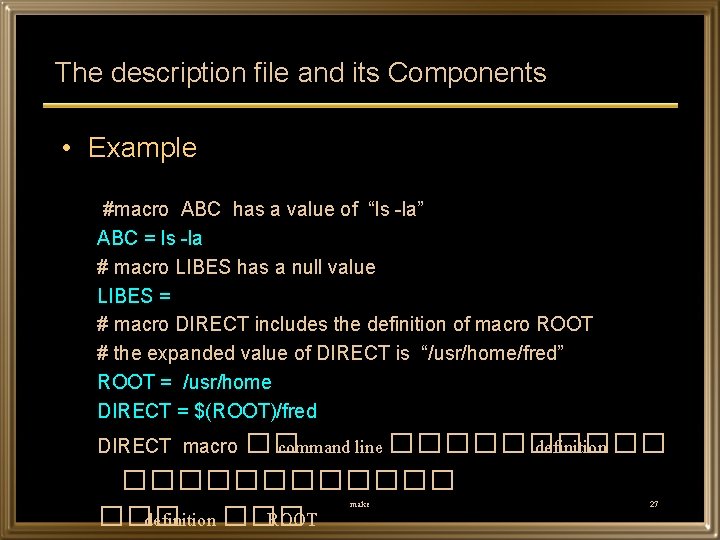

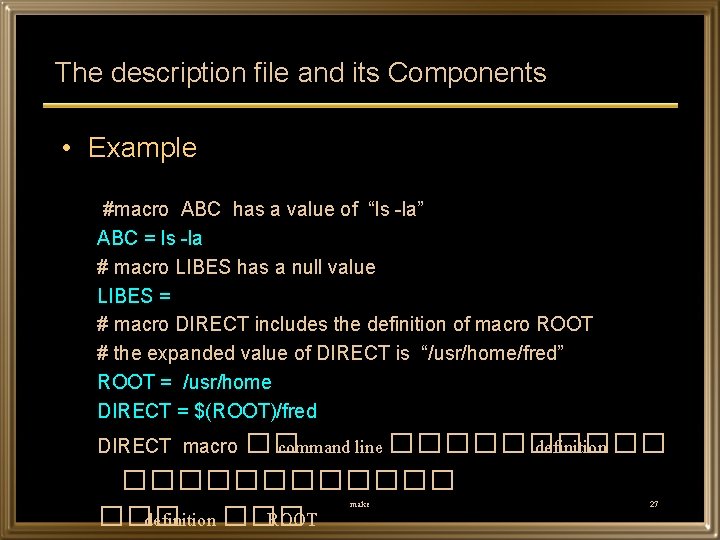

The description file and its Components • Macro used to define setting : *platform-specific commands * * * list of required files for target list of command options so on • make reads all the macro definitions before executing any commands • it is often convenient to put all the macro definitions at the head of the makefile, but this is necessary make 25

The description file and its Components • Macro format and Usage macro_name = value ��� macro_name ���������� value ������ define ���� make �������� value �� macro_name ������� description file ������� macro ���������� : . 1��������� macro. 2�������� equal sign(=) make 26. 3����� string ������� value

The description file and its Components • Example #macro ABC has a value of “ls -la” ABC = ls -la # macro LIBES has a null value LIBES = # macro DIRECT includes the definition of macro ROOT # the expanded value of DIRECT is “/usr/home/fred” ROOT = /usr/home DIRECT = $(ROOT)/fred DIRECT macro �� command line ����� definition ������ make ��� definition ��� ROOT 27

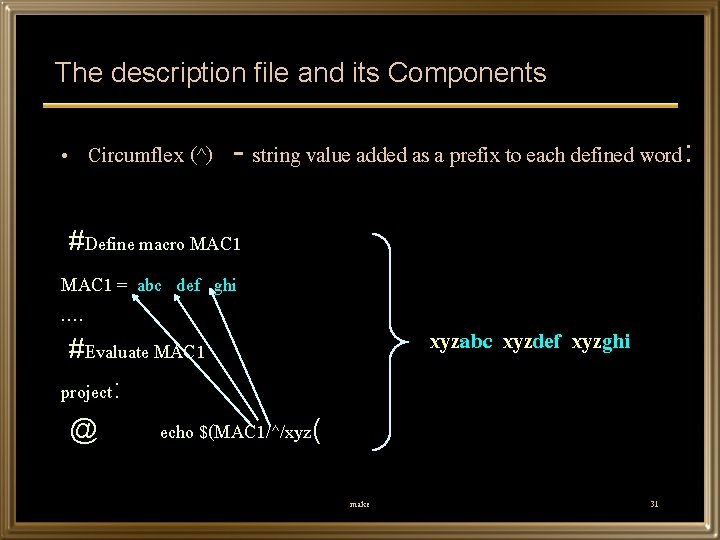

The description file and its Components • ������ macro substitution 1. ������� macro ���� string 1 ��� macro ���� string 2 : string 1 = string 2[( )$]MACRO • ���� #Define macro MAC 1 = xxx yyy zzz … #Evaluate MAC 1 project: @echo $(MAC 1 : yyy = abc( make xxx abc zzz 29

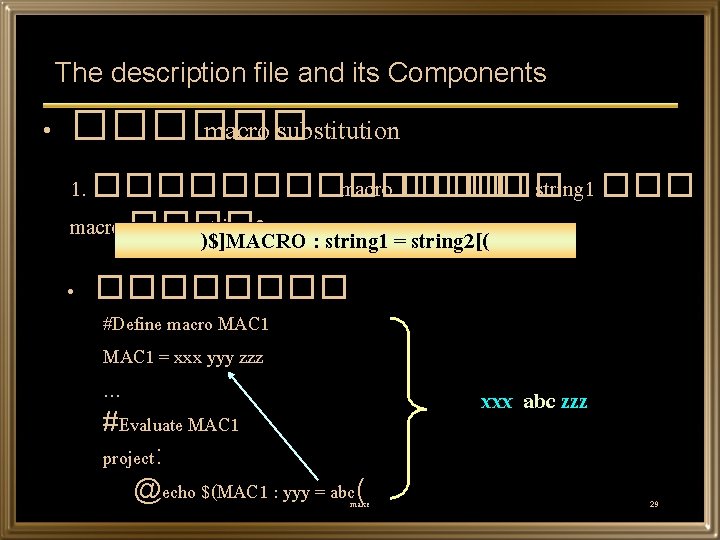

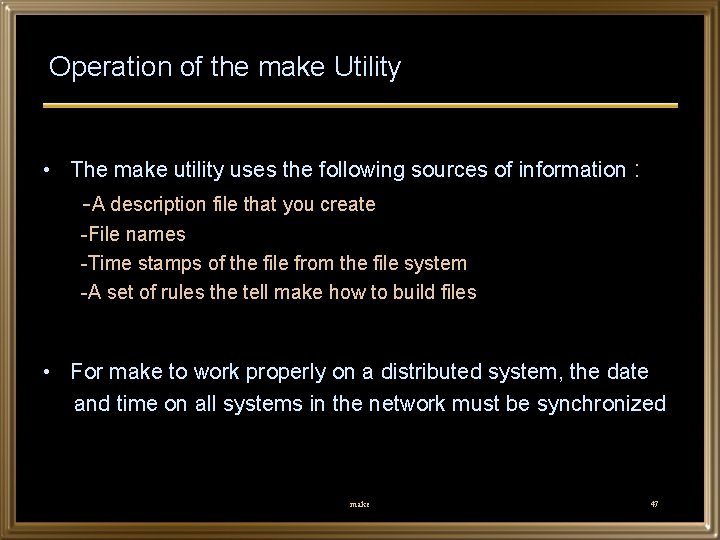

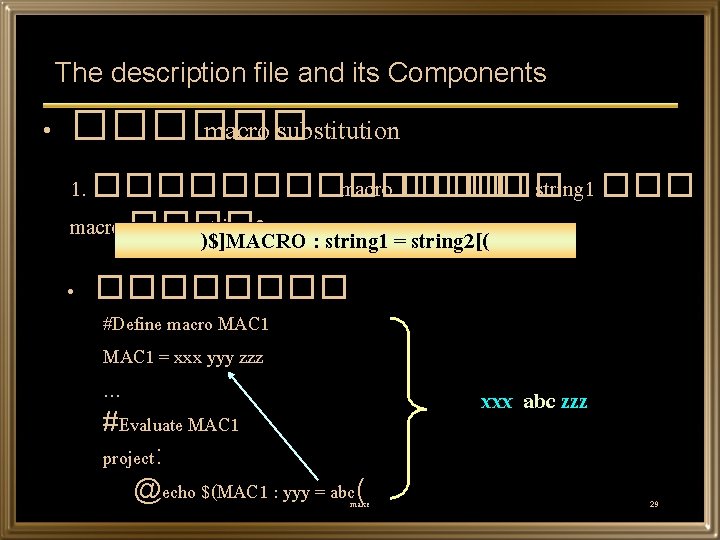

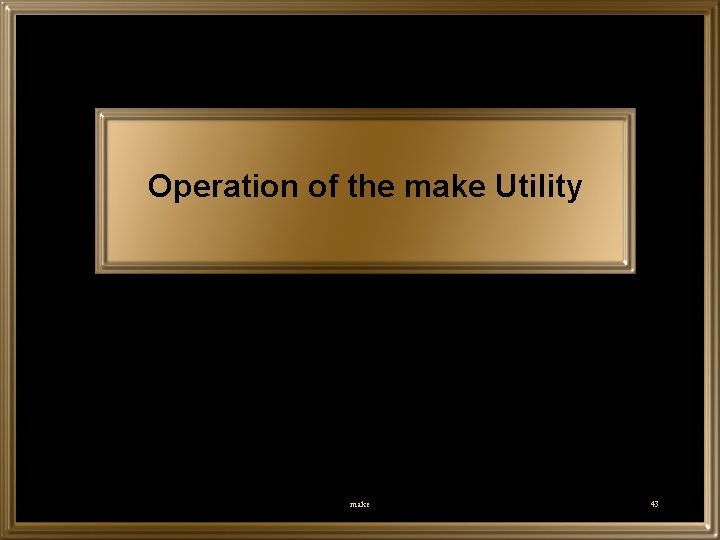

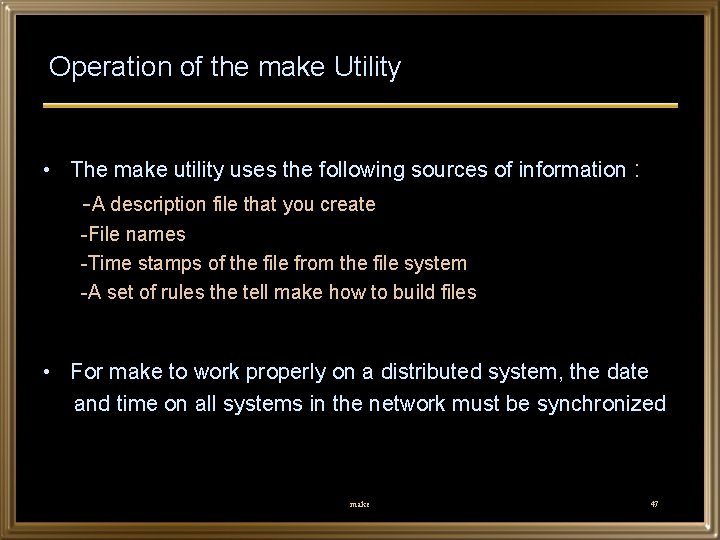

![The description file and its Components 2 word location parameterMACROlocationstring The description file and its Components 2. ����� ��� �� word ���������� location parameter)$]MACRO/location/string[(](https://slidetodoc.com/presentation_image_h2/6164e2467f836b911b7edc5478b338c6/image-30.jpg)

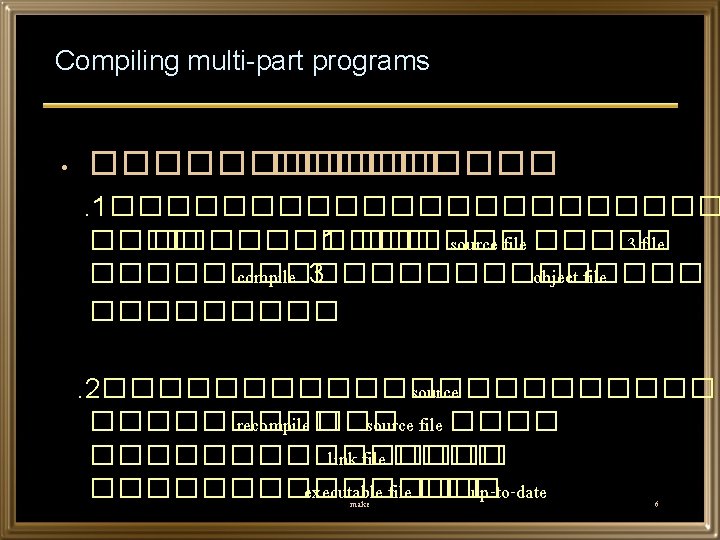

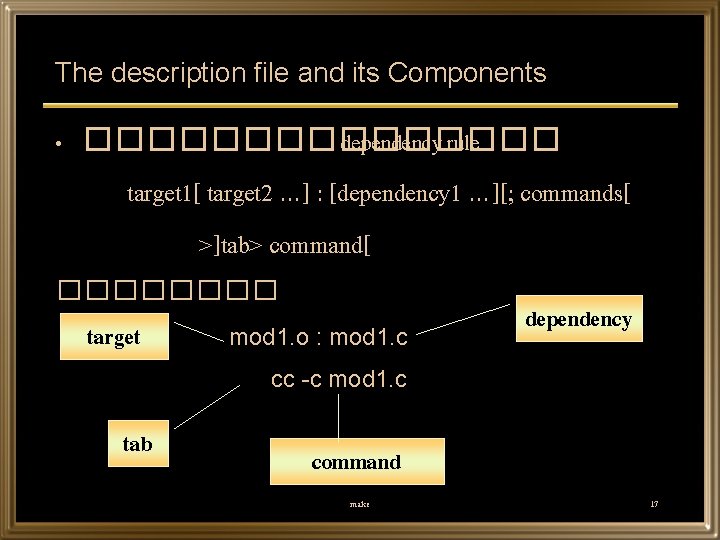

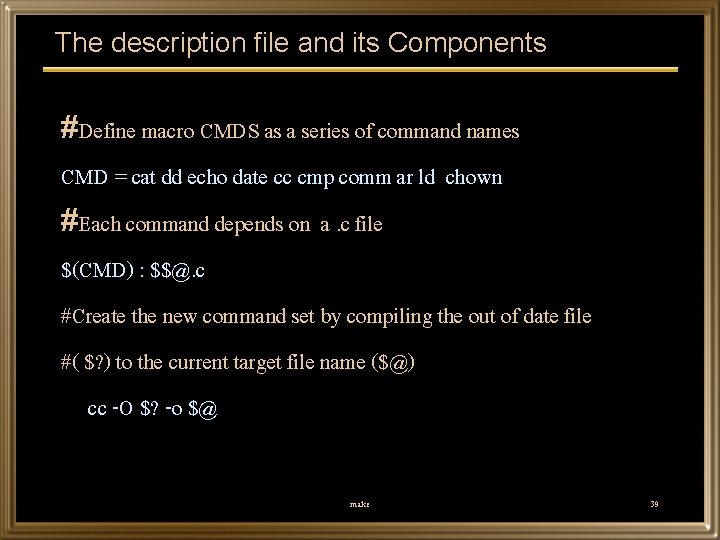

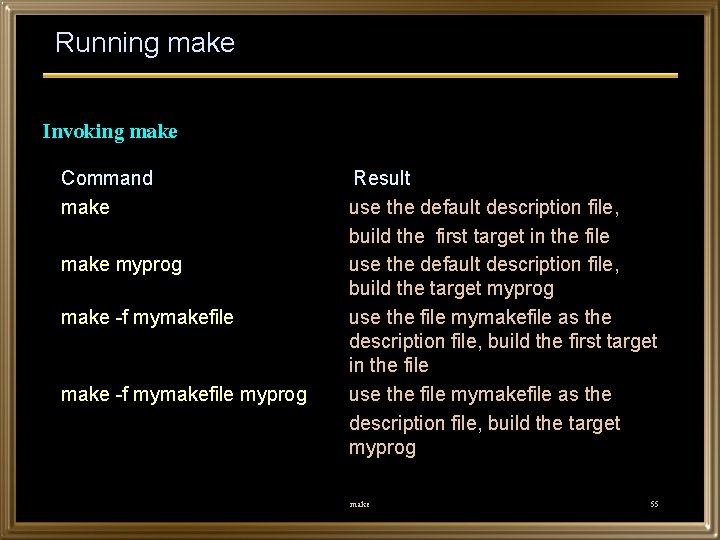

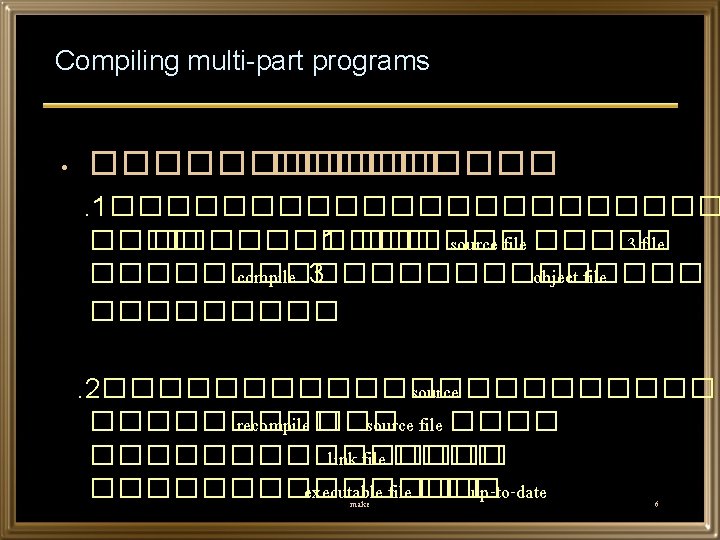

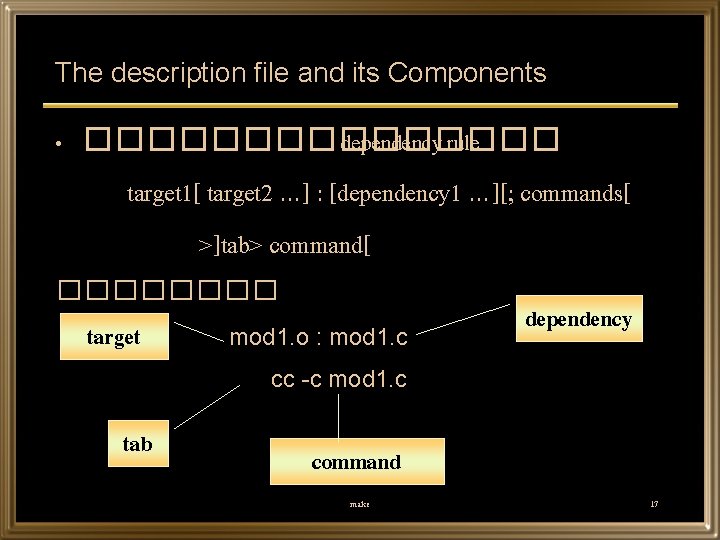

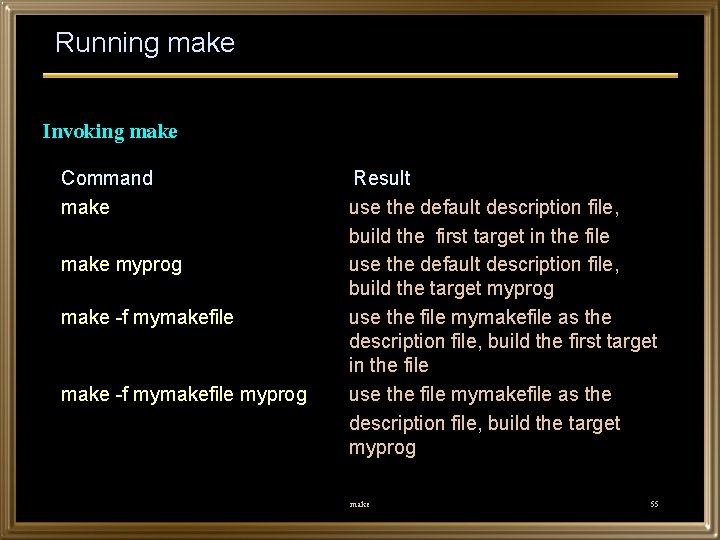

The description file and its Components 2. ����� ��� �� word ���������� location parameter)$]MACRO/location/string[( ��������� ��� location : Circumflex (^) Asterisk (*) Dollar sign($) make 30

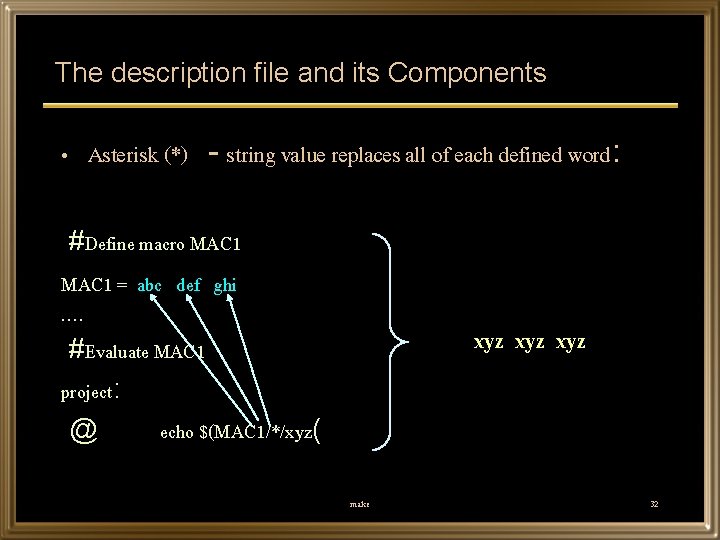

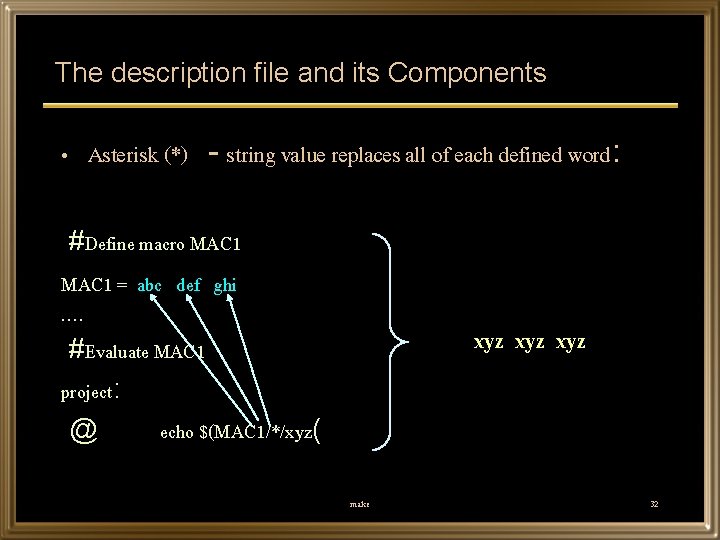

The description file and its Components • Circumflex (^) - string value added as a prefix to each defined word: #Define macro MAC 1 = abc def ghi. … #Evaluate MAC 1 project: @ echo $(MAC 1/^/xyz( xyzabc xyzdef xyzghi make 31

The description file and its Components • Asterisk (*) - string value replaces all of each defined word: #Define macro MAC 1 = abc def ghi. … #Evaluate MAC 1 project: @ echo $(MAC 1/*/xyz( xyz xyz make 32

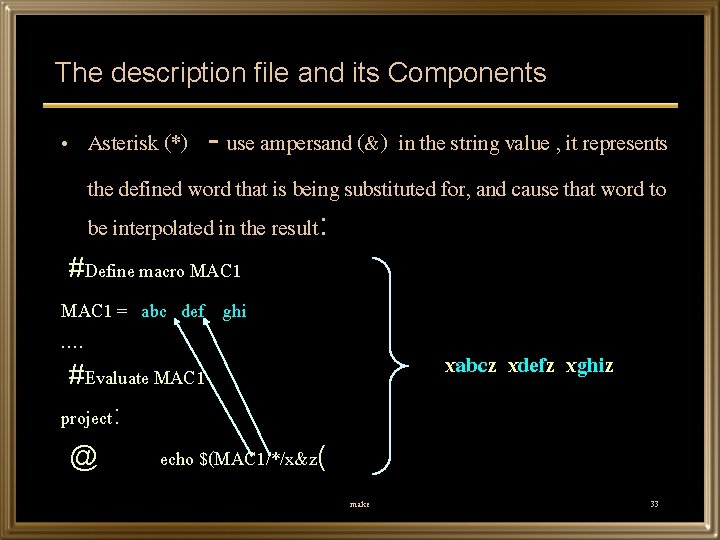

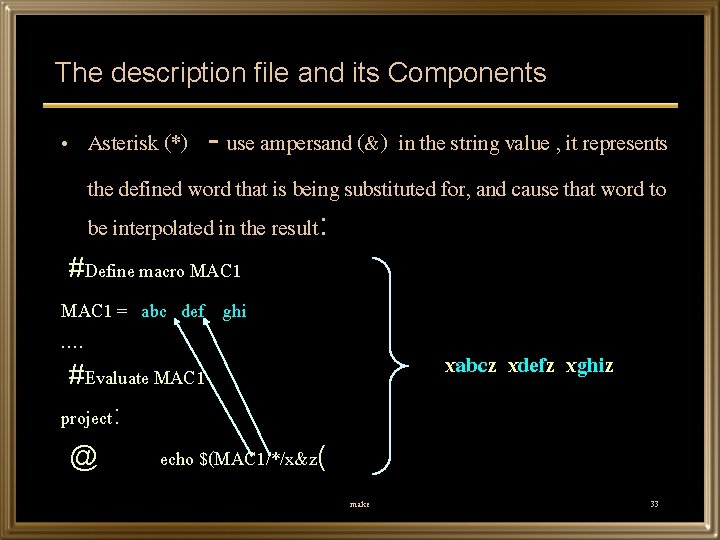

The description file and its Components • Asterisk (*) - use ampersand (&) in the string value , it represents the defined word that is being substituted for, and cause that word to be interpolated in the result: #Define macro MAC 1 = abc def ghi. … #Evaluate MAC 1 project: @ echo $(MAC 1/*/x&z( xabcz xdefz xghiz make 33

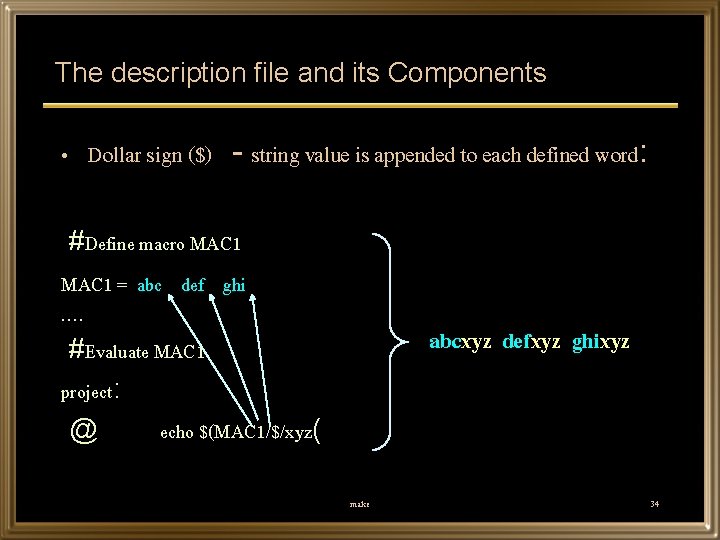

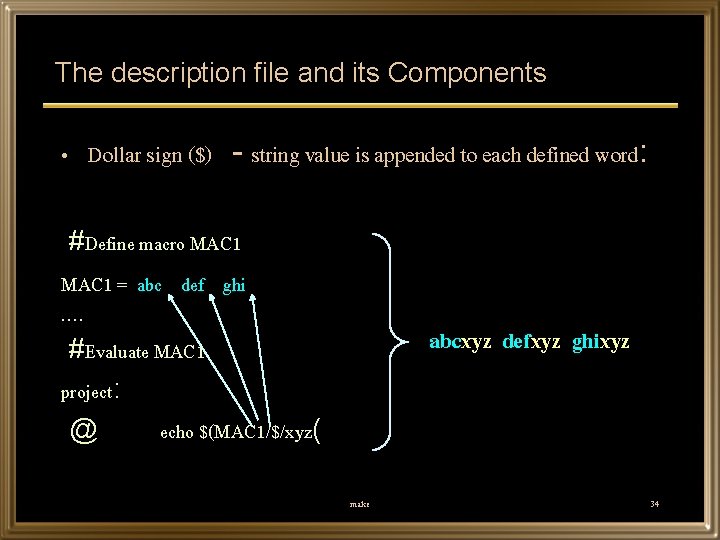

The description file and its Components • Dollar sign ($) - string value is appended to each defined word: #Define macro MAC 1 = abc def ghi. … #Evaluate MAC 1 project: @ echo $(MAC 1/$/xyz( abcxyz defxyz ghixyz make 34

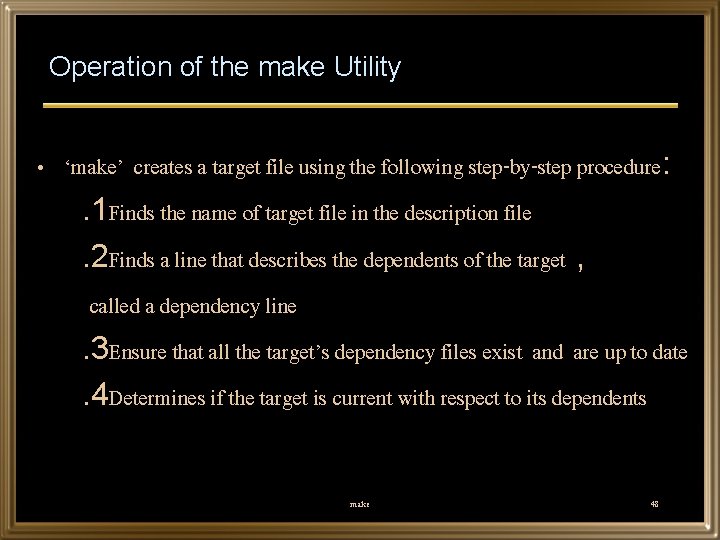

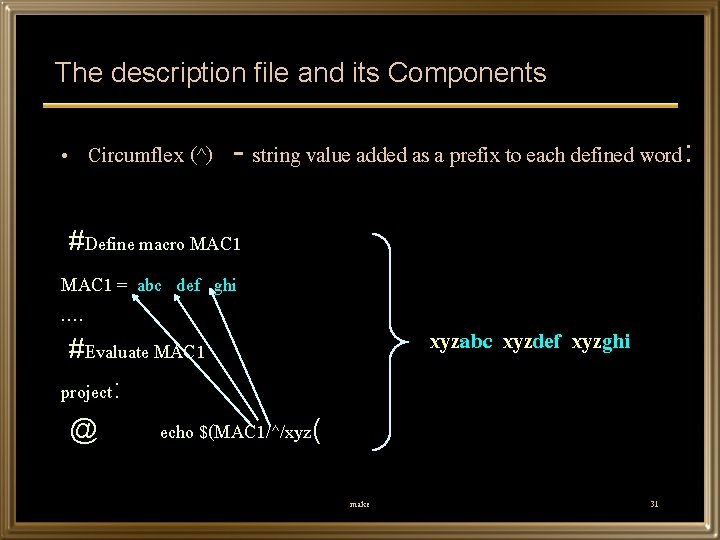

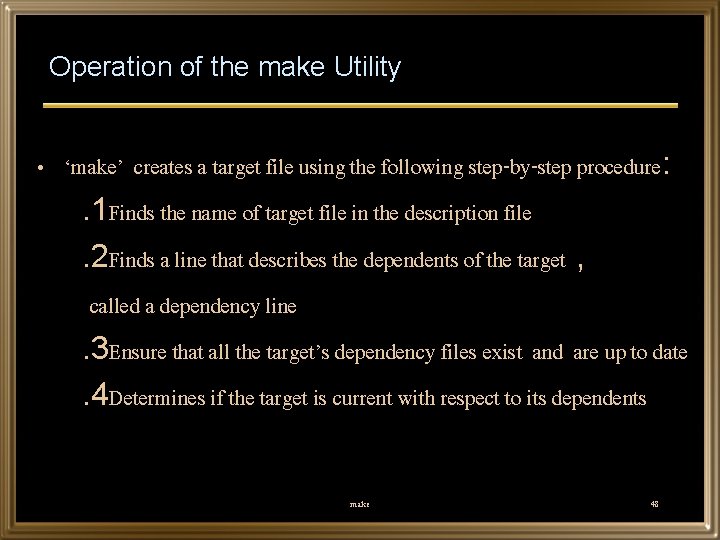

![The description file and its Components 3 MACRO string 1 string 2 The description file and its Components . 3 ���������� )$]MACRO? string 1: string 2[(](https://slidetodoc.com/presentation_image_h2/6164e2467f836b911b7edc5478b338c6/image-35.jpg)

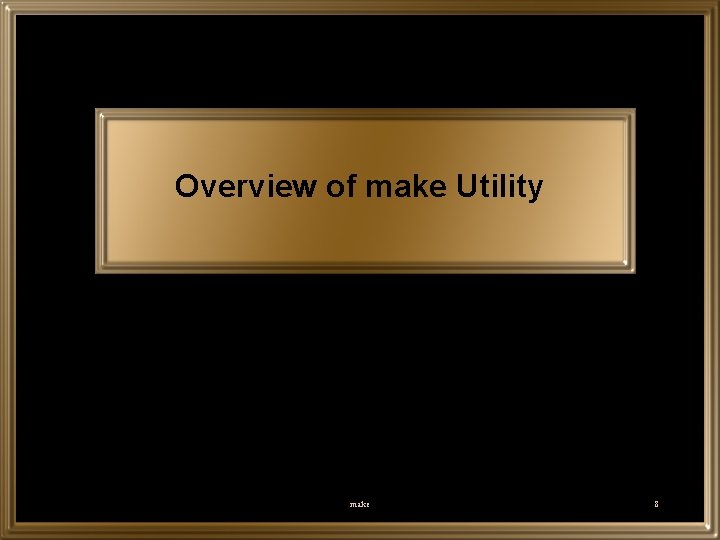

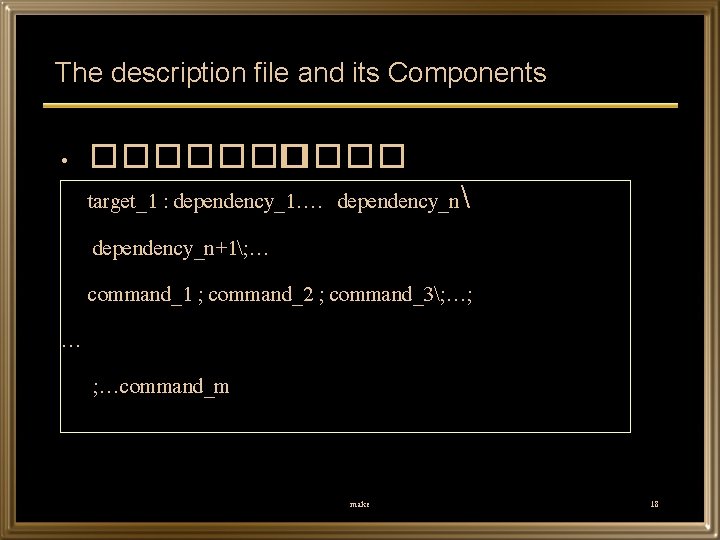

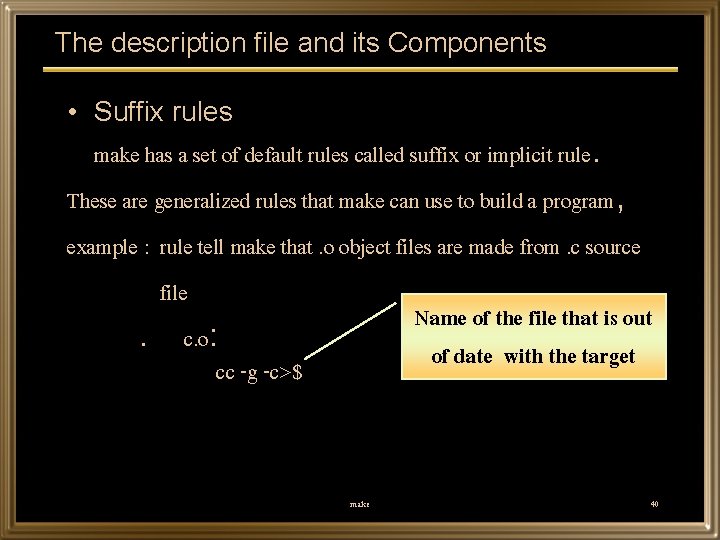

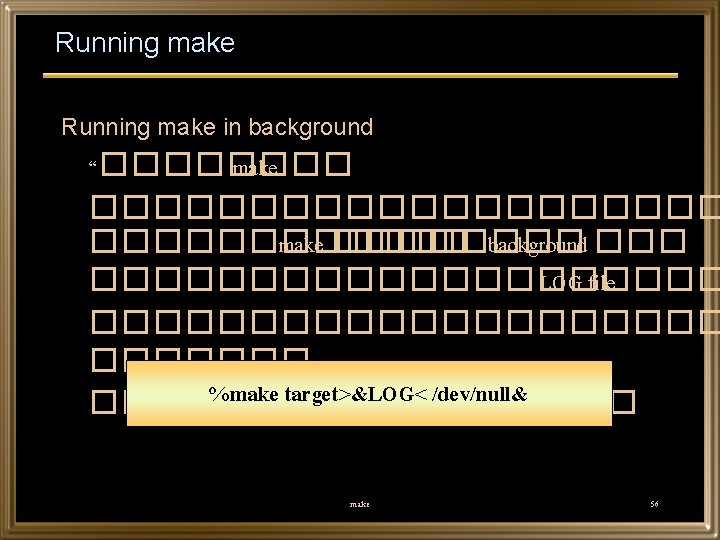

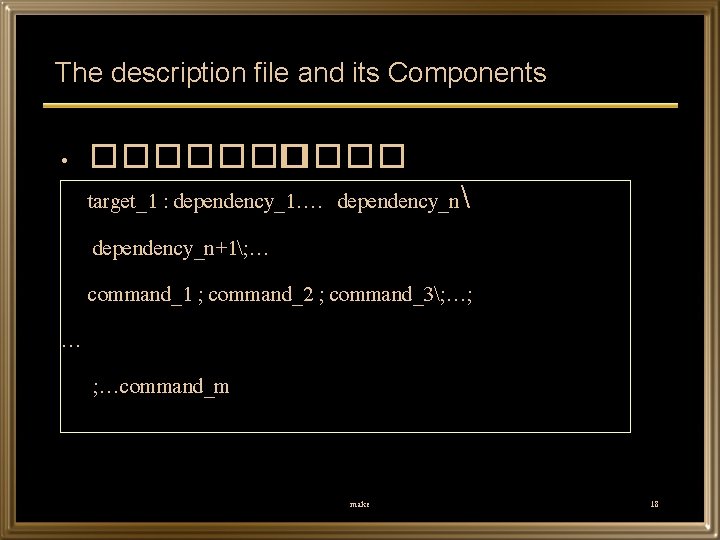

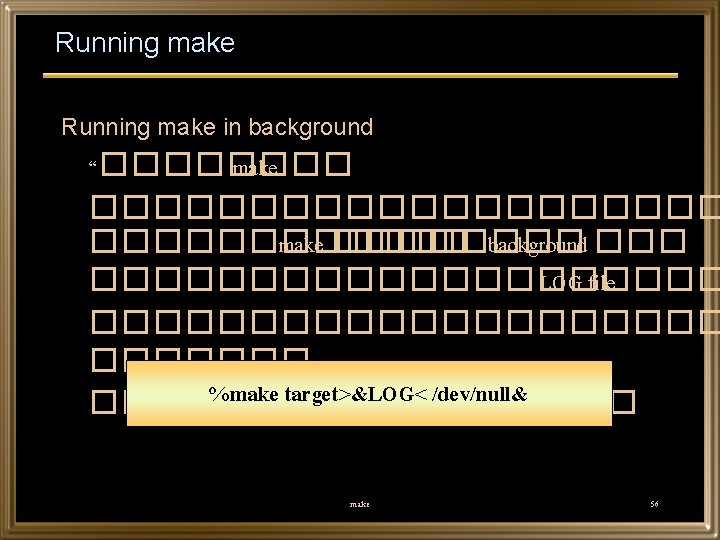

The description file and its Components . 3 ���������� )$]MACRO? string 1: string 2[( ���������� : #Define macro MAC 1 = abc def ghi. … Used #Evaluate MAC 1 MAC 2 , MAC 2 is not defined. project: @ echo $(MAC 1? uvw : xyz( make uvw 456 35

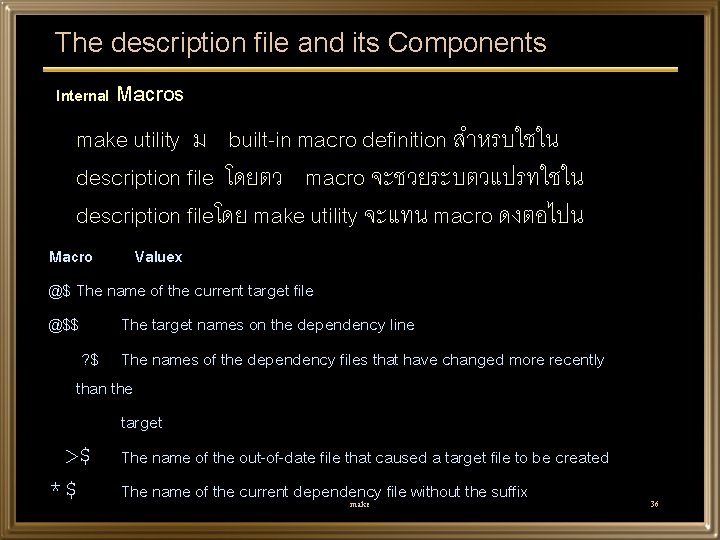

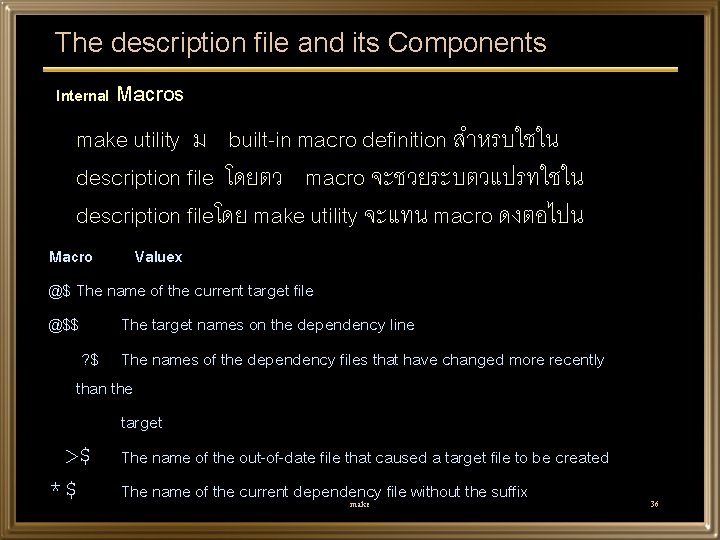

The description file and its Components Macros make utility ม built-in macro definition สำหรบใชใน description file โดยตว macro จะชวยระบตวแปรทใชใน description fileโดย make utility จะแทน macro ดงตอไปน Internal Macro Valuex @$ The name of the current target file @$$ The target names on the dependency line ? $ The names of the dependency files that have changed more recently than the target >$ The name of the out-of-date file that caused a target file to be created *$ The name of the current dependency file without the suffix make 36

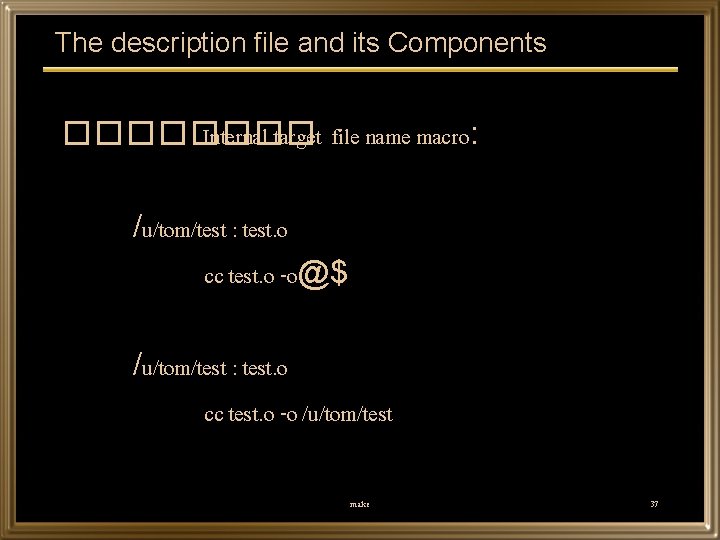

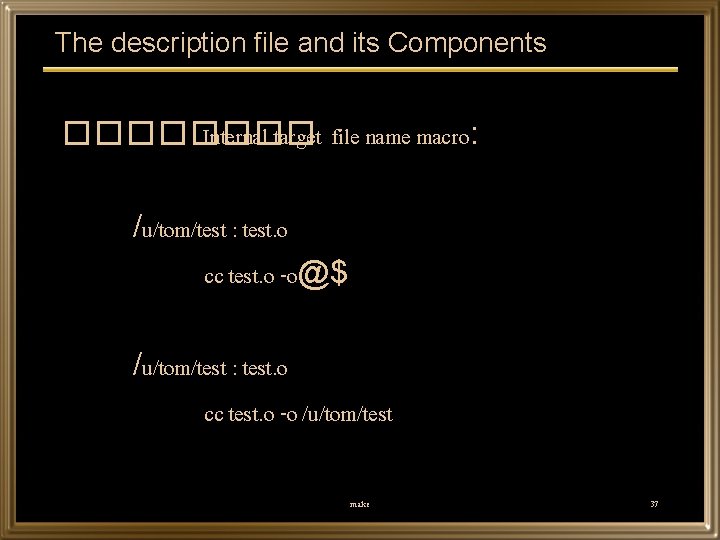

The description file and its Components ���� Internal target file name macro: /u/tom/test : test. o cc test. o -o@$ /u/tom/test : test. o cc test. o -o /u/tom/test make 37

The description file and its Components • ���� Internal label name macro: ������ $$@ ���������� cat : $$@. c ������� cat : cat. c make 38

The description file and its Components #Define macro CMDS as a series of command names CMD = cat dd echo date cc cmp comm ar ld chown #Each command depends on a. c file $(CMD) : $$@. c #Create the new command set by compiling the out of date file #( $? ) to the current target file name ($@) cc -O $? -o $@ make 39

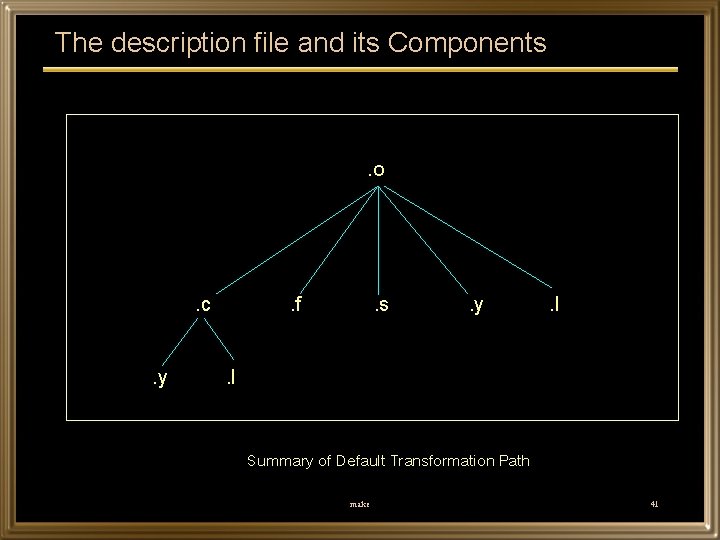

The description file and its Components • Suffix rules make has a set of default rules called suffix or implicit rule. These are generalized rules that make can use to build a program, example : rule tell make that. o object files are made from. c source file Name of the file that is out. c. o: of date with the target cc -g -c>$ make 40

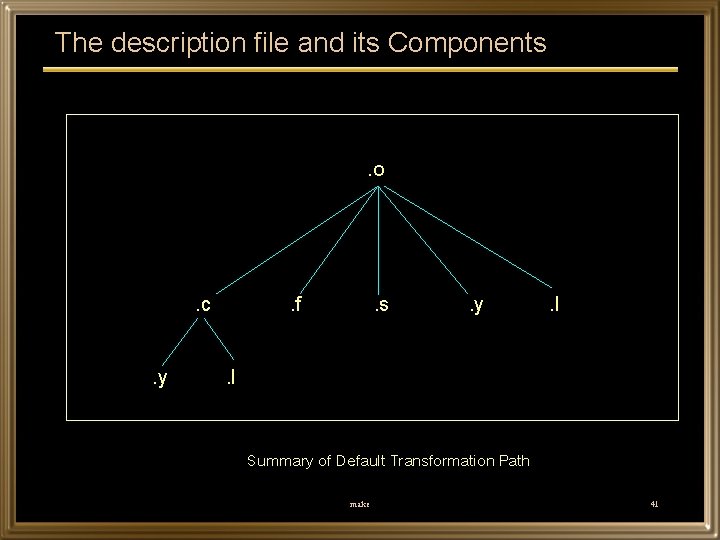

The description file and its Components . o . c. y . f . s . y . l Summary of Default Transformation Path make 41

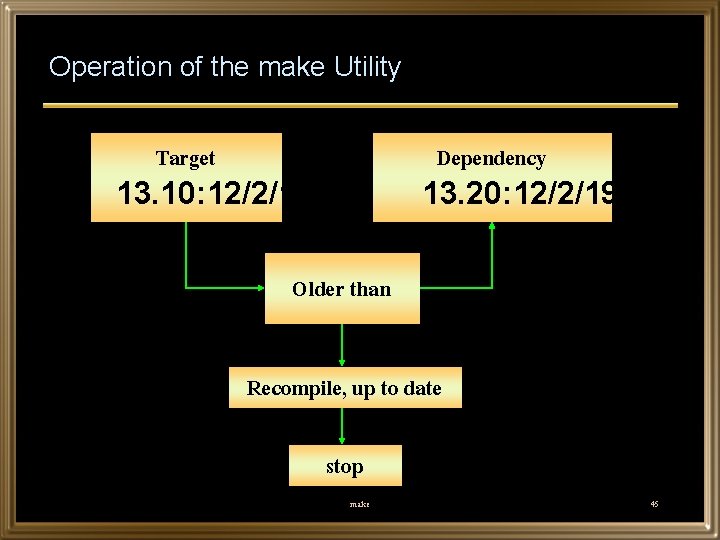

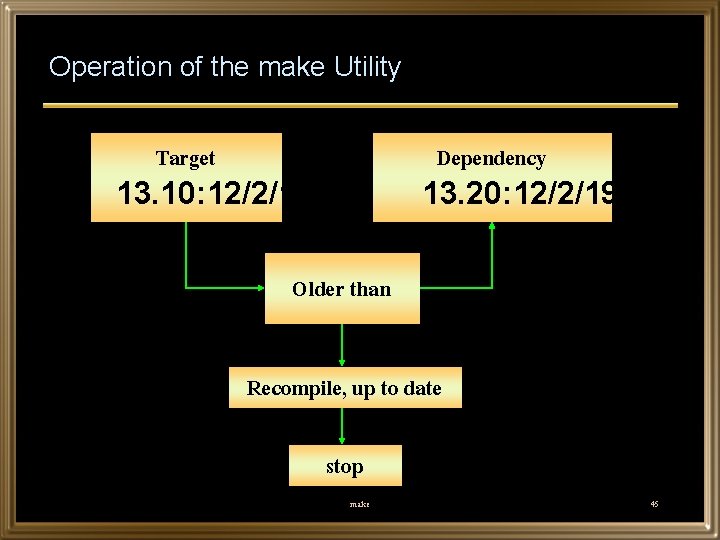

The description file and its Components Example of description file OBJS = file 1. o file 2. o file 3. 0 prog 1 : $(OBJS( cc -o prog 1 $(OBJS( file 1. o : file 1. c mydefs. h cc -c file 1. c file 2. o : file 2. c mydefs. h cc -c file 2. c file 3. o : file 3. c cc -c file 3. c clean: rm $(OBJS( make 42

Operation of the make Utility make 43

Operation of the make Utility Maintain program : • make utility ���������� creation date ����������� target ���� target file ���� date ��� file ��� modify ������� dependency files ���� dependents ��� make ����� target ������� out-of-date ����� make �� rebuild ��� target ������ compile ��������� link ���� command ������� description file make 44

Operation of the make Utility Target 13. 10: 12/2/1999 Dependency 13. 20: 12/2/1999 Older than Recompile, up to date stop make 45

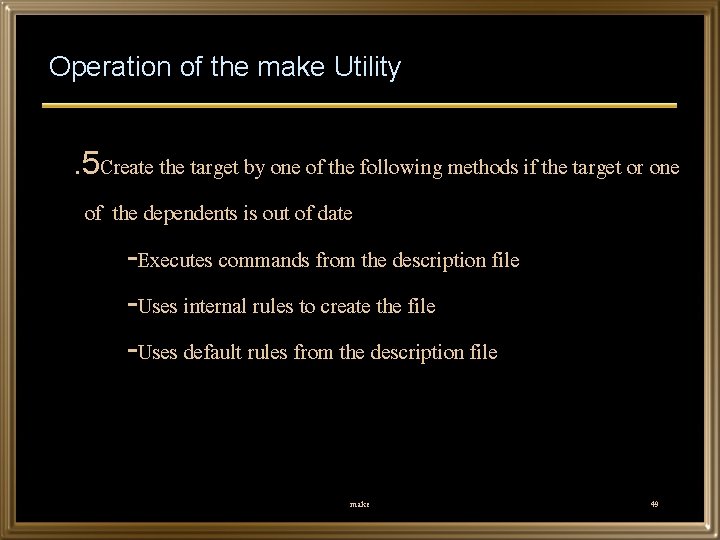

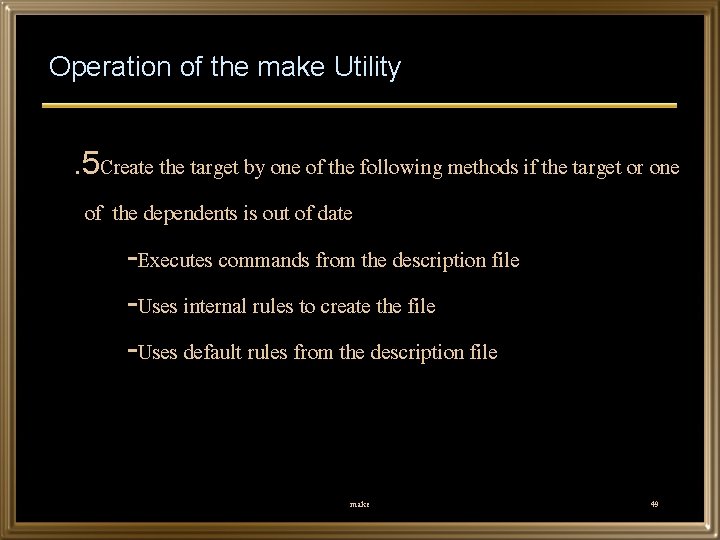

Operation of the make Utility Target 13. 30: 12/2/1999 Dependency 13. 20: 12/2/1999 New than stop make 46

Operation of the make Utility • The make utility uses the following sources of information : -A description file that you create -File names -Time stamps of the file from the file system -A set of rules the tell make how to build files • For make to work properly on a distributed system, the date and time on all systems in the network must be synchronized make 47

Operation of the make Utility • ‘make’ creates a target file using the following step-by-step procedure: . 1 Finds the name of target file in the description file. 2 Finds a line that describes the dependents of the target , called a dependency line. 3 Ensure that all the target’s dependency files exist and are up to date. 4 Determines if the target is current with respect to its dependents make 48

Operation of the make Utility . 5 Create the target by one of the following methods if the target or one of the dependents is out of date -Executes commands from the description file -Uses internal rules to create the file -Uses default rules from the description file make 49

Operation of the make Utility • If all file on the dependency line are up to date when make is run, make indicate that the target is up to date and then stops. • If any dependents are newer than their targets , make recreates only those target that are out of date • If a given target has no dependents, it is always out of date, and make rebuilds it every time you run make 50

Operation of the make Utility • The make process works from the top down in determining what targets need to be rebuilt and from the bottom up in the actual rebuilding stage make 51

Running make 52

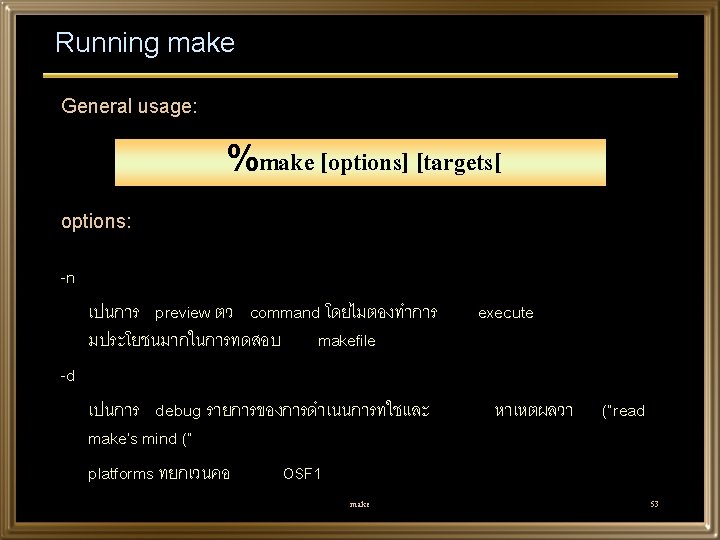

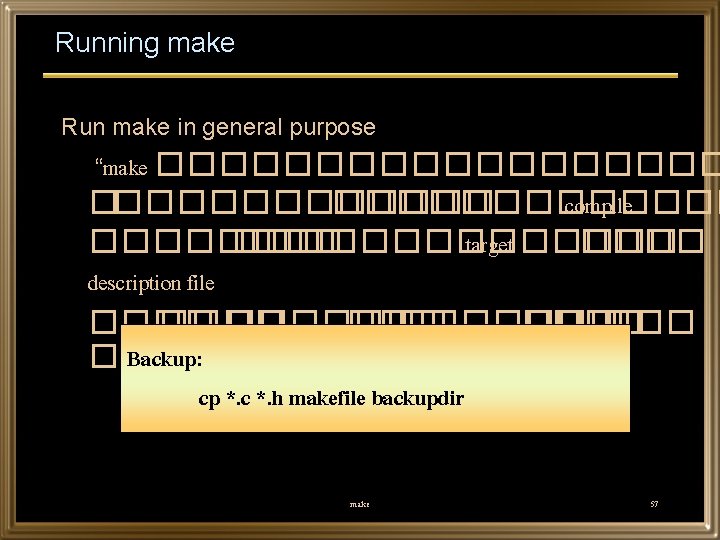

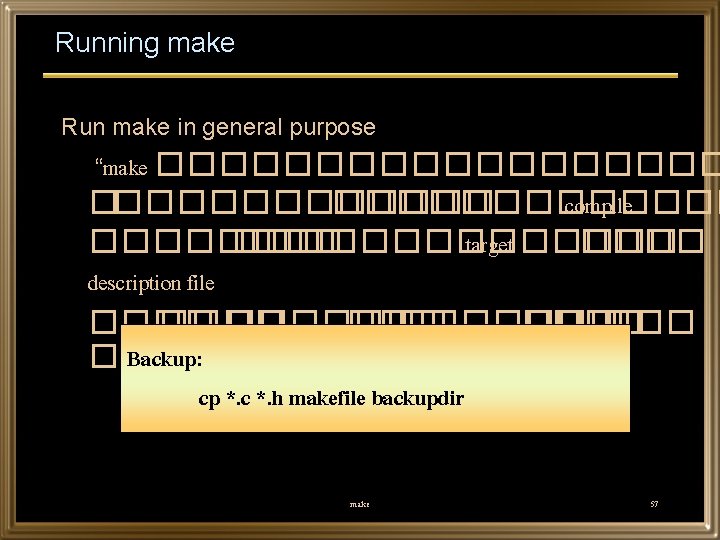

Running make -e Environment variables ยกเวน built-ins -f makefile_name ถามการตงชอ description file ทไมใช Makefile จะตองใช option นโดยการระบชอ ทตงขน (คนดวยชองวางระหวาง filename( -p –f /dev/null [|less[ พมพ built-in rules makefile หรอ description file option กบ 54

Running make Invoking make Command make myprog make -f mymakefile myprog Result use the default description file, build the first target in the file use the default description file, build the target myprog use the file mymakefile as the description file, build the first target in the file use the file mymakefile as the description file, build the target myprog make 55

Running make Run make in general purpose “make ������������� compile �������������� target ���� description file ��������� �� ��� Backup: ��� file ������ ” ���� : cp *. c *. h makefile backupdir make 57