Linear Collider Flavour Identification Programme of Work 2005

- Slides: 62

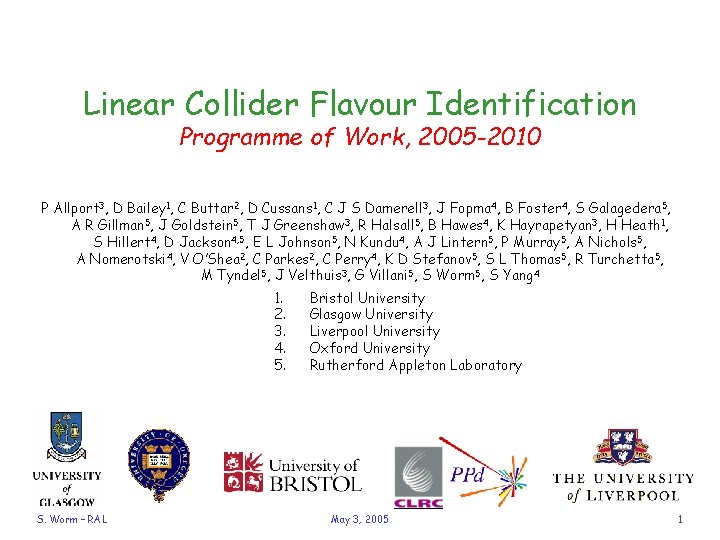

Linear Collider Flavour Identification Programme of Work, 2005 -2010 P Allport 3, D Bailey 1, C Buttar 2, D Cussans 1, C J S Damerell 3, J Fopma 4, B Foster 4, S Galagedera 5, A R Gillman 5, J Goldstein 5, T J Greenshaw 3, R Halsall 5, B Hawes 4, K Hayrapetyan 3, H Heath 1, S Hillert 4, D Jackson 4, 5, E L Johnson 5, N Kundu 4, A J Lintern 5, P Murray 5, A Nichols 5, A Nomerotski 4, V O’Shea 2, C Parkes 2, C Perry 4, K D Stefanov 5, S L Thomas 5, R Turchetta 5, M Tyndel 5, J Velthuis 3, G Villani 5, S Worm 5, S Yang 4 1. 2. 3. 4. 5. S. Worm – RAL Bristol University Glasgow University Liverpool University Oxford University Rutherford Appleton Laboratory May 3, 2005 1

Linear Collider Flavour Identification – Goals The LCFI collaboration has enjoyed 3 years of success in ILC vertex detector R&D o The new five-year proposal moves us from Research into prototype detector Development – Overall goal is to have a fully-functional and test-beam proven detector module, including sensors, readout, and mechanical support, ready in 2010. – The challenge is to take bench-top devices and develop them into fully functioning modules – Successful development will put us in the best possible position to build the ILC vertex detector o New proposal includes – 5 institutions – 58 people, plus several students – 7 new RA posts S. Worm – RAL May 3, 2005 2

LCFI Outline o 8 Work Packages: – – – – S. Worm – RAL WP 1 WP 2 WP 3 WP 4 WP 5 WP 6 WP 7 WP 8 Simulation and Physics Studies Sensor Development Readout and Drive Electronics External Electronics Integration and Testing Vertex Detector Mechanical Studies Test-beam and EMI Studies Financial and Management May 3, 2005 3

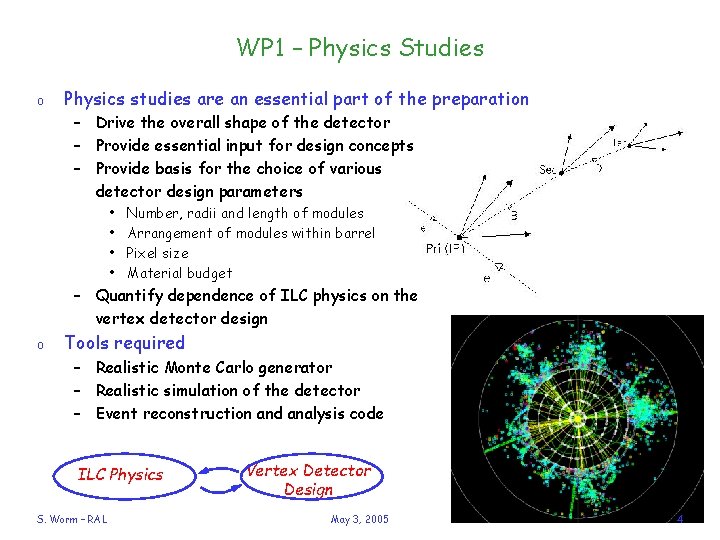

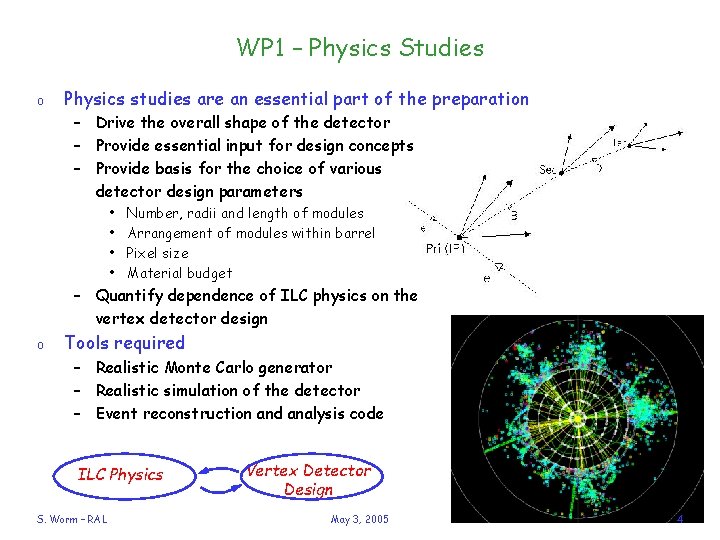

WP 1 – Physics Studies o Physics studies are an essential part of the preparation – Drive the overall shape of the detector – Provide essential input for design concepts – Provide basis for the choice of various detector design parameters • • Number, radii and length of modules Arrangement of modules within barrel Pixel size Material budget – Quantify dependence of ILC physics on the vertex detector design o Tools required – Realistic Monte Carlo generator – Realistic simulation of the detector – Event reconstruction and analysis code ILC Physics S. Worm – RAL Vertex Detector Design May 3, 2005 4

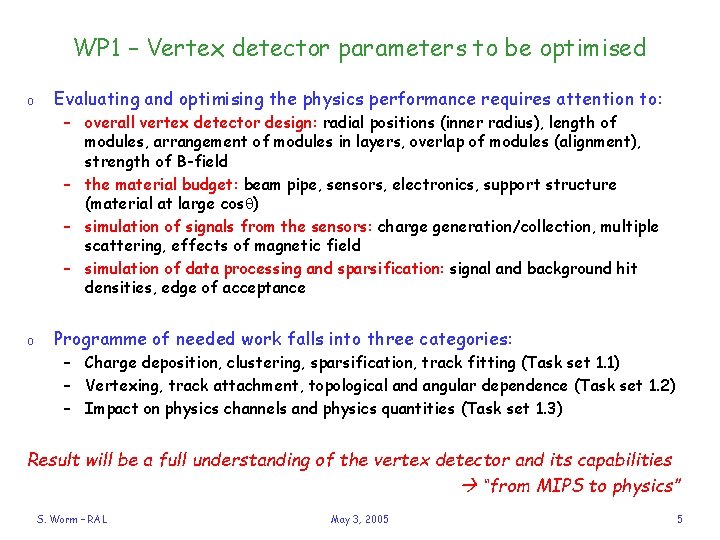

WP 1 – Vertex detector parameters to be optimised o Evaluating and optimising the physics performance requires attention to: – overall vertex detector design: radial positions (inner radius), length of modules, arrangement of modules in layers, overlap of modules (alignment), strength of B-field – the material budget: beam pipe, sensors, electronics, support structure (material at large cosq) – simulation of signals from the sensors: charge generation/collection, multiple scattering, effects of magnetic field – simulation of data processing and sparsification: signal and background hit densities, edge of acceptance o Programme of needed work falls into three categories: – Charge deposition, clustering, sparsification, track fitting (Task set 1. 1) – Vertexing, track attachment, topological and angular dependence (Task set 1. 2) – Impact on physics channels and physics quantities (Task set 1. 3) Result will be a full understanding of the vertex detector and its capabilities “from MIPS to physics” S. Worm – RAL May 3, 2005 5

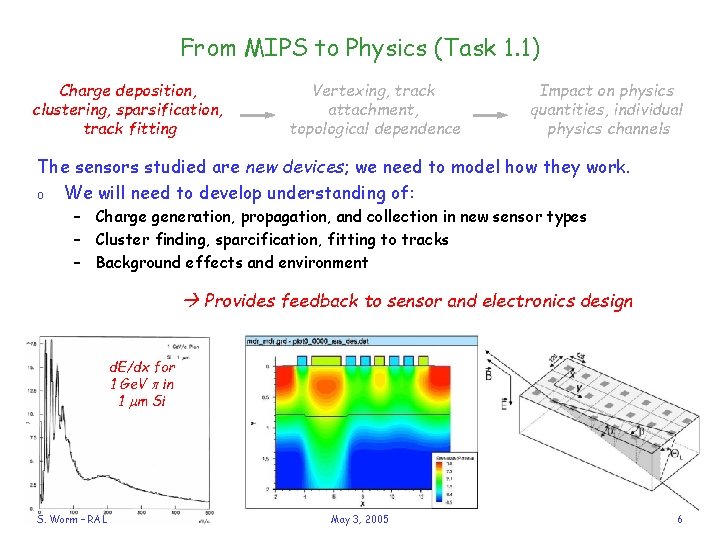

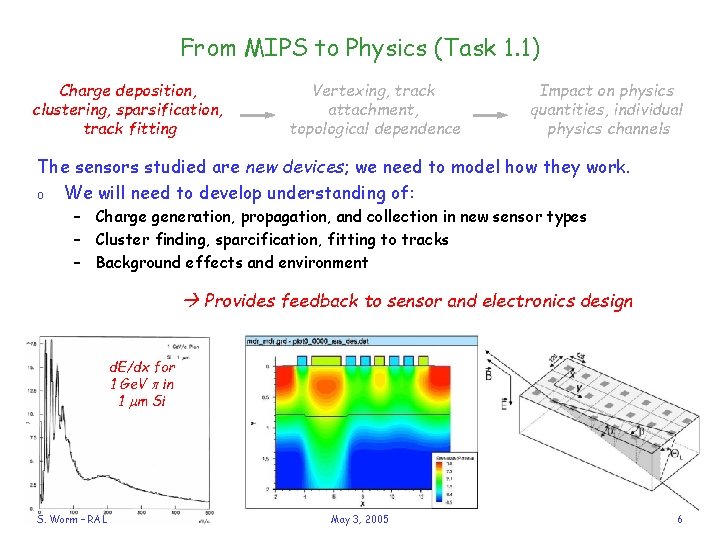

From MIPS to Physics (Task 1. 1) Charge deposition, clustering, sparsification, track fitting Vertexing, track attachment, topological dependence Impact on physics quantities, individual physics channels The sensors studied are new devices; we need to model how they work. o We will need to develop understanding of: – Charge generation, propagation, and collection in new sensor types – Cluster finding, sparcification, fitting to tracks – Background effects and environment Provides feedback to sensor and electronics design d. E/dx for 1 Ge. V p in 1 mm Si S. Worm – RAL May 3, 2005 6

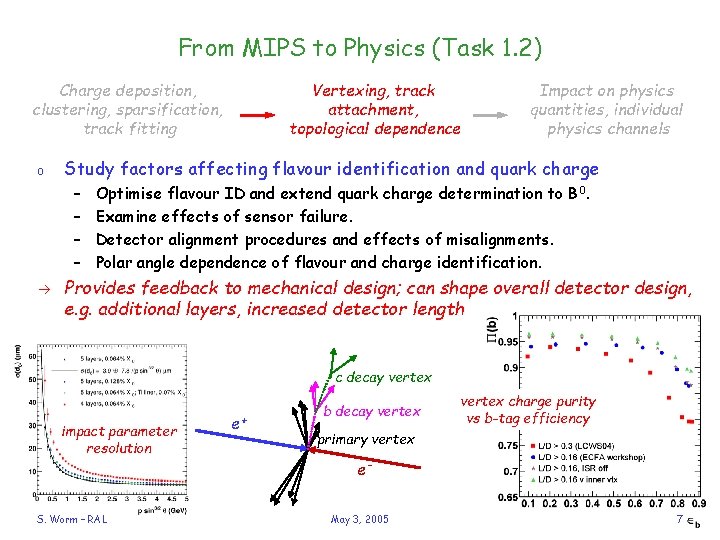

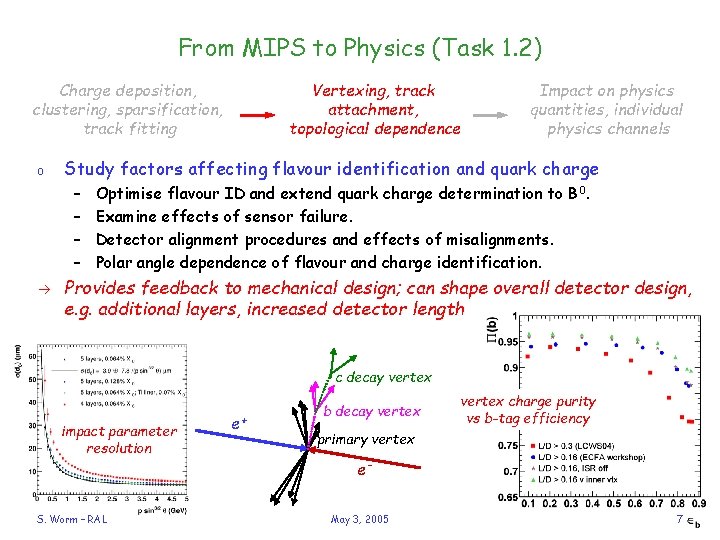

From MIPS to Physics (Task 1. 2) Charge deposition, clustering, sparsification, track fitting o Impact on physics quantities, individual physics channels Study factors affecting flavour identification and quark charge – – Vertexing, track attachment, topological dependence Optimise flavour ID and extend quark charge determination to B 0. Examine effects of sensor failure. Detector alignment procedures and effects of misalignments. Polar angle dependence of flavour and charge identification. Provides feedback to mechanical design; can shape overall detector design, e. g. additional layers, increased detector length c decay vertex impact parameter resolution S. Worm – RAL e+ b decay vertex charge purity vs b-tag efficiency primary vertex e. May 3, 2005 7

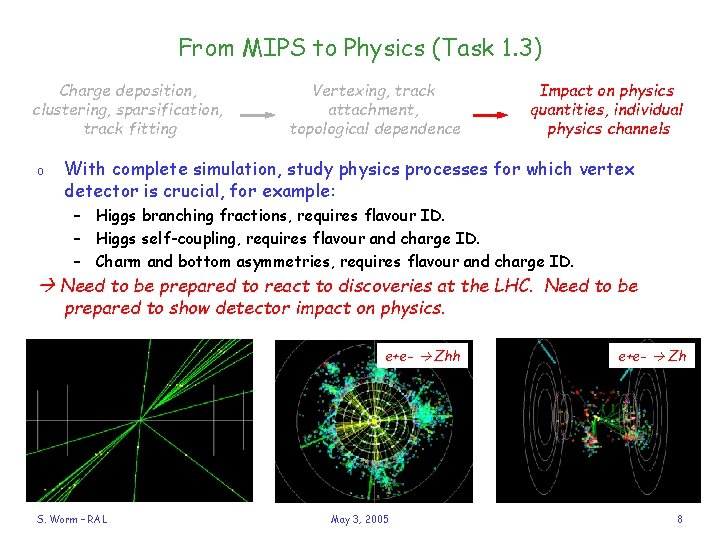

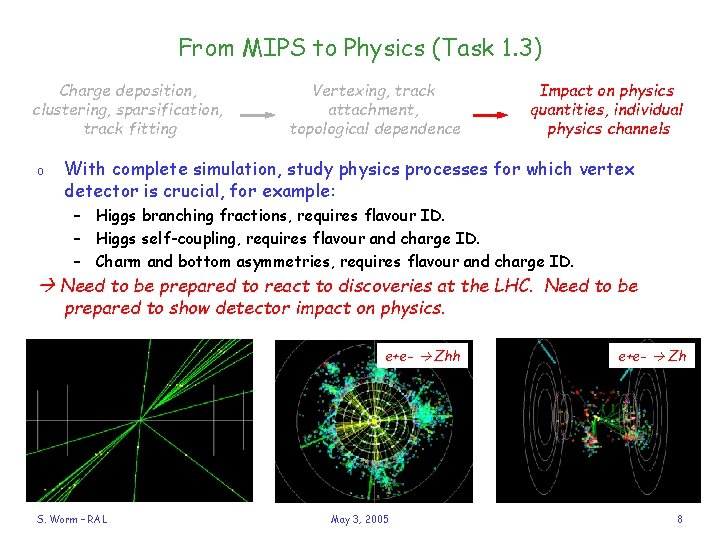

From MIPS to Physics (Task 1. 3) Charge deposition, clustering, sparsification, track fitting o Vertexing, track attachment, topological dependence Impact on physics quantities, individual physics channels With complete simulation, study physics processes for which vertex detector is crucial, for example: – Higgs branching fractions, requires flavour ID. – Higgs self-coupling, requires flavour and charge ID. – Charm and bottom asymmetries, requires flavour and charge ID. Need to be prepared to react to discoveries at the LHC. Need to be prepared to show detector impact on physics. e+e- Zhh S. Worm – RAL May 3, 2005 e+e- Zh 8

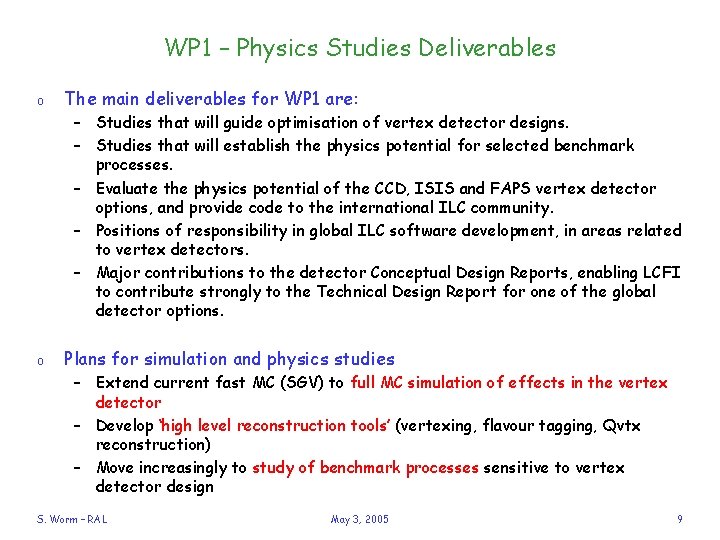

WP 1 – Physics Studies Deliverables o The main deliverables for WP 1 are: – Studies that will guide optimisation of vertex detector designs. – Studies that will establish the physics potential for selected benchmark processes. – Evaluate the physics potential of the CCD, ISIS and FAPS vertex detector options, and provide code to the international ILC community. – Positions of responsibility in global ILC software development, in areas related to vertex detectors. – Major contributions to the detector Conceptual Design Reports, enabling LCFI to contribute strongly to the Technical Design Report for one of the global detector options. o Plans for simulation and physics studies – Extend current fast MC (SGV) to full MC simulation of effects in the vertex detector – Develop ‘high level reconstruction tools’ (vertexing, flavour tagging, Qvtx reconstruction) – Move increasingly to study of benchmark processes sensitive to vertex detector design S. Worm – RAL May 3, 2005 9

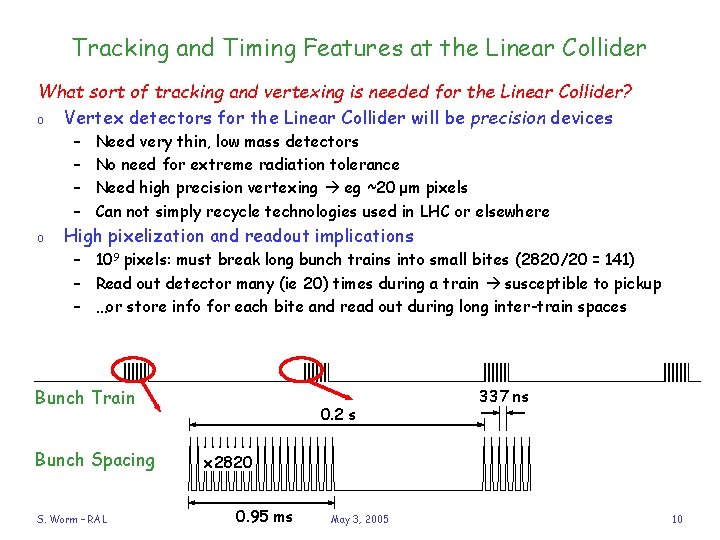

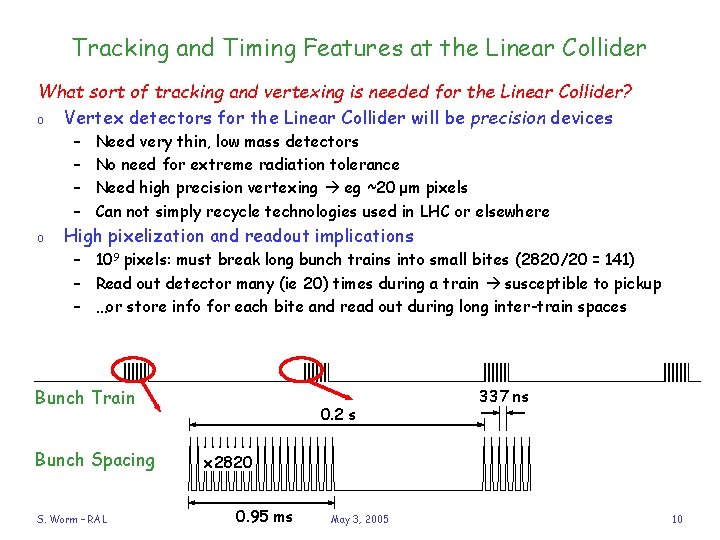

Tracking and Timing Features at the Linear Collider What sort of tracking and vertexing is needed for the Linear Collider? o Vertex detectors for the Linear Collider will be precision devices – – o Need very thin, low mass detectors No need for extreme radiation tolerance Need high precision vertexing eg ~20 μm pixels Can not simply recycle technologies used in LHC or elsewhere High pixelization and readout implications – 109 pixels: must break long bunch trains into small bites (2820/20 = 141) – Read out detector many (ie 20) times during a train susceptible to pickup – …or store info for each bite and read out during long inter-train spaces Bunch Train Bunch Spacing S. Worm – RAL 0. 2 s 337 ns x 2820 0. 95 ms May 3, 2005 10

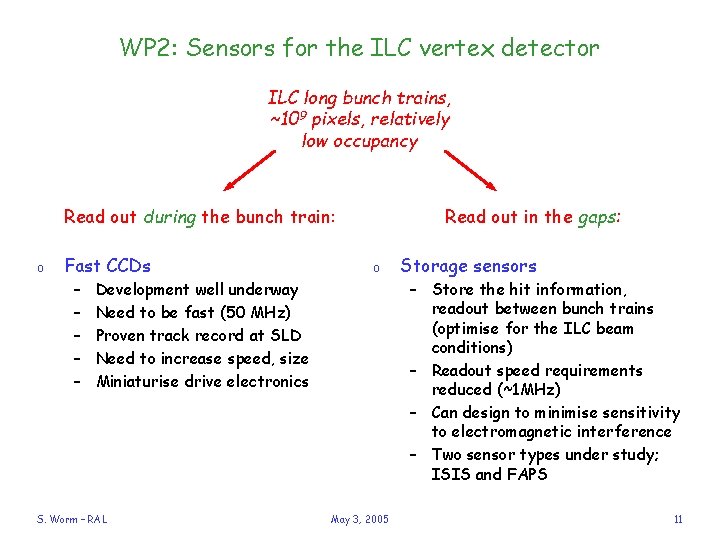

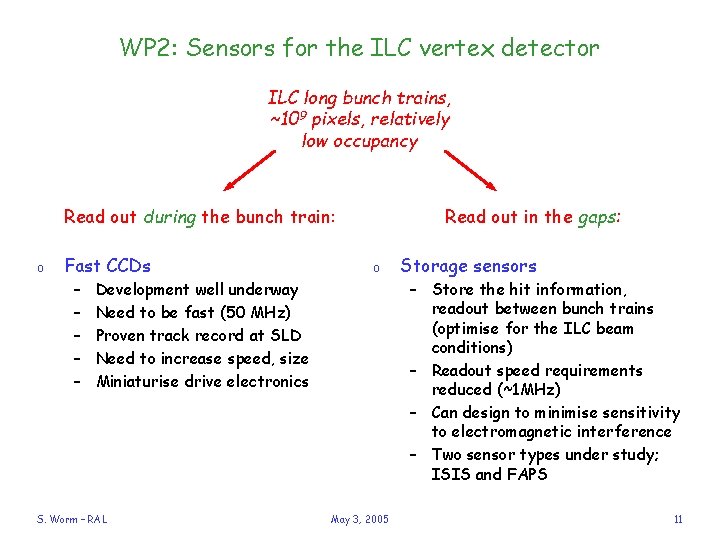

WP 2: Sensors for the ILC vertex detector ILC long bunch trains, ~109 pixels, relatively low occupancy Read out during the bunch train: o Fast CCDs – – – Read out in the gaps: o – Store the hit information, readout between bunch trains (optimise for the ILC beam conditions) – Readout speed requirements reduced (~1 MHz) – Can design to minimise sensitivity to electromagnetic interference – Two sensor types under study; ISIS and FAPS Development well underway Need to be fast (50 MHz) Proven track record at SLD Need to increase speed, size Miniaturise drive electronics S. Worm – RAL Storage sensors May 3, 2005 11

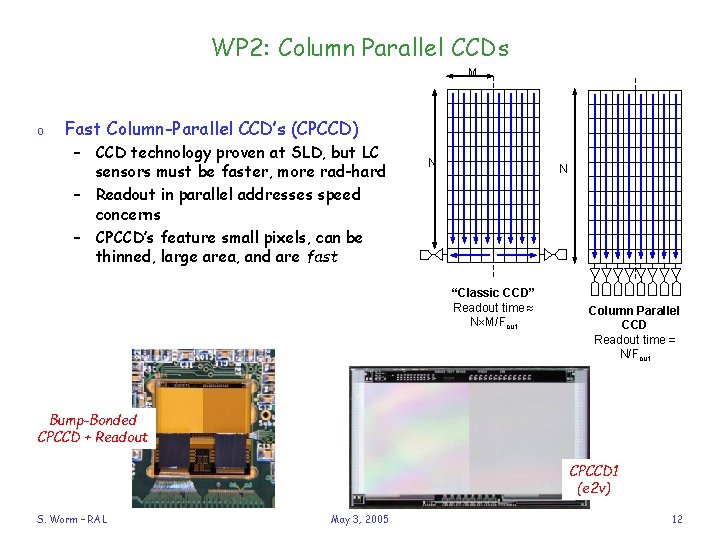

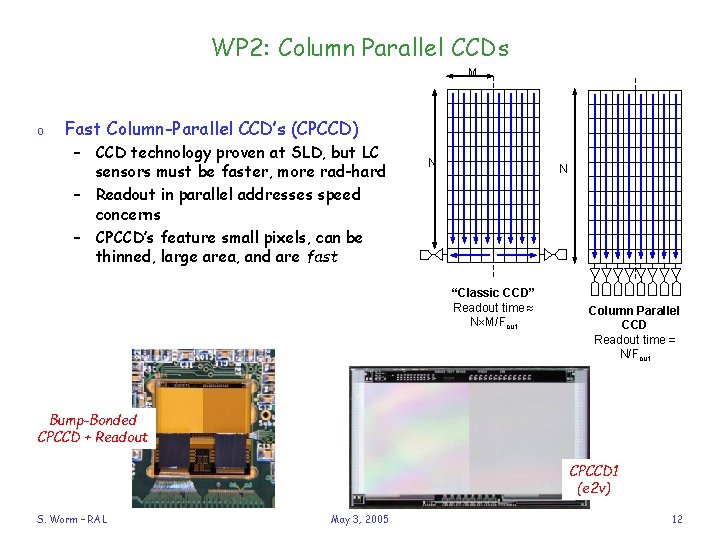

WP 2: Column Parallel CCDs M o Fast Column-Parallel CCD’s (CPCCD) – CCD technology proven at SLD, but LC sensors must be faster, more rad-hard – Readout in parallel addresses speed concerns – CPCCD’s feature small pixels, can be thinned, large area, and are fast N N “Classic CCD” Readout time N M/Fout Column Parallel CCD Readout time = N/Fout Bump-Bonded CPCCD + Readout CPCCD 1 (e 2 v) S. Worm – RAL May 3, 2005 12

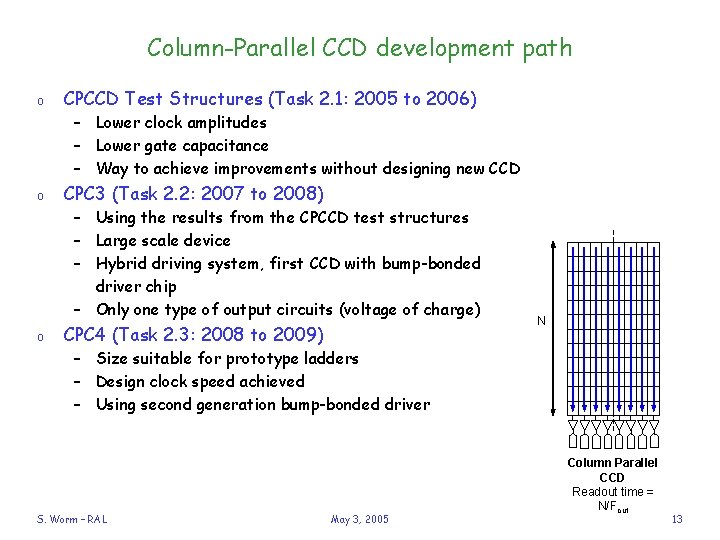

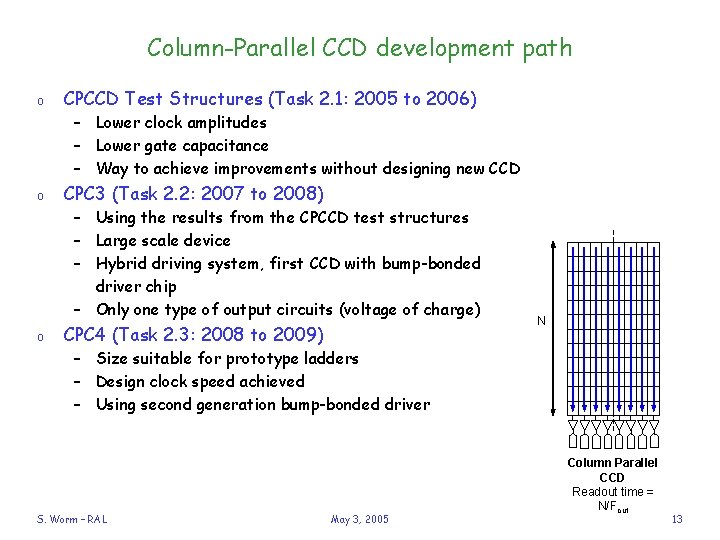

Column-Parallel CCD development path o CPCCD Test Structures (Task 2. 1: 2005 to 2006) – Lower clock amplitudes – Lower gate capacitance – Way to achieve improvements without designing new CCD o CPC 3 (Task 2. 2: 2007 to 2008) – Using the results from the CPCCD test structures – Large scale device – Hybrid driving system, first CCD with bump-bonded driver chip – Only one type of output circuits (voltage of charge) o CPC 4 (Task 2. 3: 2008 to 2009) N – Size suitable for prototype ladders – Design clock speed achieved – Using second generation bump-bonded driver S. Worm – RAL May 3, 2005 Column Parallel CCD Readout time = N/Fout 13

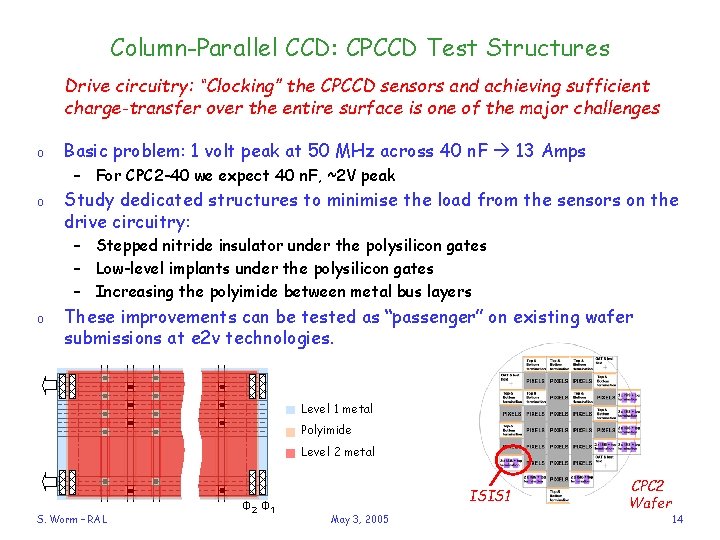

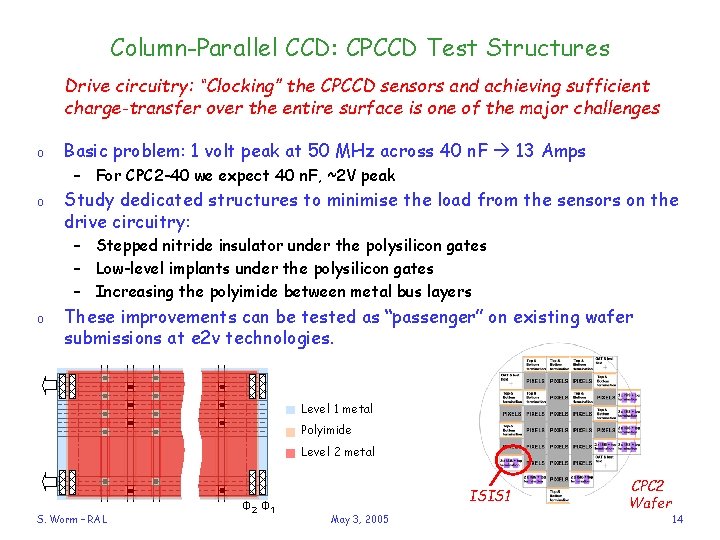

Column-Parallel CCD: CPCCD Test Structures Drive circuitry: “Clocking” the CPCCD sensors and achieving sufficient charge-transfer over the entire surface is one of the major challenges o Basic problem: 1 volt peak at 50 MHz across 40 n. F 13 Amps – For CPC 2 -40 we expect 40 n. F, ~2 V peak o Study dedicated structures to minimise the load from the sensors on the drive circuitry: – Stepped nitride insulator under the polysilicon gates – Low-level implants under the polysilicon gates – Increasing the polyimide between metal bus layers o These improvements can be tested as “passenger” on existing wafer submissions at e 2 v technologies. Level 1 metal Polyimide Level 2 metal S. Worm – RAL Φ 2 Φ 1 ISIS 1 May 3, 2005 CPC 2 Wafer 14

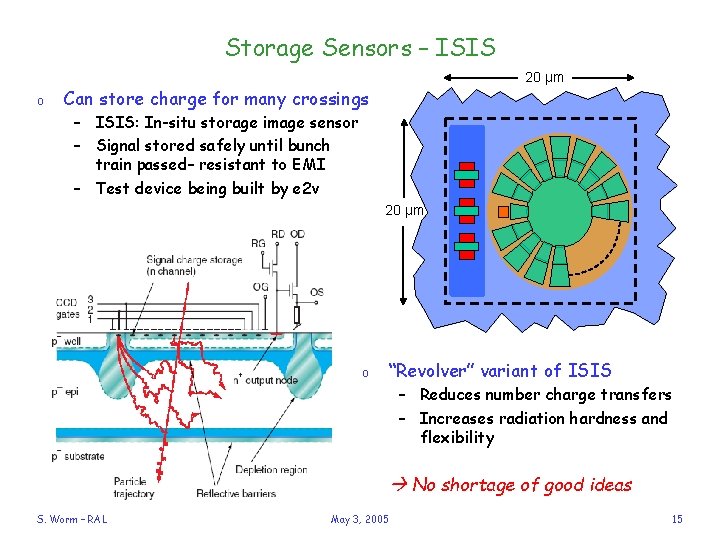

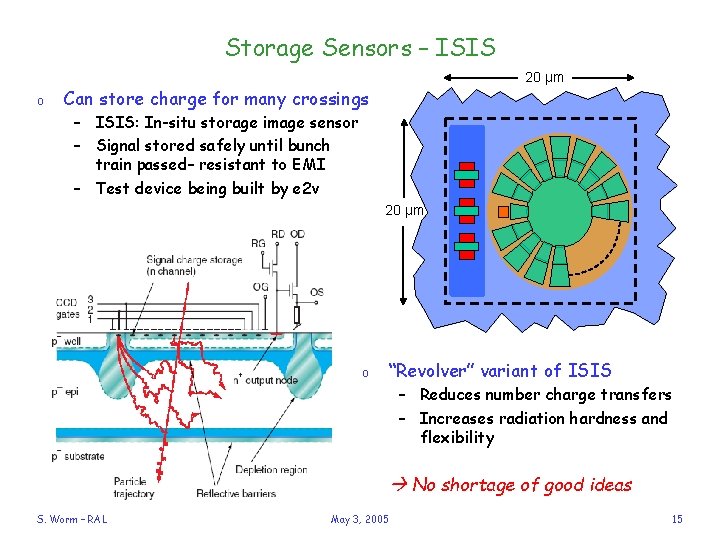

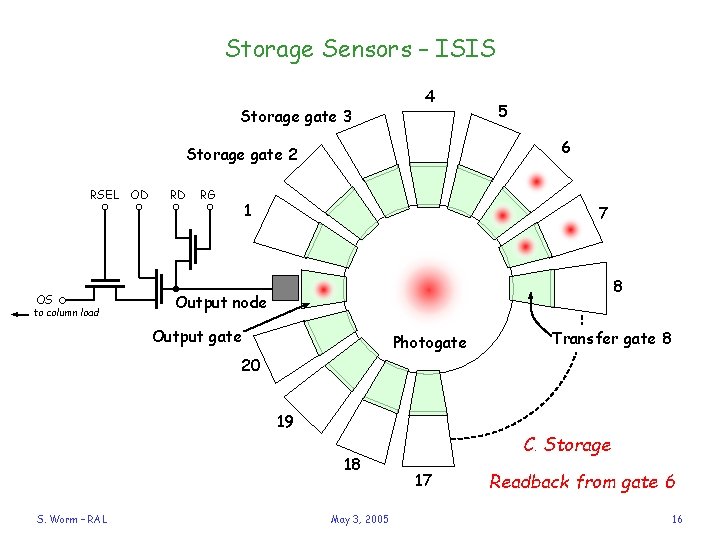

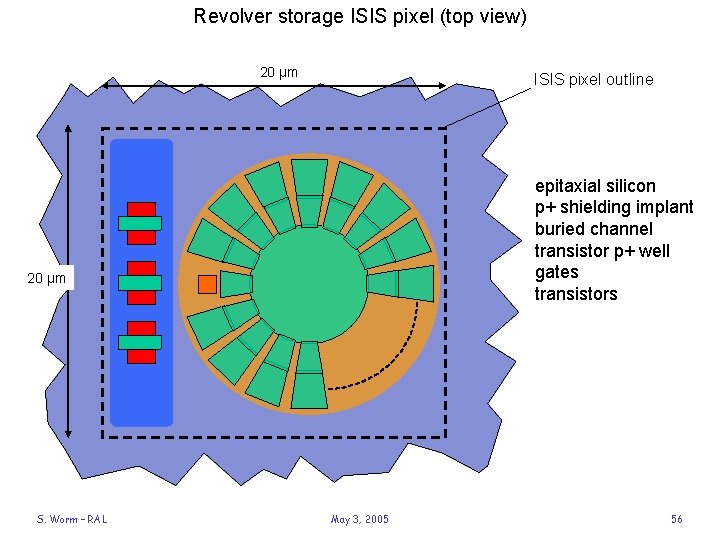

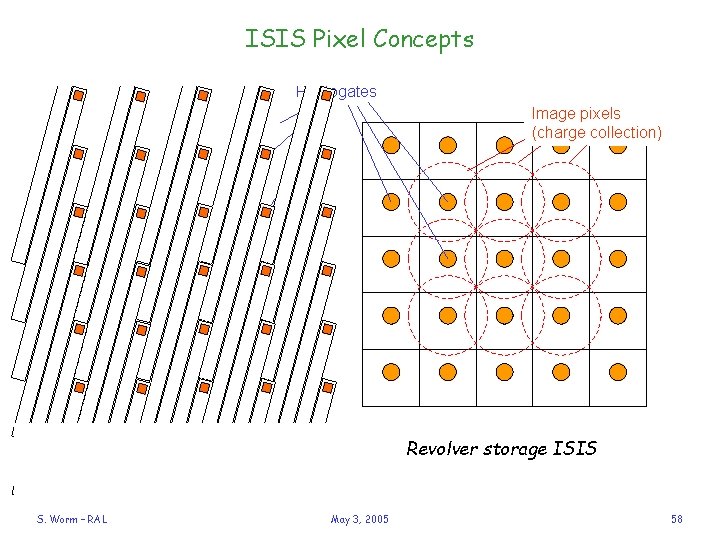

Storage Sensors – ISIS o 20 μm Can store charge for many crossings – ISIS: In-situ storage image sensor – Signal stored safely until bunch train passed– resistant to EMI – Test device being built by e 2 v 20 μm o “Revolver” variant of ISIS – Reduces number charge transfers – Increases radiation hardness and flexibility No shortage of good ideas S. Worm – RAL May 3, 2005 15

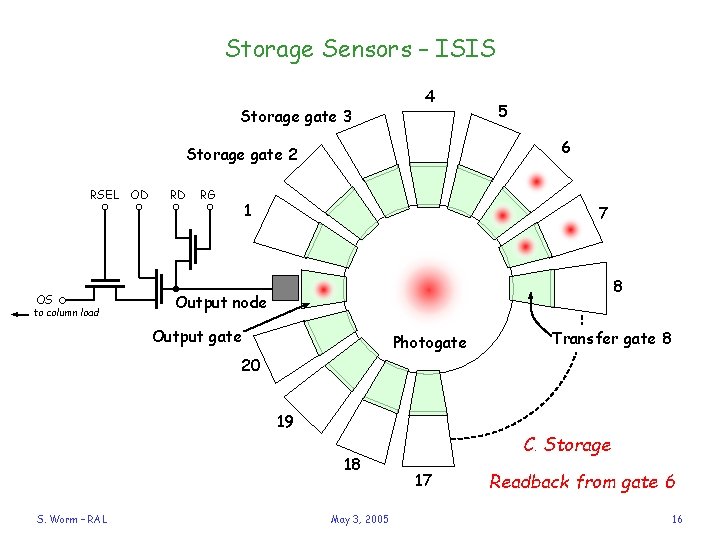

Storage Sensors – ISIS Storage gate 3 4 6 Storage gate 2 RSEL OD OS to column load RD RG 5 1 7 8 Output node Output gate Photogate Transfer gate 8 20 19 18 S. Worm – RAL May 3, 2005 Charge Storage generation Transfer 17 Readback from gate 6 16

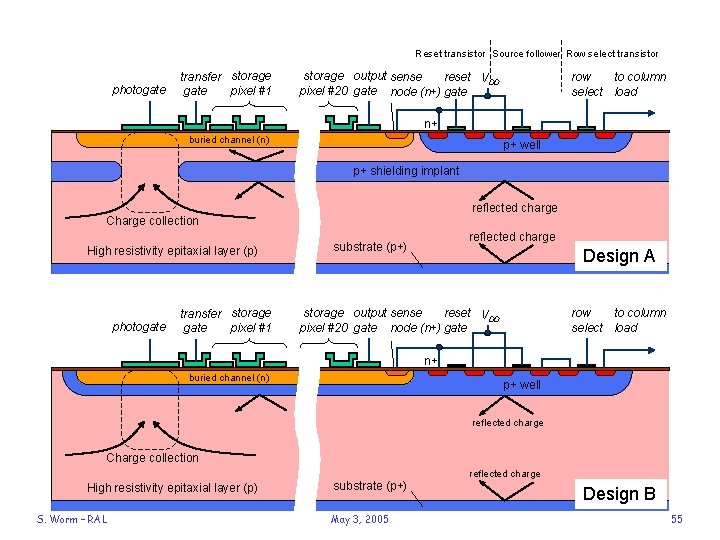

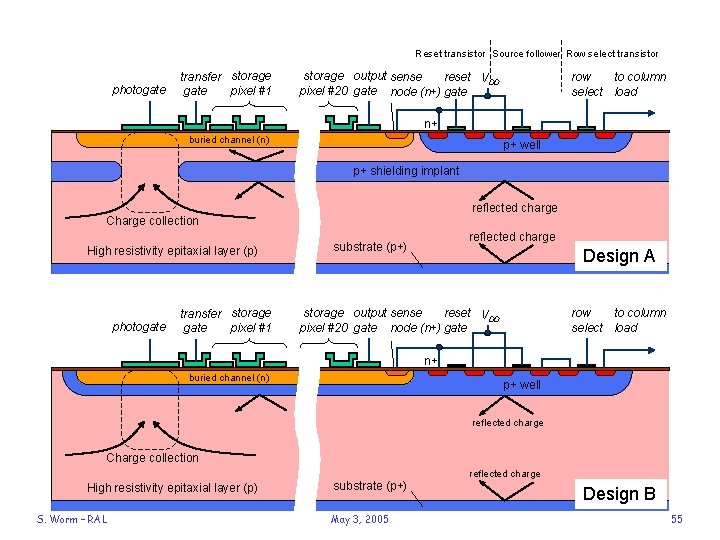

Storage Sensors – ISIS o ISIS Sensor details: – – – o CCD-like charge storage cells in CMOS technology Processed on sensitive epi layer p+ shielding implant forms reflective barrier (deep implant) Dual oxide thickness possible Overlapping poly gates not likely in CMOS, may not be needed Basic structure shown below: Reset transistor Source follower Row select transistor photogate transfer storage pixel #1 gate storage output sense reset VDD pixel #20 gate node (n+) gate row to column select load n+ buried channel (n) p+ well p+ shielding implant reflected charge Charge collection High resistivity epitaxial layer (p) S. Worm – RAL substrate (p+) May 3, 2005 reflected charge 17

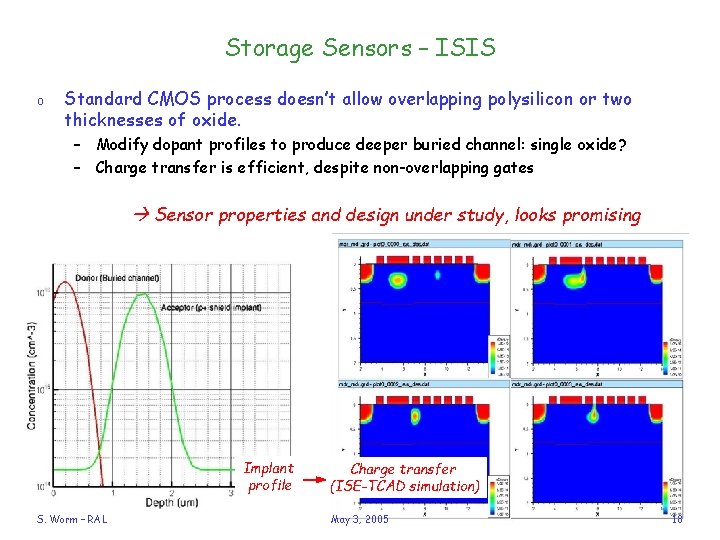

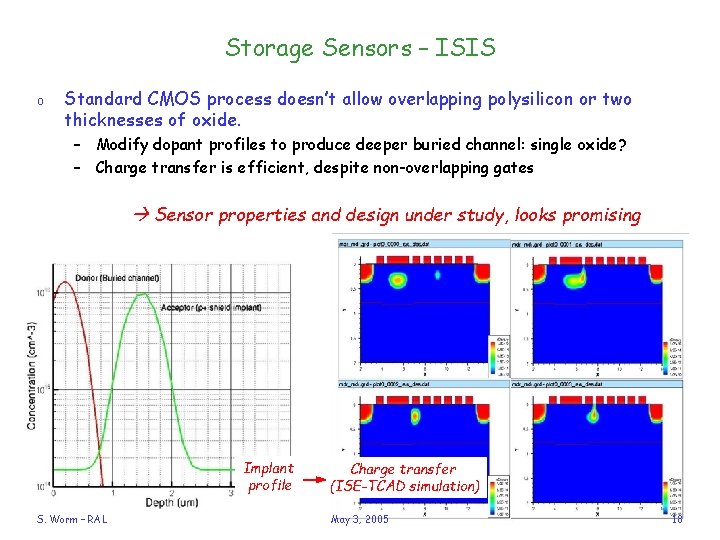

Storage Sensors – ISIS o Standard CMOS process doesn’t allow overlapping polysilicon or two thicknesses of oxide. – Modify dopant profiles to produce deeper buried channel: single oxide? – Charge transfer is efficient, despite non-overlapping gates Sensor properties and design under study, looks promising Implant profile S. Worm – RAL Charge transfer (ISE-TCAD simulation) May 3, 2005 18

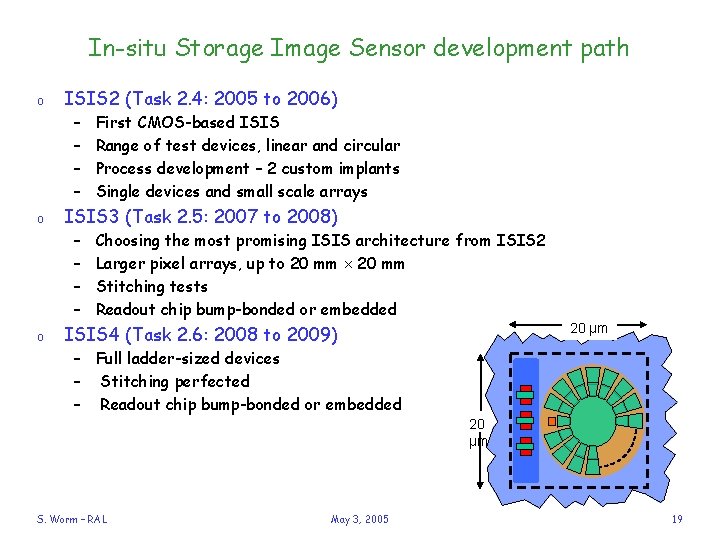

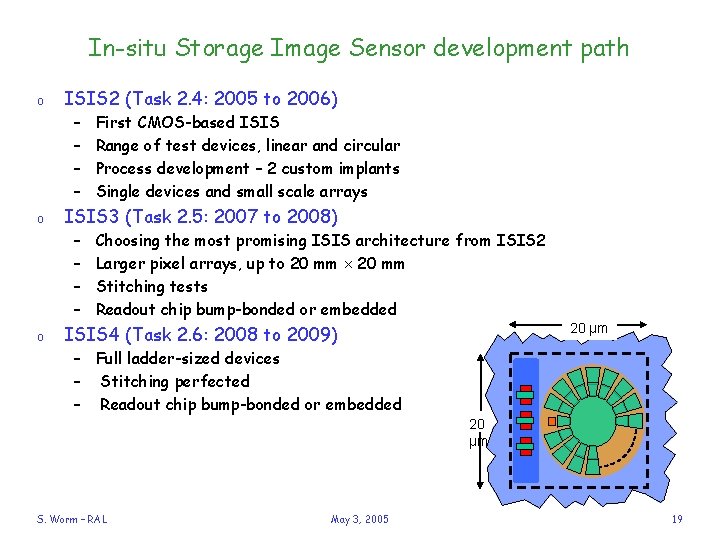

In-situ Storage Image Sensor development path o ISIS 2 (Task 2. 4: 2005 to 2006) – – o ISIS 3 (Task 2. 5: 2007 to 2008) – – o First CMOS-based ISIS Range of test devices, linear and circular Process development – 2 custom implants Single devices and small scale arrays Choosing the most promising ISIS architecture from ISIS 2 Larger pixel arrays, up to 20 mm Stitching tests Readout chip bump-bonded or embedded ISIS 4 (Task 2. 6: 2008 to 2009) 20 μm – Full ladder-sized devices – Stitching perfected – Readout chip bump-bonded or embedded 20 μm S. Worm – RAL May 3, 2005 19

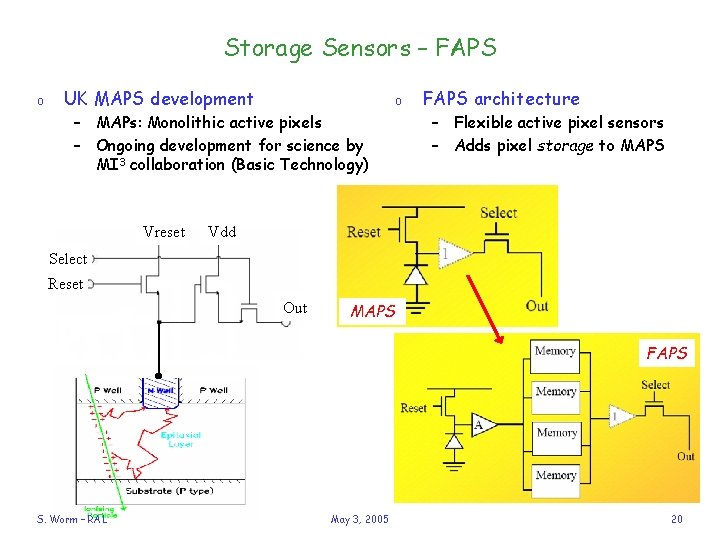

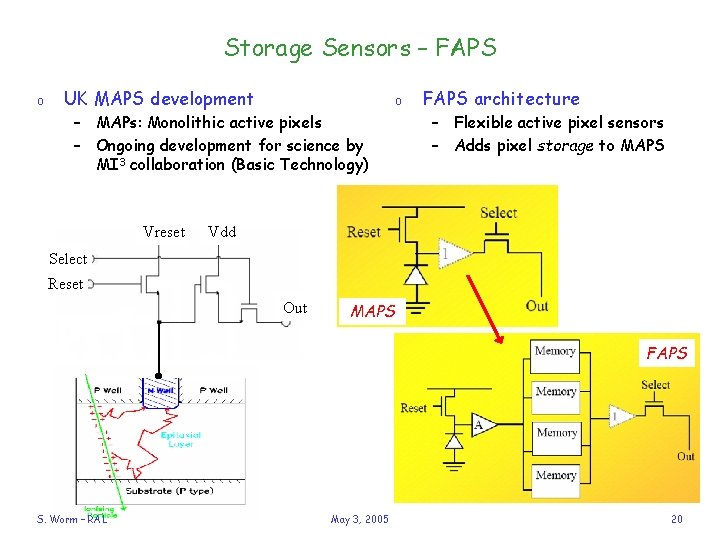

Storage Sensors – FAPS o UK MAPS development o – MAPs: Monolithic active pixels – Ongoing development for science by MI 3 collaboration (Basic Technology) Vreset FAPS architecture – Flexible active pixel sensors – Adds pixel storage to MAPS Vdd Select Reset Out MAPS FAPS S. Worm – RAL May 3, 2005 20

Storage Sensors – FAPS o FAPS architecture – Present design “proof of principle” test structure* – Pixels 20 x 20 m 2, 3 metal layers, 10 storage cells *(2 -year S. Worm – RAL o First source measurements: – 10 deep pipeline in each pixel – Common mode noise subtraction (subtract Scell 1) – S/Ncell between 15 -17 – With appropriate seed cut, inefficiencies <0. 5% PPARC funded programme to develop technology. Started June 2003) May 3, underpinning 2005 21

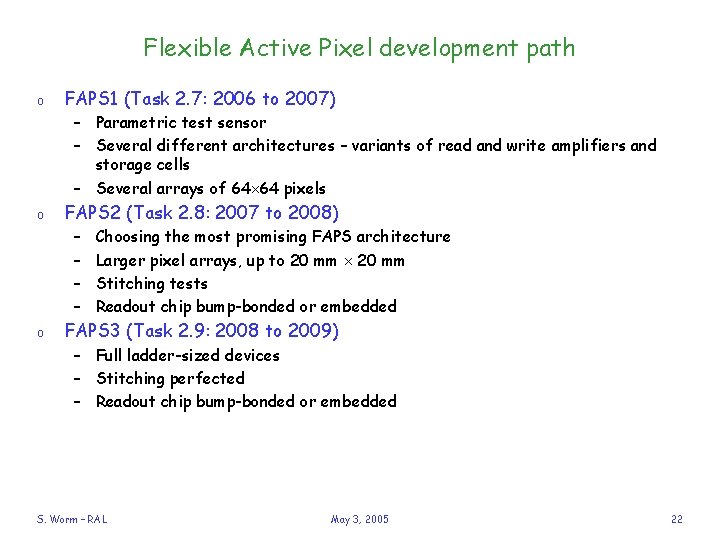

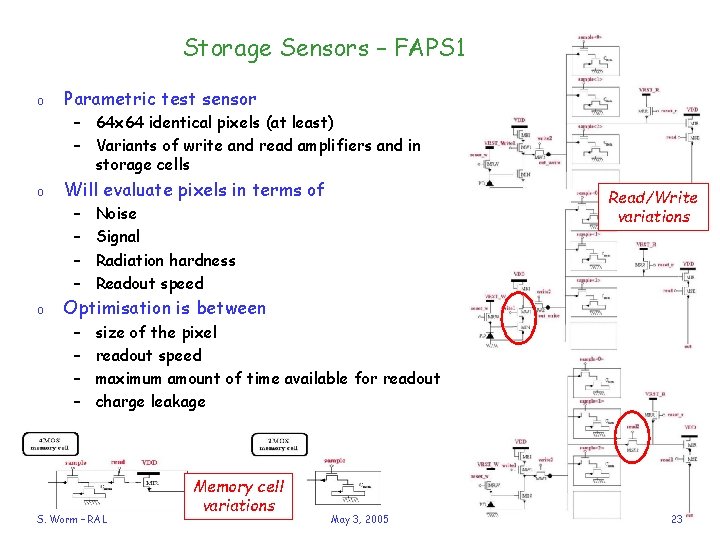

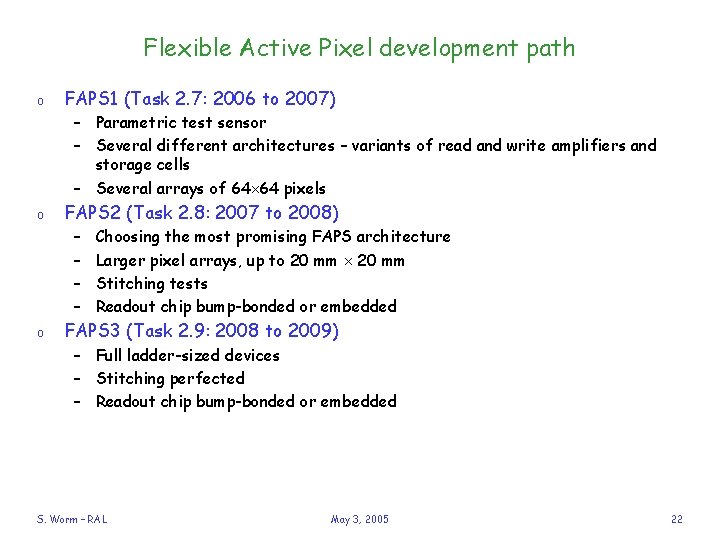

Flexible Active Pixel development path o FAPS 1 (Task 2. 7: 2006 to 2007) – Parametric test sensor – Several different architectures – variants of read and write amplifiers and storage cells – Several arrays of 64 64 pixels o FAPS 2 (Task 2. 8: 2007 to 2008) – – o Choosing the most promising FAPS architecture Larger pixel arrays, up to 20 mm Stitching tests Readout chip bump-bonded or embedded FAPS 3 (Task 2. 9: 2008 to 2009) – Full ladder-sized devices – Stitching perfected – Readout chip bump-bonded or embedded S. Worm – RAL May 3, 2005 22

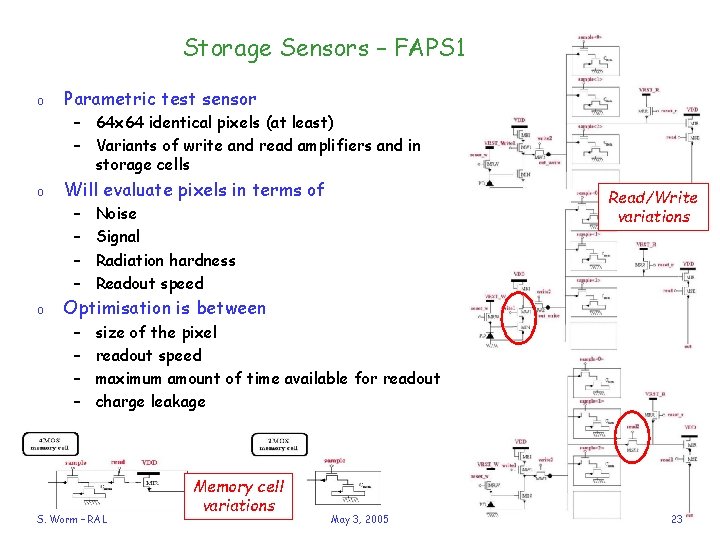

Storage Sensors – FAPS 1 plans o Parametric test sensor – 64 x 64 identical pixels (at least) – Variants of write and read amplifiers and in storage cells o Will evaluate pixels in terms of – – o Read/Write variations Noise Signal Radiation hardness Readout speed Optimisation is between – – size of the pixel readout speed maximum amount of time available for readout charge leakage S. Worm – RAL Memory cell variations May 3, 2005 23

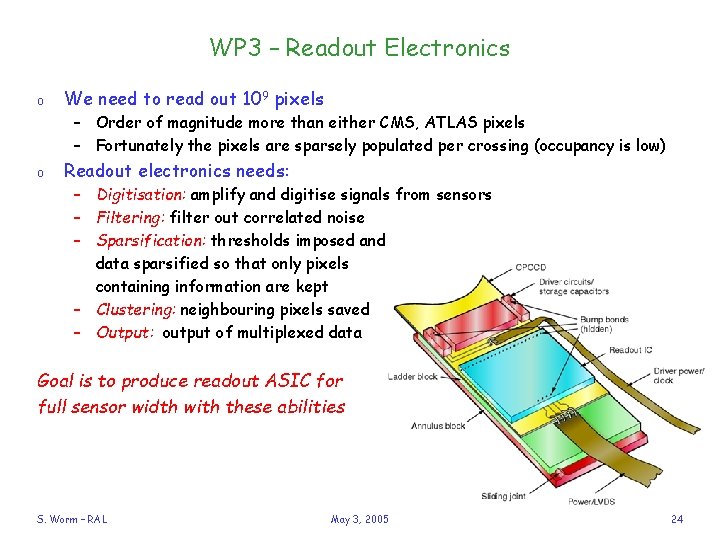

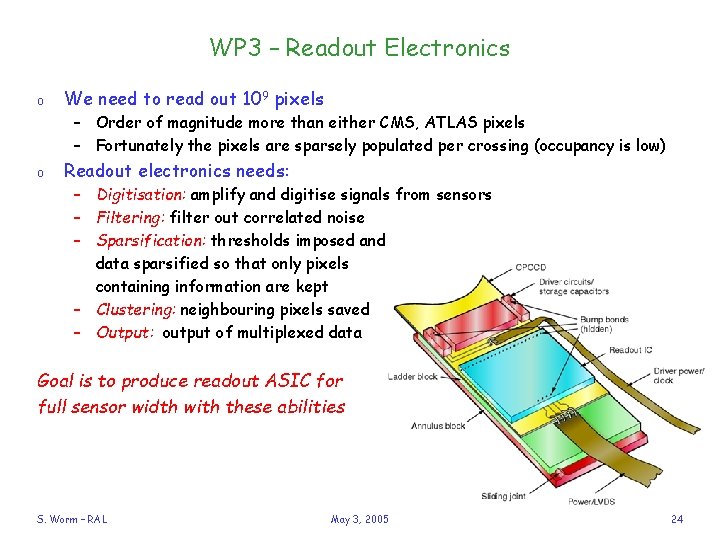

WP 3 – Readout Electronics o We need to read out 109 pixels – Order of magnitude more than either CMS, ATLAS pixels – Fortunately the pixels are sparsely populated per crossing (occupancy is low) o Readout electronics needs: – Digitisation: amplify and digitise signals from sensors – Filtering: filter out correlated noise – Sparsification: thresholds imposed and data sparsified so that only pixels containing information are kept – Clustering: neighbouring pixels saved – Output: output of multiplexed data Goal is to produce readout ASIC for full sensor width with these abilities S. Worm – RAL May 3, 2005 24

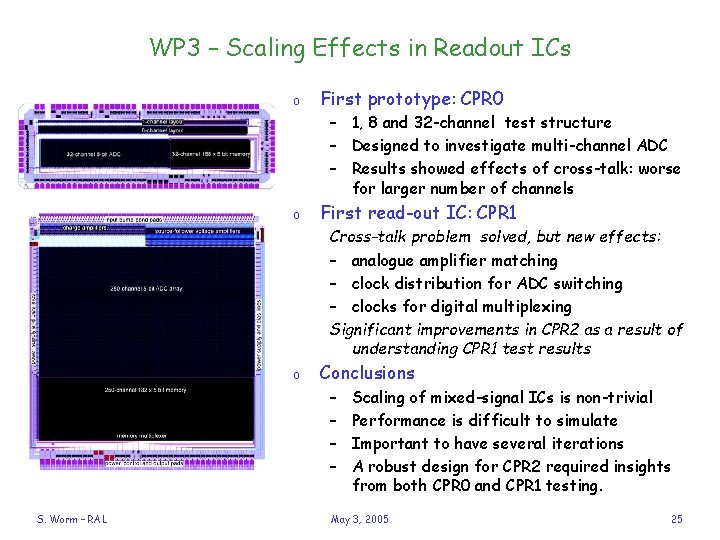

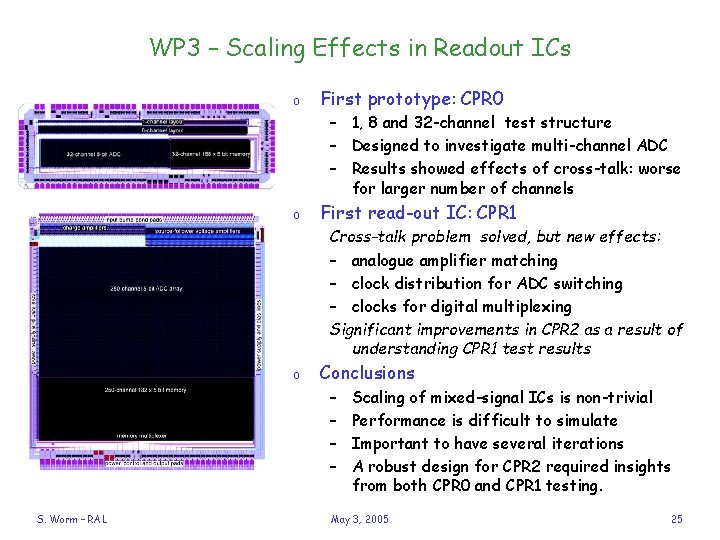

WP 3 – Scaling Effects in Readout ICs o First prototype: CPR 0 – 1, 8 and 32 -channel test structure – Designed to investigate multi-channel ADC – Results showed effects of cross-talk: worse for larger number of channels o First read-out IC: CPR 1 Cross-talk problem solved, but new effects: – analogue amplifier matching – clock distribution for ADC switching – clocks for digital multiplexing Significant improvements in CPR 2 as a result of understanding CPR 1 test results o Conclusions – – S. Worm – RAL Scaling of mixed-signal ICs is non-trivial Performance is difficult to simulate Important to have several iterations A robust design for CPR 2 required insights from both CPR 0 and CPR 1 testing. May 3, 2005 25

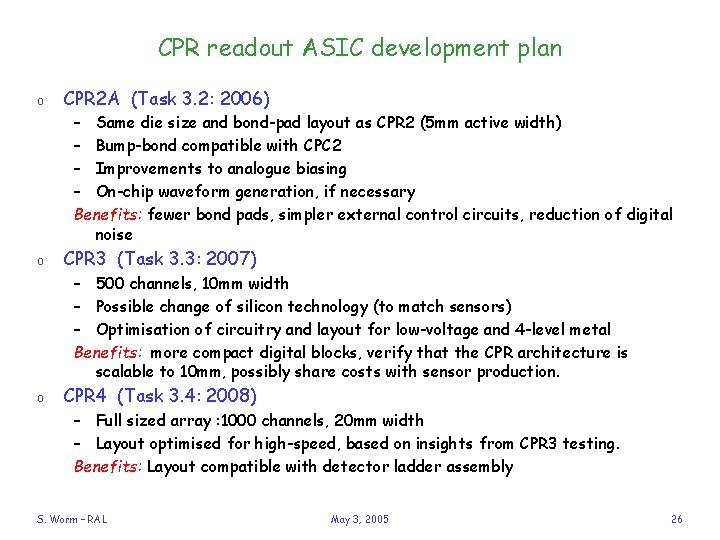

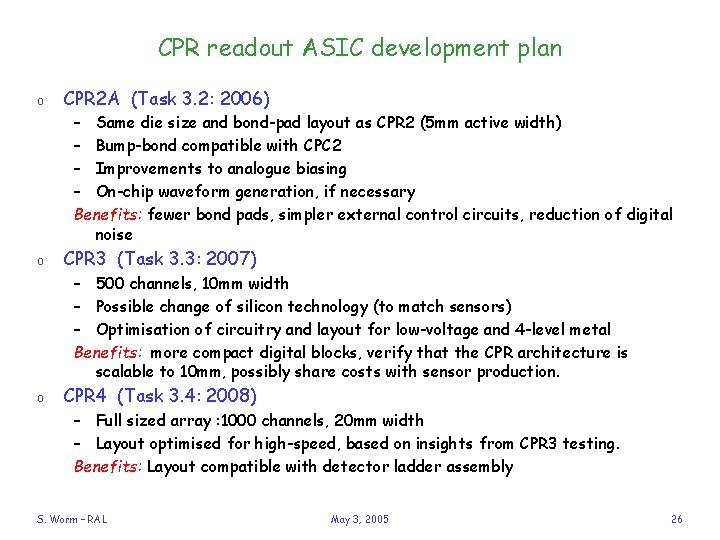

CPR readout ASIC development plan o CPR 2 A (Task 3. 2: 2006) – Same die size and bond-pad layout as CPR 2 (5 mm active width) – Bump-bond compatible with CPC 2 – Improvements to analogue biasing – On-chip waveform generation, if necessary Benefits: fewer bond pads, simpler external control circuits, reduction of digital noise o CPR 3 (Task 3. 3: 2007) – 500 channels, 10 mm width – Possible change of silicon technology (to match sensors) – Optimisation of circuitry and layout for low-voltage and 4 -level metal Benefits: more compact digital blocks, verify that the CPR architecture is scalable to 10 mm, possibly share costs with sensor production. o CPR 4 (Task 3. 4: 2008) – Full sized array : 1000 channels, 20 mm width – Layout optimised for high-speed, based on insights from CPR 3 testing. Benefits: Layout compatible with detector ladder assembly S. Worm – RAL May 3, 2005 26

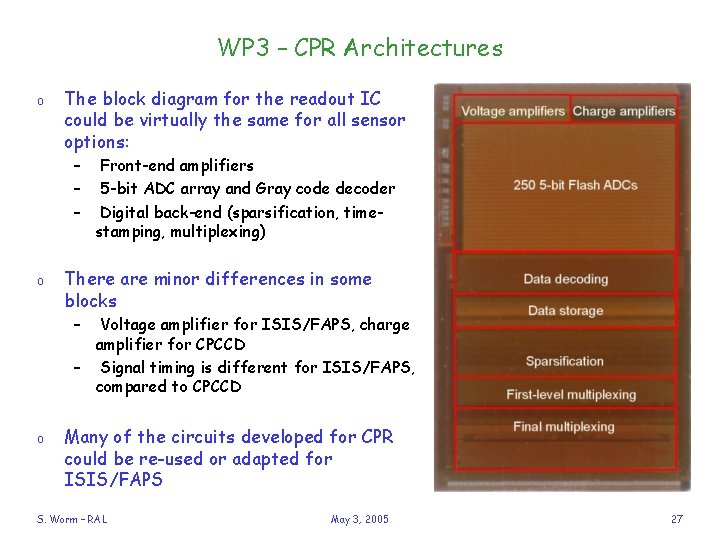

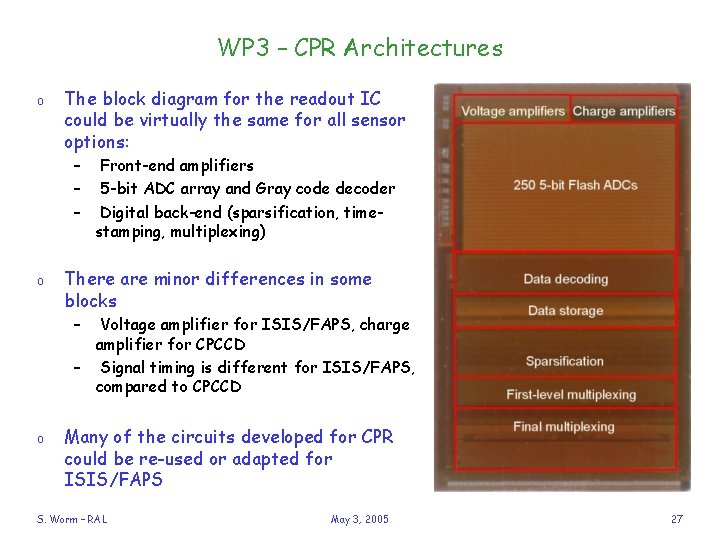

WP 3 – CPR Architectures o The block diagram for the readout IC could be virtually the same for all sensor options: – – – o Front-end amplifiers 5 -bit ADC array and Gray code decoder Digital back-end (sparsification, timestamping, multiplexing) There are minor differences in some blocks – Voltage amplifier for ISIS/FAPS, charge amplifier for CPCCD – Signal timing is different for ISIS/FAPS, compared to CPCCD o Many of the circuits developed for CPR could be re-used or adapted for ISIS/FAPS S. Worm – RAL May 3, 2005 27

WP 3 – Sensor-specific Details o There are differences between the outputs of CPCCD, ISIS, and FAPS. This makes it impracticable to implement a single readout IC. – CPCCD: charge output, typical signal ~2000 electrons – ISIS: charge storage, voltage output, ~5 m. V – FAPS: voltage storage, voltage output, ~50 m. V o There also timing differences – CPCCD: 50 MHz continuous readout during bunch train – ISIS/FAPS : slow ~1 MHz readout after bunch train o It may be possible to combine the ICs for ISIS and FAPS using a switchable-gain voltage amplifier on the front-end. S. Worm – RAL May 3, 2005 28

CPR-ISIS and CPR-FAPS details o CPR-ISIS 3 and CPR-FAPS 2 (Tasks 3. 5, 3. 7: 2007) – – o Dedicated ASIC, but drawing heavily from CPR 2 Not the same as CPR 2 given timing differences Bump-bond compatible with ISIS 3 or FAPS 2 Possibility to include in sensor submissions, monolithic or stand-alone CPR-ISIS 4 and CPR-FAPS 3 (Tasks 3. 6, 3. 8: 2008) – – Full-scale ASIC for final module readout Evolutionary development from previous CPR developments Bump-bond compatible with ISIS 4 or FAPS 3 Integration with sensor on one wafer desirable, but not assumed S. Worm – RAL May 3, 2005 29

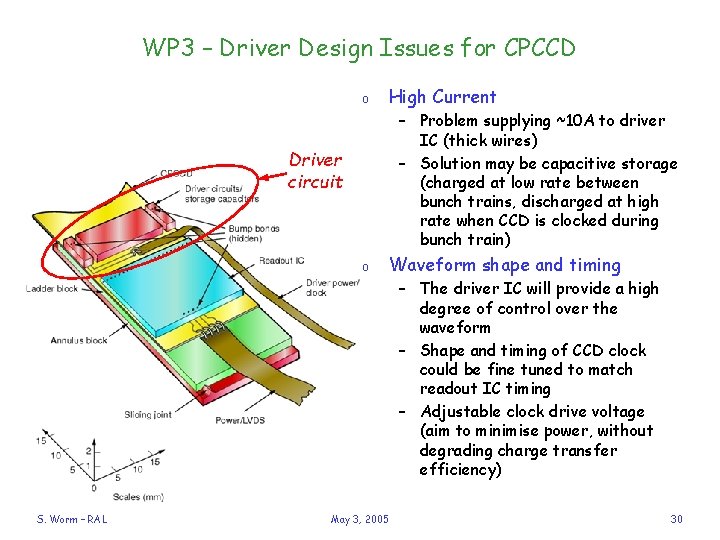

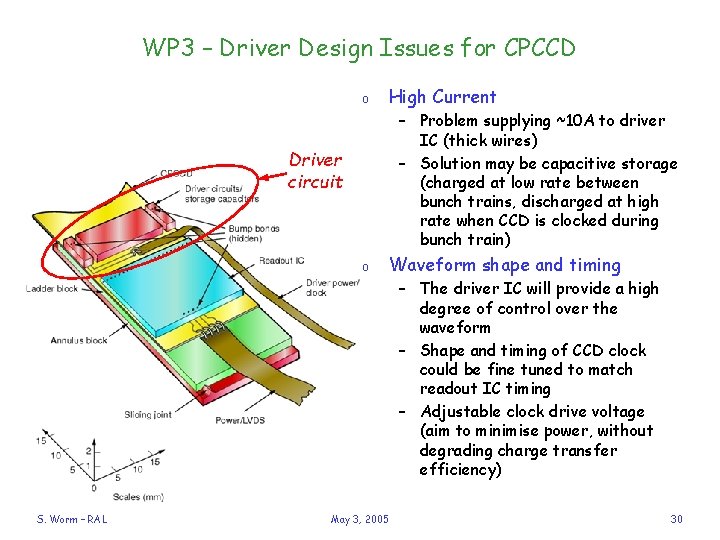

WP 3 – Driver Design Issues for CPCCD o High Current – Problem supplying ~10 A to driver IC (thick wires) – Solution may be capacitive storage (charged at low rate between bunch trains, discharged at high rate when CCD is clocked during bunch train) Driver circuit o Waveform shape and timing – The driver IC will provide a high degree of control over the waveform – Shape and timing of CCD clock could be fine tuned to match readout IC timing – Adjustable clock drive voltage (aim to minimise power, without degrading charge transfer efficiency) S. Worm – RAL May 3, 2005 30

CPD Driver ASIC o CPD 2 (Task 3. 9: 2006) – – o Wire bonded to CPC 2 High current drive (~10 A at 50 MHz) Large die size - important for power dissipation Multiple bond pads, to minimise resistance and inductance CPD 3 (Task 3. 10: 2007) – Bump bondable to CPC 3 – Optimised for innermost detector layer o CPD 4 (Task 3. 11: 2008) – Bump bondable to CPC 3/4 – Optimised for outer layers - higher current S. Worm – RAL May 3, 2005 31

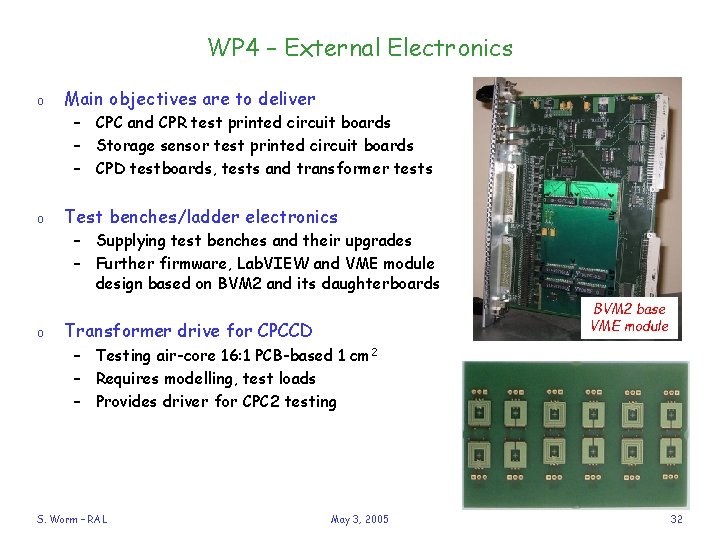

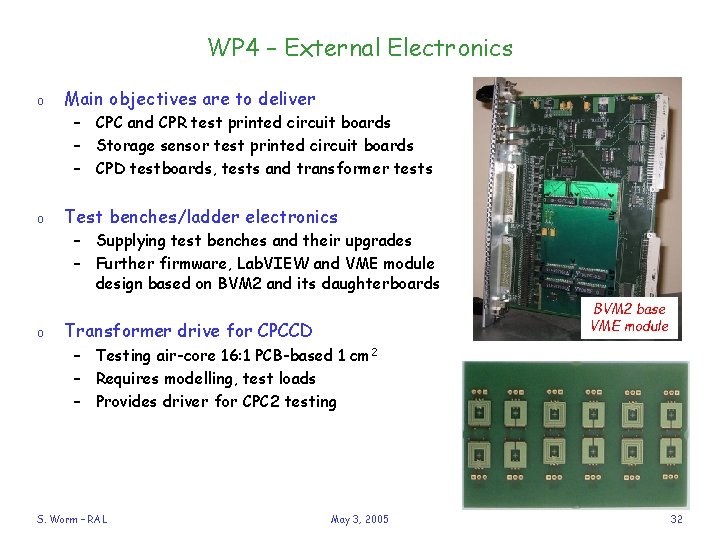

WP 4 – External Electronics o Main objectives are to deliver – CPC and CPR test printed circuit boards – Storage sensor test printed circuit boards – CPD testboards, tests and transformer tests o Test benches/ladder electronics – Supplying test benches and their upgrades – Further firmware, Lab. VIEW and VME module design based on BVM 2 and its daughterboards o BVM 2 base VME module Transformer drive for CPCCD – Testing air-core 16: 1 PCB-based 1 cm 2 – Requires modelling, test loads – Provides driver for CPC 2 testing S. Worm – RAL May 3, 2005 32

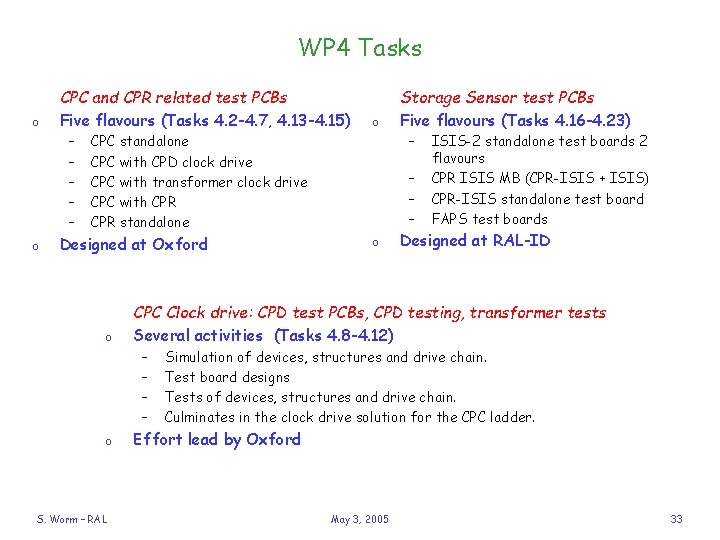

WP 4 Tasks o CPC and CPR related test PCBs Five flavours (Tasks 4. 2 -4. 7, 4. 13 -4. 15) – – – o o – CPC standalone CPC with CPD clock drive CPC with transformer clock drive CPC with CPR standalone Designed at Oxford o S. Worm – RAL – – – o ISIS-2 standalone test boards 2 flavours CPR ISIS MB (CPR-ISIS + ISIS) CPR-ISIS standalone test board FAPS test boards Designed at RAL-ID CPC Clock drive: CPD test PCBs, CPD testing, transformer tests Several activities (Tasks 4. 8 -4. 12) – – o Storage Sensor test PCBs Five flavours (Tasks 4. 16 -4. 23) Simulation of devices, structures and drive chain. Test board designs Tests of devices, structures and drive chain. Culminates in the clock drive solution for the CPC ladder. Effort lead by Oxford May 3, 2005 33

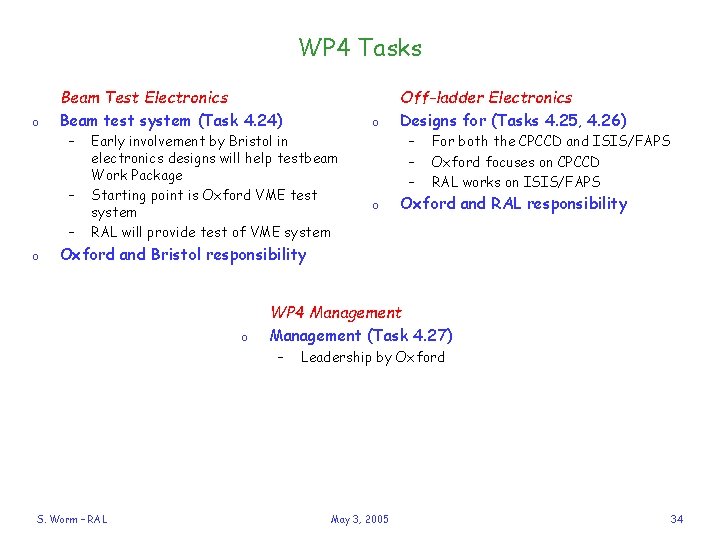

WP 4 Tasks o Beam Test Electronics Beam test system (Task 4. 24) – – – o o Early involvement by Bristol in electronics designs will help testbeam Work Package Starting point is Oxford VME test system RAL will provide test of VME system Off-ladder Electronics Designs for (Tasks 4. 25, 4. 26) – – – o For both the CPCCD and ISIS/FAPS Oxford focuses on CPCCD RAL works on ISIS/FAPS Oxford and RAL responsibility Oxford and Bristol responsibility o WP 4 Management (Task 4. 27) – S. Worm – RAL Leadership by Oxford May 3, 2005 34

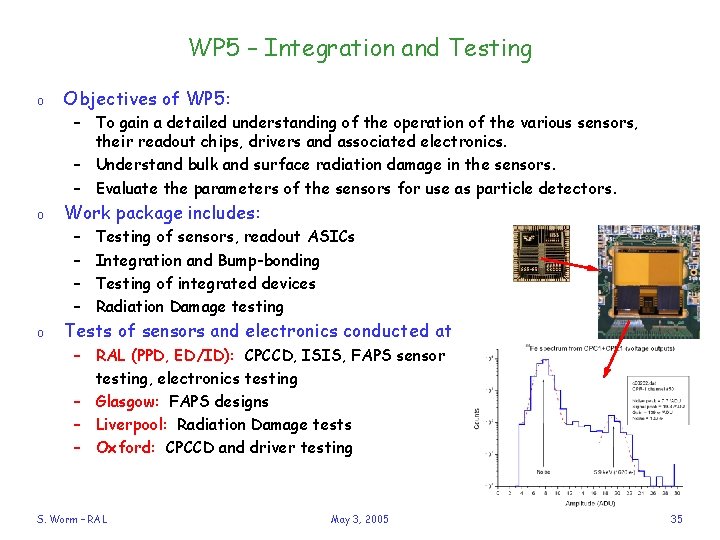

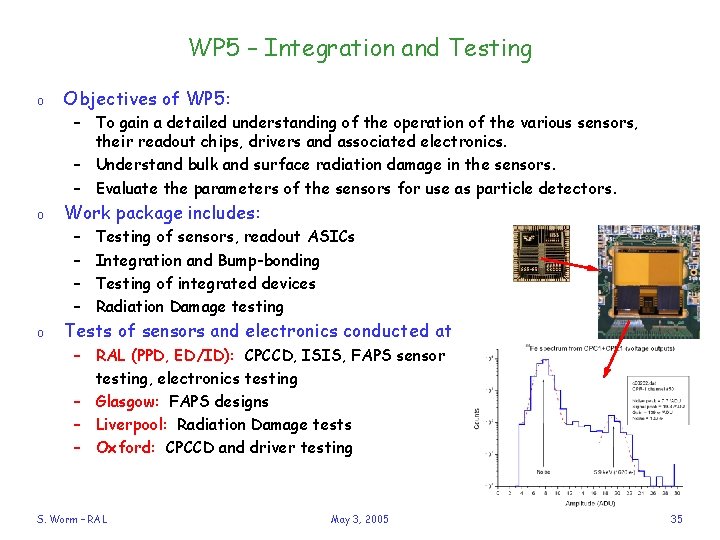

WP 5 – Integration and Testing o Objectives of WP 5: – To gain a detailed understanding of the operation of the various sensors, their readout chips, drivers and associated electronics. – Understand bulk and surface radiation damage in the sensors. – Evaluate the parameters of the sensors for use as particle detectors. o Work package includes: – – o Testing of sensors, readout ASICs Integration and Bump-bonding Testing of integrated devices Radiation Damage testing Tests of sensors and electronics conducted at – RAL (PPD, ED/ID): CPCCD, ISIS, FAPS sensor testing, electronics testing – Glasgow: FAPS designs – Liverpool: Radiation Damage tests – Oxford: CPCCD and driver testing S. Worm – RAL May 3, 2005 35

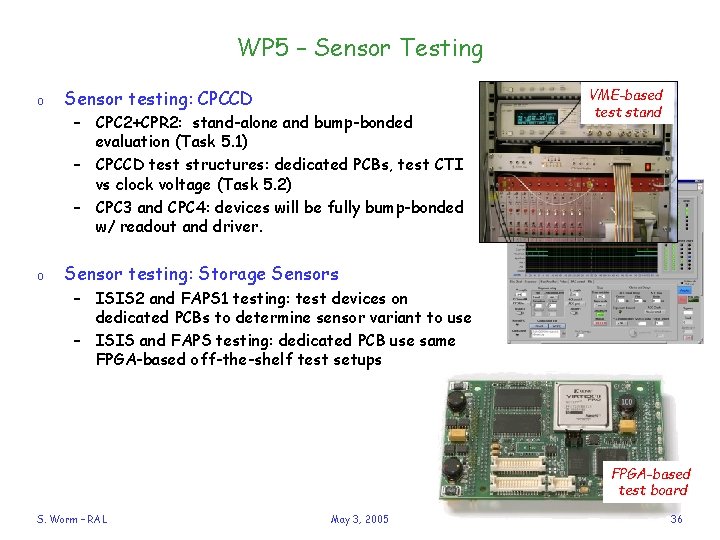

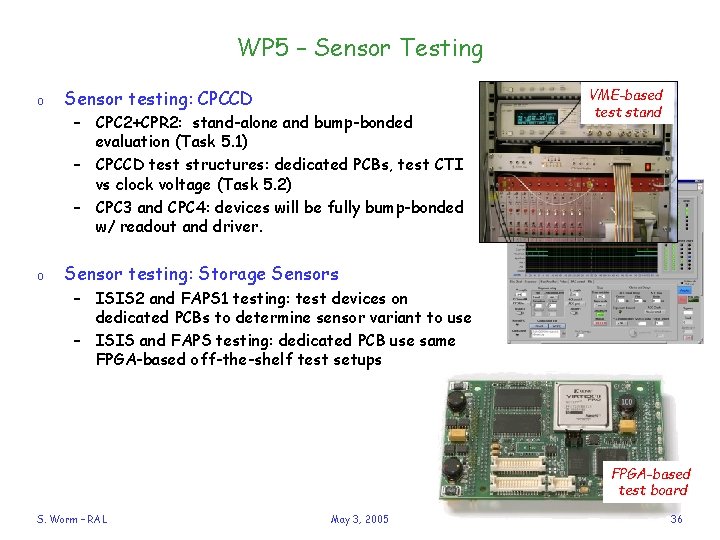

WP 5 – Sensor Testing o Sensor testing: CPCCD – CPC 2+CPR 2: stand-alone and bump-bonded evaluation (Task 5. 1) – CPCCD test structures: dedicated PCBs, test CTI vs clock voltage (Task 5. 2) – CPC 3 and CPC 4: devices will be fully bump-bonded w/ readout and driver. o VME-based test stand Sensor testing: Storage Sensors – ISIS 2 and FAPS 1 testing: test devices on dedicated PCBs to determine sensor variant to use – ISIS and FAPS testing: dedicated PCB use same FPGA-based off-the-shelf test setups FPGA-based test board S. Worm – RAL May 3, 2005 36

Bump-Bonding, Radiation Damage o Bump-bonding – Standard in semiconductor packaging… but not for small quantities, large devices, thinned devices, etc. – Necessary for dense, low-inductance connections – Primarily overseen by RAL, but Glasgow and Liverpool groups have experience o Radiation Damage studies – We need to characterise the process for resistance to radiation for any new vendor – Test bulk and surface damage for each sensor type – Look for charge transfer inefficiency in CPCCD, ISIS – Care and individual testing needed S. Worm – RAL May 3, 2005 37

WP 6 – Vertex Detector Mechanical Studies o Thin Ladder (module) construction Goals – – – 0. 1 % X/X 0 Thinned silicon sensor Uniformity over full length Wire or Bump bondable Robust under thermal cycling Work Package Goals: o Provide mechanical support for test beam studies (Tasks 6. 1– 6. 2) – Two years of material and concept evaluation – Mechanical support technology (decision by March 2007) – detailed fixturing and prototype production 2007 -2009 o Parallel global design and cooling thermal studies (Tasks 6. 3– 6. 4) – support for above tasks – natural evolution into future real detector design S. Worm – RAL May 3, 2005 38

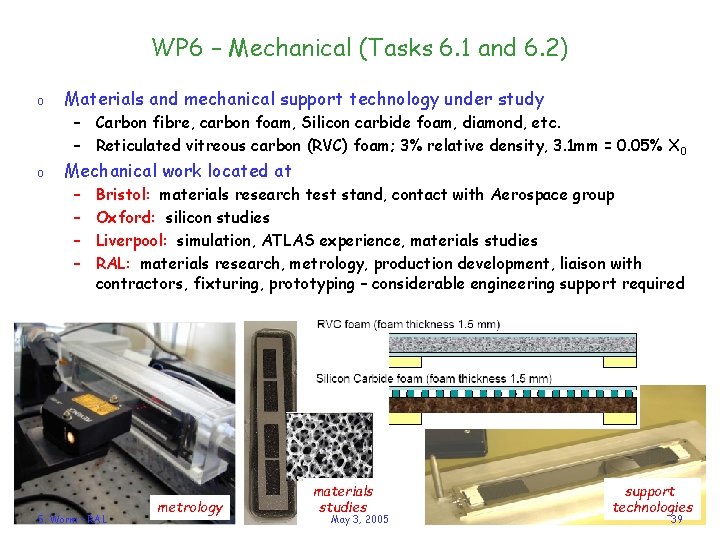

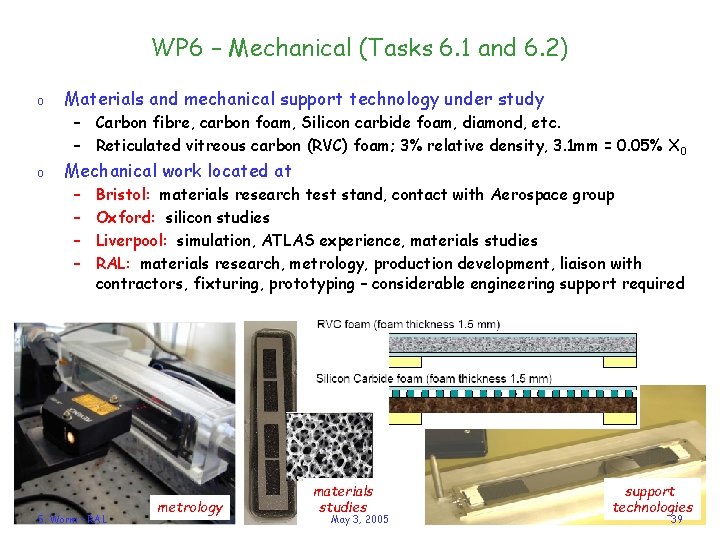

WP 6 – Mechanical (Tasks 6. 1 and 6. 2) o Materials and mechanical support technology under study – Carbon fibre, carbon foam, Silicon carbide foam, diamond, etc. – Reticulated vitreous carbon (RVC) foam; 3% relative density, 3. 1 mm = 0. 05% X 0 o Mechanical work located at – – Bristol: materials research test stand, contact with Aerospace group Oxford: silicon studies Liverpool: simulation, ATLAS experience, materials studies RAL: materials research, metrology, production development, liaison with contractors, fixturing, prototyping – considerable engineering support required S. Worm – RAL metrology materials studies May 3, 2005 support technologies 39

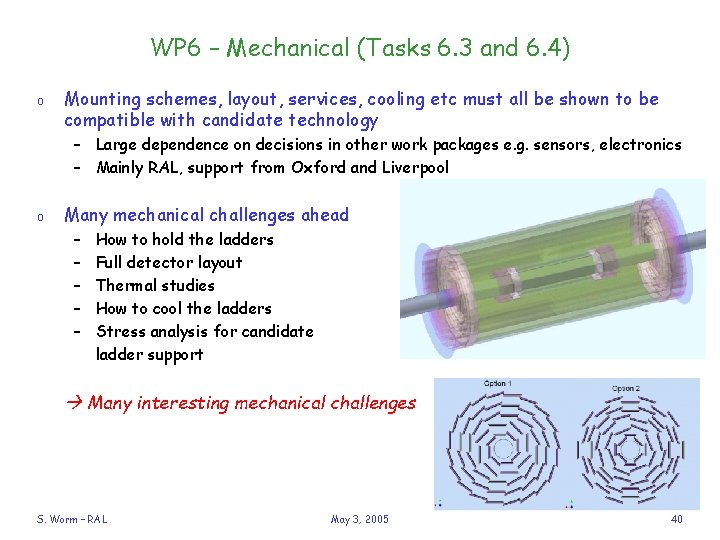

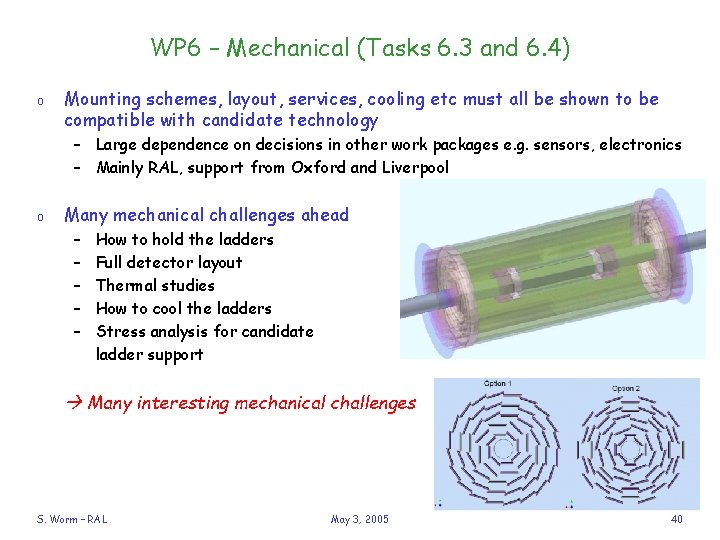

WP 6 – Mechanical (Tasks 6. 3 and 6. 4) o Mounting schemes, layout, services, cooling etc must all be shown to be compatible with candidate technology – Large dependence on decisions in other work packages e. g. sensors, electronics – Mainly RAL, support from Oxford and Liverpool o Many mechanical challenges ahead – – – How to hold the ladders Full detector layout Thermal studies How to cool the ladders Stress analysis for candidate ladder support Many interesting mechanical challenges S. Worm – RAL May 3, 2005 40

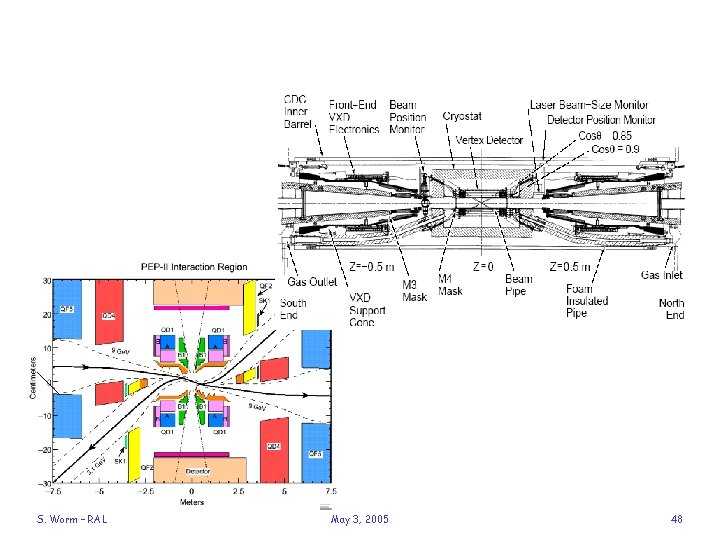

WP 7 – Testbeams and Electromagnetic Interference WP 7 Goals: o To understand the impact of the environment at the ILC on our sensors. – Beam induced RF had a serious impact on the SLD vertex detector. – The MDI panel of the world-wide study has identified EMI as one of the key issues to be addressed. o To test full-sized prototype detector modules in a Test-beam, including the study of: – – – Single hit efficiency Resolution Influence of high magnetic fields Readout speed Sparsification algorithms Noise susceptibility We must ensure that we build a detector that works by selecting the most robust technology to deliver the best physics at the ILC S. Worm – RAL May 3, 2005 41

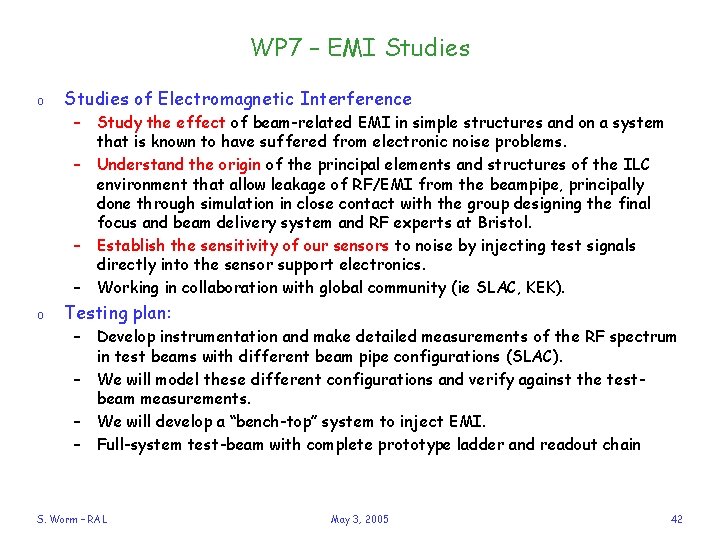

WP 7 – EMI Studies of Electromagnetic Interference – – o Study the effect of beam-related EMI in simple structures and on a system that is known to have suffered from electronic noise problems. Understand the origin of the principal elements and structures of the ILC environment that allow leakage of RF/EMI from the beampipe, principally done through simulation in close contact with the group designing the final focus and beam delivery system and RF experts at Bristol. Establish the sensitivity of our sensors to noise by injecting test signals directly into the sensor support electronics. Working in collaboration with global community (ie SLAC, KEK). Testing plan: – – Develop instrumentation and make detailed measurements of the RF spectrum in test beams with different beam pipe configurations (SLAC). We will model these different configurations and verify against the testbeam measurements. We will develop a “bench-top” system to inject EMI. Full-system test-beam with complete prototype ladder and readout chain S. Worm – RAL May 3, 2005 42

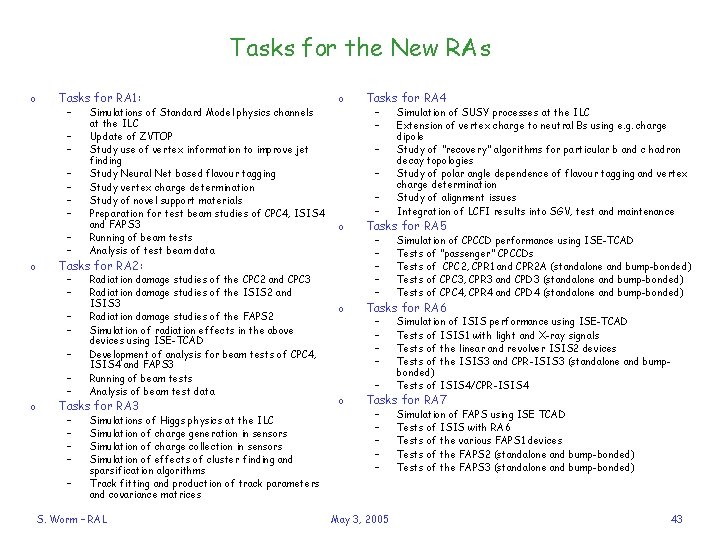

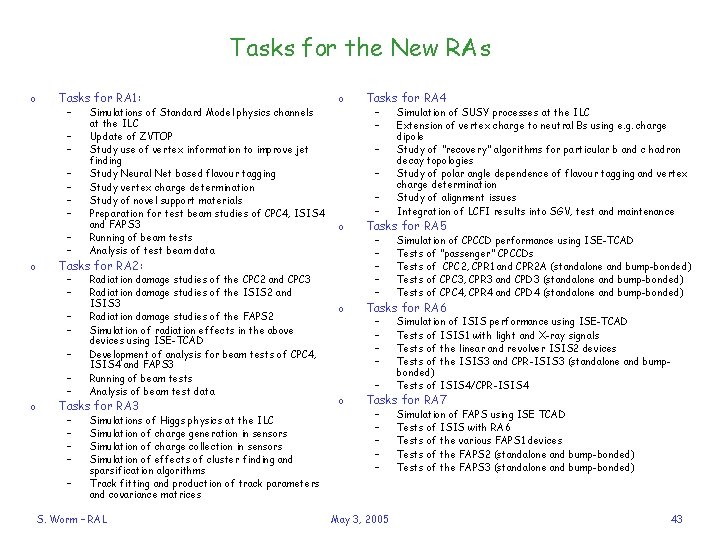

Tasks for the New RAs o Tasks for RA 1: – – – – – o – – – Radiation damage studies of the CPC 2 and CPC 3 Radiation damage studies of the ISIS 2 and ISIS 3 Radiation damage studies of the FAPS 2 Simulation of radiation effects in the above devices using ISE-TCAD Development of analysis for beam tests of CPC 4, ISIS 4 and FAPS 3 Running of beam tests Analysis of beam test data Tasks for RA 3 – – – Simulations of Higgs physics at the ILC Simulation of charge generation in sensors Simulation of charge collection in sensors Simulation of effects of cluster finding and sparsification algorithms Track fitting and production of track parameters and covariance matrices S. Worm – RAL Tasks for RA 4 – – Simulation of SUSY processes at the ILC Extension of vertex charge to neutral Bs using e. g. charge dipole Study of "recovery" algorithms for particular b and c hadron decay topologies Study of polar angle dependence of flavour tagging and vertex charge determination Study of alignment issues Integration of LCFI results into SGV, test and maintenance – – – Simulation of CPCCD performance using ISE-TCAD Tests of "passenger" CPCCDs Tests of CPC 2, CPR 1 and CPR 2 A (standalone and bump-bonded) Tests of CPC 3, CPR 3 and CPD 3 (standalone and bump-bonded) Tests of CPC 4, CPR 4 and CPD 4 (standalone and bump-bonded) – – – Simulation of ISIS performance using ISE-TCAD Tests of ISIS 1 with light and X-ray signals Tests of the linear and revolver ISIS 2 devices Tests of the ISIS 3 and CPR-ISIS 3 (standalone and bumpbonded) Tests of ISIS 4/CPR-ISIS 4 – – – Simulation of FAPS using ISE TCAD Tests of ISIS with RA 6 Tests of the various FAPS 1 devices Tests of the FAPS 2 (standalone and bump-bonded) Tests of the FAPS 3 (standalone and bump-bonded) – – o Tasks for RA 5 o Tasks for RA 6 Tasks for RA 2: – – o Simulations of Standard Model physics channels at the ILC Update of ZVTOP Study use of vertex information to improve jet finding Study Neural Net based flavour tagging Study vertex charge determination Study of novel support materials Preparation for test beam studies of CPC 4, ISIS 4 and FAPS 3 Running of beam tests Analysis of test beam data o o Tasks for RA 7 May 3, 2005 43

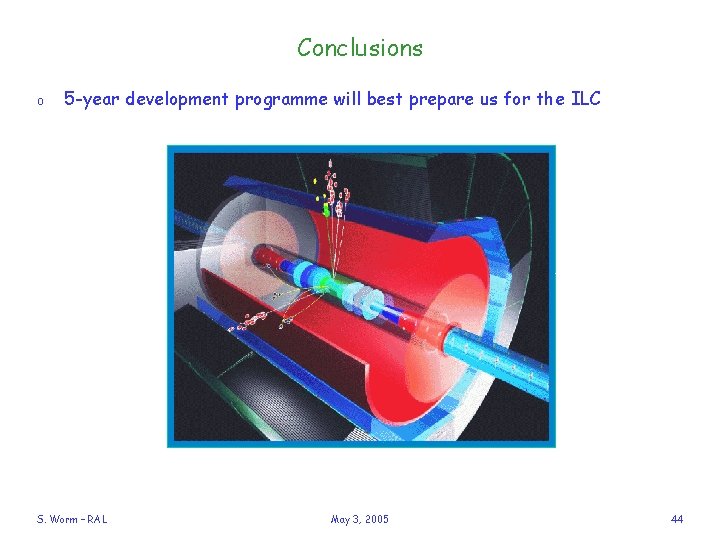

Conclusions o 5 -year development programme will best prepare us for the ILC S. Worm – RAL May 3, 2005 44

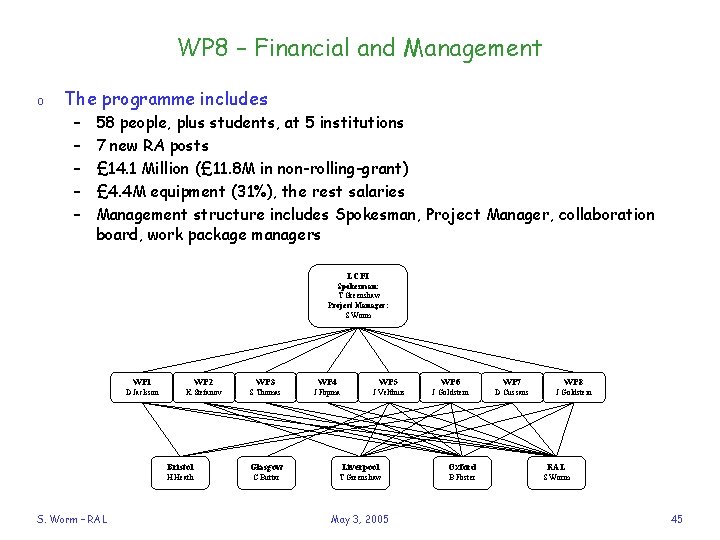

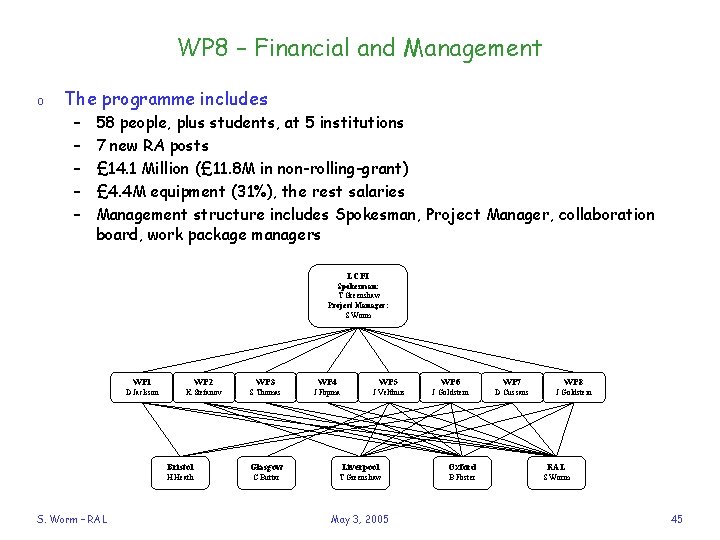

WP 8 – Financial and Management o The programme includes – – – 58 people, plus students, at 5 institutions 7 new RA posts £ 14. 1 Million (£ 11. 8 M in non-rolling-grant) £ 4. 4 M equipment (31%), the rest salaries Management structure includes Spokesman, Project Manager, collaboration board, work package managers LCFI Spokesman: T Greenshaw Project Manager: S Worm S. Worm – RAL WP 1 WP 2 WP 3 WP 4 WP 5 WP 6 WP 7 WP 8 D Jackson K Stefanov S Thomas J Fopma J Velthuis J Goldstein D Cussans J Goldstein Bristol Glasgow Liverpool Oxford RAL H Heath C Buttar T Greenshaw B Foster S Worm May 3, 2005 45

S. Worm – RAL May 3, 2005 46

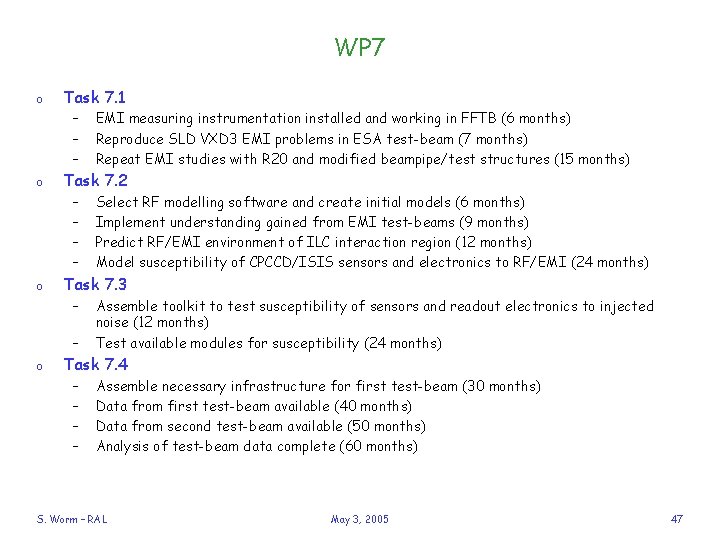

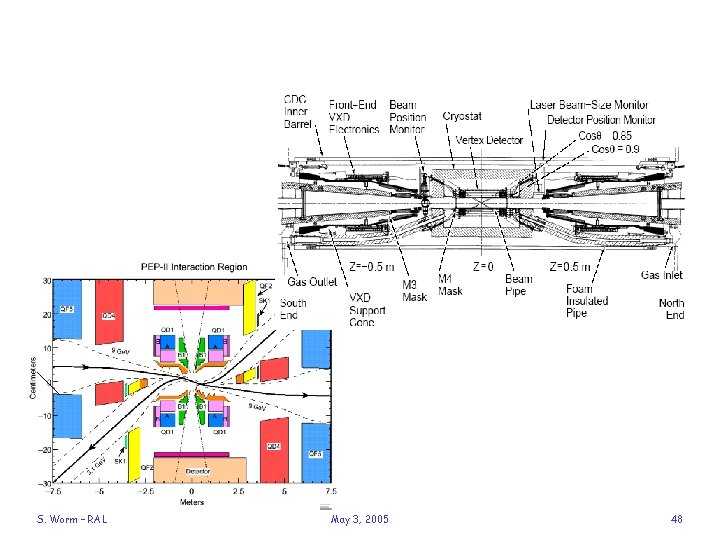

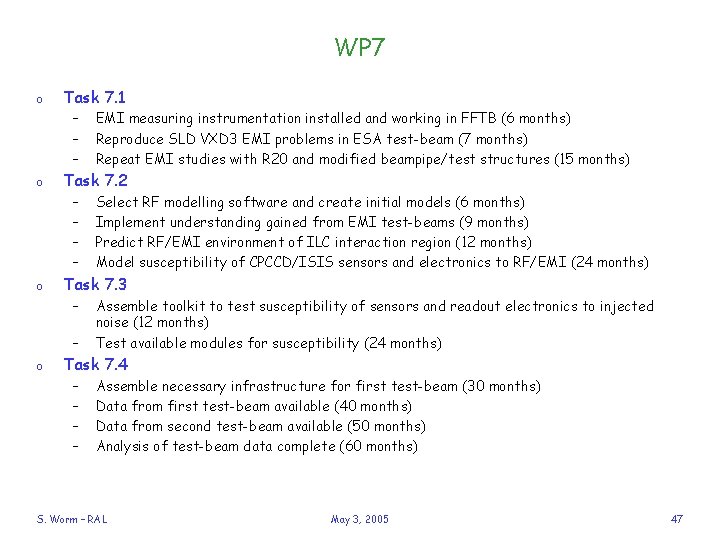

WP 7 o Task 7. 1 – – – o Task 7. 2 – – o Select RF modelling software and create initial models (6 months) Implement understanding gained from EMI test-beams (9 months) Predict RF/EMI environment of ILC interaction region (12 months) Model susceptibility of CPCCD/ISIS sensors and electronics to RF/EMI (24 months) Task 7. 3 – – o EMI measuring instrumentation installed and working in FFTB (6 months) Reproduce SLD VXD 3 EMI problems in ESA test-beam (7 months) Repeat EMI studies with R 20 and modified beampipe/test structures (15 months) Assemble toolkit to test susceptibility of sensors and readout electronics to injected noise (12 months) Test available modules for susceptibility (24 months) Task 7. 4 – – Assemble necessary infrastructure for first test-beam (30 months) Data from first test-beam available (40 months) Data from second test-beam available (50 months) Analysis of test-beam data complete (60 months) S. Worm – RAL May 3, 2005 47

S. Worm – RAL May 3, 2005 48

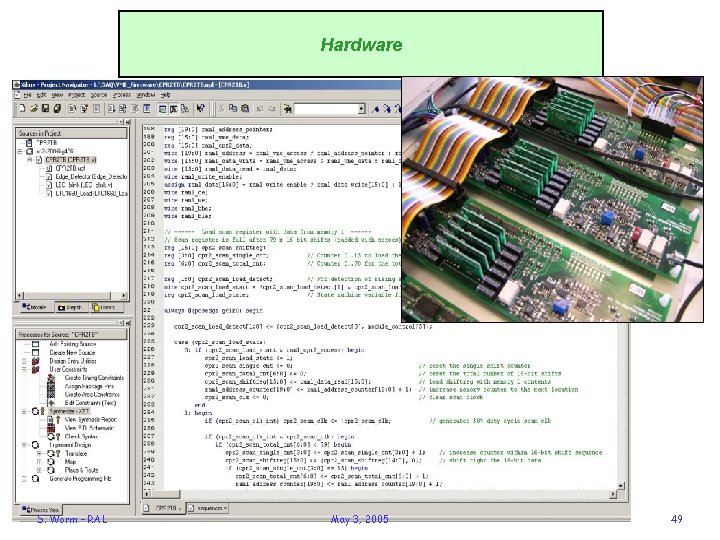

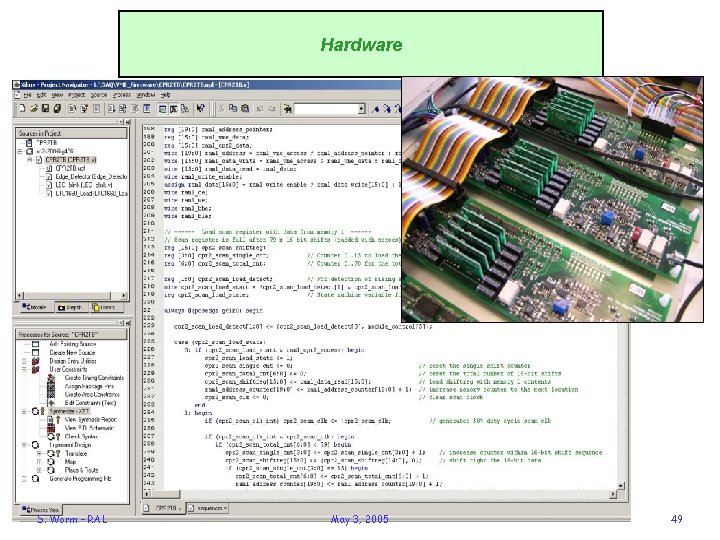

Hardware S. Worm – RAL May 3, 2005 49

S. Worm – RAL May 3, 2005 50

S. Worm – RAL May 3, 2005 51

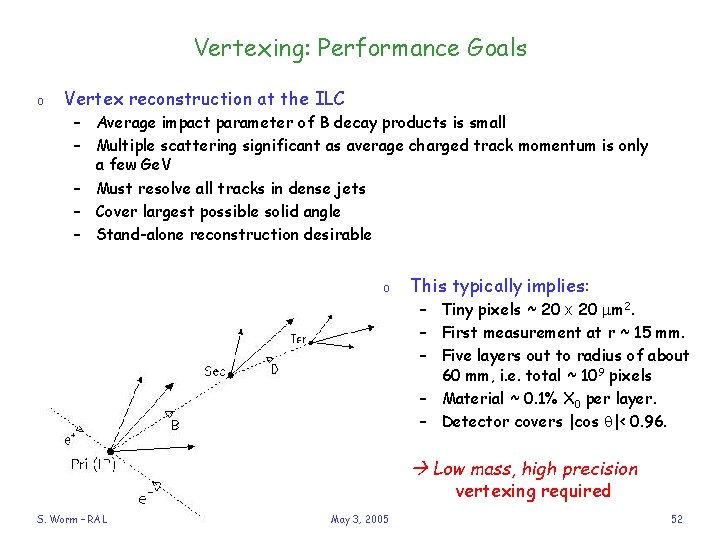

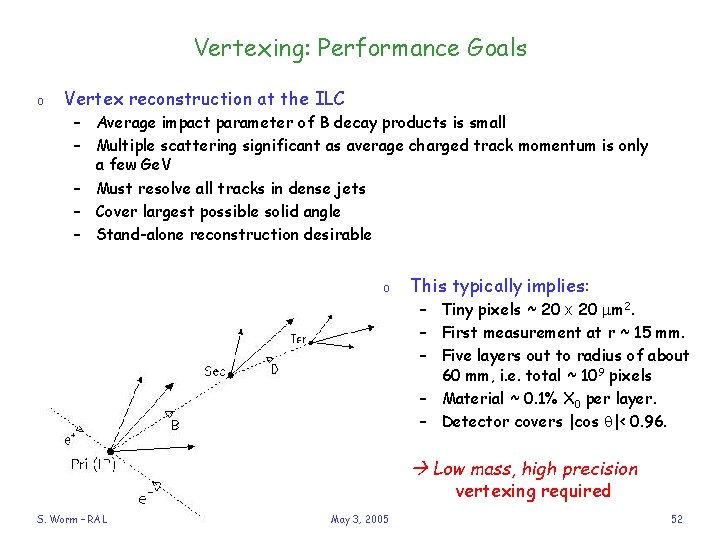

Vertexing: Performance Goals o Vertex reconstruction at the ILC – Average impact parameter of B decay products is small – Multiple scattering significant as average charged track momentum is only a few Ge. V – Must resolve all tracks in dense jets – Cover largest possible solid angle – Stand-alone reconstruction desirable o This typically implies: – Tiny pixels ~ 20 x 20 m 2. – First measurement at r ~ 15 mm. – Five layers out to radius of about 60 mm, i. e. total ~ 109 pixels – Material ~ 0. 1% X 0 per layer. – Detector covers |cos q|< 0. 96. Low mass, high precision vertexing required S. Worm – RAL May 3, 2005 52

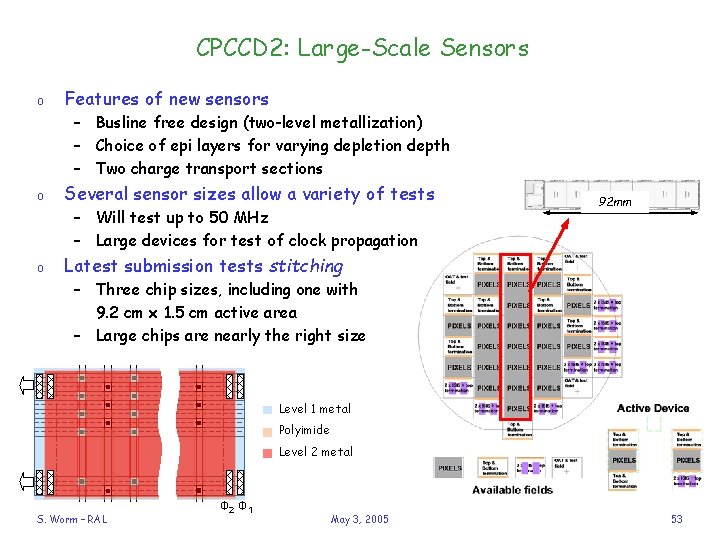

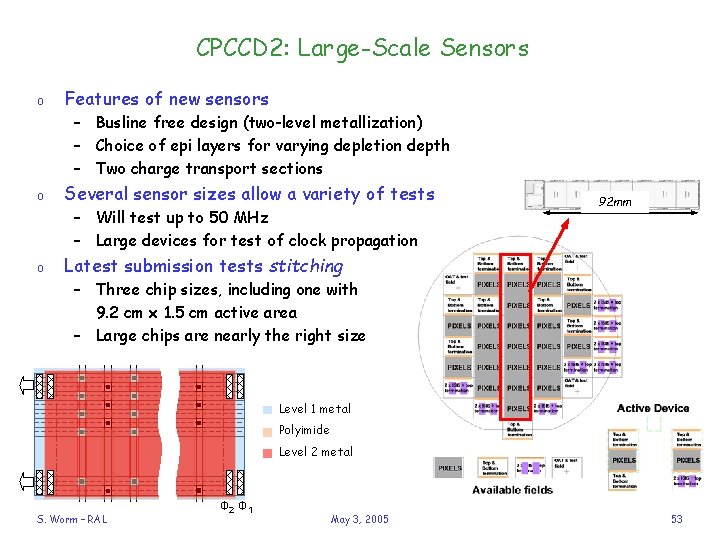

CPCCD 2: Large-Scale Sensors o Features of new sensors – Busline free design (two-level metallization) – Choice of epi layers for varying depletion depth – Two charge transport sections o Several sensor sizes allow a variety of tests – Will test up to 50 MHz – Large devices for test of clock propagation o 92 mm Latest submission tests stitching – Three chip sizes, including one with 9. 2 cm x 1. 5 cm active area – Large chips are nearly the right size Level 1 metal Polyimide Level 2 metal S. Worm – RAL Φ 2 Φ 1 May 3, 2005 53

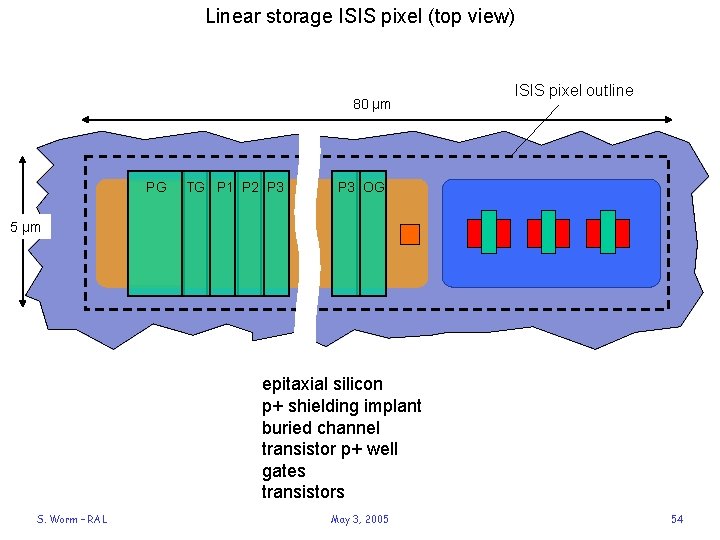

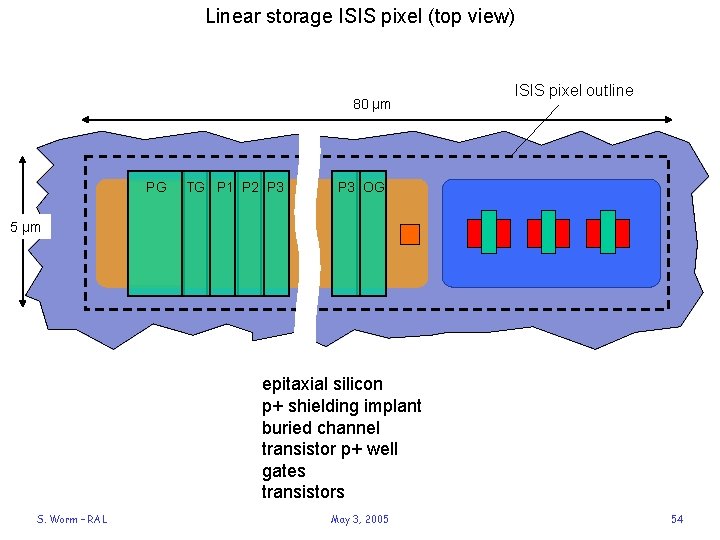

Linear storage ISIS pixel (top view) 80 μm PG TG P 1 P 2 P 3 ISIS pixel outline P 3 OG 5 μm epitaxial silicon p+ shielding implant buried channel transistor p+ well gates transistors S. Worm – RAL May 3, 2005 54

Reset transistor Source follower Row select transistor photogate transfer storage pixel #1 gate storage output sense reset VDD pixel #20 gate node (n+) gate row to column select load n+ buried channel (n) p+ well p+ shielding implant reflected charge Charge collection High resistivity epitaxial layer (p) photogate transfer storage pixel #1 gate reflected charge substrate (p+) Design A reset VDD storage output sense pixel #20 gate node (n+) gate row to column select load n+ buried channel (n) p+ well reflected charge Charge collection reflected charge High resistivity epitaxial layer (p) S. Worm – RAL substrate (p+) May 3, 2005 Design B 55

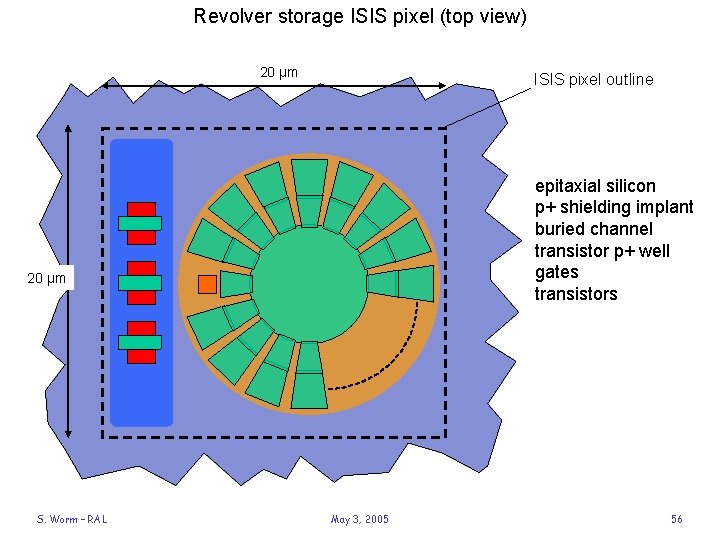

Revolver storage ISIS pixel (top view) 20 μm ISIS pixel outline epitaxial silicon p+ shielding implant buried channel transistor p+ well gates transistors 20 μm S. Worm – RAL May 3, 2005 56

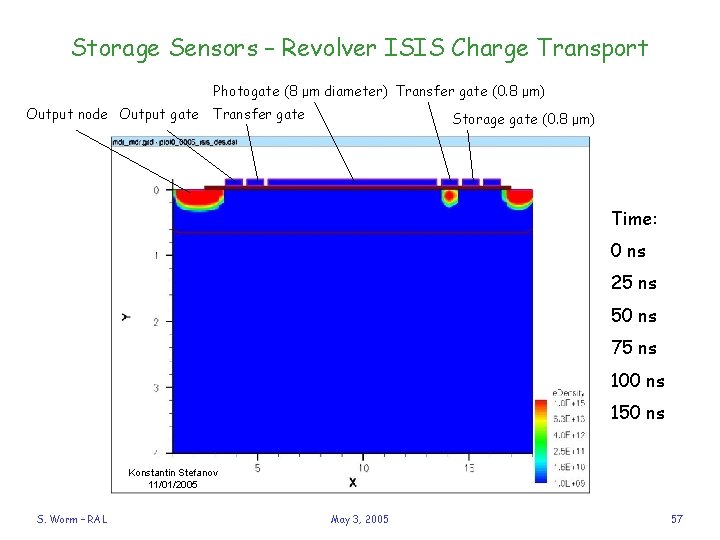

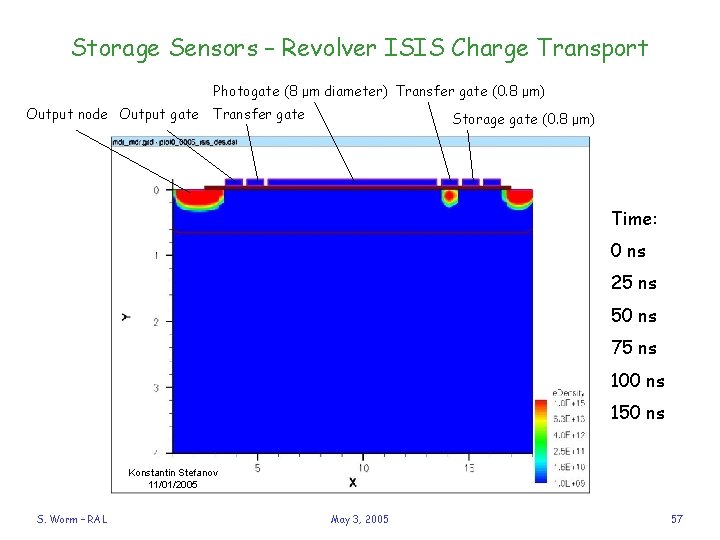

Storage Sensors – Revolver ISIS Charge Transport Photogate (8 μm diameter) Transfer gate (0. 8 μm) Output node Output gate Transfer gate Storage gate (0. 8 μm) Time: 0 ns 25 ns 50 ns 75 ns 100 ns 150 ns Konstantin Stefanov 11/01/2005 S. Worm – RAL May 3, 2005 57

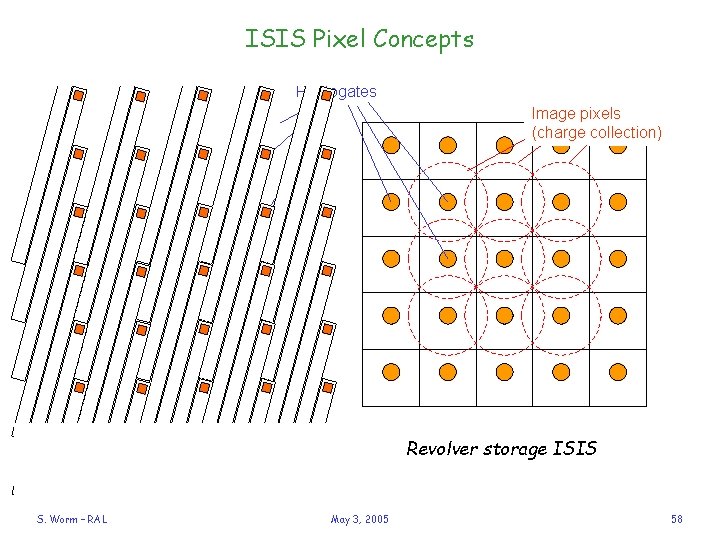

ISIS Pixel Concepts Photogates Image pixels (charge collection) Revolver storage ISIS S. Worm – RAL May 3, 2005 58

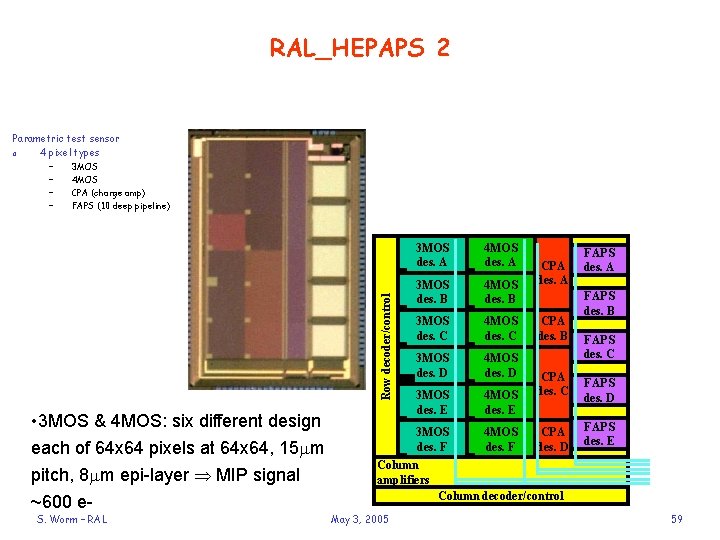

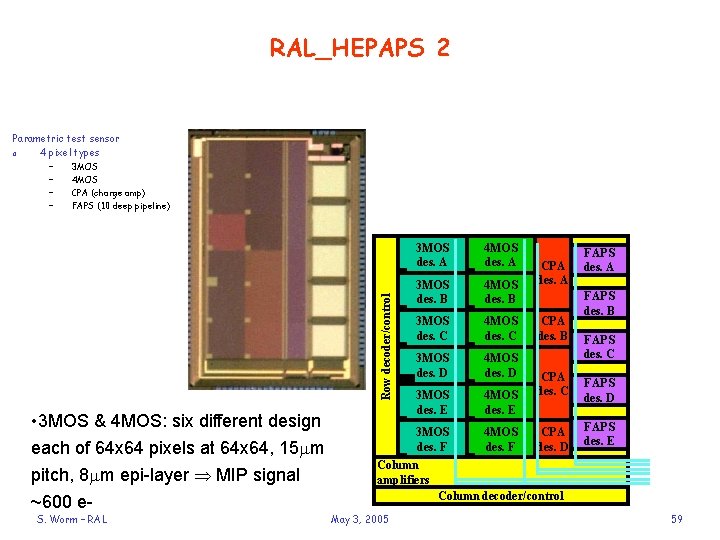

RAL_HEPAPS 2 Parametric test sensor o 4 pixel types 3 MOS 4 MOS CPA (charge amp) FAPS (10 deep pipeline) Row decoder/control – – • 3 MOS & 4 MOS: six different design each of 64 x 64 pixels at 64 x 64, 15 m pitch, 8 m epi-layer MIP signal ~600 e. S. Worm – RAL 3 MOS des. A 4 MOS des. A 3 MOS des. B 4 MOS des. B 3 MOS des. C 4 MOS des. C 3 MOS des. D 4 MOS des. D 3 MOS des. E 4 MOS des. E 3 MOS des. F 4 MOS des. F CPA des. A CPA des. B CPA des. C CPA des. D FAPS des. A FAPS des. B FAPS des. C FAPS des. D FAPS des. E Column amplifiers Column decoder/control May 3, 2005 59

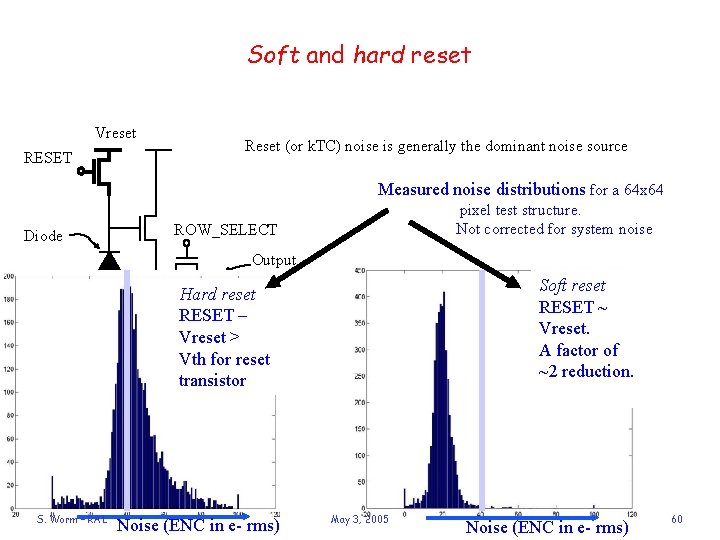

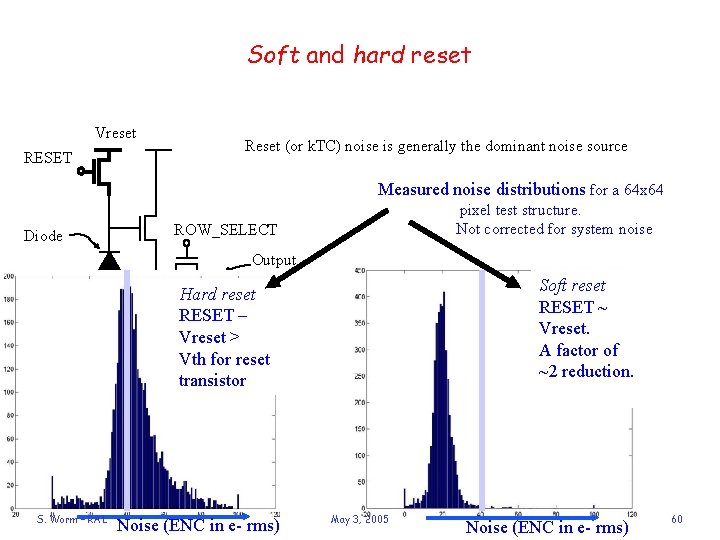

Soft and hard reset Vreset RESET Reset (or k. TC) noise is generally the dominant noise source Measured noise distributions for a 64 x 64 Diode pixel test structure. Not corrected for system noise ROW_SELECT Output Soft reset RESET ~ Vreset. A factor of ~2 reduction. Hard reset RESET – Vreset > Vth for reset transistor S. Worm – RAL Noise (ENC in e- rms) May 3, 2005 Noise (ENC in e- rms) 60

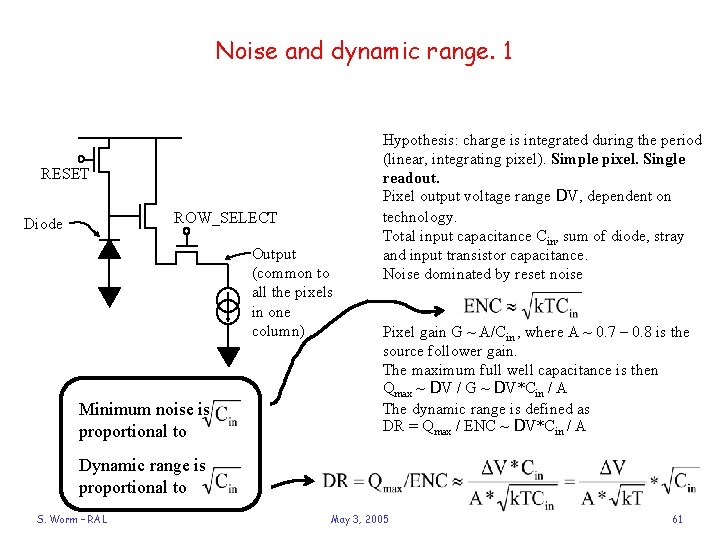

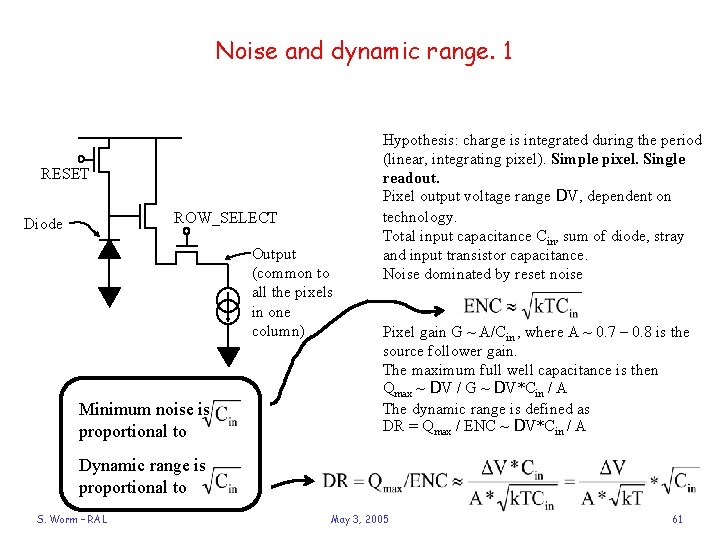

Noise and dynamic range. 1 RESET ROW_SELECT Diode Output (common to all the pixels in one column) Minimum noise is proportional to Hypothesis: charge is integrated during the period (linear, integrating pixel). Simple pixel. Single readout. Pixel output voltage range DV, dependent on technology. Total input capacitance Cin, sum of diode, stray and input transistor capacitance. Noise dominated by reset noise Pixel gain G ~ A/Cin , where A ~ 0. 7 – 0. 8 is the source follower gain. The maximum full well capacitance is then Qmax ~ DV / G ~ DV*Cin / A The dynamic range is defined as DR = Qmax / ENC ~ DV*Cin / A Dynamic range is proportional to S. Worm – RAL May 3, 2005 61

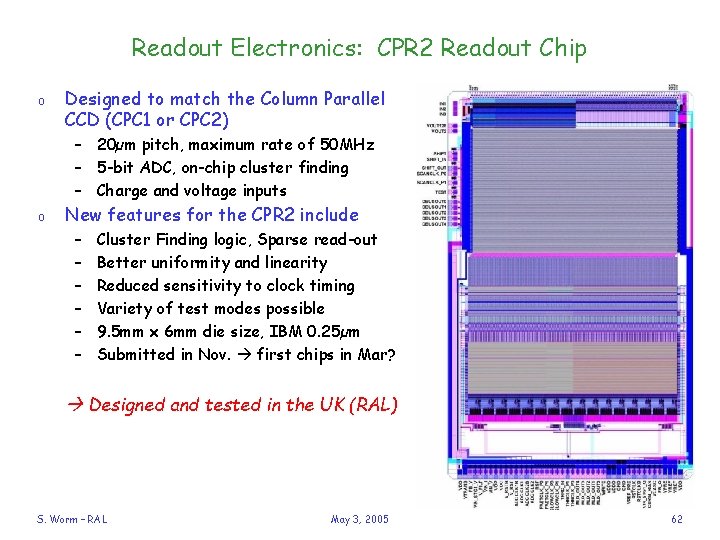

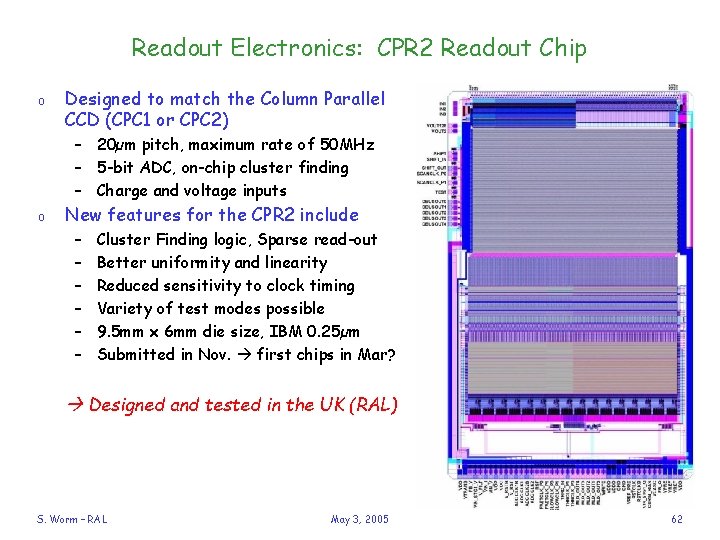

Readout Electronics: CPR 2 Readout Chip o Designed to match the Column Parallel CCD (CPC 1 or CPC 2) – 20µm pitch, maximum rate of 50 MHz – 5 -bit ADC, on-chip cluster finding – Charge and voltage inputs o New features for the CPR 2 include – – – Cluster Finding logic, Sparse read-out Better uniformity and linearity Reduced sensitivity to clock timing Variety of test modes possible 9. 5 mm x 6 mm die size, IBM 0. 25µm Submitted in Nov. first chips in Mar? Designed and tested in the UK (RAL) S. Worm – RAL May 3, 2005 62