Forward Error Correcting FEC coding for Super B

Forward Error Correcting (FEC) coding for Super. B serial links: a preliminary study Sergio Cavaliere q Department of Physics, University of Napoli “Federico II”, Italy and q INFN Sezione di Napoli, Italy e-mail: sergio. cavaliere@na. infn. it

Outline n n n FEC codes Coding in the Super. B serial links Hamming vs. Reed Solomon Case studies Interleaving and other demons…. conclusions Cavaliere - Super. B Workshop - march 2010 2

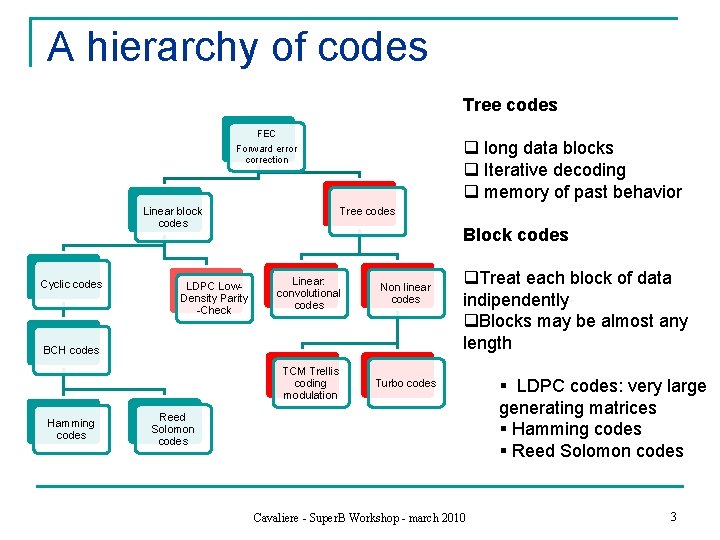

A hierarchy of codes Tree codes FEC Forward error correction Linear block codes Cyclic codes LDPC Low. Density Parity -Check q long data blocks q Iterative decoding q memory of past behavior Tree codes Block codes Linear: convolutional codes Non linear codes TCM Trellis coding modulation Turbo codes BCH codes Hamming codes q. Treat each block of data indipendently q. Blocks may be almost any length Reed Solomon codes Cavaliere - Super. B Workshop - march 2010 § LDPC codes: very large generating matrices § Hamming codes § Reed Solomon codes 3

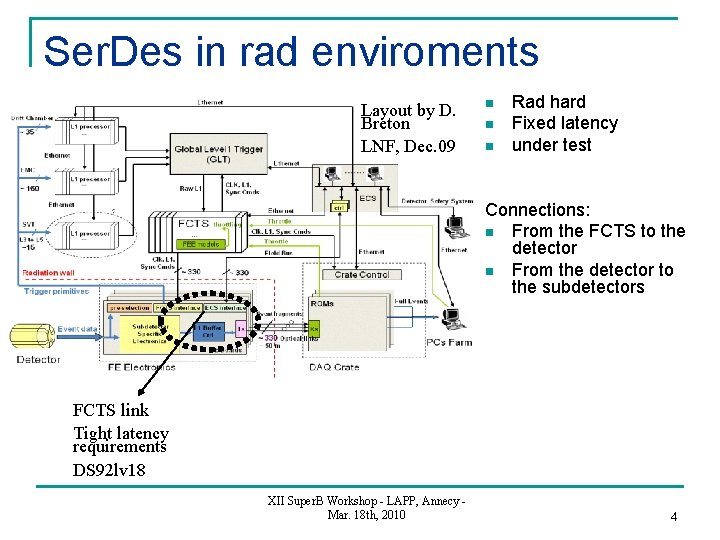

Ser. Des in rad enviroments Layout by D. Breton LNF, Dec. 09 n n n Rad hard Fixed latency under test Connections: n From the FCTS to the detector n From the detector to the subdetectors FCTS link Tight latency requirements DS 92 lv 18 XII Super. B Workshop - LAPP, Annecy Mar. 18 th, 2010 4

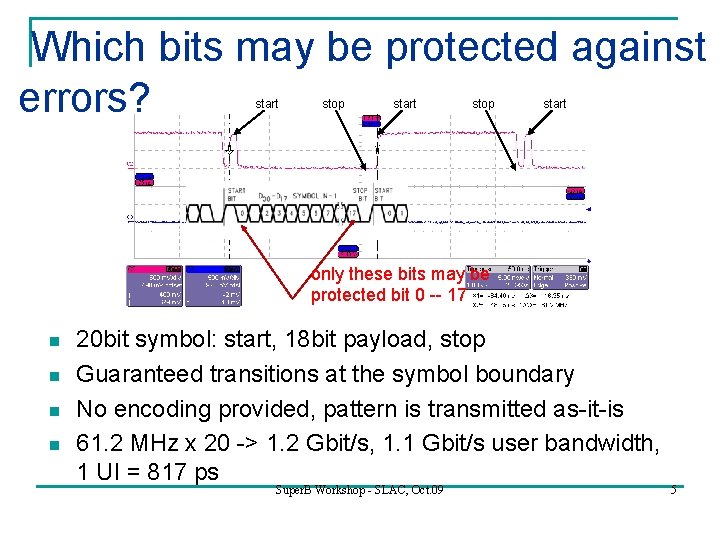

Which bits may be protected against errors? start stop start only these bits may be protected bit 0 -- 17 n n 20 bit symbol: start, 18 bit payload, stop Guaranteed transitions at the symbol boundary No encoding provided, pattern is transmitted as-it-is 61. 2 MHz x 20 -> 1. 2 Gbit/s, 1. 1 Gbit/s user bandwidth, 1 UI = 817 ps Super. B Workshop - SLAC, Oct. 09 5

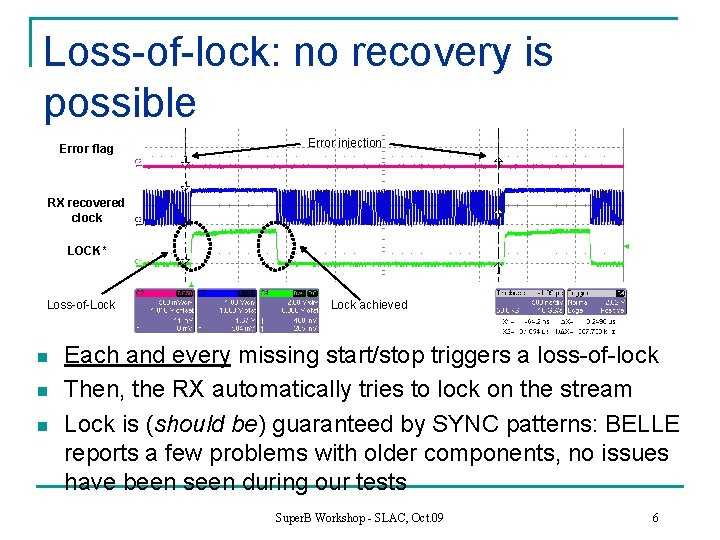

Loss-of-lock: no recovery is possible Error flag Error injection RX recovered clock LOCK* Loss-of-Lock n n n Lock achieved Each and every missing start/stop triggers a loss-of-lock Then, the RX automatically tries to lock on the stream Lock is (should be) guaranteed by SYNC patterns: BELLE reports a few problems with older components, no issues have been seen during our tests Super. B Workshop - SLAC, Oct. 09 6

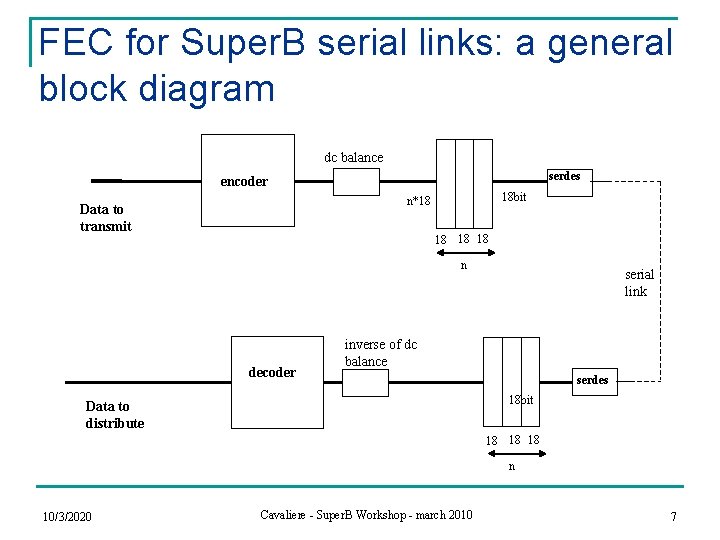

FEC for Super. B serial links: a general block diagram dc balance serdes encoder 18 bit n*18 Data to transmit 18 18 18 n decoder serial link inverse of dc balance serdes 18 bit Data to distribute 18 18 18 n 10/3/2020 Cavaliere - Super. B Workshop - march 2010 7

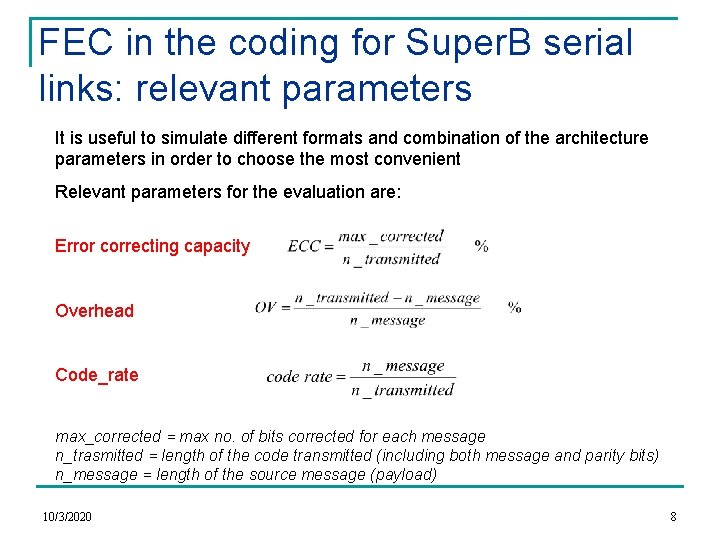

FEC in the coding for Super. B serial links: relevant parameters It is useful to simulate different formats and combination of the architecture parameters in order to choose the most convenient Relevant parameters for the evaluation are: Error correcting capacity Overhead Code_rate max_corrected = max no. of bits corrected for each message n_trasmitted = length of the code transmitted (including both message and parity bits) n_message = length of the source message (payload) 10/3/2020 8

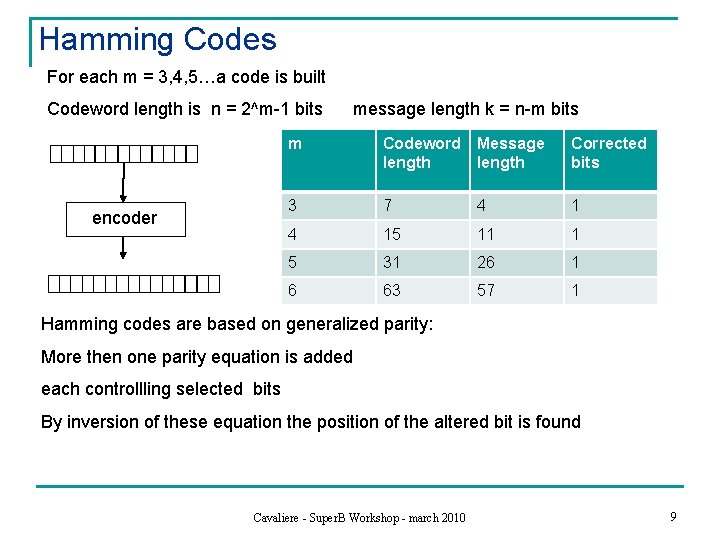

Hamming Codes For each m = 3, 4, 5…a code is built Codeword length is n = 2^m-1 bits encoder message length k = n-m bits m Codeword length Message length Corrected bits 3 7 4 15 11 1 5 31 26 1 6 63 57 1 Hamming codes are based on generalized parity: More then one parity equation is added each controllling selected bits By inversion of these equation the position of the altered bit is found Cavaliere - Super. B Workshop - march 2010 9

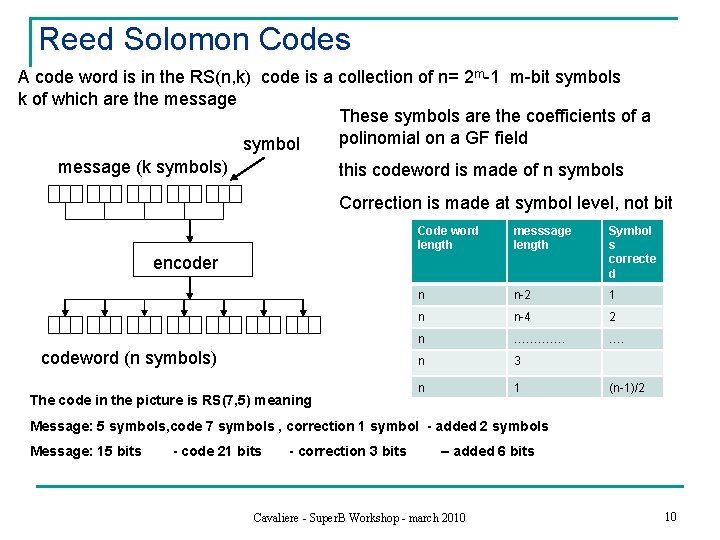

Reed Solomon Codes A code word is in the RS(n, k) code is a collection of n= 2 m-1 m-bit symbols k of which are the message These symbols are the coefficients of a polinomial on a GF field symbol message (k symbols) this codeword is made of n symbols Correction is made at symbol level, not bit Code word length messsage length Symbol s correcte d n n-2 1 n n-4 2 n …………. n 3 n 1 encoder codeword (n symbols) The code in the picture is RS(7, 5) meaning (n-1)/2 Message: 5 symbols, code 7 symbols , correction 1 symbol - added 2 symbols Message: 15 bits - code 21 bits - correction 3 bits – added 6 bits Cavaliere - Super. B Workshop - march 2010 10

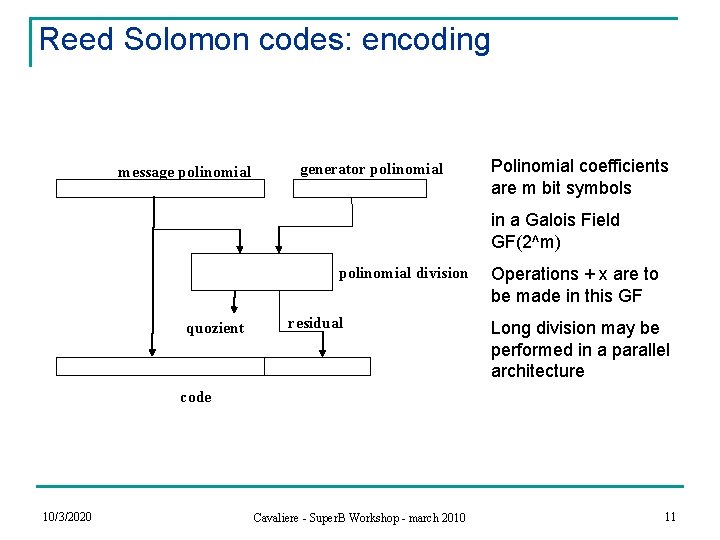

Reed Solomon codes: encoding message polinomial generator polinomial Polinomial coefficients are m bit symbols in a Galois Field GF(2^m) polinomial division quozient residual Operations + x are to be made in this GF Long division may be performed in a parallel architecture code 10/3/2020 Cavaliere - Super. B Workshop - march 2010 11

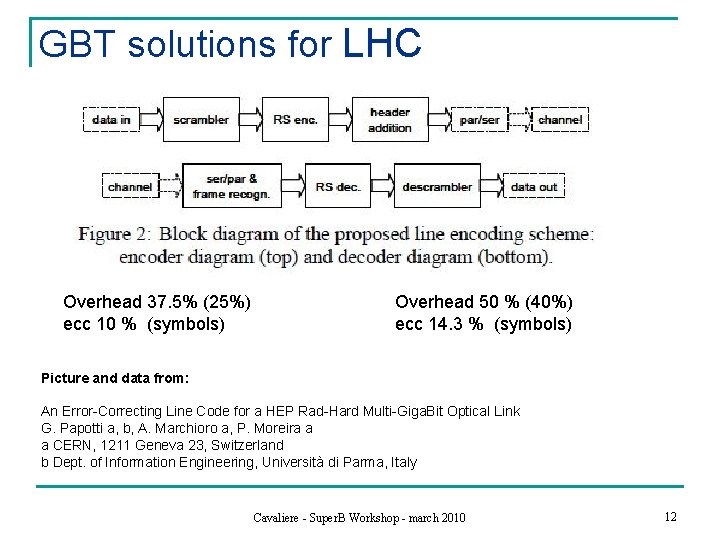

GBT solutions for LHC Overhead 37. 5% (25%) ecc 10 % (symbols) Overhead 50 % (40%) ecc 14. 3 % (symbols) Picture and data from: An Error-Correcting Line Code for a HEP Rad-Hard Multi-Giga. Bit Optical Link G. Papotti a, b, A. Marchioro a, P. Moreira a a CERN, 1211 Geneva 23, Switzerland b Dept. of Information Engineering, Università di Parma, Italy Cavaliere - Super. B Workshop - march 2010 12

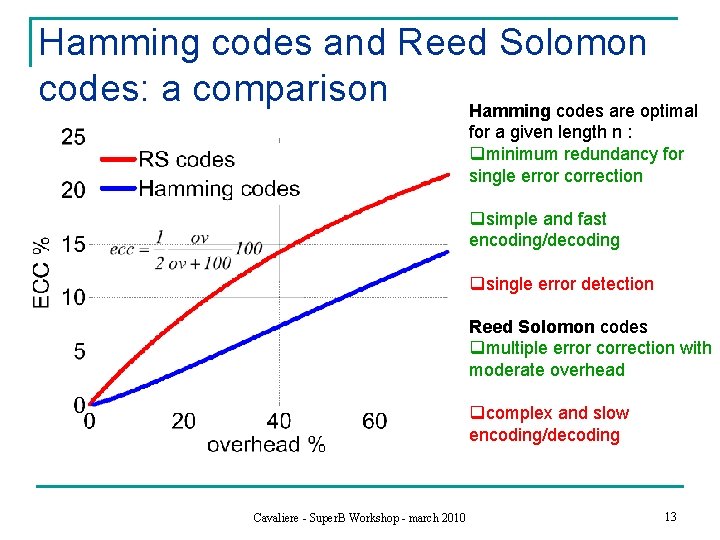

Hamming codes and Reed Solomon codes: a comparison Hamming codes are optimal for a given length n : qminimum redundancy for single error correction qsimple and fast encoding/decoding qsingle error detection Reed Solomon codes qmultiple error correction with moderate overhead qcomplex and slow encoding/decoding Cavaliere - Super. B Workshop - march 2010 13

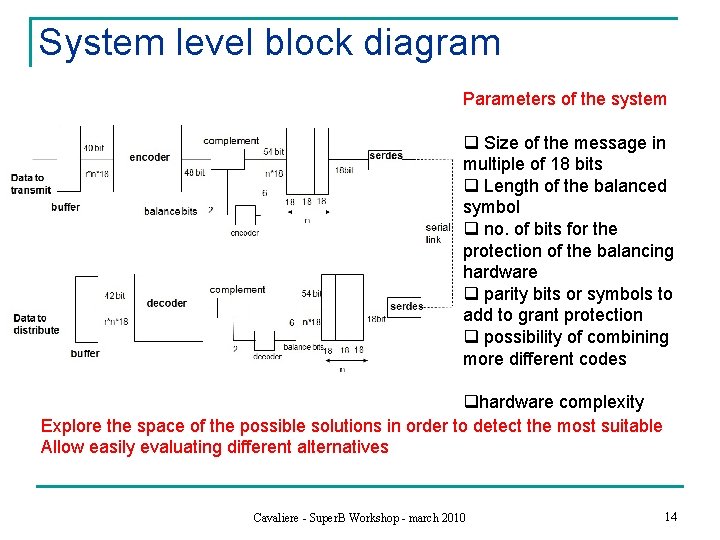

System level block diagram Parameters of the system q Size of the message in multiple of 18 bits q Length of the balanced symbol q no. of bits for the protection of the balancing hardware q parity bits or symbols to add to grant protection q possibility of combining more different codes qhardware complexity Explore the space of the possible solutions in order to detect the most suitable Allow easily evaluating different alternatives Cavaliere - Super. B Workshop - march 2010 14

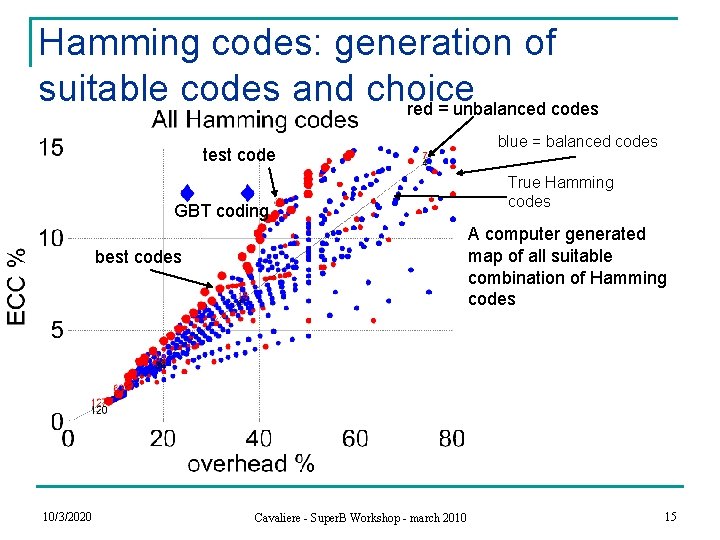

Hamming codes: generation of suitable codes and choice red = unbalanced codes test code GBT coding True Hamming codes A computer generated map of all suitable combination of Hamming codes best codes 10/3/2020 blue = balanced codes Cavaliere - Super. B Workshop - march 2010 15

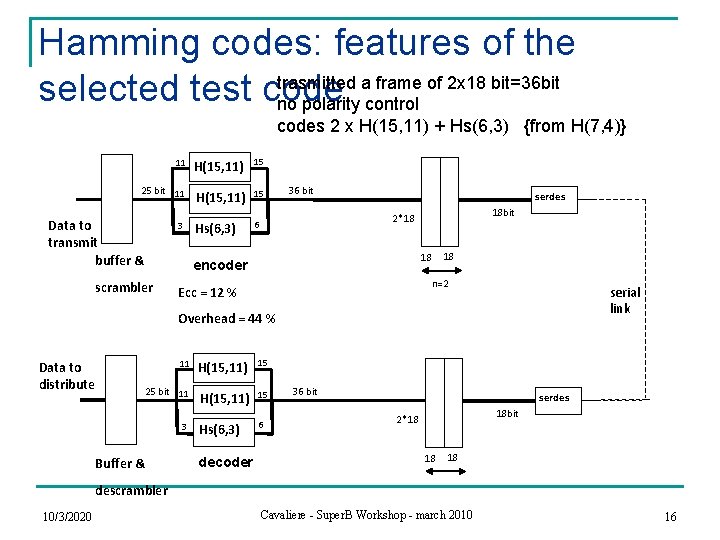

Hamming codes: features of the trasmitted a frame of 2 x 18 bit=36 bit selected test code no polarity control codes 2 x H(15, 11) + Hs(6, 3) {from H(7, 4)} 11 25 bit 11 Data to transmit buffer & 3 H(15, 11) 15 Hs(6, 3) 6 36 bit serdes 18 18 encoder scrambler 18 bit 2*18 n=2 Ecc = 12 % serial link Overhead = 44 % 11 Data to distribute 25 bit 11 3 Buffer & H(15, 11) 15 Hs(6, 3) 6 decoder 36 bit serdes 18 bit 2*18 18 18 descrambler 10/3/2020 Cavaliere - Super. B Workshop - march 2010 16

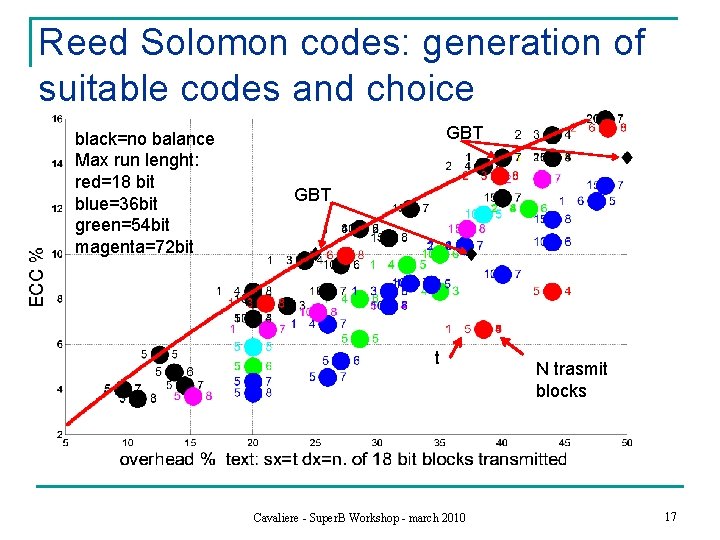

Reed Solomon codes: generation of suitable codes and choice black=no balance Max run lenght: red=18 bit blue=36 bit green=54 bit magenta=72 bit GBT t Cavaliere - Super. B Workshop - march 2010 N trasmit blocks 17

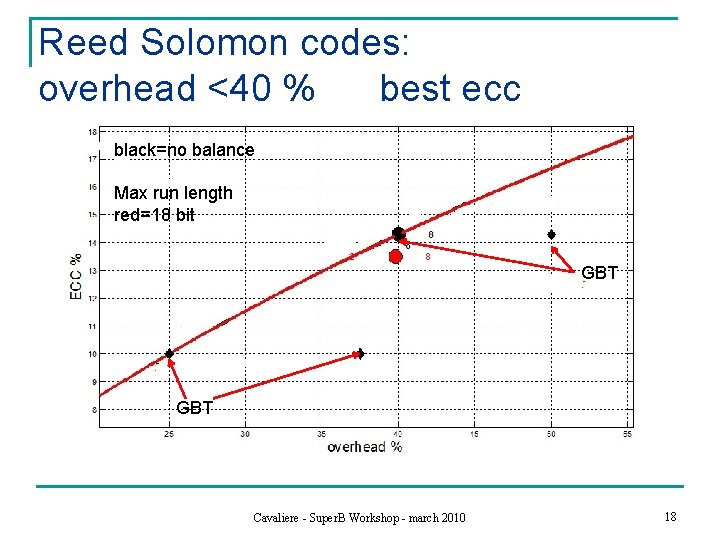

Reed Solomon codes: overhead <40 % best ecc black=no balance Max run length red=18 bit GBT Cavaliere - Super. B Workshop - march 2010 18

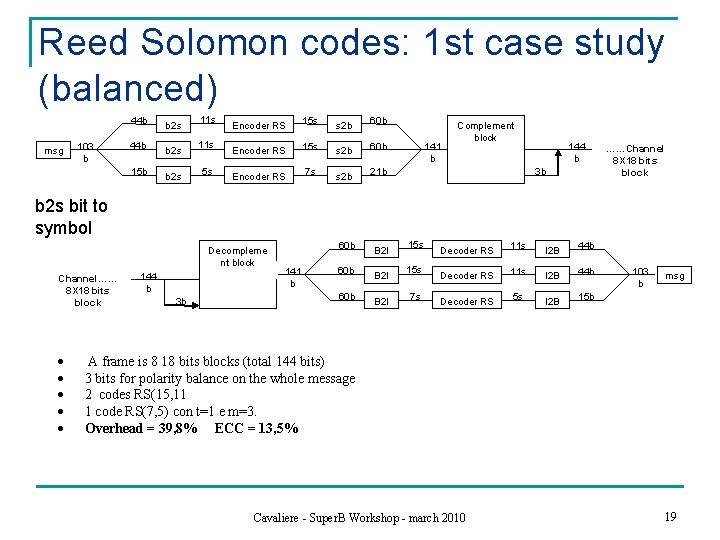

Reed Solomon codes: 1 st case study (balanced) 44 b msg 103 b 44 b 15 b b 2 s 11 s 5 s Encoder RS 15 s s 2 b 60 b Encoder RS 7 s s 2 b 141 b Complement block 21 b 144 b 3 b ……Channel 8 X 18 bits block b 2 s bit to symbol Decompleme nt block Channel…… 8 X 18 bits block 144 b 3 b 60 b 141 b 60 b B 2 I 15 s 7 s Decoder RS 11 s I 2 B 44 b Decoder RS 5 s I 2 B 103 b msg 15 b A frame is 8 18 bits blocks (total 144 bits) 3 bits for polarity balance on the whole message 2 codes RS(15, 11 1 code RS(7, 5) con t=1 e m=3. Overhead = 39, 8% ECC = 13, 5% Cavaliere - Super. B Workshop - march 2010 19

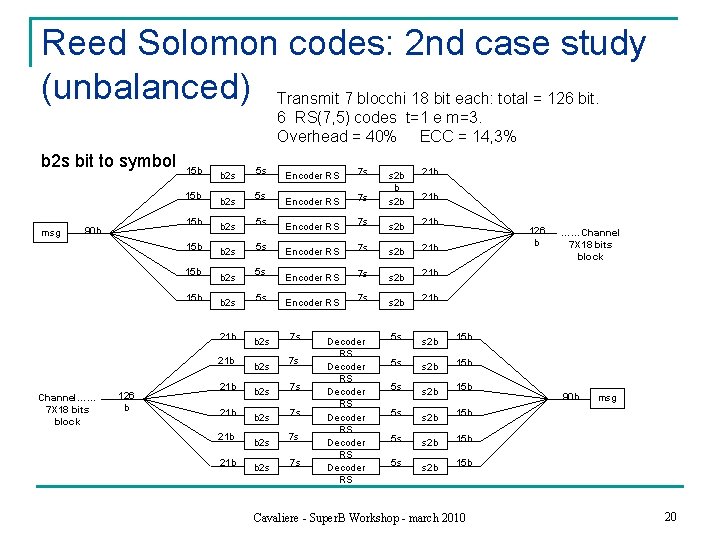

Reed Solomon codes: 2 nd case study (unbalanced) Transmit 7 blocchi 18 bit each: total = 126 bit. 6 RS(7, 5) codes t=1 e m=3. Overhead = 40% ECC = 14, 3% b 2 s bit to symbol 15 b msg 15 b 90 b 15 b 15 b b 2 s b 2 s 21 b Channel…… 7 X 18 bits block 126 b 21 b 21 b 5 s 5 s 5 s b 2 s b 2 s Encoder RS 7 s s 2 b b s 2 b 21 b 21 b Encoder RS 7 s s 2 b 21 b Encoder RS 7 s 7 s Decoder RS Decoder RS s 2 b 126 b 21 b 5 s s 2 b 15 b 5 s s 2 b 15 b 5 s ……Channel 7 X 18 bits block s 2 b 90 b msg 15 b Cavaliere - Super. B Workshop - march 2010 20

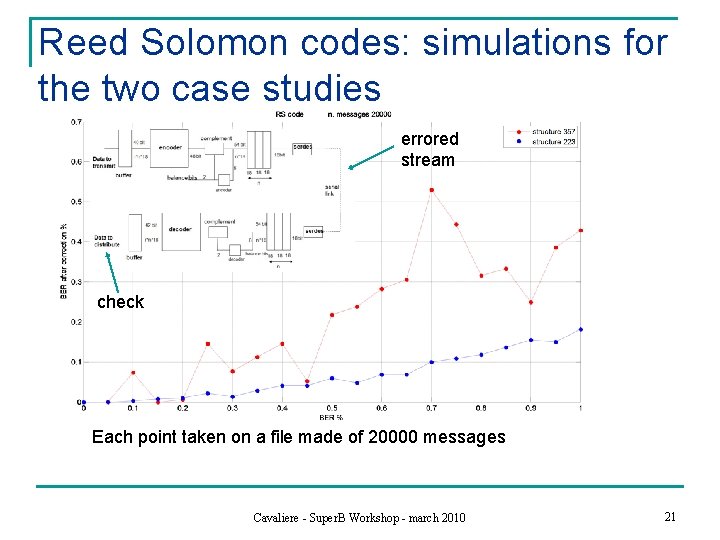

Reed Solomon codes: simulations for the two case studies errored stream check Each point taken on a file made of 20000 messages Cavaliere - Super. B Workshop - march 2010 21

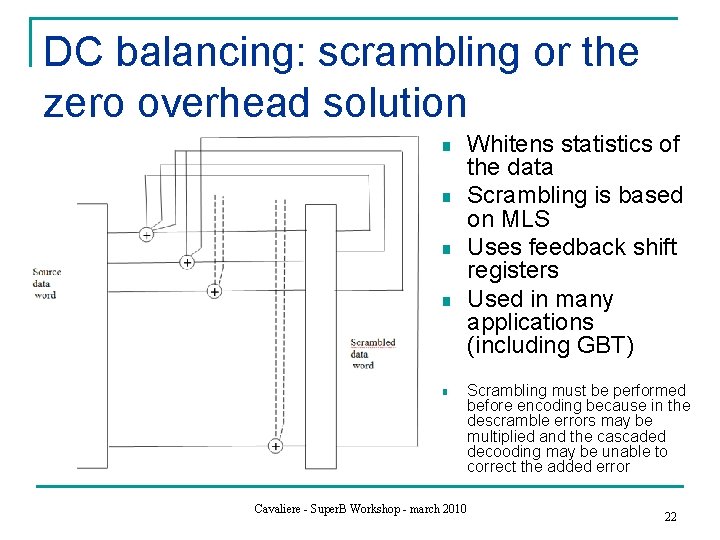

DC balancing: scrambling or the zero overhead solution n n Cavaliere - Super. B Workshop - march 2010 Whitens statistics of the data Scrambling is based on MLS Uses feedback shift registers Used in many applications (including GBT) Scrambling must be performed before encoding because in the descramble errors may be multiplied and the cascaded decooding may be unable to correct the added error 22

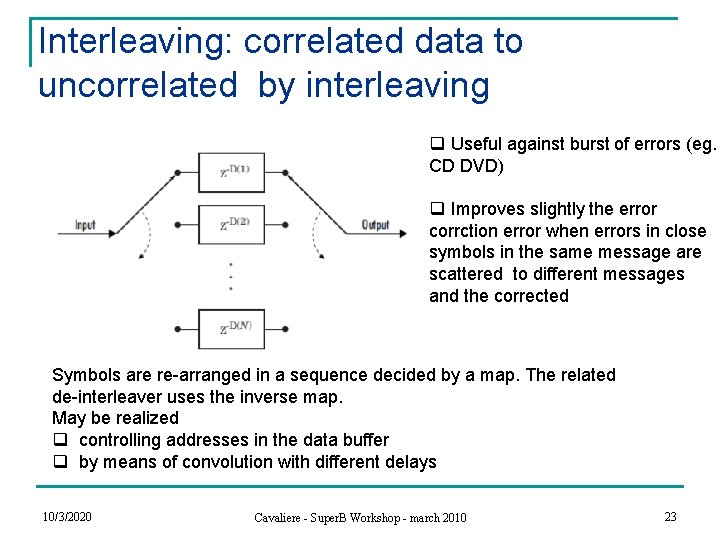

Interleaving: correlated data to uncorrelated by interleaving q Useful against burst of errors (eg. CD DVD) q Improves slightly the error corrction error when errors in close symbols in the same message are scattered to different messages and the corrected Symbols are re-arranged in a sequence decided by a map. The related de-interleaver uses the inverse map. May be realized q controlling addresses in the data buffer q by means of convolution with different delays 10/3/2020 Cavaliere - Super. B Workshop - march 2010 23

Conclusion n Preliminary analysis of coding schemes n Built tools to easily q q analyze alla possible architectural parameters and choose relevant parameters Filter the results by means of imposed prerequisites n Carried on simulations of different codes n Purposely realized logic compiler for coding/decoding architectures which will be easily interfaced to VHDL q q n Fully RTL for Hamming codes. High level, behavioral for RS codes Guidelines for the system level implementation Cavaliere - Super. B Workshop - march 2010 24

- Slides: 24