ECE 465 Lecture Notes 11 Clocking Methodologies Shantanu

- Slides: 24

ECE 465 Lecture Notes # 11 Clocking Methodologies Shantanu Dutt UIC Acknowledgement: (1) Most slides prepared by Huan Ren from Prof. Dutt’s Lecture Notes (some modifications made by Prof. Dutt). (2) Some slides extracted from Prof. David Pan’s (UT Austin) slides as indicated.

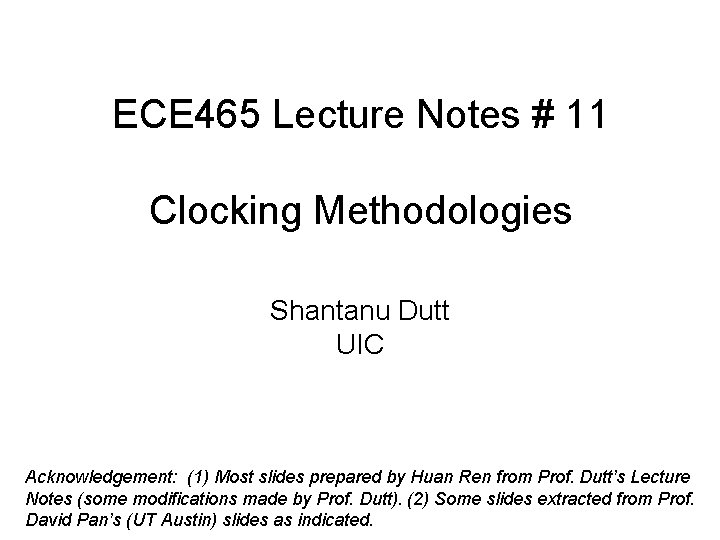

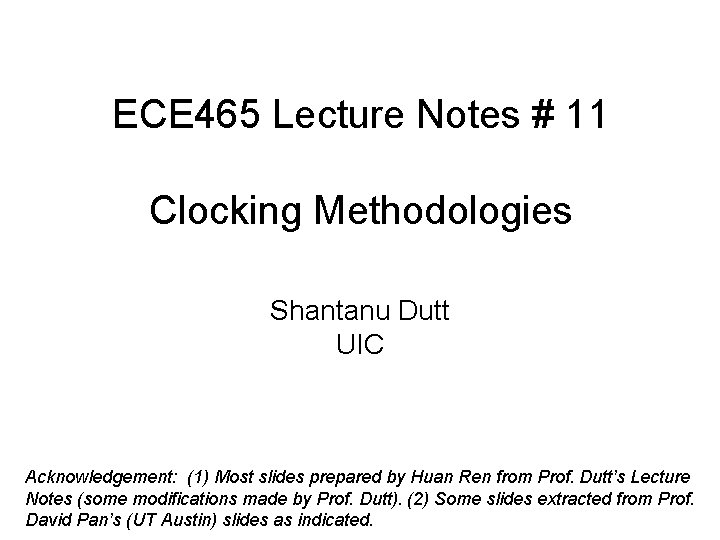

Timing Methodologies • Synchronous Sequential Circuits External I/P External O/P Comb. Logic TOPP, Logic 00, 11/0 Memory (critical path delay In the o/p logic part) TNSP, Logic (critical path delay In the NS logic part) Clk • Features Required for Correct Operation – 1) All State Transitions take place only with respect to a particular event in the clock (e. g. , positive or negative edge, etc. ) 01/1 00, 01, 10/0 B 01/0 11/0 C 10, 00/1 A Transition occurs only on positive edge of Clk

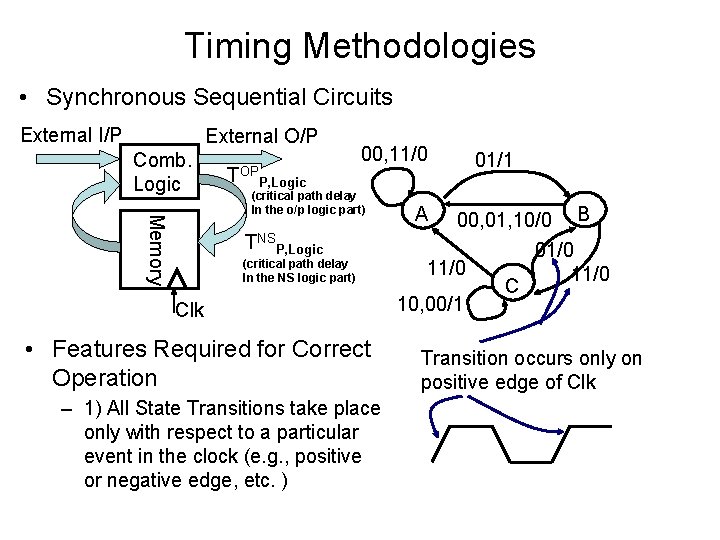

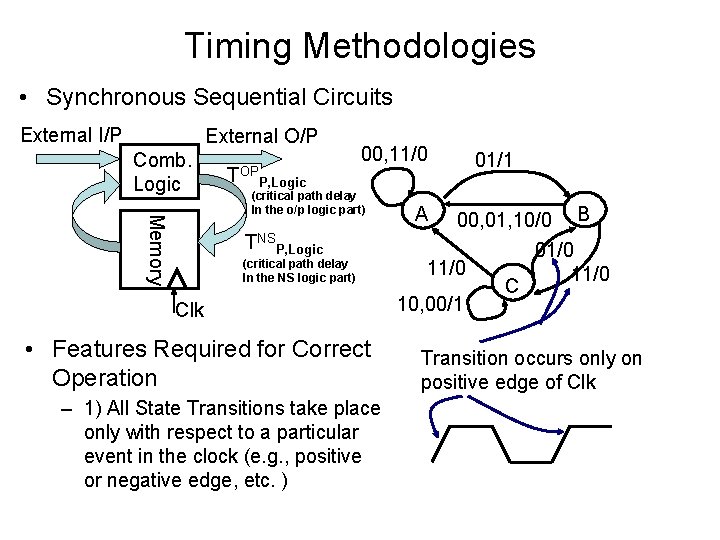

Timing Methodologies (contd) • Features Required for Correct Operation – 2) Only one state transition should take place in one clock period. – 3) All inputs to all FFs/latches should be correctly available with appropriate setup time (Tsetup or Tsu) and hold time (Thold or Th) around the triggering edge of the clock. ≥ Tsetup ≥ Thold Input Clock Tperiod =TClk i’th state transition (i+1)’th state (i+2)’th state transition [could be to the same state] (i+3)’th state transition

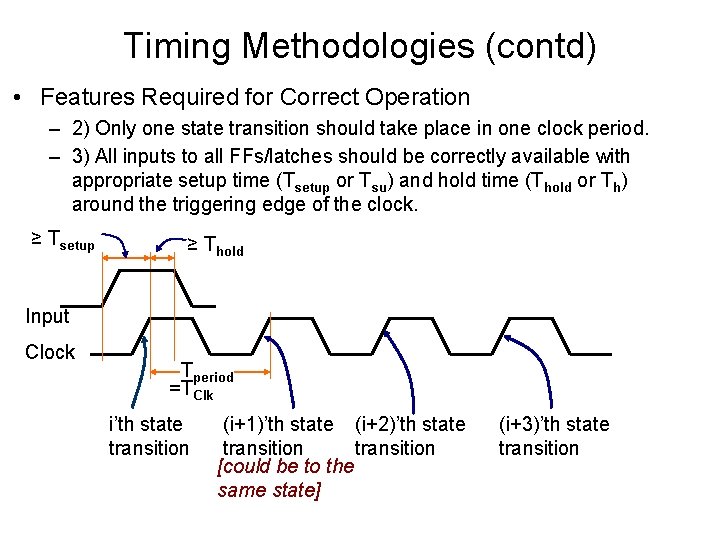

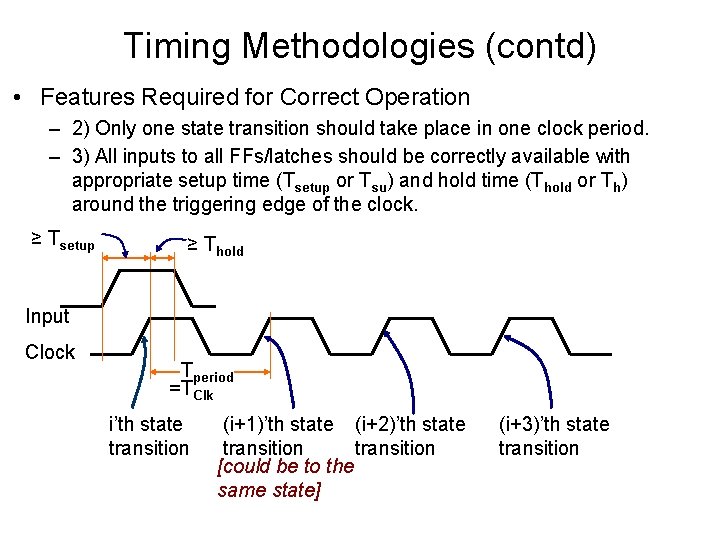

Clock Routing • A path from the clock source to clock sinks (FFs) • Different FFs are at different distances from the clock source Clock Source FF FF FF • This leads to the clock arriving at different FFs at slightly different time. This difference in clock arrival times is called clock skew From: David Pan, UT Austin

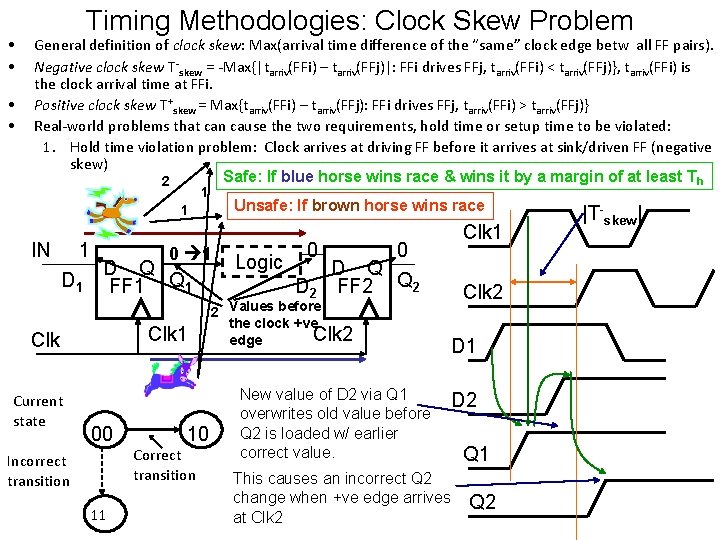

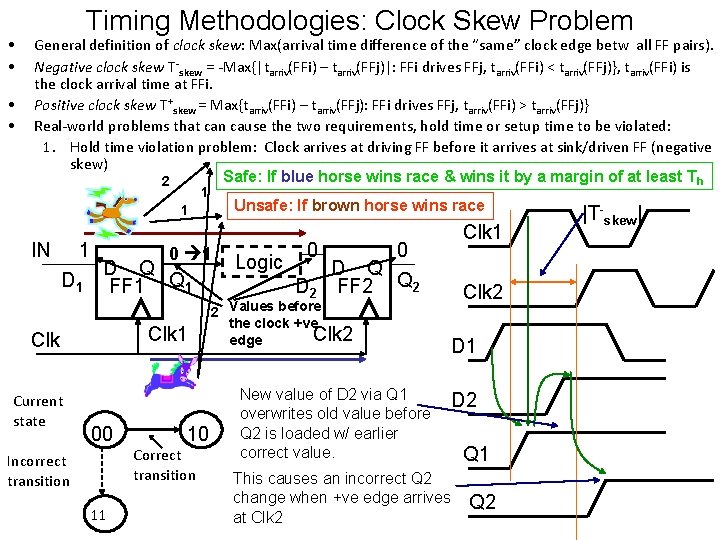

• • Timing Methodologies: Clock Skew Problem General definition of clock skew: Max(arrival time difference of the “same” clock edge betw all FF pairs). Negative clock skew T-skew = -Max{|tarriv(FFi) – tarriv(FFj)|: FFi drives FFj, tarriv(FFi) < tarriv(FFj)}, tarriv(FFi) is the clock arrival time at FFi. Positive clock skew T+skew = Max{tarriv(FFi) – tarriv(FFj): FFi drives FFj, tarriv(FFi) > tarriv(FFj)} Real-world problems that can cause the two requirements, hold time or setup time to be violated: 1. Hold time violation problem: Clock arrives at driving FF before it arrives at sink/driven FF (negative skew) Safe: If blue horse wins race & wins it by a margin of at least Th 2 1 Unsafe: If brown horse wins race 1 IN 1 D 1 0 1 D Q FF 1 Q 1 Clk Current state 00 10 Correct transition Incorrect transition 11 Logic 0 D 2 Clk 1 0 D Q FF 2 Q 2 2 Values before the clock +ve Clk 2 edge New value of D 2 via Q 1 overwrites old value before Q 2 is loaded w/ earlier correct value. Clk 2 D 1 D 2 This causes an incorrect Q 2 change when +ve edge arrives at Clk 2 Q 1 Q 2 |T-skew|

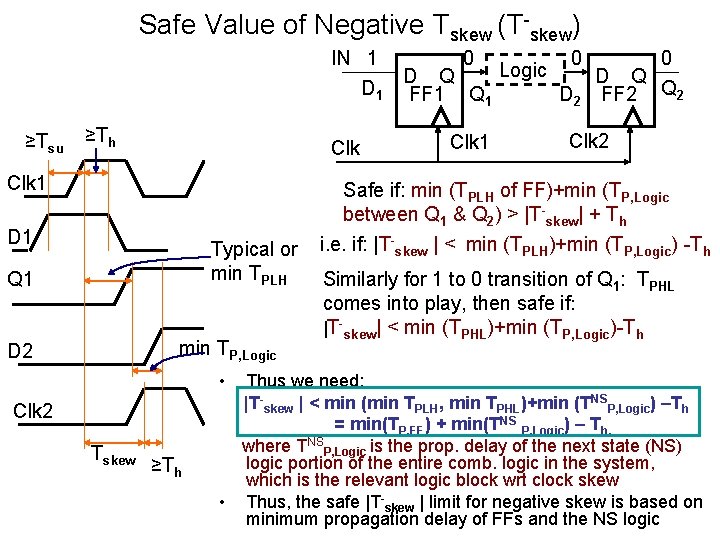

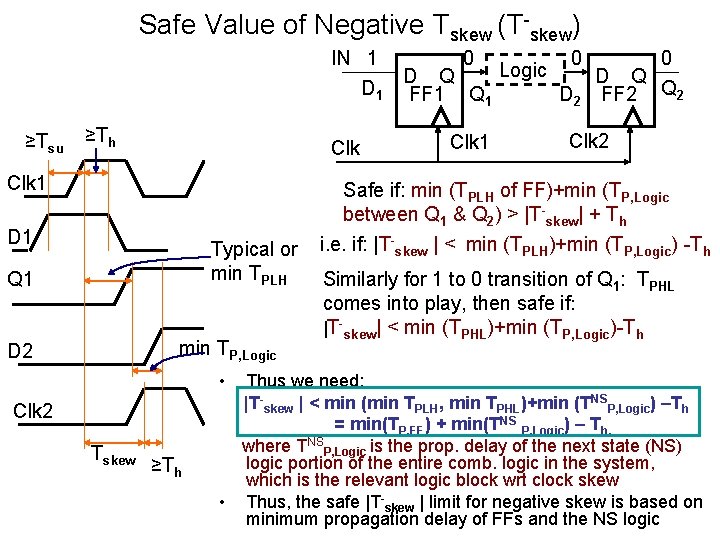

Safe Value of Negative Tskew (T-skew) IN 1 D 1 ≥Tsu ≥Th Clk 1 D 1 Typical or min TPLH Q 1 min TP, Logic D 2 • Clk 2 Tskew ≥Th 0 D Q FF 1 Q 1 Clk 1 Logic 0 D 2 0 D Q FF 2 Q 2 Clk 2 Safe if: min (TPLH of FF)+min (TP, Logic between Q 1 & Q 2) > |T-skew| + Th i. e. if: |T-skew | < min (TPLH)+min (TP, Logic) -Th Similarly for 1 to 0 transition of Q 1: TPHL comes into play, then safe if: |T-skew| < min (TPHL)+min (TP, Logic)-Th Thus we need: |T-skew | < min (min TPLH, min TPHL)+min (TNSP, Logic) –Th = min(TP, FF) + min(TNS P, Logic) – Th, where TNSP, Logic is the prop. delay of the next state (NS) logic portion of the entire comb. logic in the system, which is the relevant logic block wrt clock skew • Thus, the safe |T-skew | limit for negative skew is based on minimum propagation delay of FFs and the NS logic

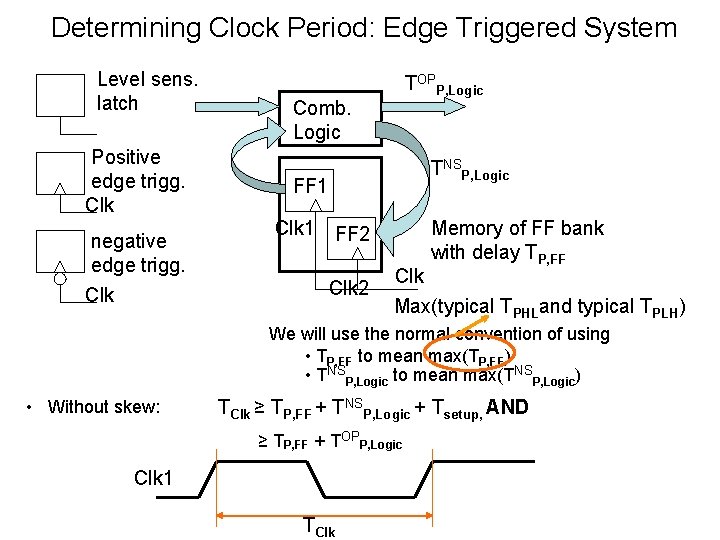

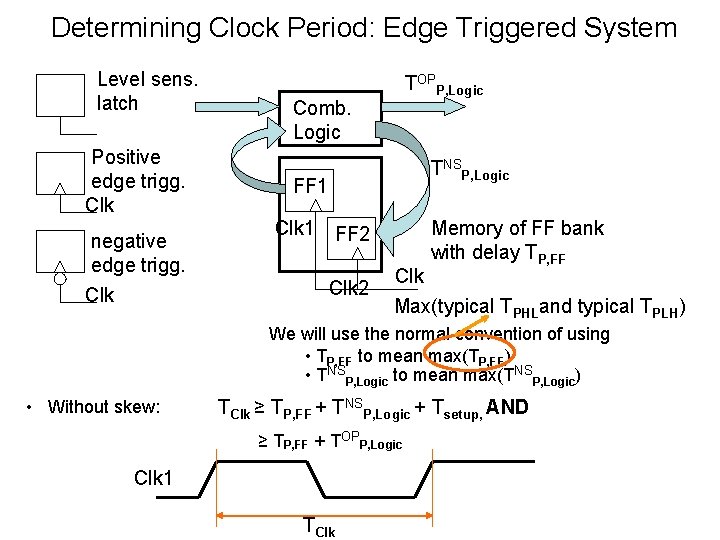

Determining Clock Period: Edge Triggered System Level sens. latch Positive edge trigg. Clk negative edge trigg. Clk TOPP, Logic Comb. Logic TNSP, Logic FF 1 Clk 1 FF 2 Clk 2 Memory of FF bank with delay TP, FF Clk Max(typical TPHLand typical TPLH) We will use the normal convention of using • TP, FF to mean max(TP, FF) • TNSP, Logic to mean max(TNSP, Logic) • Without skew: TClk ≥ TP, FF + TNSP, Logic + Tsetup, AND ≥ TP, FF + TOPP, Logic Clk 1 TClk

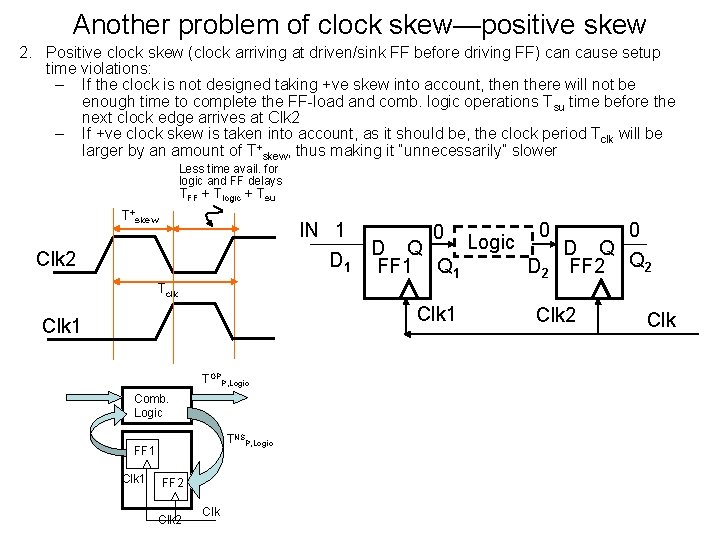

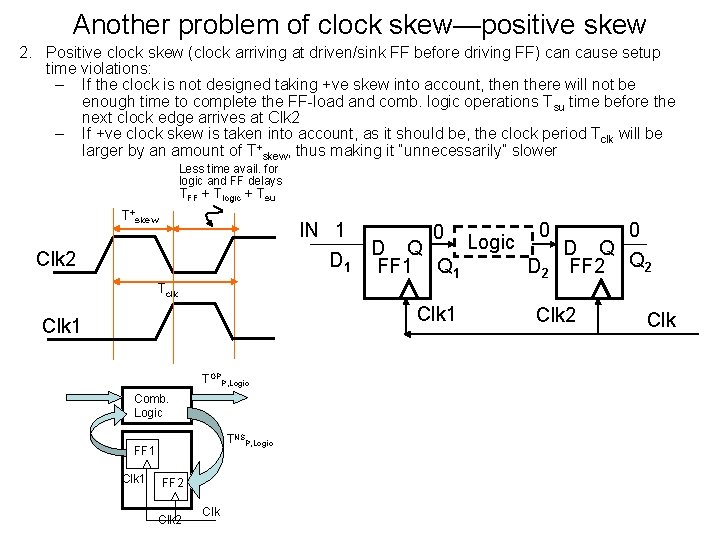

Another problem of clock skew—positive skew 2. Positive clock skew (clock arriving at driven/sink FF before driving FF) can cause setup time violations: – If the clock is not designed taking +ve skew into account, then there will not be enough time to complete the FF-load and comb. logic operations Tsu time before the next clock edge arrives at Clk 2 – If +ve clock skew is taken into account, as it should be, the clock period Tclk will be larger by an amount of T+skew, thus making it “unnecessarily” slower Less time avail. for logic and FF delays TFF + Tlogic + Tsu T+skew IN 1 D 1 Clk 2 Tclk 0 D Q FF 1 Q 1 Clk 1 TOPP, Logic Comb. Logic TNSP, Logic FF 1 Clk 1 FF 2 Clk Logic 0 D 2 0 D Q FF 2 Q 2 Clk

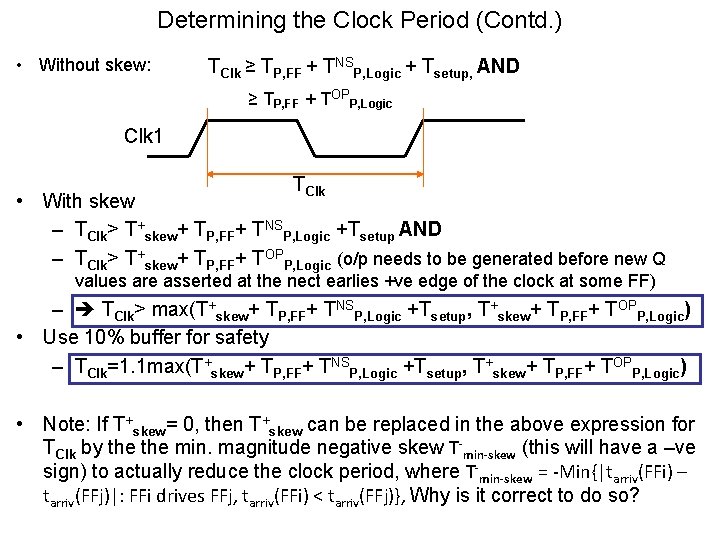

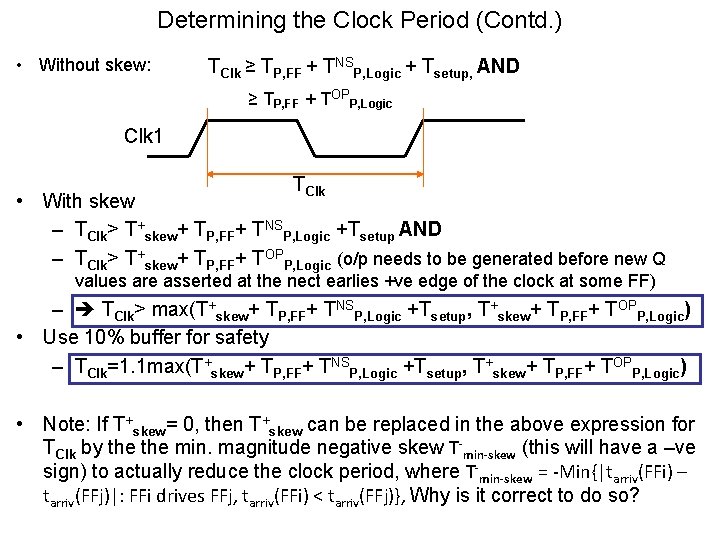

Determining the Clock Period (Contd. ) • Without skew: TClk ≥ TP, FF + TNSP, Logic + Tsetup, AND ≥ TP, FF + TOPP, Logic Clk 1 TClk • With skew – TClk> T+skew+ TP, FF+ TNSP, Logic +Tsetup AND – TClk> T+skew+ TP, FF+ TOPP, Logic (o/p needs to be generated before new Q values are asserted at the nect earlies +ve edge of the clock at some FF) – TClk> max(T+skew+ TP, FF+ TNSP, Logic +Tsetup, T+skew+ TP, FF+ TOPP, Logic) • Use 10% buffer for safety – TClk=1. 1 max(T+skew+ TP, FF+ TNSP, Logic +Tsetup, T+skew+ TP, FF+ TOPP, Logic) • Note: If T+skew= 0, then T+skew can be replaced in the above expression for TClk by the min. magnitude negative skew T-min-skew (this will have a –ve sign) to actually reduce the clock period, where T-min-skew = -Min{|tarriv(FFi) – tarriv(FFj)|: FFi drives FFj, tarriv(FFi) < tarriv(FFj)}, Why is it correct to do so?

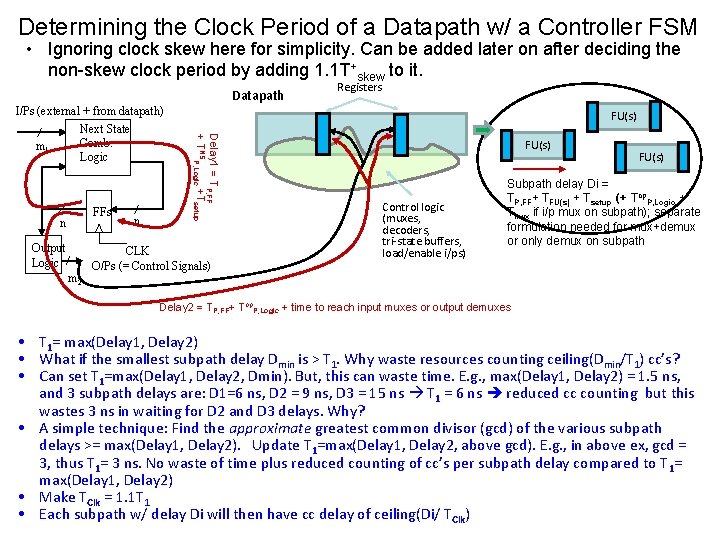

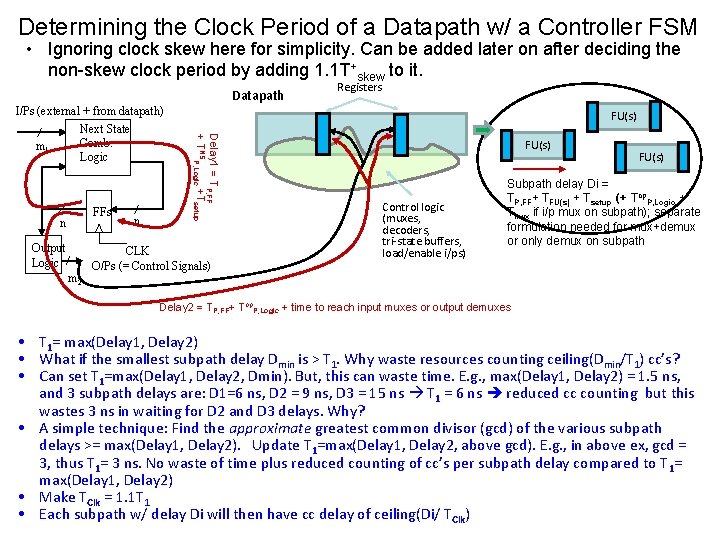

Determining the Clock Period of a Datapath w/ a Controller FSM • Ignoring clock skew here for simplicity. Can be added later on after deciding the non-skew clock period by adding 1. 1 T+skew to it. Datapath FFs n Output Logic m 2 n FU(s) Delay 1 = TP, FF + TNSP, Logic +Tsetup I/Ps (external + from datapath) Next State Comb. m 1 Logic Registers CLK O/Ps (= Control Signals) FU(s) Control logic (muxes, decoders, tri-state buffers, load/enable i/ps) FU(s) Subpath delay Di = TP, FF+ TFU(s) + Tsetup (+ Top. P, Logic + Tmux if i/p mux on subpath); separate formulation needed for mux+demux or only demux on subpath Delay 2 = TP, FF+ Top. P, Logic + time to reach input muxes or output demuxes • T 1= max(Delay 1, Delay 2) • What if the smallest subpath delay Dmin is > T 1. Why waste resources counting ceiling(Dmin/T 1) cc’s? • Can set T 1=max(Delay 1, Delay 2, Dmin). But, this can waste time. E. g. , max(Delay 1, Delay 2) = 1. 5 ns, and 3 subpath delays are: D 1=6 ns, D 2 = 9 ns, D 3 = 15 ns T 1 = 6 ns reduced cc counting but this wastes 3 ns in waiting for D 2 and D 3 delays. Why? • A simple technique: Find the approximate greatest common divisor (gcd) of the various subpath delays >= max(Delay 1, Delay 2). Update T 1=max(Delay 1, Delay 2, above gcd). E. g. , in above ex, gcd = 3, thus T 1= 3 ns. No waste of time plus reduced counting of cc’s per subpath delay compared to T 1= max(Delay 1, Delay 2) • Make TClk = 1. 1 T 1 • Each subpath w/ delay Di will then have cc delay of ceiling(Di/ TClk)

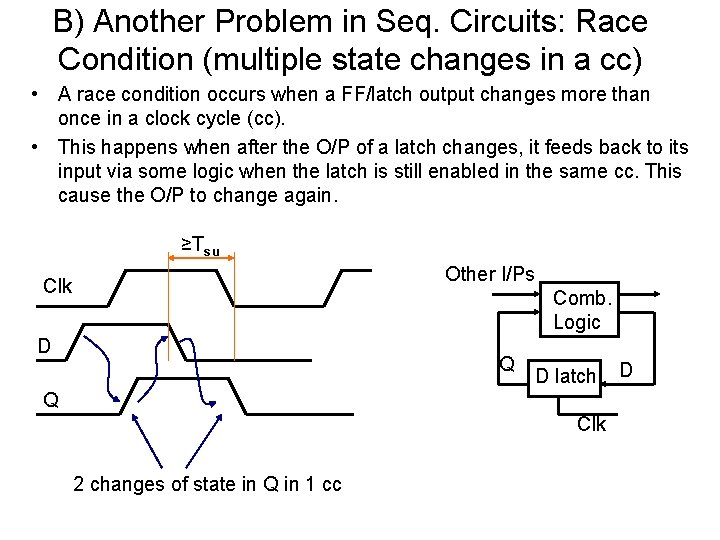

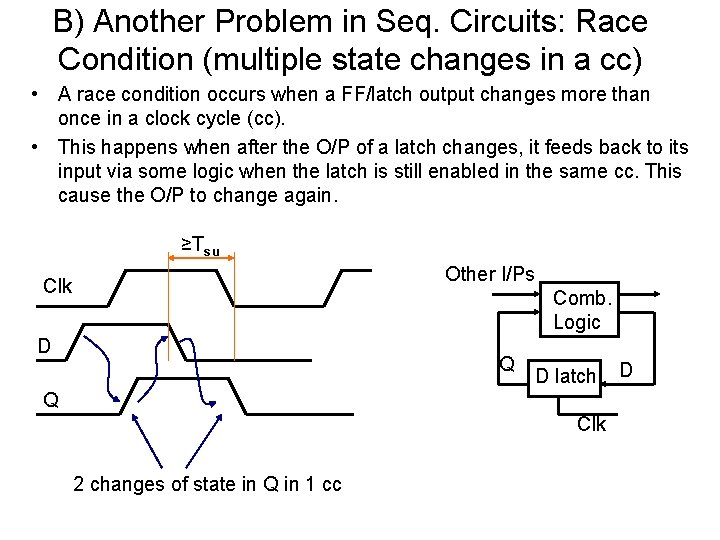

B) Another Problem in Seq. Circuits: Race Condition (multiple state changes in a cc) • A race condition occurs when a FF/latch output changes more than once in a clock cycle (cc). • This happens when after the O/P of a latch changes, it feeds back to its input via some logic when the latch is still enabled in the same cc. This cause the O/P to change again. ≥Tsu Other I/Ps Clk Comb. Logic D Q D latch Q Clk 2 changes of state in Q in 1 cc D

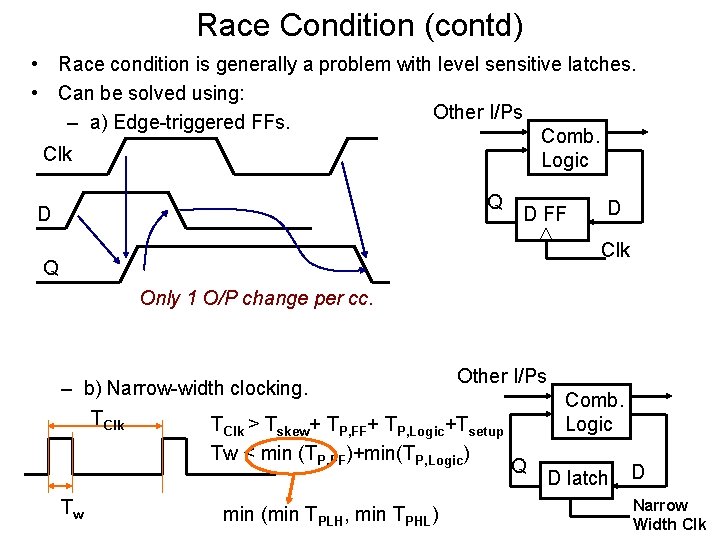

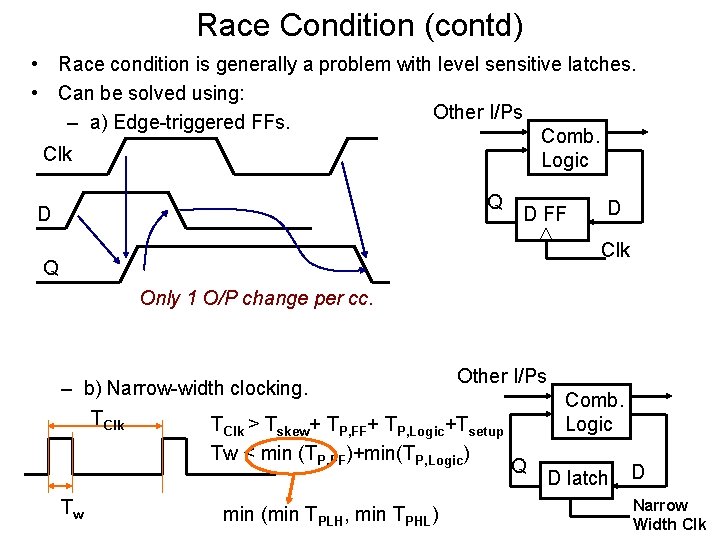

Race Condition (contd) • Race condition is generally a problem with level sensitive latches. • Can be solved using: Other I/Ps – a) Edge-triggered FFs. Comb. Clk Logic Q D D FF D Clk Q Only 1 O/P change per cc. – b) Narrow-width clocking. TClk T >T +T Other I/Ps TP, Logic+Tsetup Tw < min (TP, FF)+min(TP, Logic) Clk Tw skew Comb. Logic P, FF+ min (min TPLH, min TPHL) Q D latch D Narrow Width Clk

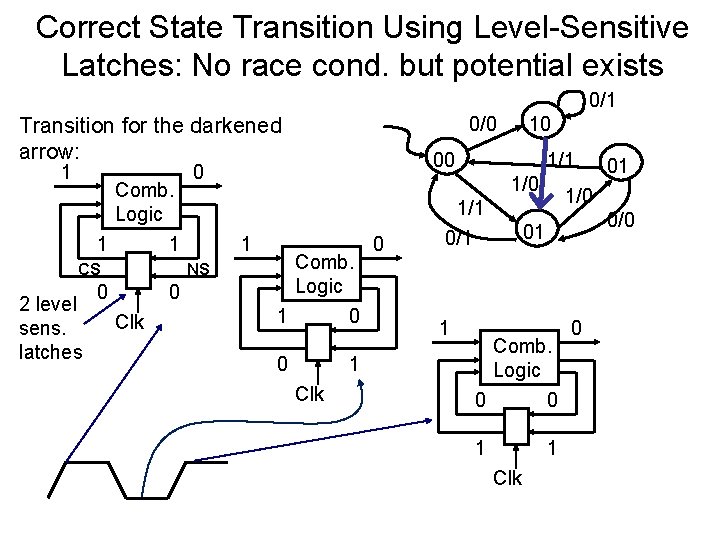

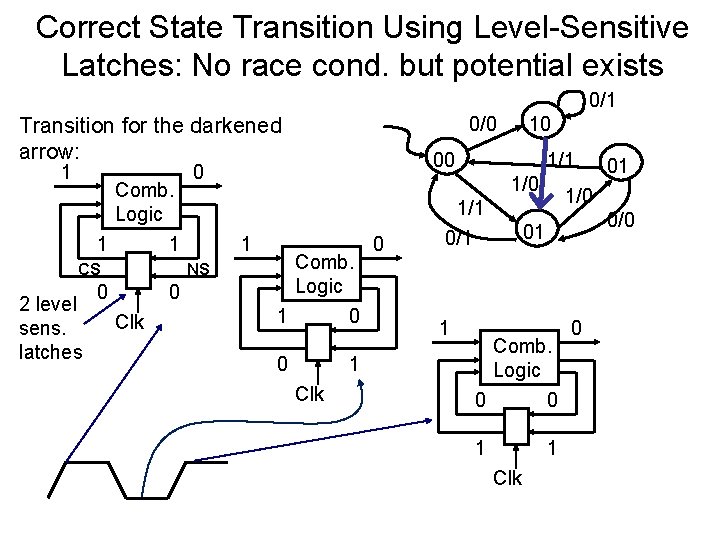

Correct State Transition Using Level-Sensitive Latches: No race cond. but potential exists 0/1 0/0 Transition for the darkened arrow: 1 Comb. Logic 1 CS 2 level sens. latches 0 Clk 1/1 1/0 1 NS 0 00 0 1 10 Comb. Logic 1 0 0 1 Clk 0 1/1 0/1 1 1/0 01 Comb. Logic 0 0 1 1 Clk 01 0

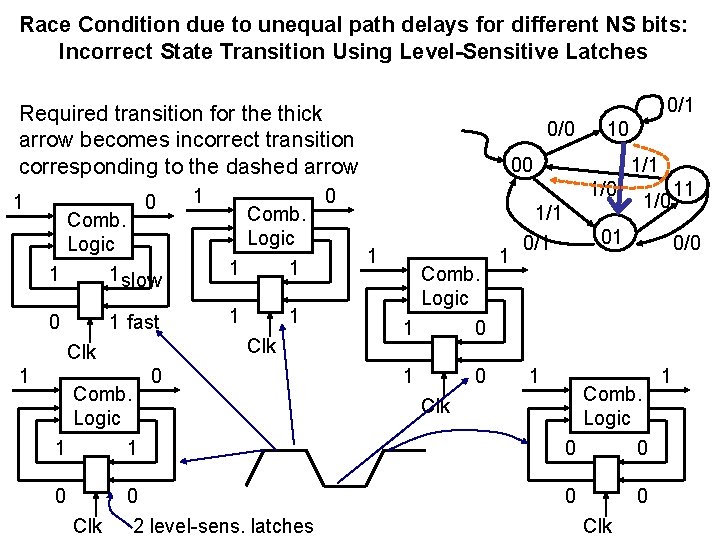

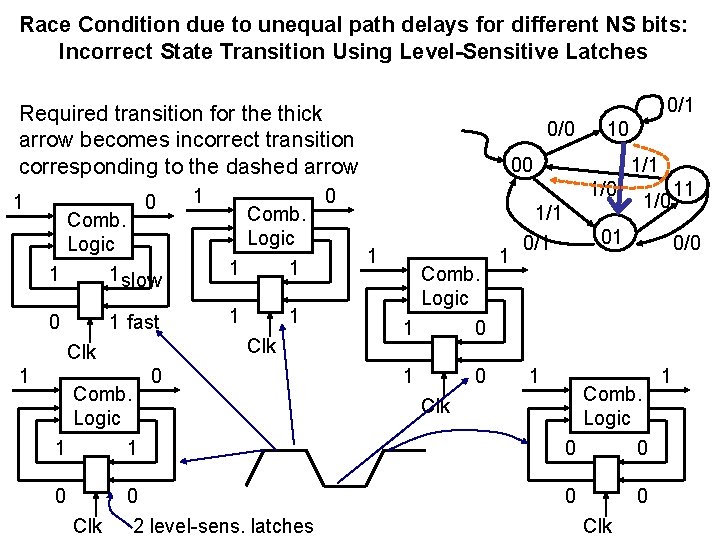

Race Condition due to unequal path delays for different NS bits: Incorrect State Transition Using Level-Sensitive Latches 0/1 Required transition for the thick arrow becomes incorrect transition corresponding to the dashed arrow 1 0 Comb. Logic 1 1 slow Comb. Logic 1 1 0 1 1 fast Comb. Logic 1 1 0 Clk 1 1 0 0 2 level-sens. latches 0/0 10 00 1/1 1/0 0 1 Comb. Logic 1 0 Clk 1 1/1 0/1 1 1/0 01 0/0 Comb. Logic 0 0 Clk 11 1

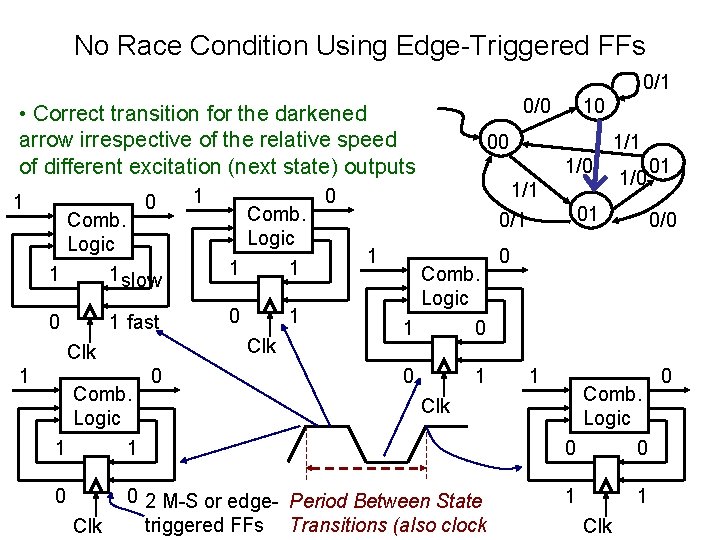

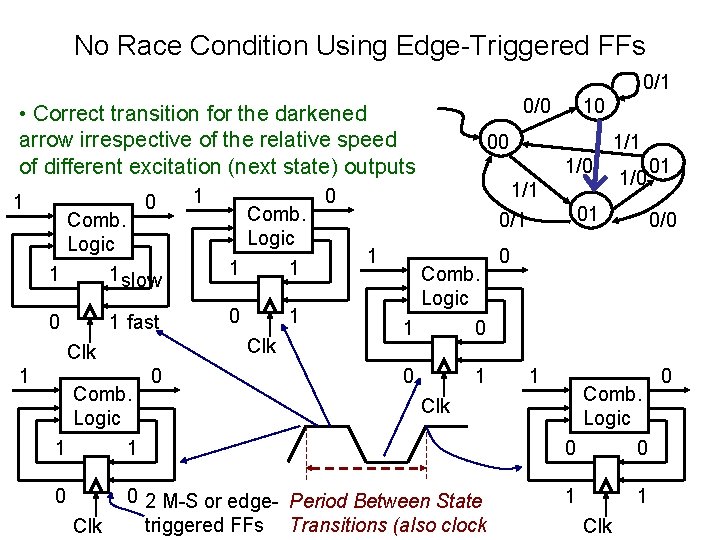

No Race Condition Using Edge-Triggered FFs 0/1 0/0 • Correct transition for the darkened arrow irrespective of the relative speed of different excitation (next state) outputs 1 0 Comb. Logic 1 1 slow Comb. Logic 1 1 0 0 1 fast Comb. Logic 1 1 0 Clk 1 1 0 10 00 1/1 1/0 1/1 0 1 Comb. Logic 1 0 0 1 Clk 0 2 M-S or edge- Period Between State triggered FFs Transitions (also clock 1/0 01 01 0/0 0 1 Comb. Logic 0 0 1 1 Clk 0

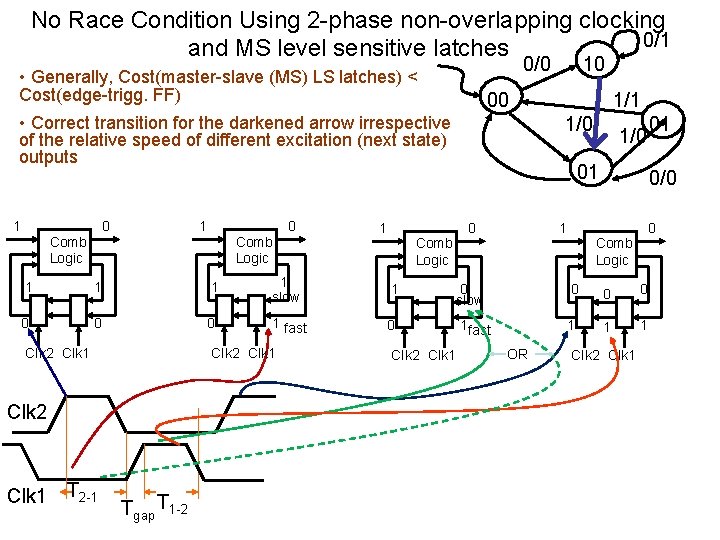

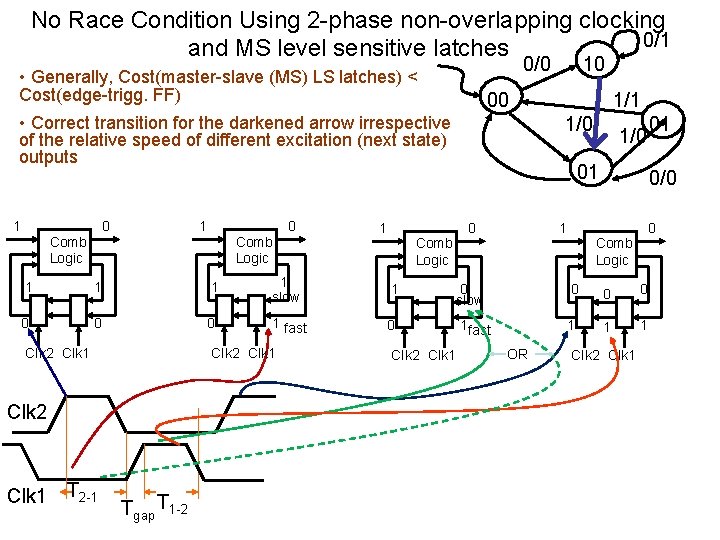

No Race Condition Using 2 -phase non-overlapping clocking 0/1 and MS level sensitive latches 0/0 • Generally, Cost(master-slave (MS) LS latches) < Cost(edge-trigg. FF) 00 • Correct transition for the darkened arrow irrespective of the relative speed of different excitation (next state) outputs 1 1 0 Comb. Logic 0 1 10 1/1 1/0 01 Comb. Logic 0 1 0/0 0 Comb. Logic 1 1 slow 1 0 slow 0 0 0 1 fast 0 1 fast 1 1 1 Clk 2 Clk 1 T 2 -1 Tgap T 1 -2 Clk 1 OR 01 Clk 2 Clk 1

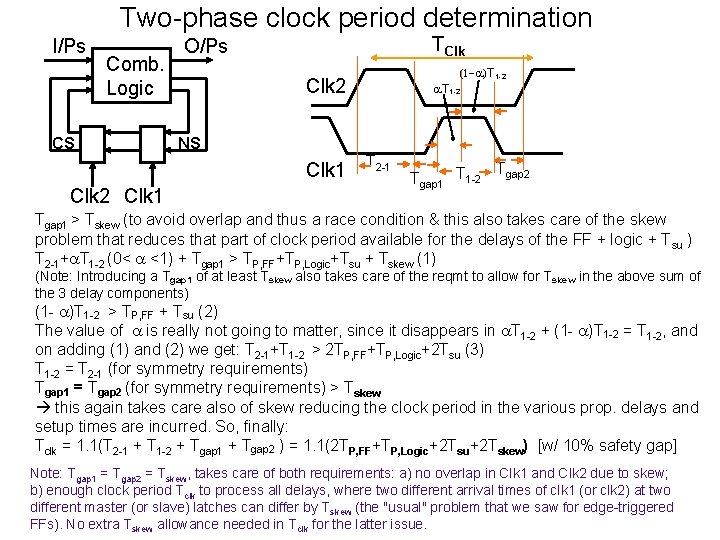

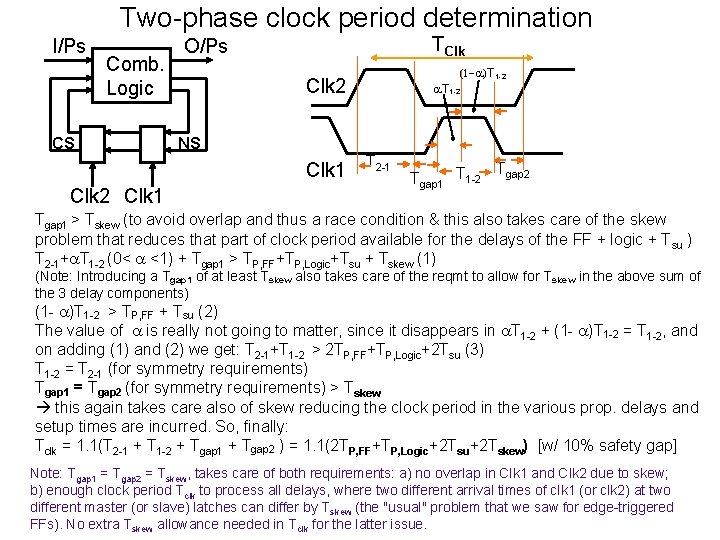

Two-phase clock period determination I/Ps Comb. Logic CS TClk O/Ps Clk 2 a. T 1 -2 NS Clk 1 Clk 2 Clk 1 (1 -a)T 1 -2 T 2 -1 Tgap 2 Tgap 1 T 1 -2 Tgap 1 > Tskew (to avoid overlap and thus a race condition & this also takes care of the skew problem that reduces that part of clock period available for the delays of the FF + logic + T su ) T 2 -1+a. T 1 -2 (0< a <1) + Tgap 1 > TP, FF+TP, Logic+Tsu + Tskew (1) (Note: Introducing a Tgap 1 of at least Tskew also takes care of the reqmt to allow for Tskew in the above sum of the 3 delay components) (1 - a)T 1 -2 > TP, FF + Tsu (2) The value of a is really not going to matter, since it disappears in a. T 1 -2 + (1 - a)T 1 -2 = T 1 -2, and on adding (1) and (2) we get: T 2 -1+T 1 -2 > 2 TP, FF+TP, Logic+2 Tsu (3) T 1 -2 = T 2 -1 (for symmetry requirements) Tgap 1 = Tgap 2 (for symmetry requirements) > Tskew this again takes care also of skew reducing the clock period in the various prop. delays and setup times are incurred. So, finally: Tclk = 1. 1(T 2 -1 + T 1 -2 + Tgap 1 + Tgap 2 ) = 1. 1(2 TP, FF+TP, Logic+2 Tsu+2 Tskew) [w/ 10% safety gap] Note: Tgap 1 = Tgap 2 = Tskew, takes care of both requirements: a) no overlap in Clk 1 and Clk 2 due to skew; b) enough clock period Tclk to process all delays, where two different arrival times of clk 1 (or clk 2) at two different master (or slave) latches can differ by Tskew (the "usual" problem that we saw for edge-triggered FFs). No extra Tskew allowance needed in Tclk for the latter issue.

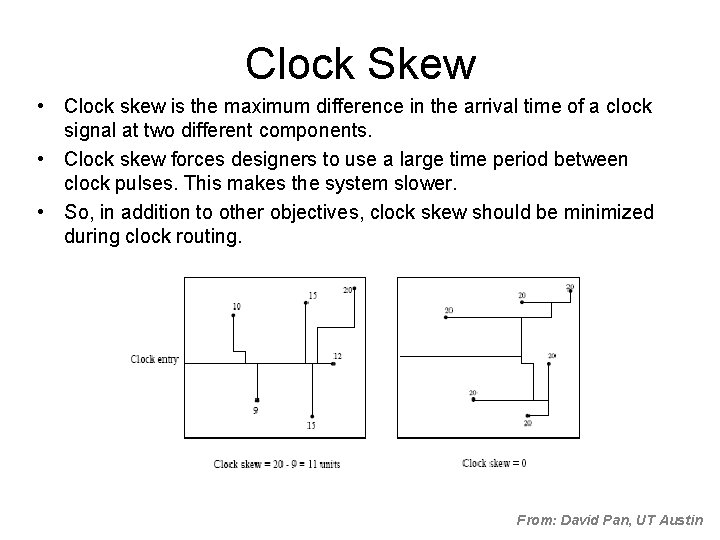

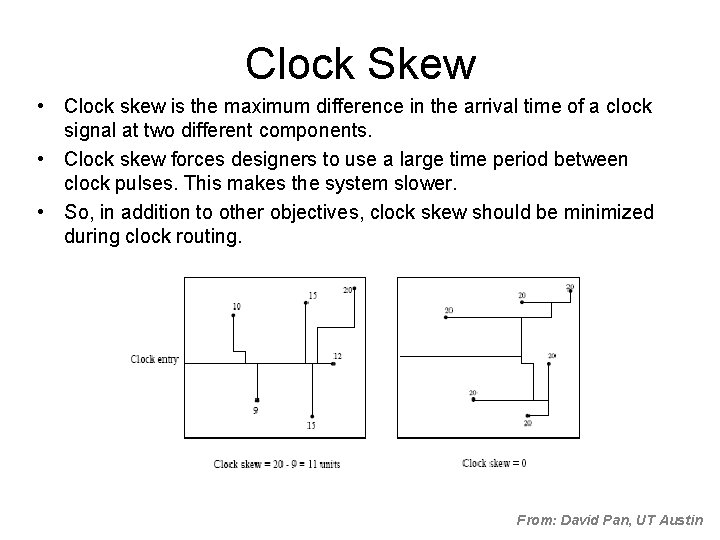

Clock Skew • Clock skew is the maximum difference in the arrival time of a clock signal at two different components. • Clock skew forces designers to use a large time period between clock pulses. This makes the system slower. • So, in addition to other objectives, clock skew should be minimized during clock routing. From: David Pan, UT Austin

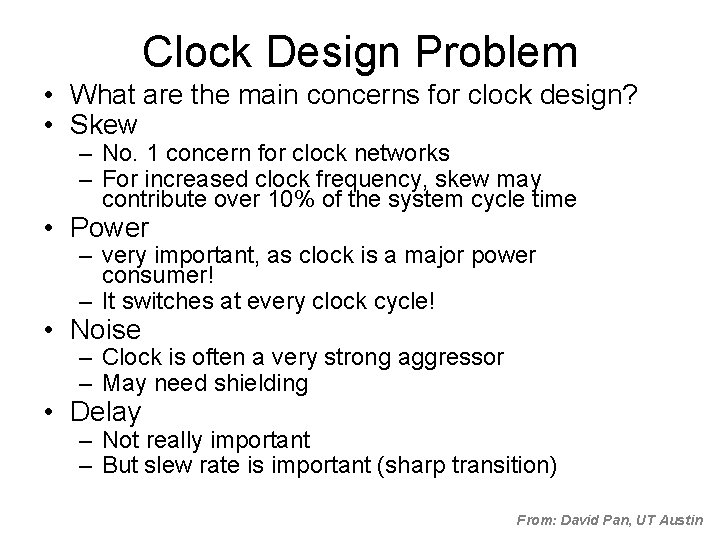

Clock Design Problem • What are the main concerns for clock design? • Skew – No. 1 concern for clock networks – For increased clock frequency, skew may contribute over 10% of the system cycle time • Power – very important, as clock is a major power consumer! – It switches at every clock cycle! • Noise – Clock is often a very strong aggressor – May need shielding • Delay – Not really important – But slew rate is important (sharp transition) From: David Pan, UT Austin

The Clock Routing Problem • Given a source and n sinks (FFs). • Connect all sinks to the source by an interconnect tree so as to minimize: – Clock Skew = maxi, j |ti - tj| – Delay = maxi ti – Total wirelength – Noise and coupling effect From: David Pan, UT Austin

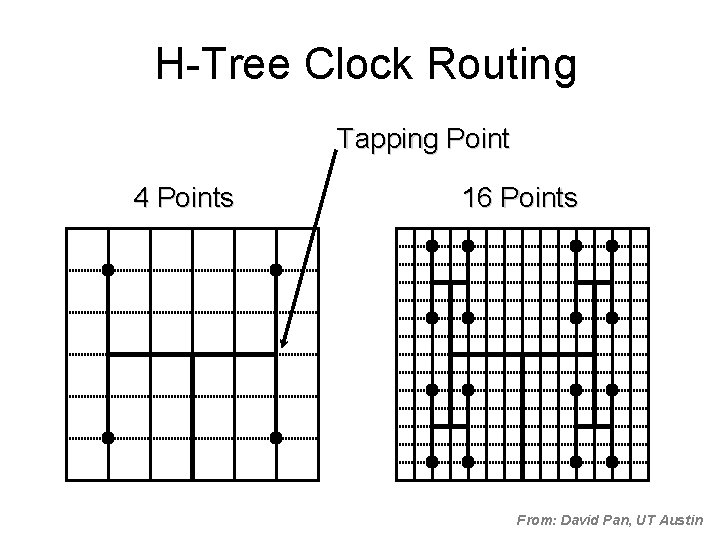

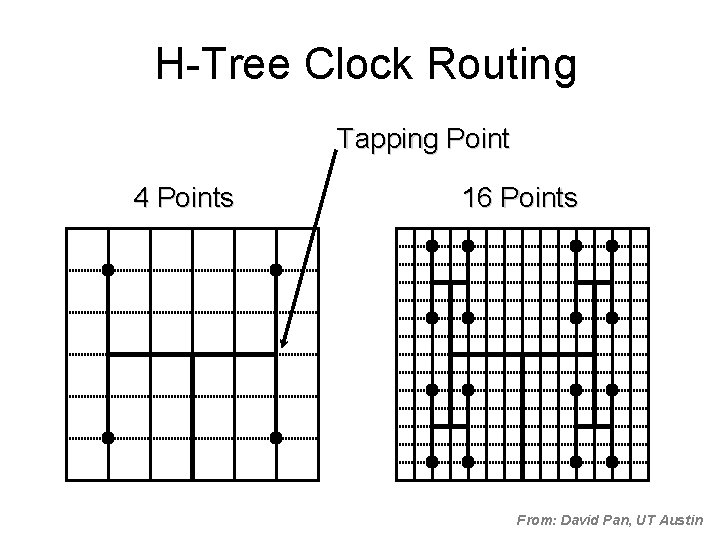

H-Tree Clock Routing Tapping Point 4 Points 16 Points From: David Pan, UT Austin

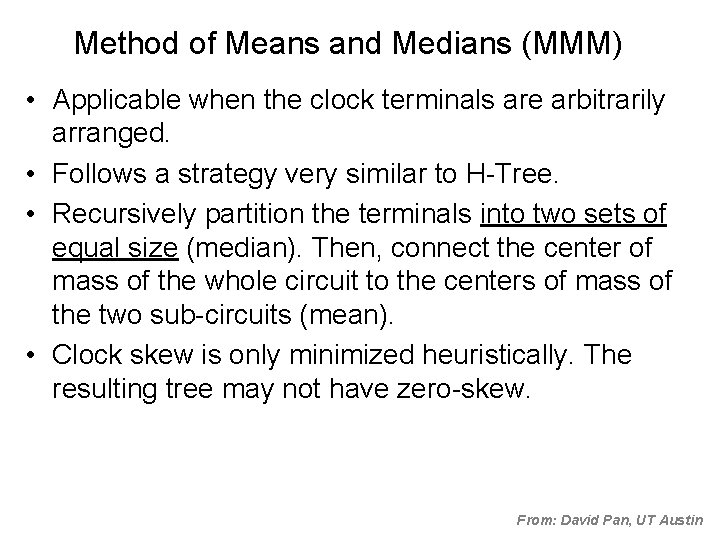

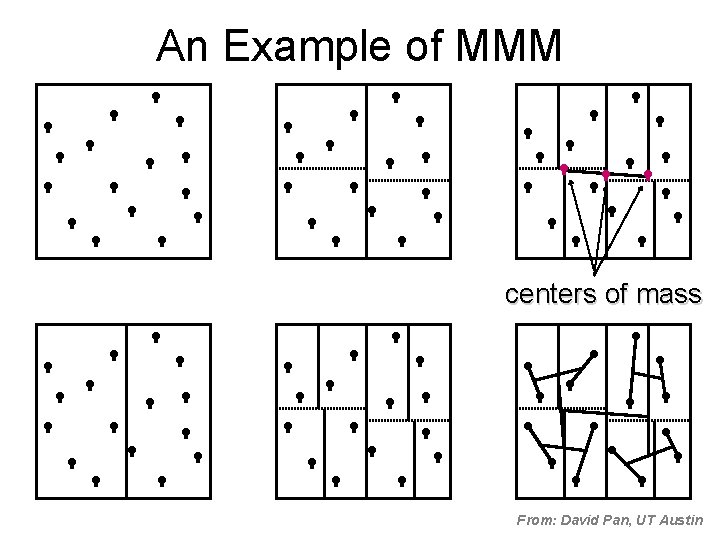

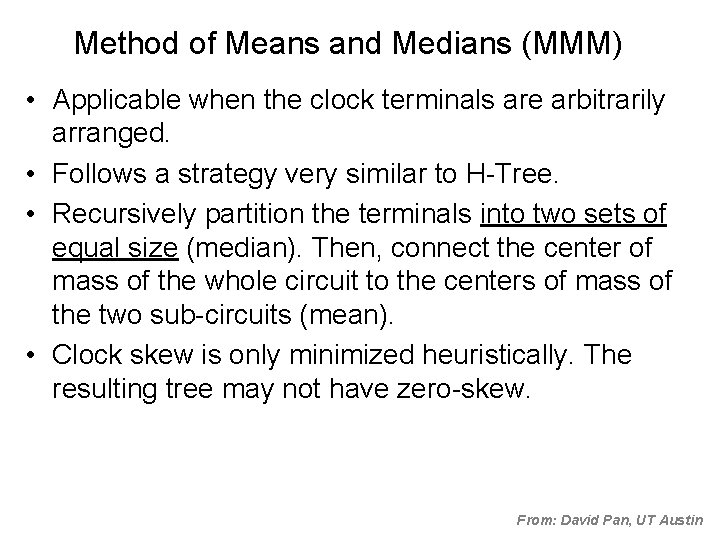

Method of Means and Medians (MMM) • Applicable when the clock terminals are arbitrarily arranged. • Follows a strategy very similar to H-Tree. • Recursively partition the terminals into two sets of equal size (median). Then, connect the center of mass of the whole circuit to the centers of mass of the two sub-circuits (mean). • Clock skew is only minimized heuristically. The resulting tree may not have zero-skew. From: David Pan, UT Austin

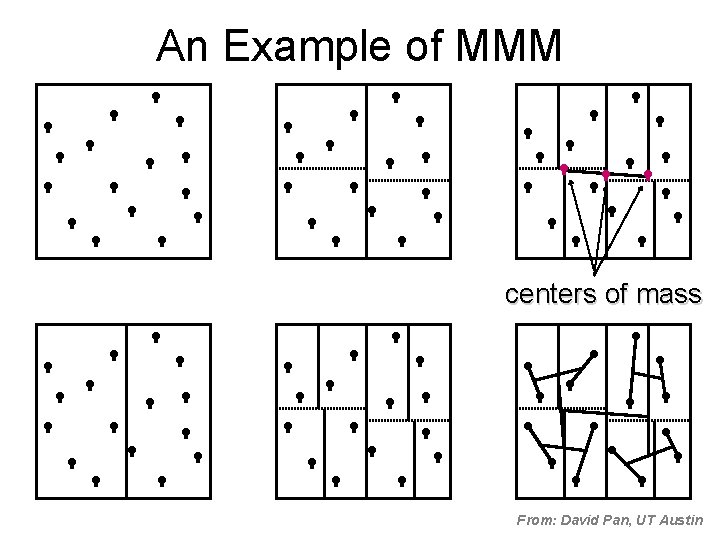

An Example of MMM centers of mass From: David Pan, UT Austin

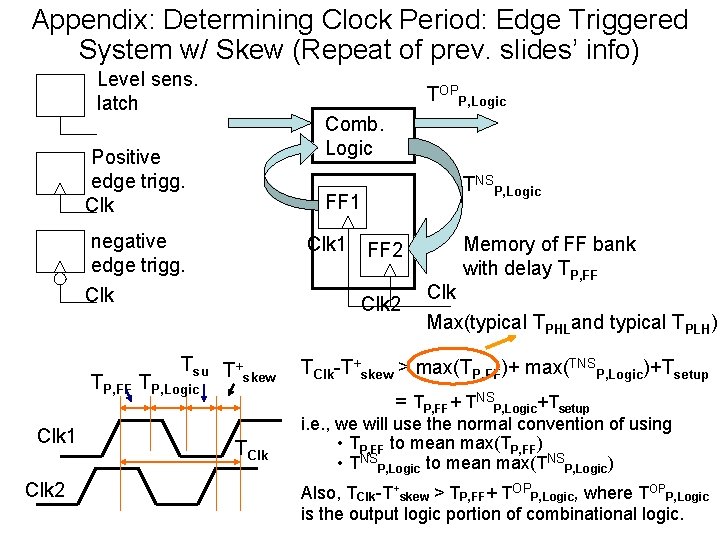

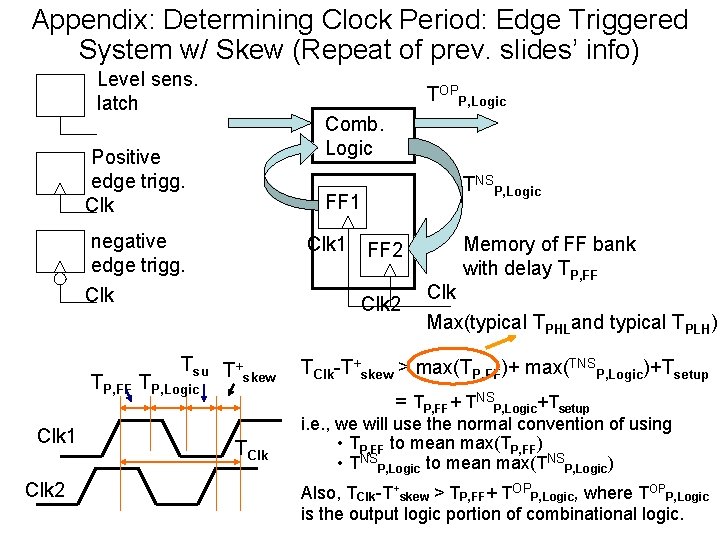

Appendix: Determining Clock Period: Edge Triggered System w/ Skew (Repeat of prev. slides’ info) Level sens. latch TOPP, Logic Comb. Logic Positive edge trigg. Clk FF 1 negative edge trigg. Clk 1 TP, FF TP, Logic Clk 2 FF 2 Clk 2 Tsu T+ skew Clk 1 TNSP, Logic Memory of FF bank with delay TP, FF Clk Max(typical TPHLand typical TPLH) TClk-T+skew > max(TP, FF)+ max(TNSP, Logic)+Tsetup = TP, FF+ TNSP, Logic+Tsetup TClk i. e. , we will use the normal convention of using • TP, FF to mean max(TP, FF) • TNSP, Logic to mean max(TNSP, Logic) Also, TClk-T+skew > TP, FF+ TOPP, Logic, where TOPP, Logic is the output logic portion of combinational logic.