ECE 368 Simple VHDL Synthesis Examples Shantanu Dutt

- Slides: 7

ECE 368 Simple VHDL Synthesis Examples Shantanu Dutt ECE Dept. Univ. of Illinois at Chicago

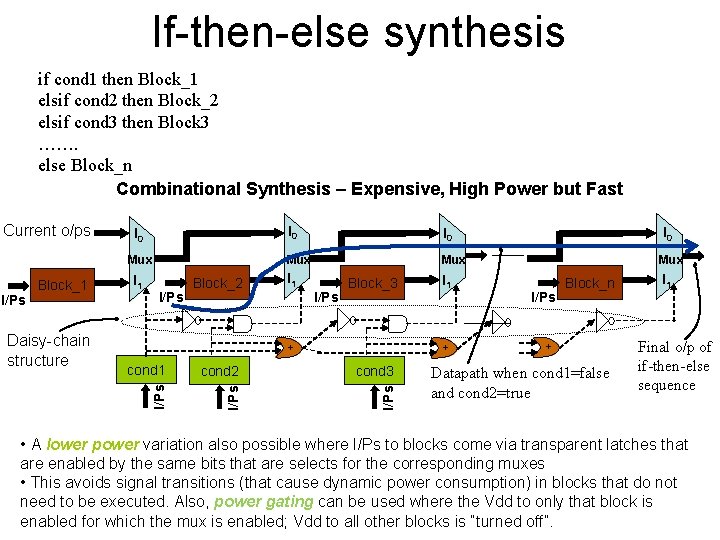

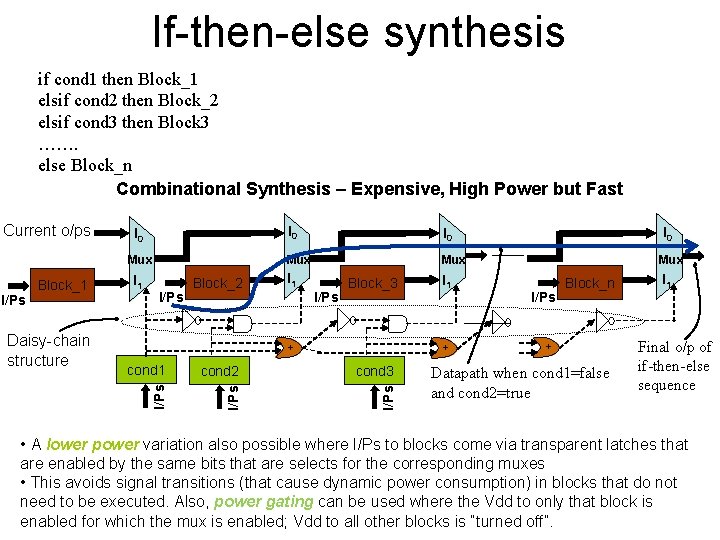

If-then-else synthesis if cond 1 then Block_1 elsif cond 2 then Block_2 elsif cond 3 then Block 3 ……. else Block_n Combinational Synthesis – Expensive, High Power but Fast Current o/ps I 0 Mux I/Ps Block_2 Mux I 1 I/Ps Block_3 + I 1 cond 2 cond 3 I/Ps + I/Ps Daisy-chain structure I 1 I 0 I/Ps Block_1 I 0 Mux I/Ps Block_n + Datapath when cond 1=false and cond 2=true I 1 Final o/p of if-then-else sequence • A lower power variation also possible where I/Ps to blocks come via transparent latches that are enabled by the same bits that are selects for the corresponding muxes • This avoids signal transitions (that cause dynamic power consumption) in blocks that do not need to be executed. Also, power gating can be used where the Vdd to only that block is enabled for which the mux is enabled; Vdd to all other blocks is “turned off”.

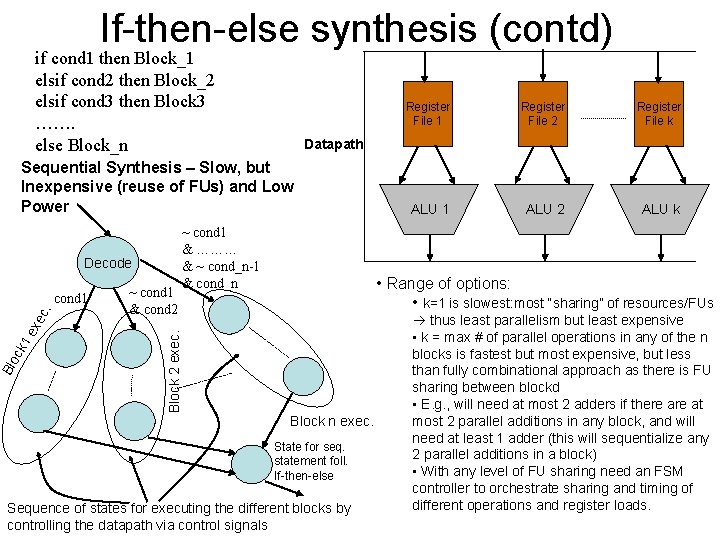

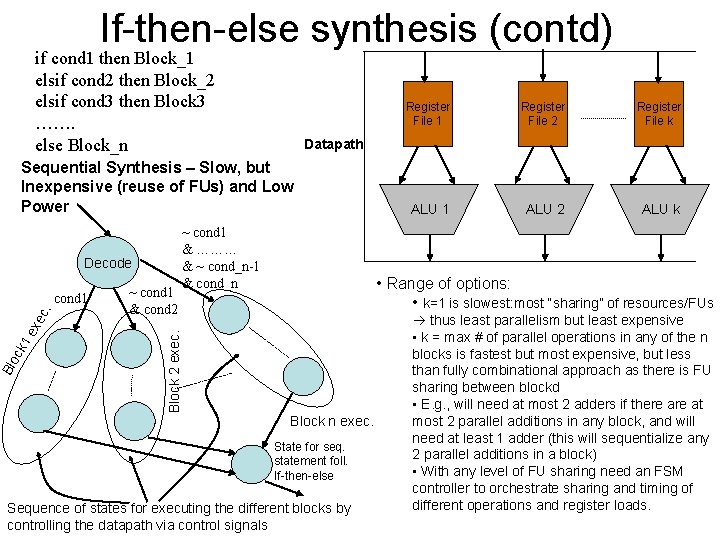

If-then-else synthesis (contd) if cond 1 then Block_1 elsif cond 2 then Block_2 elsif cond 3 then Block 3 ……. else Block_n ~ cond 1 & cond 2 ~ cond 1 & ……… & ~ cond_n-1 & cond_n Register File k ALU 1 ALU 2 ALU k • Range of options: • k=1 is slowest: most “sharing” of resources/FUs Block 2 exec. Blo c k 1 ex ec. cond 1 Register File 2 Datapath Sequential Synthesis – Slow, but Inexpensive (reuse of FUs) and Low Power Decode Register File 1 Block n exec. State for seq. statement foll. If-then-else Sequence of states for executing the different blocks by controlling the datapath via control signals thus least parallelism but least expensive • k = max # of parallel operations in any of the n blocks is fastest but most expensive, but less than fully combinational approach as there is FU sharing between blockd • E. g. , will need at most 2 adders if there at most 2 parallel additions in any block, and will need at least 1 adder (this will sequentialize any 2 parallel additions in a block) • With any level of FU sharing need an FSM controller to orchestrate sharing and timing of different operations and register loads.

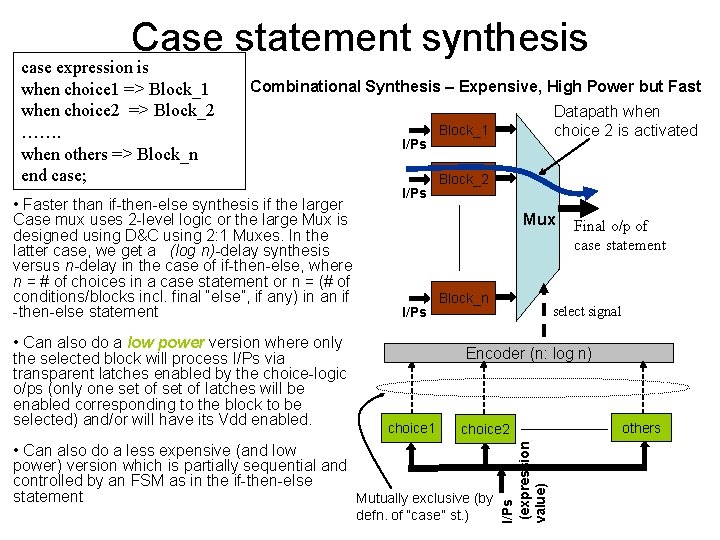

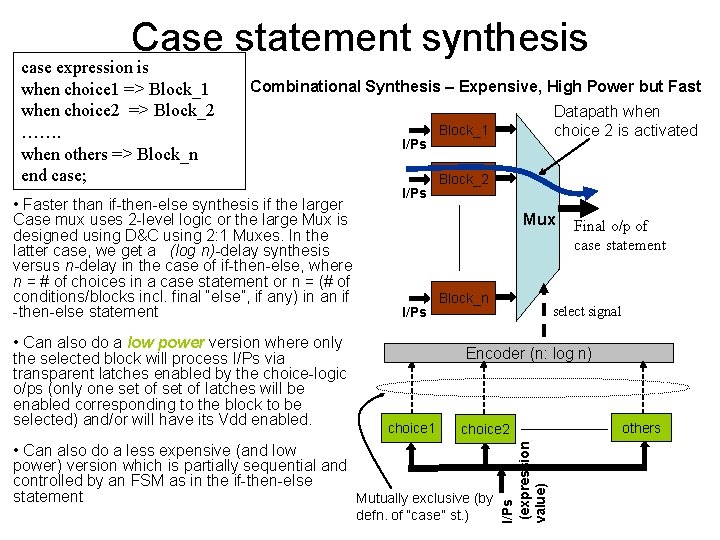

Case statement synthesis Combinational Synthesis – Expensive, High Power but Fast • Faster than if-then-else synthesis if the larger Case mux uses 2 -level logic or the large Mux is designed using D&C using 2: 1 Muxes. In the latter case, we get a (log n)-delay synthesis versus n-delay in the case of if-then-else, where n = # of choices in a case statement or n = (# of conditions/blocks incl. final “else”, if any) in an if -then-else statement • Can also do a low power version where only the selected block will process I/Ps via transparent latches enabled by the choice-logic o/ps (only one set of latches will be enabled corresponding to the block to be selected) and/or will have its Vdd enabled. I/Ps Datapath when choice 2 is activated Block_1 Block_2 Mux I/Ps Block_n Final o/p of case statement select signal Encoder (n: log n) choice 1 choice 2 • Can also do a less expensive (and low power) version which is partially sequential and controlled by an FSM as in the if-then-else statement Mutually exclusive (by defn. of “case” st. ) I/Ps (expression value) case expression is when choice 1 => Block_1 when choice 2 => Block_2 ……. when others => Block_n end case; others

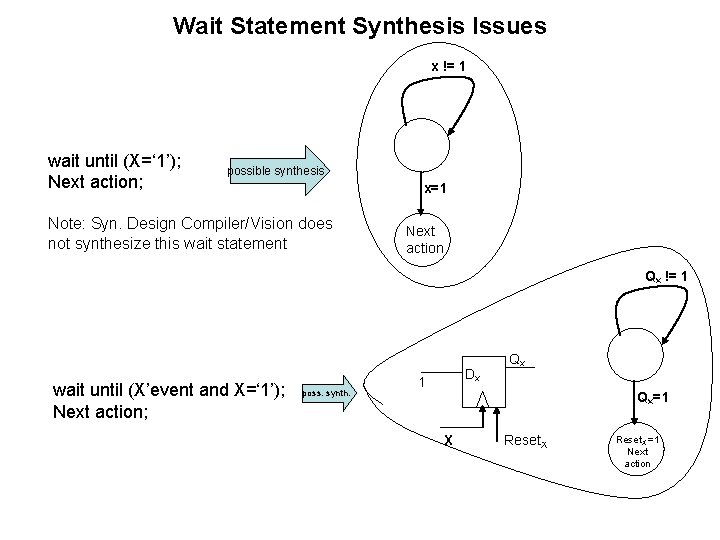

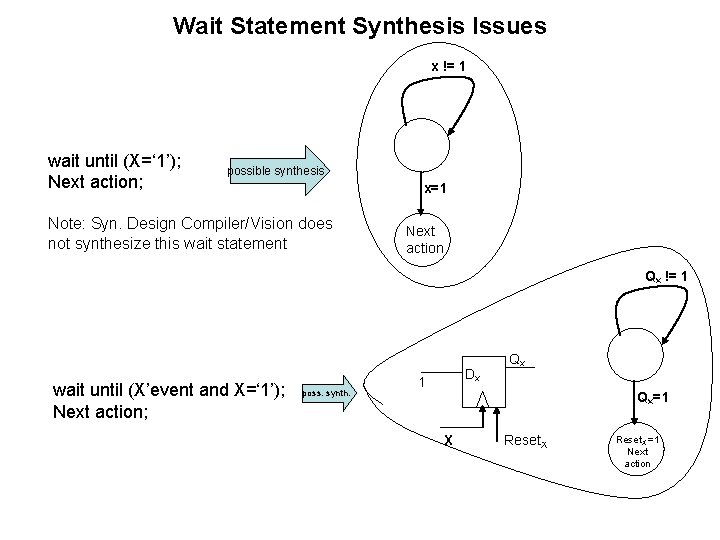

Wait Statement Synthesis Issues x != 1 wait until (X=‘ 1’); Next action; possible synthesis x=1 Note: Syn. Design Compiler/Vision does not synthesize this wait statement Next action Qx != 1 wait until (X’event and X=‘ 1’); Next action; poss. synth. Dx 1 Qx Qx=1 X Reset. X =1 Next action

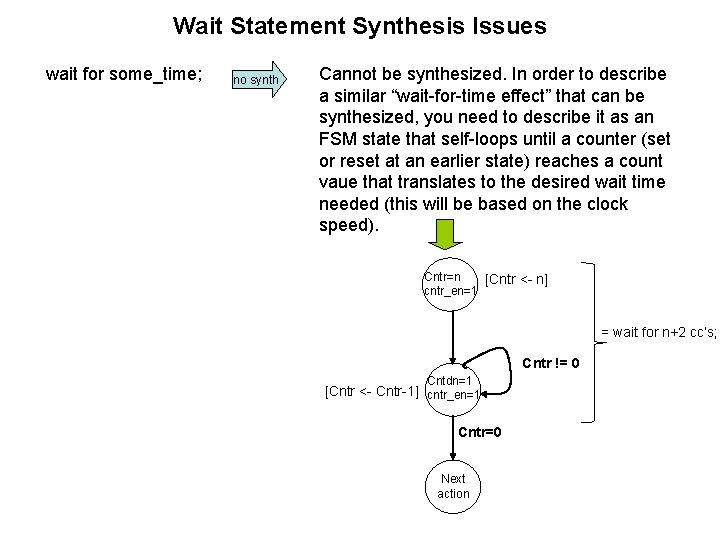

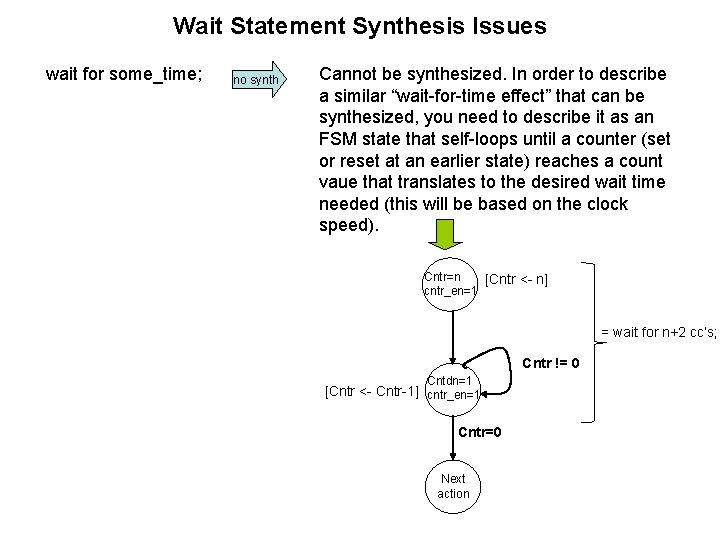

Wait Statement Synthesis Issues wait for some_time; no synth Cannot be synthesized. In order to describe a similar “wait-for-time effect” that can be synthesized, you need to describe it as an FSM state that self-loops until a counter (set or reset at an earlier state) reaches a count vaue that translates to the desired wait time needed (this will be based on the clock speed). Cntr=n [Cntr <- n] cntr_en=1 = wait for n+2 cc’s; Cntr != 0 Cntdn=1 [Cntr <- Cntr-1] cntr_en=1 Cntr=0 Next action

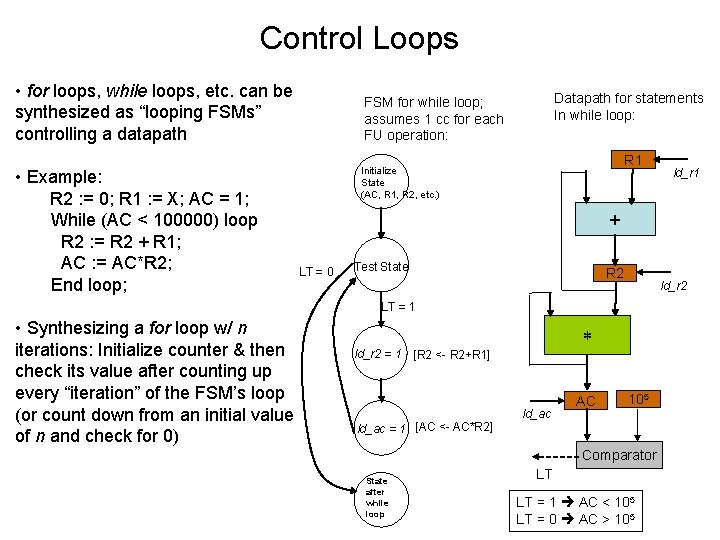

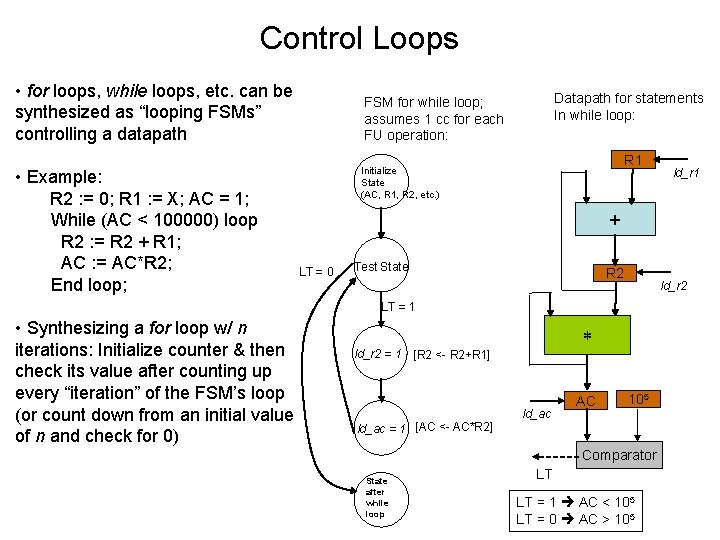

Control Loops • for loops, while loops, etc. can be synthesized as “looping FSMs” controlling a datapath • Example: R 2 : = 0; R 1 : = X; AC = 1; While (AC < 100000) loop R 2 : = R 2 + R 1; AC : = AC*R 2; End loop; Datapath for statements In while loop: FSM for while loop; assumes 1 cc for each FU operation: R 1 Initialize State (AC, R 1, R 2, etc. ) + LT = 0 Test State R 2 ld_r 2 LT = 1 • Synthesizing a for loop w/ n iterations: Initialize counter & then check its value after counting up every “iteration” of the FSM’s loop (or count down from an initial value of n and check for 0) ld_r 1 ld_r 2 = 1 * [R 2 <- R 2+R 1] ld_ac = 1 [AC <- AC*R 2] ld_ac AC 105 Comparator State after while loop LT LT = 1 AC < 105 LT = 0 AC > 105