Digital Logic Design ELCT 201 Spring 2020 Tutorial

- Slides: 47

Digital Logic Design ELCT 201 Spring 2020 Tutorial 10 Design of Finite State Machines (FSMs) Eng. Heba Elhosary 1

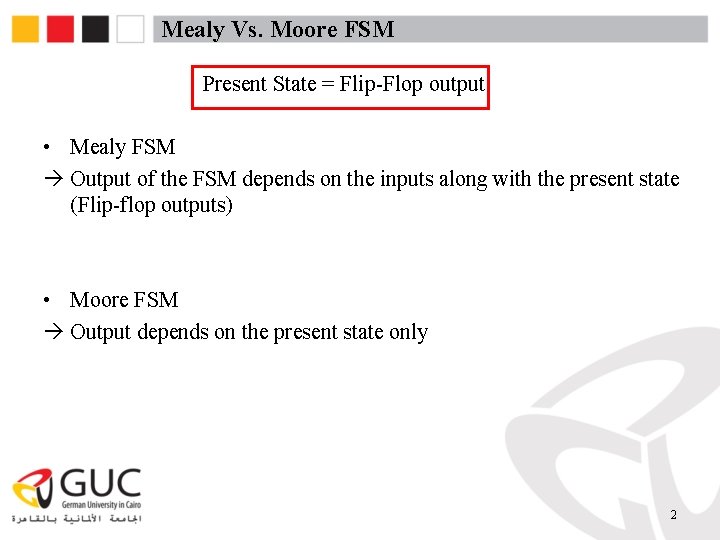

Mealy Vs. Moore FSM Present State = Flip-Flop output • Mealy FSM Output of the FSM depends on the inputs along with the present state (Flip-flop outputs) • Moore FSM Output depends on the present state only 2

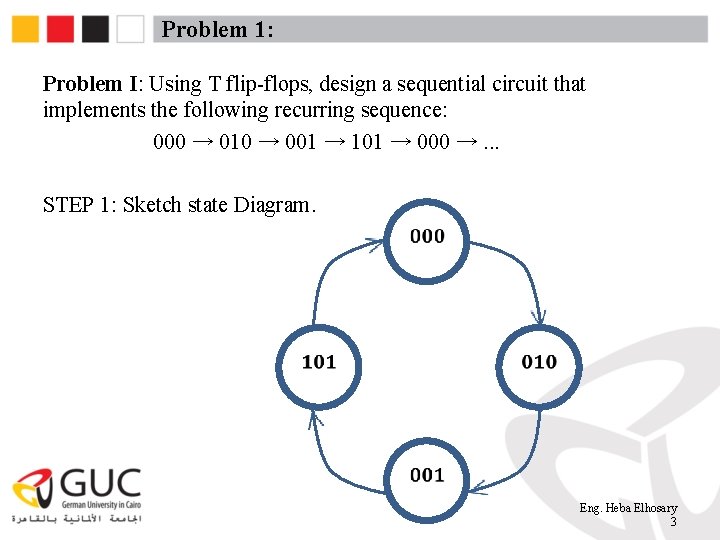

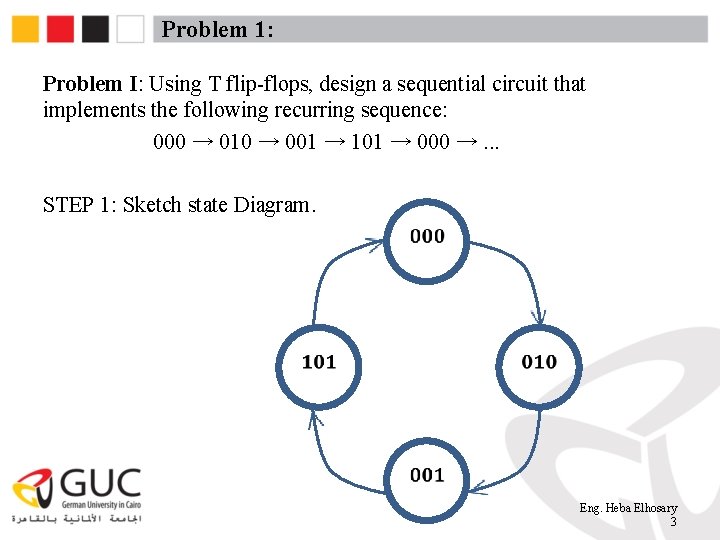

Problem 1: Problem I: Using T flip-flops, design a sequential circuit that implements the following recurring sequence: 000 → 010 → 001 → 101 → 000 →. . . STEP 1: Sketch state Diagram. Eng. Heba Elhosary 3

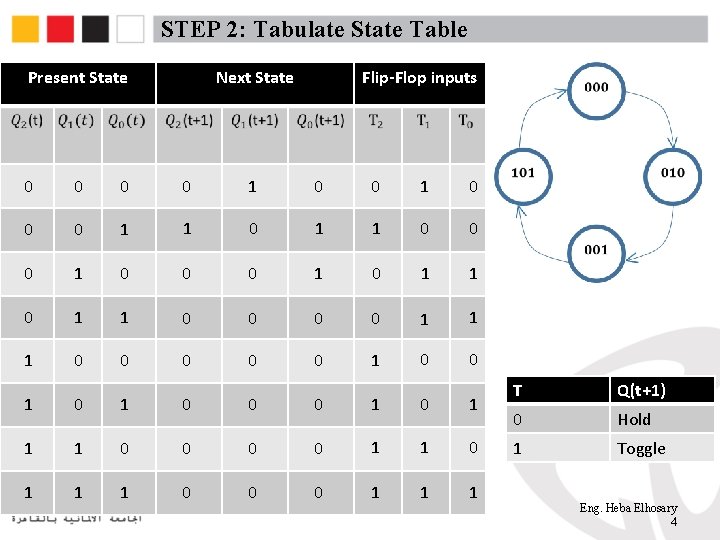

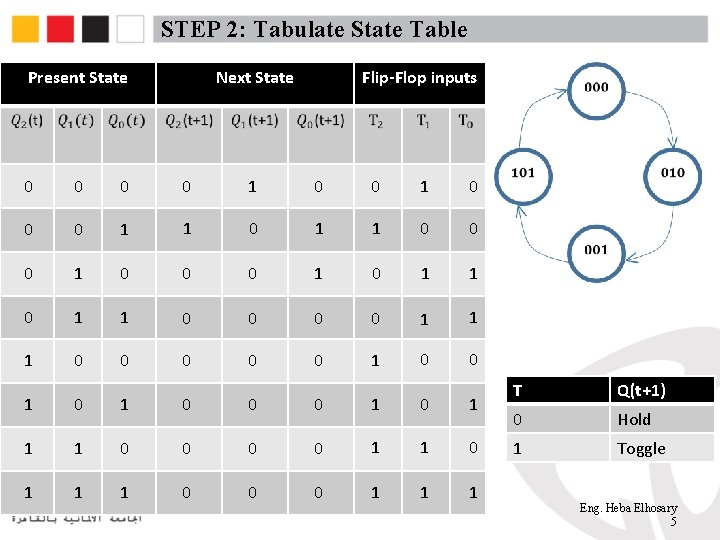

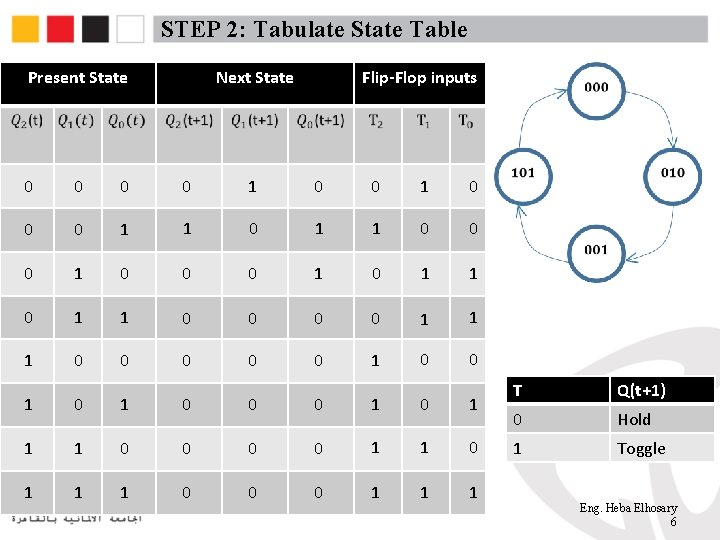

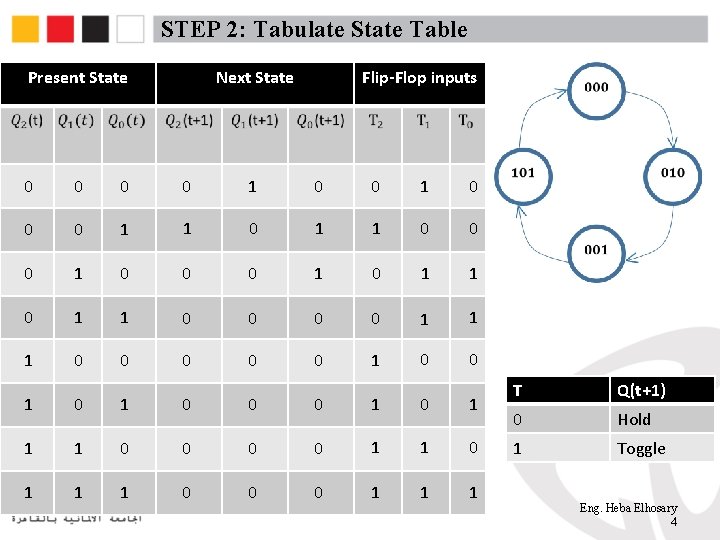

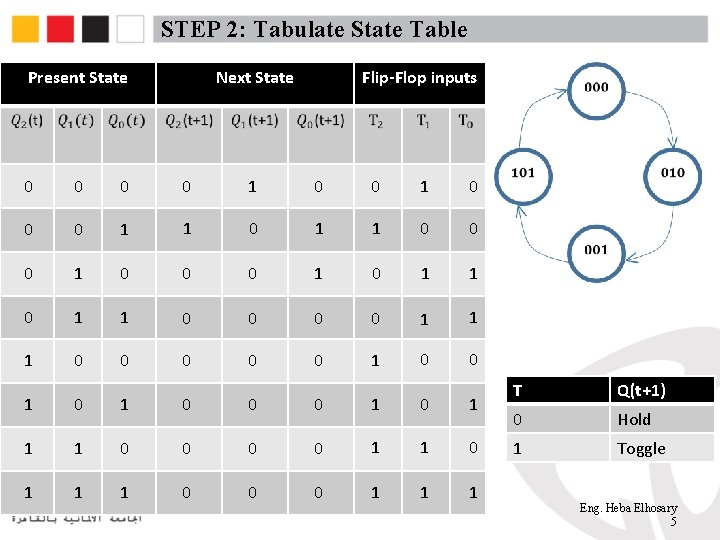

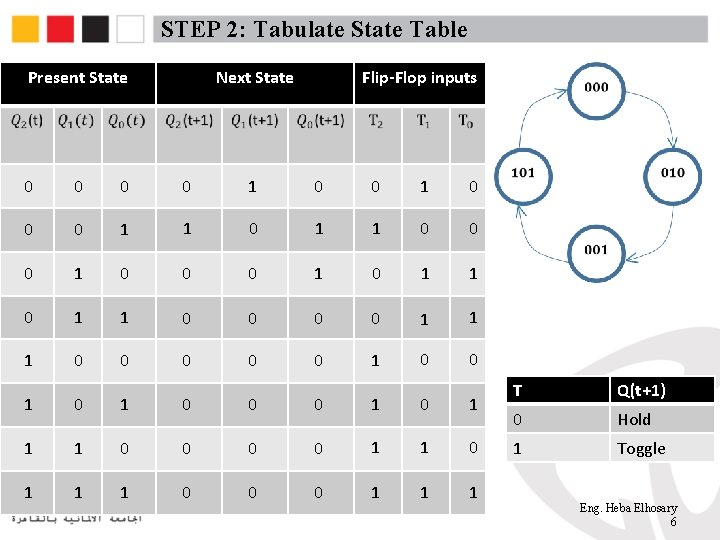

STEP 2: Tabulate State Table Present State Next State Flip-Flop inputs 0 0 1 0 0 0 1 0 1 1 0 0 1 1 1 0 0 0 1 0 1 0 0 0 1 1 1 0 0 1 1 1 0 0 0 1 1 1 T Q(t+1) 0 Hold 1 Toggle Eng. Heba Elhosary 4

STEP 2: Tabulate State Table Present State Next State Flip-Flop inputs 0 0 1 0 0 0 1 0 1 1 0 0 1 1 1 0 0 0 1 0 1 0 0 0 1 1 1 0 0 1 1 1 0 0 0 1 1 1 T Q(t+1) 0 Hold 1 Toggle Eng. Heba Elhosary 5

STEP 2: Tabulate State Table Present State Next State Flip-Flop inputs 0 0 1 0 0 0 1 0 1 1 0 0 1 1 1 0 0 0 1 0 1 0 0 0 1 1 1 0 0 1 1 1 0 0 0 1 1 1 T Q(t+1) 0 Hold 1 Toggle Eng. Heba Elhosary 6

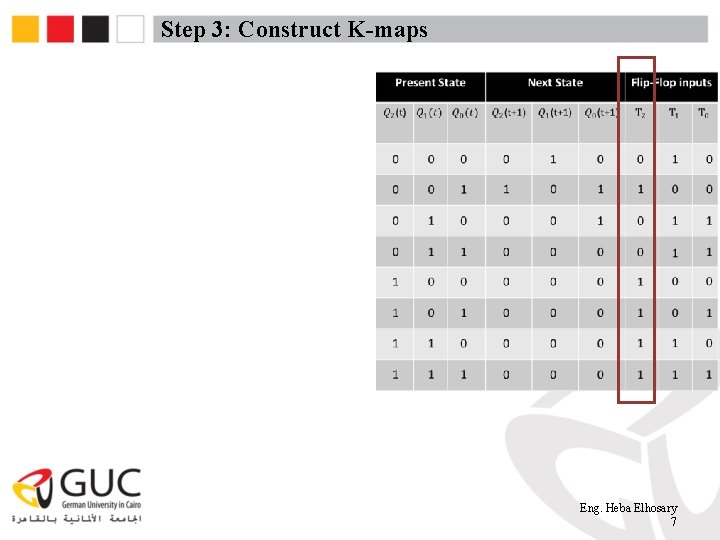

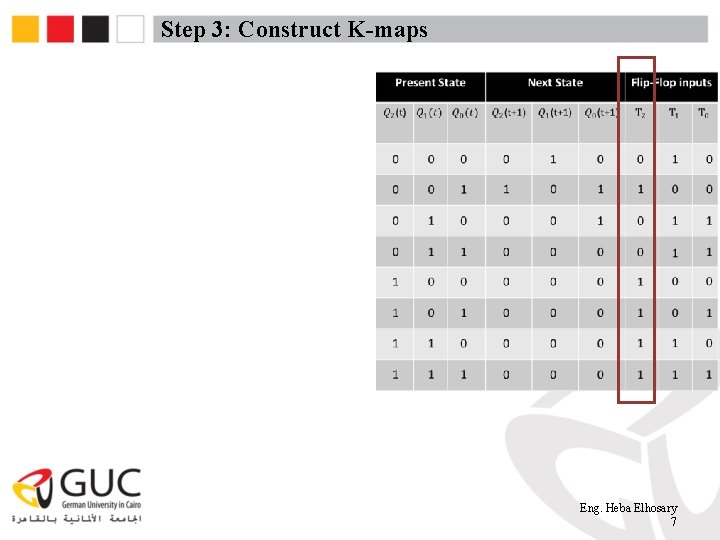

Step 3: Construct K-maps Eng. Heba Elhosary 7

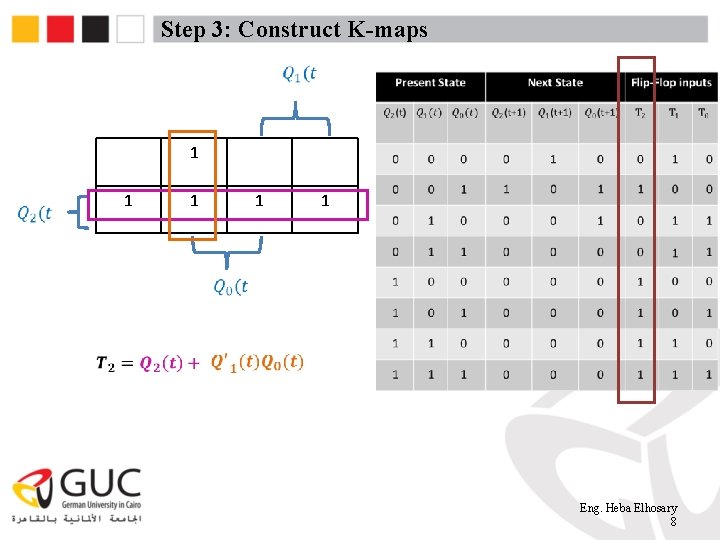

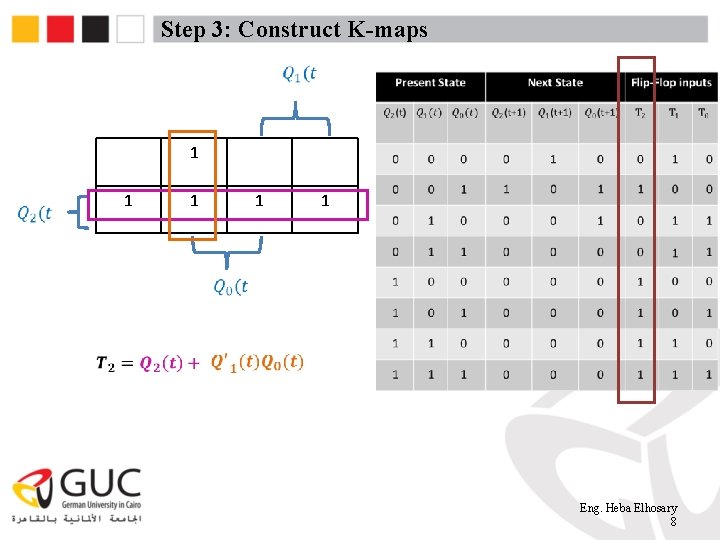

Step 3: Construct K-maps 1 1 1 Eng. Heba Elhosary 8

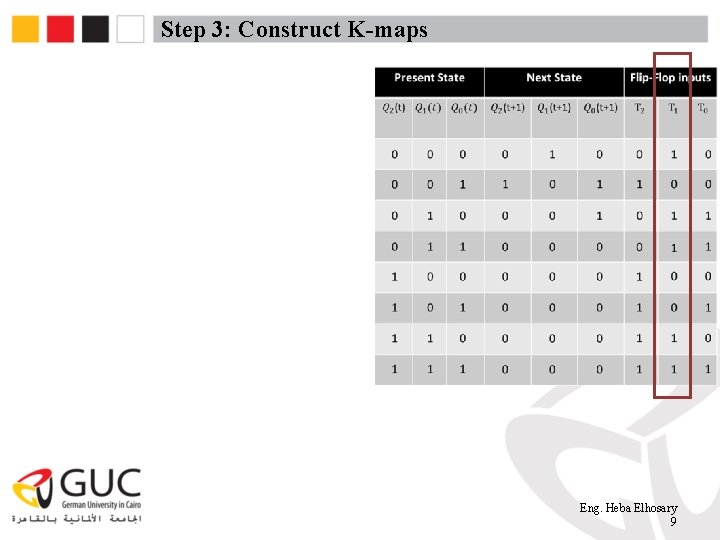

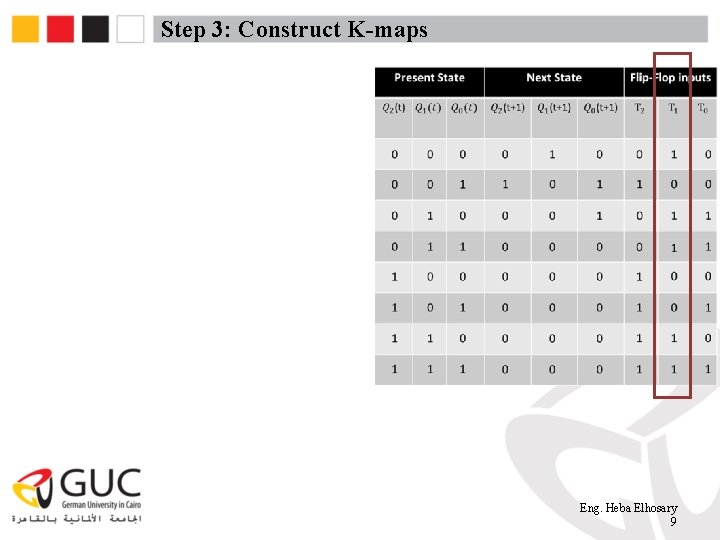

Step 3: Construct K-maps Eng. Heba Elhosary 9

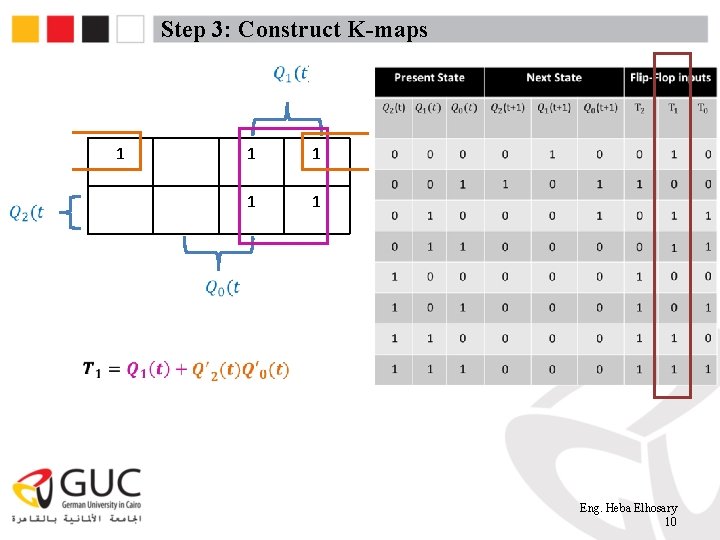

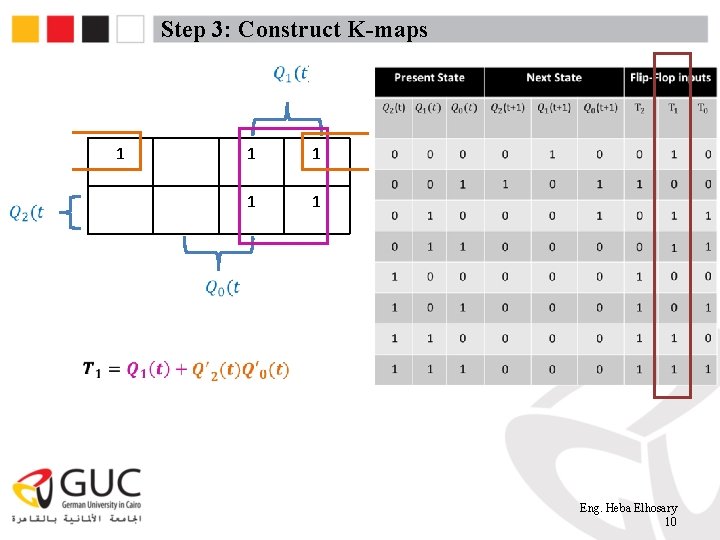

Step 3: Construct K-maps 1 1 1 Eng. Heba Elhosary 10

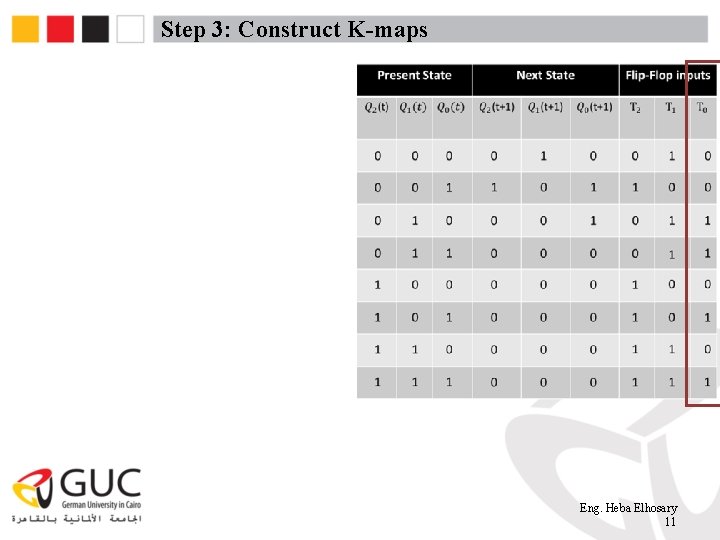

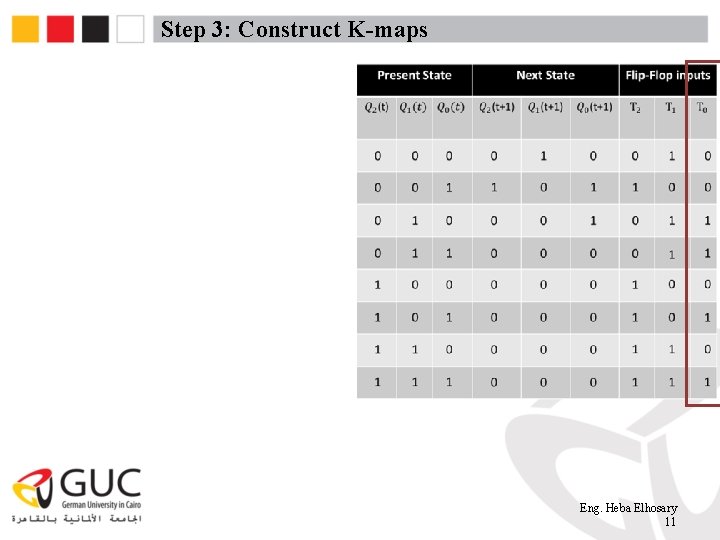

Step 3: Construct K-maps Eng. Heba Elhosary 11

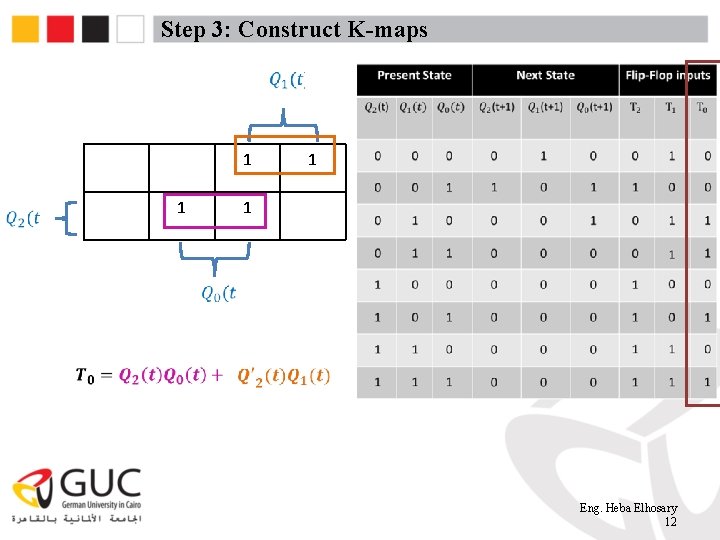

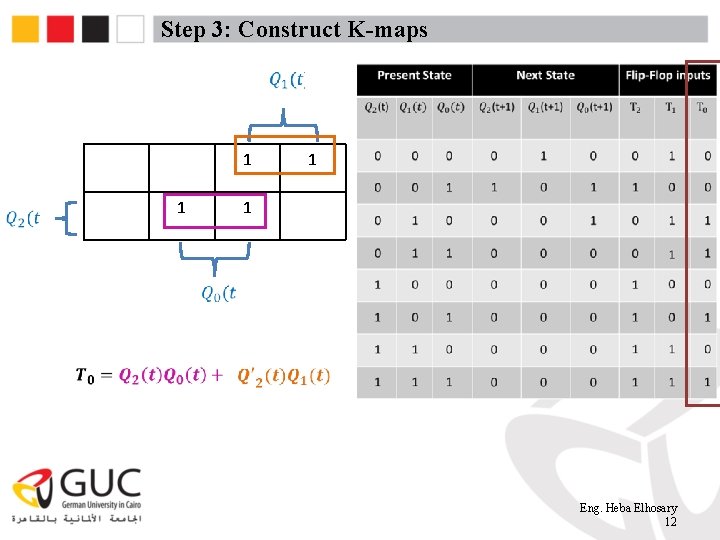

Step 3: Construct K-maps 1 1 Eng. Heba Elhosary 12

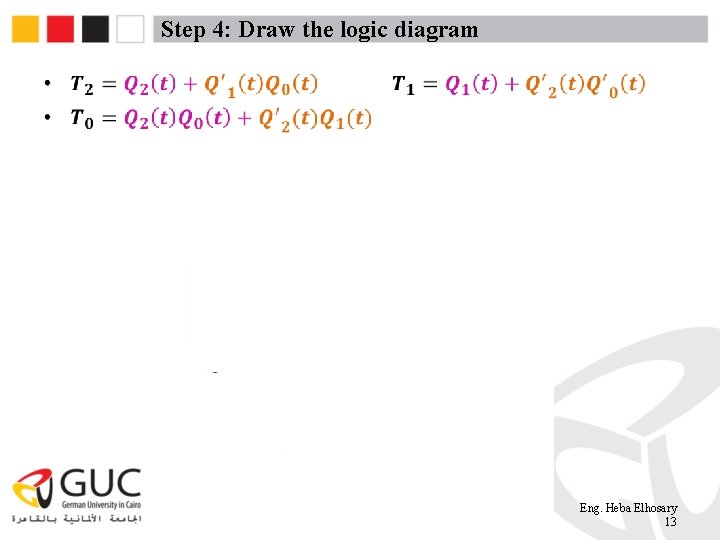

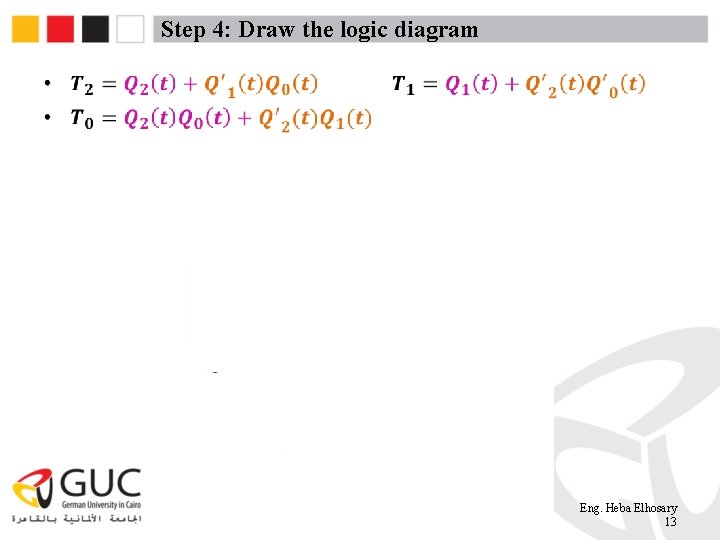

Step 4: Draw the logic diagram • Eng. Heba Elhosary 13

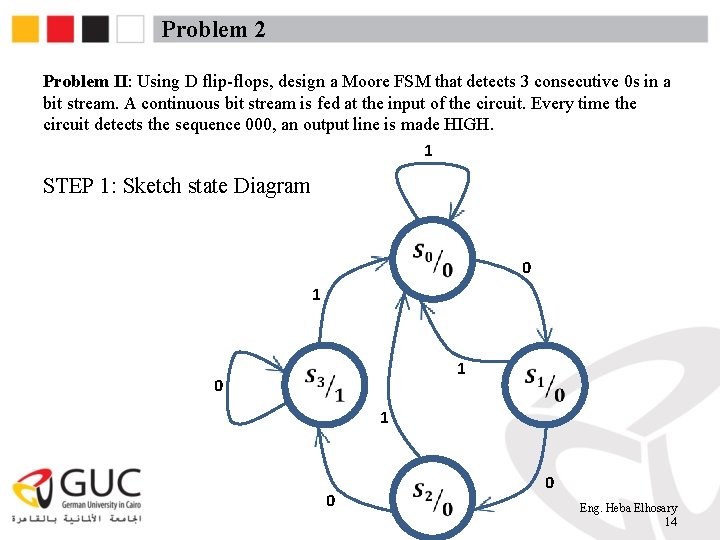

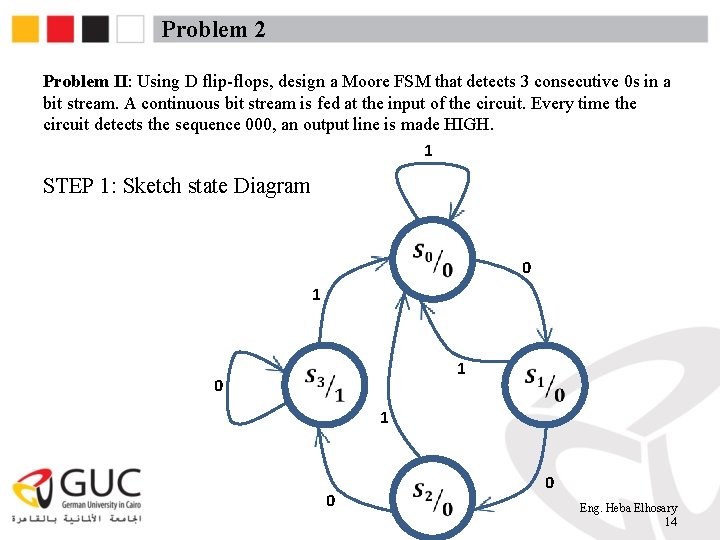

Problem 2 Problem II: Using D flip-flops, design a Moore FSM that detects 3 consecutive 0 s in a bit stream. A continuous bit stream is fed at the input of the circuit. Every time the circuit detects the sequence 000, an output line is made HIGH. 1 STEP 1: Sketch state Diagram 0 1 1 0 0 Eng. Heba Elhosary 14

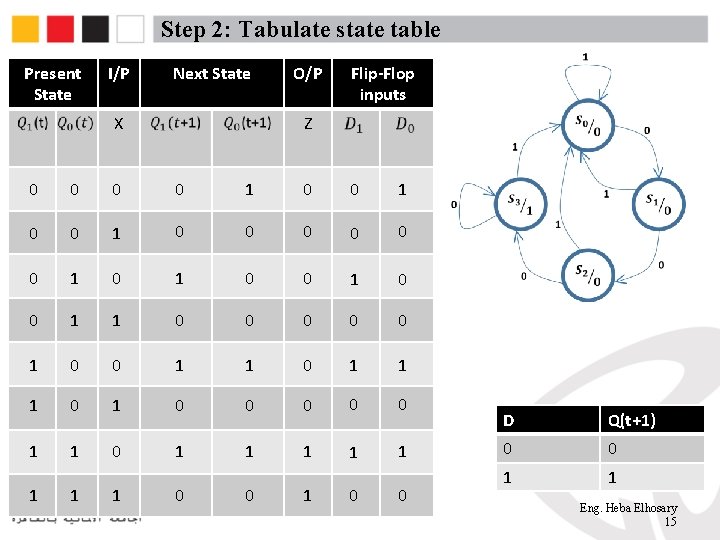

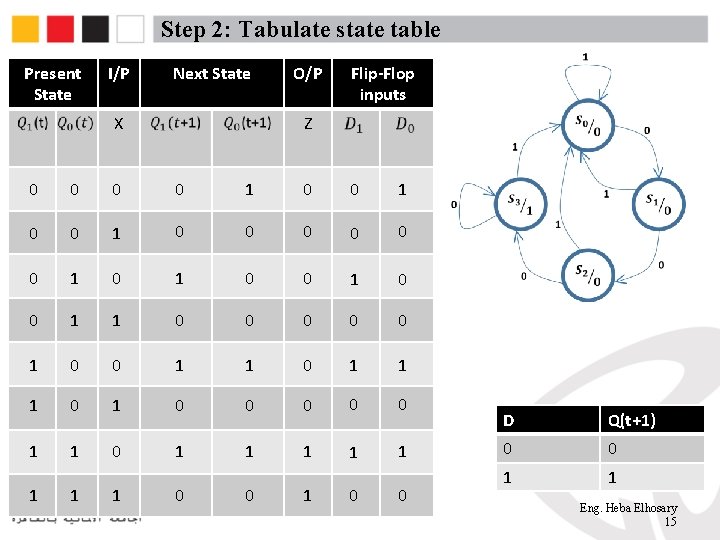

Step 2: Tabulate state table Present State I/P Next State X O/P Flip-Flop inputs Z 0 0 1 0 0 1 0 0 1 1 0 0 0 1 1 1 0 0 0 1 1 1 1 0 0 D Q(t+1) 0 0 1 1 Eng. Heba Elhosary 15

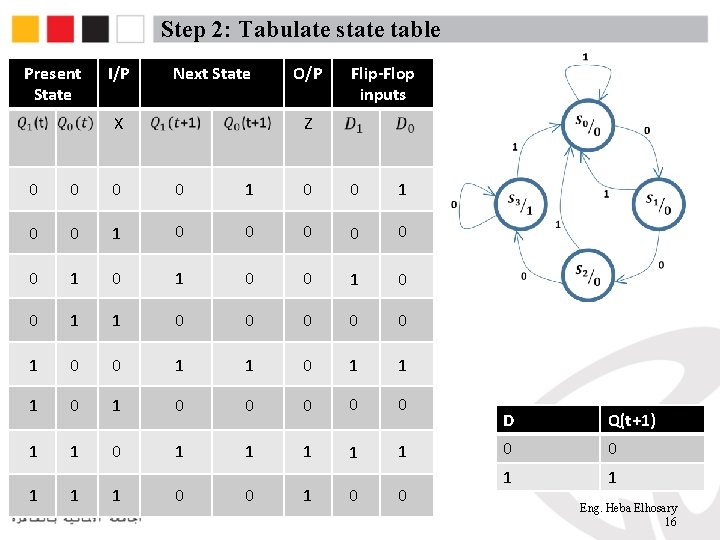

Step 2: Tabulate state table Present State I/P Next State X O/P Flip-Flop inputs Z 0 0 1 0 0 1 0 0 1 1 0 0 0 1 1 1 0 0 0 1 1 1 1 0 0 D Q(t+1) 0 0 1 1 Eng. Heba Elhosary 16

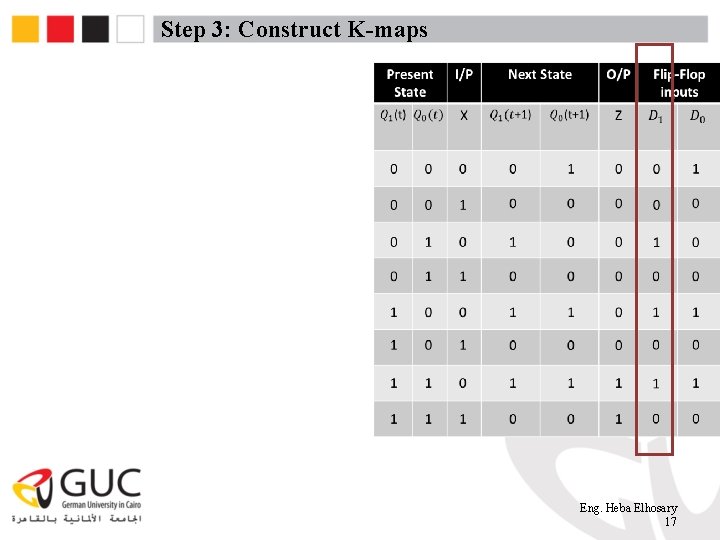

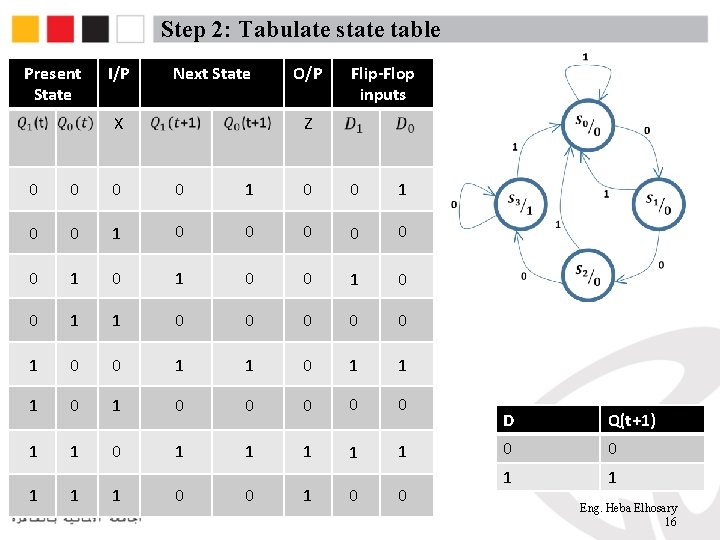

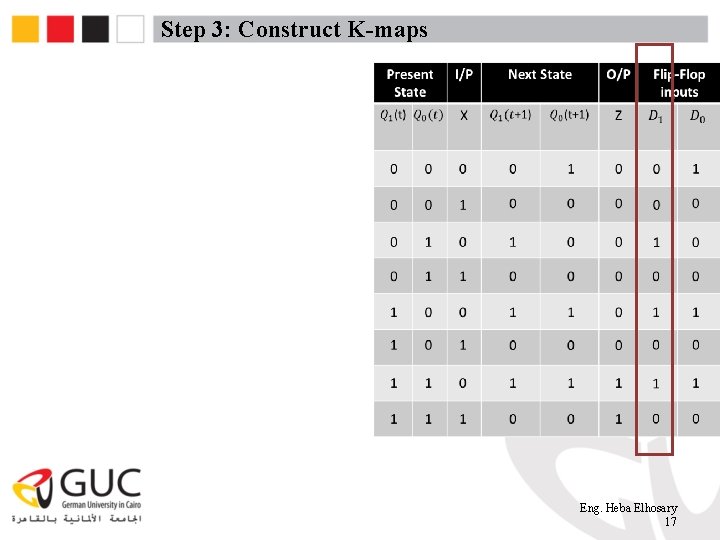

Step 3: Construct K-maps Eng. Heba Elhosary 17

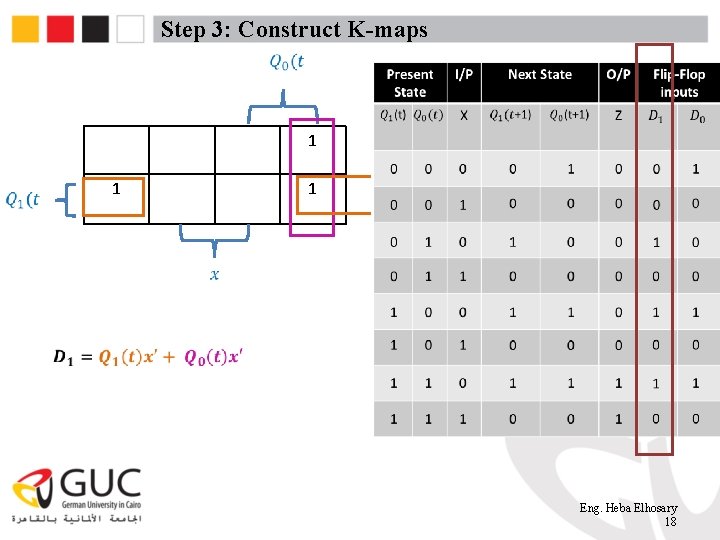

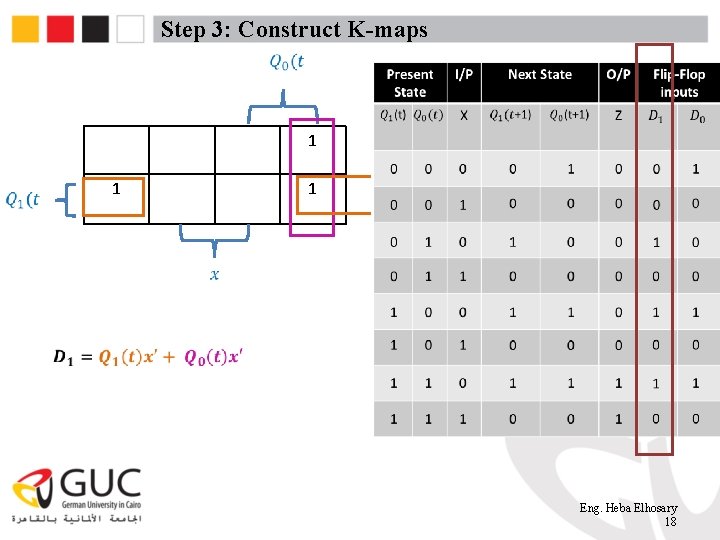

Step 3: Construct K-maps 1 1 1 Eng. Heba Elhosary 18

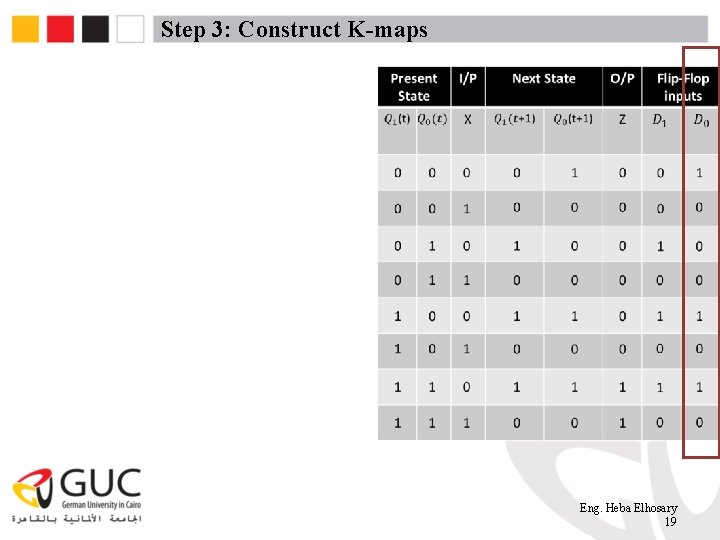

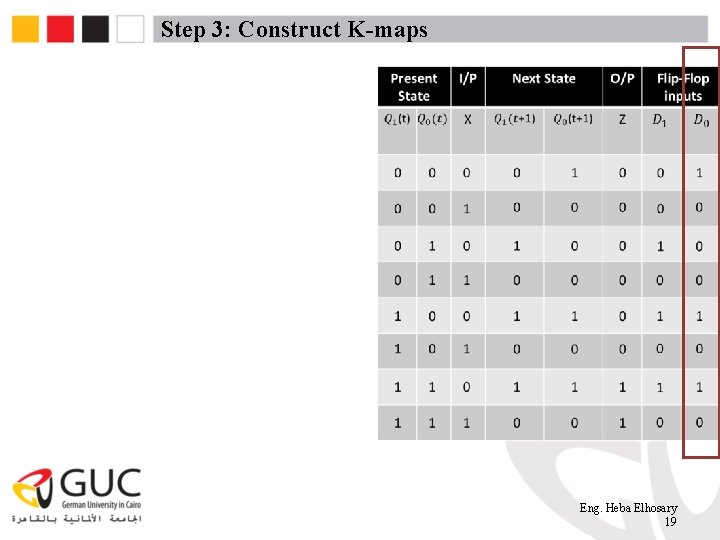

Step 3: Construct K-maps Eng. Heba Elhosary 19

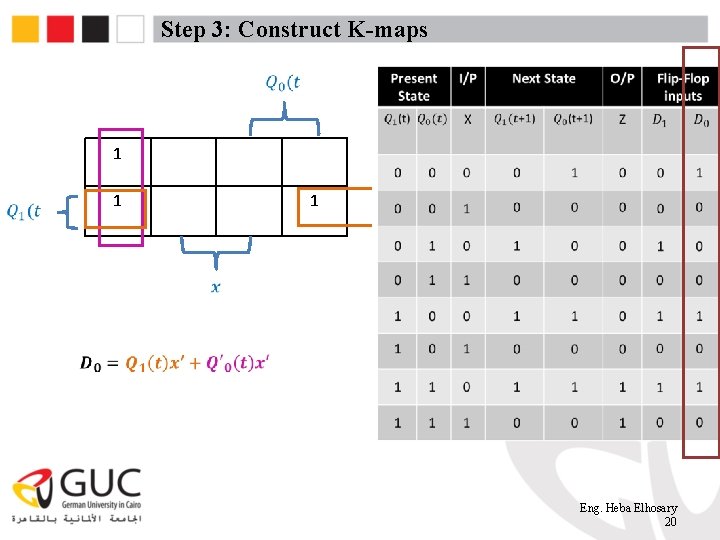

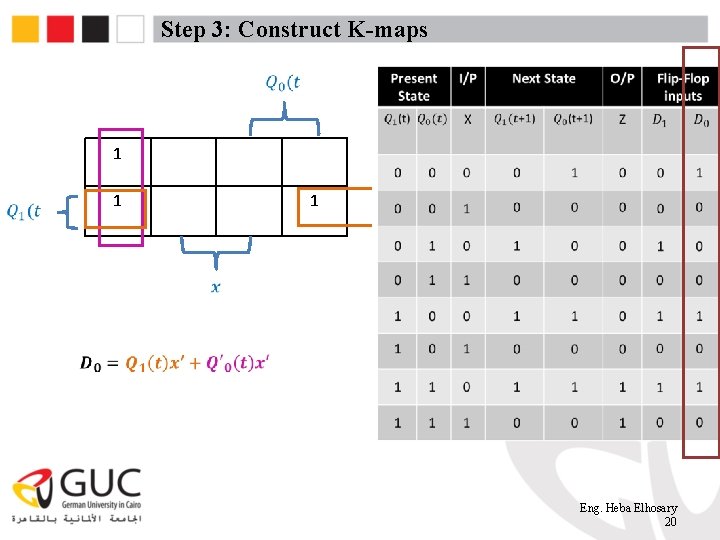

Step 3: Construct K-maps 1 1 1 Eng. Heba Elhosary 20

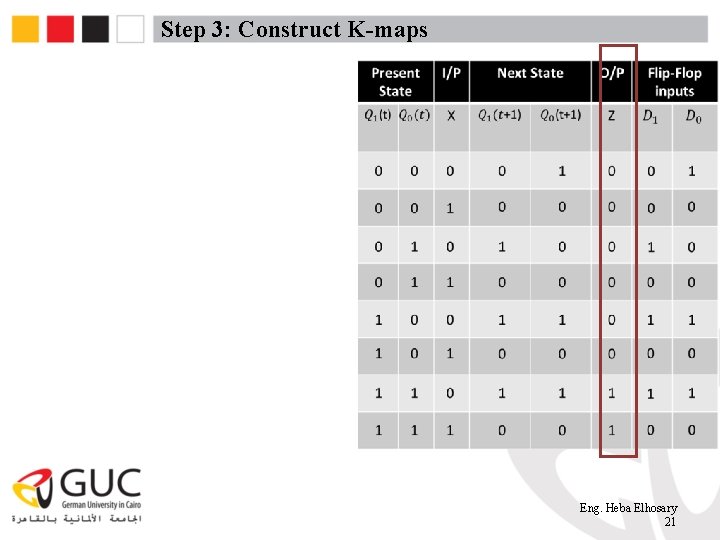

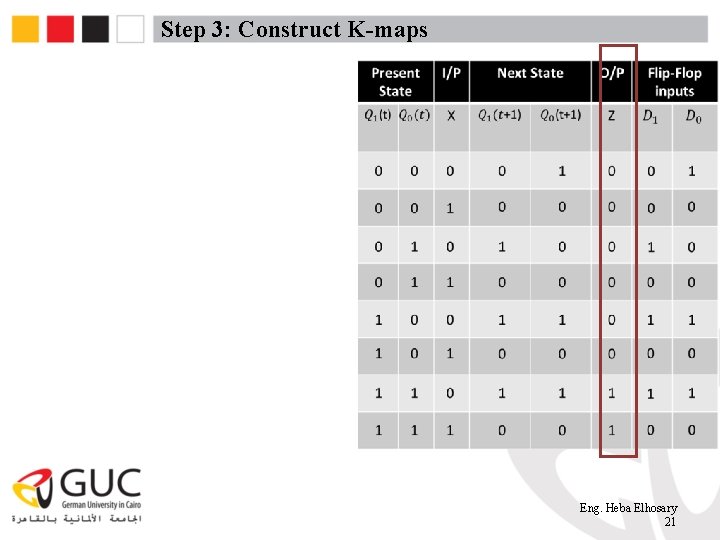

Step 3: Construct K-maps Eng. Heba Elhosary 21

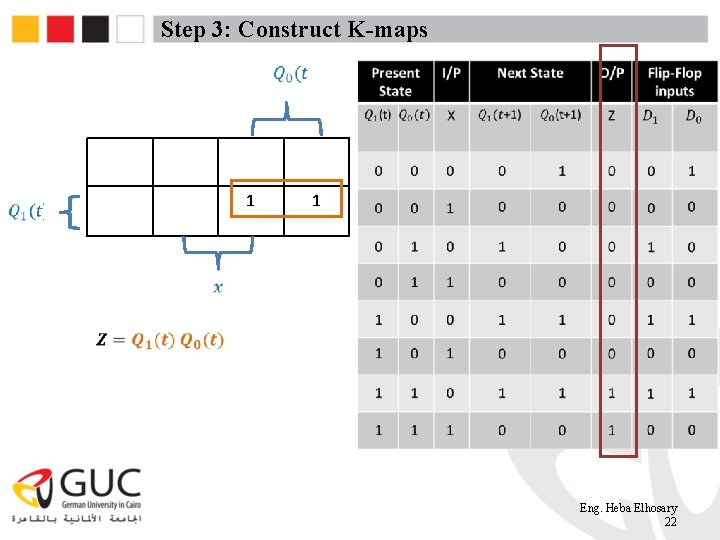

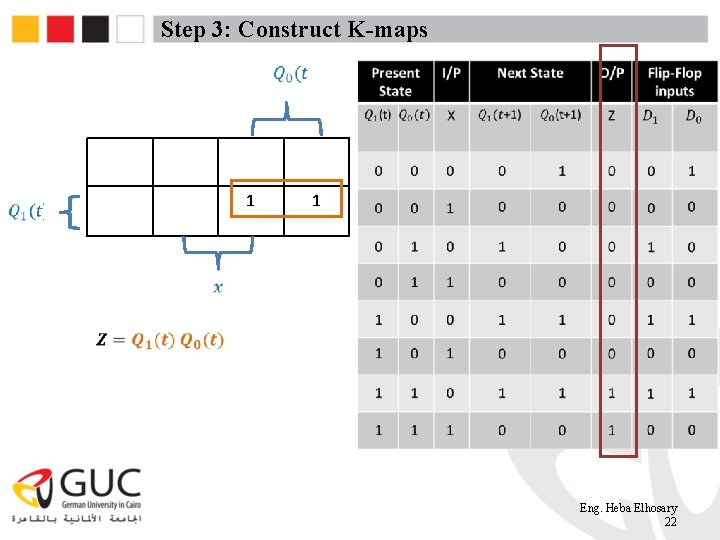

Step 3: Construct K-maps 1 1 Eng. Heba Elhosary 22

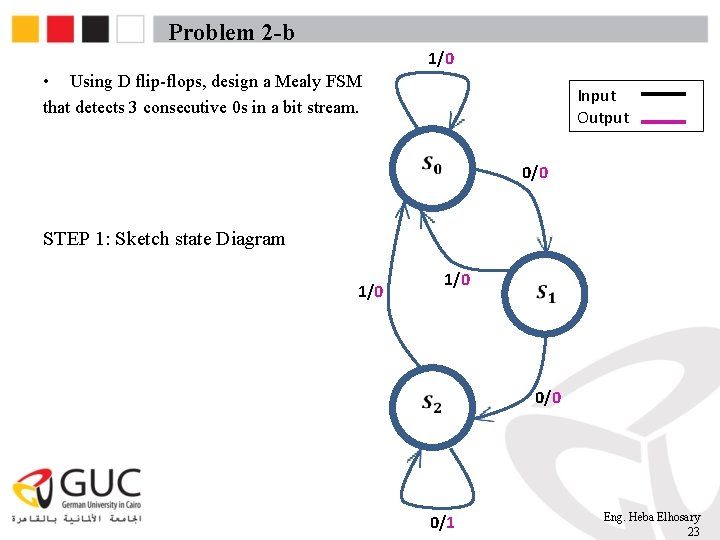

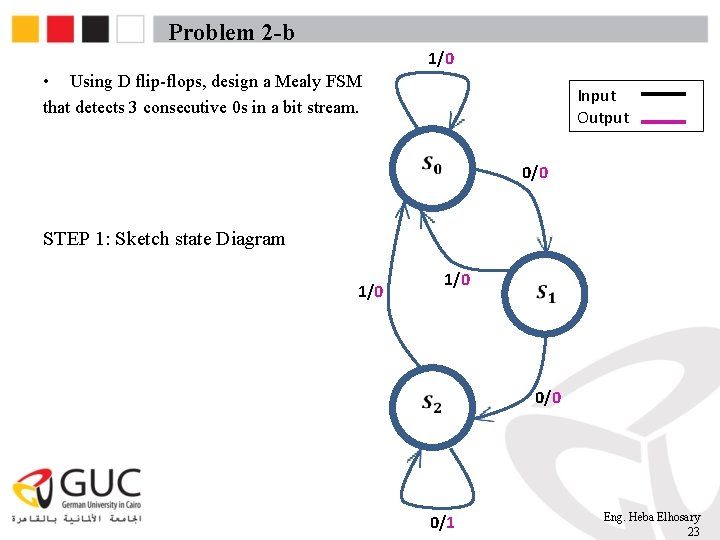

Problem 2 -b 1/0 • Using D flip-flops, design a Mealy FSM that detects 3 consecutive 0 s in a bit stream. Input Output 0/0 STEP 1: Sketch state Diagram 1/0 0/0 0/1 Eng. Heba Elhosary 23

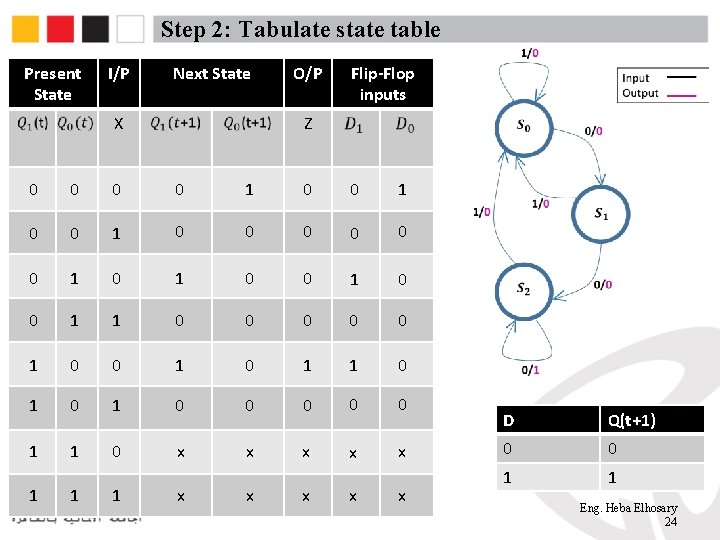

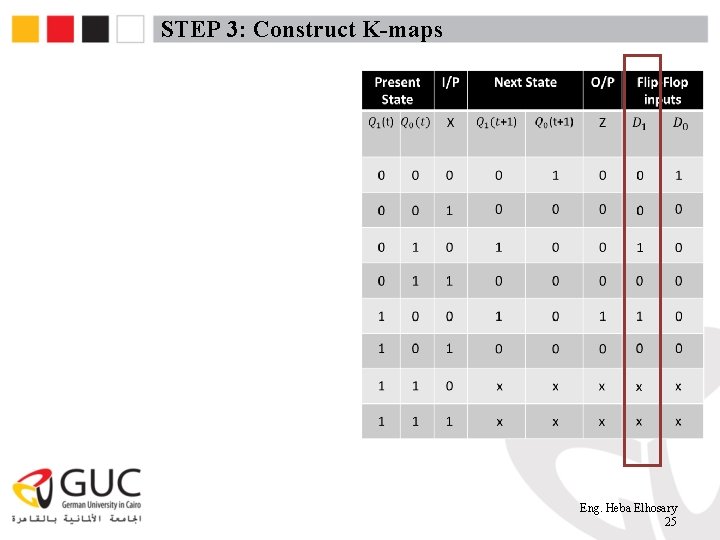

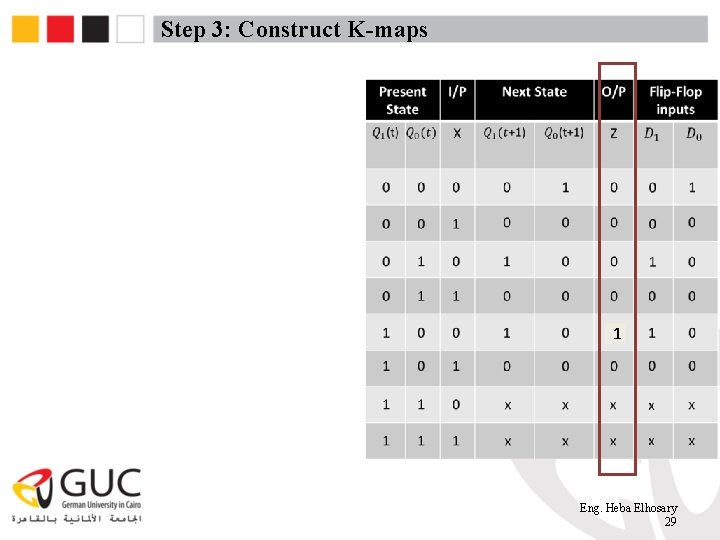

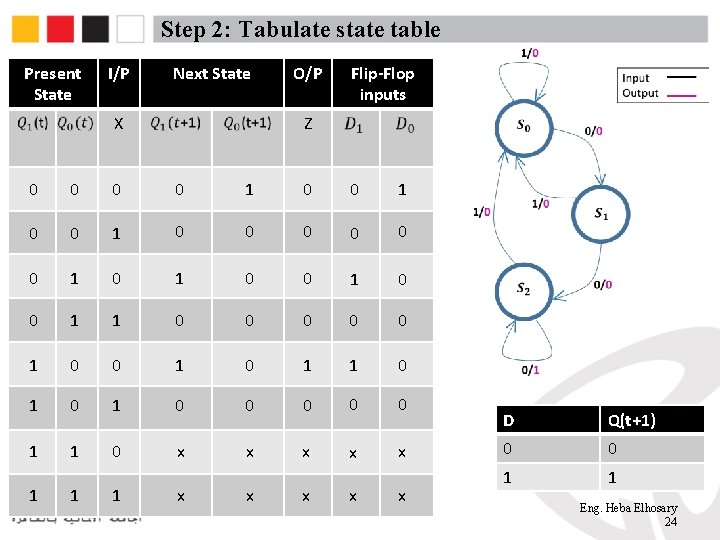

Step 2: Tabulate state table Present State I/P Next State X O/P Flip-Flop inputs Z 0 0 1 0 0 1 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 0 x x x 1 1 1 x x x D Q(t+1) 0 0 1 1 Eng. Heba Elhosary 24

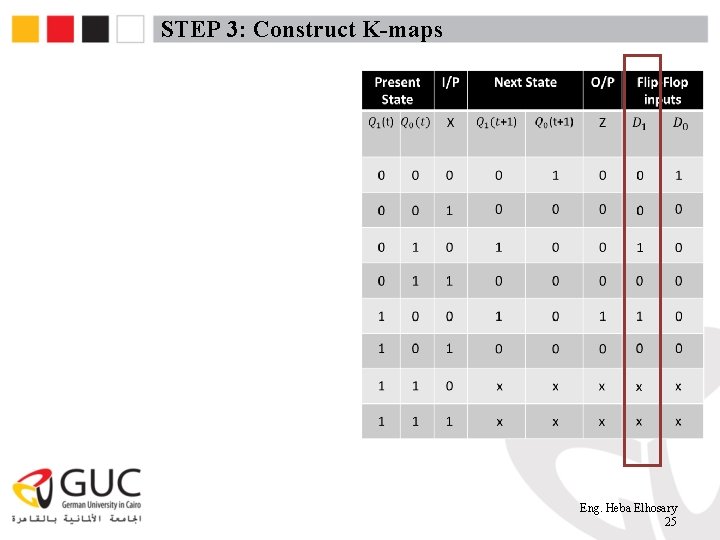

STEP 3: Construct K-maps Eng. Heba Elhosary 25

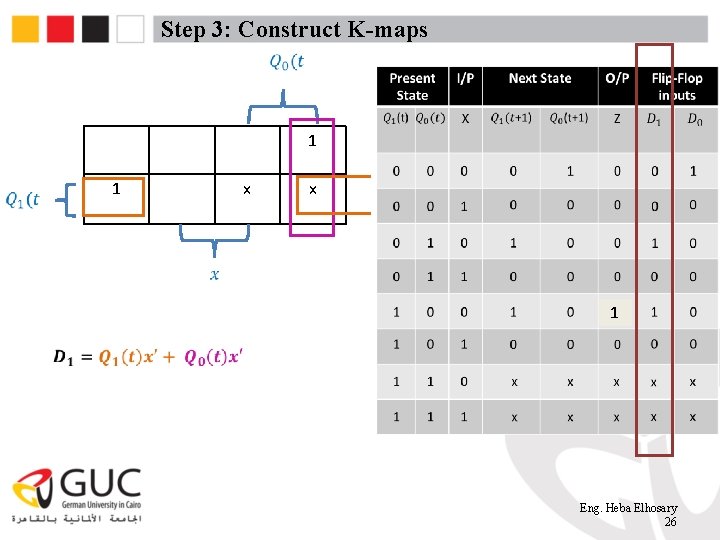

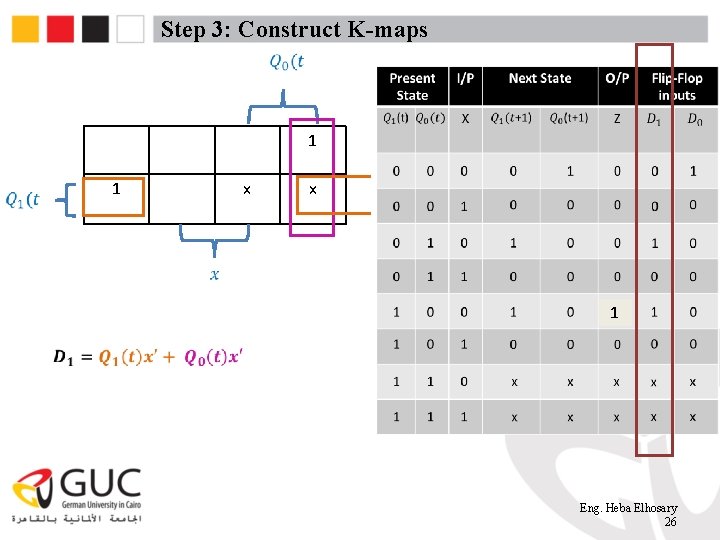

Step 3: Construct K-maps 1 1 x x 1 Eng. Heba Elhosary 26

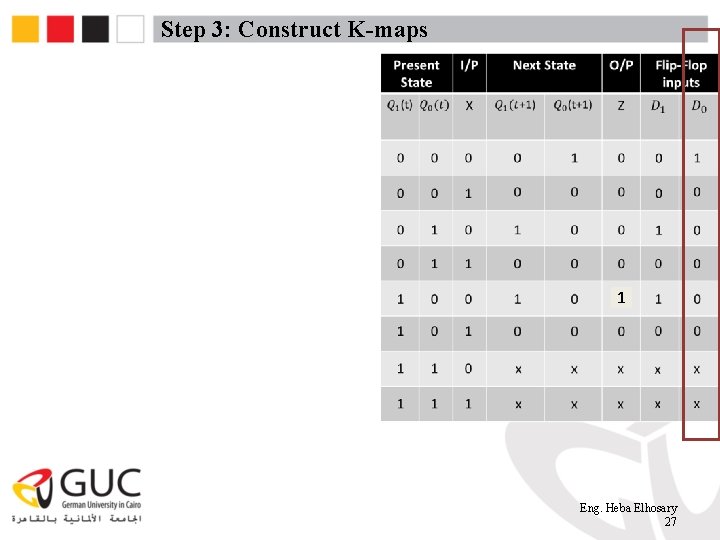

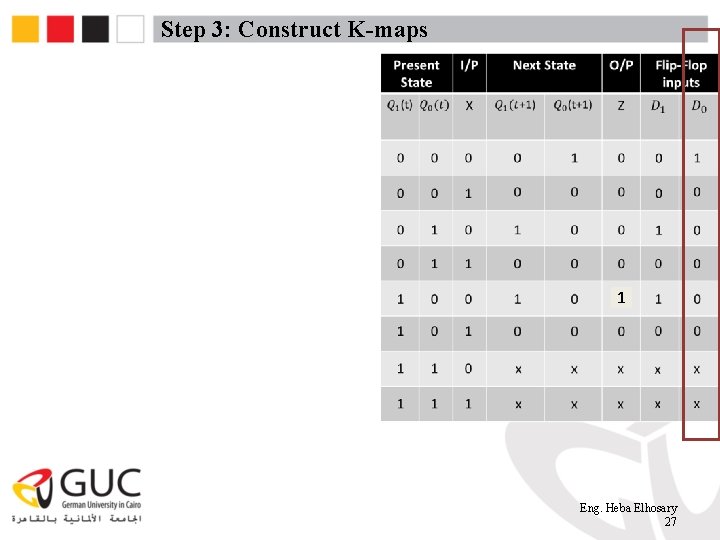

Step 3: Construct K-maps 1 Eng. Heba Elhosary 27

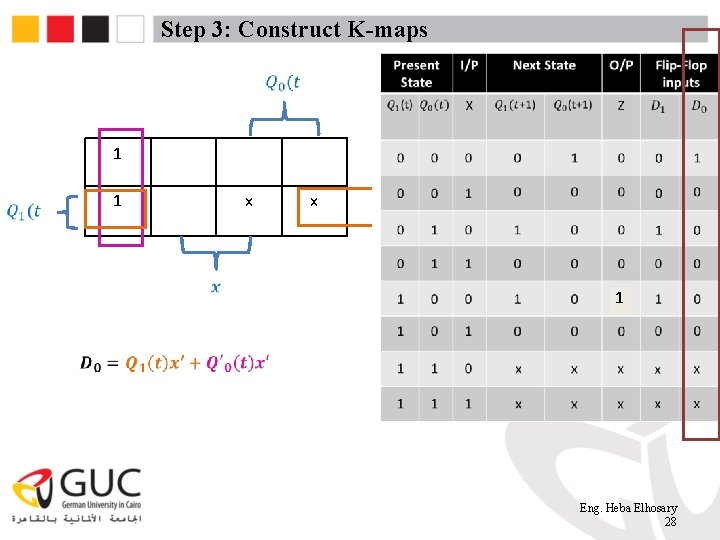

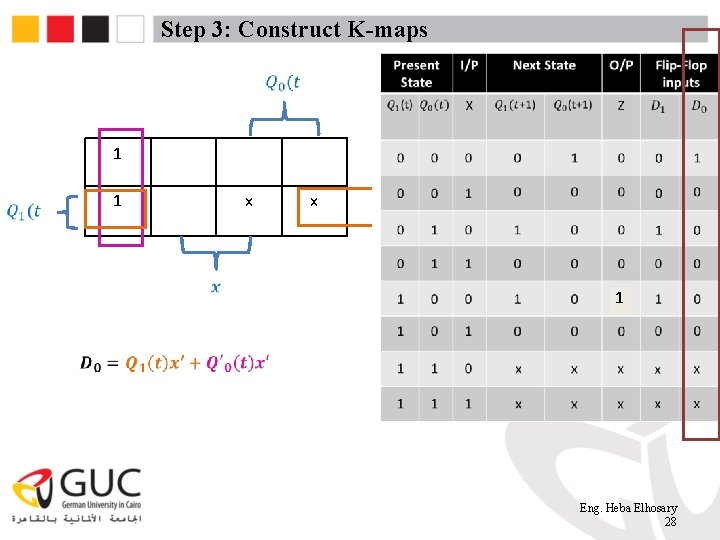

Step 3: Construct K-maps 1 1 x x 1 Eng. Heba Elhosary 28

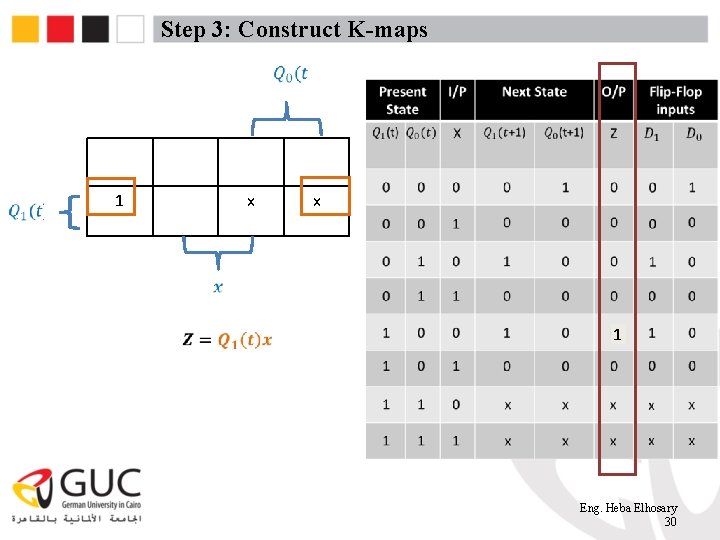

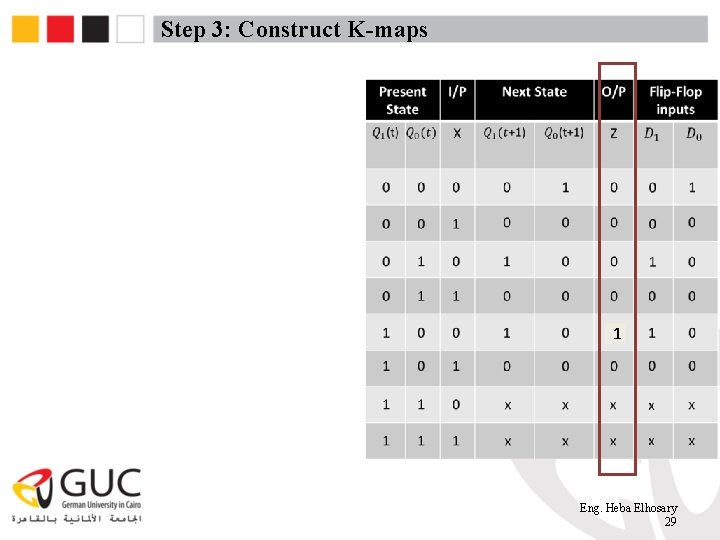

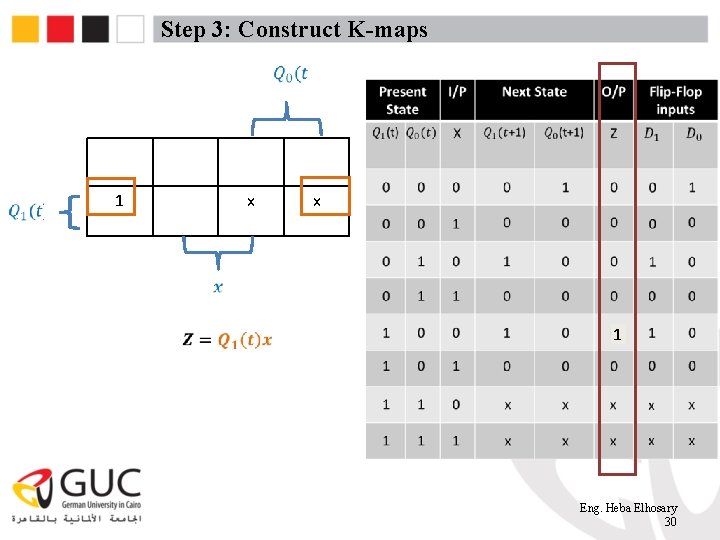

Step 3: Construct K-maps 1 Eng. Heba Elhosary 29

Step 3: Construct K-maps 1 x x 1 Eng. Heba Elhosary 30

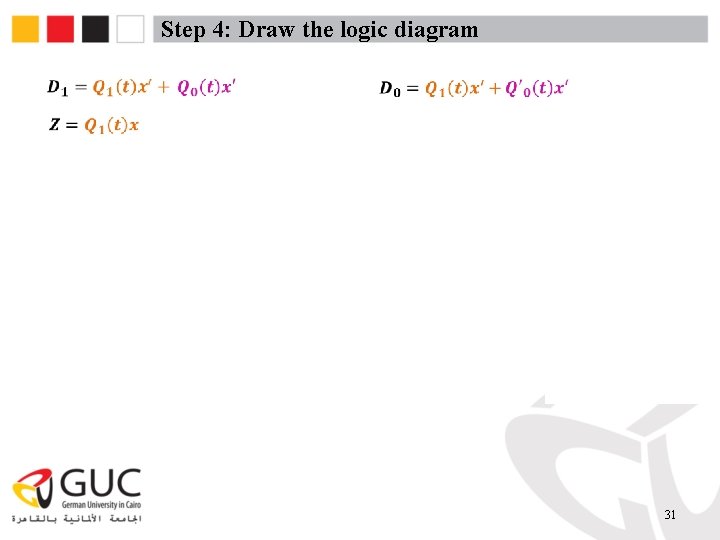

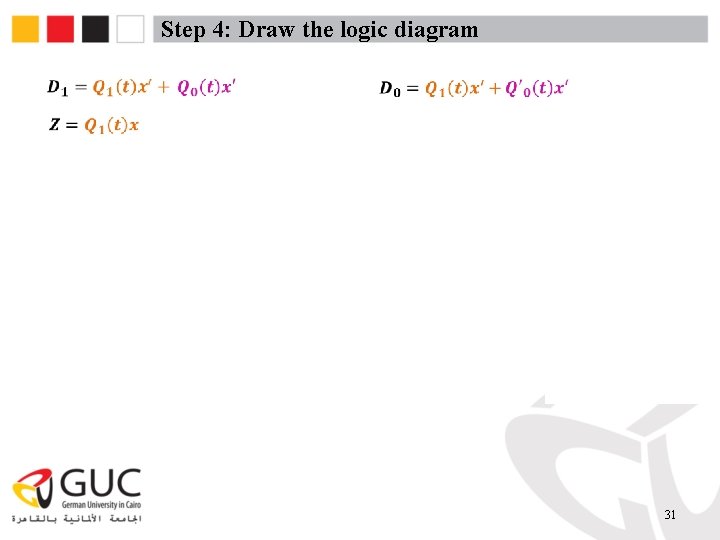

Step 4: Draw the logic diagram 31

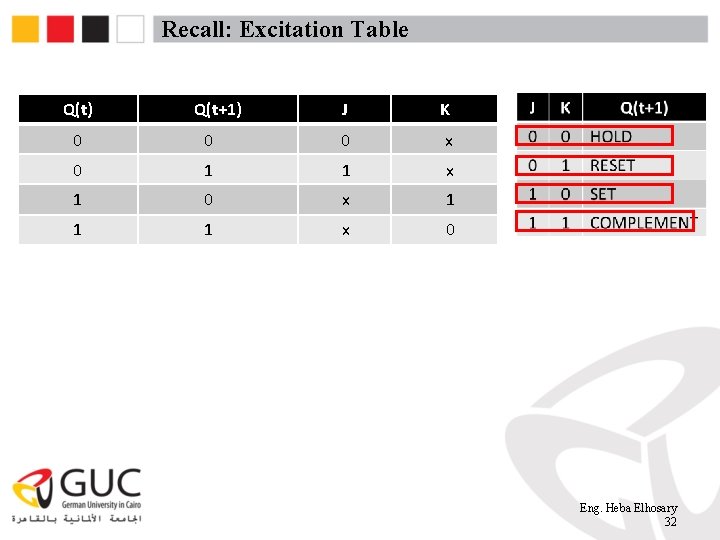

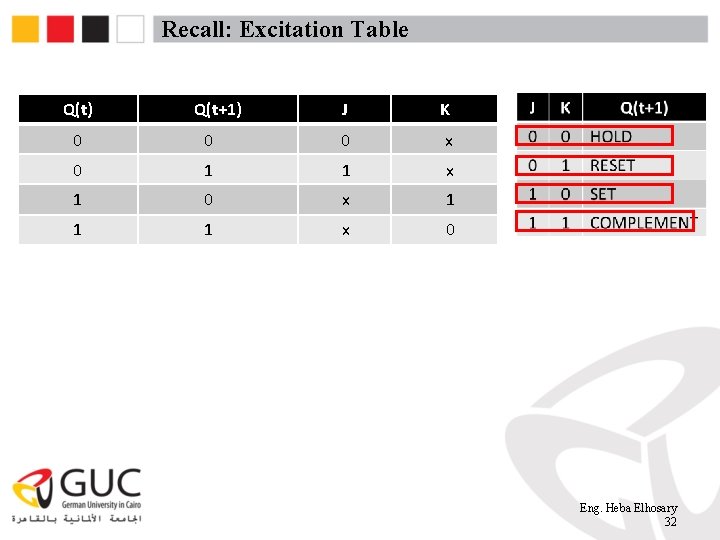

Recall: Excitation Table Q(t) Q(t+1) J K 0 0 0 x 0 1 1 x 1 0 x 1 1 1 x 0 Eng. Heba Elhosary 32

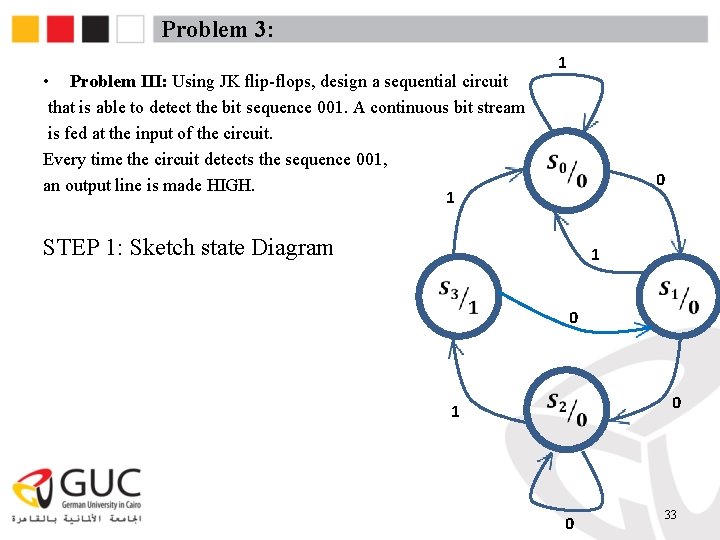

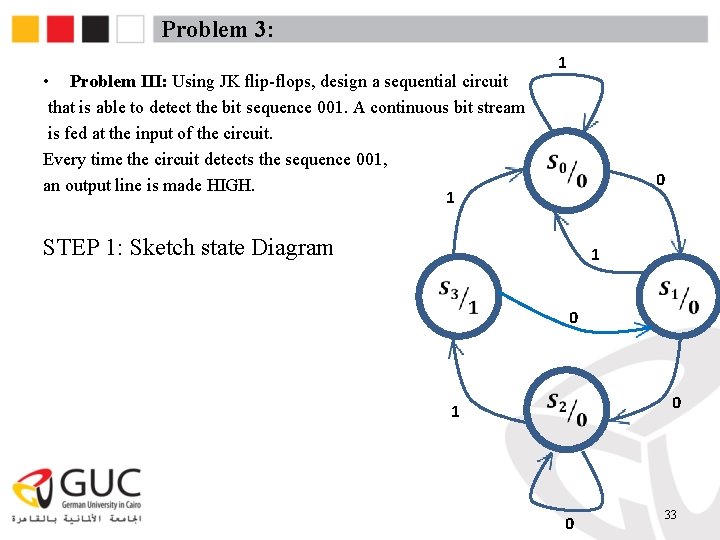

Problem 3: • Problem III: Using JK flip-flops, design a sequential circuit that is able to detect the bit sequence 001. A continuous bit stream is fed at the input of the circuit. Every time the circuit detects the sequence 001, an output line is made HIGH. 1 1 0 STEP 1: Sketch state Diagram 1 0 0 1 0 33

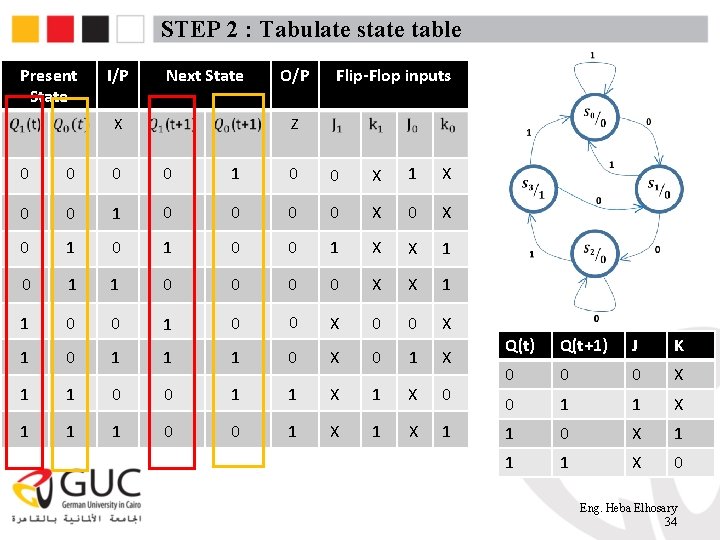

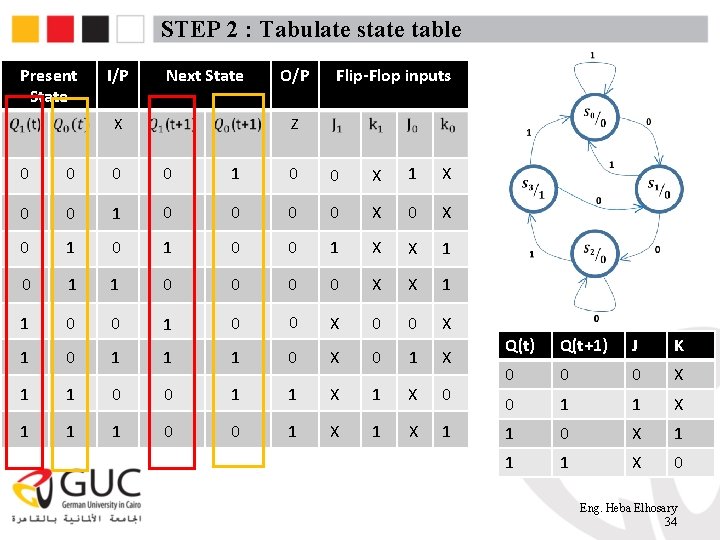

STEP 2 : Tabulate state table Present State I/P Next State X O/P Flip-Flop inputs Z 0 0 1 0 0 X 1 X 0 0 1 0 0 X 0 1 0 0 1 X X 1 0 1 1 0 0 X X 1 1 0 0 X 1 0 1 1 1 0 X 0 1 X 1 1 0 0 1 1 X 0 1 1 1 0 0 1 X 1 Q(t) Q(t+1) J K 0 0 0 X 0 1 1 X 1 0 X 1 1 1 X 0 Eng. Heba Elhosary 34

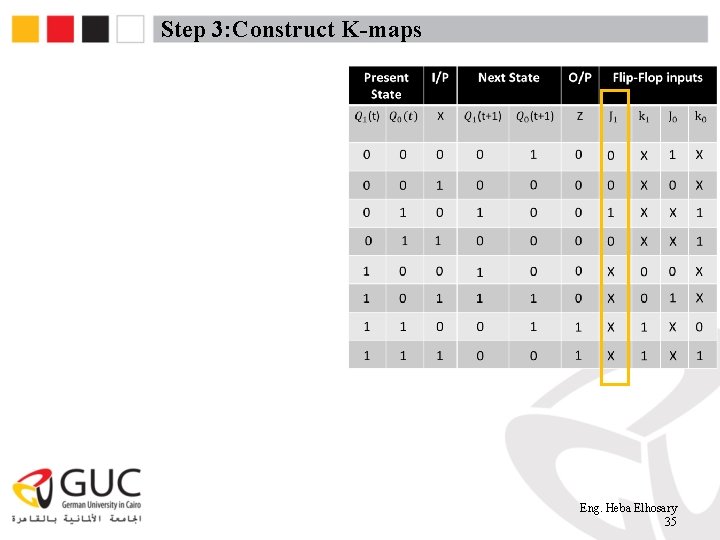

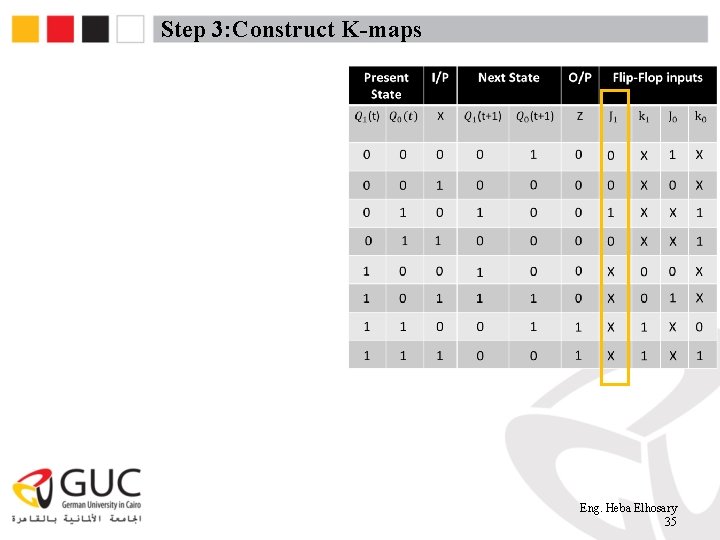

Step 3: Construct K-maps Eng. Heba Elhosary 35

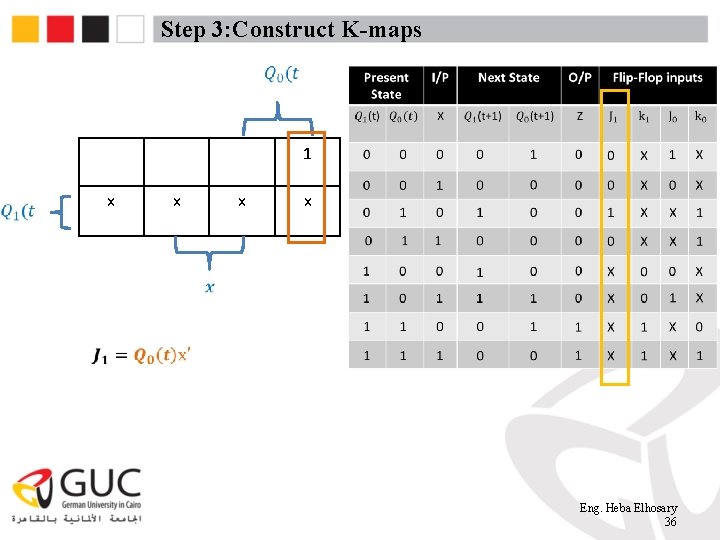

Step 3: Construct K-maps 1 x x Eng. Heba Elhosary 36

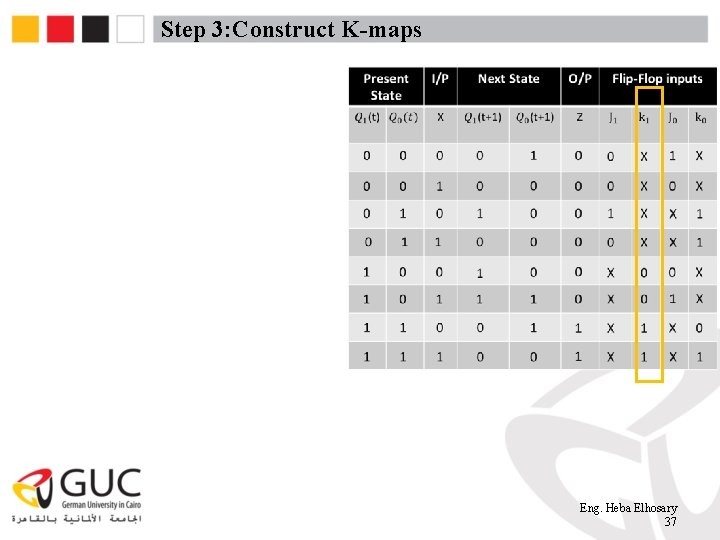

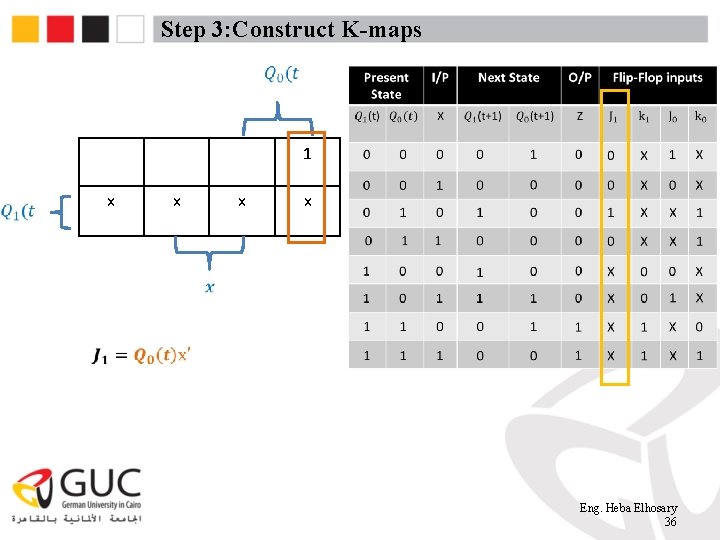

Step 3: Construct K-maps Eng. Heba Elhosary 37

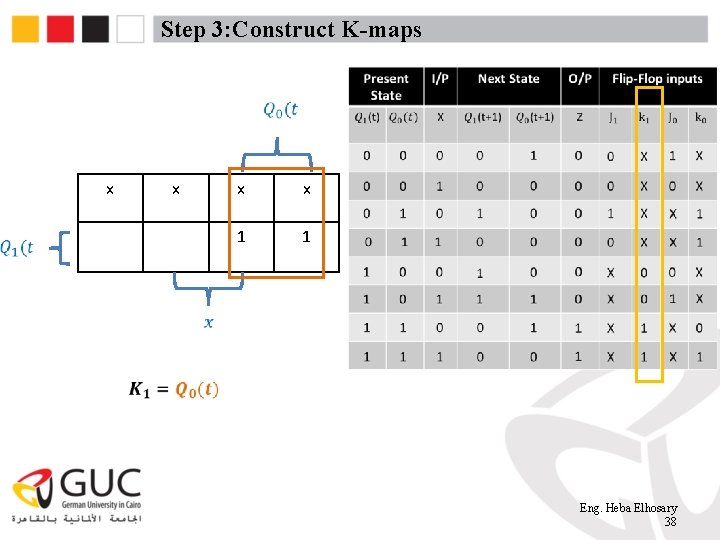

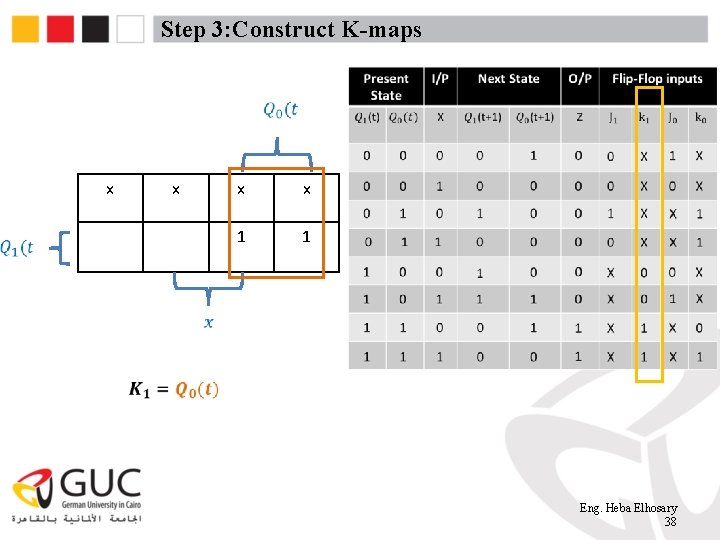

Step 3: Construct K-maps x x 1 1 Eng. Heba Elhosary 38

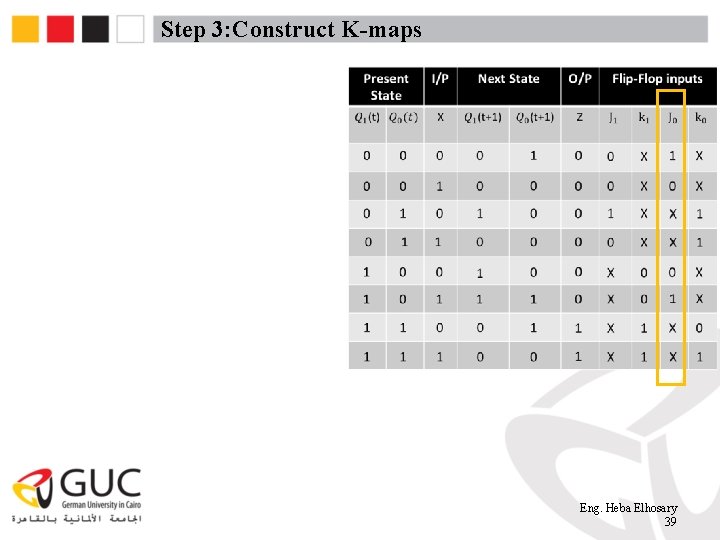

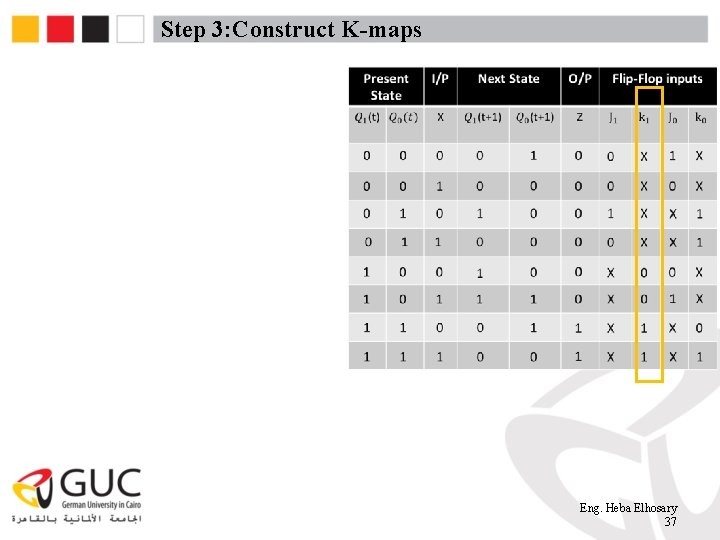

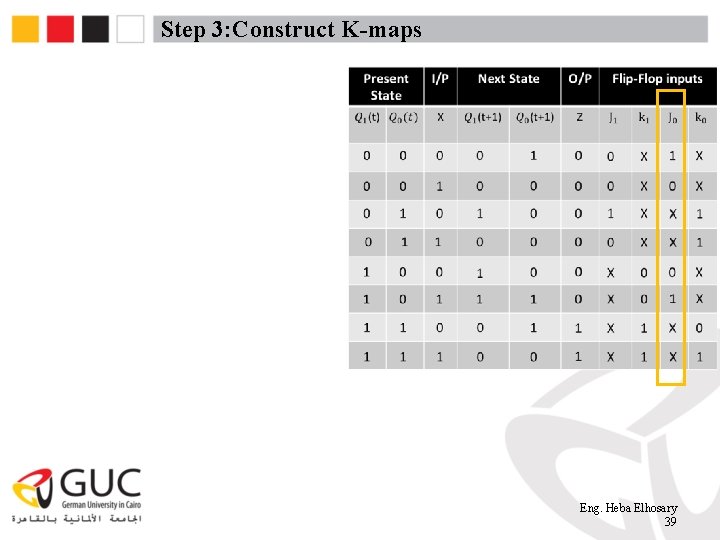

Step 3: Construct K-maps Eng. Heba Elhosary 39

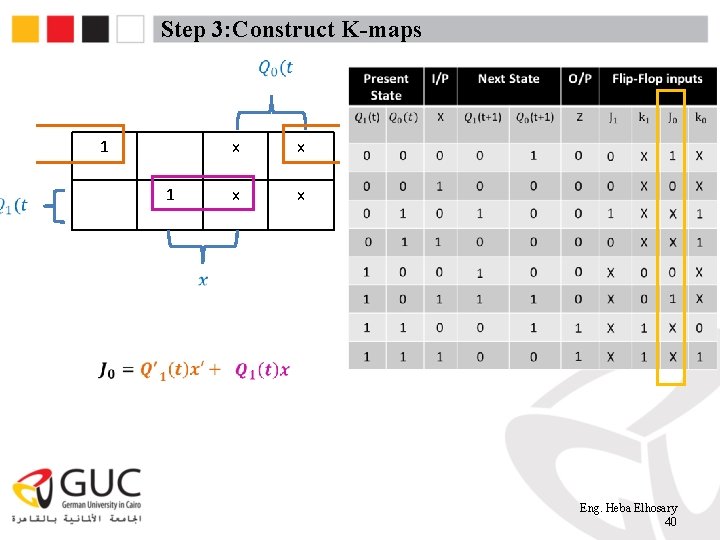

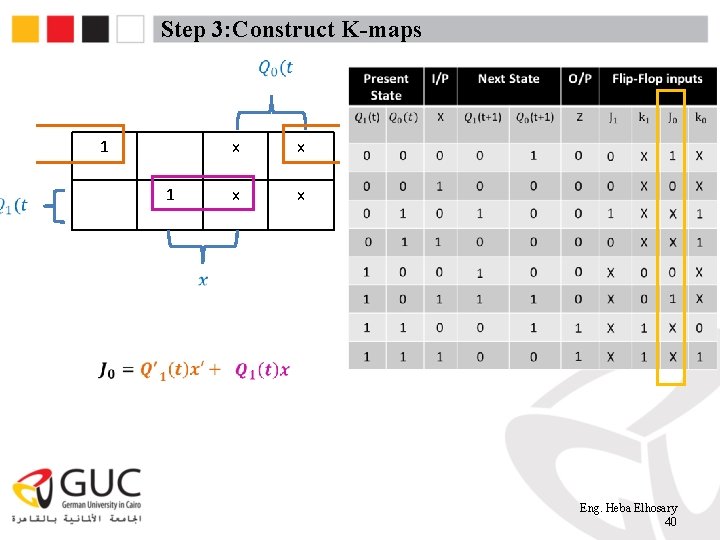

Step 3: Construct K-maps 1 1 x x Eng. Heba Elhosary 40

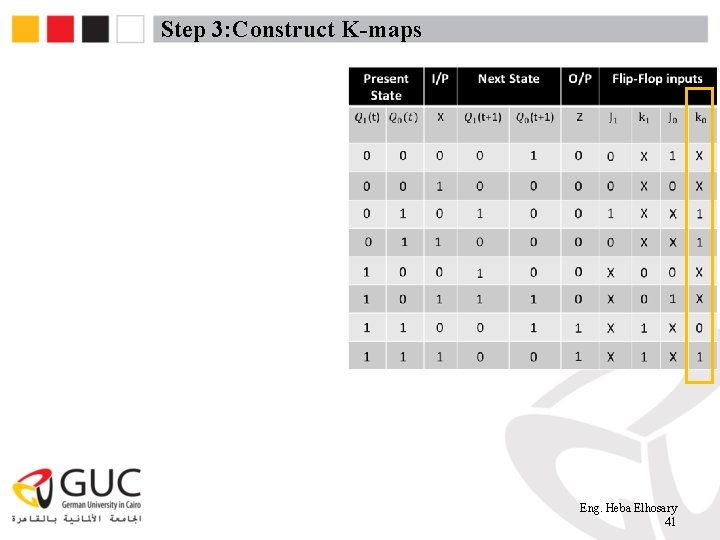

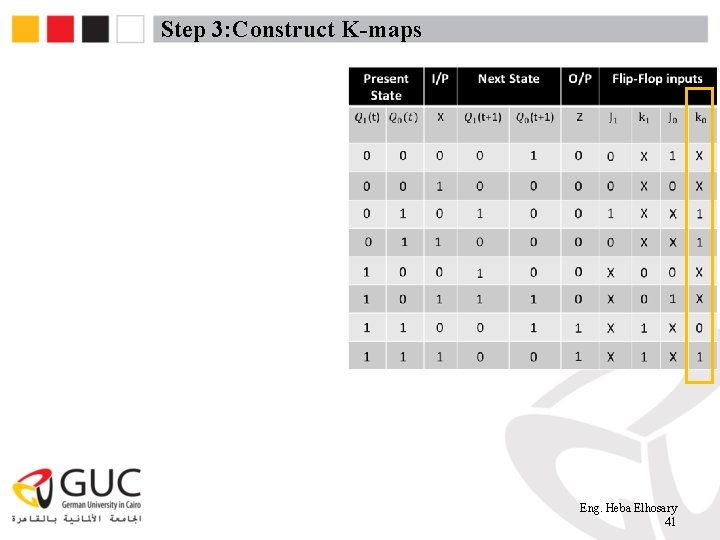

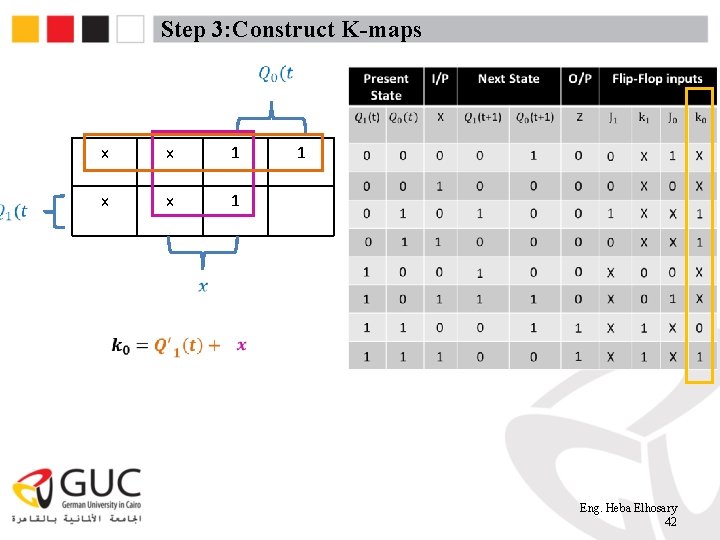

Step 3: Construct K-maps Eng. Heba Elhosary 41

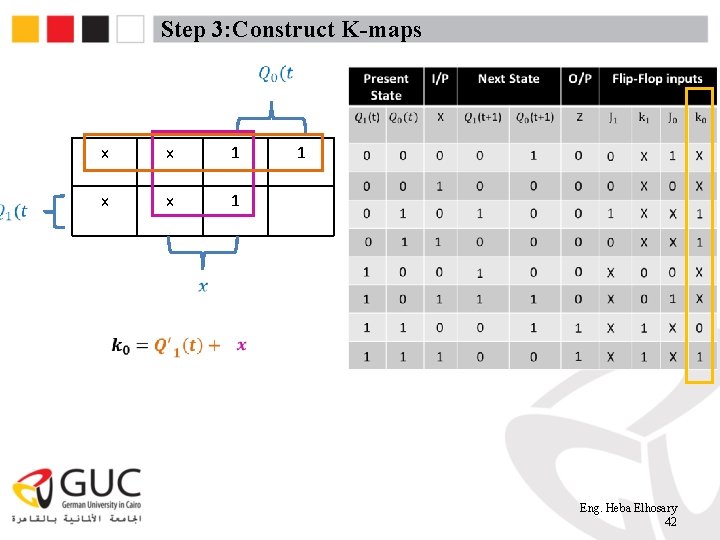

Step 3: Construct K-maps x x 1 1 Eng. Heba Elhosary 42

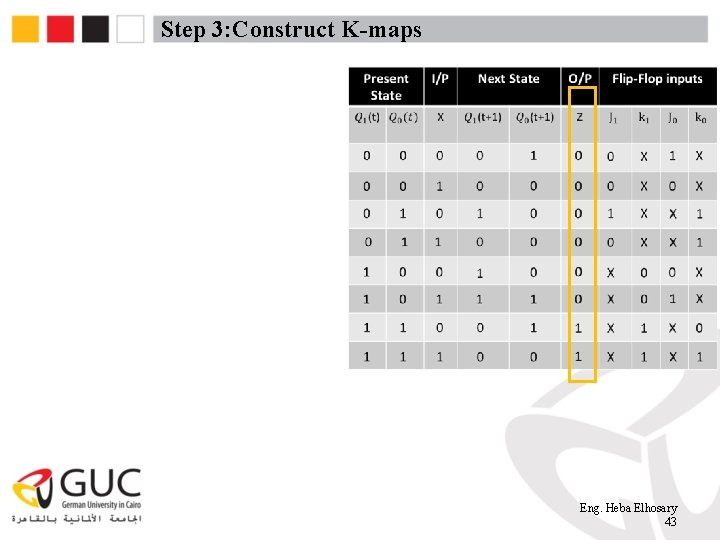

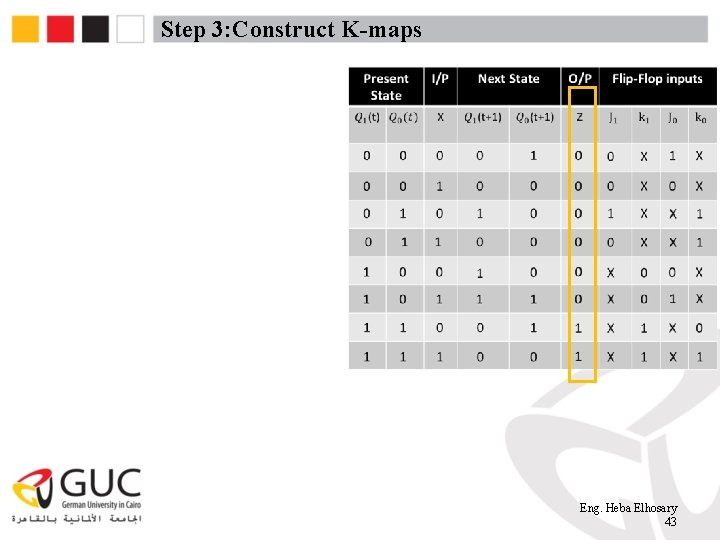

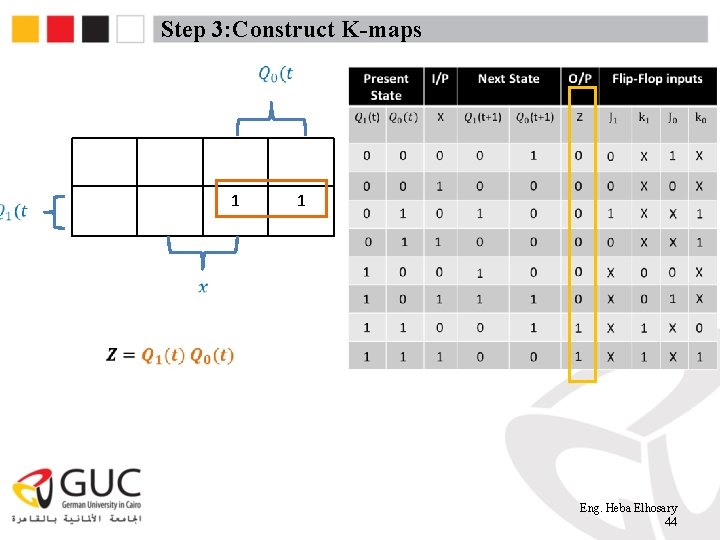

Step 3: Construct K-maps Eng. Heba Elhosary 43

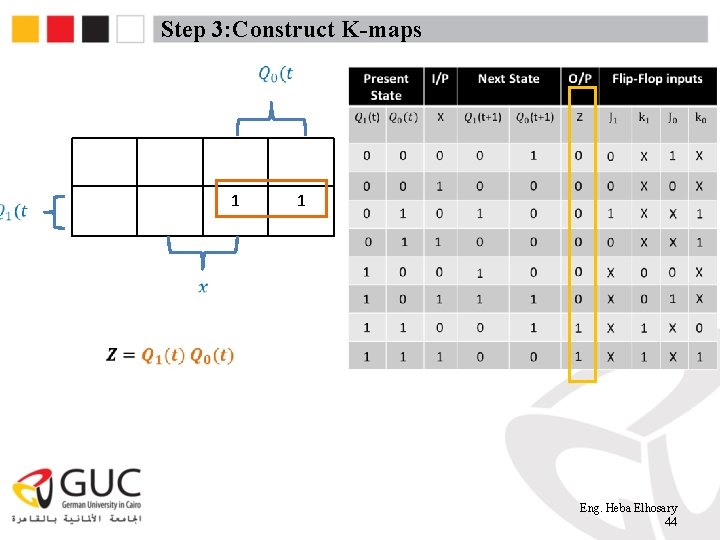

Step 3: Construct K-maps 1 1 Eng. Heba Elhosary 44

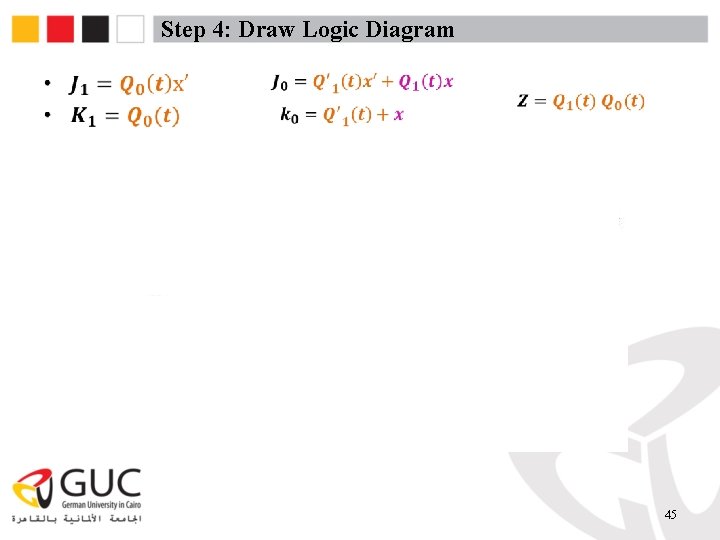

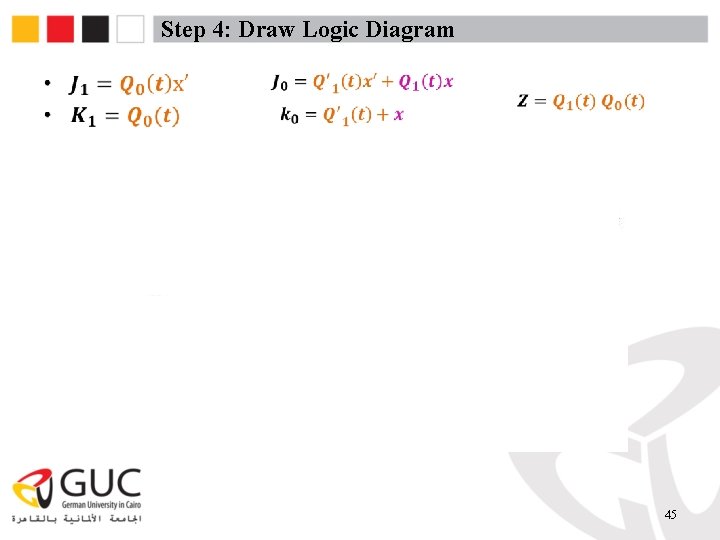

Step 4: Draw Logic Diagram • 45

FSMs Design Steps 1. 2. 2. 1 3. 4. Sketch state diagram. Tabulate characteristic/Excitation table for the exploited flip-flop. Tabulate state table Construct k-maps for flip-flop inputs and the outputs(if any) Draw logic diagram Eng. Heba Elhosary 46

E-mail Heba. elhosary@guc. edu. eg 47