CS 152 Computer Architecture and Engineering Lecture 8

![A Summary of Control Signals inst Register Transfer ADD R[rd] <– R[rs] + R[rt]; A Summary of Control Signals inst Register Transfer ADD R[rd] <– R[rs] + R[rt];](https://slidetodoc.com/presentation_image/7d02e29aef4e2c030cf3edfba146a457/image-20.jpg)

- Slides: 39

CS 152 Computer Architecture and Engineering Lecture 8 Designing Single Cycle Control Feb 22, 1999 John Kubiatowicz (http. cs. berkeley. edu/~kubitron) lecture slides: http: //www-inst. eecs. berkeley. edu/~cs 152/ 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 1

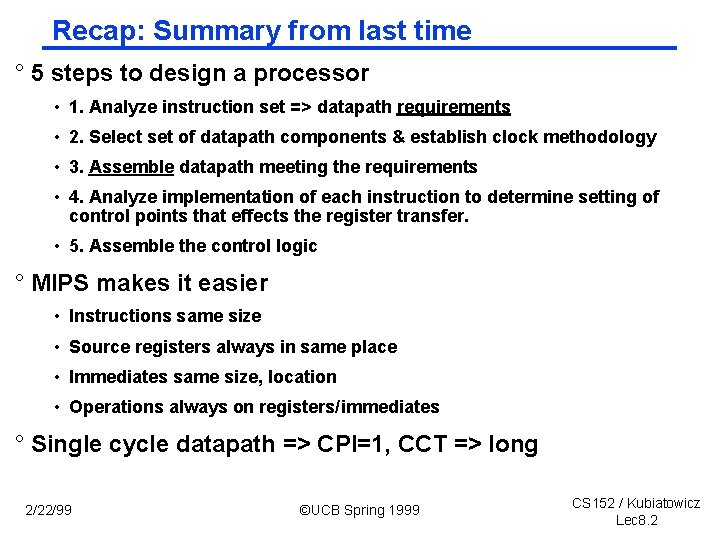

Recap: Summary from last time ° 5 steps to design a processor • 1. Analyze instruction set => datapath requirements • 2. Select set of datapath components & establish clock methodology • 3. Assemble datapath meeting the requirements • 4. Analyze implementation of each instruction to determine setting of control points that effects the register transfer. • 5. Assemble the control logic ° MIPS makes it easier • Instructions same size • Source registers always in same place • Immediates same size, location • Operations always on registers/immediates ° Single cycle datapath => CPI=1, CCT => long 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 2

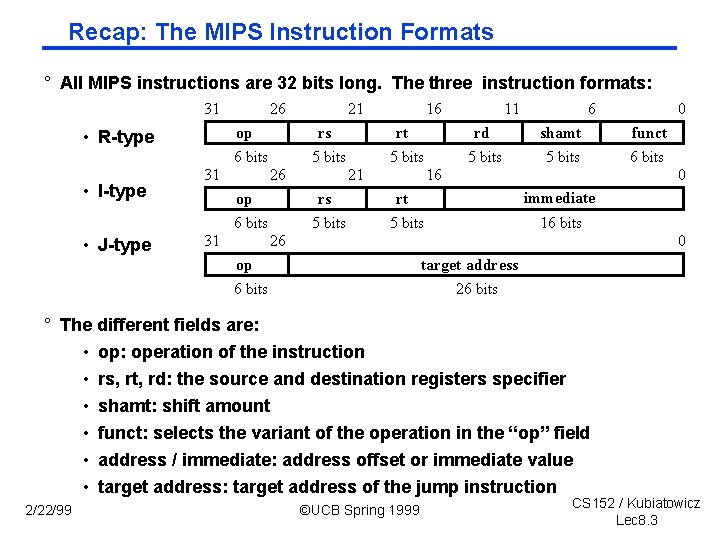

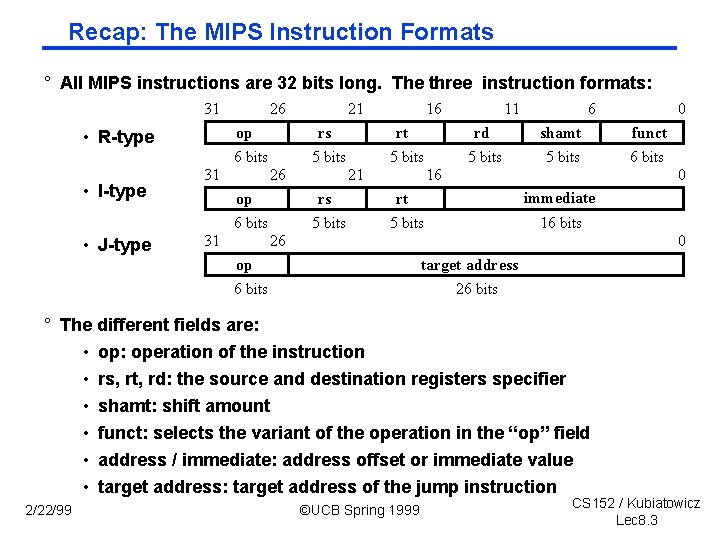

Recap: The MIPS Instruction Formats ° All MIPS instructions are 32 bits long. The three instruction formats: 31 26 op • R-type rs 6 bits • I-type • J-type 31 21 op 6 bits 31 rt 5 bits 26 16 5 bits 21 rs 5 bits 11 6 rd shamt funct 5 bits 6 bits 16 rt 5 bits 0 immediate 16 bits 26 0 op 6 bits target address 26 bits ° The different fields are: • op: operation of the instruction • rs, rt, rd: the source and destination registers specifier • shamt: shift amount • funct: selects the variant of the operation in the “op” field • address / immediate: address offset or immediate value • target address: target address of the jump instruction 2/22/99 0 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 3

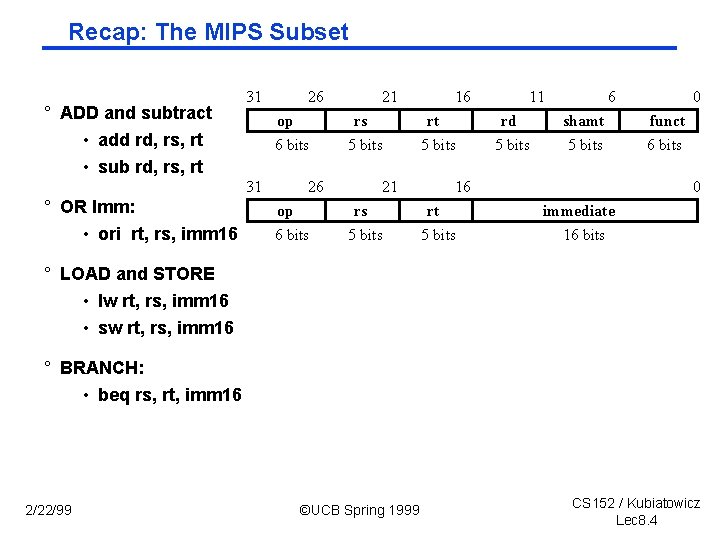

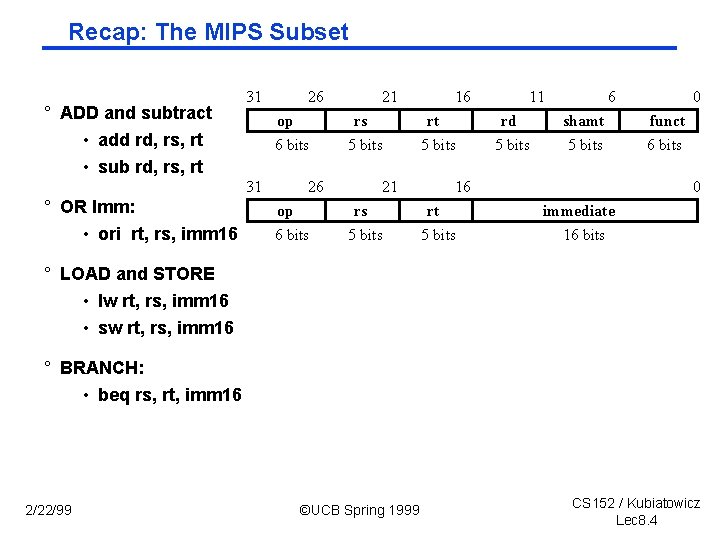

Recap: The MIPS Subset ° ADD and subtract • add rd, rs, rt • sub rd, rs, rt 31 op 6 bits 31 ° OR Imm: • ori rt, rs, imm 16 26 26 op 6 bits 21 rs 5 bits 16 rt 5 bits 11 rd 5 bits 6 shamt 5 bits 16 rt 5 bits 0 funct 6 bits 0 immediate 16 bits ° LOAD and STORE • lw rt, rs, imm 16 • sw rt, rs, imm 16 ° BRANCH: • beq rs, rt, imm 16 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 4

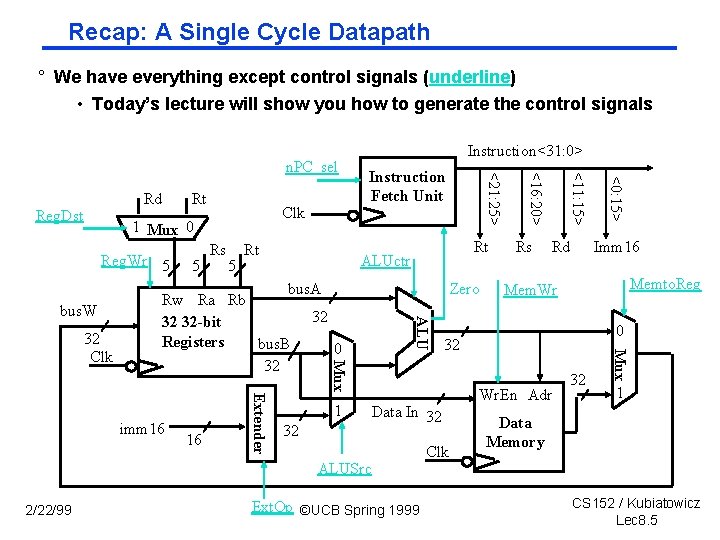

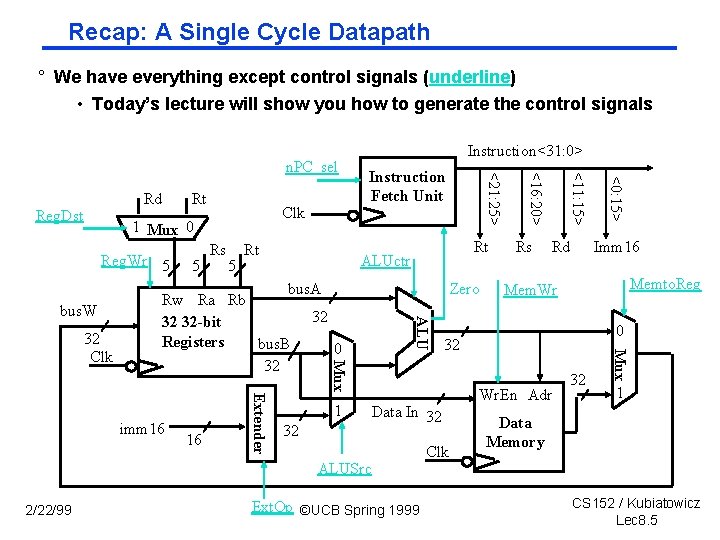

Recap: A Single Cycle Datapath ° We have everything except control signals (underline) • Today’s lecture will show you how to generate the control signals 1 Mux 0 Reg. Wr 5 5 Rs 5 Rt Rt ALUctr bus. A 0 1 32 2/22/99 Ext. Op ©UCB Spring 1999 Imm 16 Memto. Reg Mem. Wr 0 32 Data In 32 ALUSrc Rd Clk Wr. En Adr 32 Mux 16 Extender imm 16 32 Mux 32 Clk Rw Ra Rb 32 32 -bit Registers bus. B 32 ALU bus. W Zero Rs <0: 15> Clk <11: 15> Reg. Dst Rt <16: 20> Rd Instruction Fetch Unit <21: 25> n. PC_sel Instruction<31: 0> 1 Data Memory CS 152 / Kubiatowicz Lec 8. 5

The Big Picture: Where are We Now? ° The Five Classic Components of a Computer Processor Input Control Memory Datapath Output ° Today’s Topic: Designing the Control for the Single Cycle Datapath 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 6

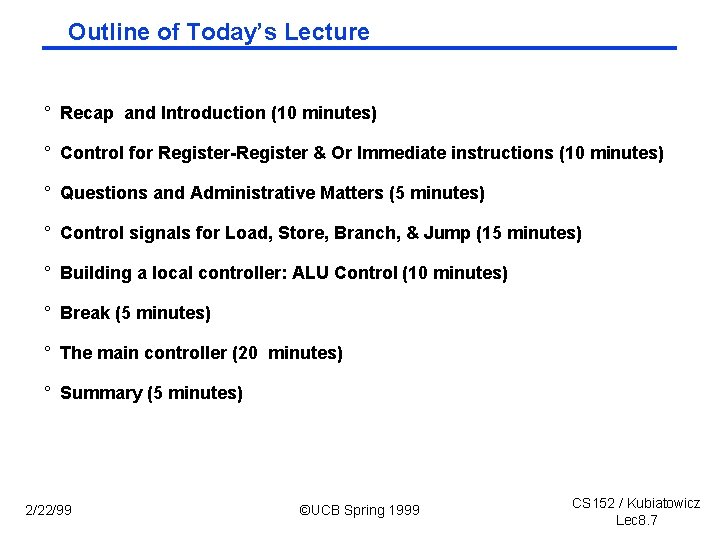

Outline of Today’s Lecture ° Recap and Introduction (10 minutes) ° Control for Register-Register & Or Immediate instructions (10 minutes) ° Questions and Administrative Matters (5 minutes) ° Control signals for Load, Store, Branch, & Jump (15 minutes) ° Building a local controller: ALU Control (10 minutes) ° Break (5 minutes) ° The main controller (20 minutes) ° Summary (5 minutes) 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 7

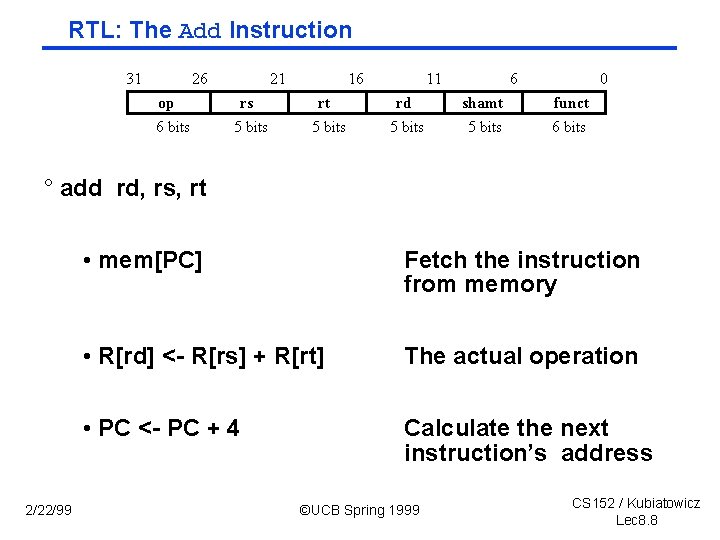

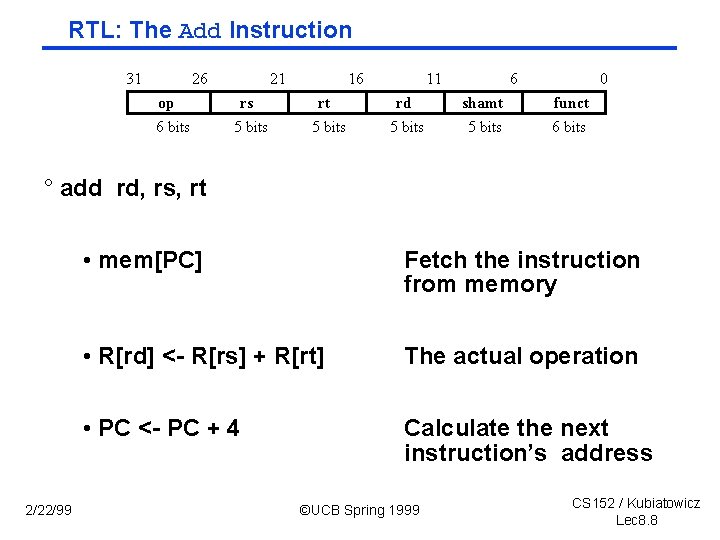

RTL: The Add Instruction 31 26 op 6 bits 21 rs 5 bits 16 rt 5 bits 11 rd 5 bits 6 shamt 5 bits 0 funct 6 bits ° add rd, rs, rt 2/22/99 • mem[PC] Fetch the instruction from memory • R[rd] <- R[rs] + R[rt] The actual operation • PC <- PC + 4 Calculate the next instruction’s address ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 8

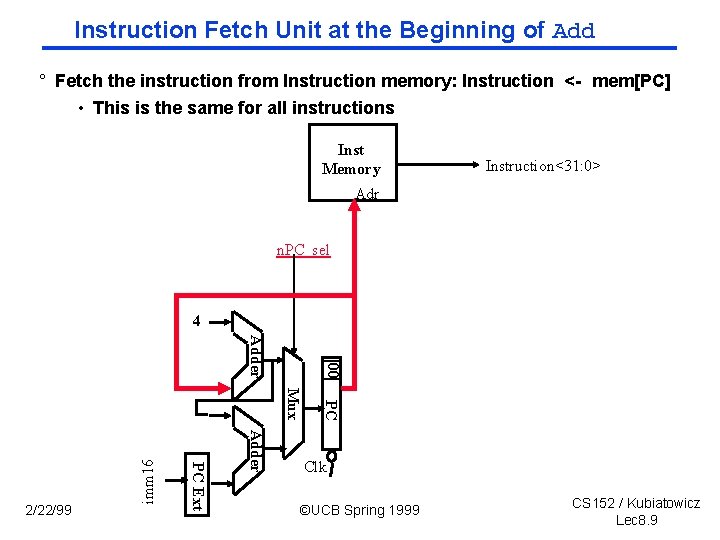

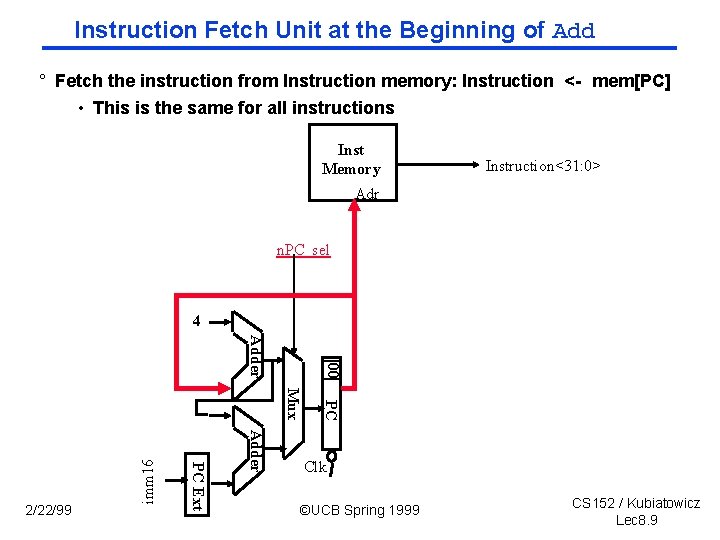

Instruction Fetch Unit at the Beginning of Add ° Fetch the instruction from Instruction memory: Instruction <- mem[PC] • This is the same for all instructions Inst Memory Instruction<31: 0> Adr n. PC_sel 4 00 Adder imm 16 PC Mux Adder PC Ext 2/22/99 Clk ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 9

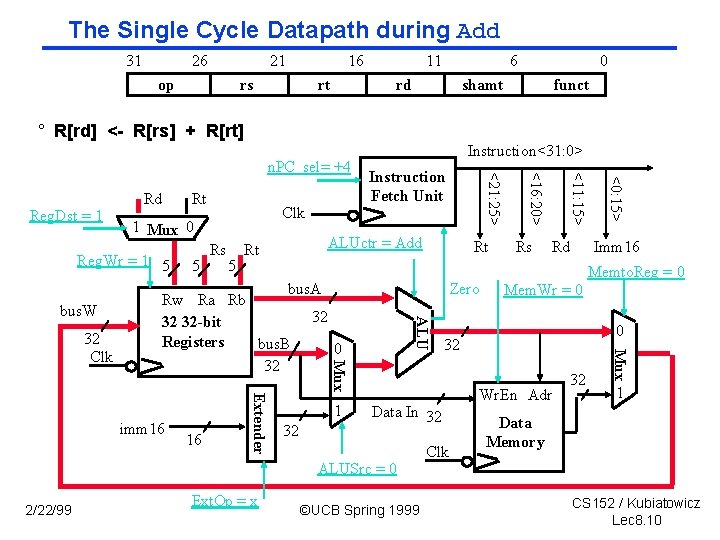

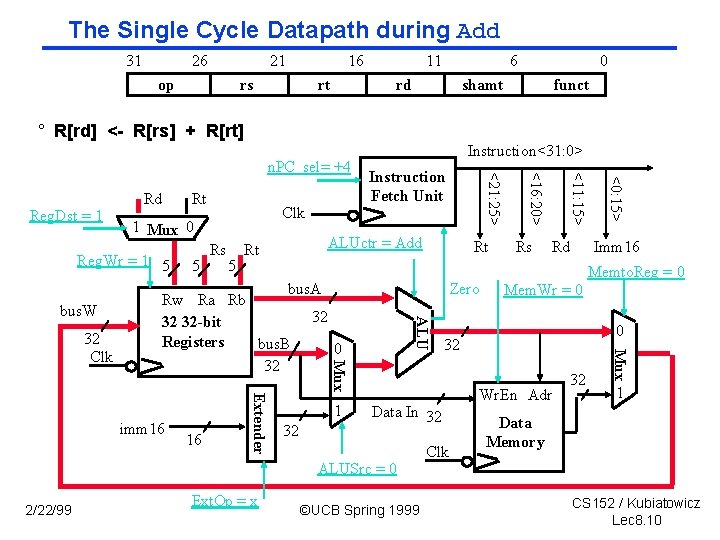

The Single Cycle Datapath during Add 31 26 21 op 16 rs rt 11 6 rd 0 shamt funct ° R[rd] <- R[rs] + R[rt] Zero ALU 16 Extender imm 16 1 32 2/22/99 Ext. Op = x ©UCB Spring 1999 Rd Imm 16 Memto. Reg = 0 Mem. Wr = 0 0 32 Data In 32 ALUSrc = 0 Rs Clk Wr. En Adr 32 Mux bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rt <0: 15> 5 ALUctr = Add Rt <11: 15> 5 Rs Mux 32 Clk 1 Mux 0 Reg. Wr = 1 5 bus. W Rt <16: 20> Reg. Dst = 1 Rd Instruction Fetch Unit <21: 25> n. PC_sel= +4 Instruction<31: 0> 1 Data Memory CS 152 / Kubiatowicz Lec 8. 10

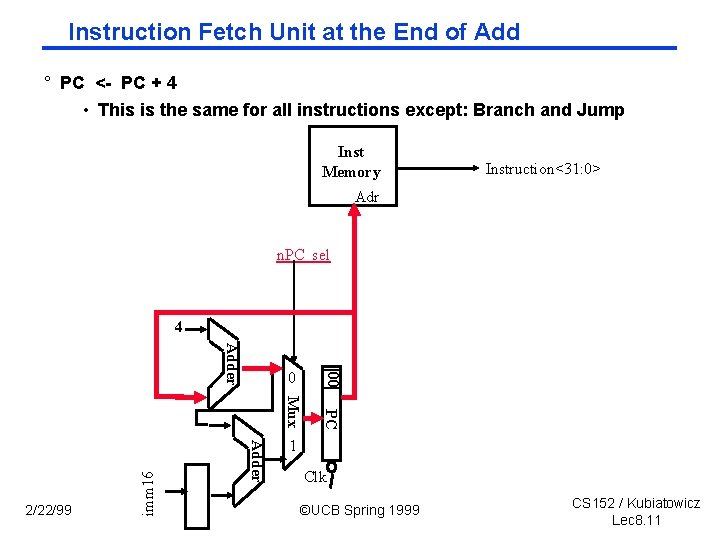

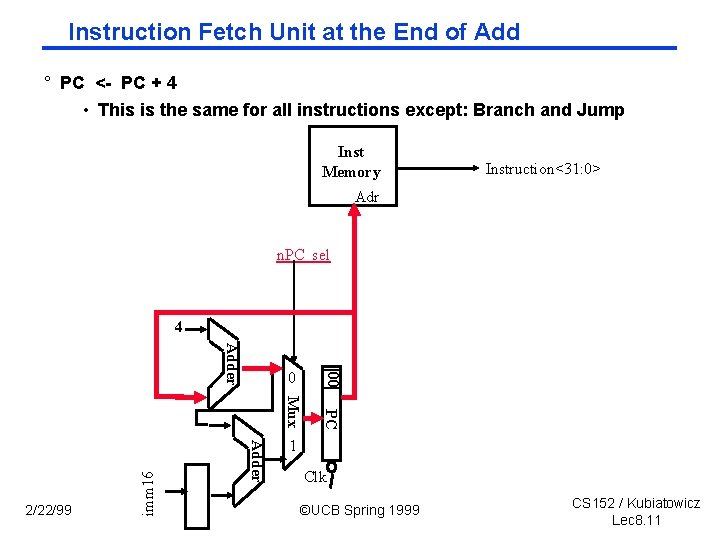

Instruction Fetch Unit at the End of Add ° PC <- PC + 4 • This is the same for all instructions except: Branch and Jump Inst Memory Instruction<31: 0> Adr n. PC_sel 4 Adder 00 0 imm 16 PC Mux Adder 2/22/99 1 Clk ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 11

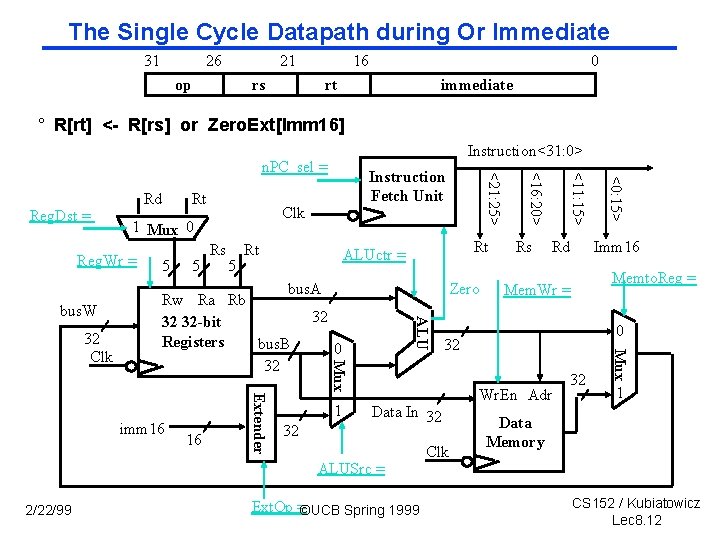

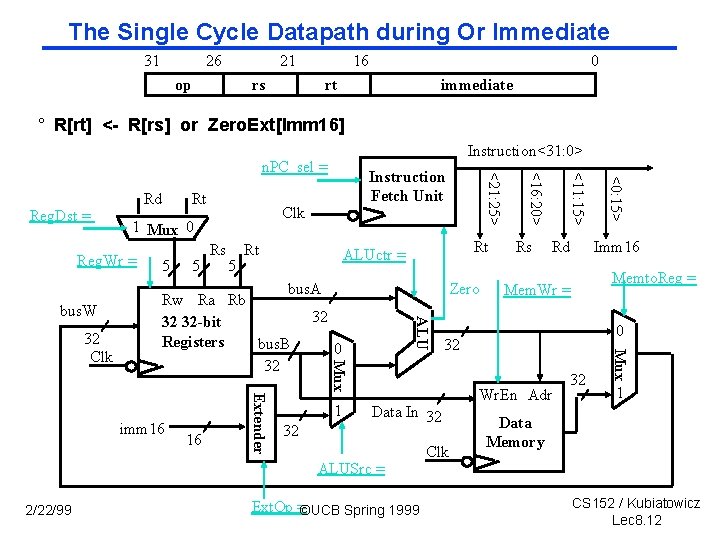

The Single Cycle Datapath during Or Immediate 31 26 21 op 16 rs 0 rt immediate ° R[rt] <- R[rs] or Zero. Ext[Imm 16] Instruction<31: 0> 1 Mux 0 Reg. Wr = 5 5 Rs 5 Rt Rt ALUctr = bus. A 0 1 32 2/22/99 Ext. Op =©UCB Spring 1999 Imm 16 Memto. Reg = Mem. Wr = 0 32 Data In 32 ALUSrc = Rd Clk Wr. En Adr 32 Mux 16 Extender imm 16 32 Mux 32 Clk Rw Ra Rb 32 32 -bit Registers bus. B 32 ALU bus. W Zero Rs <0: 15> Clk <11: 15> Rt <21: 25> Reg. Dst = Rd Instruction Fetch Unit <16: 20> n. PC_sel = 1 Data Memory CS 152 / Kubiatowicz Lec 8. 12

The Single Cycle Datapath during Load 31 26 21 op 16 rs 0 rt immediate ° R[rt] <- Data Memory {R[rs] + Sign. Ext[imm 16]} bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rt Zero 32 2/22/99 Ext. Op = 1 ©UCB Spring 1999 Imm 16 Memto. Reg = 1 Mem. Wr = 0 0 32 Data In 32 ALUSrc = 1 Rd Clk Mux ALU 16 Extender imm 16 1 Rs <0: 15> 5 ALUctr = Add Rt <11: 15> 5 Rs Mux 32 Clk 1 Mux 0 Reg. Wr = 1 5 bus. W Rt <16: 20> Reg. Dst = 0 Rd Instruction Fetch Unit <21: 25> n. PC_sel= +4 Instruction<31: 0> 1 Wr. En Adr Data Memory 32 CS 152 / Kubiatowicz Lec 8. 14

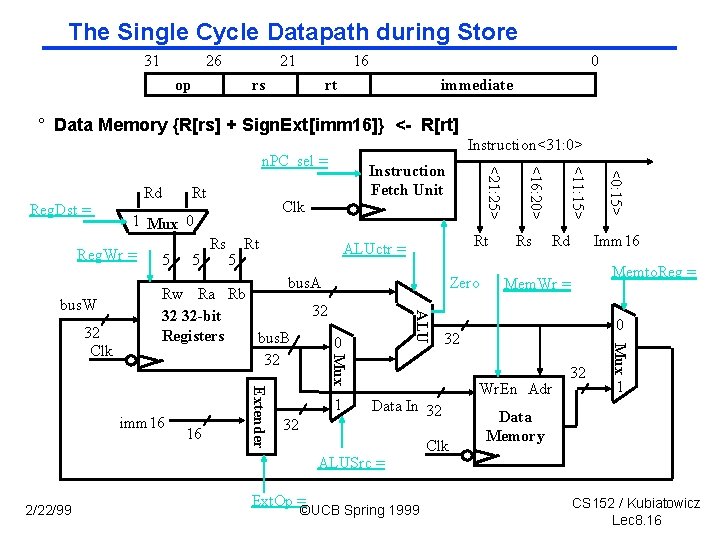

Questions and Administrative Matters ° Tomorrow: select groups for labs 4 --7. • Unbalanced sections. Volunteers to come to afternoon? • If you don’t come to section tomorrow, you may end up in random group. ° Midterm next Wednesday 3/3: • 5: 30 pm to 8: 30 pm, 277 Cory Hall • Make-up quiz on Tuesday • No class on that day ° Midterm reminders: • Pencil, calculator, two 8. 5” x 11” pages of handwritten notes • Sit in every other chair, every other row (odd row & odd seat) ° Meet at La. Val’s pizza after the midterm - Need a headcount. How many are definitely coming? 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 15

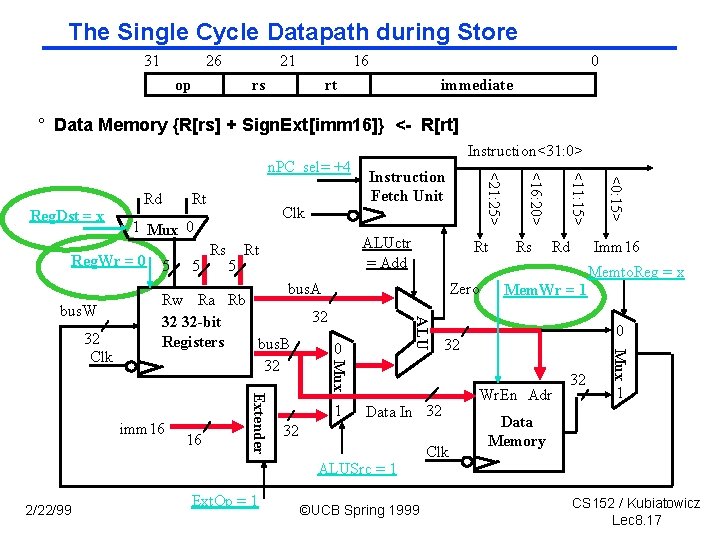

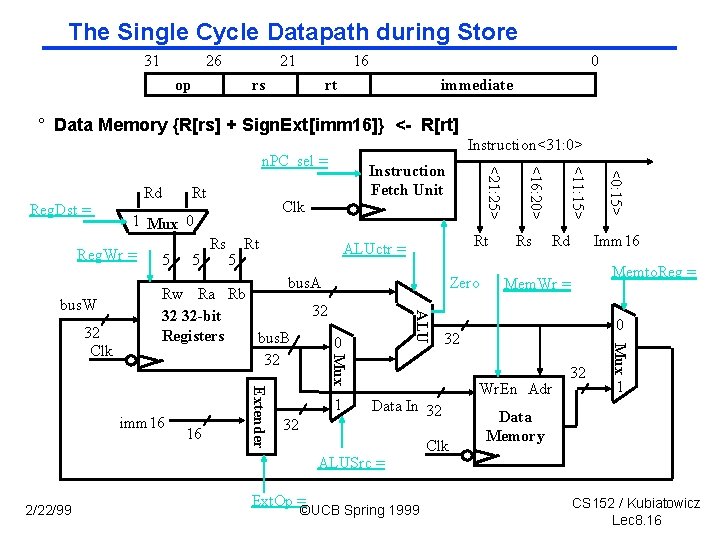

The Single Cycle Datapath during Store 31 26 21 op 16 rs 0 rt immediate ° Data Memory {R[rs] + Sign. Ext[imm 16]} <- R[rt] Instruction<31: 0> 1 Mux 0 Reg. Wr = 5 5 Rs 5 Rt Rt ALUctr = bus. A 0 1 32 2/22/99 Ext. Op = ©UCB Spring 1999 Imm 16 Memto. Reg = Mem. Wr = 0 32 Data In 32 ALUSrc = Rd Clk Wr. En Adr 32 Mux 16 Extender imm 16 32 Mux 32 Clk Rw Ra Rb 32 32 -bit Registers bus. B 32 ALU bus. W Zero Rs <0: 15> Clk <11: 15> Rt <21: 25> Reg. Dst = Rd Instruction Fetch Unit <16: 20> n. PC_sel = 1 Data Memory CS 152 / Kubiatowicz Lec 8. 16

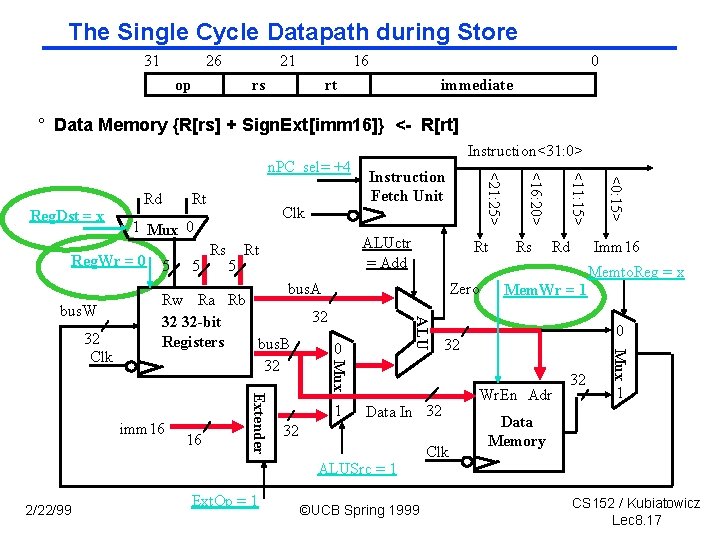

The Single Cycle Datapath during Store 31 26 21 op 16 rs 0 rt immediate ° Data Memory {R[rs] + Sign. Ext[imm 16]} <- R[rt] Zero ALU 16 Extender imm 16 1 2/22/99 Ext. Op = 1 32 ©UCB Spring 1999 Rd Imm 16 Memto. Reg = x Mem. Wr = 1 0 32 Data In 32 ALUSrc = 1 Rs Clk Wr. En Adr 32 Mux bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rt <0: 15> 5 ALUctr = Add Rt <11: 15> 5 Rs Mux 32 Clk 1 Mux 0 Reg. Wr = 0 5 bus. W Rt <16: 20> Reg. Dst = x Rd Instruction Fetch Unit <21: 25> n. PC_sel= +4 Instruction<31: 0> 1 Data Memory CS 152 / Kubiatowicz Lec 8. 17

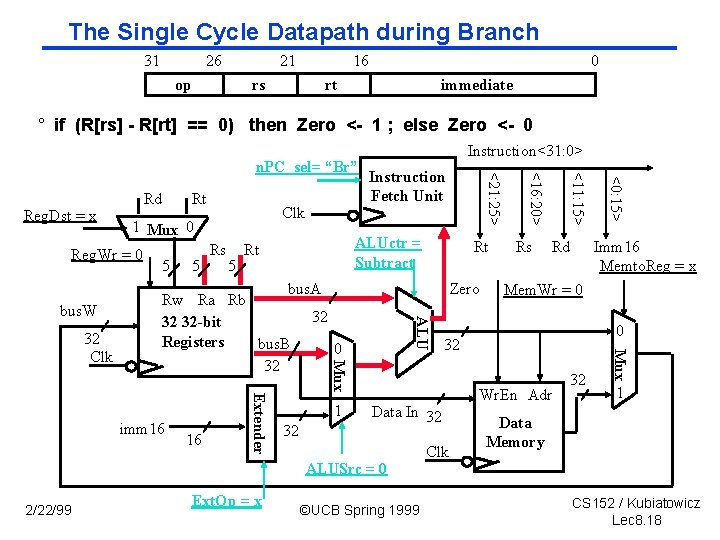

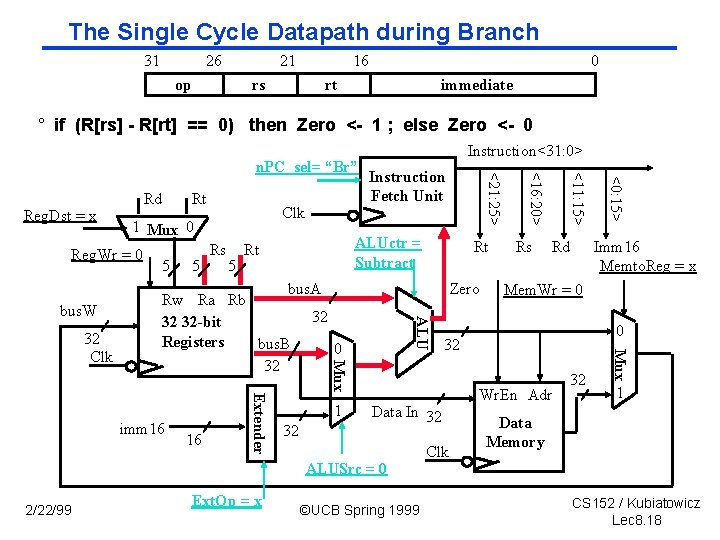

The Single Cycle Datapath during Branch 31 26 21 op 16 rs 0 rt immediate ° if (R[rs] - R[rt] == 0) then Zero <- 1 ; else Zero <- 0 5 Zero ALU 16 Extender imm 16 1 32 2/22/99 Ext. Op = x ©UCB Spring 1999 Rd Imm 16 Memto. Reg = x Mem. Wr = 0 0 32 Data In 32 ALUSrc = 0 Rs Clk Wr. En Adr 32 Mux bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rt <0: 15> 5 ALUctr = Subtract Rt <11: 15> 5 Rs Mux 32 Clk 1 Mux 0 Reg. Wr = 0 bus. W Rt <16: 20> Reg. Dst = x Rd Instruction Fetch Unit <21: 25> n. PC_sel= “Br” Instruction<31: 0> 1 Data Memory CS 152 / Kubiatowicz Lec 8. 18

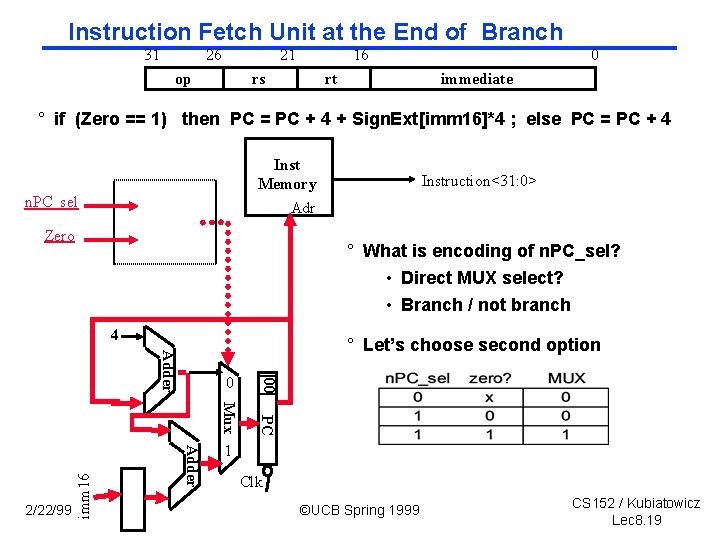

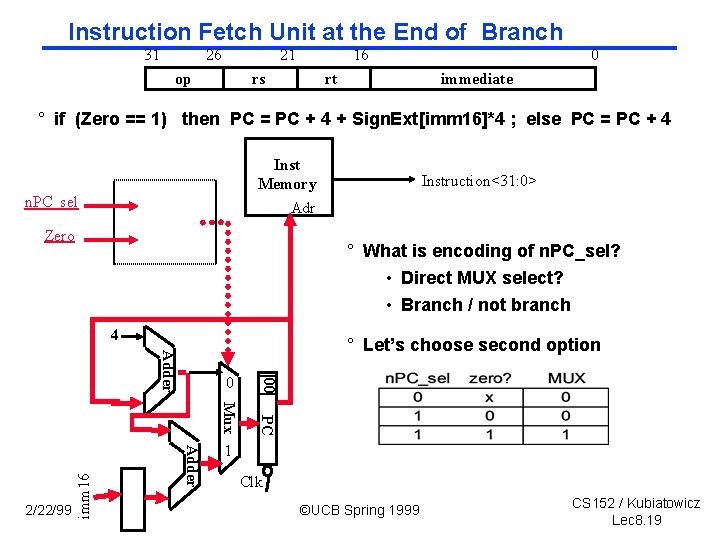

Instruction Fetch Unit at the End of Branch 31 26 21 op 16 rs rt 0 immediate ° if (Zero == 1) then PC = PC + 4 + Sign. Ext[imm 16]*4 ; else PC = PC + 4 Inst Memory n. PC_sel Adr Zero ° What is encoding of n. PC_sel? • Direct MUX select? • Branch / not branch 4 0 PC Mux Adder imm 16 00 ° Let’s choose second option Adder 2/22/99 Instruction<31: 0> 1 Clk ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 19

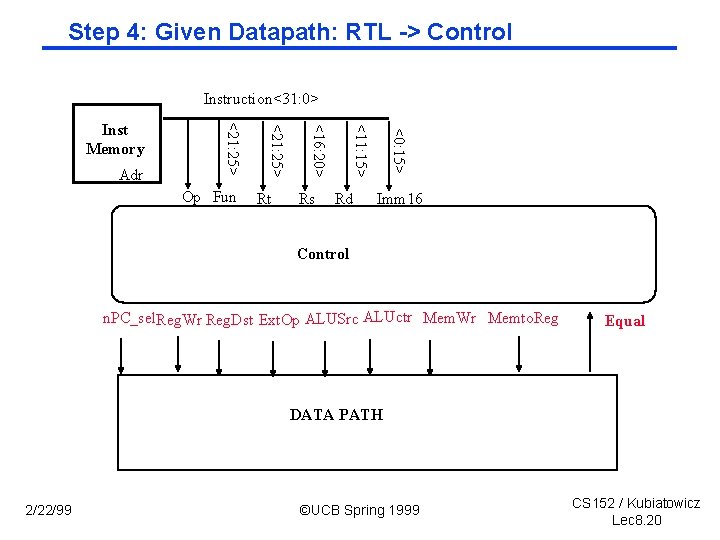

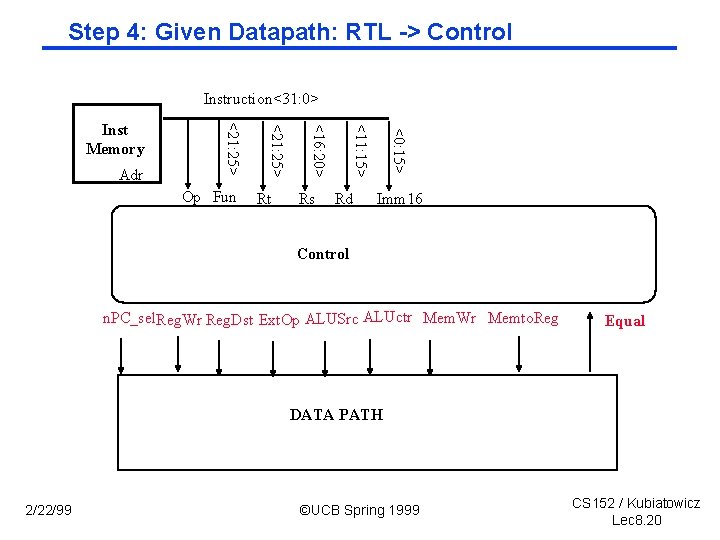

Step 4: Given Datapath: RTL -> Control Instruction<31: 0> Rd <0: 15> Rs <11: 15> Rt <16: 20> Op Fun <21: 25> Adr <21: 25> Inst Memory Imm 16 Control n. PC_sel. Reg. Wr Reg. Dst Ext. Op ALUSrc ALUctr Mem. Wr Memto. Reg Equal DATA PATH 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 20

![A Summary of Control Signals inst Register Transfer ADD Rrd Rrs Rrt A Summary of Control Signals inst Register Transfer ADD R[rd] <– R[rs] + R[rt];](https://slidetodoc.com/presentation_image/7d02e29aef4e2c030cf3edfba146a457/image-20.jpg)

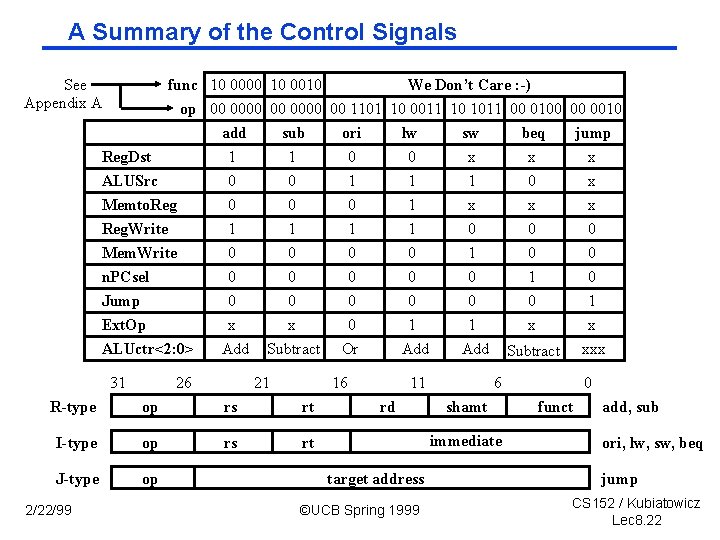

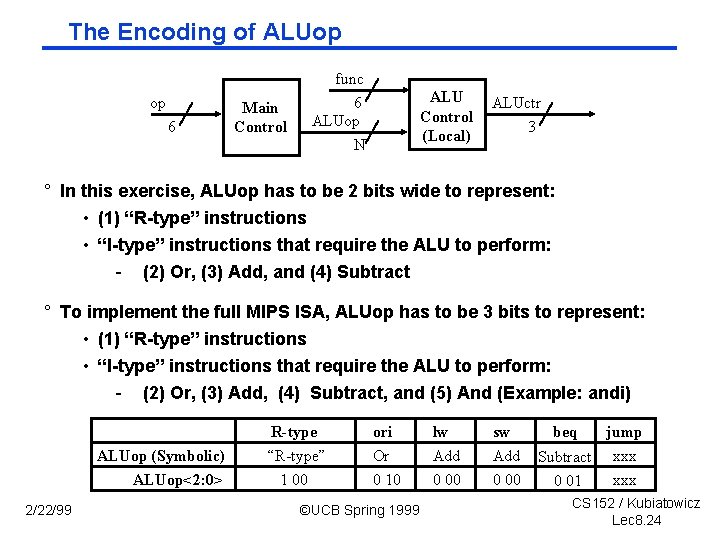

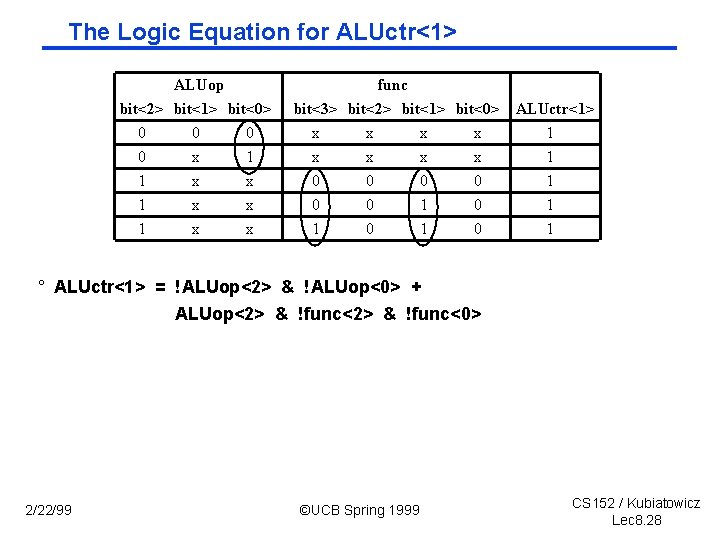

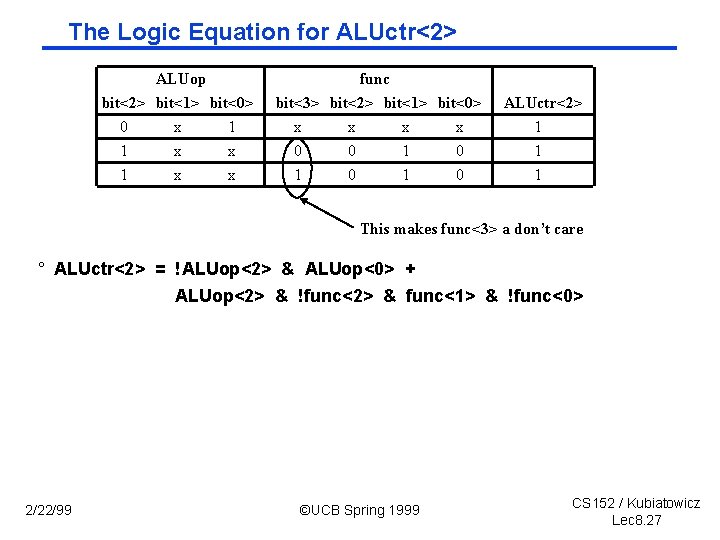

A Summary of Control Signals inst Register Transfer ADD R[rd] <– R[rs] + R[rt]; PC <– PC + 4 ALUsrc = Reg. B, ALUctr = “add”, Reg. Dst = rd, Reg. Wr, n. PC_sel = “+4” SUB R[rd] <– R[rs] – R[rt]; PC <– PC + 4 ALUsrc = Reg. B, ALUctr = “sub”, Reg. Dst = rd, Reg. Wr, n. PC_sel = “+4” ORi R[rt] <– R[rs] + zero_ext(Imm 16); PC <– PC + 4 ALUsrc = Im, Extop = “Z”, ALUctr = “or”, Reg. Dst = rt, Reg. Wr, n. PC_sel = “+4” LOAD R[rt] <– MEM[ R[rs] + sign_ext(Imm 16)]; PC <– PC + 4 ALUsrc = Im, Extop = “Sn”, ALUctr = “add”, Memto. Reg, Reg. Dst = rt, Reg. Wr, n. PC_sel = “+4” STORE MEM[ R[rs] + sign_ext(Imm 16)] <– R[rs]; PC <– PC + 4 ALUsrc = Im, Extop = “Sn”, ALUctr = “add”, Mem. Wr, n. PC_sel = “+4” BEQ if ( R[rs] == R[rt] ) then PC <– PC + sign_ext(Imm 16)] || 00 else PC <– PC + 4 n. PC_sel = “Br”, ALUctr = “sub” 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 21

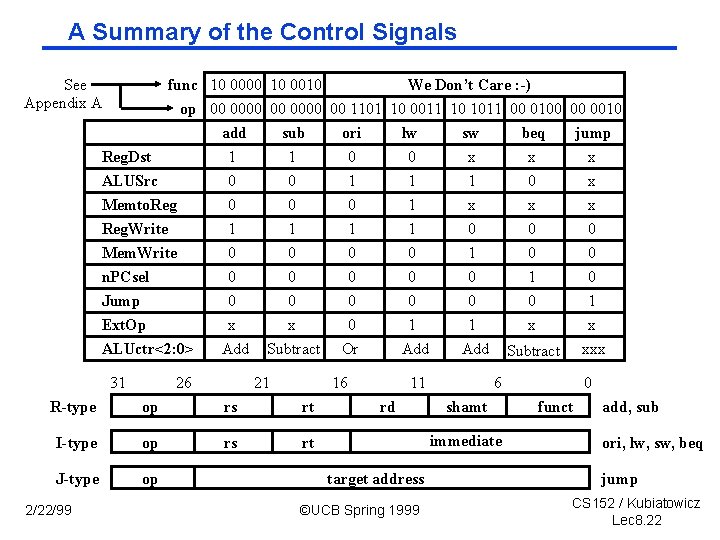

A Summary of the Control Signals See Appendix A func 10 0000 10 0010 We Don’t Care : -) op 00 0000 00 1101 10 0011 10 1011 00 0100 00 0010 add sub ori lw sw beq jump Reg. Dst 1 1 0 0 x x x ALUSrc 0 0 1 1 1 0 x Memto. Reg 0 0 0 1 x x x Reg. Write 1 1 0 0 0 Mem. Write 0 0 1 0 0 n. PCsel 0 0 0 1 0 Jump 0 0 0 1 Ext. Op x x 0 1 1 x x ALUctr<2: 0> Add Subtract Or Add Subtract xxx 31 26 21 16 R-type op rs rt I-type op rs rt J-type op 2/22/99 11 rd 6 shamt immediate target address ©UCB Spring 1999 0 funct add, sub ori, lw, sw, beq jump CS 152 / Kubiatowicz Lec 8. 22

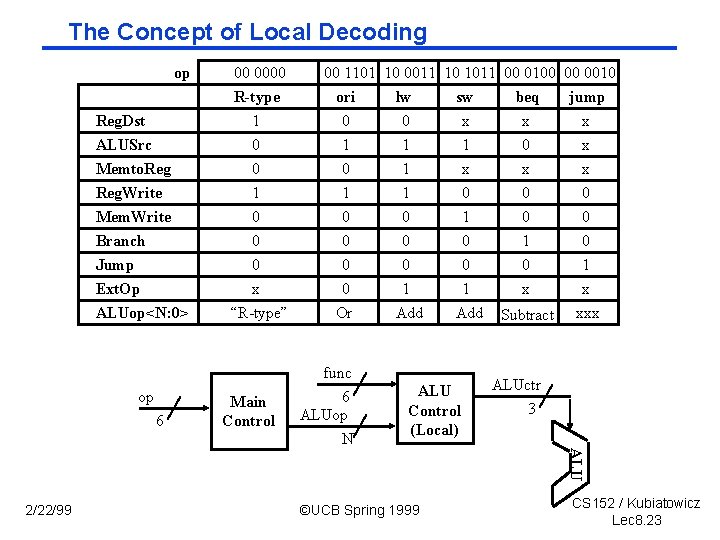

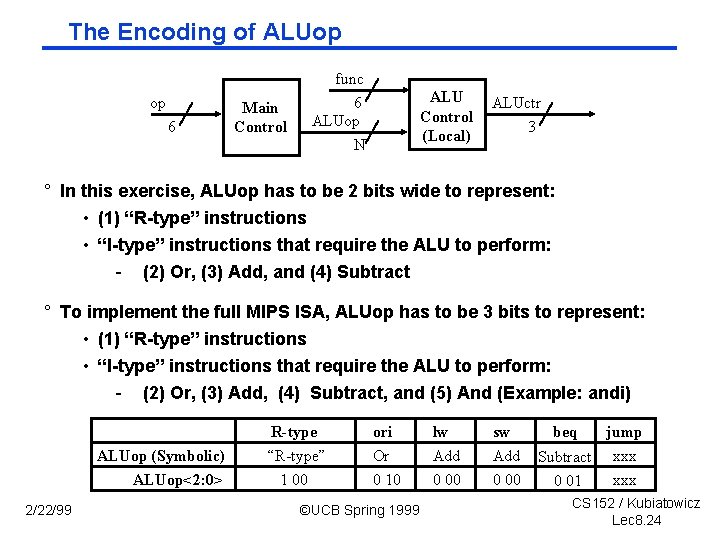

The Concept of Local Decoding op Reg. Dst ALUSrc Memto. Reg 00 0000 R-type 1 0 0 Reg. Write 1 1 1 0 0 0 x “R-type” 0 0 Or 0 0 0 1 Add 1 0 0 1 Add 0 1 0 x 0 0 1 x xxx Mem. Write Branch Jump Ext. Op ALUop<N: 0> op 6 func 6 ALUop N ALU Control (Local) ©UCB Spring 1999 Subtract ALUctr 3 ALU 2/22/99 Main Control 00 1101 10 0011 10 1011 00 0100 00 0010 ori lw sw beq jump 0 0 x x x 1 1 1 0 x 0 1 x x x CS 152 / Kubiatowicz Lec 8. 23

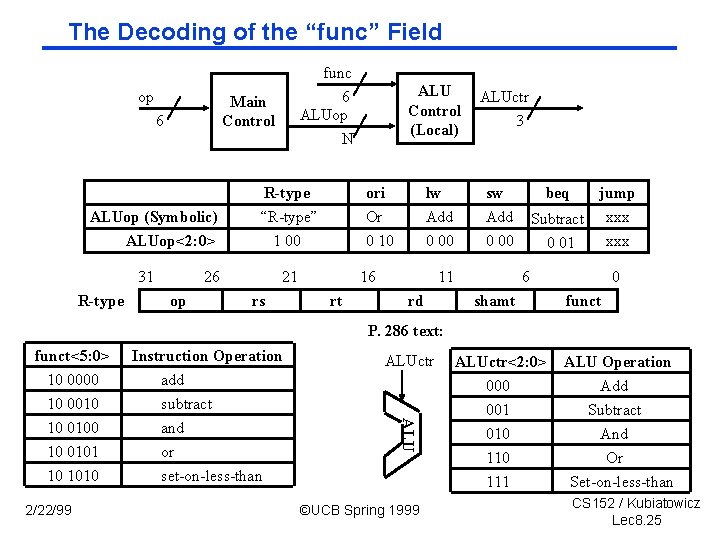

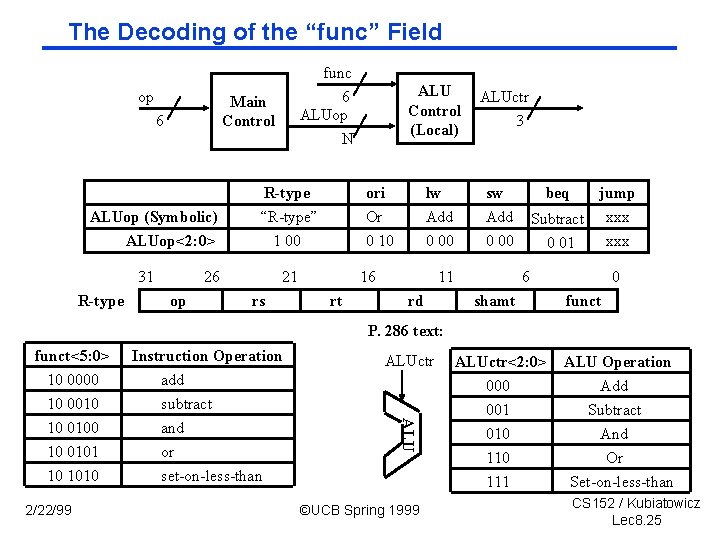

The Encoding of ALUop op 6 Main Control func 6 ALUop N ALU Control (Local) ALUctr 3 ° In this exercise, ALUop has to be 2 bits wide to represent: • (1) “R-type” instructions • “I-type” instructions that require the ALU to perform: - (2) Or, (3) Add, and (4) Subtract ° To implement the full MIPS ISA, ALUop has to be 3 bits to represent: • (1) “R-type” instructions • “I-type” instructions that require the ALU to perform: - (2) Or, (3) Add, (4) Subtract, and (5) And (Example: andi) ALUop (Symbolic) ALUop<2: 0> 2/22/99 R-type “R-type” 1 00 ori Or 0 10 ©UCB Spring 1999 lw Add 0 00 sw Add 0 00 beq jump Subtract xxx 0 01 CS 152 / Kubiatowicz Lec 8. 24

The Decoding of the “func” Field op Main Control 6 ALUop (Symbolic) ALUop<2: 0> 31 R-type func 6 ALUop N ALUctr 3 R-type ori lw sw “R-type” 1 00 Or 0 10 Add 0 00 26 op ALU Control (Local) 21 rs 16 rt 11 rd beq jump Subtract 0 01 xxx 6 shamt 0 funct P. 286 text: funct<5: 0> Instruction Operation add subtract 10 0100 10 0101 and or 10 1010 set-on-less-than 2/22/99 ALU 10 0000 10 0010 ALUctr ©UCB Spring 1999 ALUctr<2: 0> 000 ALU Operation Add 001 010 Subtract And 110 111 Or Set-on-less-than CS 152 / Kubiatowicz Lec 8. 25

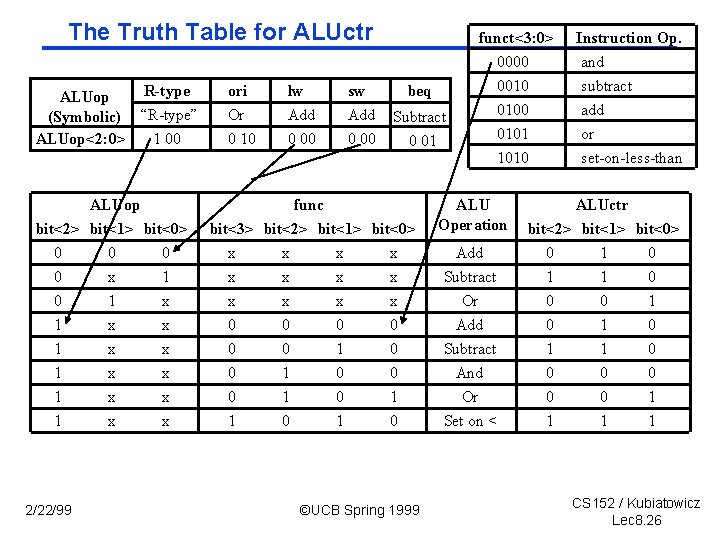

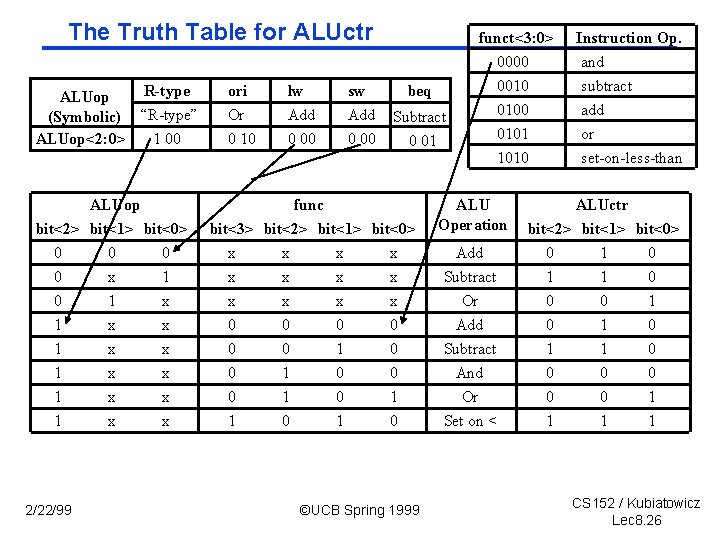

The Truth Table for ALUctr R-type ALUop (Symbolic) “R-type” ALUop<2: 0> 1 00 ALUop bit<2> bit<1> bit<0> 0 0 0 1 1 1 2/22/99 x 1 x x x ori Or 0 10 lw Add 0 00 sw Add 0 00 x x 0 0 1 1 0 x x 0 1 0 0 1 Instruction Op. and 0010 0101 1010 subtract add or set-on-less-than beq Subtract 0 01 func bit<3> bit<2> bit<1> bit<0> x x x 0 0 1 funct<3: 0> 0000 x x 0 0 0 1 0 ©UCB Spring 1999 ALU Operation Add Subtract Or Add Subtract And Or Set on < ALUctr bit<2> bit<1> bit<0> 0 1 0 0 1 1 0 0 1 0 0 0 1 1 CS 152 / Kubiatowicz Lec 8. 26

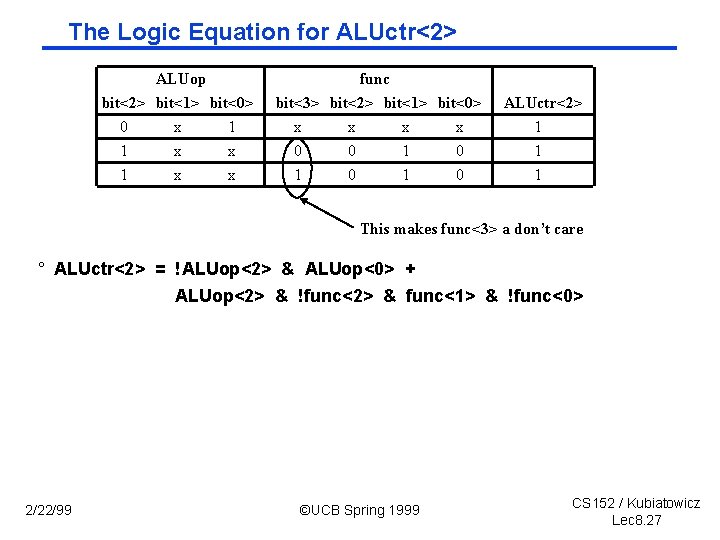

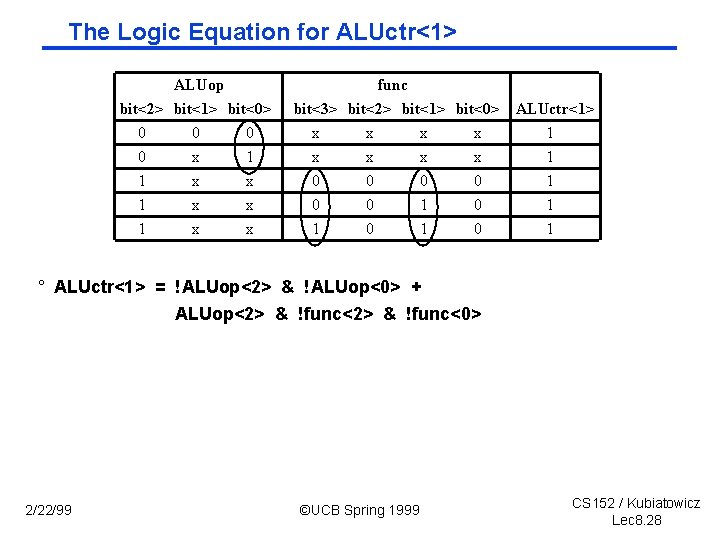

The Logic Equation for ALUctr<2> ALUop bit<2> bit<1> bit<0> 0 x 1 1 x x func bit<3> bit<2> bit<1> bit<0> x x 0 0 1 0 1 0 ALUctr<2> 1 1 1 This makes func<3> a don’t care ° ALUctr<2> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<2> & func<1> & !func<0> 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 27

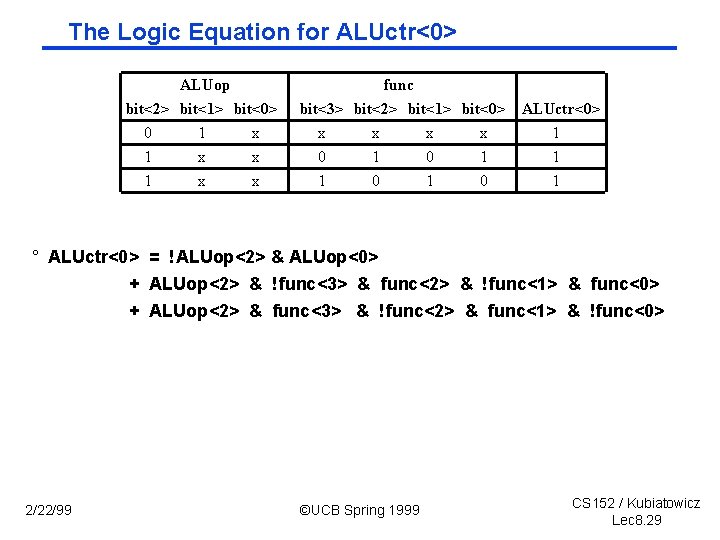

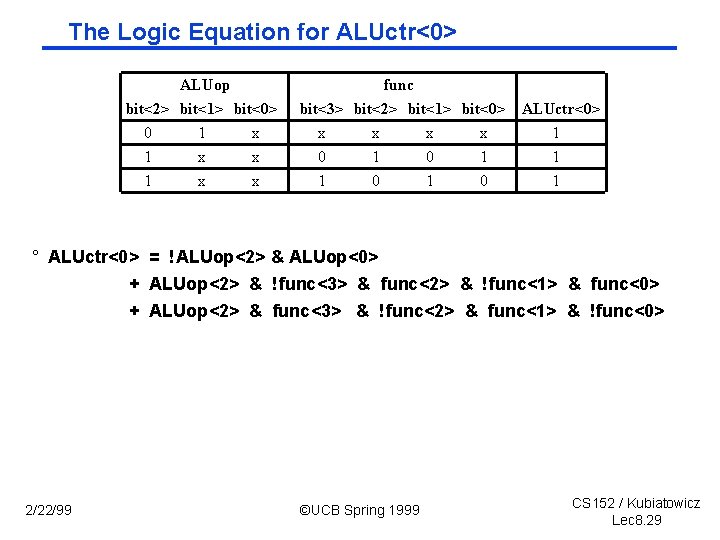

The Logic Equation for ALUctr<1> ALUop bit<2> bit<1> bit<0> 0 0 x 1 1 x x func bit<3> bit<2> bit<1> bit<0> ALUctr<1> x x x x 1 0 0 1 1 0 1 ° ALUctr<1> = !ALUop<2> & !ALUop<0> + ALUop<2> & !func<0> 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 28

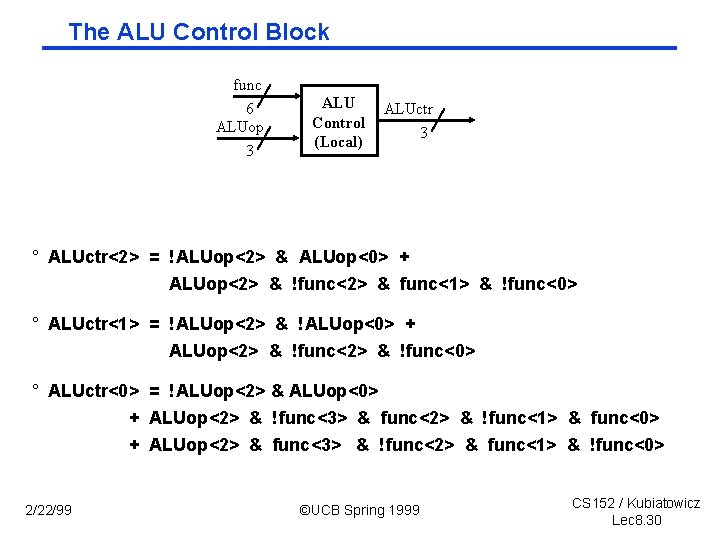

The Logic Equation for ALUctr<0> ALUop bit<2> bit<1> bit<0> 0 1 x x func bit<3> bit<2> bit<1> bit<0> ALUctr<0> x x 1 0 1 1 1 0 1 ° ALUctr<0> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<3> & func<2> & !func<1> & func<0> + ALUop<2> & func<3> & !func<2> & func<1> & !func<0> 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 29

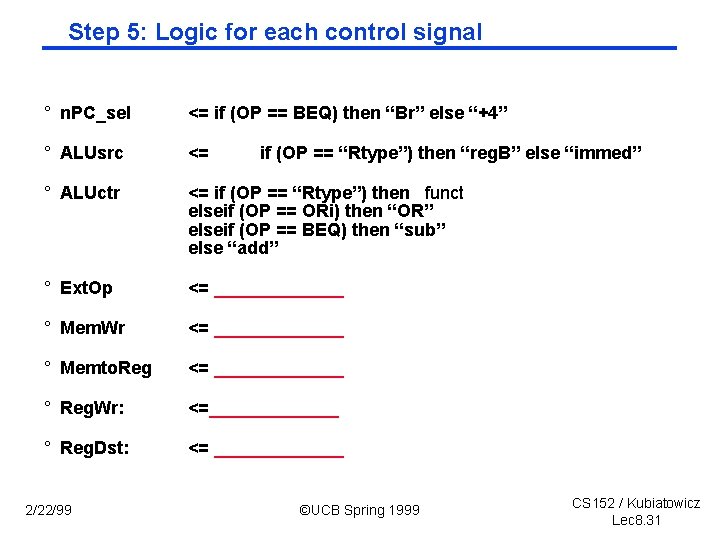

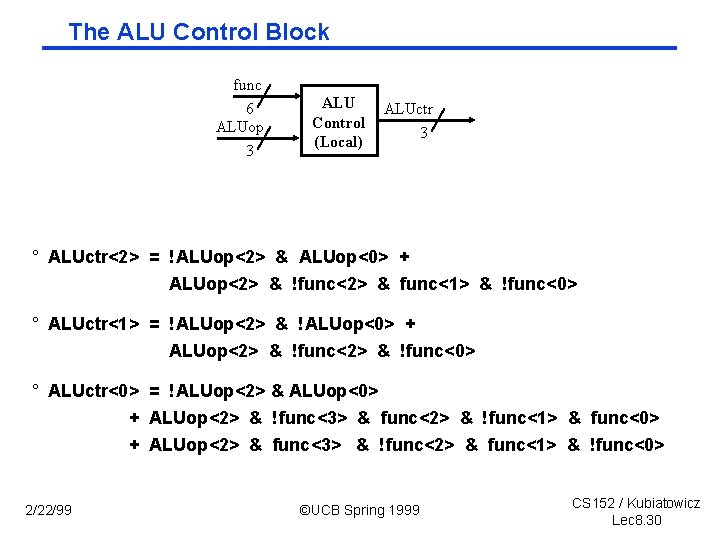

The ALU Control Block func 6 ALUop 3 ALU Control (Local) ALUctr 3 ° ALUctr<2> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<2> & func<1> & !func<0> ° ALUctr<1> = !ALUop<2> & !ALUop<0> + ALUop<2> & !func<0> ° ALUctr<0> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<3> & func<2> & !func<1> & func<0> + ALUop<2> & func<3> & !func<2> & func<1> & !func<0> 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 30

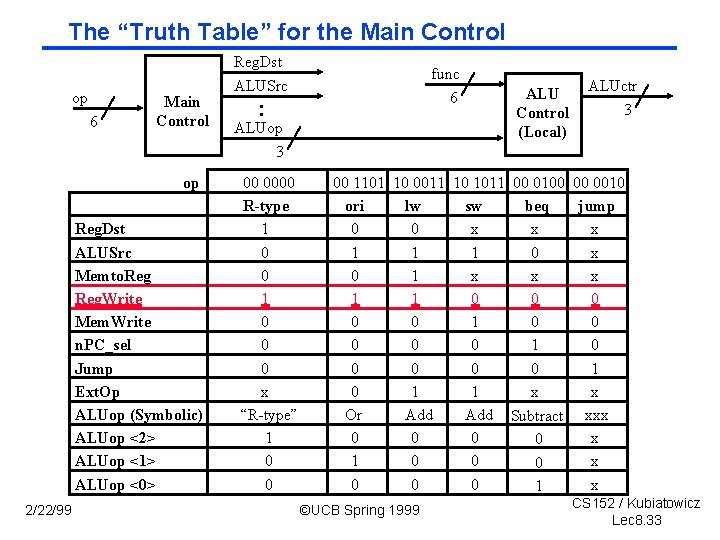

Step 5: Logic for each control signal ° n. PC_sel <= if (OP == BEQ) then “Br” else “+4” ° ALUsrc <= ° ALUctr <= if (OP == “Rtype”) then funct elseif (OP == ORi) then “OR” elseif (OP == BEQ) then “sub” else “add” ° Ext. Op <= _______ ° Mem. Wr <= _______ ° Memto. Reg <= _______ ° Reg. Wr: <=_______ ° Reg. Dst: <= _______ 2/22/99 if (OP == “Rtype”) then “reg. B” else “immed” ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 31

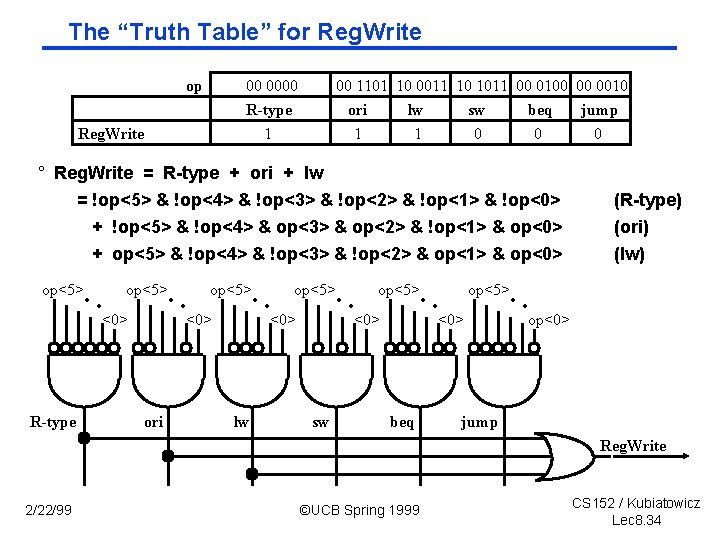

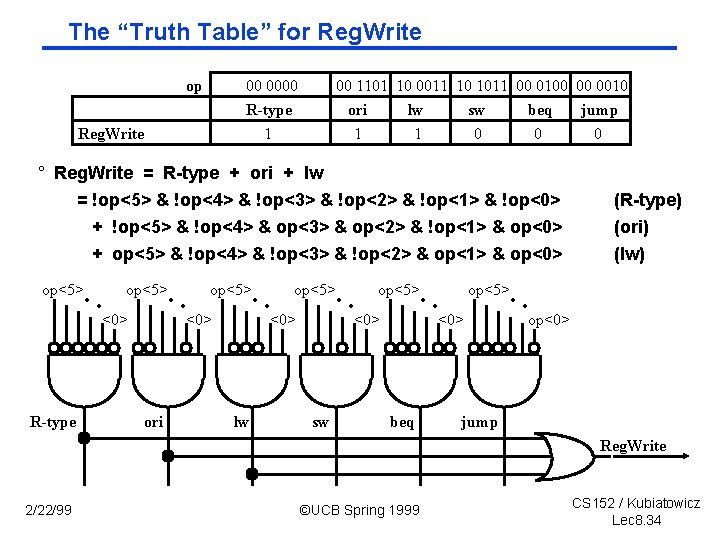

The “Truth Table” for the Main Control op 6 Main Control Reg. Dst ALUSrc func 6 : ALUop ALU Control (Local) ALUctr 3 3 op Reg. Dst ALUSrc Memto. Reg. Write Mem. Write n. PC_sel Jump Ext. Op ALUop (Symbolic) ALUop <2> ALUop <1> ALUop <0> 2/22/99 00 0000 R-type 1 0 0 0 x “R-type” 1 0 0 00 1101 10 0011 10 1011 00 0100 00 0010 ori lw sw beq jump 0 0 x x x 1 1 1 0 x 0 1 x x x 1 1 0 0 0 0 0 1 1 x x Or Add Subtract xxx 0 0 0 x 0 1 0 0 x 1 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 33

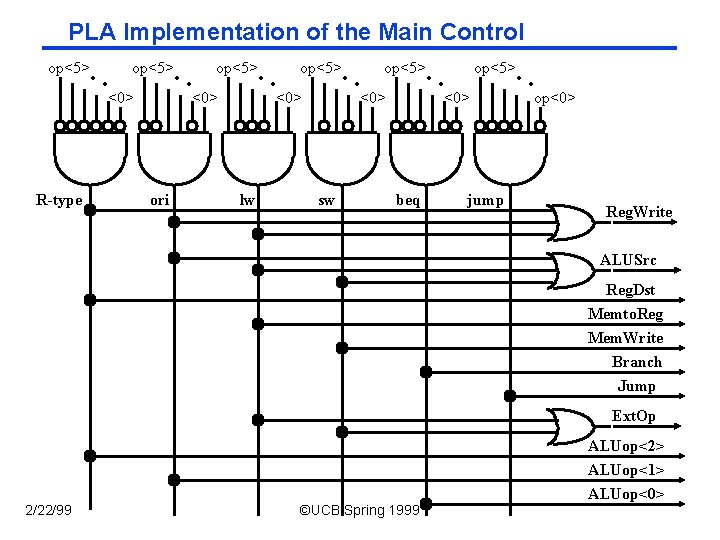

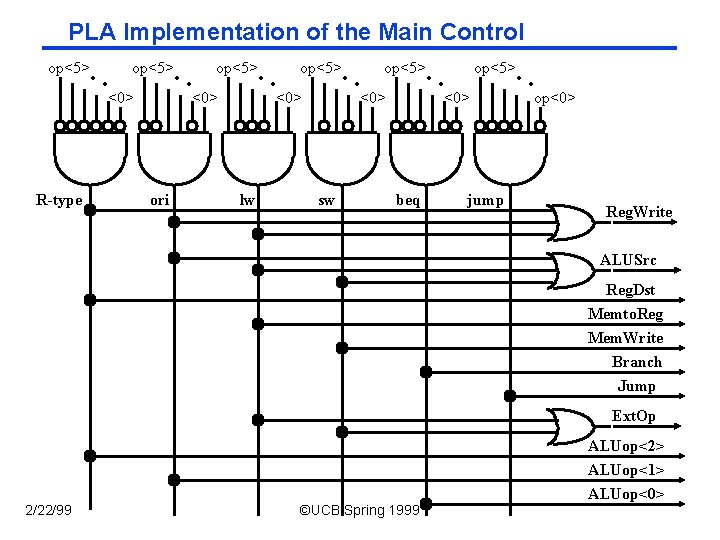

The “Truth Table” for Reg. Write op 00 0000 R-type 1 Reg. Write 00 1101 10 0011 10 1011 00 0100 00 0010 ori lw sw beq jump 1 1 0 0 0 ° Reg. Write = R-type + ori + lw = !op<5> & !op<4> & !op<3> & !op<2> & !op<1> & !op<0> + !op<5> & !op<4> & op<3> & op<2> & !op<1> & op<0> + op<5> & !op<4> & !op<3> & !op<2> & op<1> & op<0> . . op<5> <0> R-type . . op<5> <0> ori . . op<5> <0> lw . . op<5> <0> sw . . op<5> <0> beq (R-type) (ori) (lw) op<0> jump Reg. Write 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 34

PLA Implementation of the Main Control . . op<5> <0> R-type . . op<5> <0> ori . . op<5> <0> lw . . op<5> <0> sw <0> beq . . op<5> jump op<0> Reg. Write ALUSrc Reg. Dst Memto. Reg Mem. Write Branch Jump Ext. Op ALUop<2> ALUop<1> ALUop<0> 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 35

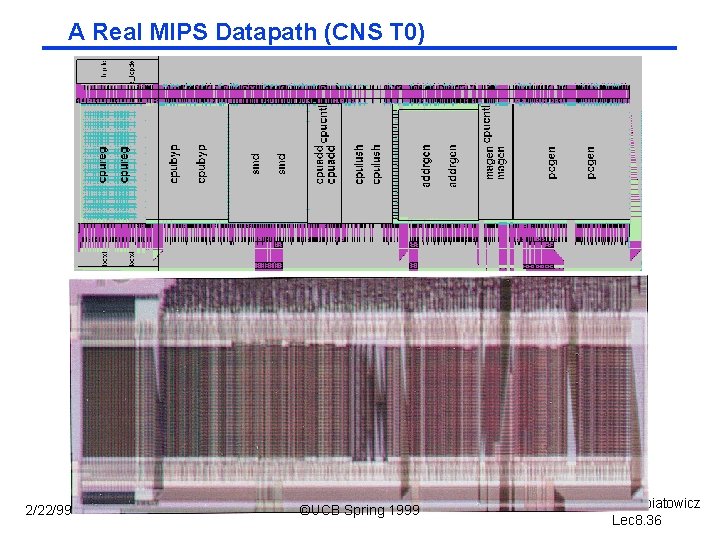

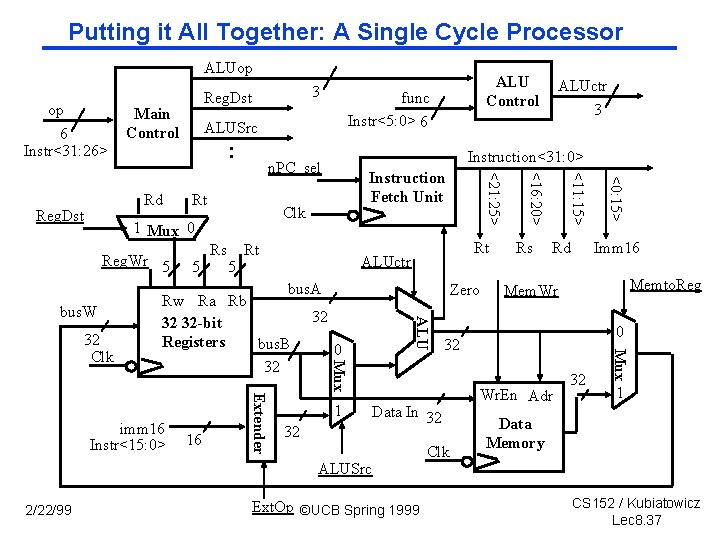

A Real MIPS Datapath (CNS T 0) 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 36

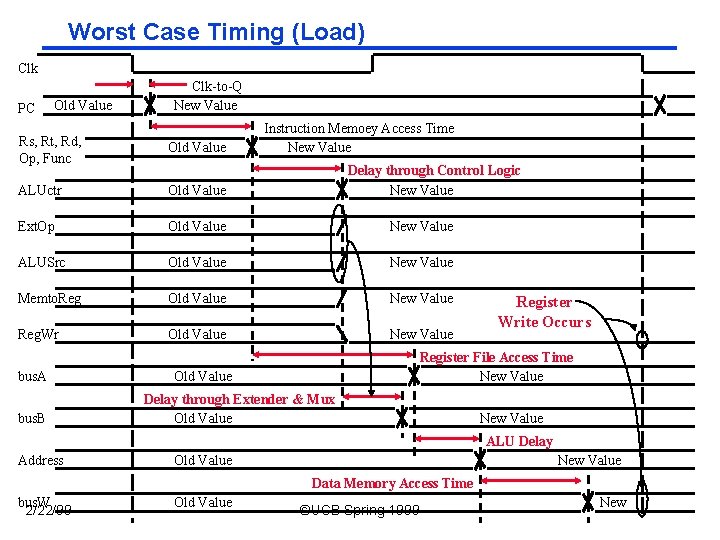

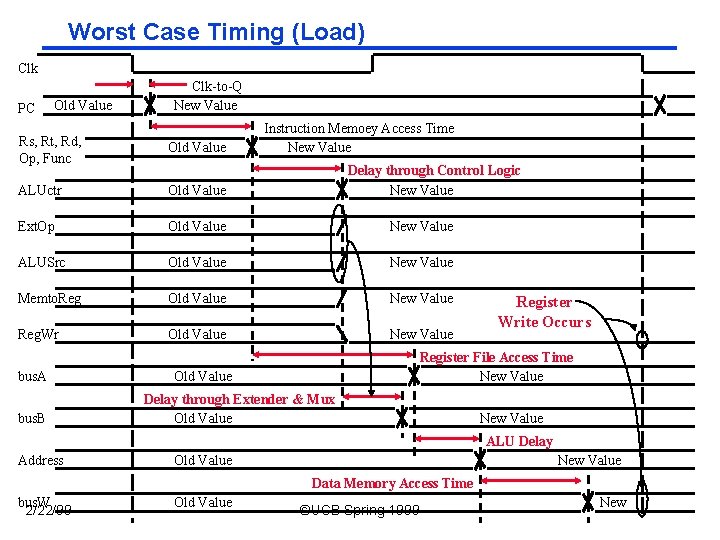

Putting it All Together: A Single Cycle Processor ALUop op 6 Instr<31: 26> Rs 5 Rt Rt ALUctr bus. A 0 1 32 2/22/99 Ext. Op ©UCB Spring 1999 Imm 16 Memto. Reg Mem. Wr 0 32 Data In 32 ALUSrc Rd Clk Wr. En Adr 32 Mux 16 Extender imm 16 Instr<15: 0> 32 Mux 32 Clk Rw Ra Rb 32 32 -bit Registers bus. B 32 ALU bus. W Zero Rs <0: 15> Clk <11: 15> 5 Instruction Fetch Unit <16: 20> Rt ALUctr 3 Instruction<31: 0> n. PC_sel 1 Mux 0 Reg. Wr 5 func Instr<5: 0> 6 ALUSrc : ALU Control <21: 25> Reg. Dst Main Control Rd 3 1 Data Memory CS 152 / Kubiatowicz Lec 8. 37

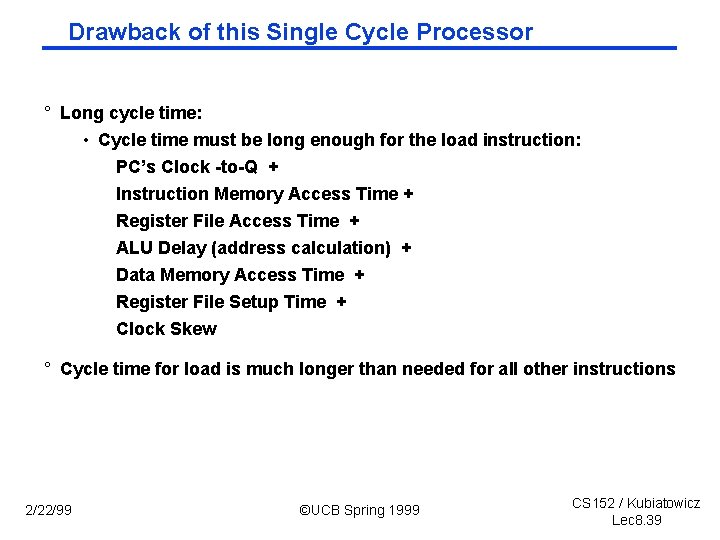

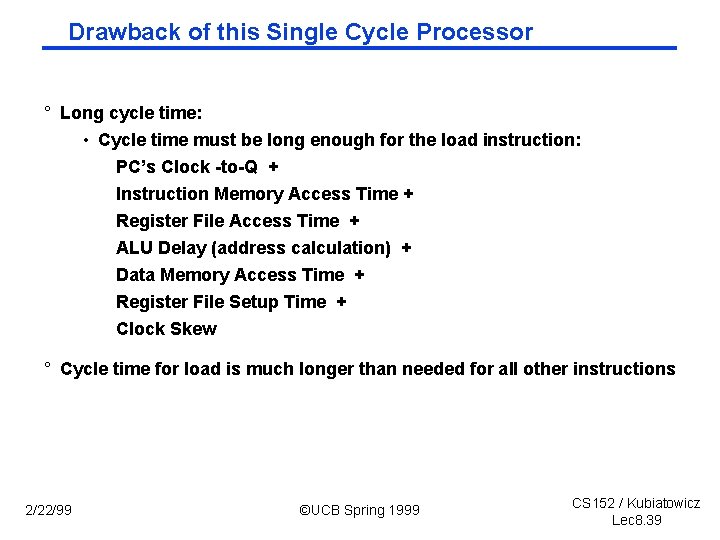

Worst Case Timing (Load) Clk PC Old Value Clk-to-Q New Value Instruction Memoey Access Time New Value Rs, Rt, Rd, Op, Func Old Value ALUctr Old Value Ext. Op Old Value New Value ALUSrc Old Value New Value Memto. Reg Old Value New Value Reg. Wr Old Value New Value bus. A bus. B Delay through Control Logic New Value Register Write Occurs Register File Access Time New Value Old Value Delay through Extender & Mux Old Value New Value ALU Delay Address Old Value New Value Data Memory Access Time bus. W 2/22/99 Old Value ©UCB Spring 1999 New CS 152 / Kubiatowicz Lec 8. 38

Drawback of this Single Cycle Processor ° Long cycle time: • Cycle time must be long enough for the load instruction: PC’s Clock -to-Q + Instruction Memory Access Time + Register File Access Time + ALU Delay (address calculation) + Data Memory Access Time + Register File Setup Time + Clock Skew ° Cycle time for load is much longer than needed for all other instructions 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 39

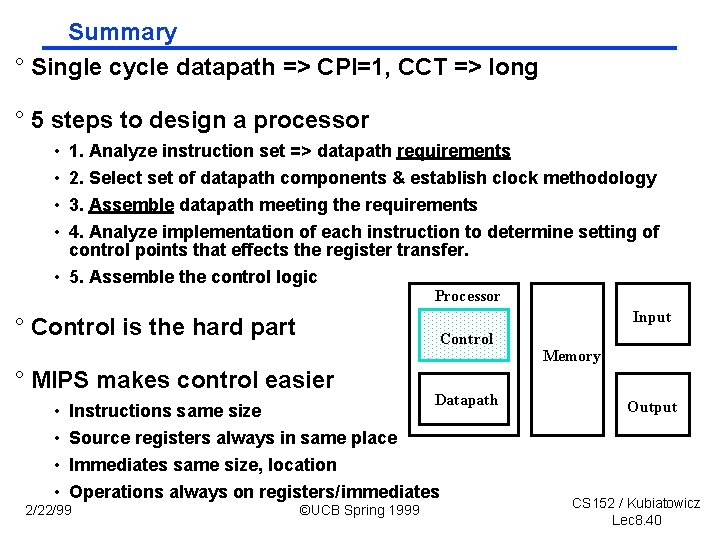

Summary ° Single cycle datapath => CPI=1, CCT => long ° 5 steps to design a processor • • 1. Analyze instruction set => datapath requirements 2. Select set of datapath components & establish clock methodology 3. Assemble datapath meeting the requirements 4. Analyze implementation of each instruction to determine setting of control points that effects the register transfer. • 5. Assemble the control logic Processor Input ° Control is the hard part Control ° MIPS makes control easier • • Instructions same size Datapath Memory Output Source registers always in same place Immediates same size, location Operations always on registers/immediates 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 40

Where to get more information? ° Chapter 5. 1 to 5. 3 of your text book: • David Patterson and John Hennessy, “Computer Organization & Design: The Hardware / Software Interface, ” Second Edition, Morgan Kaufman Publishers, San Mateo, California, 1998. ° One of the best Ph. D thesis on processor design: • Manolis Katevenis, “Reduced Instruction Set Computer Architecture for VLSI, ” Ph. D Dissertation, EECS, U C Berkeley, 1982. ° For a reference on the MIPS architecture: • Gerry Kane, “MIPS RISC Architecture, ” Prentice Hall. 2/22/99 ©UCB Spring 1999 CS 152 / Kubiatowicz Lec 8. 41