CS 152 Computer Architecture and Engineering Lecture 5

- Slides: 65

CS 152 Computer Architecture and Engineering Lecture 5 VHDL, Multiply, Shift September 13, 1999 John Kubiatowicz (http. cs. berkeley. edu/~kubitron) lecture slides: http: //www-inst. eecs. berkeley. edu/~cs 152/ 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 1

Today’s Outline ° Review of Last lecture ° Intro to VHDL ° Administrative Issues ° on-line lab notebook ° Designing a Multiplier ° Booth’s algorithm ° Shifters 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 2

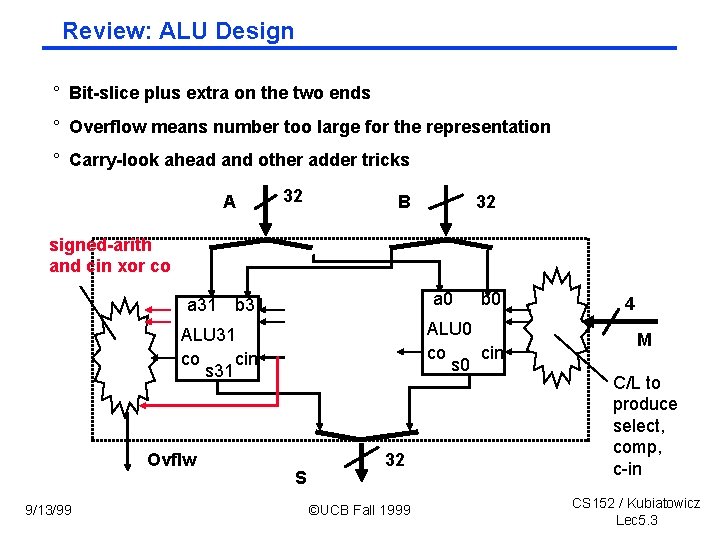

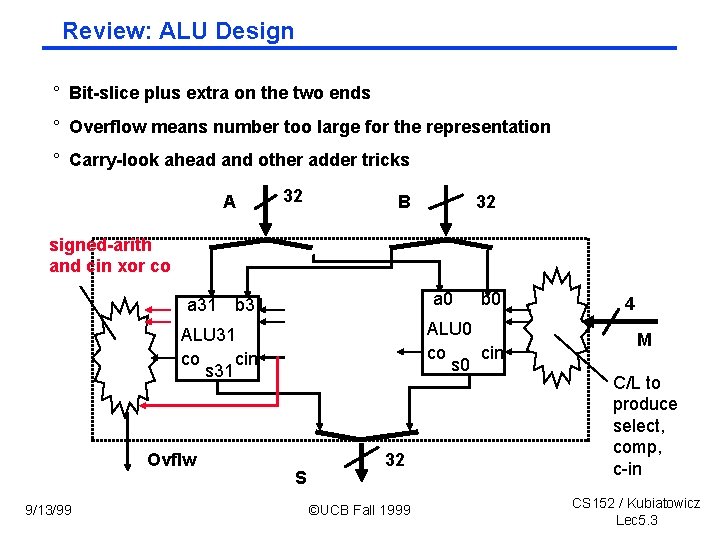

Review: ALU Design ° Bit-slice plus extra on the two ends ° Overflow means number too large for the representation ° Carry-look ahead and other adder tricks A 32 B 32 signed-arith and cin xor co a 0 a 31 b 31 ALU 0 co cin s 0 ALU 31 co cin s 31 Ovflw 9/13/99 b 0 S 32 ©UCB Fall 1999 4 M C/L to produce select, comp, c-in CS 152 / Kubiatowicz Lec 5. 3

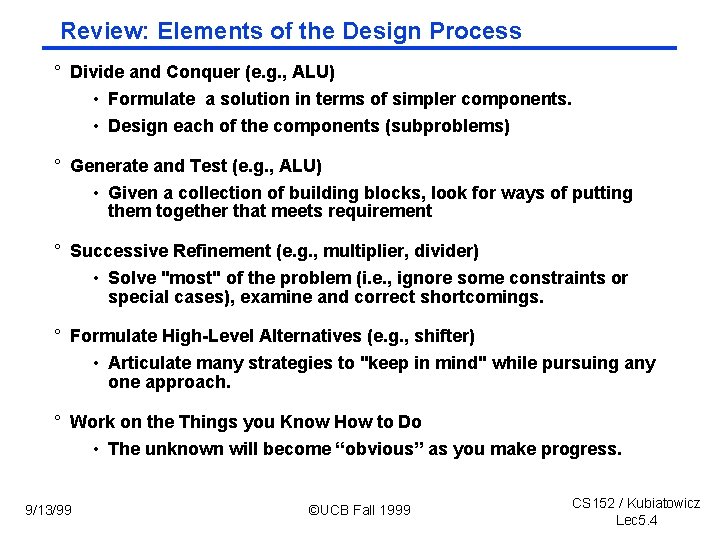

Review: Elements of the Design Process ° Divide and Conquer (e. g. , ALU) • Formulate a solution in terms of simpler components. • Design each of the components (subproblems) ° Generate and Test (e. g. , ALU) • Given a collection of building blocks, look for ways of putting them together that meets requirement ° Successive Refinement (e. g. , multiplier, divider) • Solve "most" of the problem (i. e. , ignore some constraints or special cases), examine and correct shortcomings. ° Formulate High-Level Alternatives (e. g. , shifter) • Articulate many strategies to "keep in mind" while pursuing any one approach. ° Work on the Things you Know How to Do • The unknown will become “obvious” as you make progress. 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 4

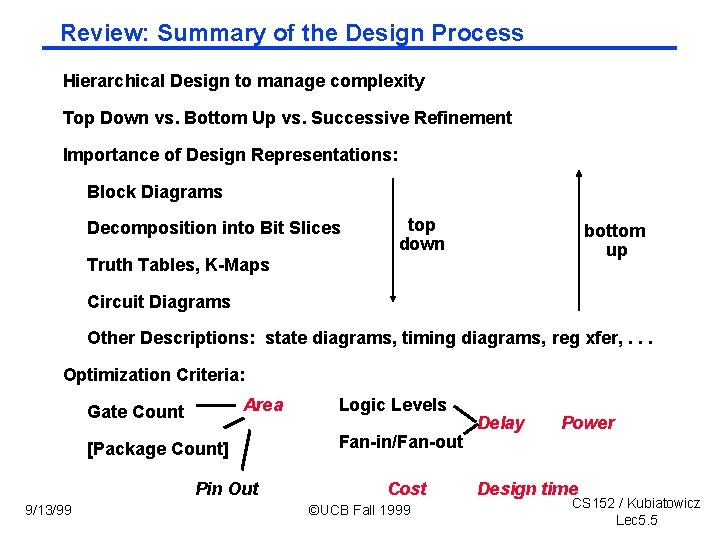

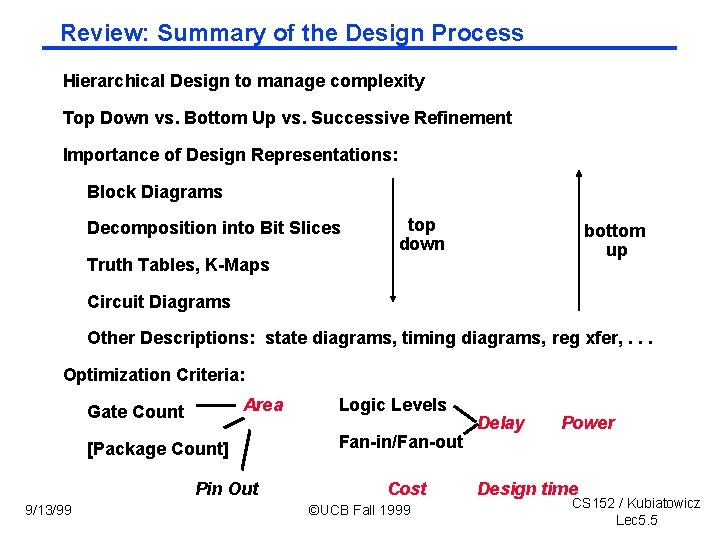

Review: Summary of the Design Process Hierarchical Design to manage complexity Top Down vs. Bottom Up vs. Successive Refinement Importance of Design Representations: Block Diagrams Decomposition into Bit Slices top down bottom up Truth Tables, K-Maps Circuit Diagrams Other Descriptions: state diagrams, timing diagrams, reg xfer, . . . Optimization Criteria: Area Gate Count [Package Count] Pin Out 9/13/99 Logic Levels Fan-in/Fan-out Cost ©UCB Fall 1999 Delay Power Design time CS 152 / Kubiatowicz Lec 5. 5

Why should you keep an design notebook? ° Keep track of the design decisions and the reasons behind them • Otherwise, it will be hard to debug and/or refine the design • Write it down so that can remember in long project: 2 weeks ->2 yrs • Others can review notebook to see what happened ° Record insights you have on certain aspect of the design as they come up ° Record of the different design & debug experiments • Memory can fail when very tired ° Industry practice: learn from others mistakes 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 6

Why do we keep it on-line? ° You need to force yourself to take notes • Open a window and leave an editor running while you work 1) Acts as reminder to take notes 2) Makes it easy to take notes • 1) + 2) => will actually do it ° Take advantage of the window system’s “cut and paste” features ° It is much easier to read your typing than your writing ° Also, paper log books have problems • Limited capacity => end up with many books • May not have right book with you at time vs. networked screens • Can use computer to search files/index files to find what looking for 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 7

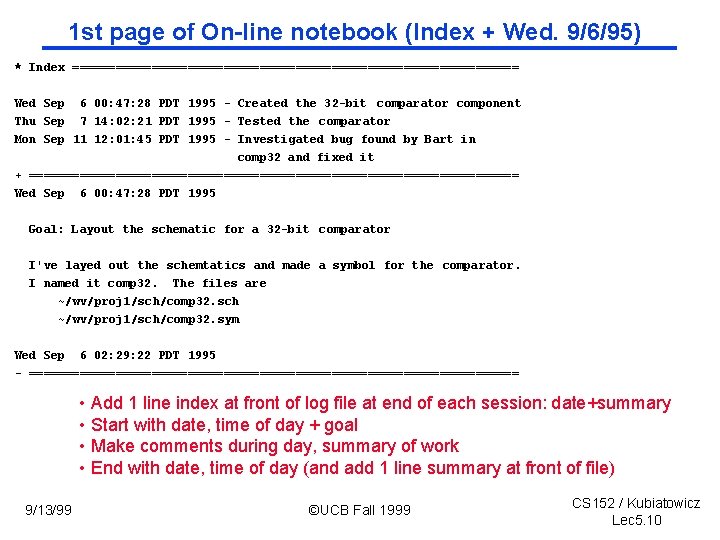

How should you do it? ° Keep it simple • DON’T make it so elaborate that you won’t use (fonts, layout, . . . ) ° Separate the entries by dates • type “date” command in another window and cut&paste ° Start day with problems going to work on today ° Record output of simulation into log with cut&paste; add date • May help sort out which version of simulation did what ° Record key email with cut&paste ° Record of what works & doesn’t helps team decide what went wrong after you left ° Index: write a one-line summary of what you did at end of each day 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 8

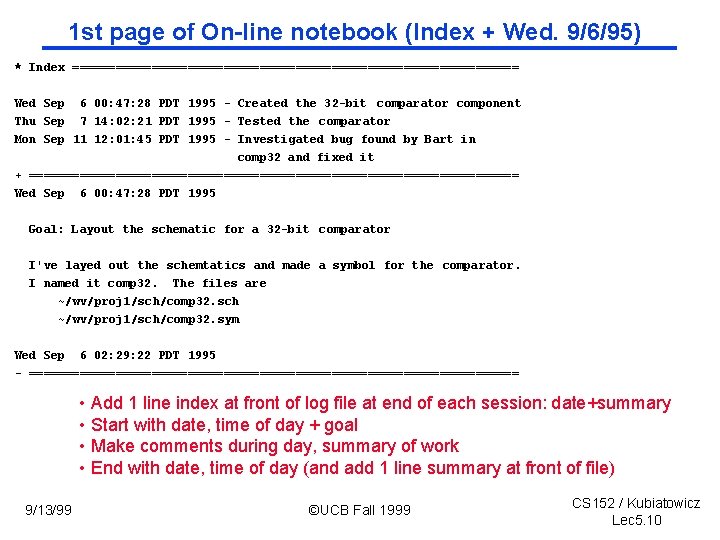

On-line Notebook Example Refer to the handout: “Example of On-Line Log Book” on cs 152 home page (handouts section) 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 9

1 st page of On-line notebook (Index + Wed. 9/6/95) * Index =============================== Wed Sep 6 00: 47: 28 PDT 1995 - Created the 32 -bit comparator component Thu Sep 7 14: 02: 21 PDT 1995 - Tested the comparator Mon Sep 11 12: 01: 45 PDT 1995 - Investigated bug found by Bart in comp 32 and fixed it + ================================== Wed Sep 6 00: 47: 28 PDT 1995 Goal: Layout the schematic for a 32 -bit comparator I've layed out the schemtatics and made a symbol for the comparator. I named it comp 32. The files are ~/wv/proj 1/sch/comp 32. sch ~/wv/proj 1/sch/comp 32. sym Wed Sep 6 02: 29: 22 PDT 1995 - ================================== • Add 1 line index at front of log file at end of each session: date+summary • Start with date, time of day + goal • Make comments during day, summary of work • End with date, time of day (and add 1 line summary at front of file) 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 10

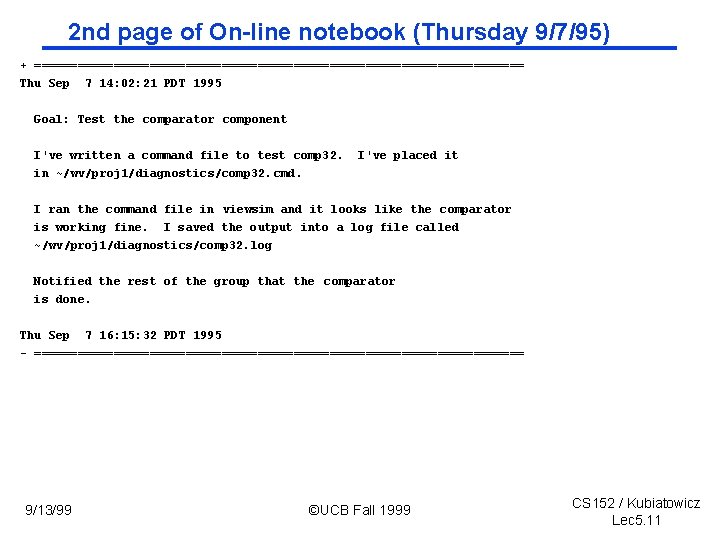

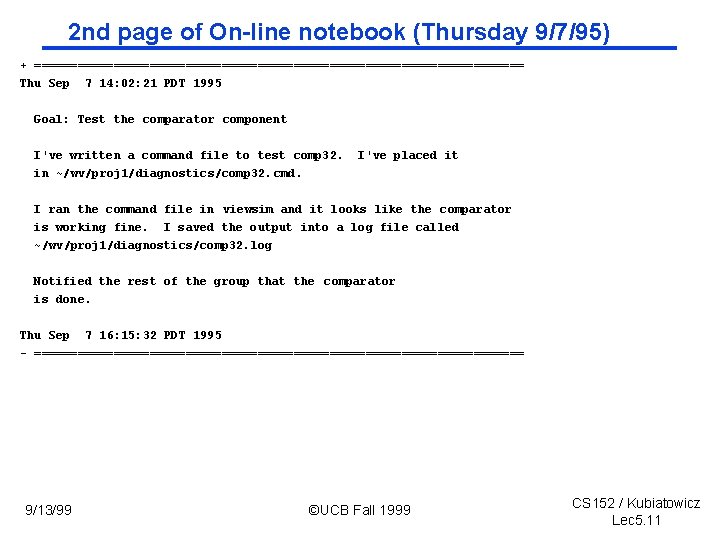

2 nd page of On-line notebook (Thursday 9/7/95) + ================================== Thu Sep 7 14: 02: 21 PDT 1995 Goal: Test the comparator component I've written a command file to test comp 32. in ~/wv/proj 1/diagnostics/comp 32. cmd. I've placed it I ran the command file in viewsim and it looks like the comparator is working fine. I saved the output into a log file called ~/wv/proj 1/diagnostics/comp 32. log Notified the rest of the group that the comparator is done. Thu Sep 7 16: 15: 32 PDT 1995 - ================================== 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 11

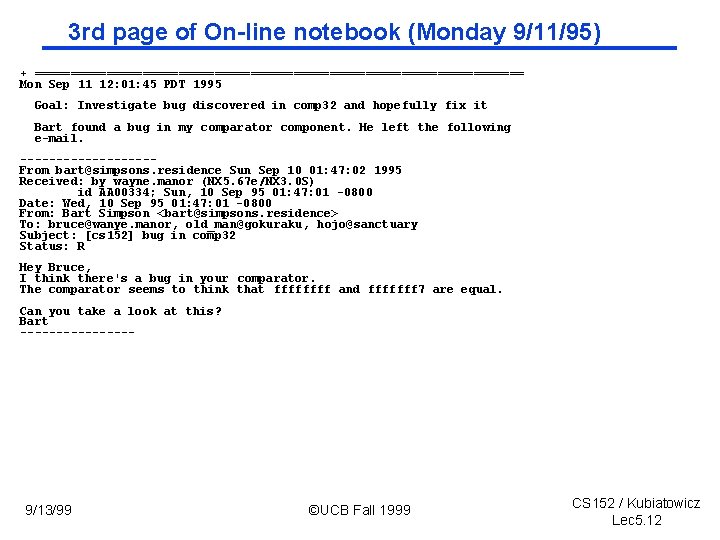

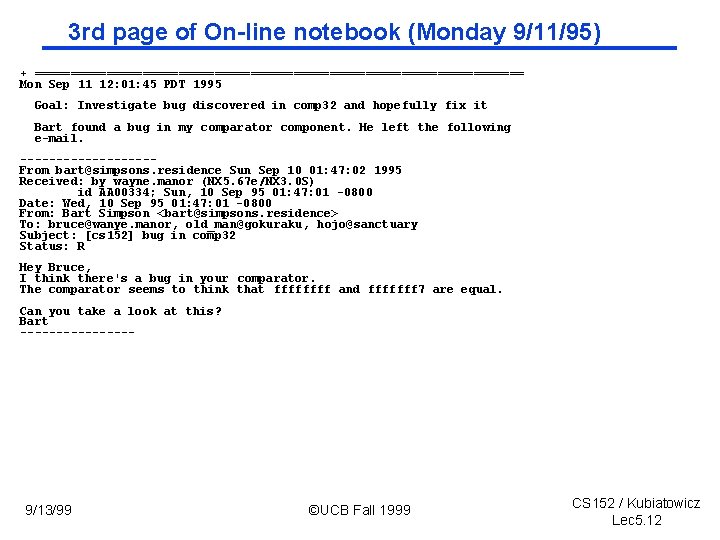

3 rd page of On-line notebook (Monday 9/11/95) + ================================== Mon Sep 11 12: 01: 45 PDT 1995 Goal: Investigate bug discovered in comp 32 and hopefully fix it Bart found a bug in my comparator component. He left the following e-mail. ---------From bart@simpsons. residence Sun Sep 10 01: 47: 02 1995 Received: by wayne. manor (NX 5. 67 e/NX 3. 0 S) id AA 00334; Sun, 10 Sep 95 01: 47: 01 -0800 Date: Wed, 10 Sep 95 01: 47: 01 -0800 From: Bart Simpson <bart@simpsons. residence> To: bruce@wanye. manor, old_man@gokuraku, hojo@sanctuary Subject: [cs 152] bug in comp 32 Status: R Hey Bruce, I think there's a bug in your comparator. The comparator seems to think that ffff and fffffff 7 are equal. Can you take a look at this? Bart -------- 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 12

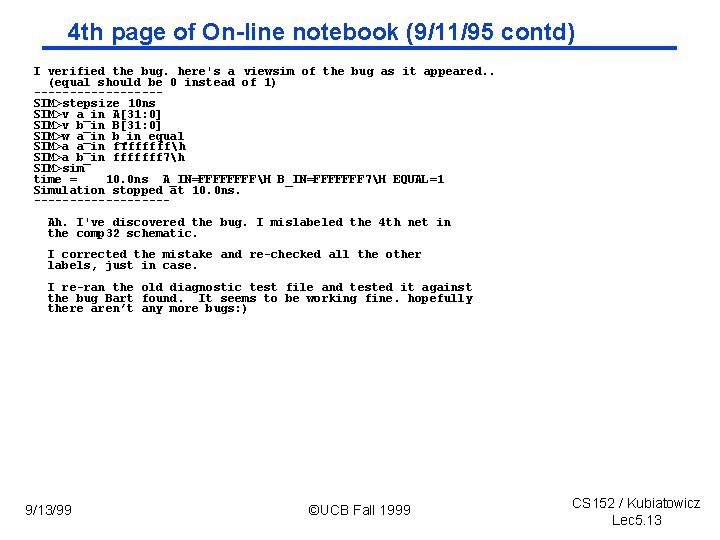

4 th page of On-line notebook (9/11/95 contd) I verified the bug. here's a viewsim of the bug as it appeared. . (equal should be 0 instead of 1) ---------SIM>stepsize 10 ns SIM>v a_in A[31: 0] SIM>v b_in B[31: 0] SIM>w a_in b_in equal SIM>a a_in ffffh SIM>a b_in fffffff 7h SIM>sim time = 10. 0 ns A_IN=FFFFH B_IN=FFFFFFF 7H EQUAL=1 Simulation stopped at 10. 0 ns. ---------Ah. I've discovered the bug. I mislabeled the 4 th net in the comp 32 schematic. I corrected the mistake and re-checked all the other labels, just in case. I re-ran the old diagnostic test file and tested it against the bug Bart found. It seems to be working fine. hopefully there aren’t any more bugs: ) 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 13

5 th page of On-line notebook (9/11/95 contd) On second inspectation of the whole layout, I think I can remove one level of gates in the design and make it go faster. But who cares! the comparator is not in the critical path right now. the delay through the ALU is dominating the critical path. so unless the ALU gets a lot faster, we can live with a less than optimal comparator. I e-mailed the group that the bug has been fixed Mon Sep 11 14: 03: 41 PDT 1995 - ================================== • Perhaps later critical path changes; what was idea to make compartor faster? Check log book! 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 14

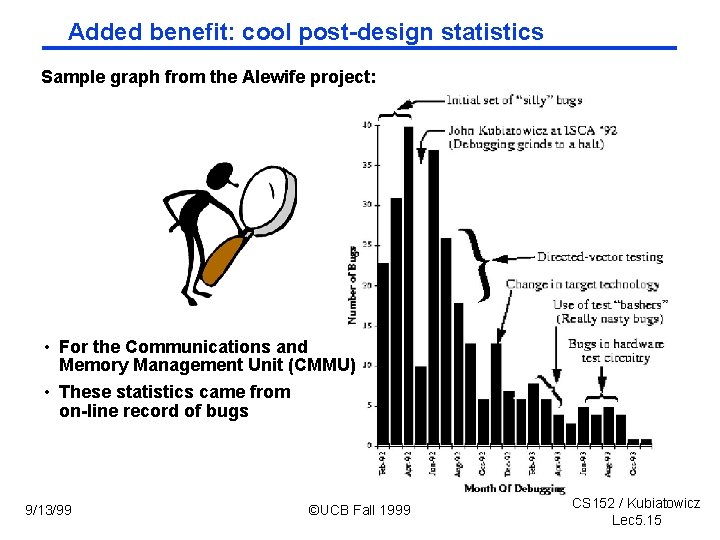

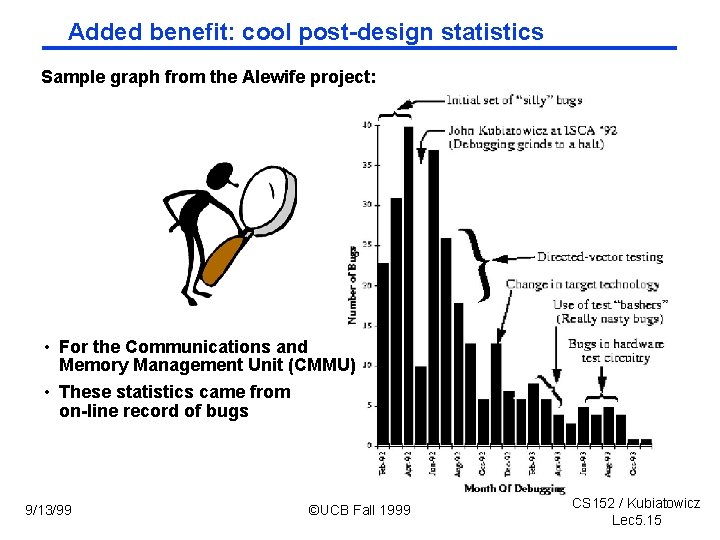

Added benefit: cool post-design statistics Sample graph from the Alewife project: • For the Communications and Memory Management Unit (CMMU) • These statistics came from on-line record of bugs 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 15

Representation Languages Hardware Representation Languages: Block Diagrams: FUs, Registers, & Dataflows Register Transfer Diagrams: Choice of busses to connect FUs, Regs Flowcharts State Diagrams Two different ways to describe sequencing & microoperations Fifth Representation "Language": Hardware Description Languages E. G. , ISP' VHDL Verilog hw modules described like programs with i/o ports, internal state, & parallel execution of assignment statements Descriptions in these languages can be used as input to simulation systems "software breadboard" synthesis systems generate hw from high level description "To Design is to Represent" 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 16

Simulation Before Construction "Physical Breadboarding" discrete components/lower scale integration preceeds actual construction of prototype verify initial design concept No longer possible as designs reach higher levels of integration! Simulation Before Construction high level constructs implies faster to construct play "what if" more easily limited performance accuracy, however 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 17

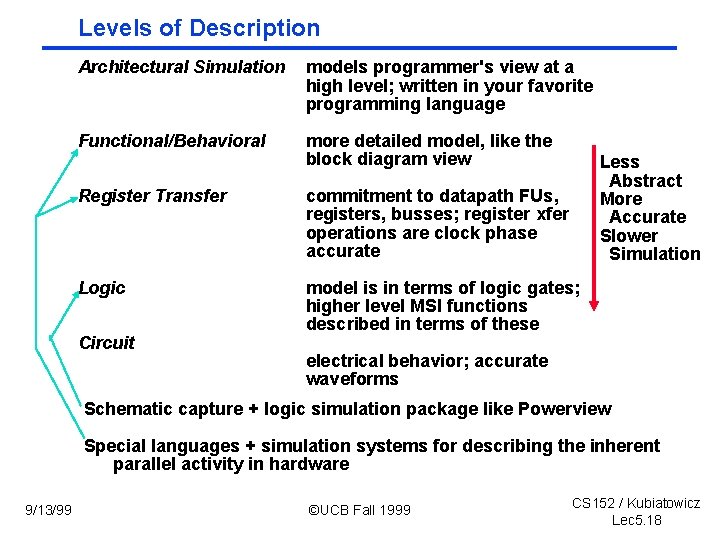

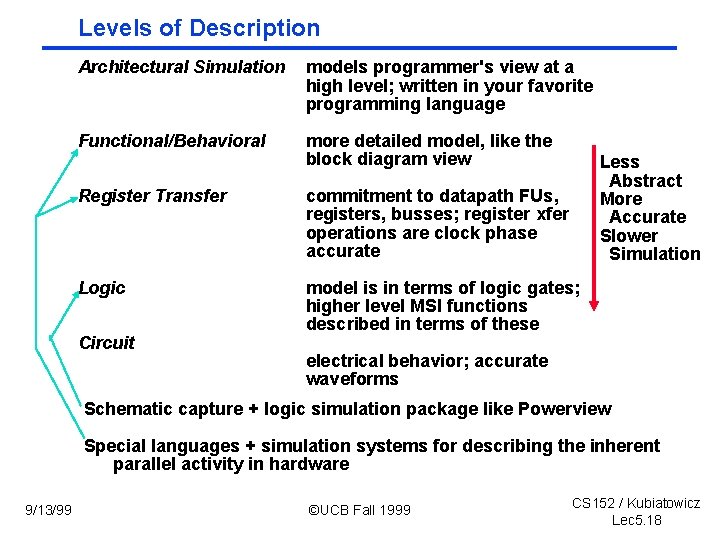

Levels of Description Architectural Simulation models programmer's view at a high level; written in your favorite programming language Functional/Behavioral more detailed model, like the block diagram view Less Abstract More Accurate Slower Simulation Register Transfer commitment to datapath FUs, registers, busses; register xfer operations are clock phase accurate Logic model is in terms of logic gates; higher level MSI functions described in terms of these Circuit electrical behavior; accurate waveforms Schematic capture + logic simulation package like Powerview Special languages + simulation systems for describing the inherent parallel activity in hardware 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 18

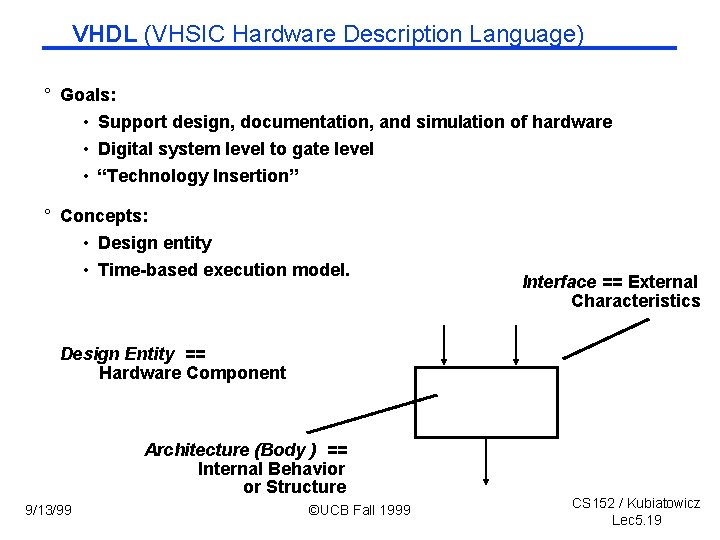

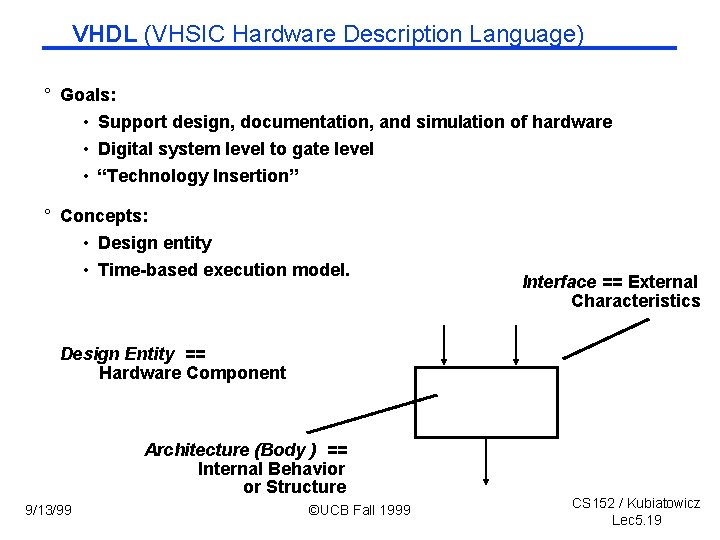

VHDL (VHSIC Hardware Description Language) ° Goals: • Support design, documentation, and simulation of hardware • Digital system level to gate level • “Technology Insertion” ° Concepts: • Design entity • Time-based execution model. Interface == External Characteristics Design Entity == Hardware Component Architecture (Body ) == Internal Behavior or Structure 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 19

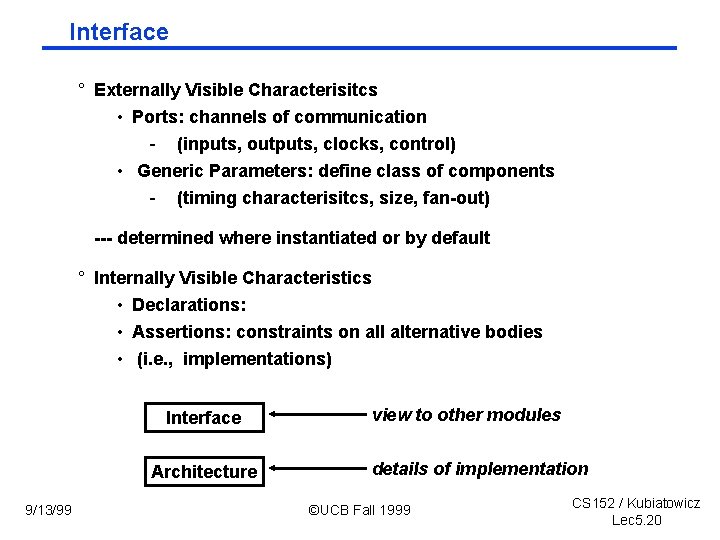

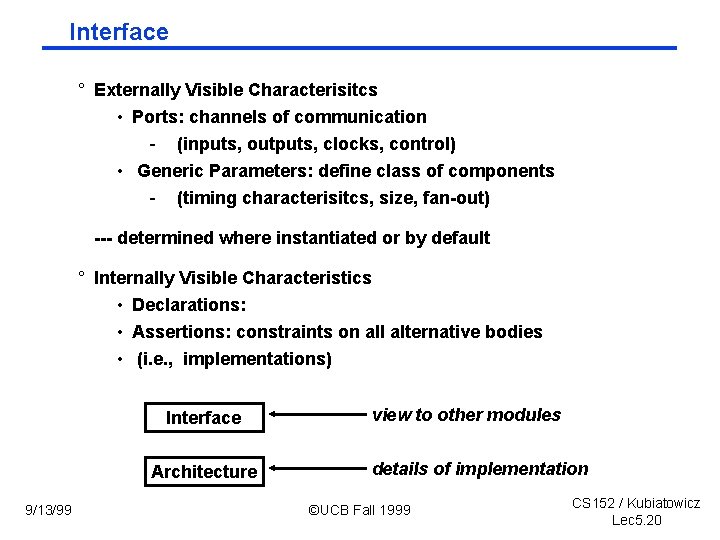

Interface ° Externally Visible Characterisitcs • Ports: channels of communication - (inputs, outputs, clocks, control) • Generic Parameters: define class of components - (timing characterisitcs, size, fan-out) --- determined where instantiated or by default ° Internally Visible Characteristics • Declarations: • Assertions: constraints on all alternative bodies • (i. e. , implementations) Interface Architecture 9/13/99 view to other modules details of implementation ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 20

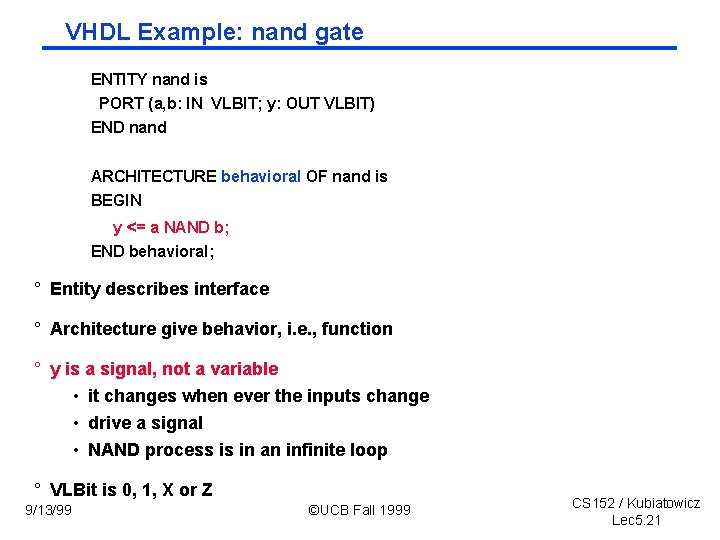

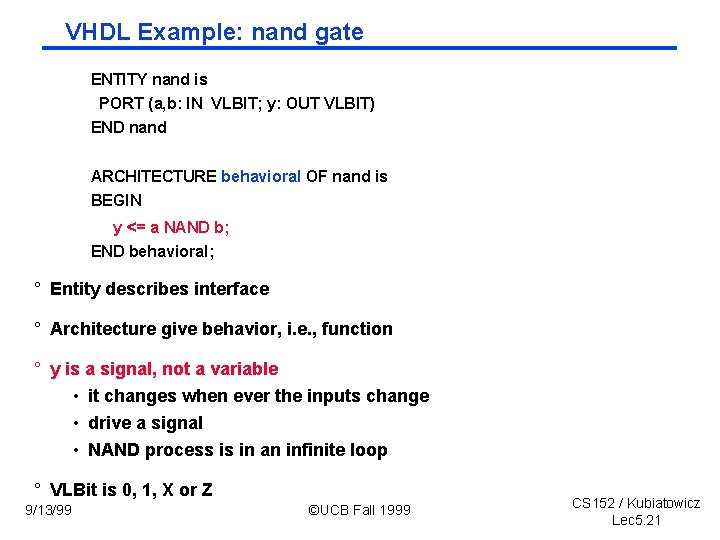

VHDL Example: nand gate ENTITY nand is PORT (a, b: IN VLBIT; y: OUT VLBIT) END nand ARCHITECTURE behavioral OF nand is BEGIN y <= a NAND b; END behavioral; ° Entity describes interface ° Architecture give behavior, i. e. , function ° y is a signal, not a variable • it changes when ever the inputs change • drive a signal • NAND process is in an infinite loop ° VLBit is 0, 1, X or Z 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 21

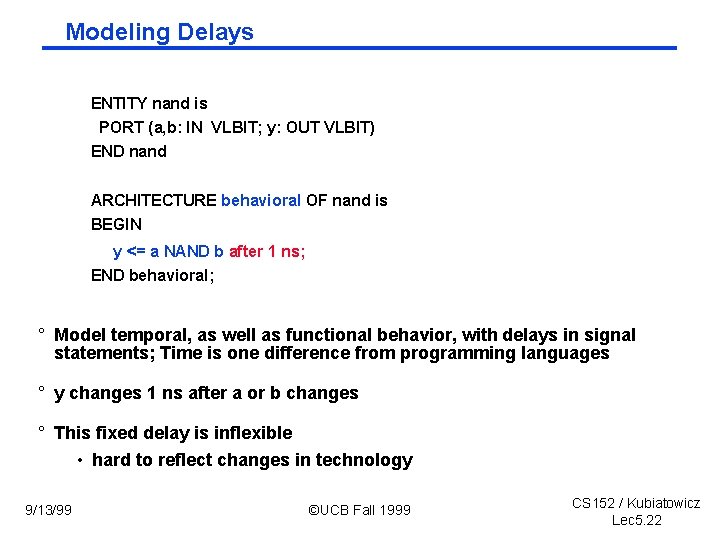

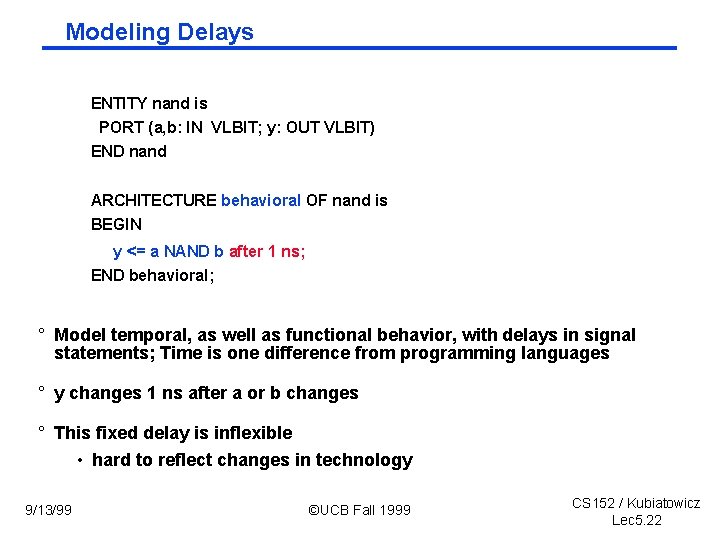

Modeling Delays ENTITY nand is PORT (a, b: IN VLBIT; y: OUT VLBIT) END nand ARCHITECTURE behavioral OF nand is BEGIN y <= a NAND b after 1 ns; END behavioral; ° Model temporal, as well as functional behavior, with delays in signal statements; Time is one difference from programming languages ° y changes 1 ns after a or b changes ° This fixed delay is inflexible • hard to reflect changes in technology 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 22

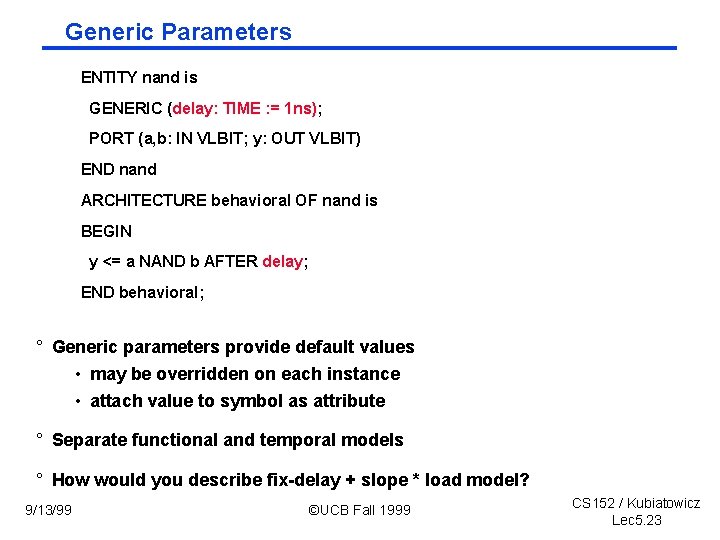

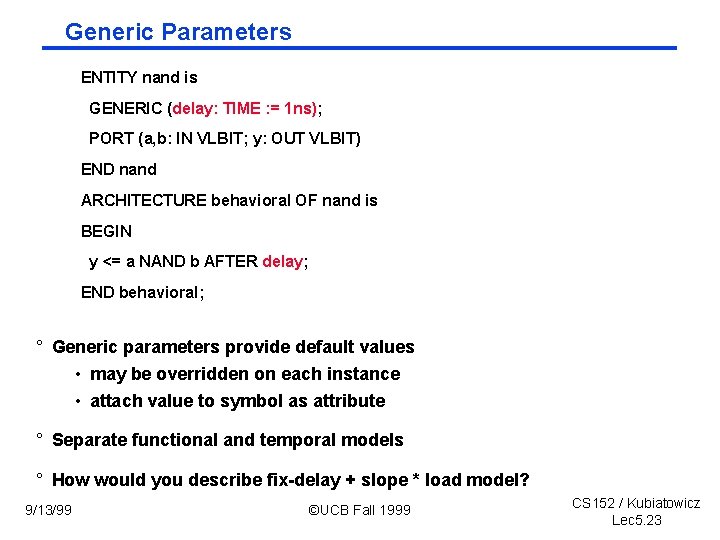

Generic Parameters ENTITY nand is GENERIC (delay: TIME : = 1 ns); PORT (a, b: IN VLBIT; y: OUT VLBIT) END nand ARCHITECTURE behavioral OF nand is BEGIN y <= a NAND b AFTER delay; END behavioral; ° Generic parameters provide default values • may be overridden on each instance • attach value to symbol as attribute ° Separate functional and temporal models ° How would you describe fix-delay + slope * load model? 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 23

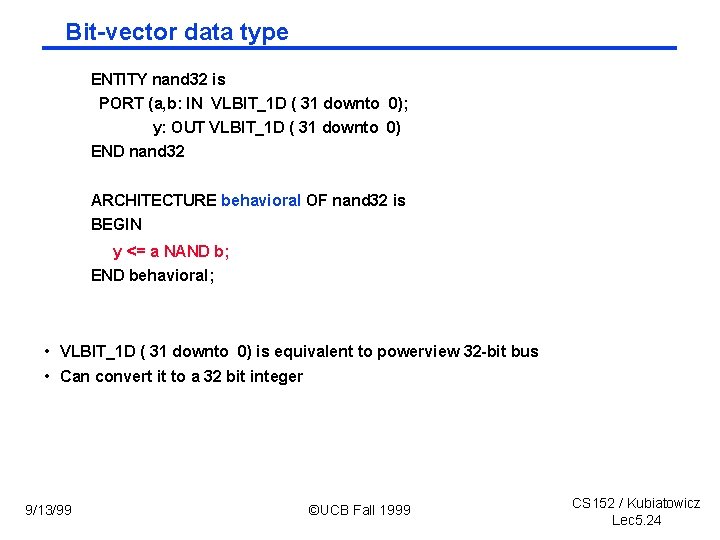

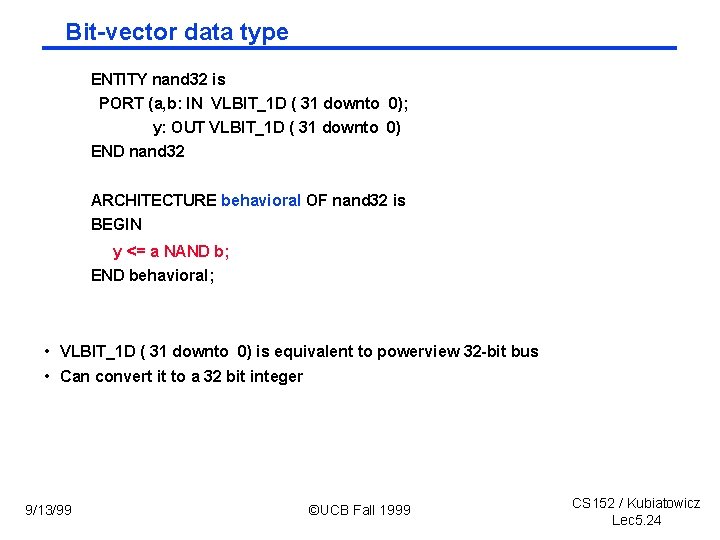

Bit-vector data type ENTITY nand 32 is PORT (a, b: IN VLBIT_1 D ( 31 downto 0); y: OUT VLBIT_1 D ( 31 downto 0) END nand 32 ARCHITECTURE behavioral OF nand 32 is BEGIN y <= a NAND b; END behavioral; • VLBIT_1 D ( 31 downto 0) is equivalent to powerview 32 -bit bus • Can convert it to a 32 bit integer 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 24

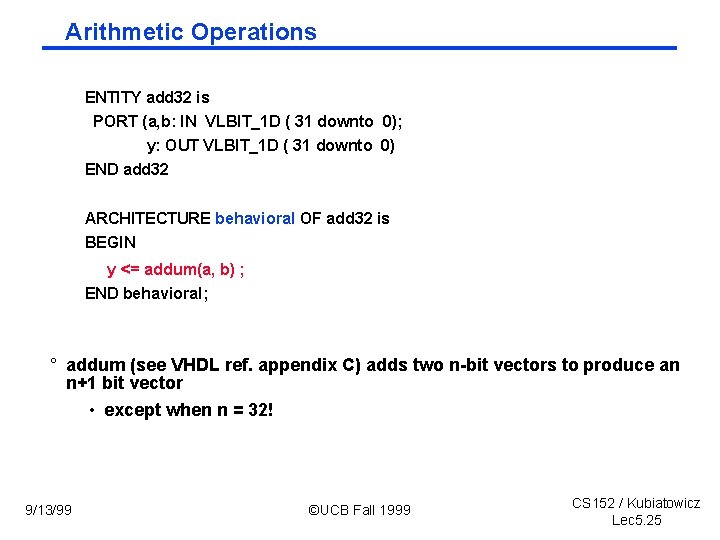

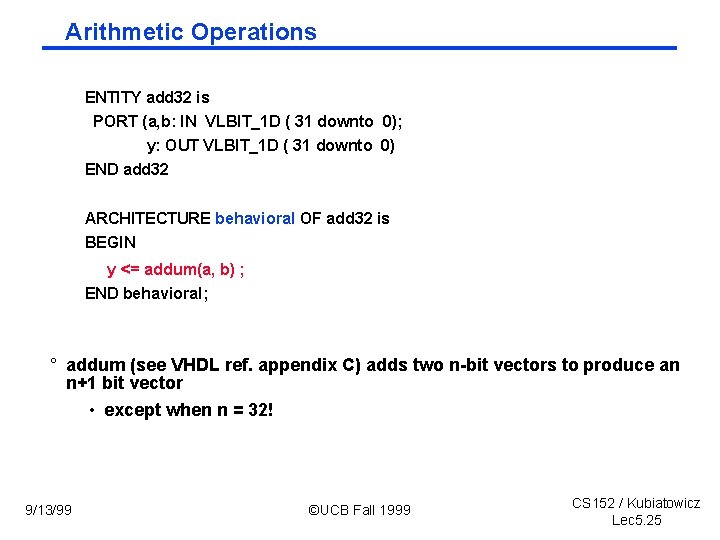

Arithmetic Operations ENTITY add 32 is PORT (a, b: IN VLBIT_1 D ( 31 downto 0); y: OUT VLBIT_1 D ( 31 downto 0) END add 32 ARCHITECTURE behavioral OF add 32 is BEGIN y <= addum(a, b) ; END behavioral; ° addum (see VHDL ref. appendix C) adds two n-bit vectors to produce an n+1 bit vector • except when n = 32! 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 25

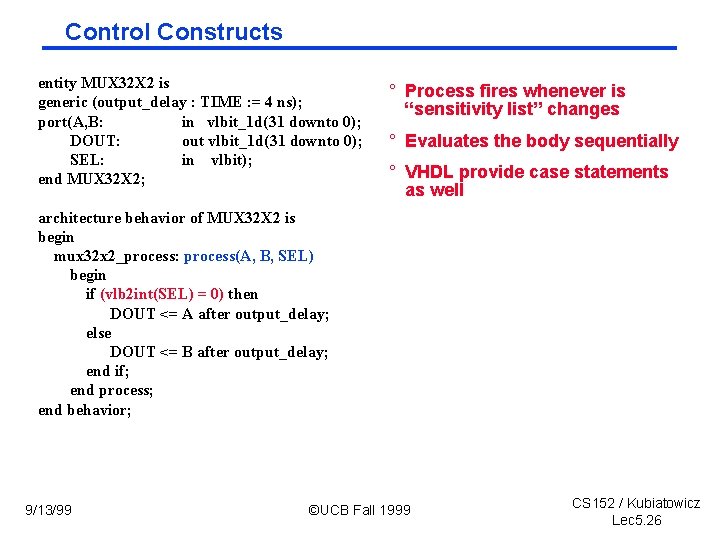

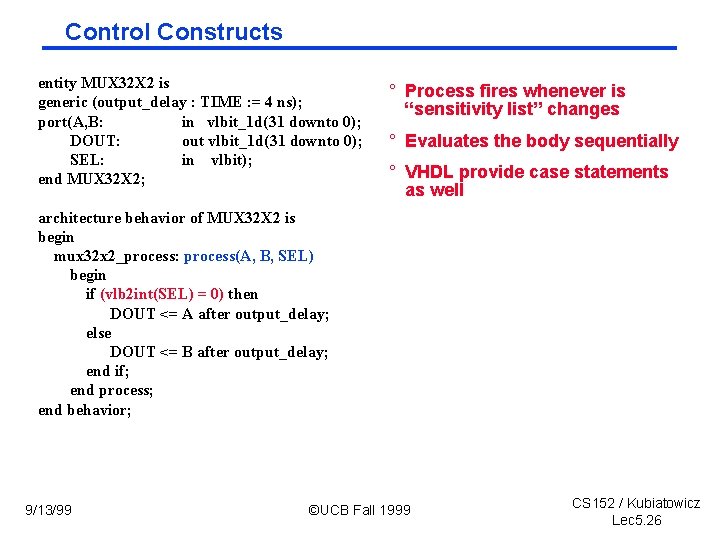

Control Constructs entity MUX 32 X 2 is generic (output_delay : TIME : = 4 ns); port(A, B: in vlbit_1 d(31 downto 0); DOUT: out vlbit_1 d(31 downto 0); SEL: in vlbit); end MUX 32 X 2; ° Process fires whenever is “sensitivity list” changes ° Evaluates the body sequentially ° VHDL provide case statements as well architecture behavior of MUX 32 X 2 is begin mux 32 x 2_process: process(A, B, SEL) begin if (vlb 2 int(SEL) = 0) then DOUT <= A after output_delay; else DOUT <= B after output_delay; end if; end process; end behavior; 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 26

Administrative Matters ° Final class list is online. ° Remember that homework due this Wednesday! • First homework quiz at BEGINNING of class. ° On-line lab notebook is such a good idea, its required! (starting with Lab 3) ° Reading Chapter 4 now 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 27

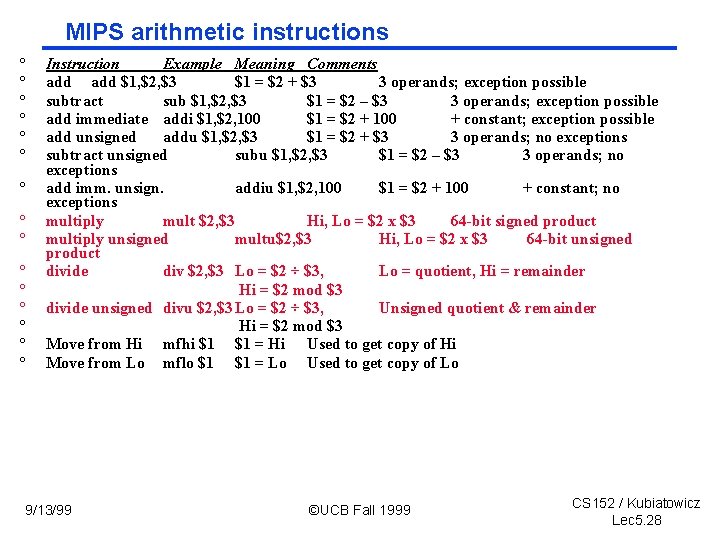

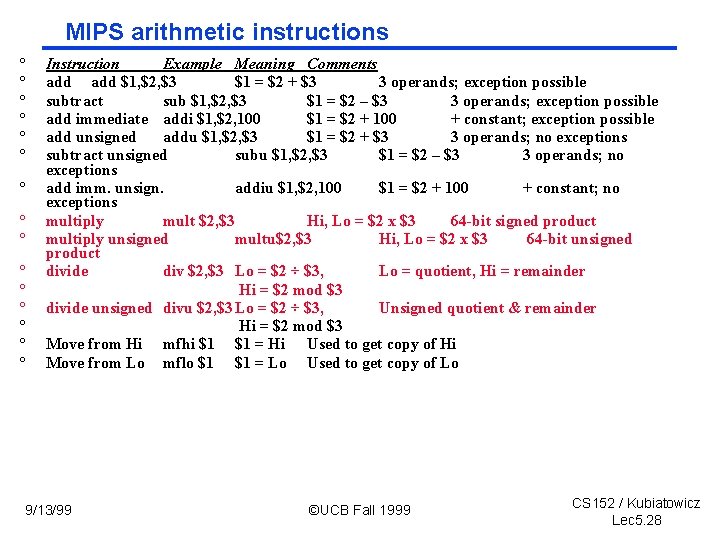

MIPS arithmetic instructions ° ° ° ° Instruction Example Meaning Comments add $1, $2, $3 $1 = $2 + $3 3 operands; exception possible subtract sub $1, $2, $3 $1 = $2 – $3 3 operands; exception possible add immediate addi $1, $2, 100 $1 = $2 + 100 + constant; exception possible add unsigned addu $1, $2, $3 $1 = $2 + $3 3 operands; no exceptions subtract unsigned subu $1, $2, $3 $1 = $2 – $3 3 operands; no exceptions add imm. unsign. addiu $1, $2, 100 $1 = $2 + 100 + constant; no exceptions multiply mult $2, $3 Hi, Lo = $2 x $3 64 -bit signed product multiply unsigned multu$2, $3 Hi, Lo = $2 x $3 64 -bit unsigned product divide div $2, $3 Lo = $2 ÷ $3, Lo = quotient, Hi = remainder Hi = $2 mod $3 divide unsigned divu $2, $3 Lo = $2 ÷ $3, Unsigned quotient & remainder Hi = $2 mod $3 Move from Hi mfhi $1 $1 = Hi Used to get copy of Hi Move from Lo mflo $1 $1 = Lo Used to get copy of Lo 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 28

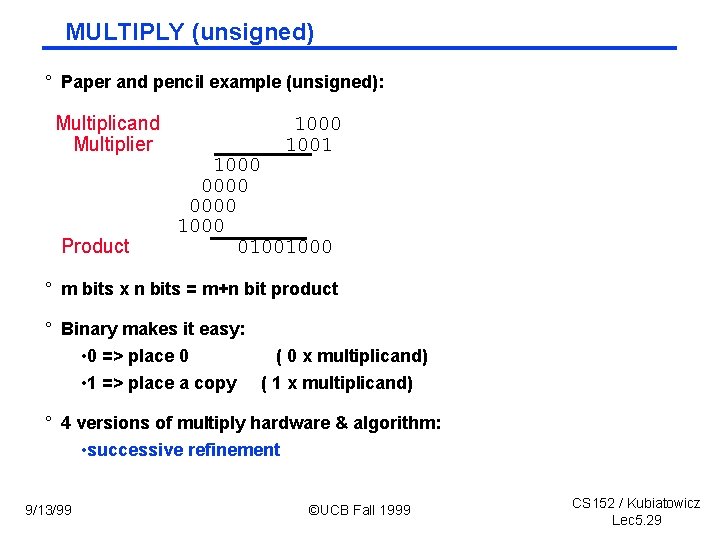

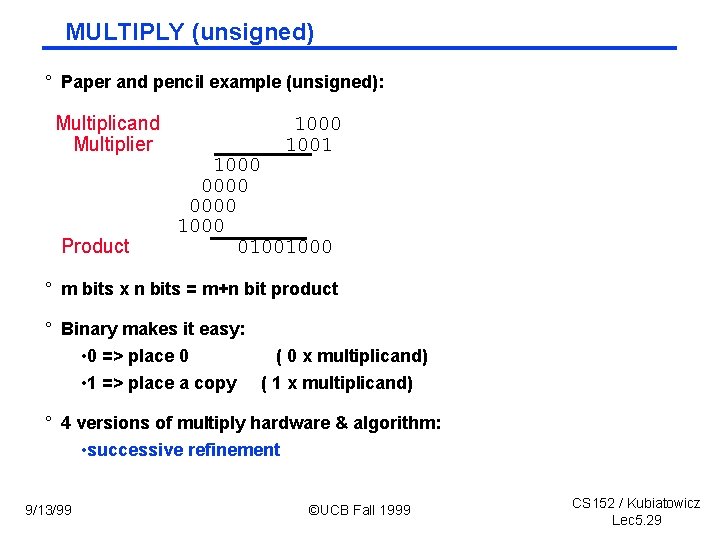

MULTIPLY (unsigned) ° Paper and pencil example (unsigned): Multiplicand Multiplier Product 1000 1001 1000 0000 1000 01001000 ° m bits x n bits = m+n bit product ° Binary makes it easy: • 0 => place 0 ( 0 x multiplicand) • 1 => place a copy ( 1 x multiplicand) ° 4 versions of multiply hardware & algorithm: • successive refinement 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 29

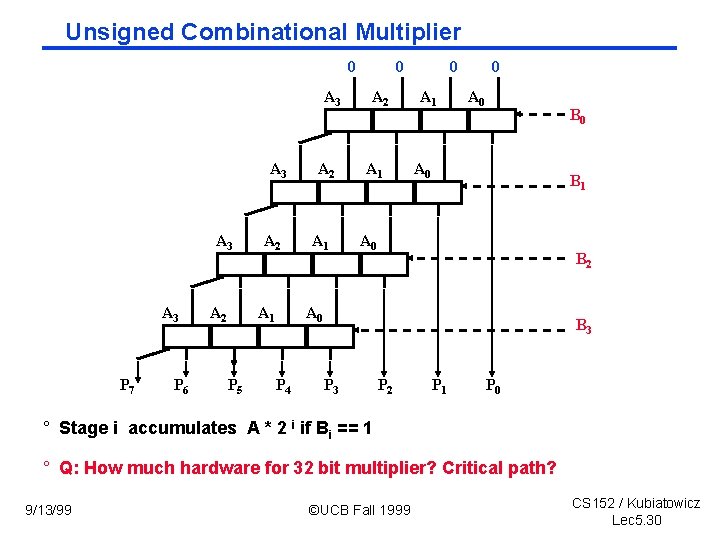

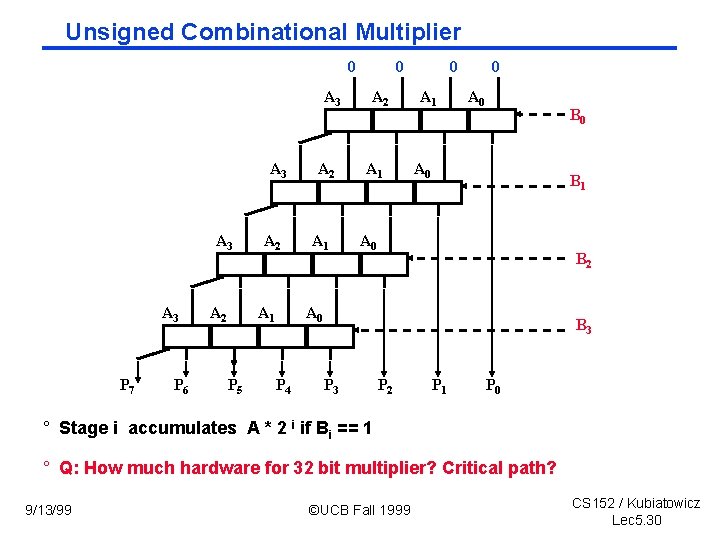

Unsigned Combinational Multiplier 0 A 3 A 3 P 7 P 6 A 2 A 1 P 5 A 2 A 1 0 A 0 B 1 A 0 B 2 A 0 P 4 B 3 P 2 P 1 P 0 ° Stage i accumulates A * 2 i if Bi == 1 ° Q: How much hardware for 32 bit multiplier? Critical path? 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 30

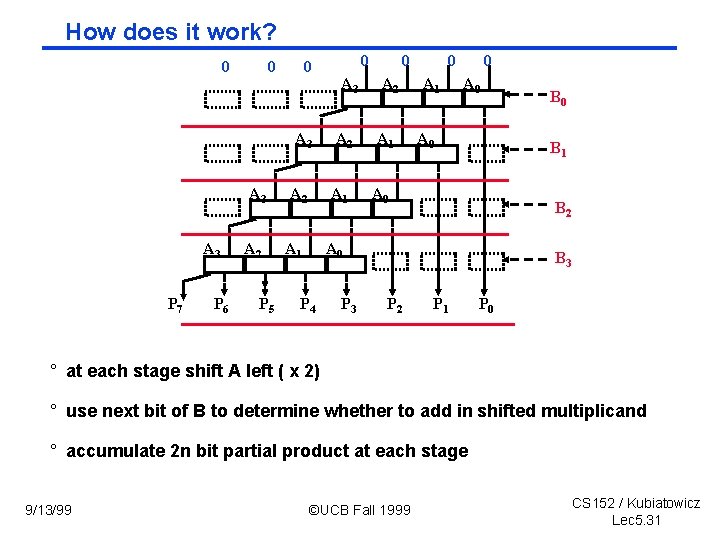

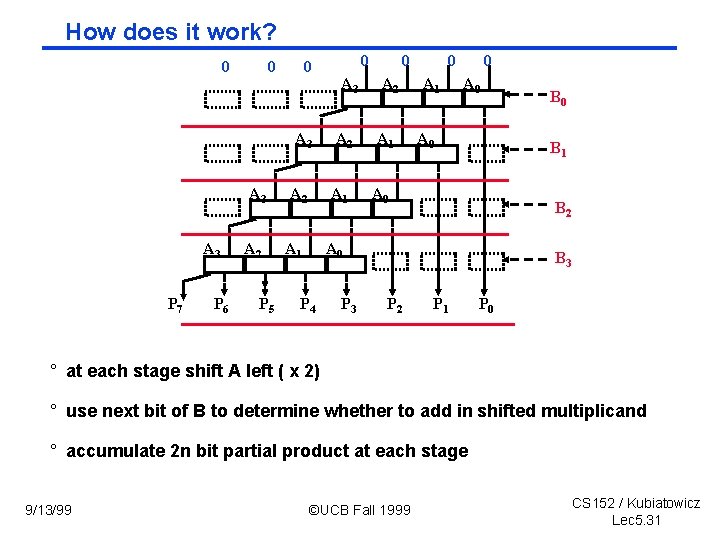

How does it work? 0 0 0 A 3 A 3 P 7 P 6 A 2 P 5 A 2 0 A 3 A 2 A 1 0 A 0 B 1 A 0 B 2 A 0 P 4 P 3 B 0 B 3 P 2 P 1 P 0 ° at each stage shift A left ( x 2) ° use next bit of B to determine whether to add in shifted multiplicand ° accumulate 2 n bit partial product at each stage 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 31

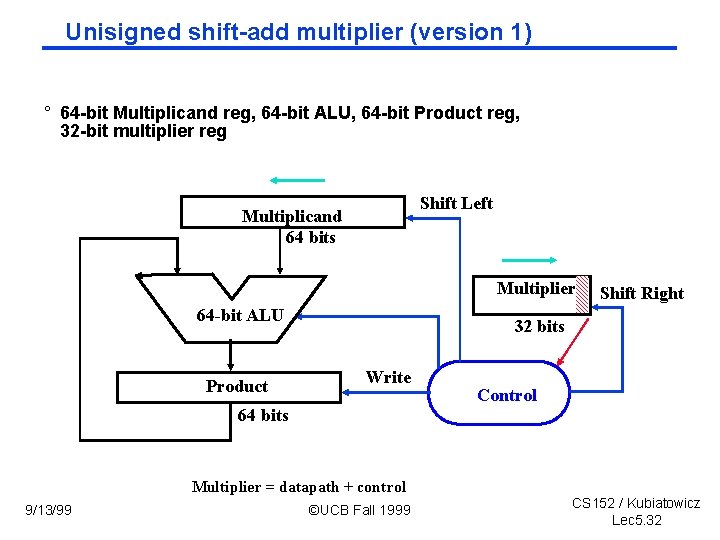

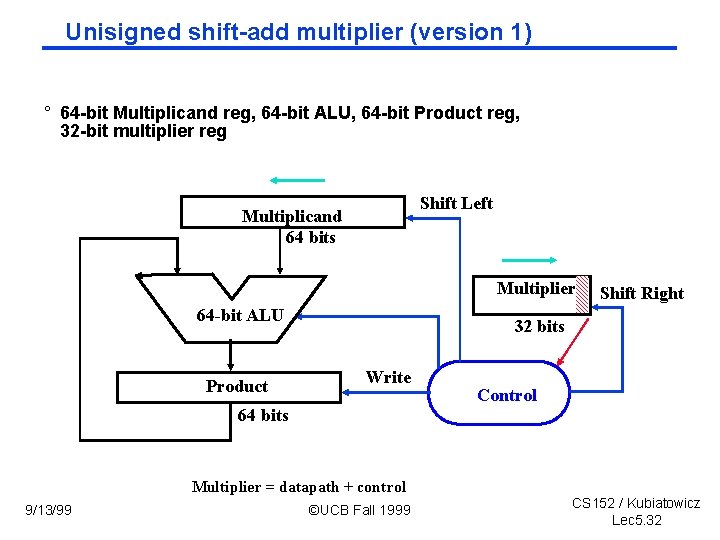

Unisigned shift-add multiplier (version 1) ° 64 -bit Multiplicand reg, 64 -bit ALU, 64 -bit Product reg, 32 -bit multiplier reg Shift Left Multiplicand 64 bits Multiplier 64 -bit ALU Product 32 bits Write 64 bits Multiplier = datapath + control 9/13/99 Shift Right ©UCB Fall 1999 Control CS 152 / Kubiatowicz Lec 5. 32

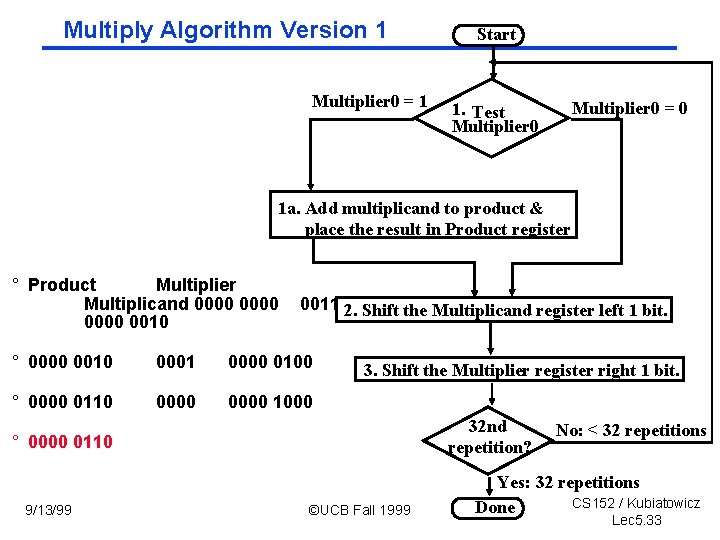

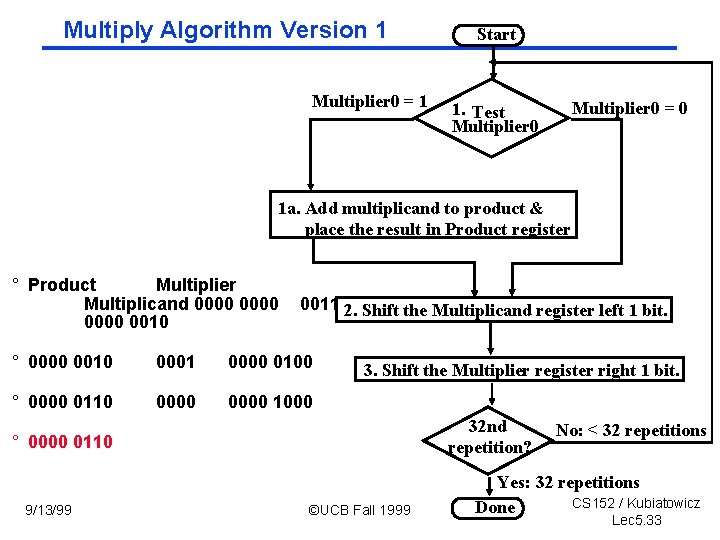

Multiply Algorithm Version 1 Multiplier 0 = 1 Start Multiplier 0 = 0 1. Test Multiplier 0 1 a. Add multiplicand to product & place the result in Product register ° Product Multiplier Multiplicand 0000 0011 2. Shift the Multiplicand register left 1 bit. ° 0000 0010 0001 0000 0100 ° 0000 0110 0000 1000 3. Shift the Multiplier register right 1 bit. 32 nd repetition? ° 0000 0110 9/13/99 ©UCB Fall 1999 No: < 32 repetitions Yes: 32 repetitions CS 152 / Kubiatowicz Done Lec 5. 33

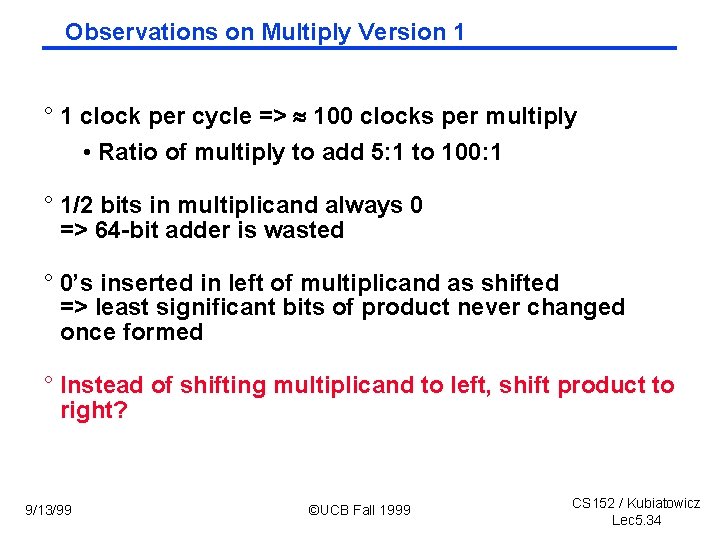

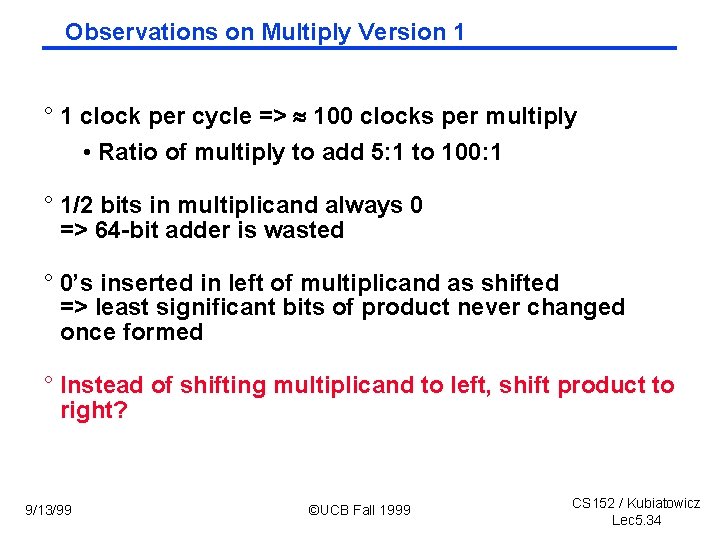

Observations on Multiply Version 1 ° 1 clock per cycle => 100 clocks per multiply • Ratio of multiply to add 5: 1 to 100: 1 ° 1/2 bits in multiplicand always 0 => 64 -bit adder is wasted ° 0’s inserted in left of multiplicand as shifted => least significant bits of product never changed once formed ° Instead of shifting multiplicand to left, shift product to right? 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 34

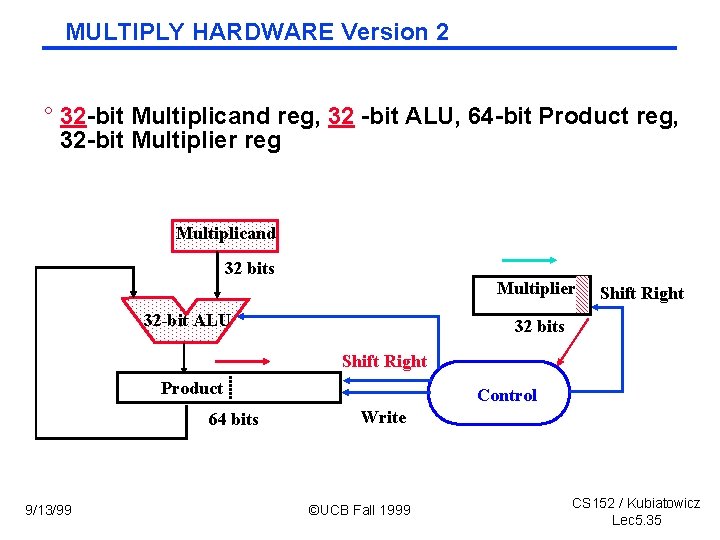

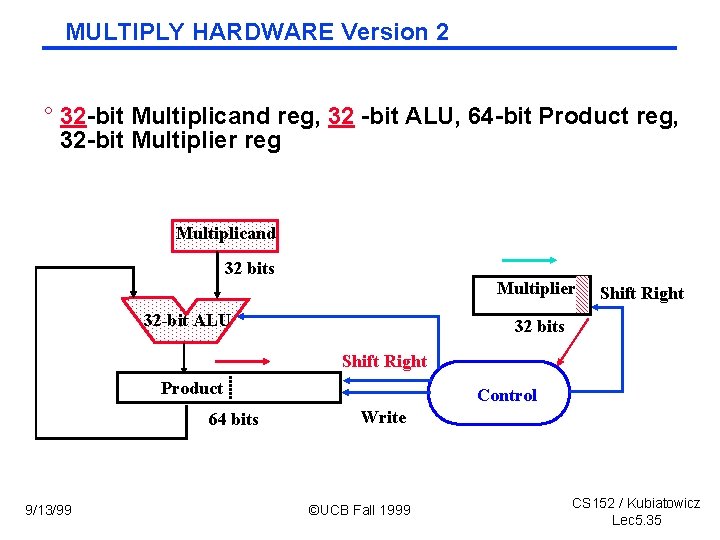

MULTIPLY HARDWARE Version 2 ° 32 -bit Multiplicand reg, 32 -bit ALU, 64 -bit Product reg, 32 -bit Multiplier reg Multiplicand 32 bits Multiplier 32 -bit ALU Shift Right 32 bits Shift Right Product 64 bits 9/13/99 Control Write ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 35

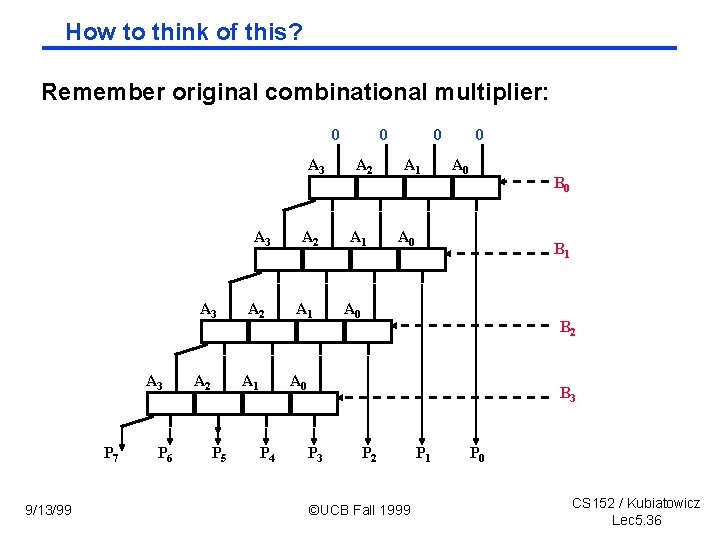

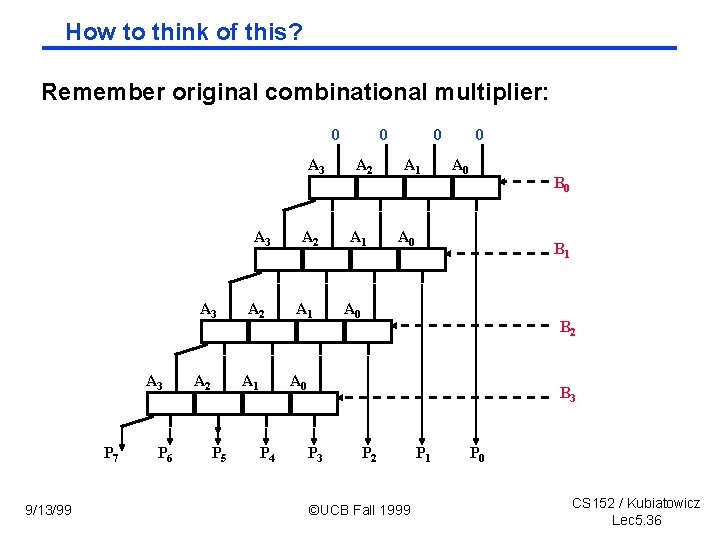

How to think of this? Remember original combinational multiplier: 0 A 3 A 3 P 7 9/13/99 P 6 A 2 A 1 P 5 A 2 A 1 0 A 0 B 1 A 0 B 2 A 0 P 4 B 3 P 2 ©UCB Fall 1999 P 1 P 0 CS 152 / Kubiatowicz Lec 5. 36

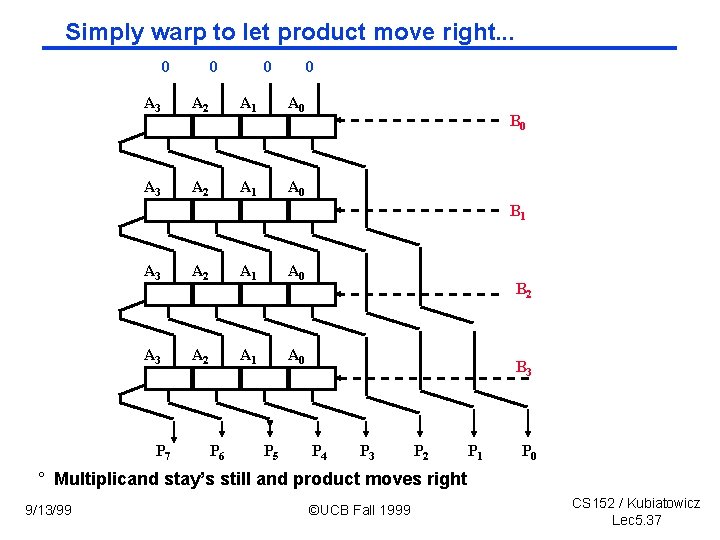

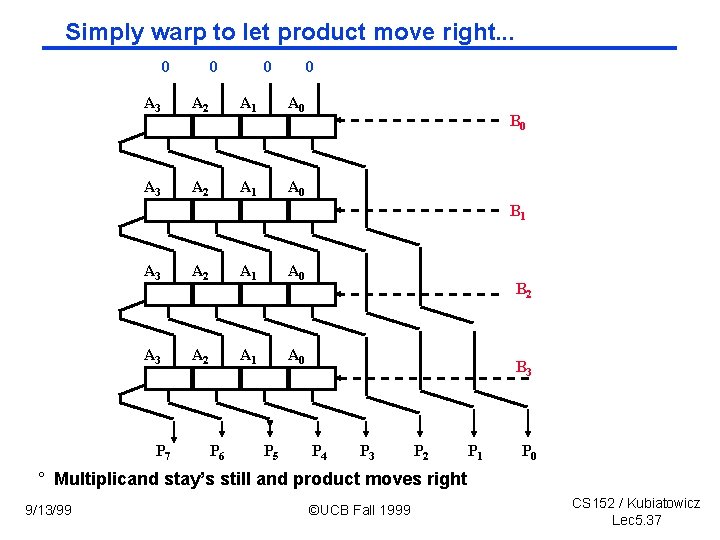

Simply warp to let product move right. . . 0 0 A 3 A 2 A 1 A 0 B 0 B 1 A 3 A 2 A 1 A 0 P 7 P 6 P 5 B 2 B 3 P 4 P 3 P 2 P 1 P 0 ° Multiplicand stay’s still and product moves right 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 37

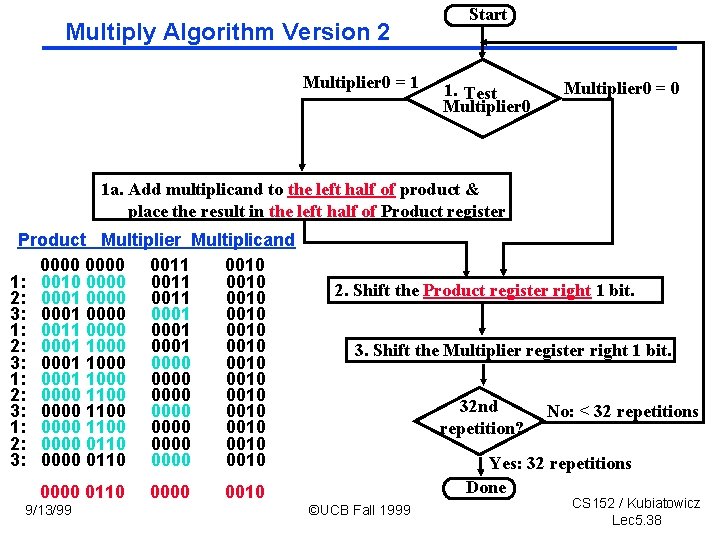

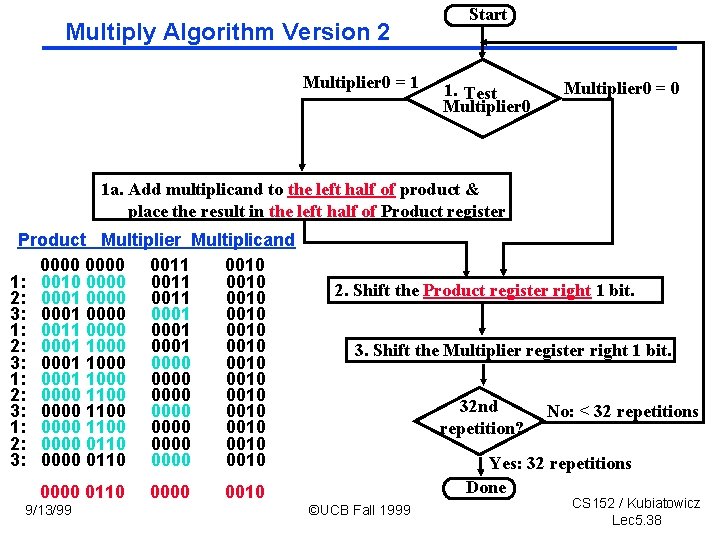

Multiply Algorithm Version 2 Multiplier 0 = 1 Start 1. Test Multiplier 0 = 0 1 a. Add multiplicand to the left half of product & place the result in the left half of Product register Product Multiplier Multiplicand 0000 0011 0010 1: 0010 0000 0011 0010 2: 0001 0000 0011 0010 3: 0001 0000 0001 0010 1: 0011 0000 0001 0010 2: 0001 1000 0001 0010 3: 0001 1000 0010 1: 0001 1000 0010 2: 0000 1100 0010 3: 0000 1100 0010 1: 0000 1100 0010 2: 0000 0110 0000 0010 3: 0000 0110 0000 0010 0000 0110 9/13/99 0000 2. Shift the Product register right 1 bit. 3. Shift the Multiplier register right 1 bit. 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done 0010 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 38

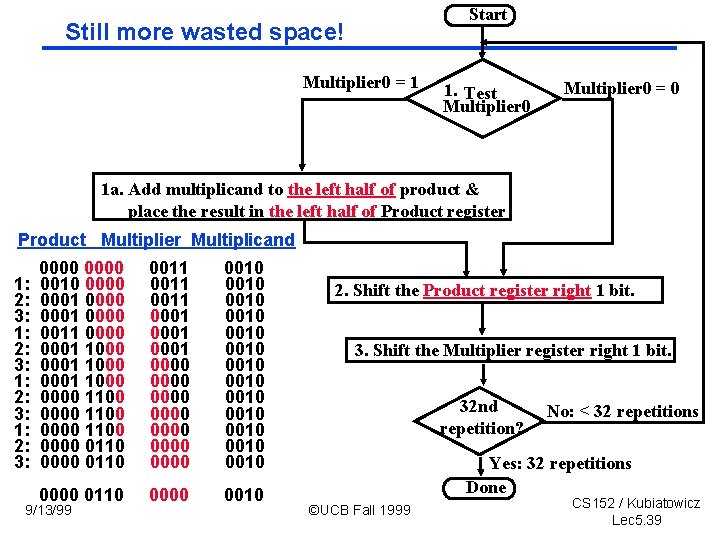

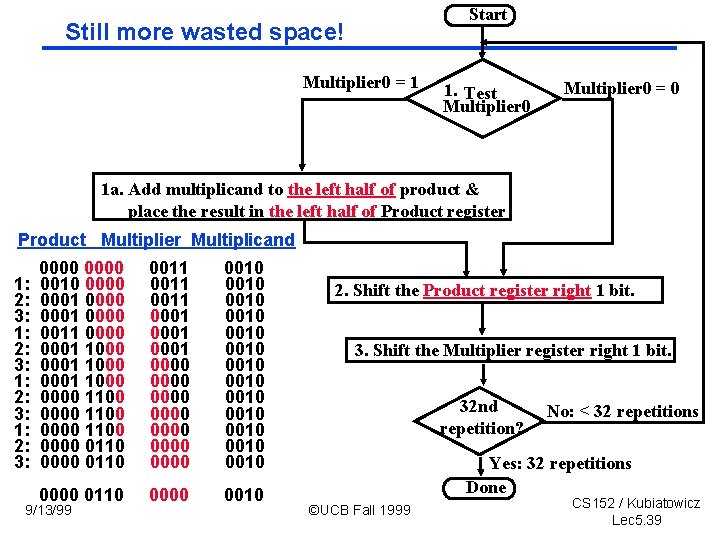

Start Still more wasted space! Multiplier 0 = 1 1. Test Multiplier 0 = 0 1 a. Add multiplicand to the left half of product & place the result in the left half of Product register Product Multiplier Multiplicand 1: 2: 3: 0000 0010 0001 0000 0011 0000 0001 1000 0000 1100 0000 0110 0011 0001 0000 0000 0010 0010 0010 0010 0000 0110 0000 0010 9/13/99 2. Shift the Product register right 1 bit. 3. Shift the Multiplier register right 1 bit. 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 39

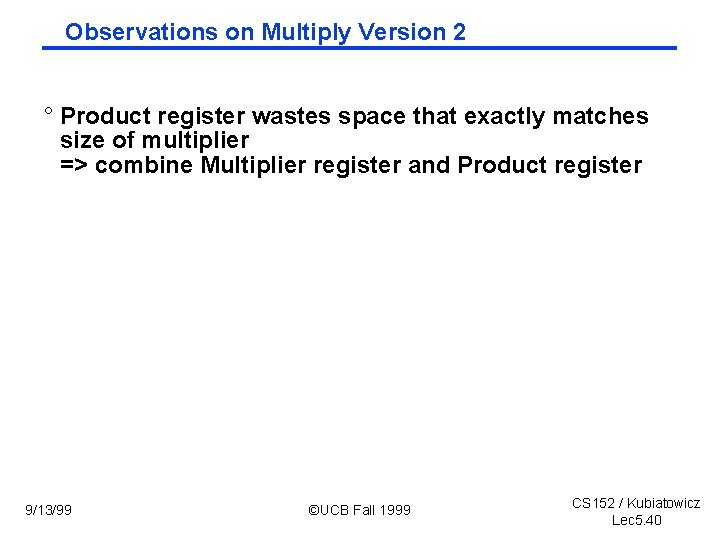

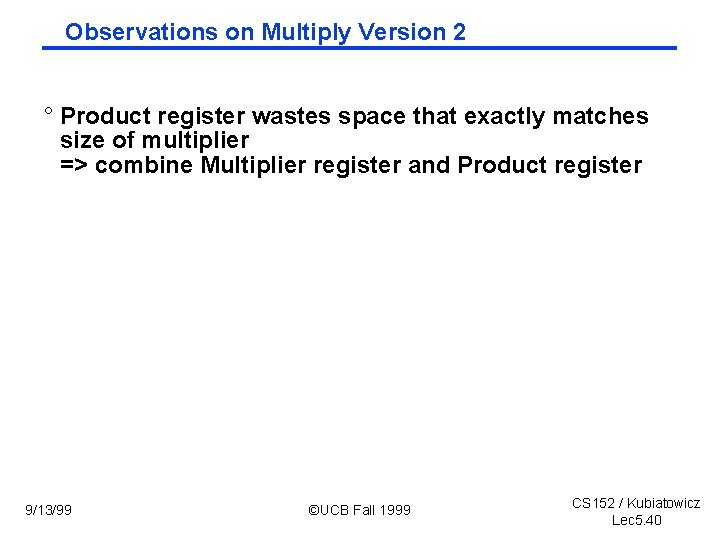

Observations on Multiply Version 2 ° Product register wastes space that exactly matches size of multiplier => combine Multiplier register and Product register 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 40

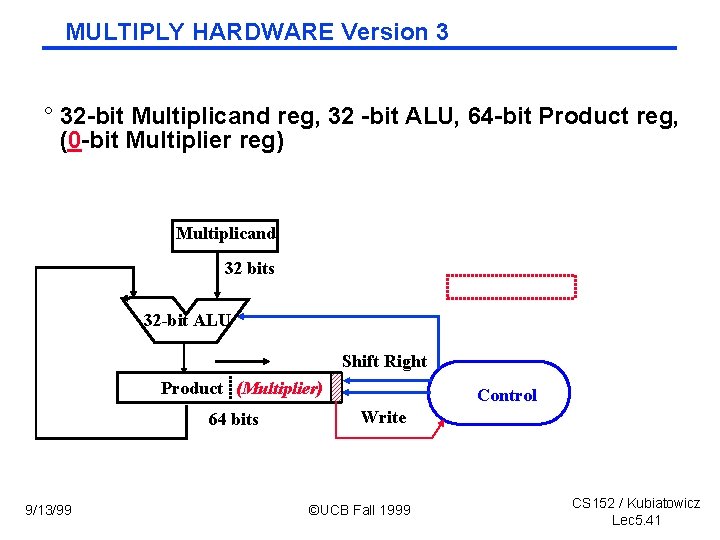

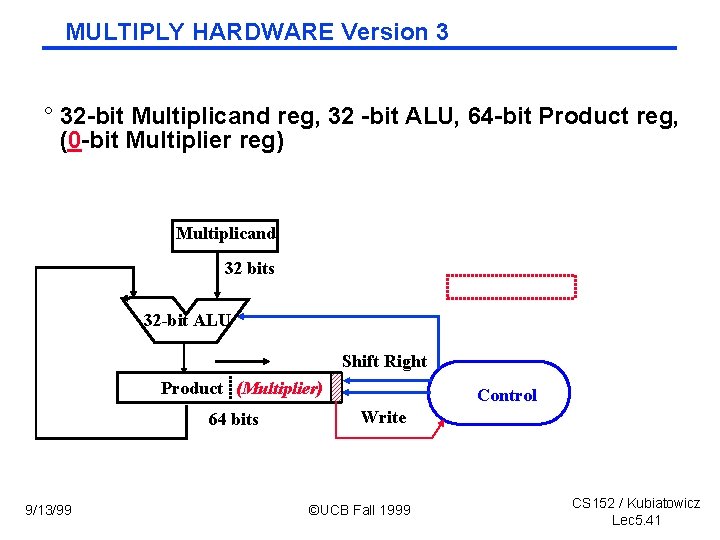

MULTIPLY HARDWARE Version 3 ° 32 -bit Multiplicand reg, 32 -bit ALU, 64 -bit Product reg, (0 -bit Multiplier reg) Multiplicand 32 bits 32 -bit ALU Shift Right Product (Multiplier) 64 bits 9/13/99 Control Write ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 41

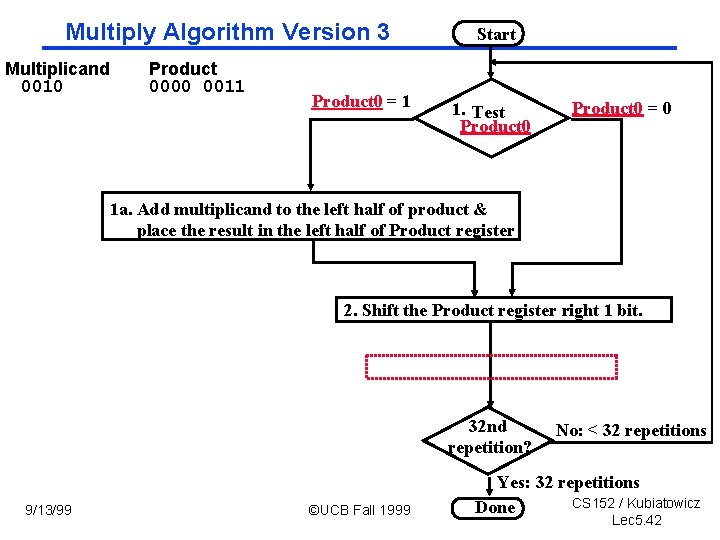

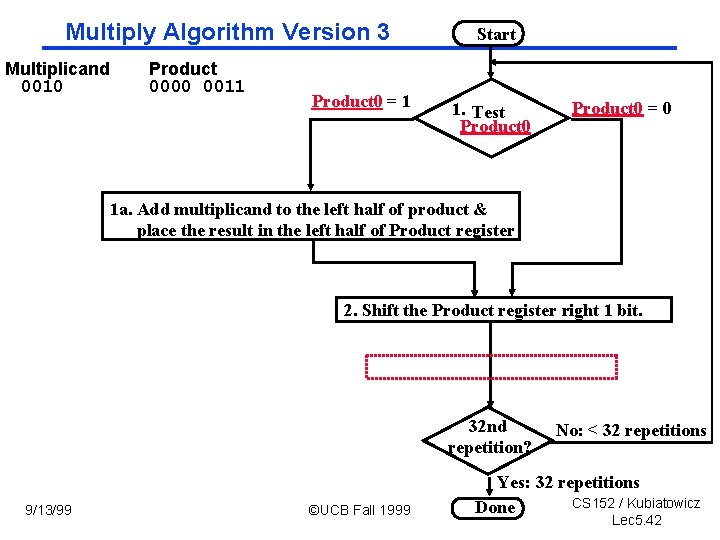

Multiply Algorithm Version 3 Multiplicand 0010 Product 0000 0011 Product 0 = 1 Start 1. Test Product 0 = 0 1 a. Add multiplicand to the left half of product & place the result in the left half of Product register 2. Shift the Product register right 1 bit. 32 nd repetition? 9/13/99 ©UCB Fall 1999 No: < 32 repetitions Yes: 32 repetitions CS 152 / Kubiatowicz Done Lec 5. 42

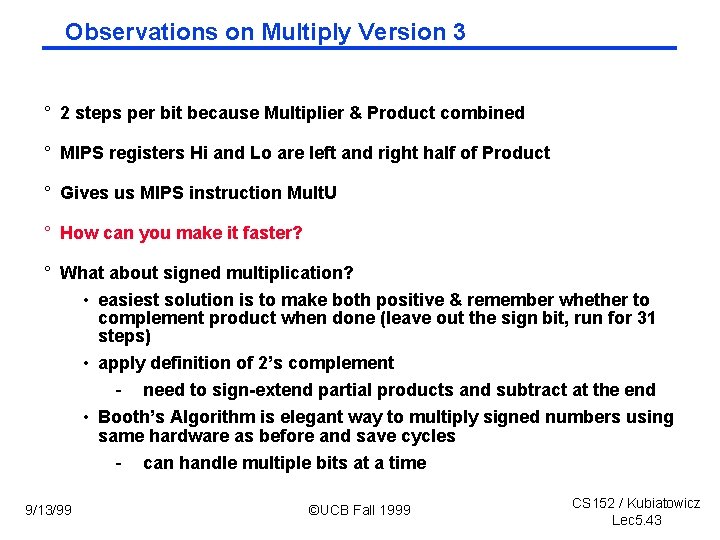

Observations on Multiply Version 3 ° 2 steps per bit because Multiplier & Product combined ° MIPS registers Hi and Lo are left and right half of Product ° Gives us MIPS instruction Mult. U ° How can you make it faster? ° What about signed multiplication? • easiest solution is to make both positive & remember whether to complement product when done (leave out the sign bit, run for 31 steps) • apply definition of 2’s complement - need to sign-extend partial products and subtract at the end • Booth’s Algorithm is elegant way to multiply signed numbers using same hardware as before and save cycles - can handle multiple bits at a time 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 43

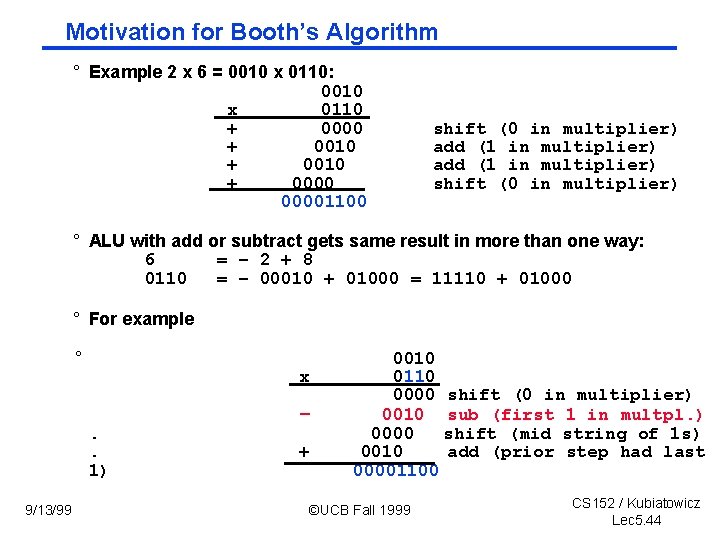

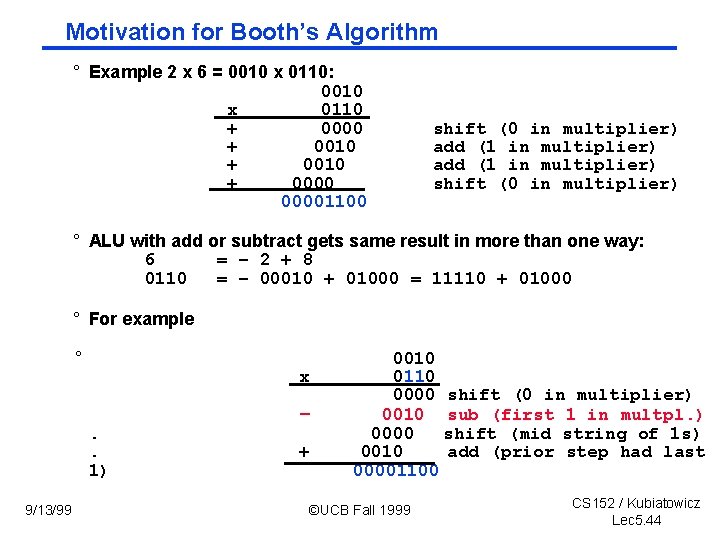

Motivation for Booth’s Algorithm ° Example 2 x 6 = 0010 x 0110: 0010 x 0110 + 0000 + 0010 + 00001100 shift (0 in multiplier) add (1 in multiplier) shift (0 in multiplier) ° ALU with add or subtract gets same result in more than one way: 6 = – 2 + 8 0110 = – 00010 + 01000 = 11110 + 01000 ° For example ° x. . 1) 9/13/99 – + 0010 0110 0000 shift (0 in multiplier) 0010 sub (first 1 in multpl. ) 0000 shift (mid string of 1 s) 0010 add (prior step had last 00001100 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 44

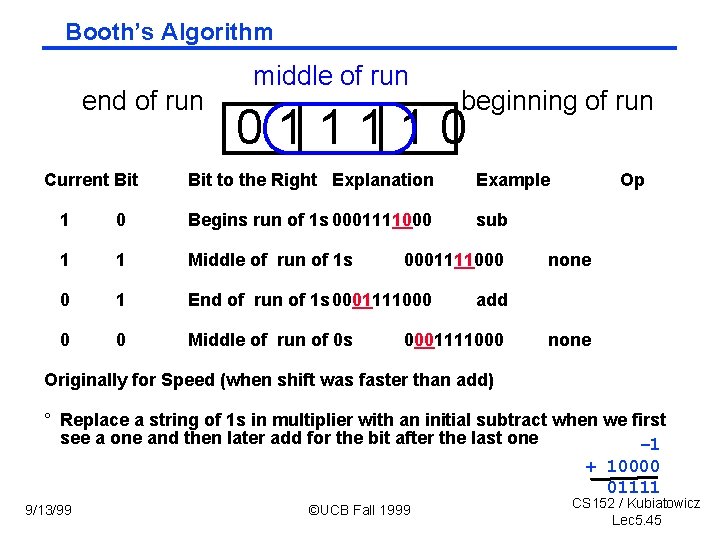

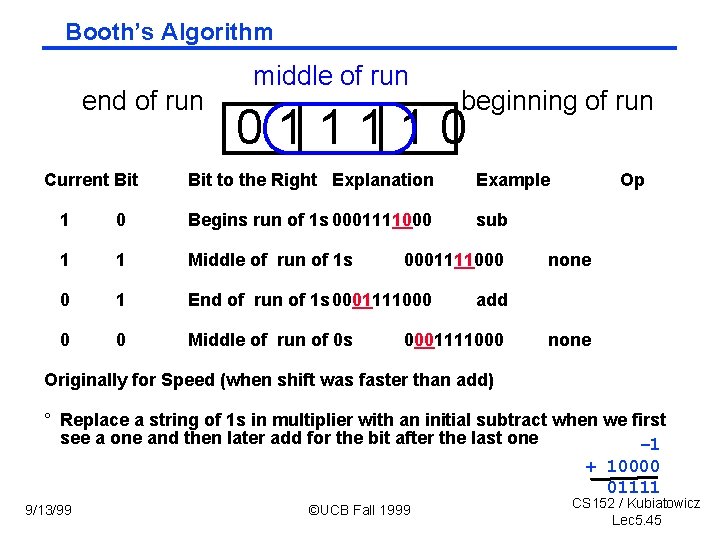

Booth’s Algorithm end of run Current Bit middle of run beginning of run 011110 Bit to the Right Explanation Example sub 1 0 Begins run of 1 s 0001111000 1 1 Middle of run of 1 s 0 1 End of run of 1 s 0001111000 0 0 Middle of run of 0 s 0001111000 Op none add 0001111000 none Originally for Speed (when shift was faster than add) ° Replace a string of 1 s in multiplier with an initial subtract when we first see a one and then later add for the bit after the last one – 1 + 10000 01111 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 45

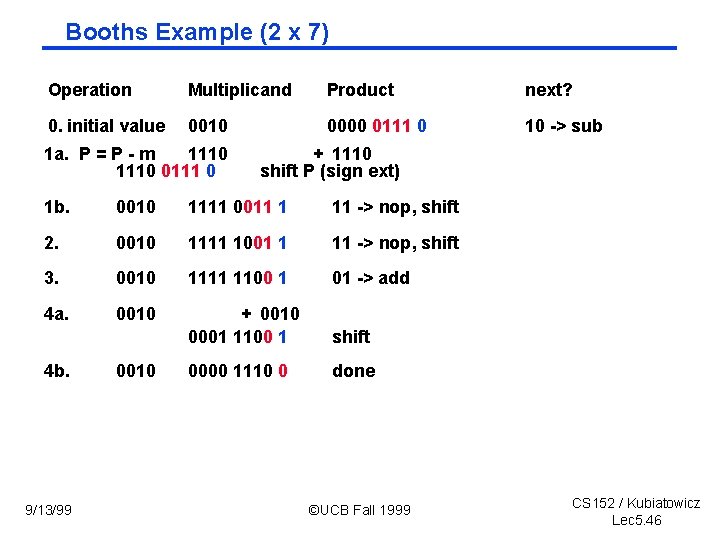

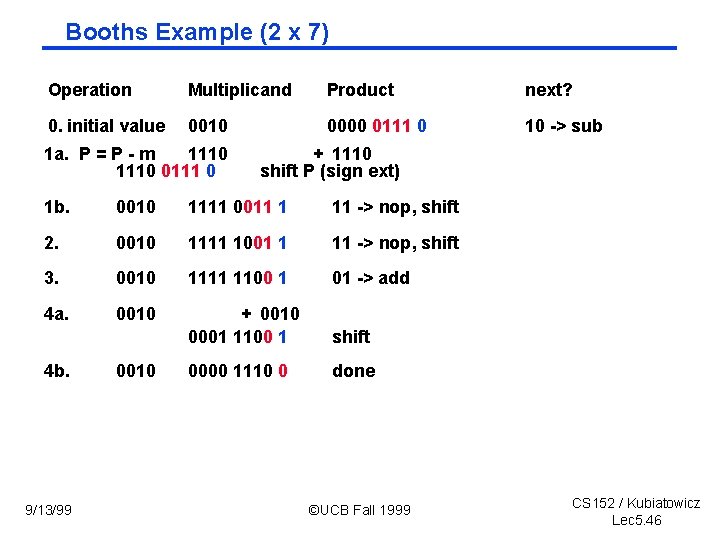

Booths Example (2 x 7) Operation Multiplicand Product next? 0. initial value 0010 0000 0111 0 10 -> sub 1 a. P = P - m 1110 0111 0 + 1110 shift P (sign ext) 1 b. 0010 1111 0011 1 11 -> nop, shift 2. 0010 1111 1001 1 11 -> nop, shift 3. 0010 1111 1100 1 01 -> add 4 a. 0010 + 0010 0001 1100 1 shift 0000 1110 0 done 4 b. 9/13/99 0010 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 46

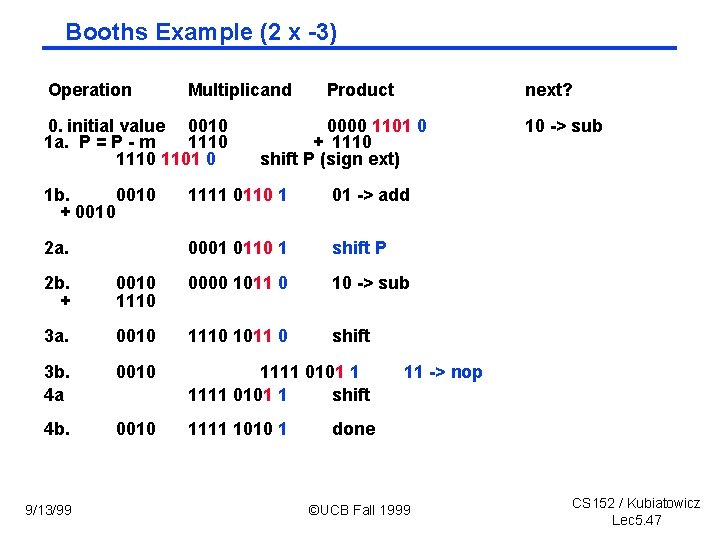

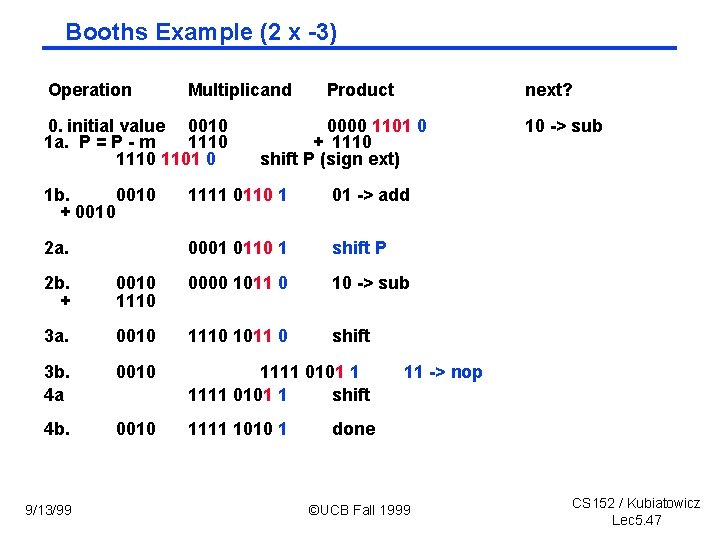

Booths Example (2 x -3) Operation Multiplicand 0. initial value 0010 1 a. P = P - m 1110 1101 0 Product next? 0000 1101 0 + 1110 shift P (sign ext) 1 b. 0010 + 0010 1111 0110 1 01 -> add 2 a. 0001 0110 1 shift P 2 b. + 0010 1110 0000 1011 0 10 -> sub 3 a. 0010 1110 1011 0 shift 3 b. 4 a 0010 1111 0101 1 shift 4 b. 0010 1111 1010 1 9/13/99 10 -> sub 11 -> nop done ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 47

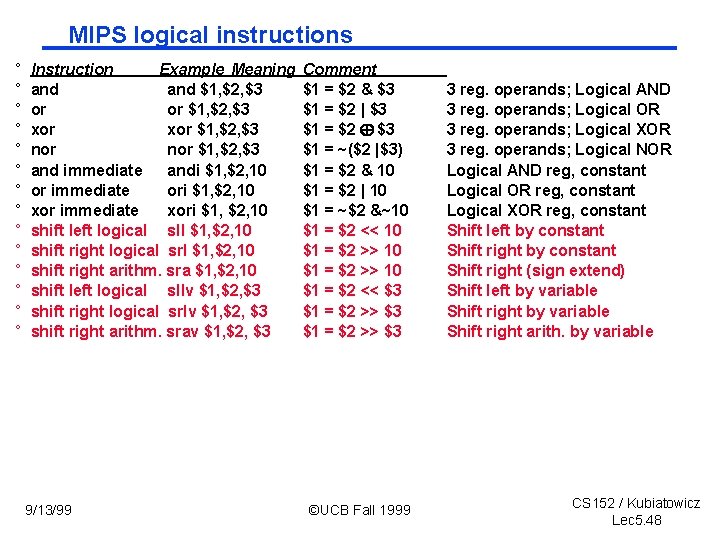

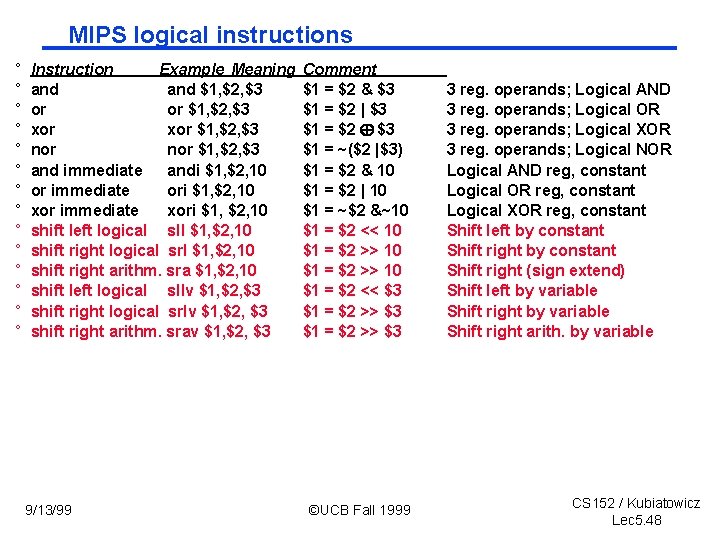

MIPS logical instructions ° ° ° ° Instruction Example Meaning and $1, $2, $3 or or $1, $2, $3 xor $1, $2, $3 nor $1, $2, $3 and immediate andi $1, $2, 10 or immediate ori $1, $2, 10 xor immediate xori $1, $2, 10 shift left logical sll $1, $2, 10 shift right logical srl $1, $2, 10 shift right arithm. sra $1, $2, 10 shift left logical sllv $1, $2, $3 shift right logical srlv $1, $2, $3 shift right arithm. srav $1, $2, $3 9/13/99 Comment $1 = $2 & $3 $1 = $2 | $3 $1 = $2 $3 $1 = ~($2 |$3) $1 = $2 & 10 $1 = $2 | 10 $1 = ~$2 &~10 $1 = $2 << 10 $1 = $2 >> 10 $1 = $2 << $3 $1 = $2 >> $3 ©UCB Fall 1999 3 reg. operands; Logical AND 3 reg. operands; Logical OR 3 reg. operands; Logical XOR 3 reg. operands; Logical NOR Logical AND reg, constant Logical OR reg, constant Logical XOR reg, constant Shift left by constant Shift right (sign extend) Shift left by variable Shift right arith. by variable CS 152 / Kubiatowicz Lec 5. 48

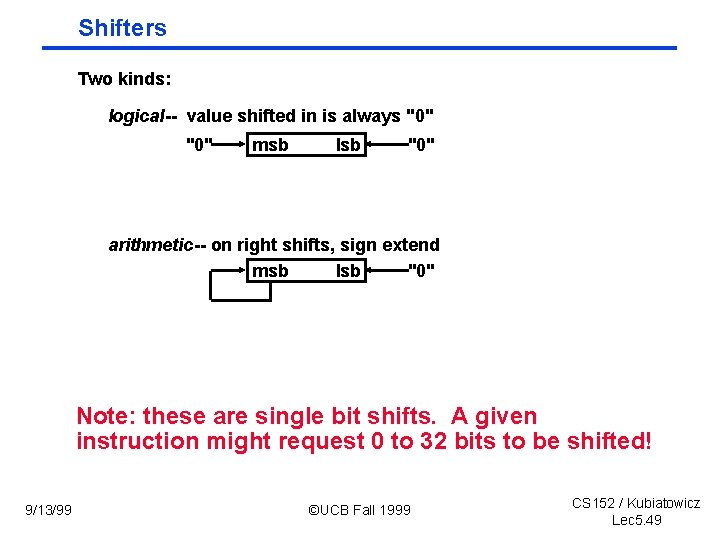

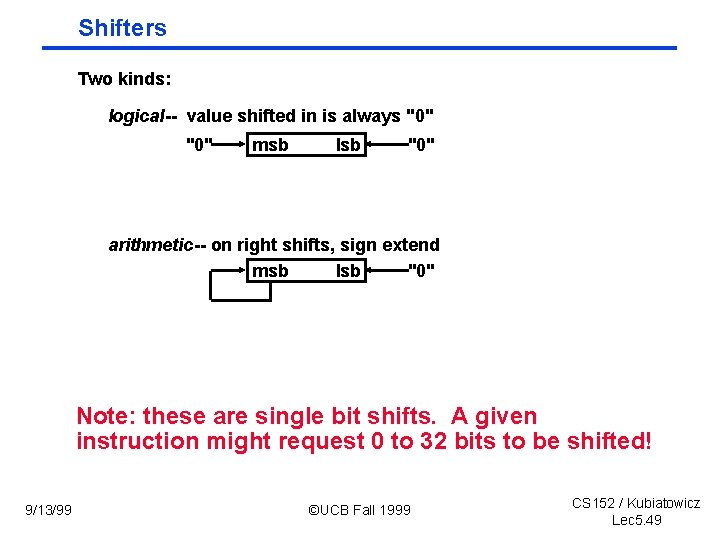

Shifters Two kinds: logical-- value shifted in is always "0" msb lsb "0" arithmetic-- on right shifts, sign extend msb lsb "0" Note: these are single bit shifts. A given instruction might request 0 to 32 bits to be shifted! 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 49

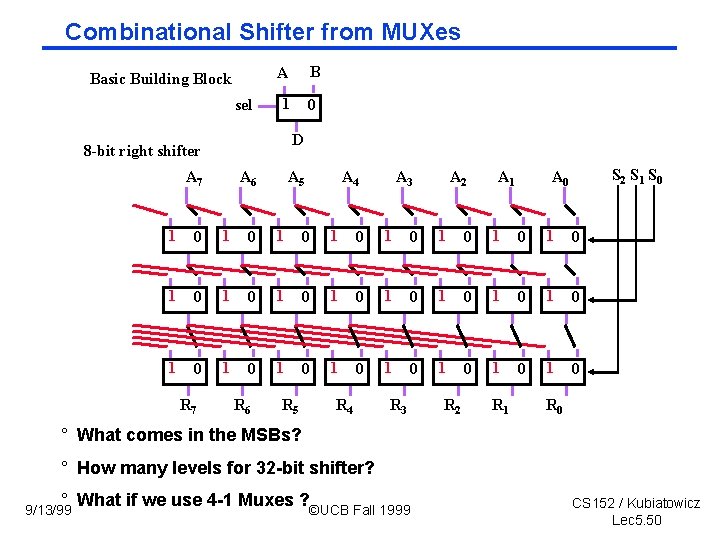

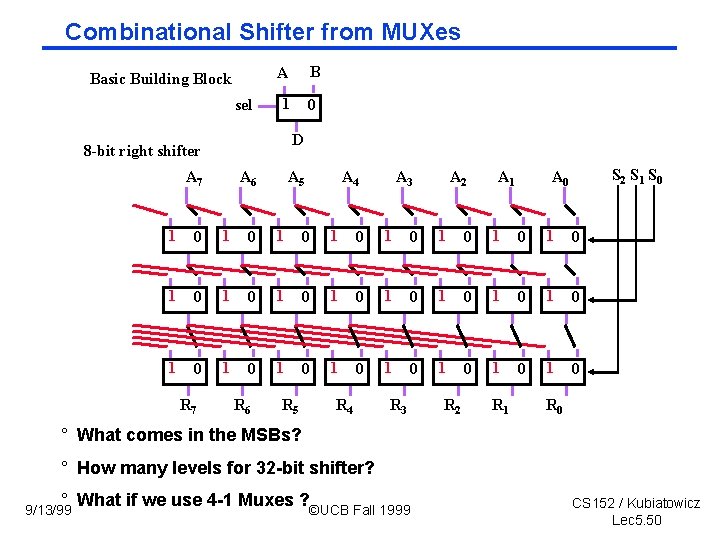

Combinational Shifter from MUXes Basic Building Block sel A B 1 0 D 8 -bit right shifter A 7 A 6 A 5 A 4 A 3 A 2 A 1 S 2 S 1 S 0 A 0 1 0 1 0 1 0 1 0 1 0 1 0 R 7 R 6 R 5 R 4 R 3 R 2 R 1 R 0 ° What comes in the MSBs? ° How many levels for 32 -bit shifter? ° What if we use 4 -1 Muxes ? ©UCB Fall 1999 9/13/99 CS 152 / Kubiatowicz Lec 5. 50

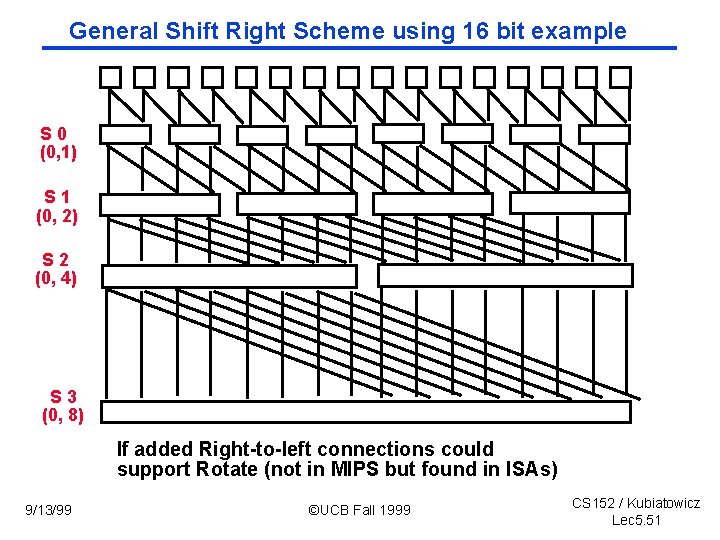

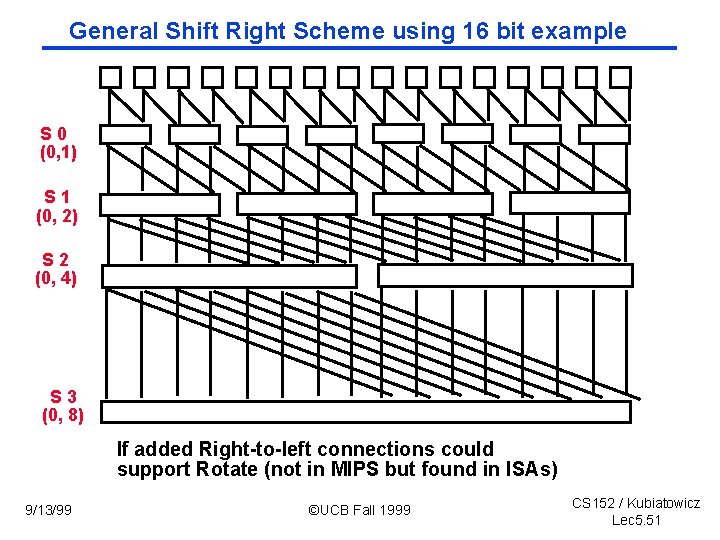

General Shift Right Scheme using 16 bit example S 0 (0, 1) S 1 (0, 2) S 2 (0, 4) S 3 (0, 8) If added Right-to-left connections could support Rotate (not in MIPS but found in ISAs) 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 51

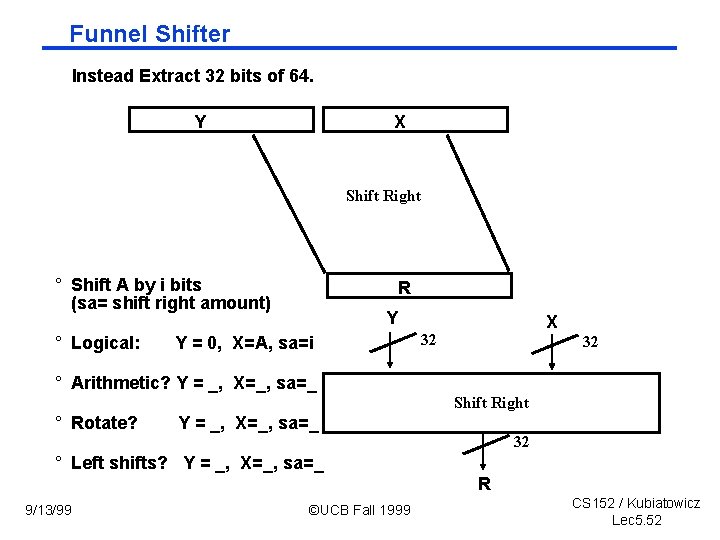

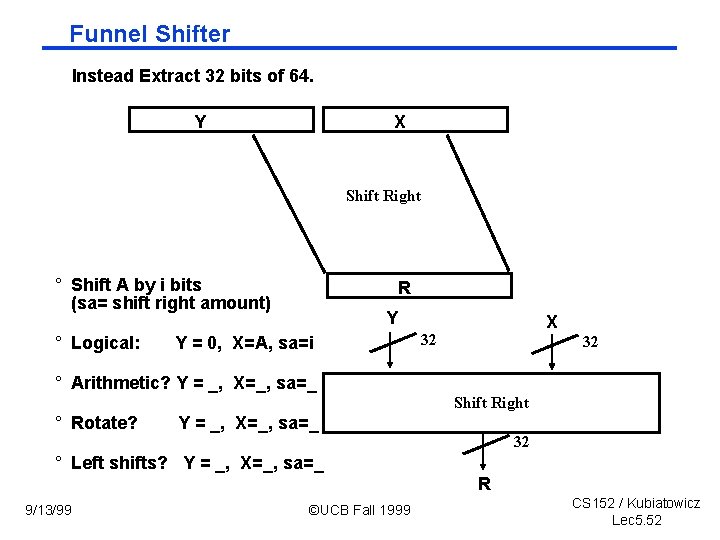

Funnel Shifter Instead Extract 32 bits of 64. Y X Shift Right ° Shift A by i bits (sa= shift right amount) ° Logical: R Y Y = 0, X=A, sa=i X 32 32 ° Arithmetic? Y = _, X=_, sa=_ Shift Right ° Rotate? Y = _, X=_, sa=_ 32 ° Left shifts? Y = _, X=_, sa=_ R 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 52

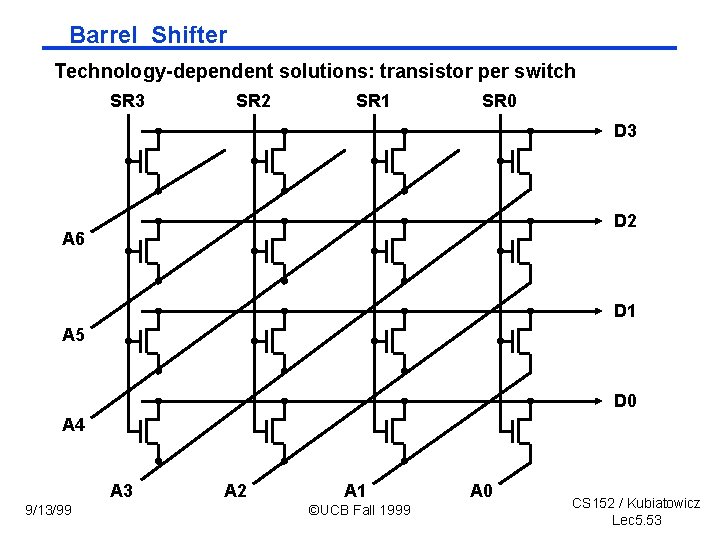

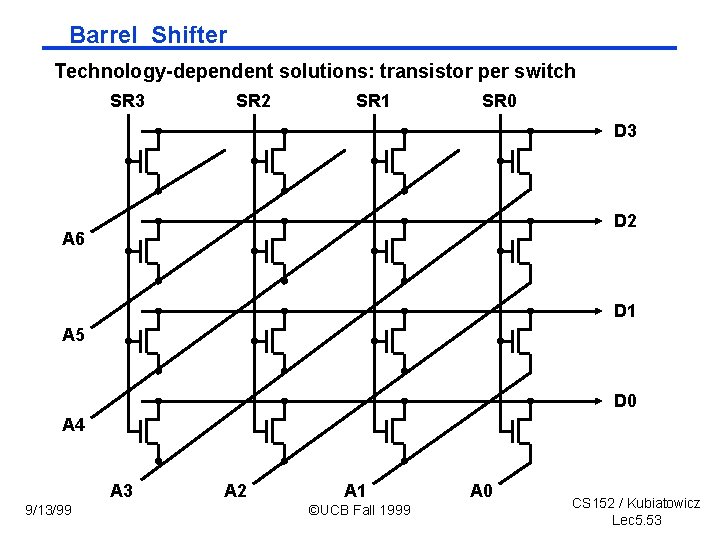

Barrel Shifter Technology-dependent solutions: transistor per switch SR 3 SR 2 SR 1 SR 0 D 3 D 2 A 6 D 1 A 5 D 0 A 4 A 3 9/13/99 A 2 A 1 ©UCB Fall 1999 A 0 CS 152 / Kubiatowicz Lec 5. 53

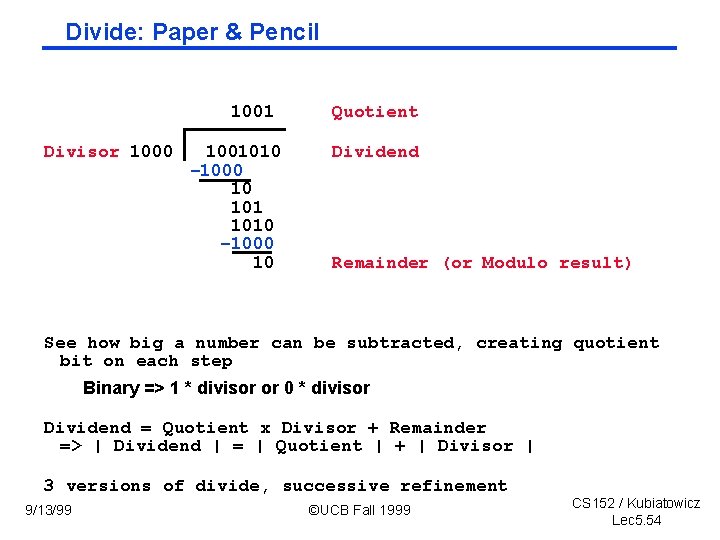

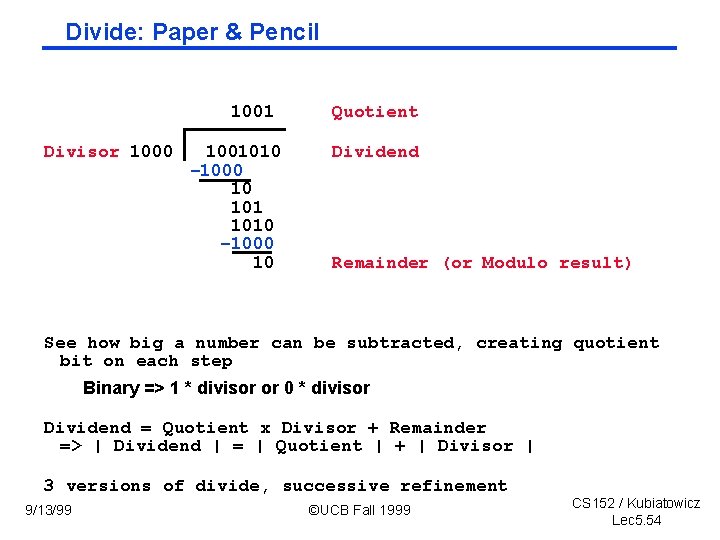

Divide: Paper & Pencil 1001 Divisor 1000 1001010 – 1000 10 Quotient Dividend Remainder (or Modulo result) See how big a number can be subtracted, creating quotient bit on each step Binary => 1 * divisor or 0 * divisor Dividend = Quotient x Divisor + Remainder => | Dividend | = | Quotient | + | Divisor | 3 versions of divide, successive refinement 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 54

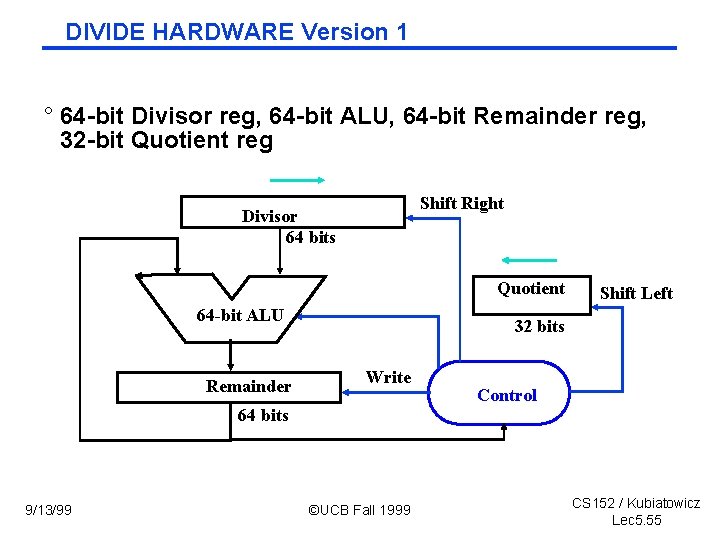

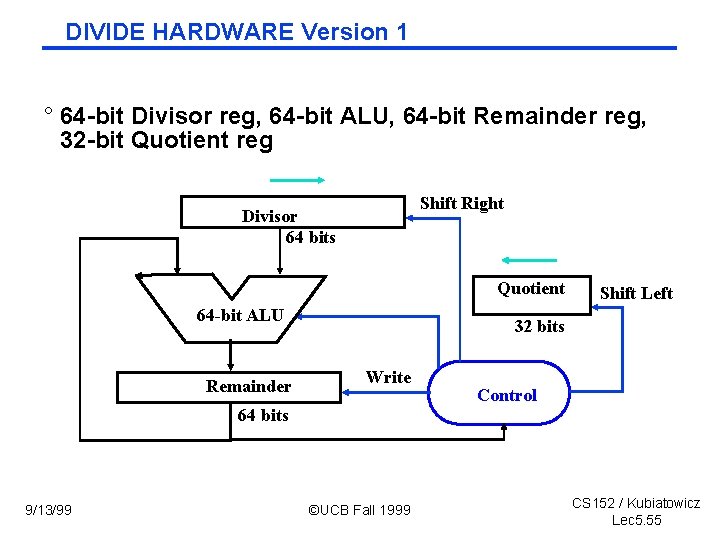

DIVIDE HARDWARE Version 1 ° 64 -bit Divisor reg, 64 -bit ALU, 64 -bit Remainder reg, 32 -bit Quotient reg Shift Right Divisor 64 bits Quotient 64 -bit ALU Remainder 32 bits Write 64 bits 9/13/99 Shift Left ©UCB Fall 1999 Control CS 152 / Kubiatowicz Lec 5. 55

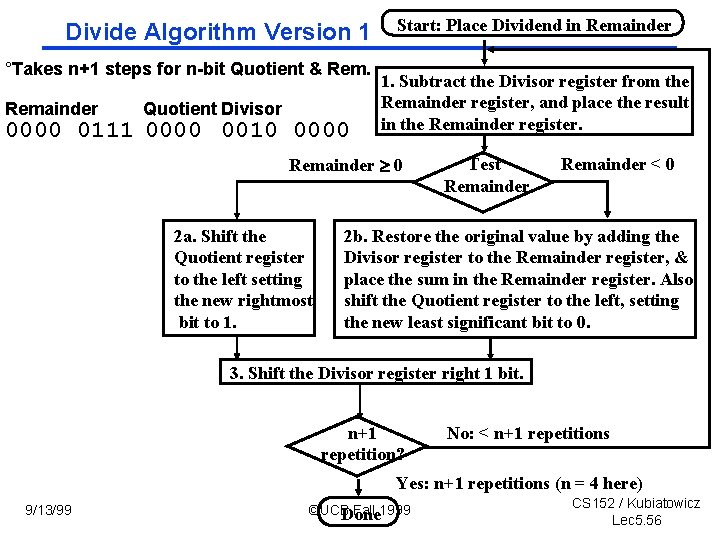

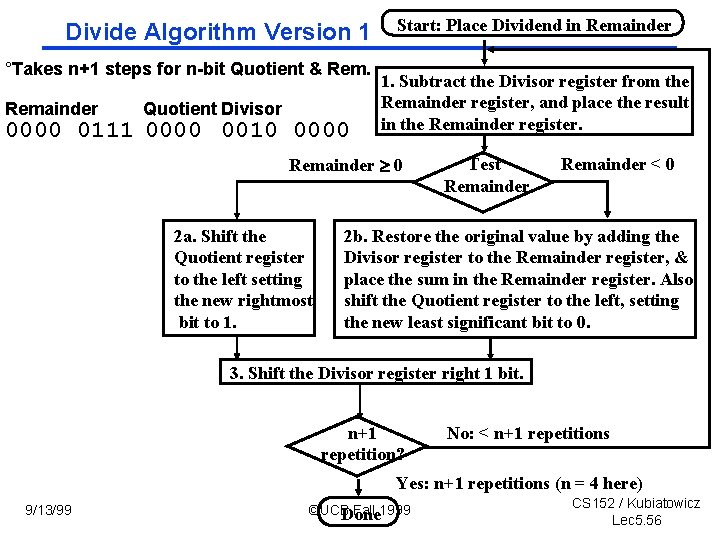

Divide Algorithm Version 1 °Takes n+1 steps for n-bit Quotient & Remainder Quotient Divisor 0000 0111 0000 0010 0000 Start: Place Dividend in Remainder 1. Subtract the Divisor register from the Remainder register, and place the result in the Remainder register. Remainder 0 2 a. Shift the Quotient register to the left setting the new rightmost bit to 1. Test Remainder < 0 2 b. Restore the original value by adding the Divisor register to the Remainder register, & place the sum in the Remainder register. Also shift the Quotient register to the left, setting the new least significant bit to 0. 3. Shift the Divisor register right 1 bit. n+1 repetition? No: < n+1 repetitions Yes: n+1 repetitions (n = 4 here) 9/13/99 ©UCB Fall 1999 Done CS 152 / Kubiatowicz Lec 5. 56

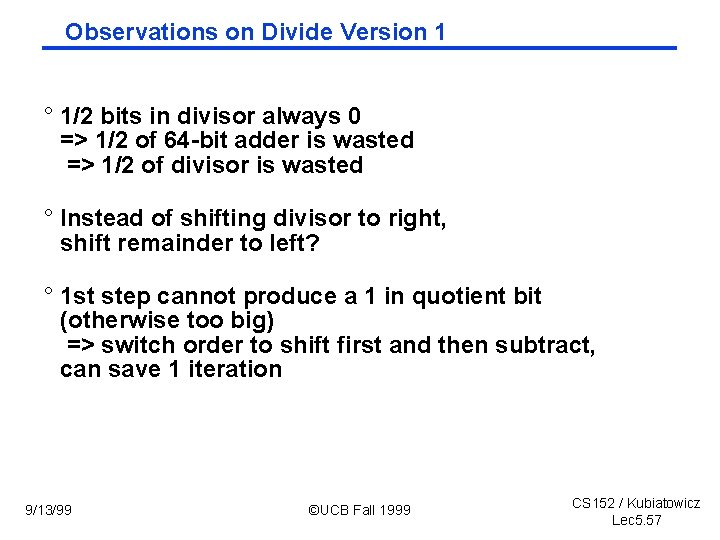

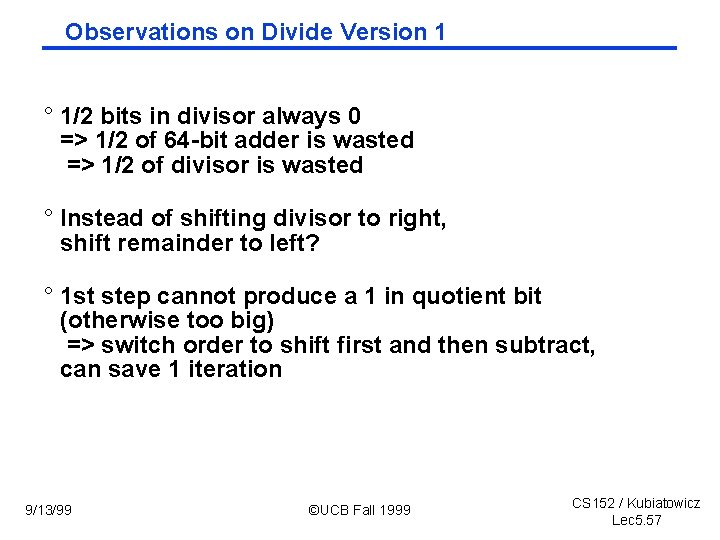

Observations on Divide Version 1 ° 1/2 bits in divisor always 0 => 1/2 of 64 -bit adder is wasted => 1/2 of divisor is wasted ° Instead of shifting divisor to right, shift remainder to left? ° 1 st step cannot produce a 1 in quotient bit (otherwise too big) => switch order to shift first and then subtract, can save 1 iteration 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 57

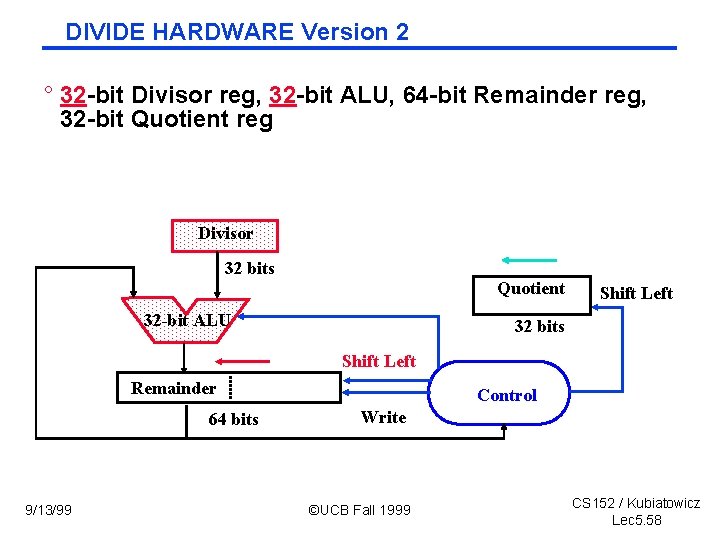

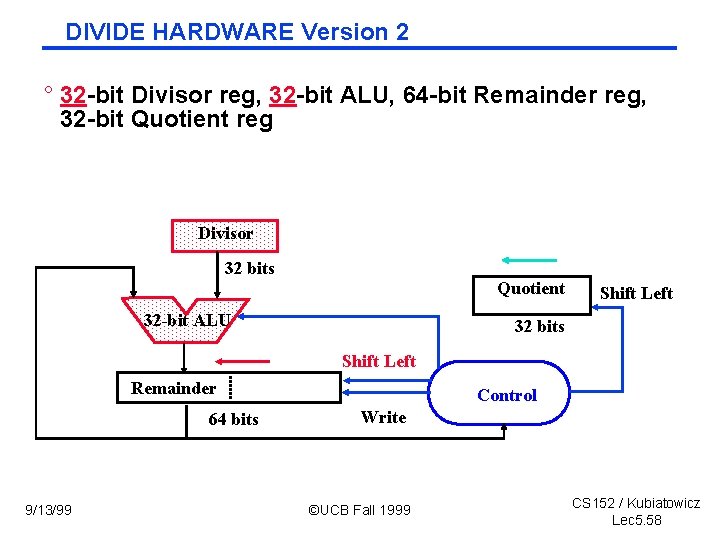

DIVIDE HARDWARE Version 2 ° 32 -bit Divisor reg, 32 -bit ALU, 64 -bit Remainder reg, 32 -bit Quotient reg Divisor 32 bits Quotient 32 -bit ALU Shift Left 32 bits Shift Left Remainder 64 bits 9/13/99 Control Write ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 58

Divide Algorithm Version 2 Remainder 0000 0111 Quotient Divisor 0000 0010 Start: Place Dividend in Remainder 1. Shift the Remainder register left 1 bit. 2. Subtract the Divisor register from the left half of the Remainder register, & place the result in the left half of the Remainder register. Remainder 0 3 a. Shift the Quotient register to the left setting the new rightmost bit to 1. Test Remainder < 0 3 b. Restore the original value by adding the Divisor register to the left half of the Remainderregister, &place the sum in the left half of the Remainder register. Also shift the Quotient register to the left, setting the new least significant bit to 0. nth repetition? No: < n repetitions Yes: n repetitions (n = 4 here) 9/13/99 ©UCB Fall 1999 Done CS 152 / Kubiatowicz Lec 5. 59

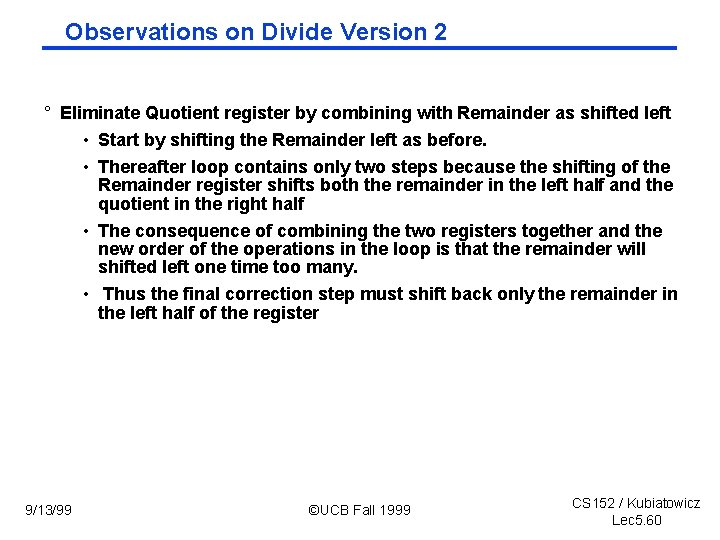

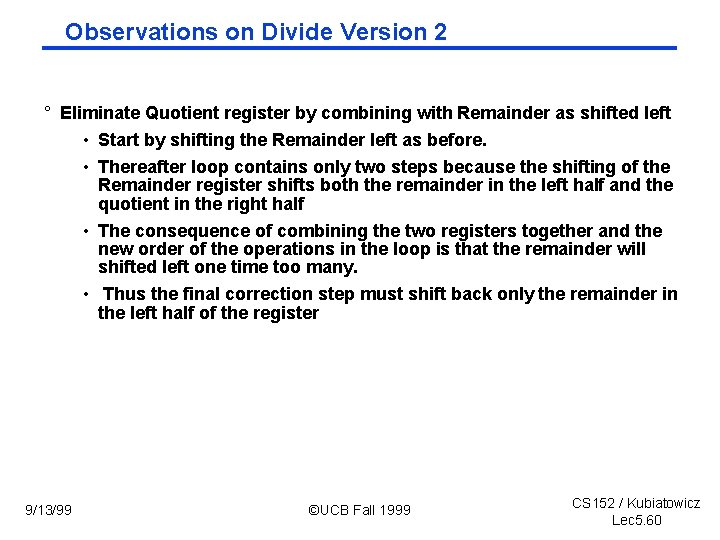

Observations on Divide Version 2 ° Eliminate Quotient register by combining with Remainder as shifted left • Start by shifting the Remainder left as before. • Thereafter loop contains only two steps because the shifting of the Remainder register shifts both the remainder in the left half and the quotient in the right half • The consequence of combining the two registers together and the new order of the operations in the loop is that the remainder will shifted left one time too many. • Thus the final correction step must shift back only the remainder in the left half of the register 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 60

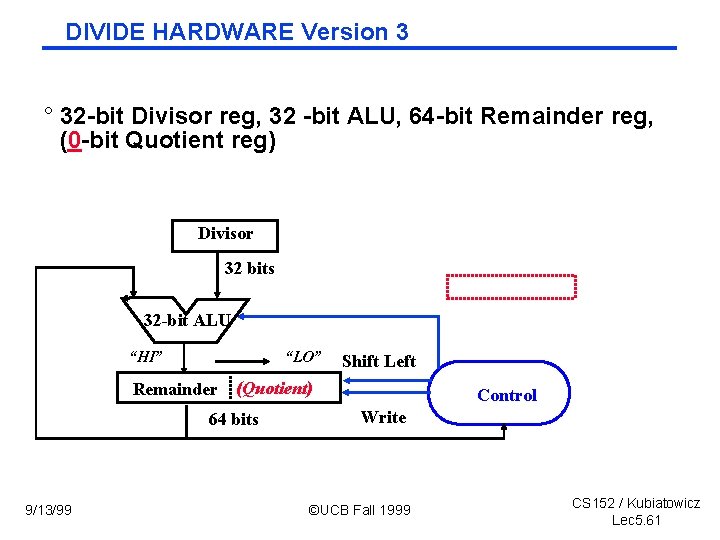

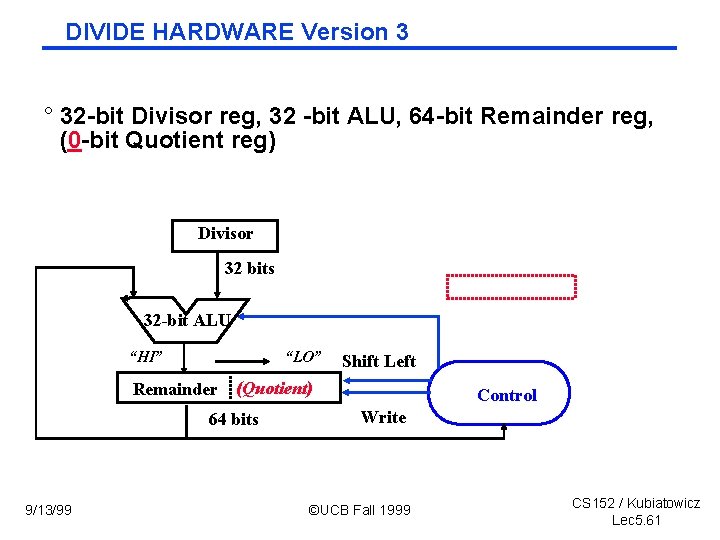

DIVIDE HARDWARE Version 3 ° 32 -bit Divisor reg, 32 -bit ALU, 64 -bit Remainder reg, (0 -bit Quotient reg) Divisor 32 bits 32 -bit ALU “HI” “LO” Shift Left Remainder (Quotient) 64 bits 9/13/99 Control Write ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 61

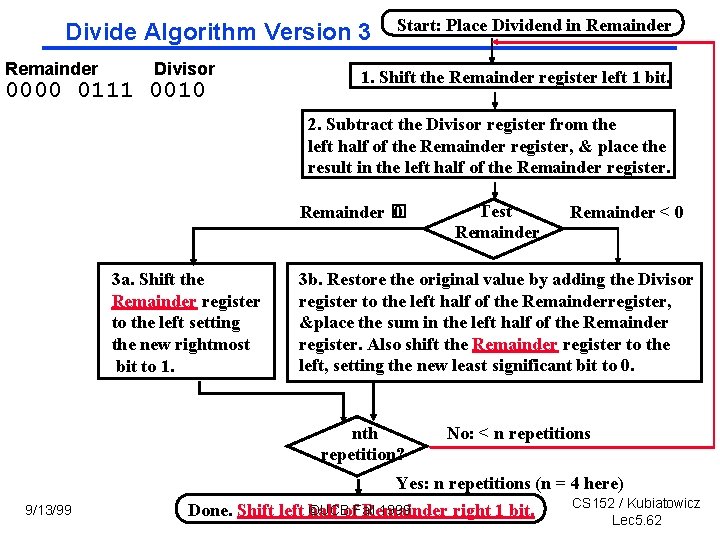

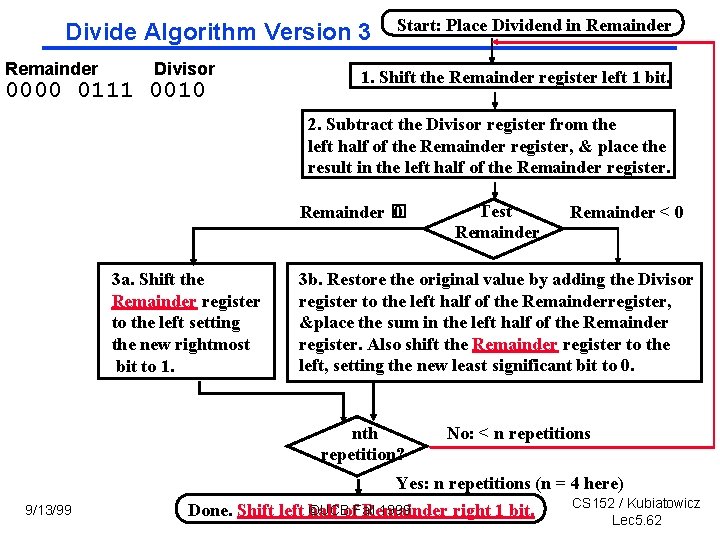

Divide Algorithm Version 3 Remainder Divisor 0000 0111 0010 Start: Place Dividend in Remainder 1. Shift the Remainder register left 1 bit. 2. Subtract the Divisor register from the left half of the Remainder register, & place the result in the left half of the Remainder register. Remainder � 0 3 a. Shift the Remainder register to the left setting the new rightmost bit to 1. Test Remainder < 0 3 b. Restore the original value by adding the Divisor register to the left half of the Remainderregister, &place the sum in the left half of the Remainder register. Also shift the Remainder register to the left, setting the new least significant bit to 0. nth repetition? No: < n repetitions Yes: n repetitions (n = 4 here) 9/13/99 ©UCBof. Fall 1999 Done. Shift left half Remainder right 1 bit. CS 152 / Kubiatowicz Lec 5. 62

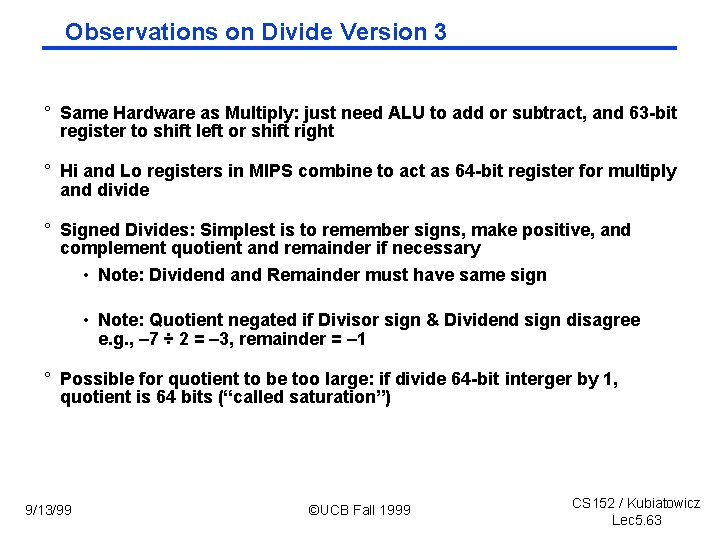

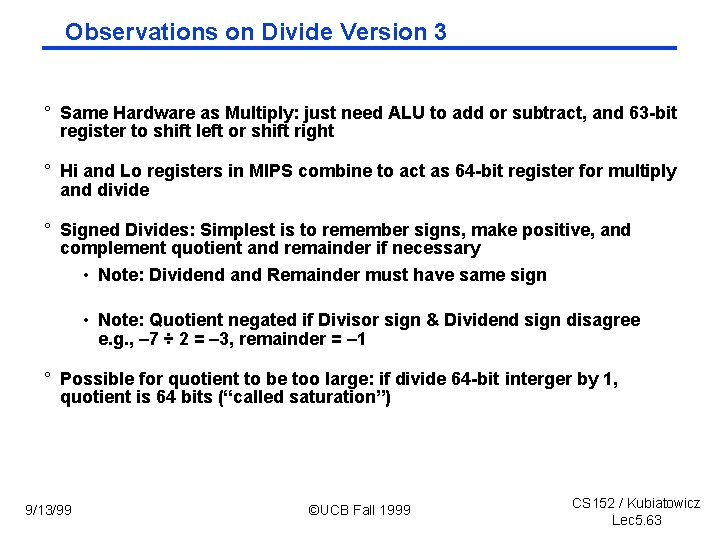

Observations on Divide Version 3 ° Same Hardware as Multiply: just need ALU to add or subtract, and 63 -bit register to shift left or shift right ° Hi and Lo registers in MIPS combine to act as 64 -bit register for multiply and divide ° Signed Divides: Simplest is to remember signs, make positive, and complement quotient and remainder if necessary • Note: Dividend and Remainder must have same sign • Note: Quotient negated if Divisor sign & Dividend sign disagree e. g. , – 7 ÷ 2 = – 3, remainder = – 1 ° Possible for quotient to be too large: if divide 64 -bit interger by 1, quotient is 64 bits (“called saturation”) 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 63

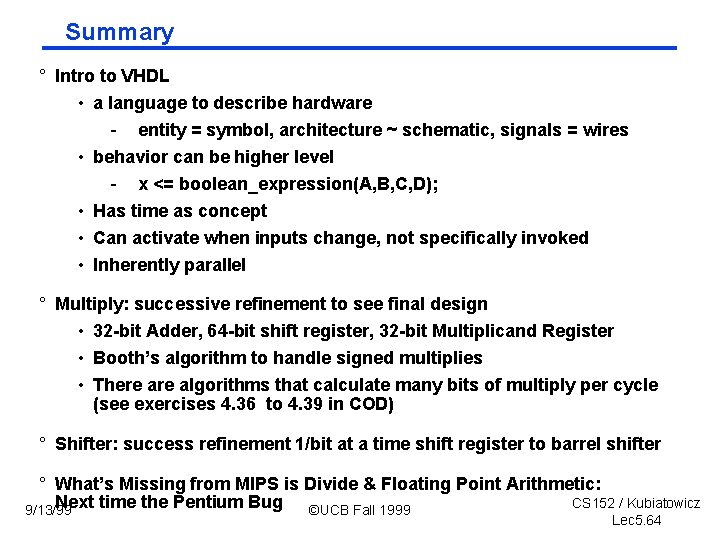

Summary ° Intro to VHDL • a language to describe hardware - entity = symbol, architecture ~ schematic, signals = wires • behavior can be higher level - x <= boolean_expression(A, B, C, D); • Has time as concept • Can activate when inputs change, not specifically invoked • Inherently parallel ° Multiply: successive refinement to see final design • 32 -bit Adder, 64 -bit shift register, 32 -bit Multiplicand Register • Booth’s algorithm to handle signed multiplies • There algorithms that calculate many bits of multiply per cycle (see exercises 4. 36 to 4. 39 in COD) ° Shifter: success refinement 1/bit at a time shift register to barrel shifter ° What’s Missing from MIPS is Divide & Floating Point Arithmetic: CS 152 / Kubiatowicz Next time the Pentium Bug ©UCB Fall 1999 9/13/99 Lec 5. 64

To Get More Information ° Chapter 4 of your text book: • David Patterson & John Hennessy, “Computer Organization & Design, ” Morgan Kaufmann Publishers, 1994. ° David Winkel & Franklin Prosser, “The Art of Digital Design: An Introduction to Top-Down Design, ” Prentice-Hall, Inc. , 1980. ° Kai Hwang, “Computer Arithmetic: Principles, archtiecture, and design”, Wiley 1979 9/13/99 ©UCB Fall 1999 CS 152 / Kubiatowicz Lec 5. 65