Computer Architecture Prof Dr Nizamettin AYDIN naydinyildiz edu

![MIPS operands • Memory Operand example 2: – C code: A[12] = h + MIPS operands • Memory Operand example 2: – C code: A[12] = h +](https://slidetodoc.com/presentation_image_h2/466e99688b457ed636ed0f5b53a22b5c/image-10.jpg)

- Slides: 44

Computer Architecture Prof. Dr. Nizamettin AYDIN naydin@yildiz. edu. tr nizamettinaydin@gmail. com http: //www. yildiz. edu. tr/~naydin 1

MIPS Instruction Set-I 2

Outline • MIPS Instruction Set – Overview – MIPS operands • Register operands • Memory operands • Immediate operands – MIPS instruction formats – MIPS operations • Aritmetic operations • Logical operations – Hexadecimal notation 3

Instructions: Overview • Language of the machine • More primitive than higher level languages, – e. g. , no sophisticated control flow such as while or for loops • Very restrictive – e. g. , MIPS arithmetic instructions • MIPS instruction set architecture – inspired most architectures developed since the 80's • used by NEC, Nintendo, Silicon Graphics, Sony – Design goals • maximize performance and minimize cost and reduce design time 4

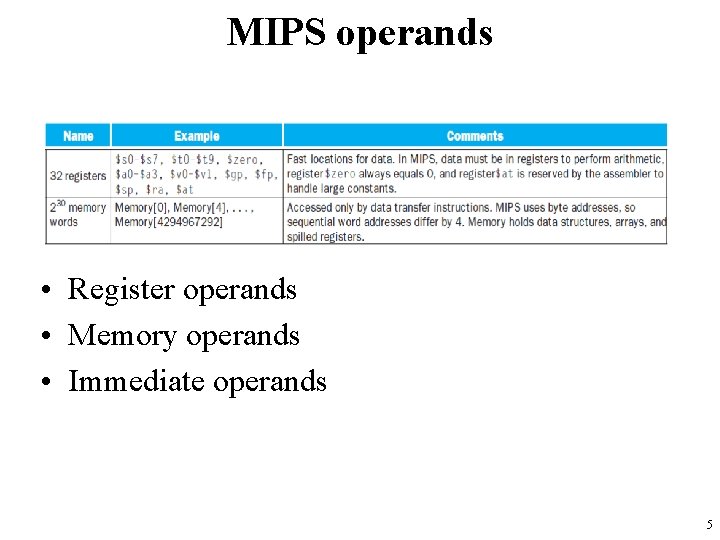

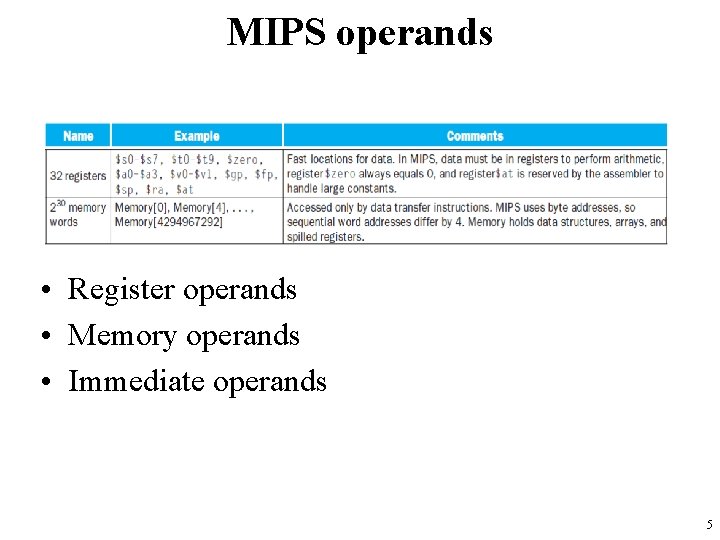

MIPS operands • Register operands • Memory operands • Immediate operands 5

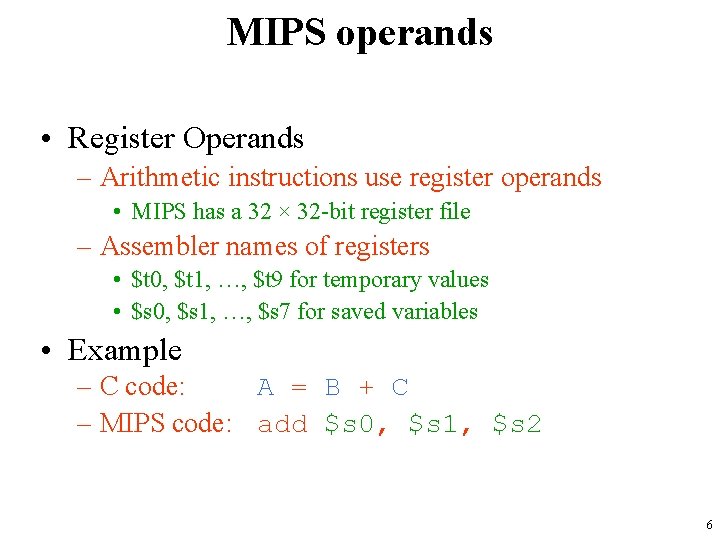

MIPS operands • Register Operands – Arithmetic instructions use register operands • MIPS has a 32 × 32 -bit register file – Assembler names of registers • $t 0, $t 1, …, $t 9 for temporary values • $s 0, $s 1, …, $s 7 for saved variables • Example – C code: A = B + C – MIPS code: add $s 0, $s 1, $s 2 6

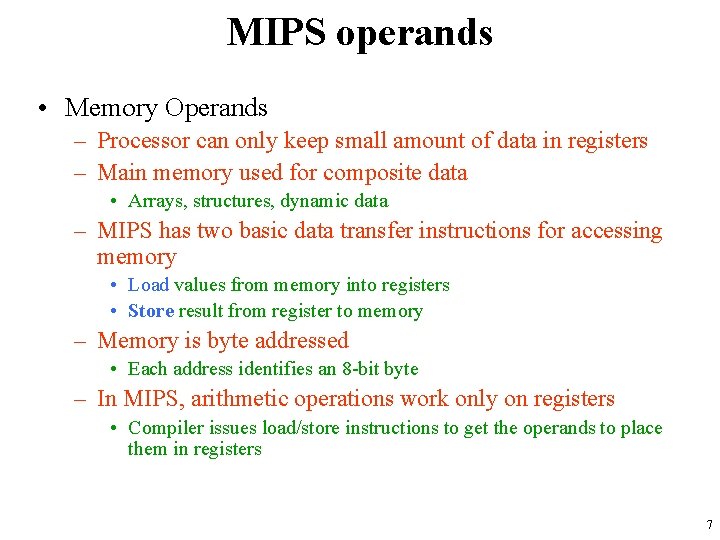

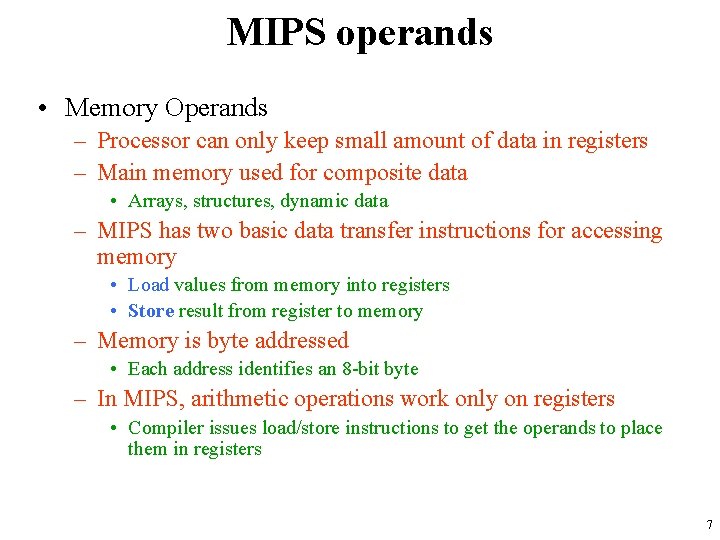

MIPS operands • Memory Operands – Processor can only keep small amount of data in registers – Main memory used for composite data • Arrays, structures, dynamic data – MIPS has two basic data transfer instructions for accessing memory • Load values from memory into registers • Store result from register to memory – Memory is byte addressed • Each address identifies an 8 -bit byte – In MIPS, arithmetic operations work only on registers • Compiler issues load/store instructions to get the operands to place them in registers 7

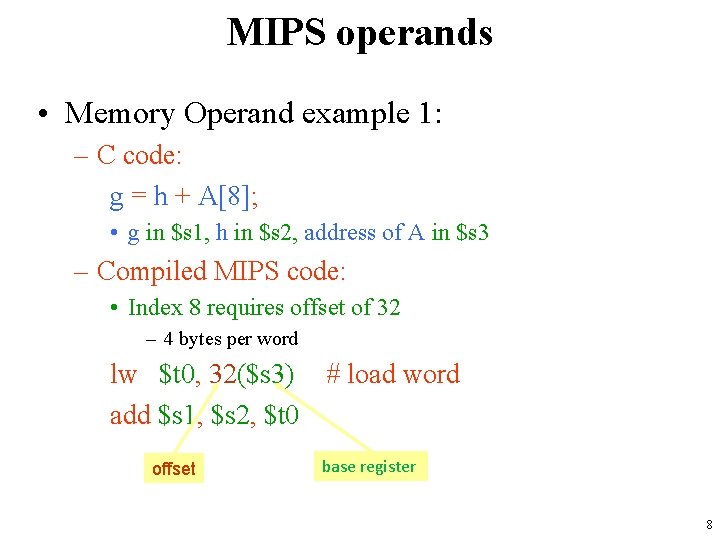

MIPS operands • Memory Operand example 1: – C code: g = h + A[8]; • g in $s 1, h in $s 2, address of A in $s 3 – Compiled MIPS code: • Index 8 requires offset of 32 – 4 bytes per word lw $t 0, 32($s 3) # load word add $s 1, $s 2, $t 0 offset base register 8

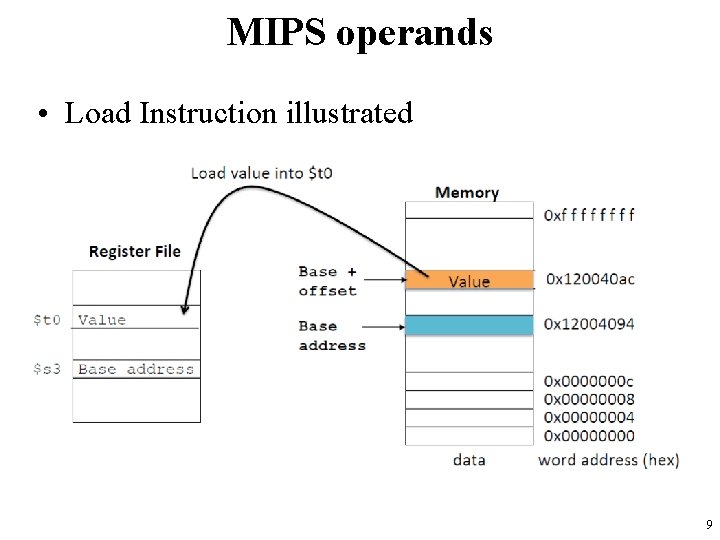

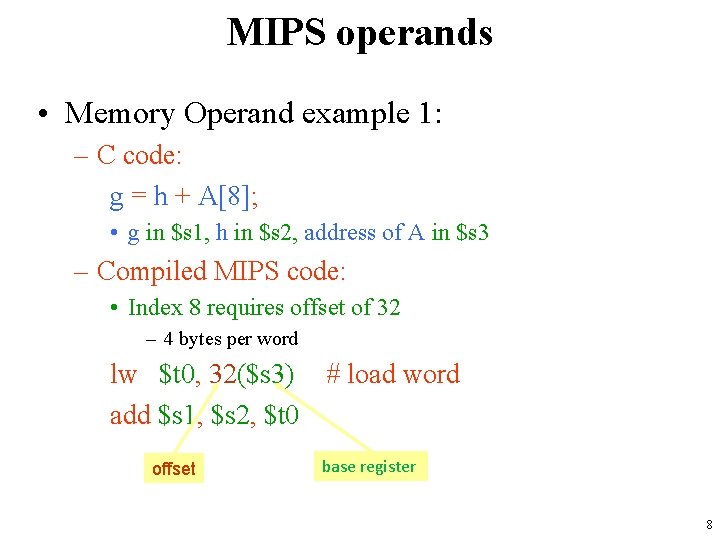

MIPS operands • Load Instruction illustrated 9

![MIPS operands Memory Operand example 2 C code A12 h MIPS operands • Memory Operand example 2: – C code: A[12] = h +](https://slidetodoc.com/presentation_image_h2/466e99688b457ed636ed0f5b53a22b5c/image-10.jpg)

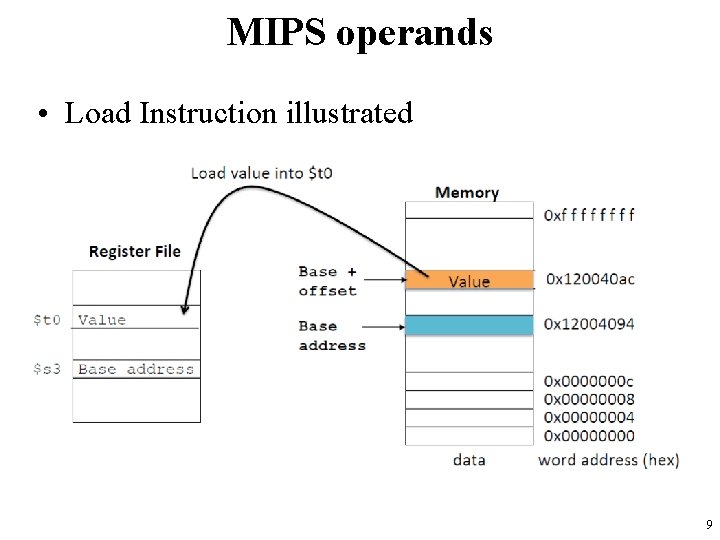

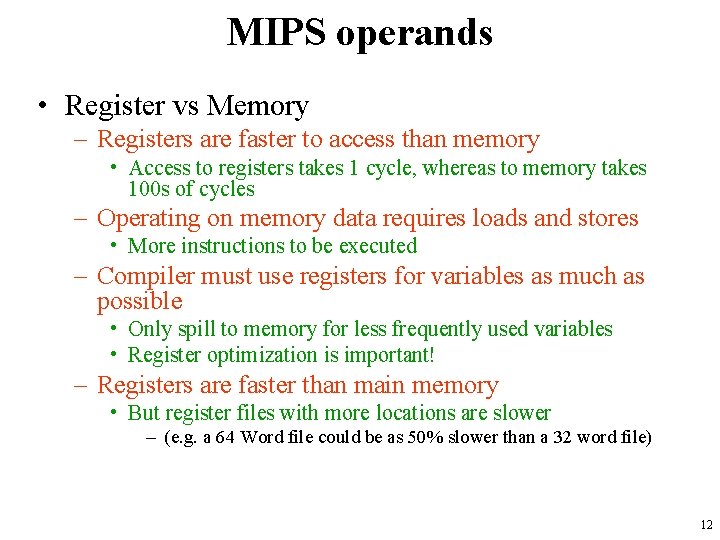

MIPS operands • Memory Operand example 2: – C code: A[12] = h + A[8]; • h in $s 2, base address of A in $s 3 – Compiled MIPS code: • Index 8 requires offset of 32 lw $t 0, 32($s 3) add $t 0, $s 2, $t 0 sw $t 0, 48($s 3) # load word # store word 10

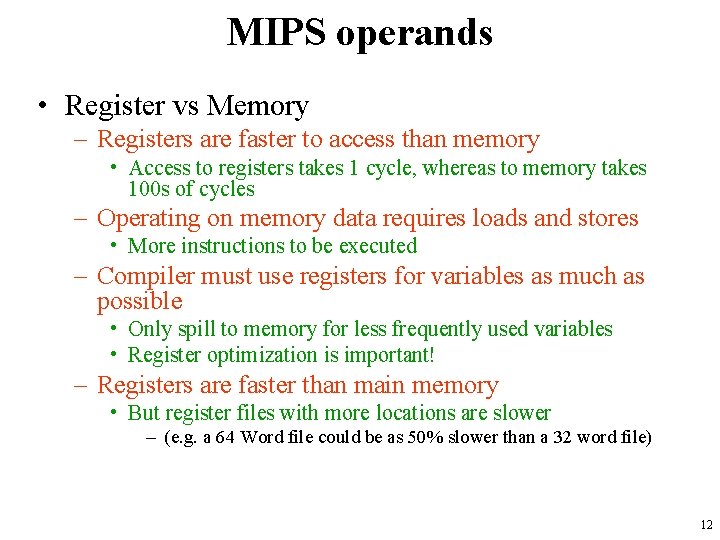

MIPS operands • Store Instruction illustrated: 11

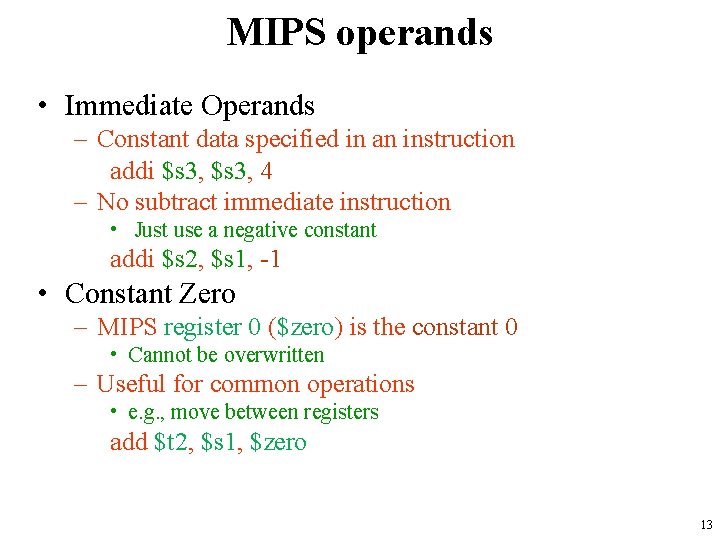

MIPS operands • Register vs Memory – Registers are faster to access than memory • Access to registers takes 1 cycle, whereas to memory takes 100 s of cycles – Operating on memory data requires loads and stores • More instructions to be executed – Compiler must use registers for variables as much as possible • Only spill to memory for less frequently used variables • Register optimization is important! – Registers are faster than main memory • But register files with more locations are slower – (e. g. a 64 Word file could be as 50% slower than a 32 word file) 12

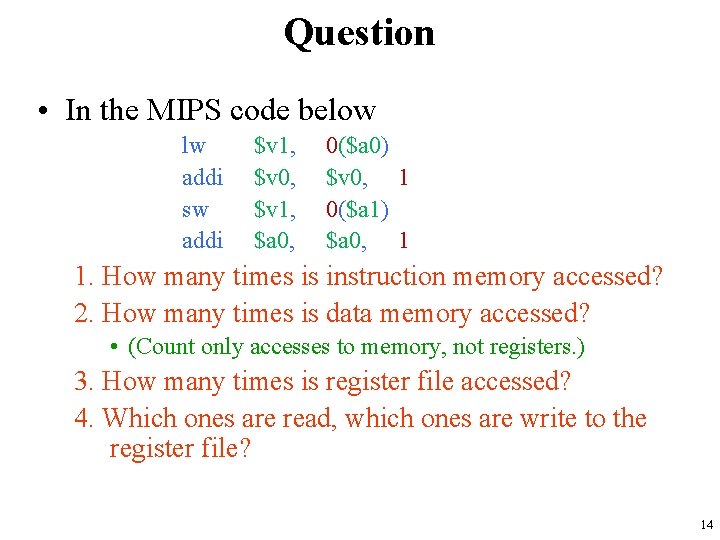

MIPS operands • Immediate Operands – Constant data specified in an instruction addi $s 3, 4 – No subtract immediate instruction • Just use a negative constant addi $s 2, $s 1, -1 • Constant Zero – MIPS register 0 ($zero) is the constant 0 • Cannot be overwritten – Useful for common operations • e. g. , move between registers add $t 2, $s 1, $zero 13

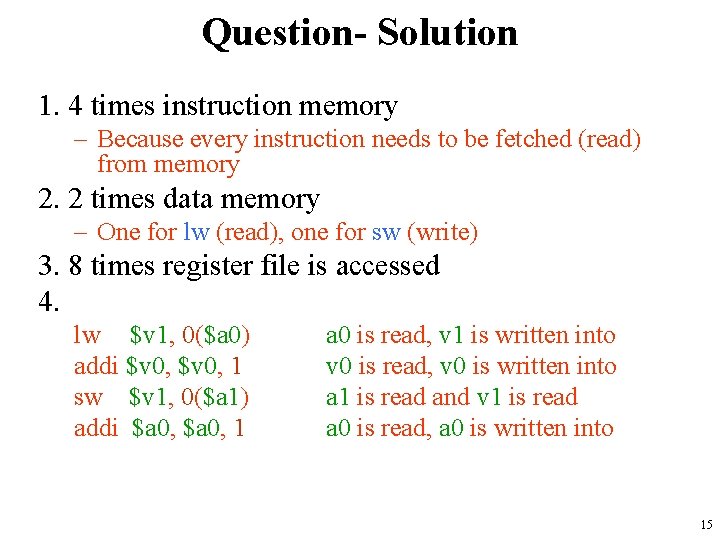

Question • In the MIPS code below lw addi sw addi $v 1, $v 0, $v 1, $a 0, 0($a 0) $v 0, 1 0($a 1) $a 0, 1 1. How many times is instruction memory accessed? 2. How many times is data memory accessed? • (Count only accesses to memory, not registers. ) 3. How many times is register file accessed? 4. Which ones are read, which ones are write to the register file? 14

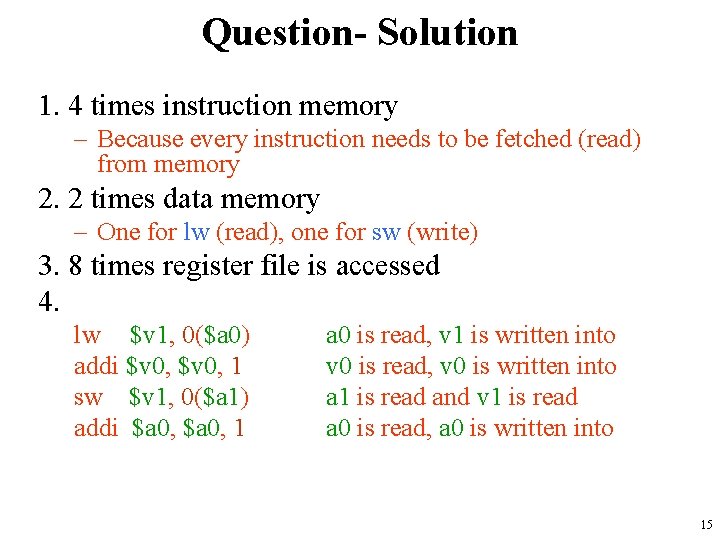

Question- Solution 1. 4 times instruction memory – Because every instruction needs to be fetched (read) from memory 2. 2 times data memory – One for lw (read), one for sw (write) 3. 8 times register file is accessed 4. lw $v 1, 0($a 0) addi $v 0, 1 sw $v 1, 0($a 1) addi $a 0, 1 a 0 is read, v 1 is written into v 0 is read, v 0 is written into a 1 is read and v 1 is read a 0 is read, a 0 is written into 15

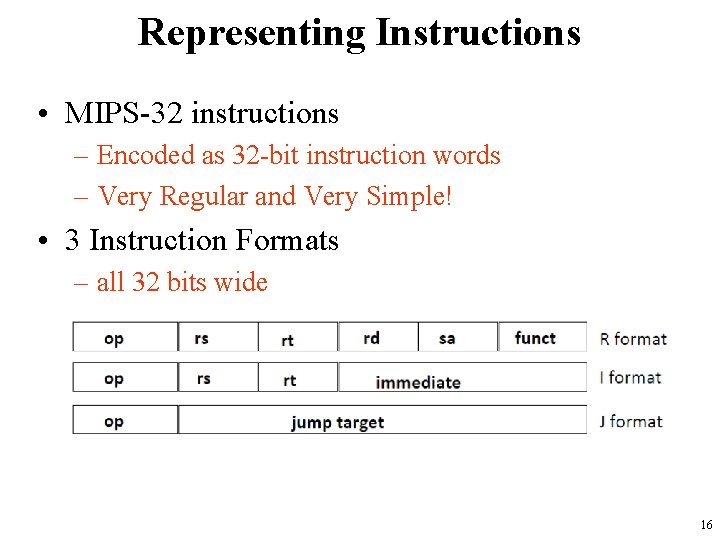

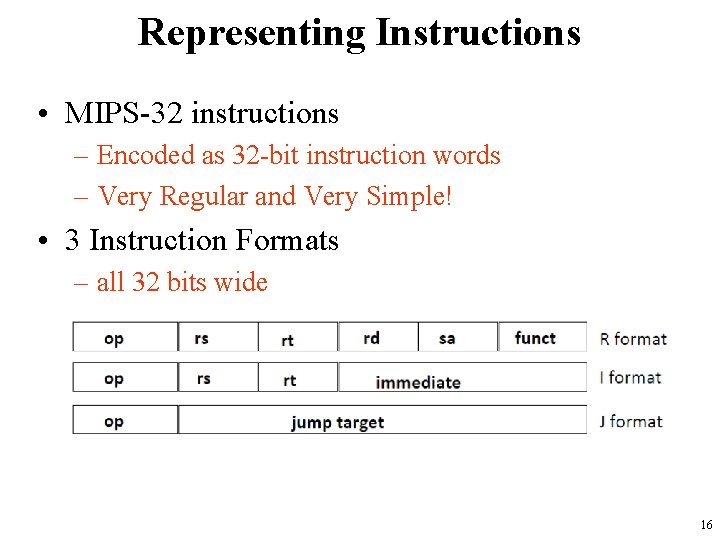

Representing Instructions • MIPS-32 instructions – Encoded as 32 -bit instruction words – Very Regular and Very Simple! • 3 Instruction Formats – all 32 bits wide 16

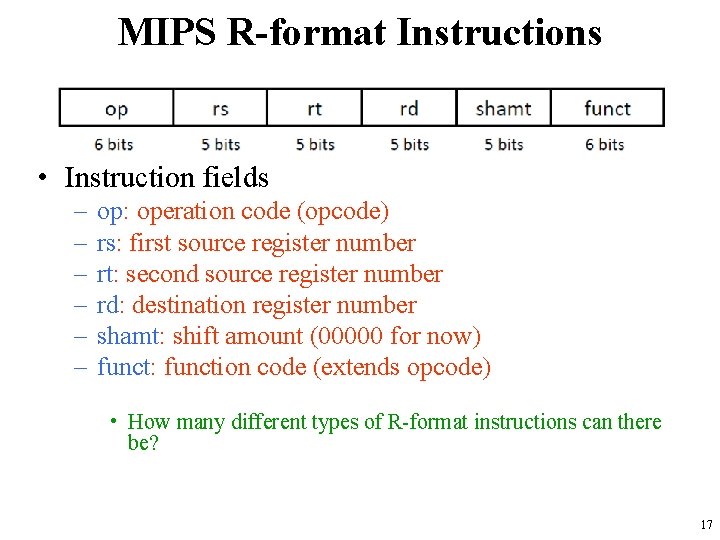

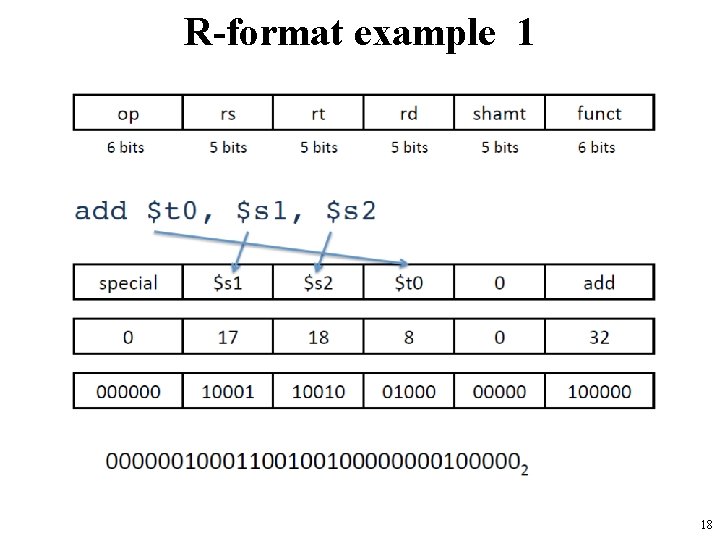

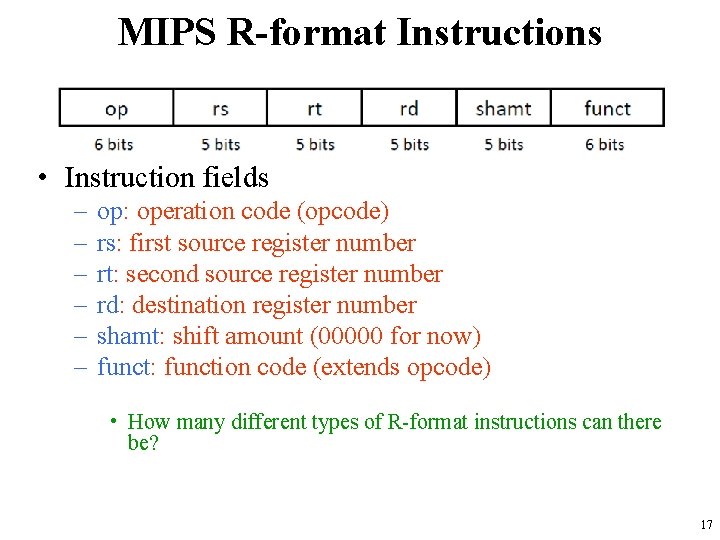

MIPS R-format Instructions • Instruction fields – – – op: operation code (opcode) rs: first source register number rt: second source register number rd: destination register number shamt: shift amount (00000 for now) funct: function code (extends opcode) • How many different types of R-format instructions can there be? 17

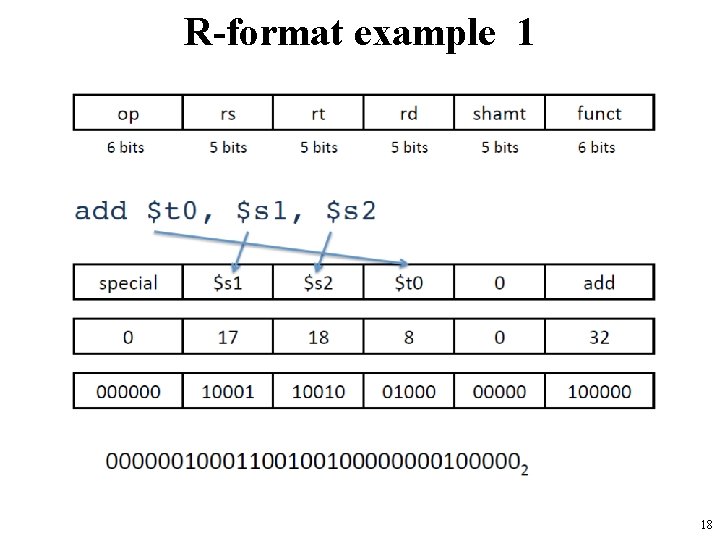

R-format example 1 18

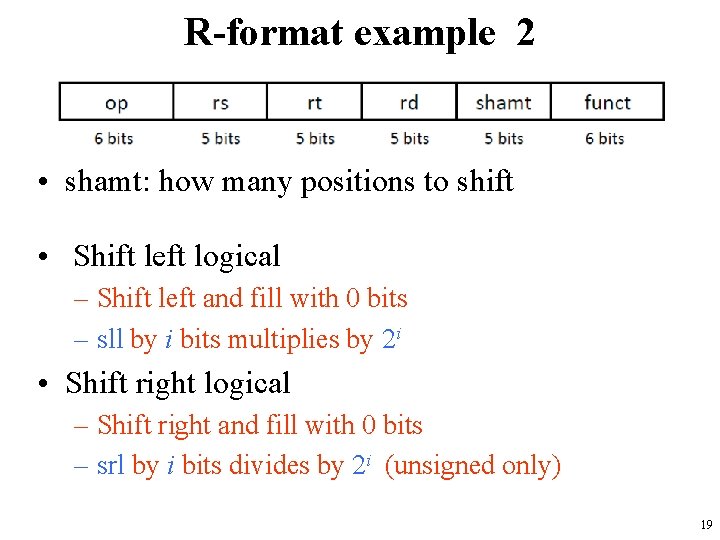

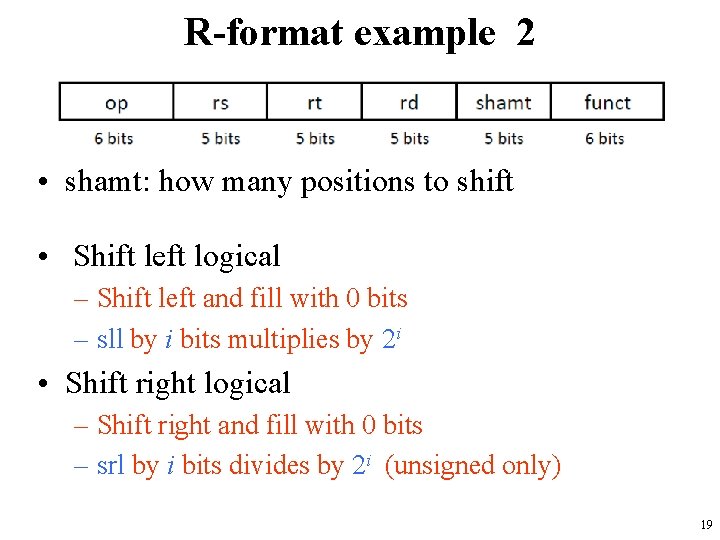

R-format example 2 • shamt: how many positions to shift • Shift left logical – Shift left and fill with 0 bits – sll by i bits multiplies by 2 i • Shift right logical – Shift right and fill with 0 bits – srl by i bits divides by 2 i (unsigned only) 19

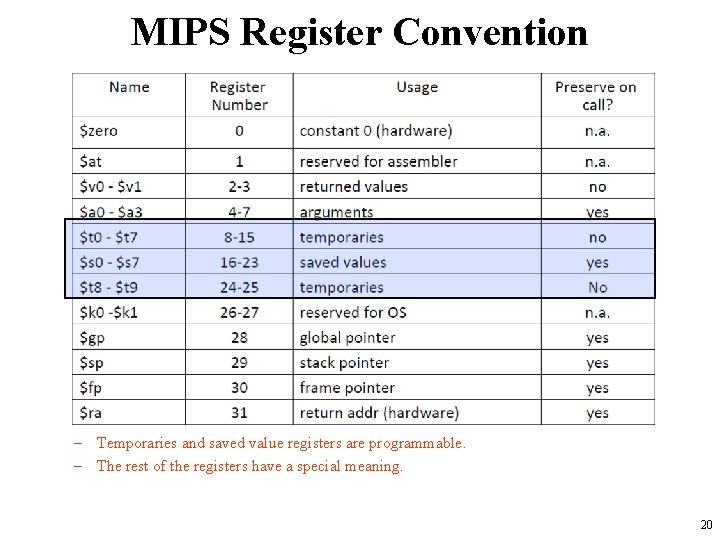

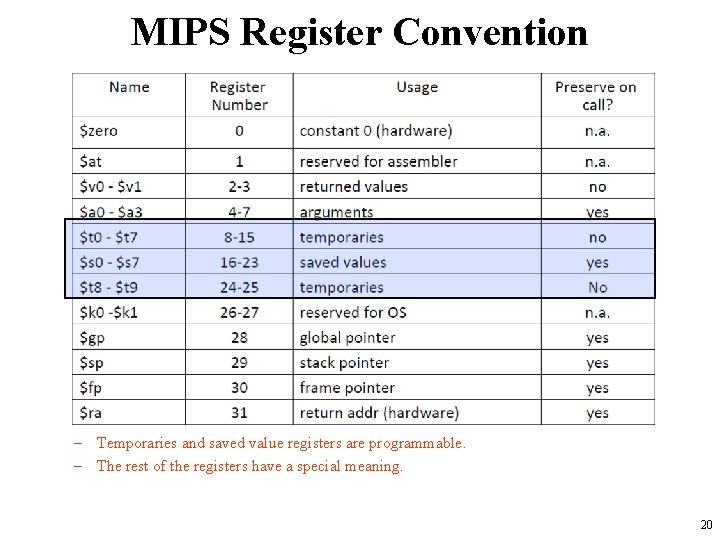

MIPS Register Convention – Temporaries and saved value registers are programmable. – The rest of the registers have a special meaning. 20

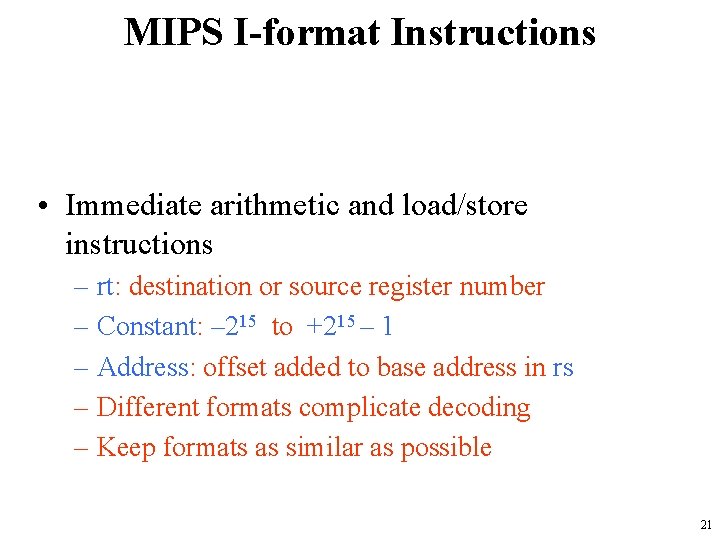

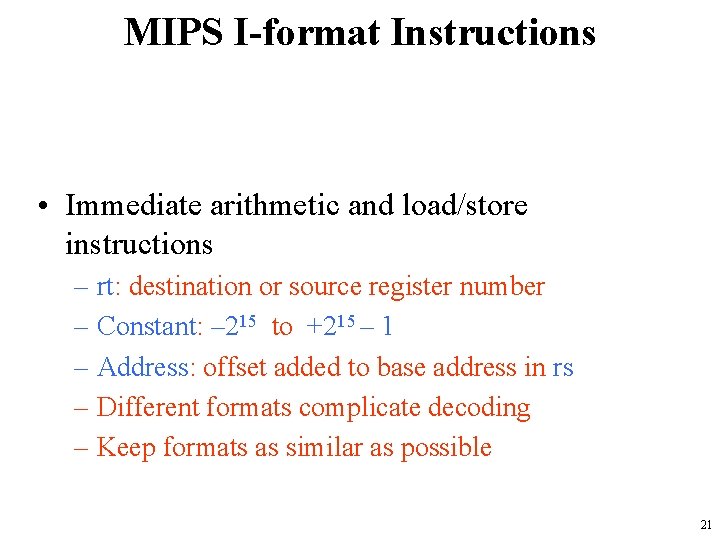

MIPS I-format Instructions • Immediate arithmetic and load/store instructions – rt: destination or source register number – Constant: – 215 to +215 – 1 – Address: offset added to base address in rs – Different formats complicate decoding – Keep formats as similar as possible 21

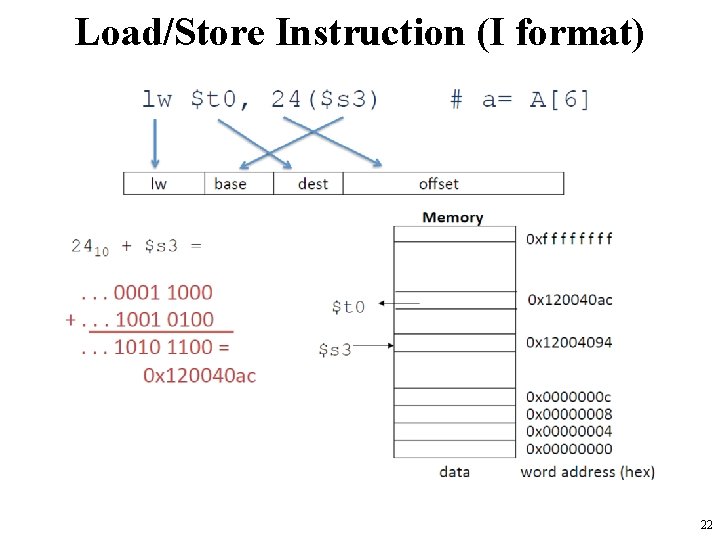

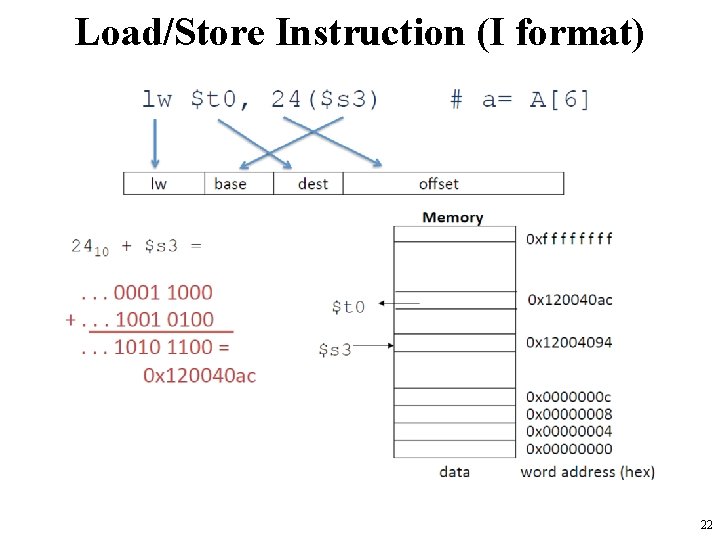

Load/Store Instruction (I format) 22

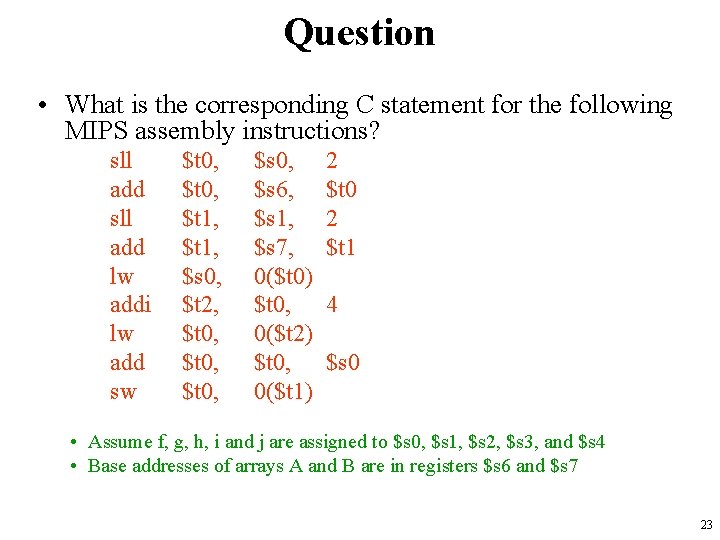

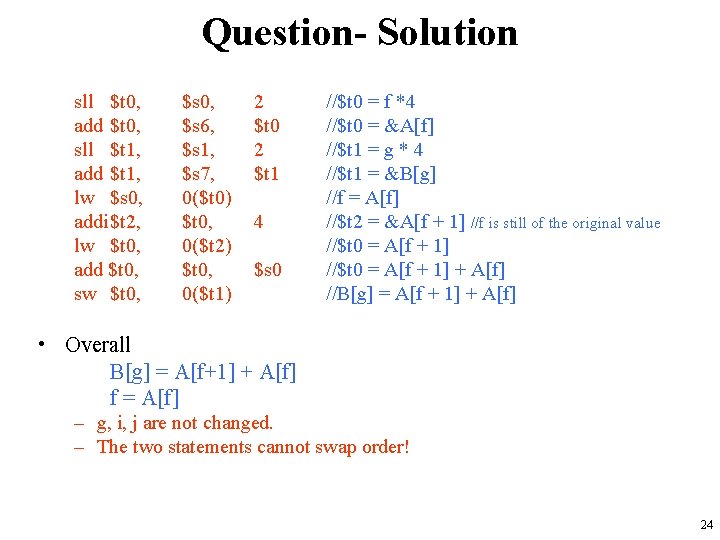

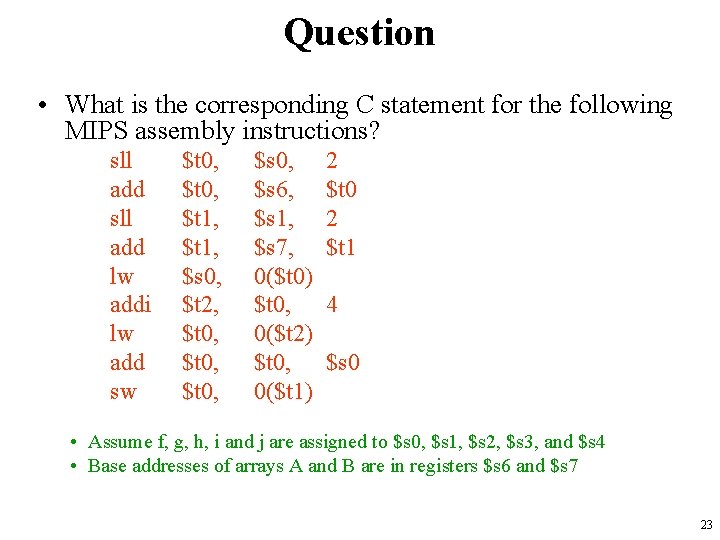

Question • What is the corresponding C statement for the following MIPS assembly instructions? sll add lw addi lw add sw $t 0, $t 1, $s 0, $t 2, $t 0, $s 0, $s 6, $s 1, $s 7, 0($t 0) $t 0, 0($t 2) $t 0, 0($t 1) 2 $t 0 2 $t 1 4 $s 0 • Assume f, g, h, i and j are assigned to $s 0, $s 1, $s 2, $s 3, and $s 4 • Base addresses of arrays A and B are in registers $s 6 and $s 7 23

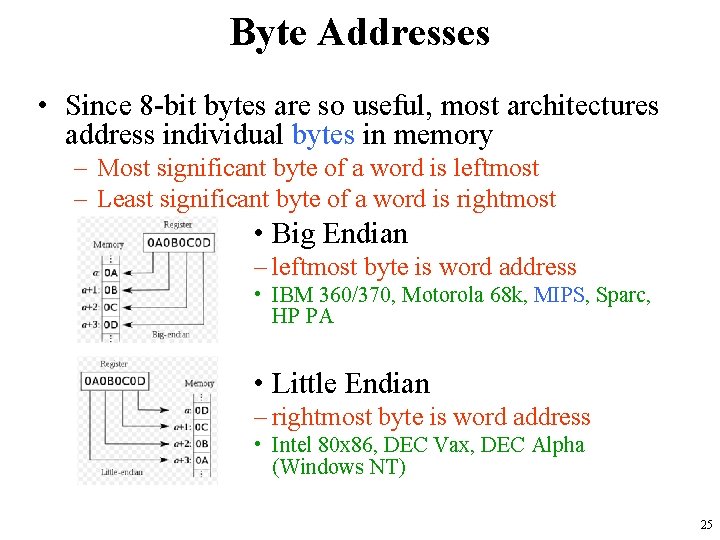

Question- Solution sll $t 0, add $t 0, sll $t 1, add $t 1, lw $s 0, addi$t 2, lw $t 0, add $t 0, sw $t 0, $s 0, $s 6, $s 1, $s 7, 0($t 0) $t 0, 0($t 2) $t 0, 0($t 1) 2 $t 0 2 $t 1 4 $s 0 //$t 0 = f *4 //$t 0 = &A[f] //$t 1 = g * 4 //$t 1 = &B[g] //f = A[f] //$t 2 = &A[f + 1] //f is still of the original value //$t 0 = A[f + 1] + A[f] //B[g] = A[f + 1] + A[f] • Overall B[g] = A[f+1] + A[f] f = A[f] – g, i, j are not changed. – The two statements cannot swap order! 24

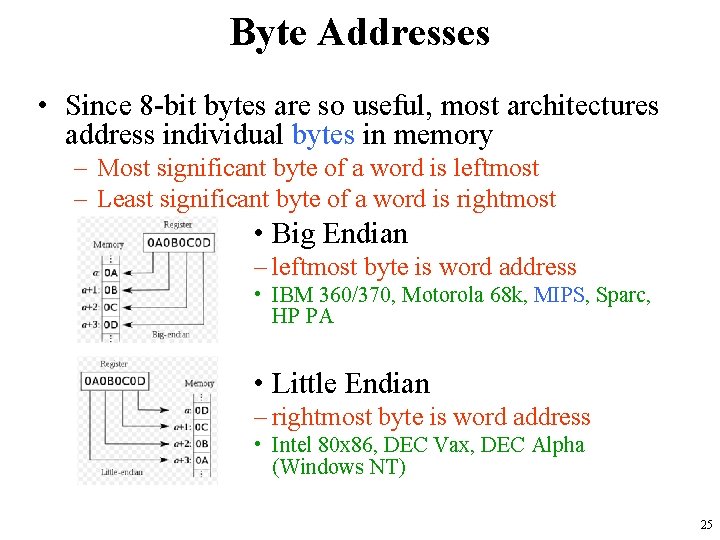

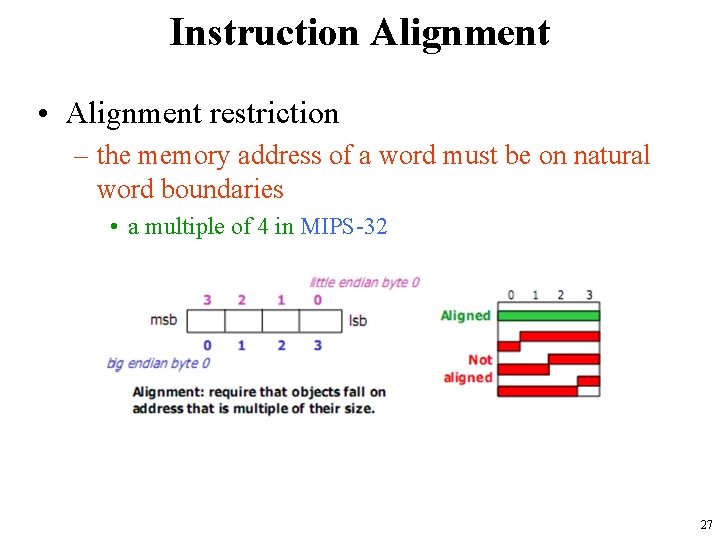

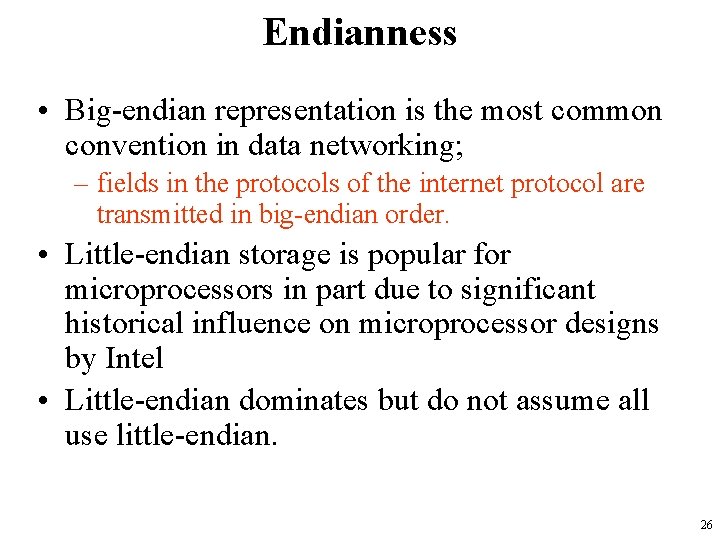

Byte Addresses • Since 8 -bit bytes are so useful, most architectures address individual bytes in memory – Most significant byte of a word is leftmost – Least significant byte of a word is rightmost • Big Endian – leftmost byte is word address • IBM 360/370, Motorola 68 k, MIPS, Sparc, HP PA • Little Endian – rightmost byte is word address • Intel 80 x 86, DEC Vax, DEC Alpha (Windows NT) 25

Endianness • Big-endian representation is the most common convention in data networking; – fields in the protocols of the internet protocol are transmitted in big-endian order. • Little-endian storage is popular for microprocessors in part due to significant historical influence on microprocessor designs by Intel • Little-endian dominates but do not assume all use little-endian. 26

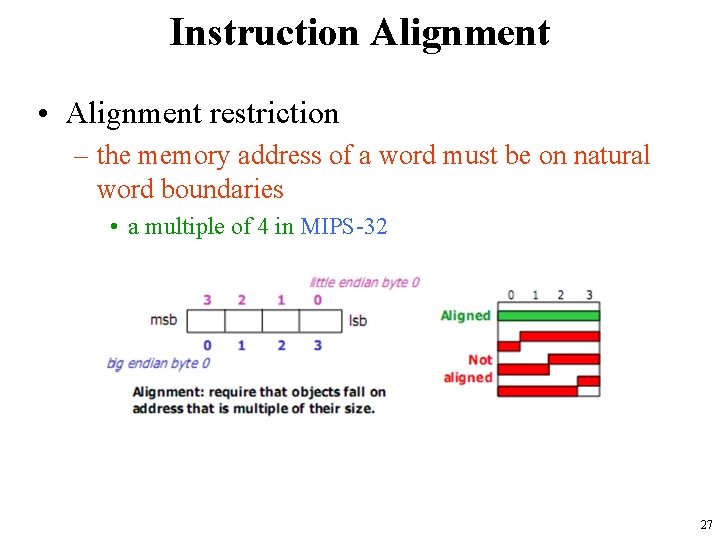

Instruction Alignment • Alignment restriction – the memory address of a word must be on natural word boundaries • a multiple of 4 in MIPS-32 27

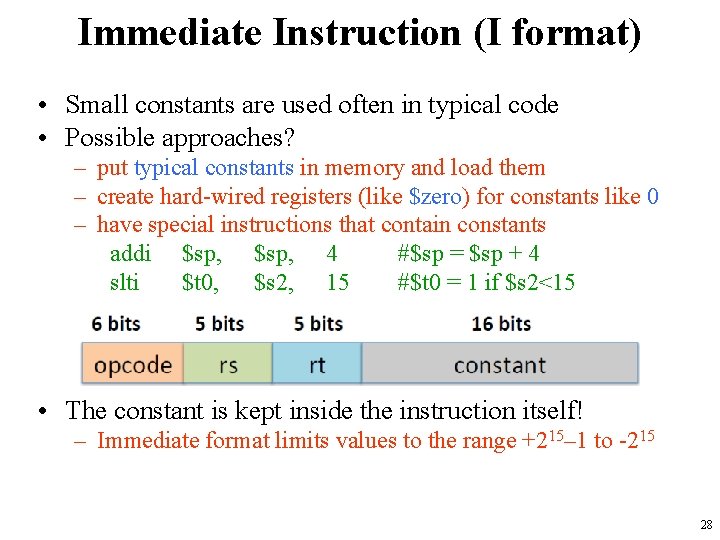

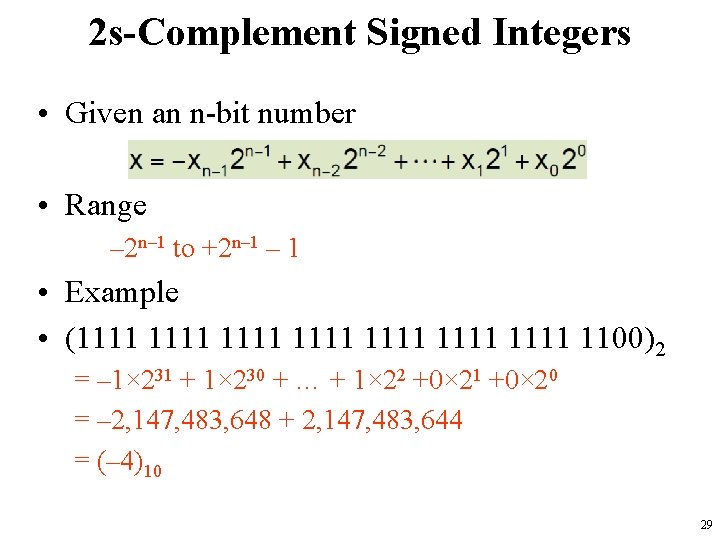

Immediate Instruction (I format) • Small constants are used often in typical code • Possible approaches? – put typical constants in memory and load them – create hard-wired registers (like $zero) for constants like 0 – have special instructions that contain constants addi $sp, 4 #$sp = $sp + 4 slti $t 0, $s 2, 15 #$t 0 = 1 if $s 2<15 • The constant is kept inside the instruction itself! – Immediate format limits values to the range +215– 1 to -215 28

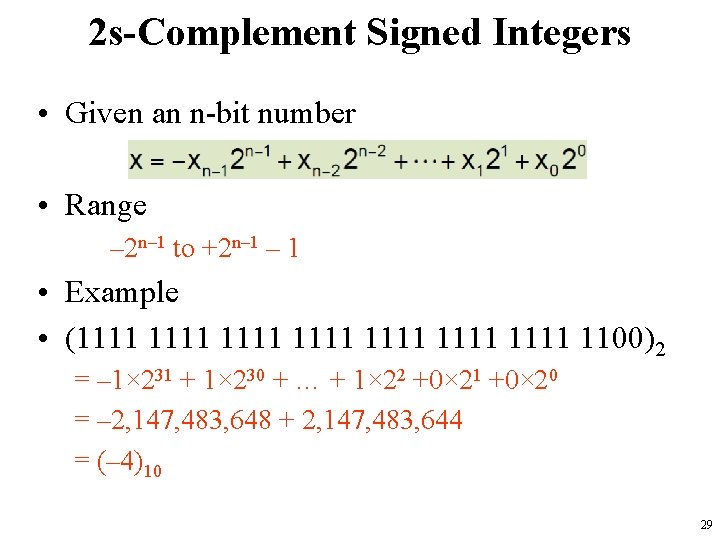

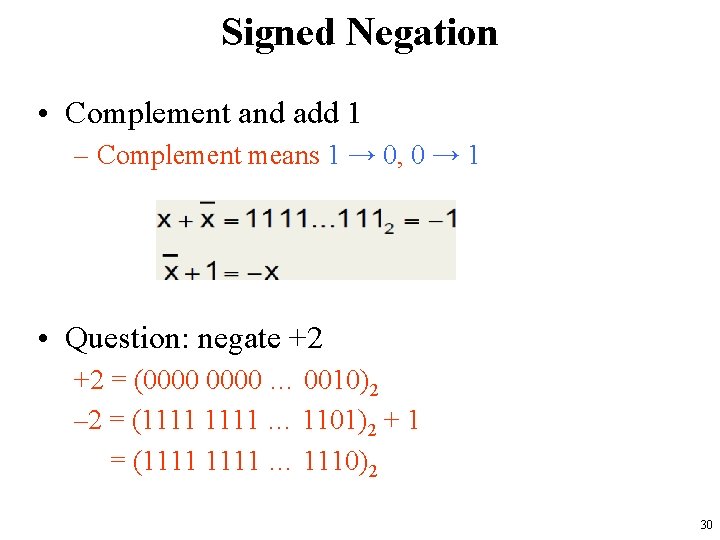

2 s-Complement Signed Integers • Given an n-bit number • Range – 2 n– 1 to +2 n– 1 • Example • (1111 1111 1100)2 = – 1× 231 + 1× 230 + … + 1× 22 +0× 21 +0× 20 = – 2, 147, 483, 648 + 2, 147, 483, 644 = (– 4)10 29

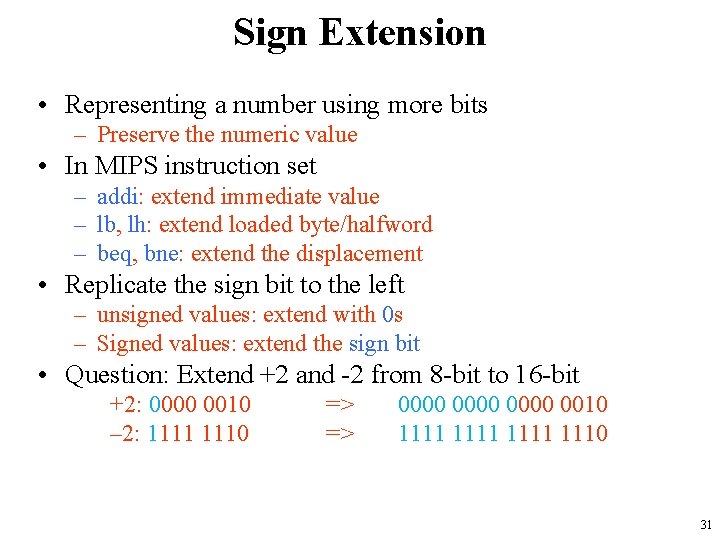

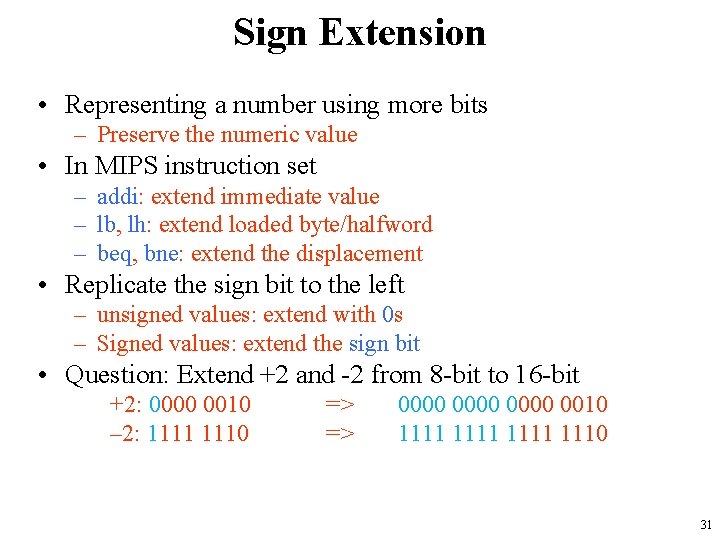

Signed Negation • Complement and add 1 – Complement means 1 → 0, 0 → 1 • Question: negate +2 +2 = (0000 … 0010)2 – 2 = (1111 … 1101)2 + 1 = (1111 … 1110)2 30

Sign Extension • Representing a number using more bits – Preserve the numeric value • In MIPS instruction set – addi: extend immediate value – lb, lh: extend loaded byte/halfword – beq, bne: extend the displacement • Replicate the sign bit to the left – unsigned values: extend with 0 s – Signed values: extend the sign bit • Question: Extend +2 and -2 from 8 -bit to 16 -bit +2: 0000 0010 – 2: 1111 1110 => => 0000 0010 1111 1110 31

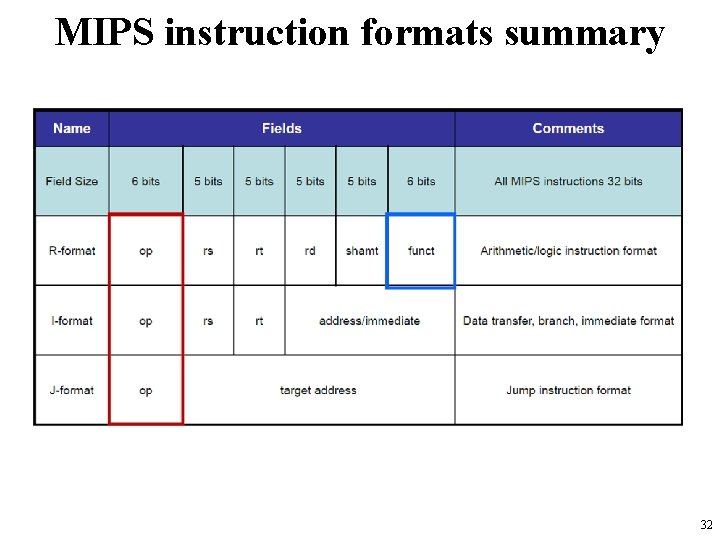

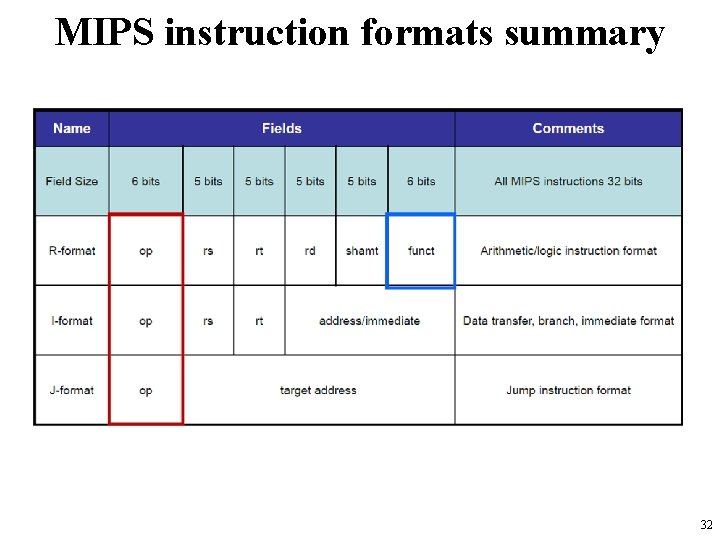

MIPS instruction formats summary 32

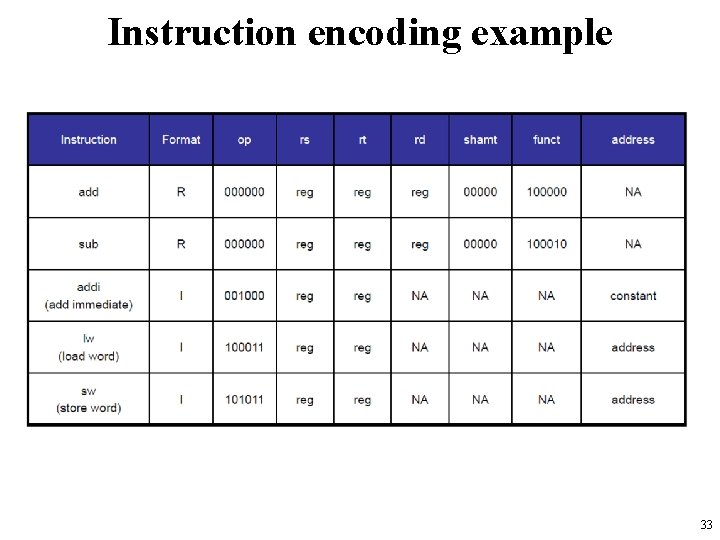

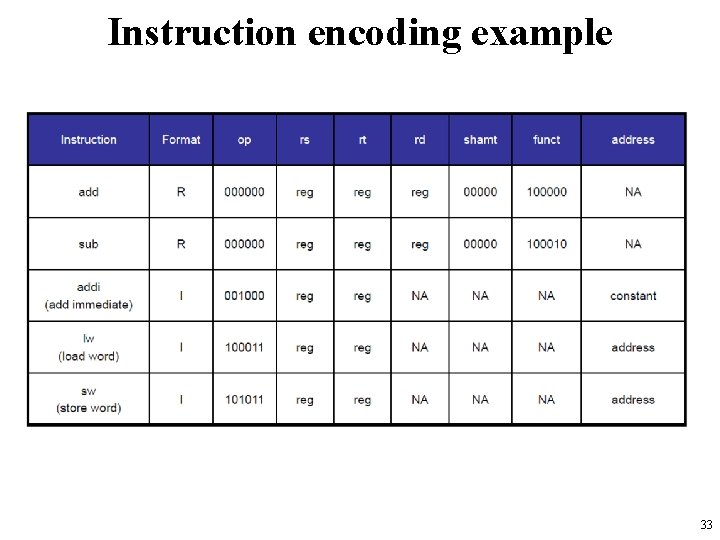

Instruction encoding example 33

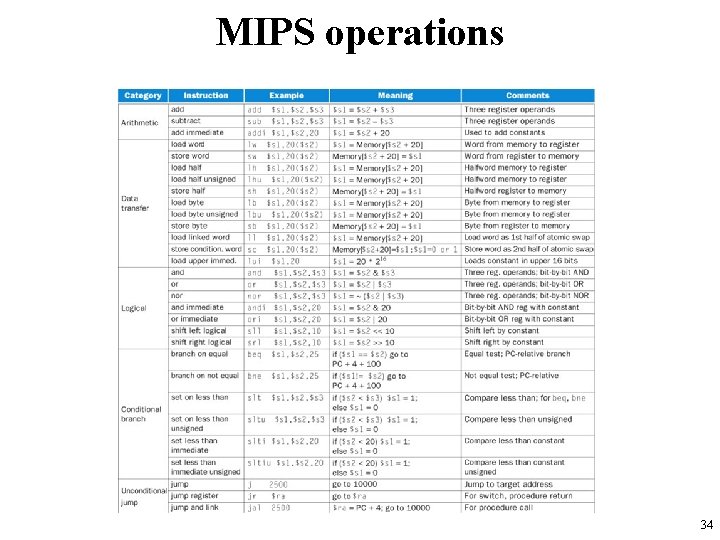

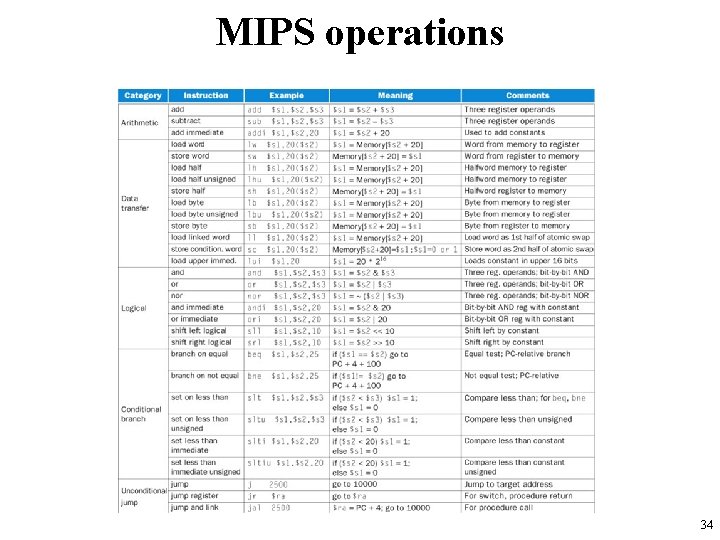

MIPS operations 34

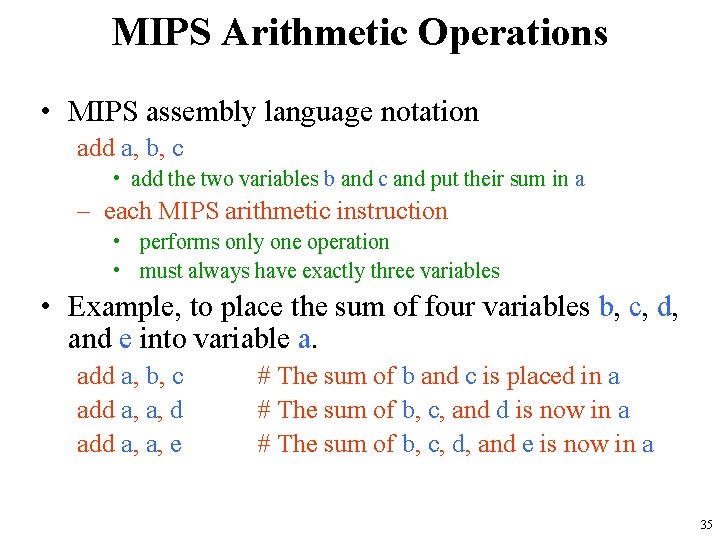

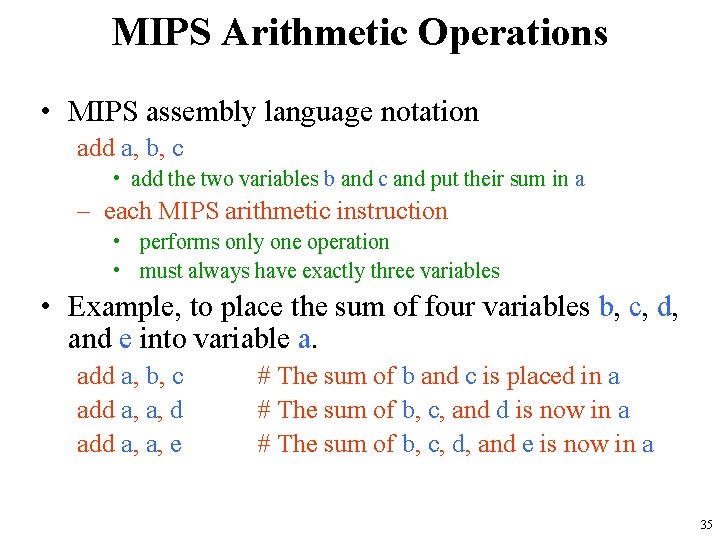

MIPS Arithmetic Operations • MIPS assembly language notation add a, b, c • add the two variables b and c and put their sum in a – each MIPS arithmetic instruction • performs only one operation • must always have exactly three variables • Example, to place the sum of four variables b, c, d, and e into variable a. add a, b, c add a, a, d add a, a, e # The sum of b and c is placed in a # The sum of b, c, and d is now in a # The sum of b, c, d, and e is now in a 35

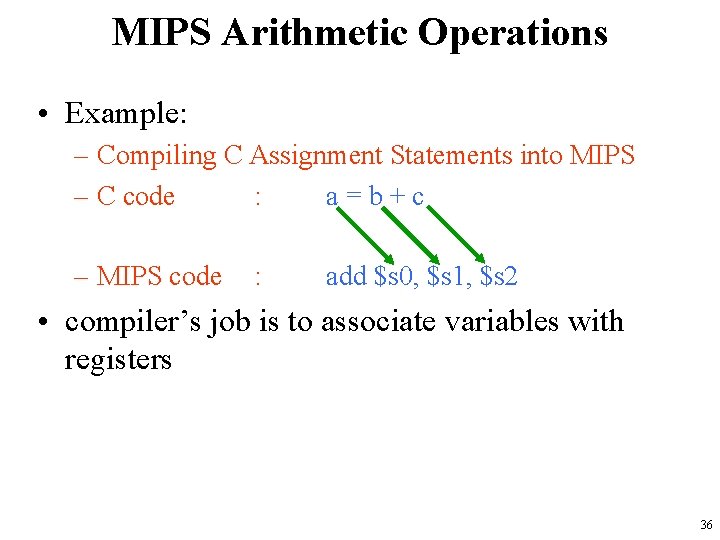

MIPS Arithmetic Operations • Example: – Compiling C Assignment Statements into MIPS – C code : a=b+c – MIPS code : add $s 0, $s 1, $s 2 • compiler’s job is to associate variables with registers 36

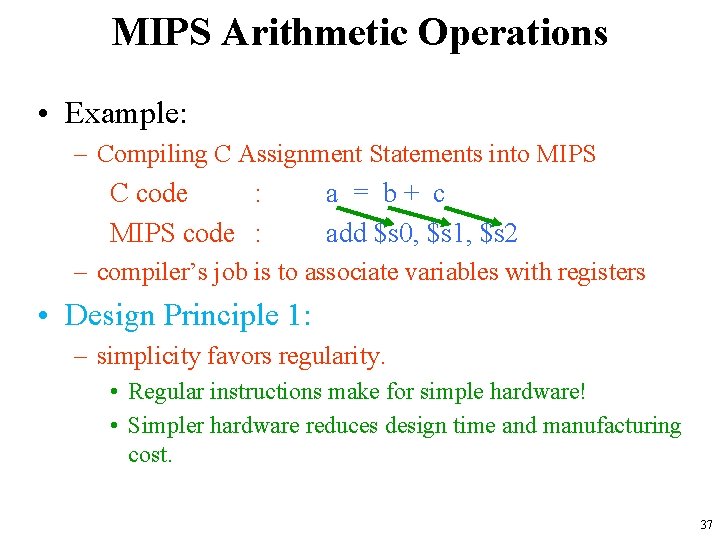

MIPS Arithmetic Operations • Example: – Compiling C Assignment Statements into MIPS C code : MIPS code : a = b+ c add $s 0, $s 1, $s 2 – compiler’s job is to associate variables with registers • Design Principle 1: – simplicity favors regularity. • Regular instructions make for simple hardware! • Simpler hardware reduces design time and manufacturing cost. 37

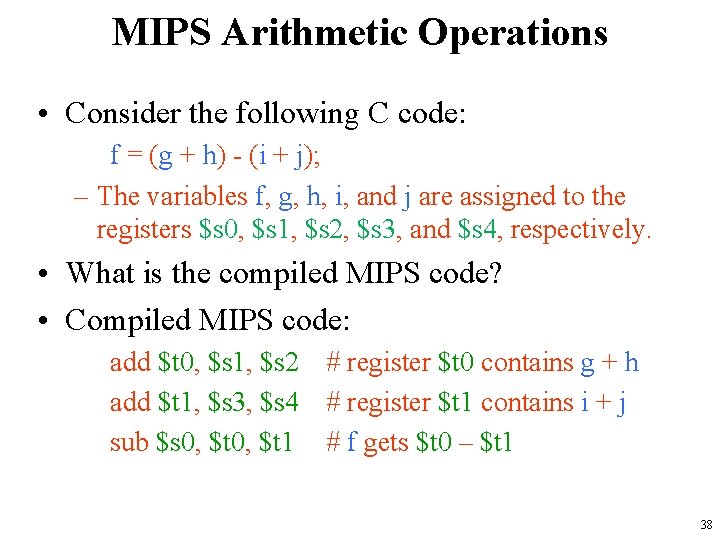

MIPS Arithmetic Operations • Consider the following C code: f = (g + h) - (i + j); – The variables f, g, h, i, and j are assigned to the registers $s 0, $s 1, $s 2, $s 3, and $s 4, respectively. • What is the compiled MIPS code? • Compiled MIPS code: add $t 0, $s 1, $s 2 # register $t 0 contains g + h add $t 1, $s 3, $s 4 # register $t 1 contains i + j sub $s 0, $t 1 # f gets $t 0 – $t 1 38

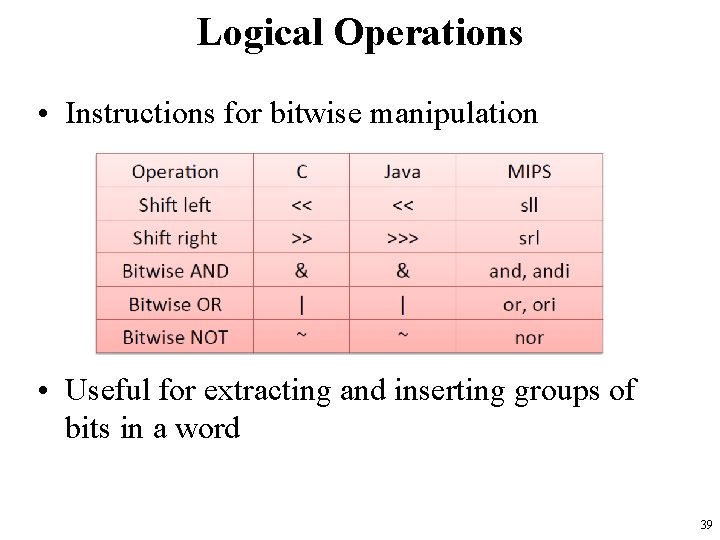

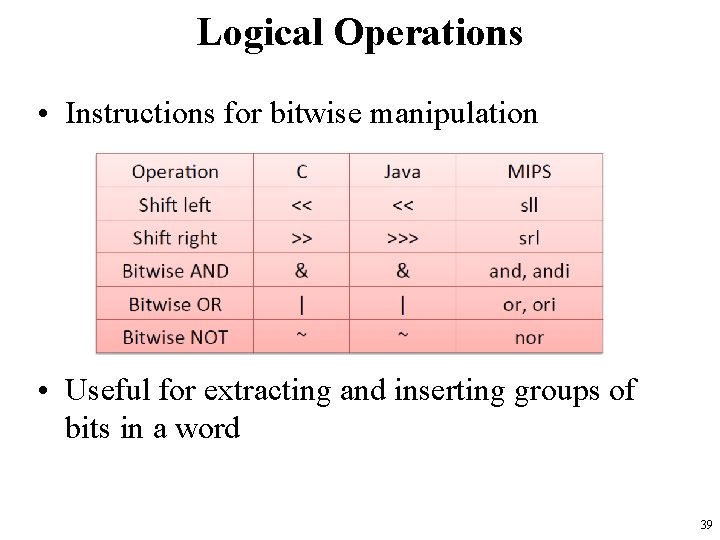

Logical Operations • Instructions for bitwise manipulation • Useful for extracting and inserting groups of bits in a word 39

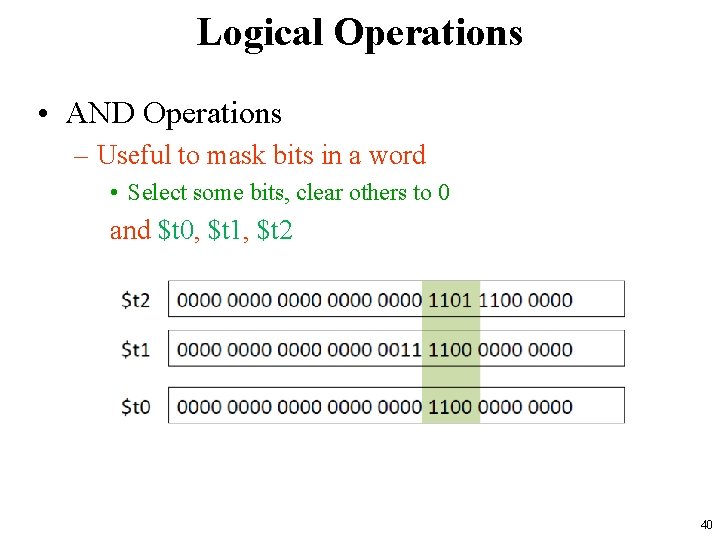

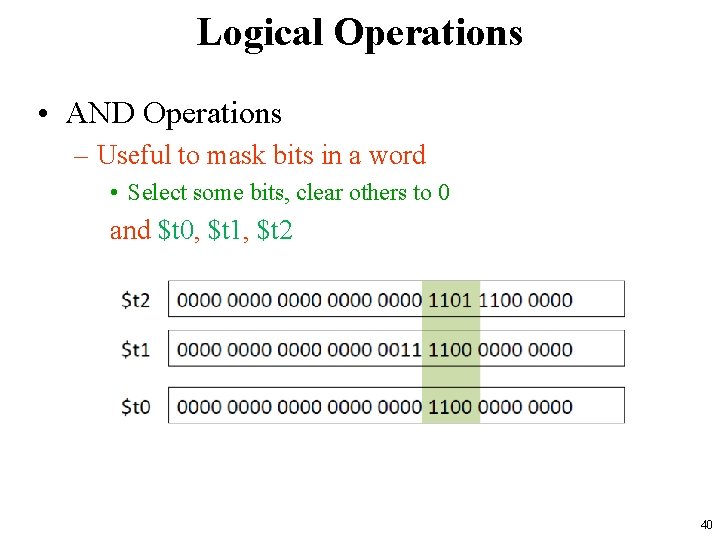

Logical Operations • AND Operations – Useful to mask bits in a word • Select some bits, clear others to 0 and $t 0, $t 1, $t 2 40

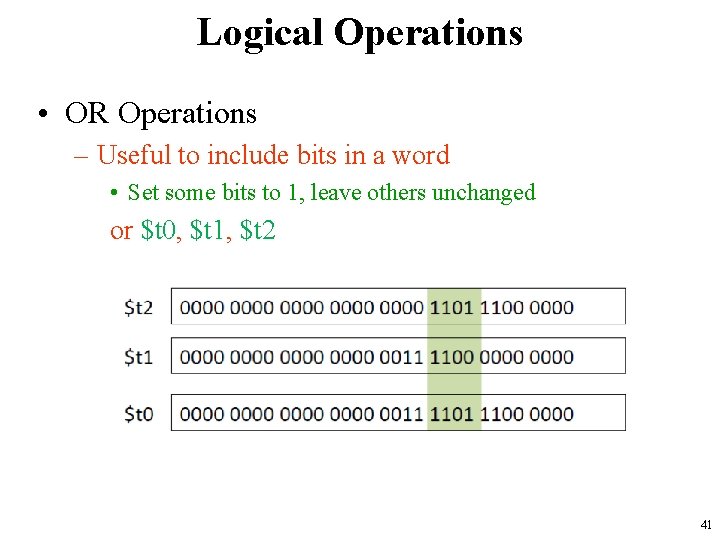

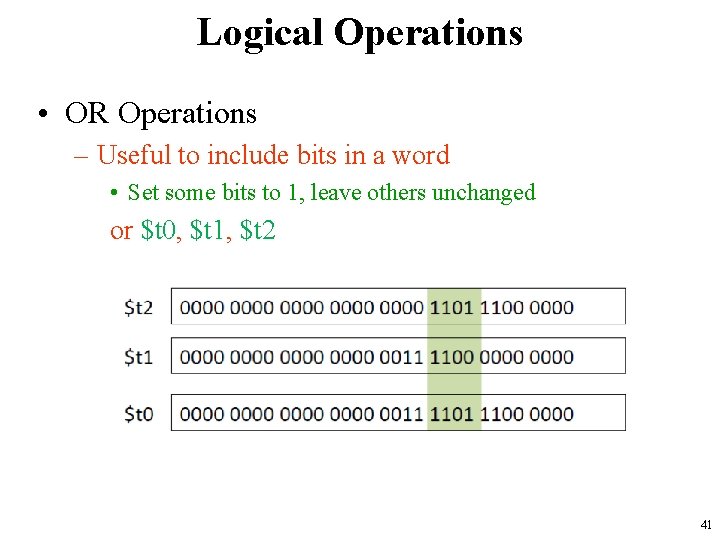

Logical Operations • OR Operations – Useful to include bits in a word • Set some bits to 1, leave others unchanged or $t 0, $t 1, $t 2 41

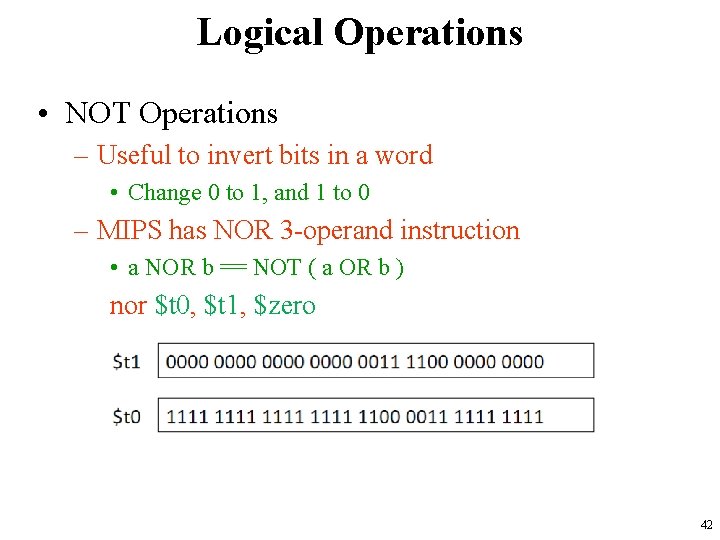

Logical Operations • NOT Operations – Useful to invert bits in a word • Change 0 to 1, and 1 to 0 – MIPS has NOR 3 -operand instruction • a NOR b == NOT ( a OR b ) nor $t 0, $t 1, $zero 42

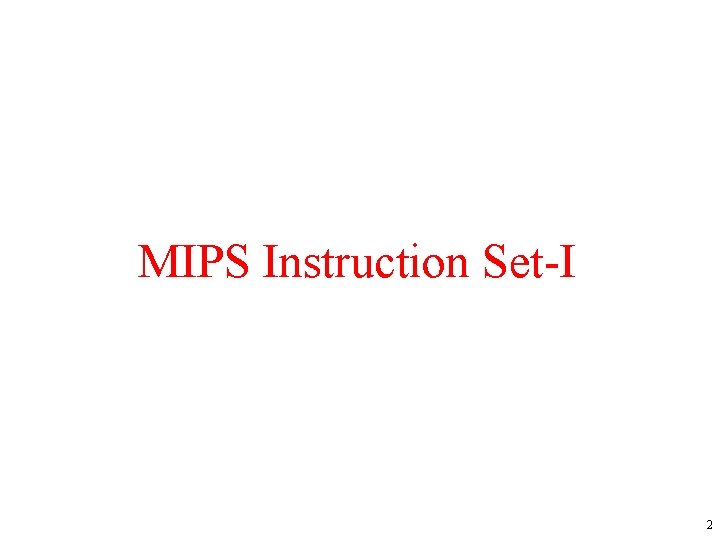

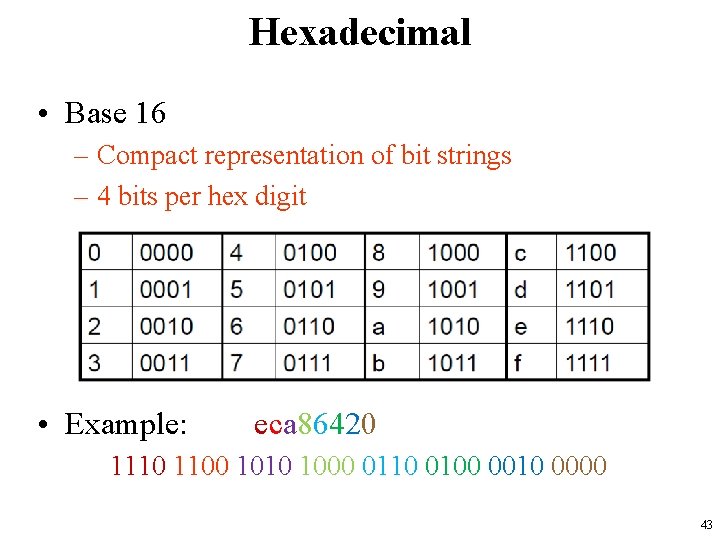

Hexadecimal • Base 16 – Compact representation of bit strings – 4 bits per hex digit • Example: eca 86420 1110 1100 1010 1000 0110 0100 0010 0000 43

44