Computer Architecture Prof Dr Nizamettin AYDIN naydinyildiz edu

![Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1] Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1]](https://slidetodoc.com/presentation_image_h2/5629fb4a6cf68ffa8b81cfdb6c546661/image-4.jpg)

- Slides: 60

Computer Architecture Prof. Dr. Nizamettin AYDIN naydin@yildiz. edu. tr http: //www. yildiz. edu. tr/~naydin 1

Fundamental Computer Elements 2

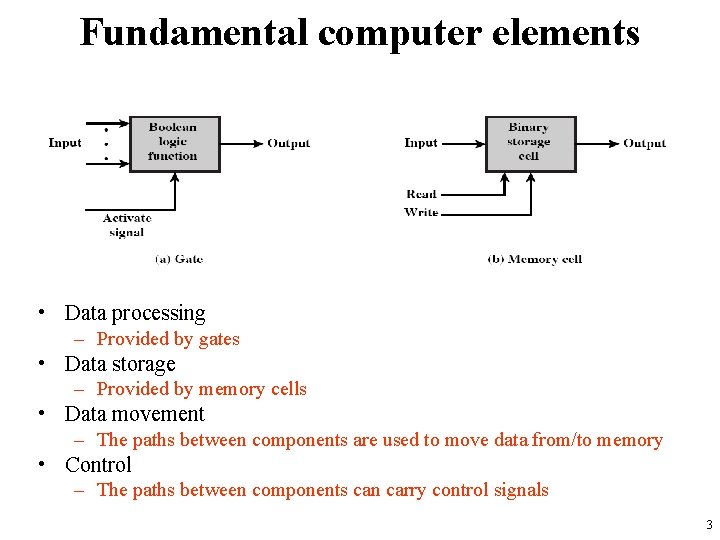

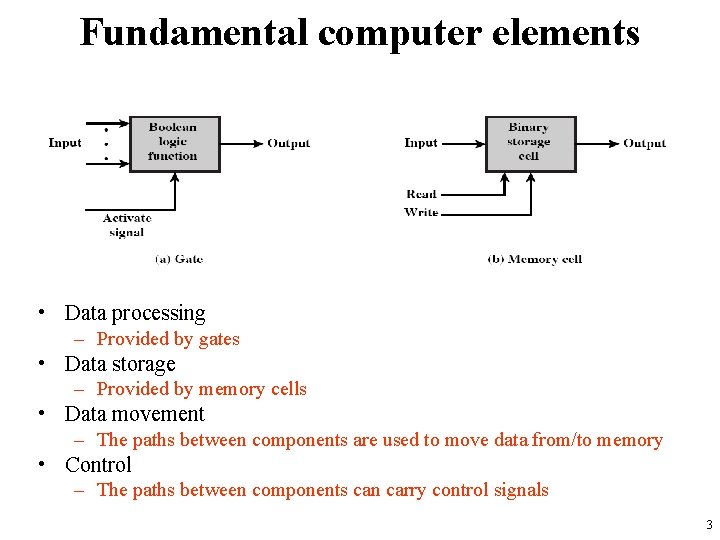

Fundamental computer elements • Data processing – Provided by gates • Data storage – Provided by memory cells • Data movement – The paths between components are used to move data from/to memory • Control – The paths between components can carry control signals 3

![Levels of Representation temp vk High Level Language Program vk vk1 vk1 Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1]](https://slidetodoc.com/presentation_image_h2/5629fb4a6cf68ffa8b81cfdb6c546661/image-4.jpg)

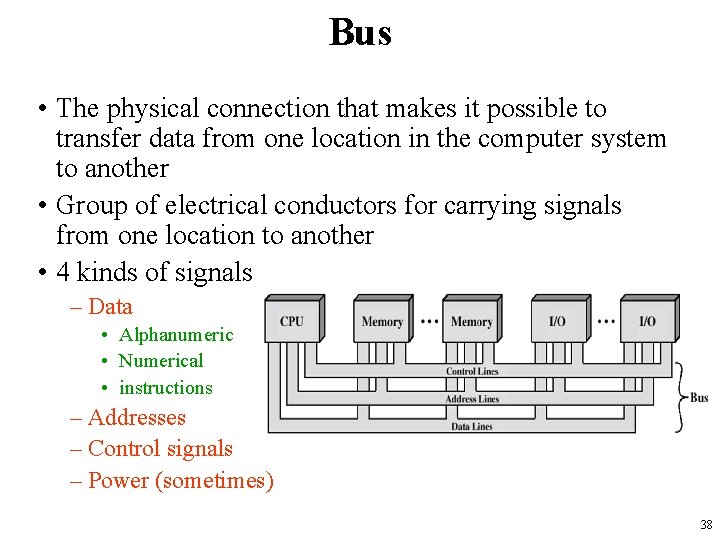

Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1] = temp; Compiler lw lw sw sw Assembly Language Program Assembler Machine Language Program 0000 1010 1100 0101 1001 1111 0110 1000 1100 0101 1010 0000 $15, $16, $15, 0110 1000 1111 1001 1010 0000 0101 1100 0($2) 4($2) 1111 1000 0110 0101 1100 0000 1010 1000 0110 1001 1111 Machine Interpretation Control Signal Specification ALUOP[0: 3] <= Inst. Reg[9: 11] & MASK ° ° 4

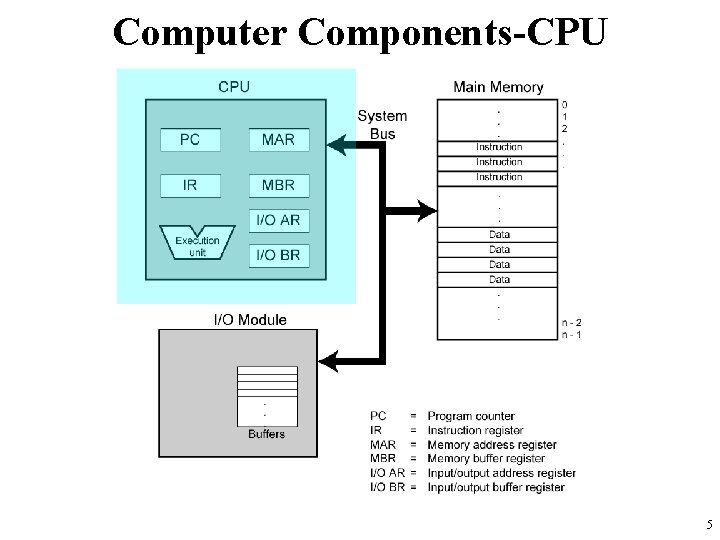

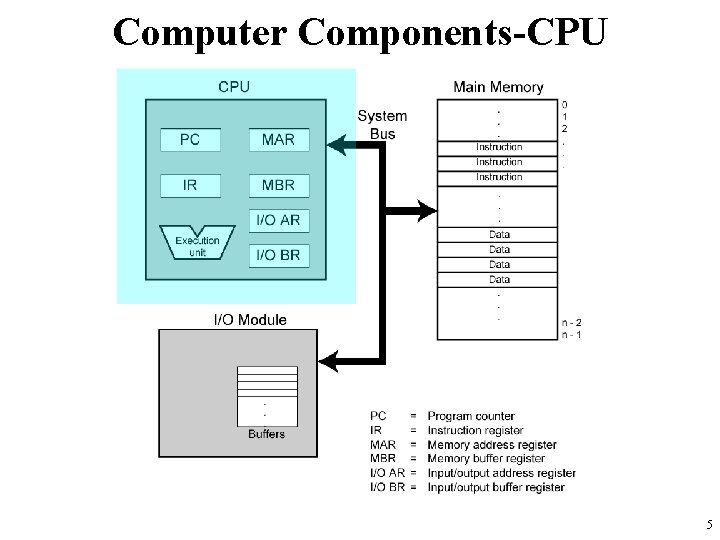

Computer Components-CPU 5

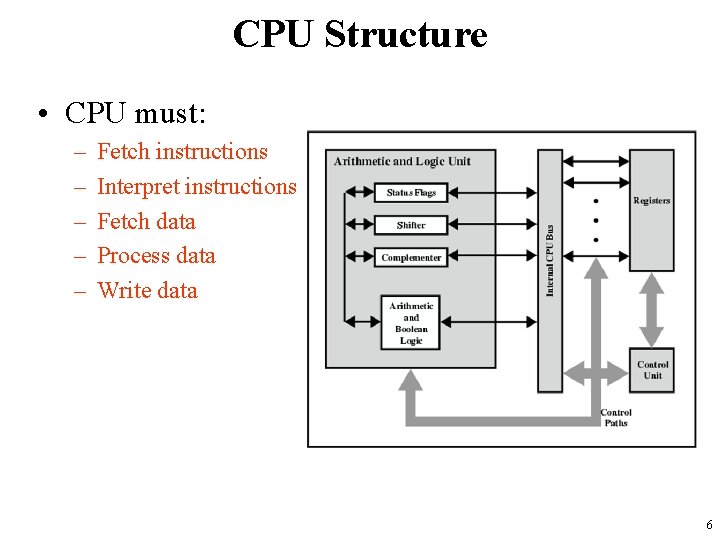

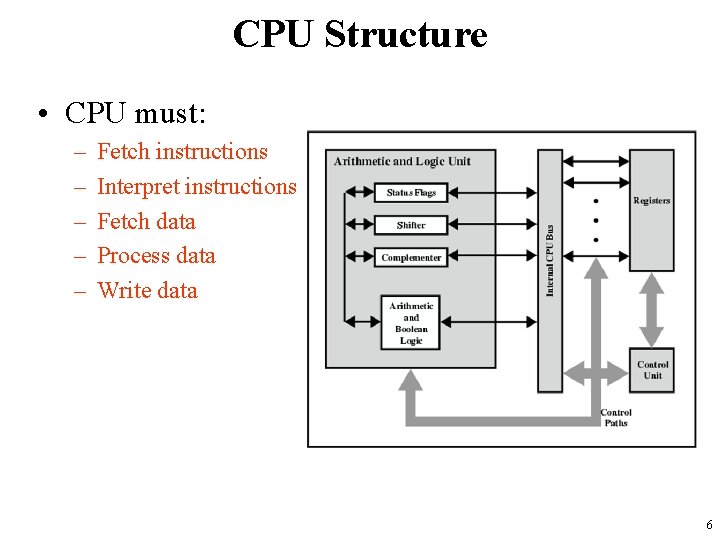

CPU Structure • CPU must: – – – Fetch instructions Interpret instructions Fetch data Process data Write data 6

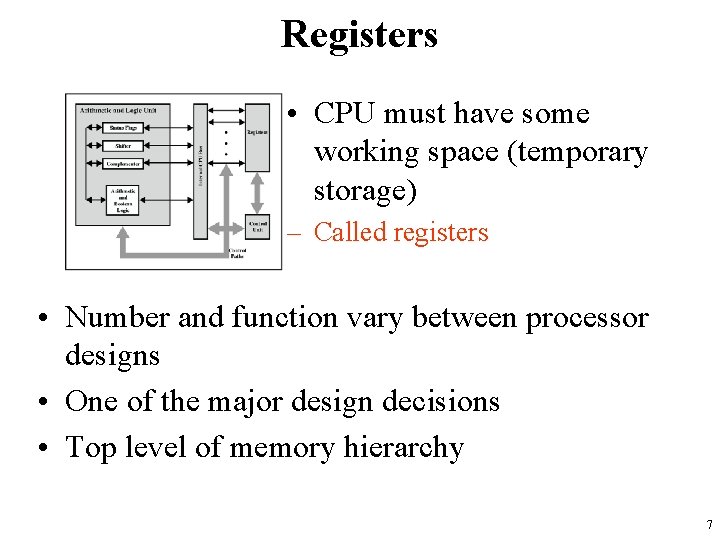

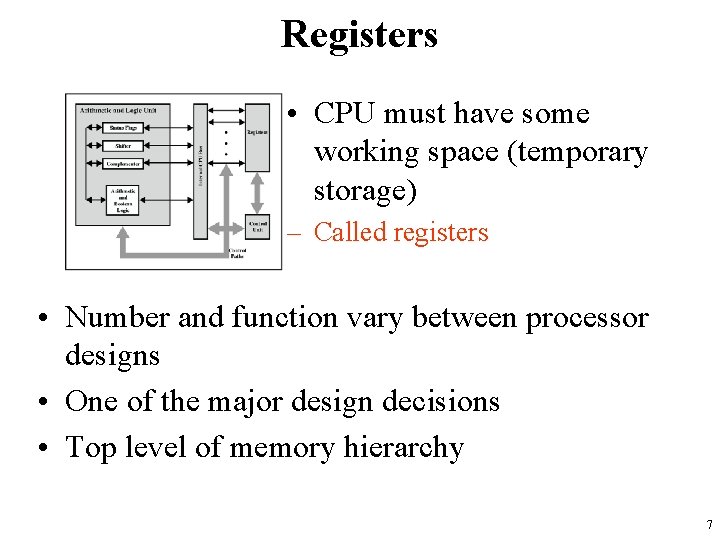

Registers • CPU must have some working space (temporary storage) – Called registers • Number and function vary between processor designs • One of the major design decisions • Top level of memory hierarchy 7

Registers in the P perform two roles: • User-visible registers – Enable the machine- or assembly language programmer to minimize main memory references by optimizing use of registers • Control and status registers – Used by the control unit to control the operation of the processor and by priviliged, operating system programs to control the execution of programs 8

User Visible Registers • General Purpose registers • Data registers • Address registers • Condition Codes (flags) 9

Condition Code Registers • Sets of individual bits – e. g. result of last operation was zero • Can be read (implicitly) by programs – e. g. Jump if zero • Can not (usually) be set by programs 10

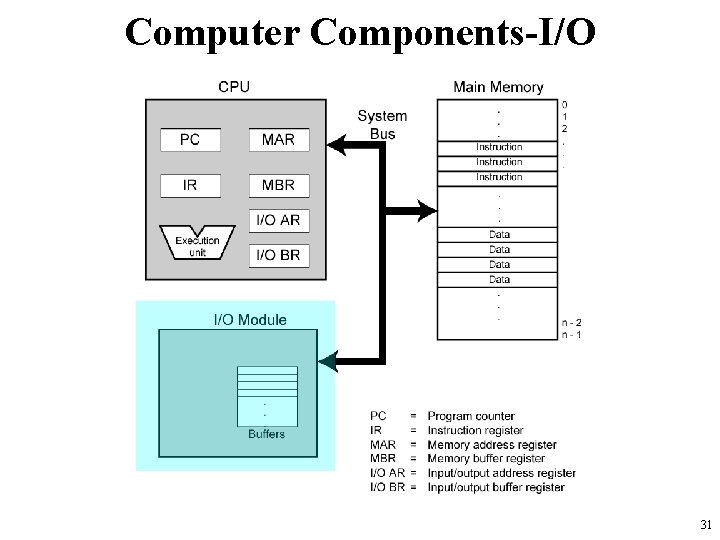

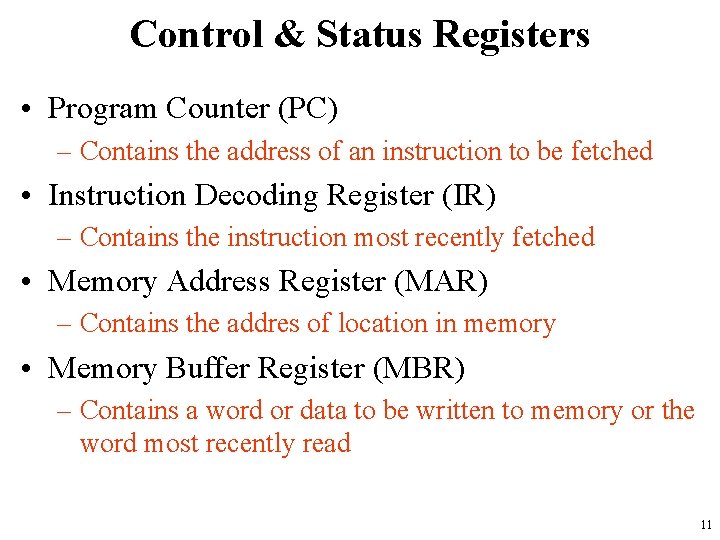

Control & Status Registers • Program Counter (PC) – Contains the address of an instruction to be fetched • Instruction Decoding Register (IR) – Contains the instruction most recently fetched • Memory Address Register (MAR) – Contains the addres of location in memory • Memory Buffer Register (MBR) – Contains a word or data to be written to memory or the word most recently read 11

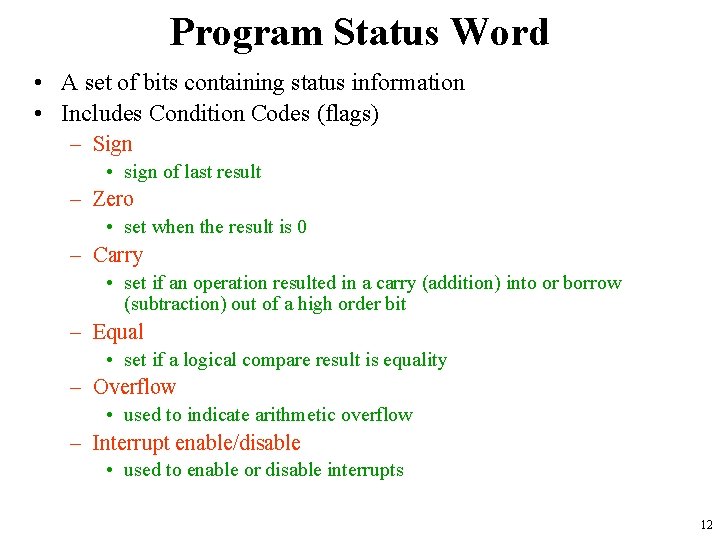

Program Status Word • A set of bits containing status information • Includes Condition Codes (flags) – Sign • sign of last result – Zero • set when the result is 0 – Carry • set if an operation resulted in a carry (addition) into or borrow (subtraction) out of a high order bit – Equal • set if a logical compare result is equality – Overflow • used to indicate arithmetic overflow – Interrupt enable/disable • used to enable or disable interrupts 12

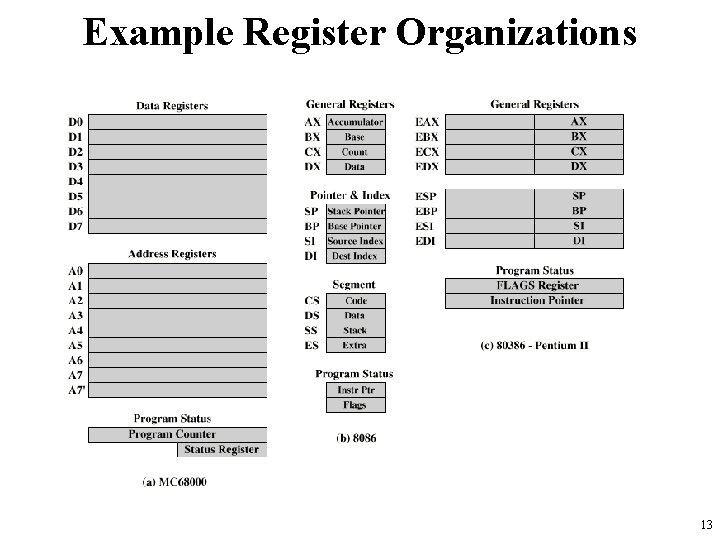

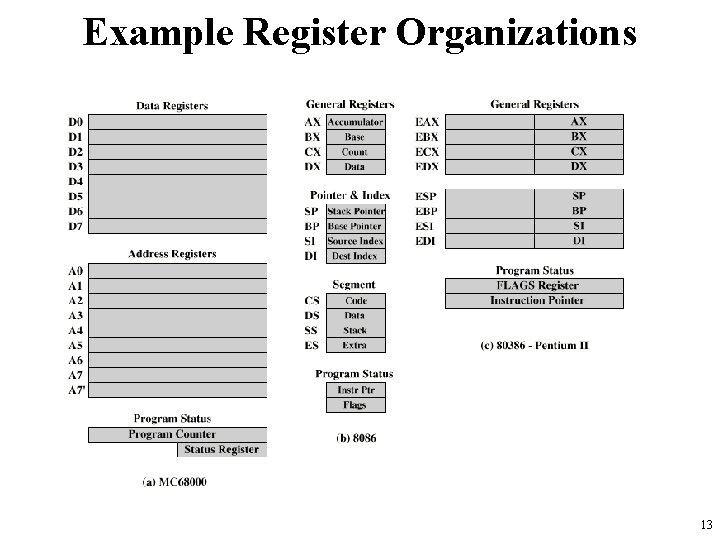

Example Register Organizations 13

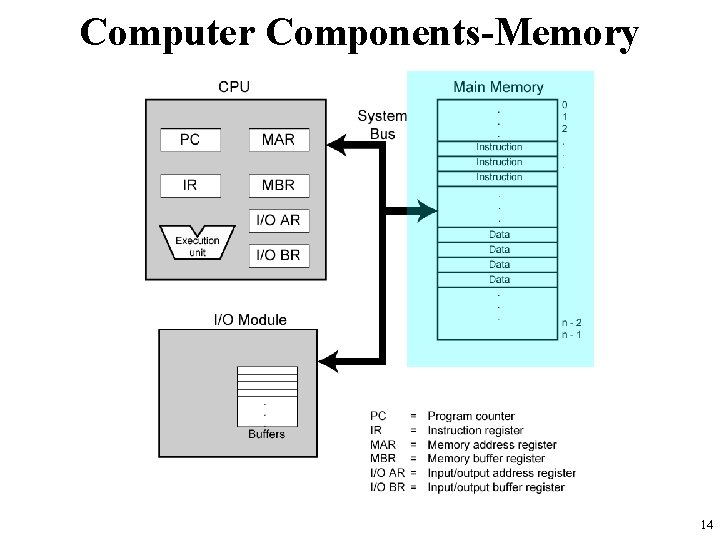

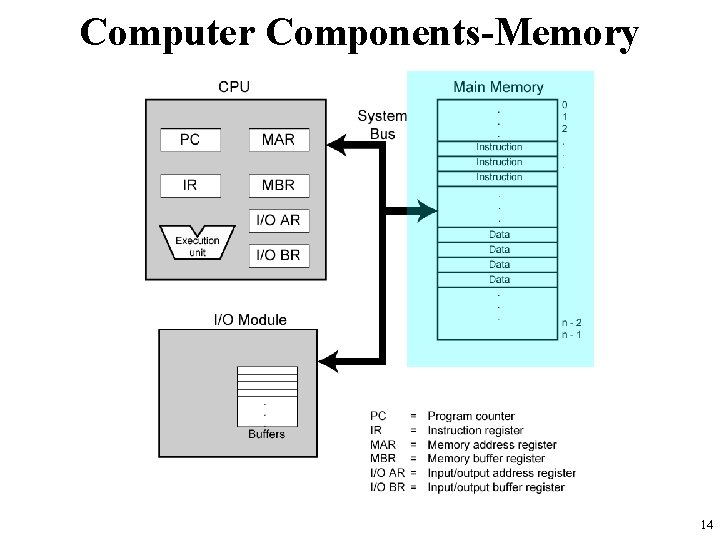

Computer Components-Memory 14

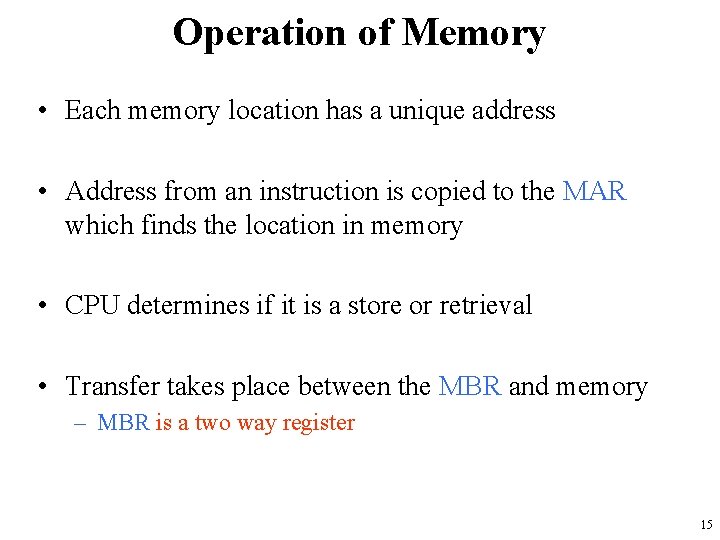

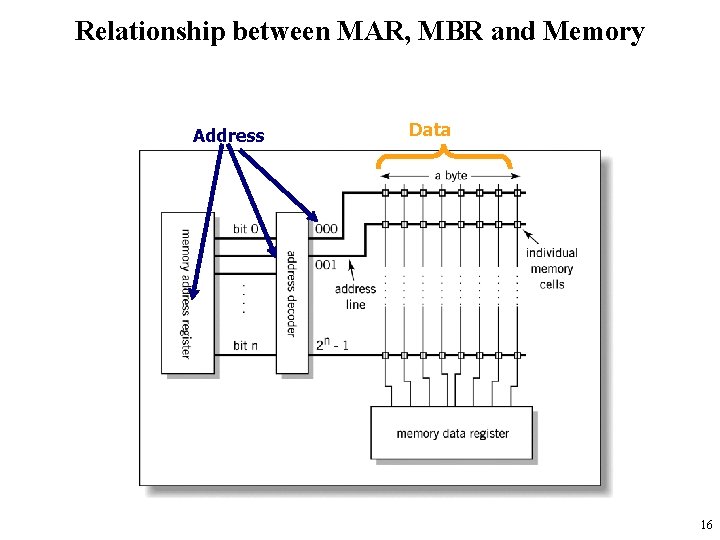

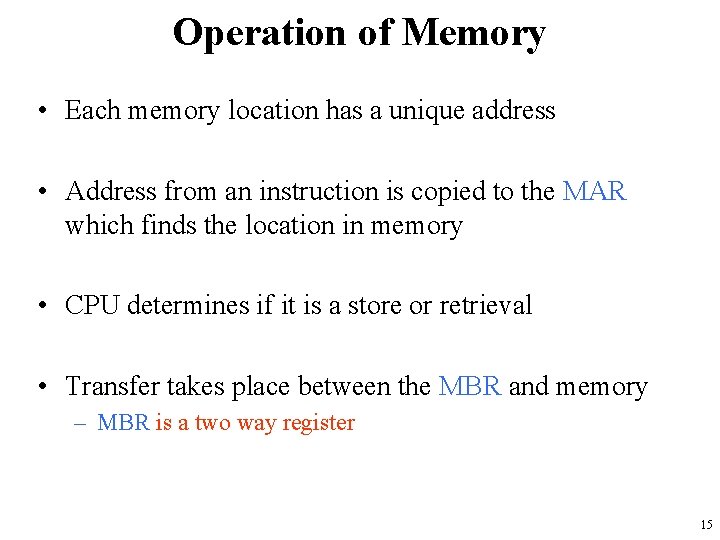

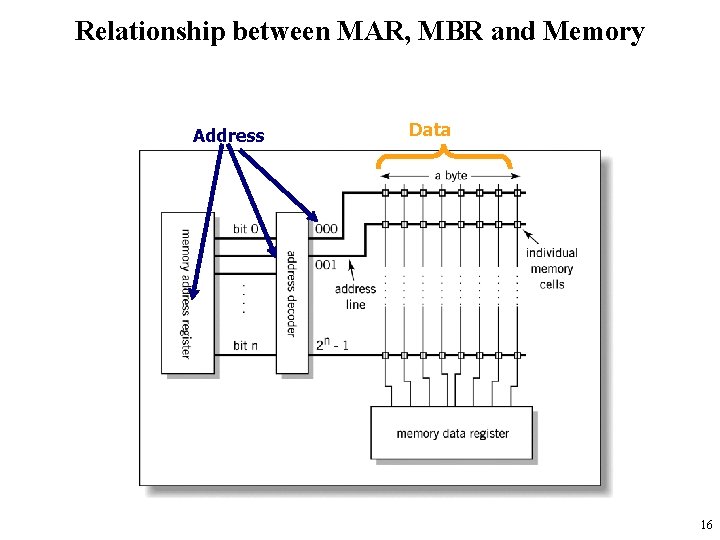

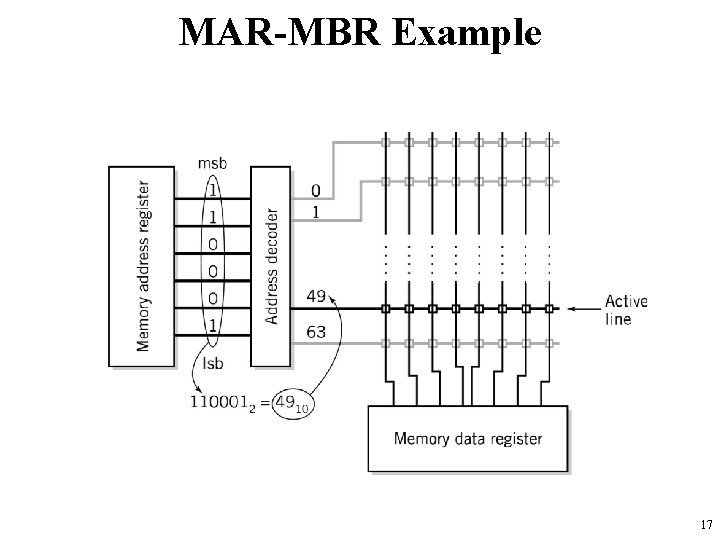

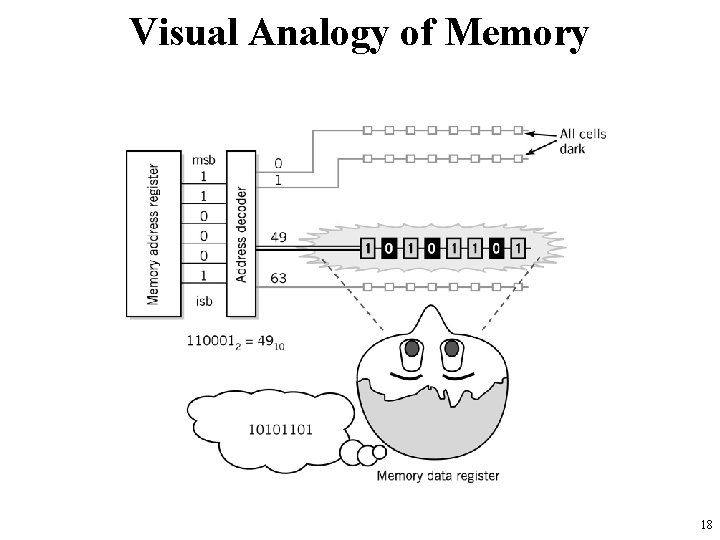

Operation of Memory • Each memory location has a unique address • Address from an instruction is copied to the MAR which finds the location in memory • CPU determines if it is a store or retrieval • Transfer takes place between the MBR and memory – MBR is a two way register 15

Relationship between MAR, MBR and Memory Address Data 16

MAR-MBR Example 17

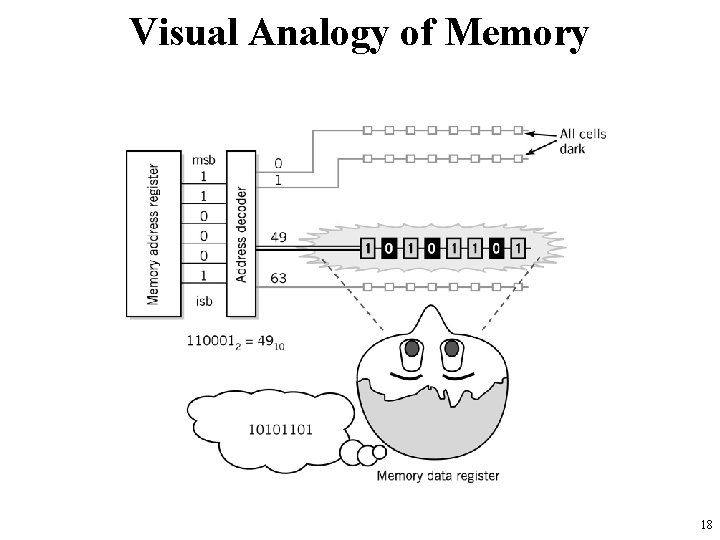

Visual Analogy of Memory 18

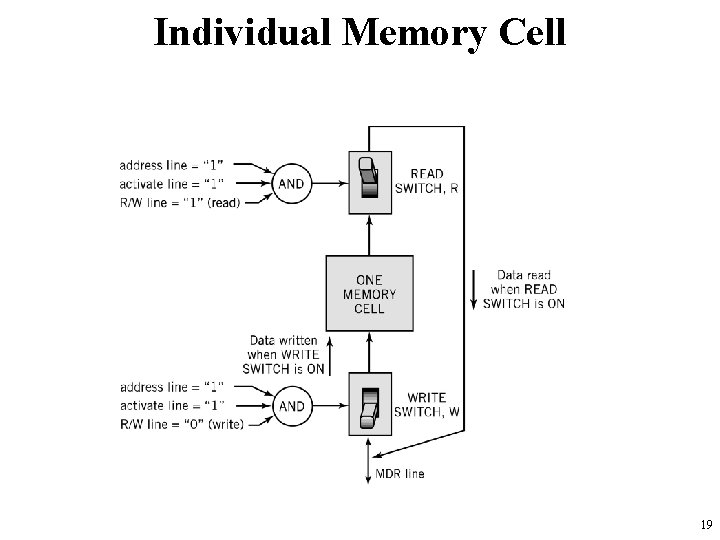

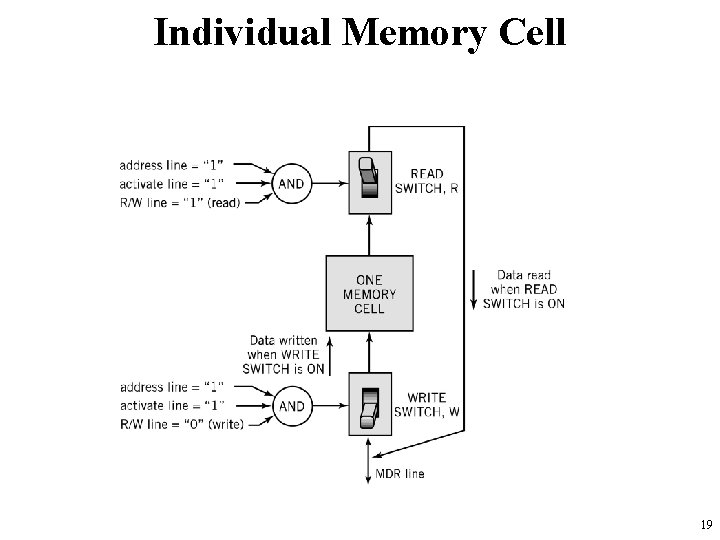

Individual Memory Cell 19

Memory Capacity • Determined by two factors – Number of bits in the MAR • 2 K where K = width of the register in bits – Size of the address portion of the instruction • 4 bits allows 16 locations • 8 bits allows 256 locations • 32 bits allows 4, 294, 967, 296 or 4 GB • Important for performance – Insufficient memory can cause a processor to work at 50% below performance 20

Memory Hierarchy • Registers – In CPU • Internal or Main memory – May include one or more levels of cache – “RAM” • External memory – Backing store 21

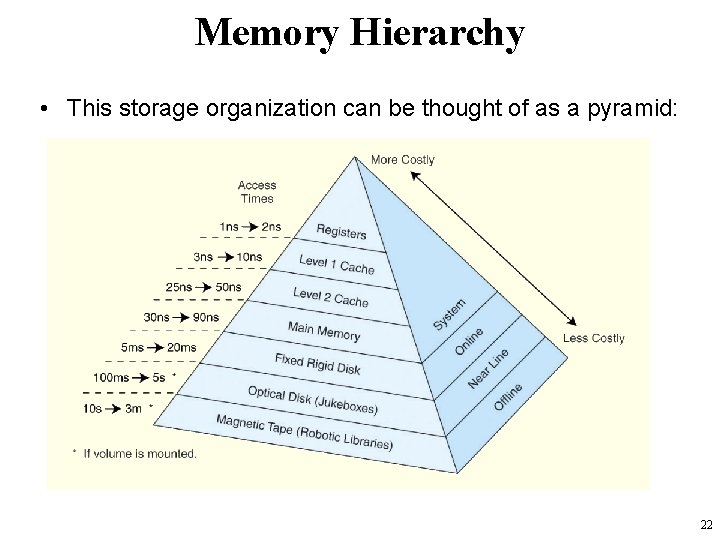

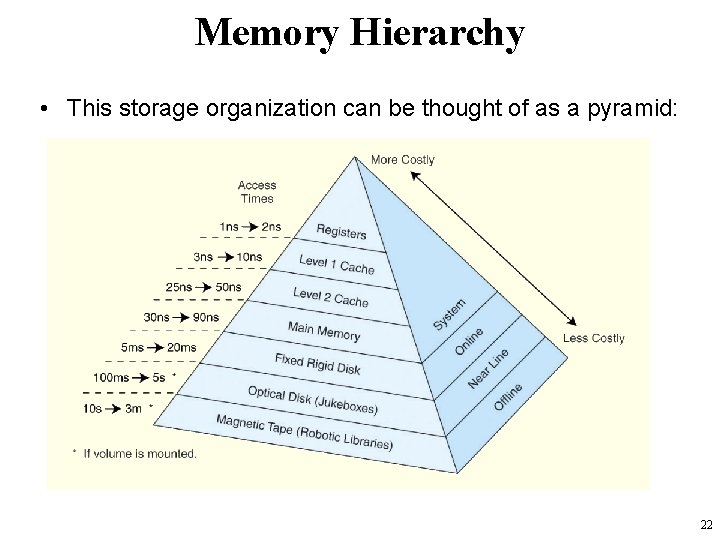

Memory Hierarchy • This storage organization can be thought of as a pyramid: 22

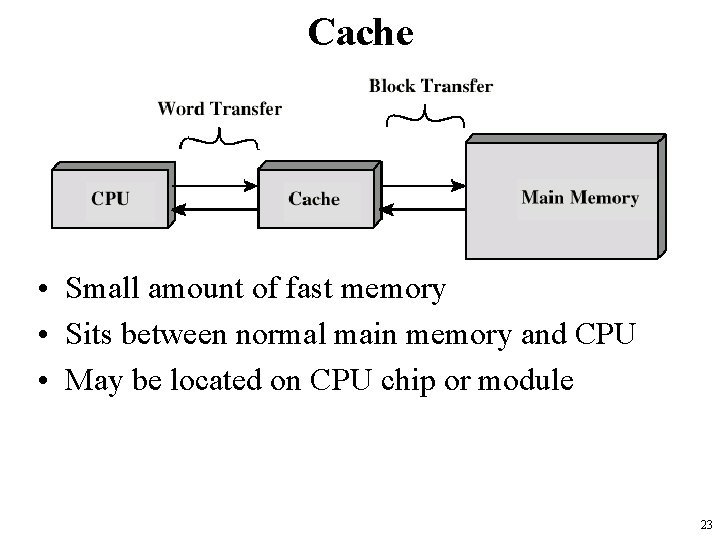

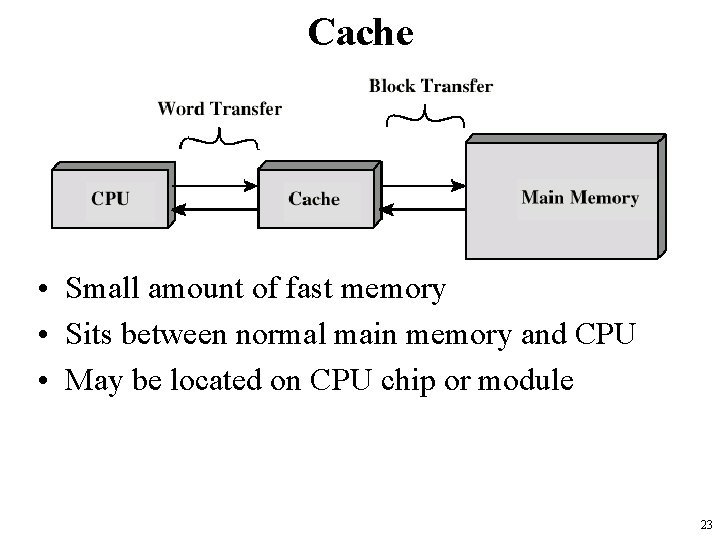

Cache • Small amount of fast memory • Sits between normal main memory and CPU • May be located on CPU chip or module 23

Virtual Memory • Cache memory enhances performance by providing faster memory access speed. • Virtual memory enhances performance by providing greater memory capacity, without the expense of adding main memory. • Instead, a portion of a disk drive serves as an extension of main memory. • If a system uses paging, virtual memory partitions main memory into individually managed page frames, that are written (or paged) to disk when they are not immediately needed. 24

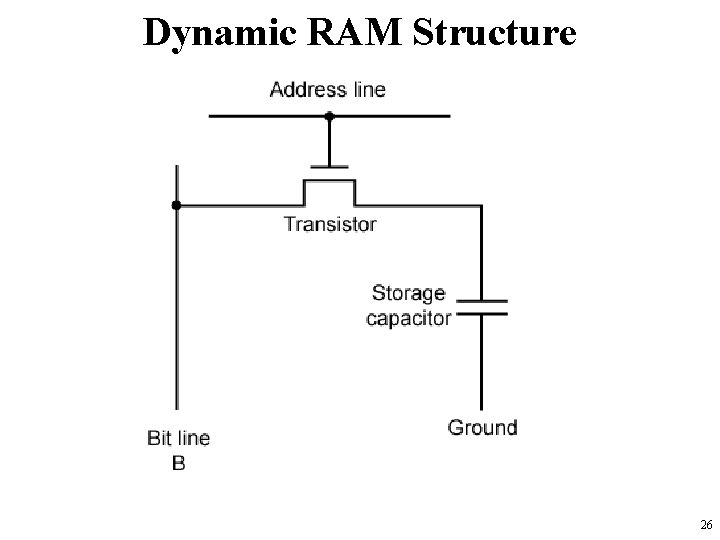

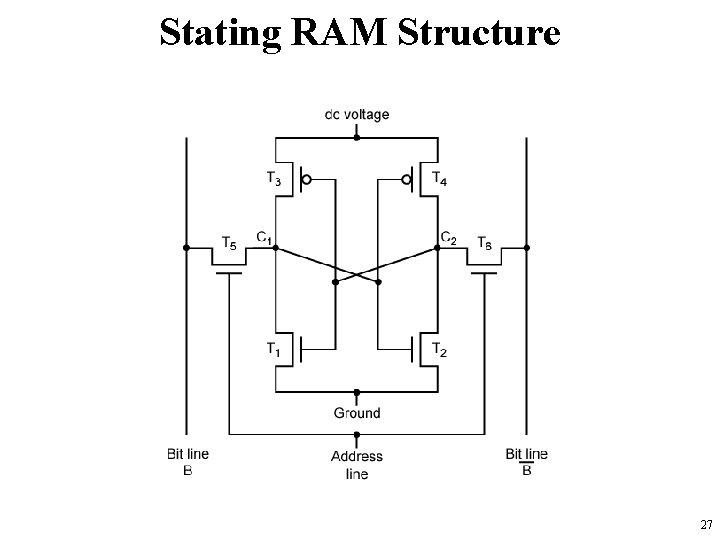

RAM: Random Access Memory • DRAM (Dynamic RAM) – Most common, cheap – Volatile: must be refreshed (recharged with power) 1000’s of times each second • SRAM (static RAM) – Faster than DRAM and more expensive than DRAM – Volatile – Frequently small amount used in cache memory for highspeed access used 25

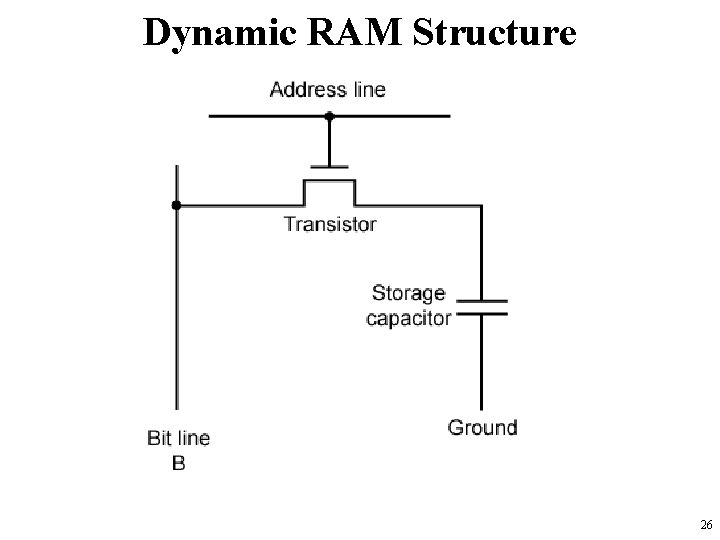

Dynamic RAM Structure 26

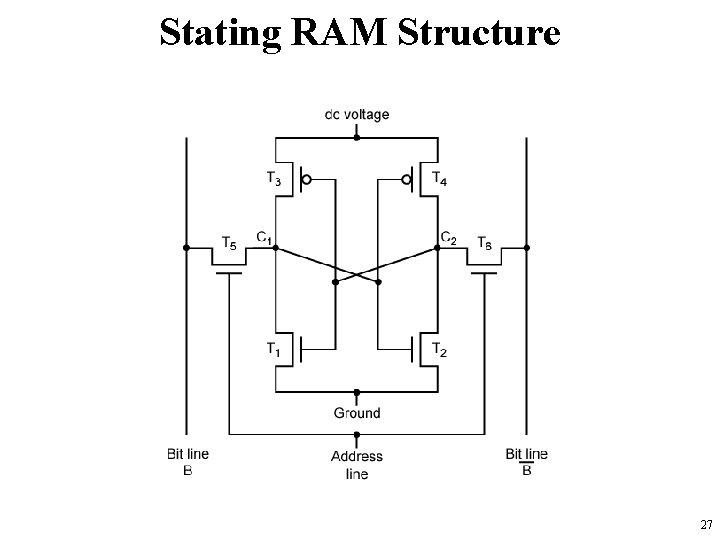

Stating RAM Structure 27

Read Only Memory (ROM) • Permanent storage – Nonvolatile • Used in. . . – Microprogramming – Library subroutines – Systems programs (BIOS) – Function tables 28

Types of ROM • Written during manufacture – Very expensive for small runs • Programmable (once) – PROM – Needs special equipment to program • Read “mostly” – Erasable Programmable (EPROM) • Erased by UV – Electrically Erasable (EEPROM) • Takes much longer to write than read – Flash memory • Erase whole memory electrically 29

Types of External Memory • SSD – Fast – Expensive (relatively) • Magnetic Disk – RAID – Removable • Optical – – CD-ROM CD-Recordable (CD-R) CD-R/W DVD • Magnetic Tape 30

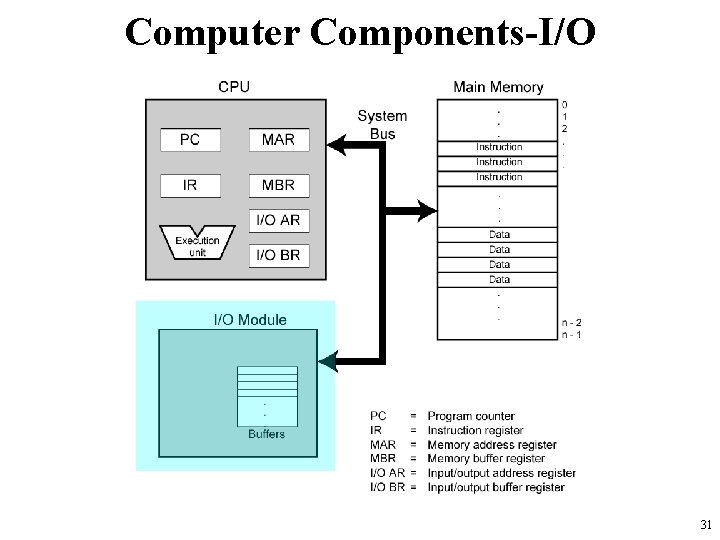

Computer Components-I/O 31

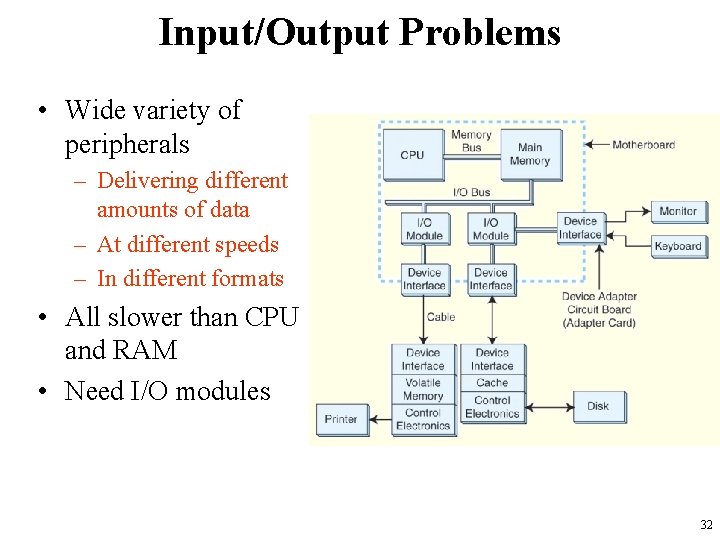

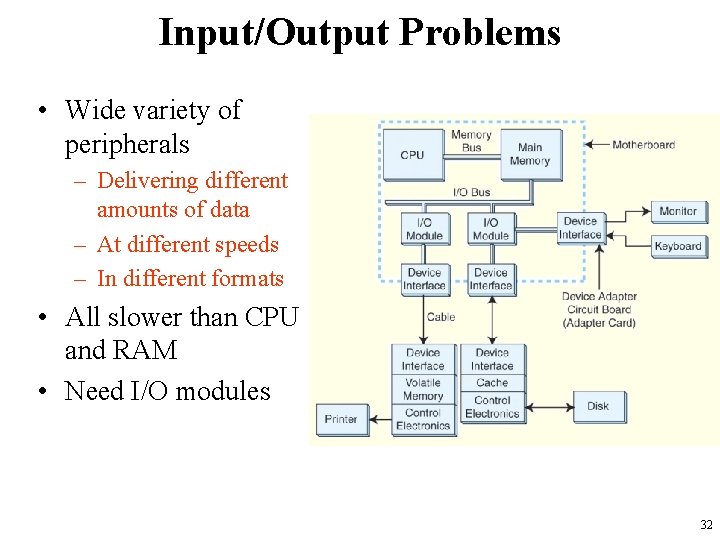

Input/Output Problems • Wide variety of peripherals – Delivering different amounts of data – At different speeds – In different formats • All slower than CPU and RAM • Need I/O modules 32

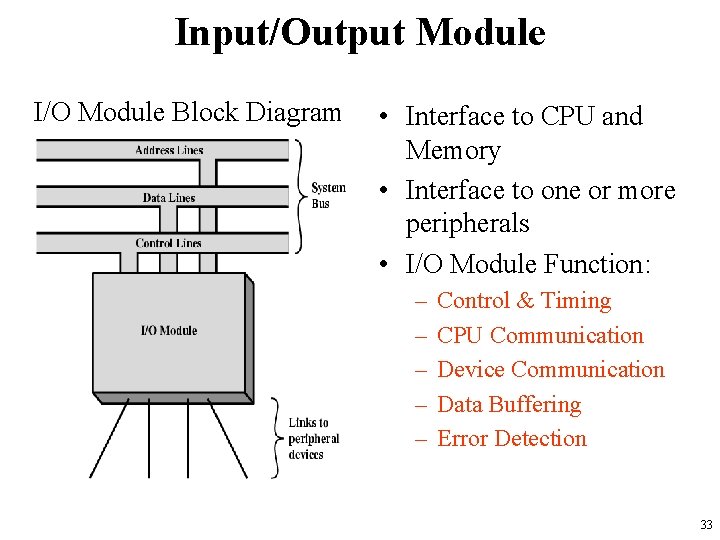

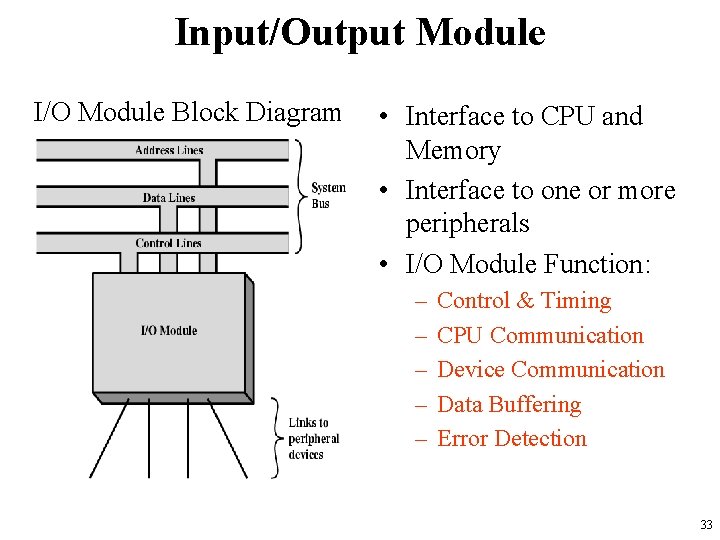

Input/Output Module I/O Module Block Diagram • Interface to CPU and Memory • Interface to one or more peripherals • I/O Module Function: – – – Control & Timing CPU Communication Device Communication Data Buffering Error Detection 33

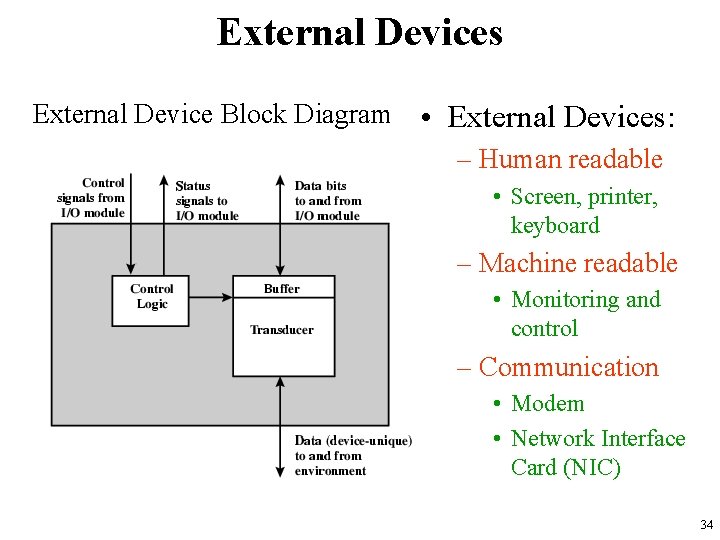

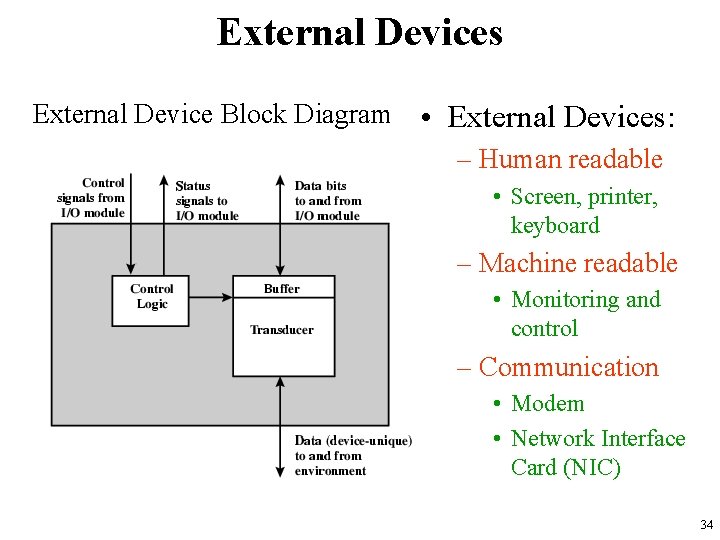

External Devices External Device Block Diagram • External Devices: – Human readable • Screen, printer, keyboard – Machine readable • Monitoring and control – Communication • Modem • Network Interface Card (NIC) 34

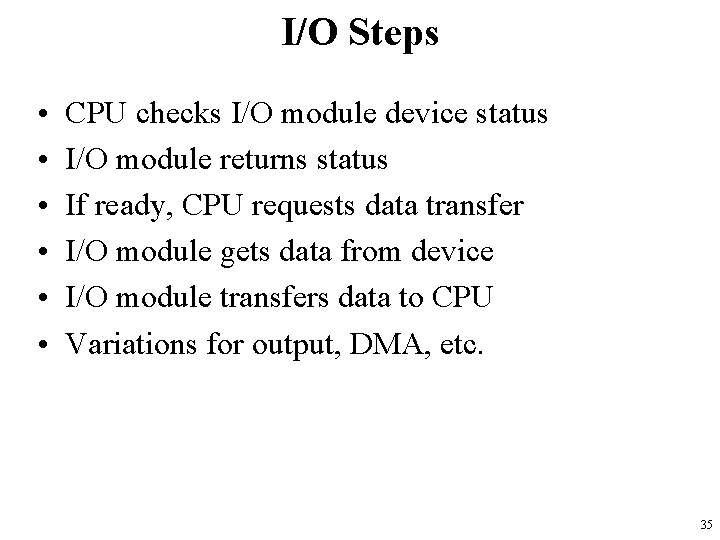

I/O Steps • • • CPU checks I/O module device status I/O module returns status If ready, CPU requests data transfer I/O module gets data from device I/O module transfers data to CPU Variations for output, DMA, etc. 35

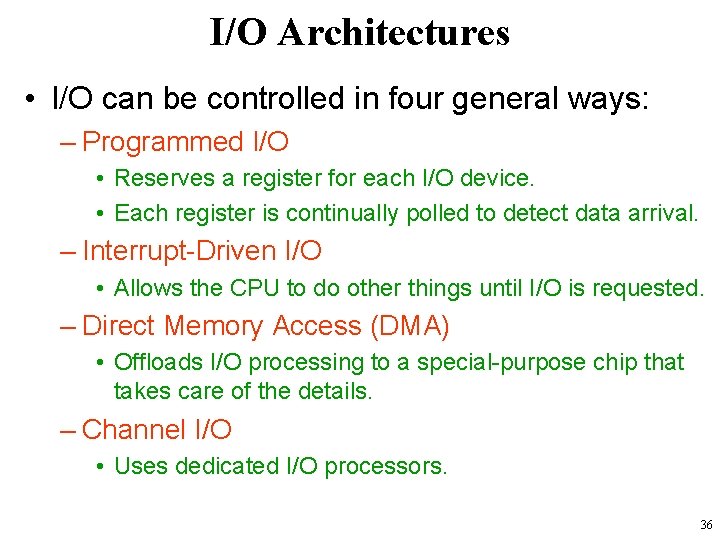

I/O Architectures • I/O can be controlled in four general ways: – Programmed I/O • Reserves a register for each I/O device. • Each register is continually polled to detect data arrival. – Interrupt-Driven I/O • Allows the CPU to do other things until I/O is requested. – Direct Memory Access (DMA) • Offloads I/O processing to a special-purpose chip that takes care of the details. – Channel I/O • Uses dedicated I/O processors. 36

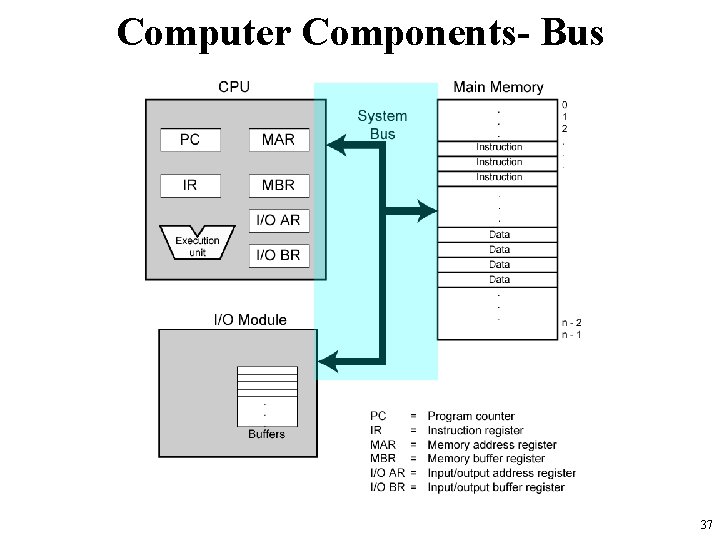

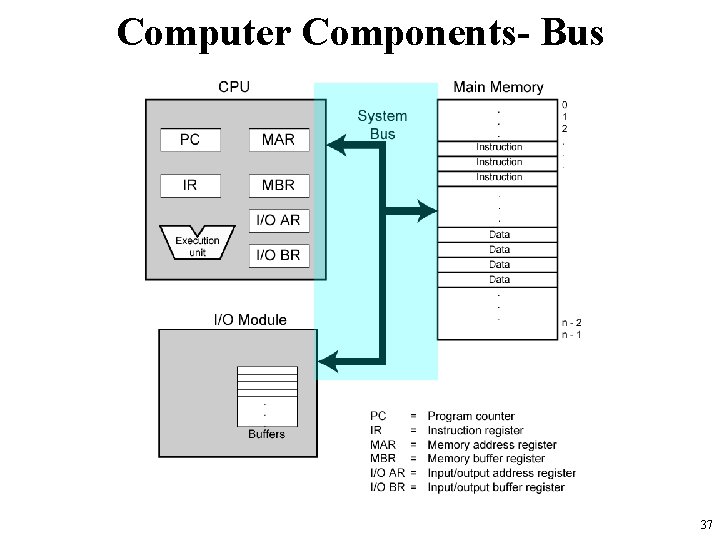

Computer Components- Bus 37

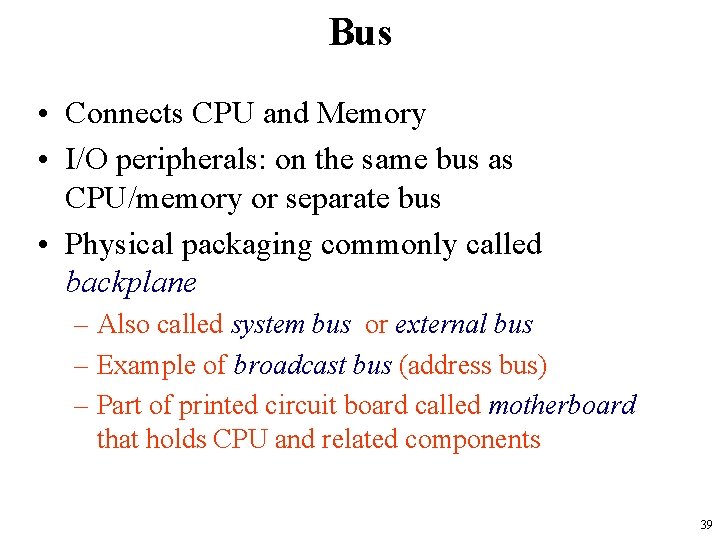

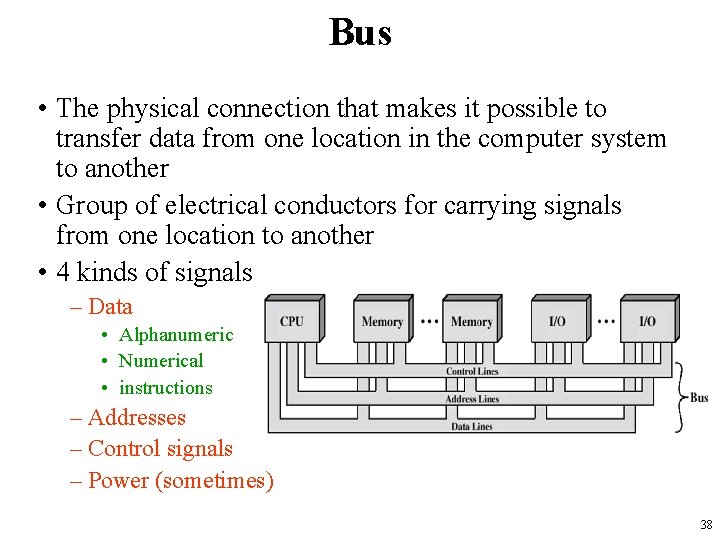

Bus • The physical connection that makes it possible to transfer data from one location in the computer system to another • Group of electrical conductors for carrying signals from one location to another • 4 kinds of signals – Data • Alphanumeric • Numerical • instructions – Addresses – Control signals – Power (sometimes) 38

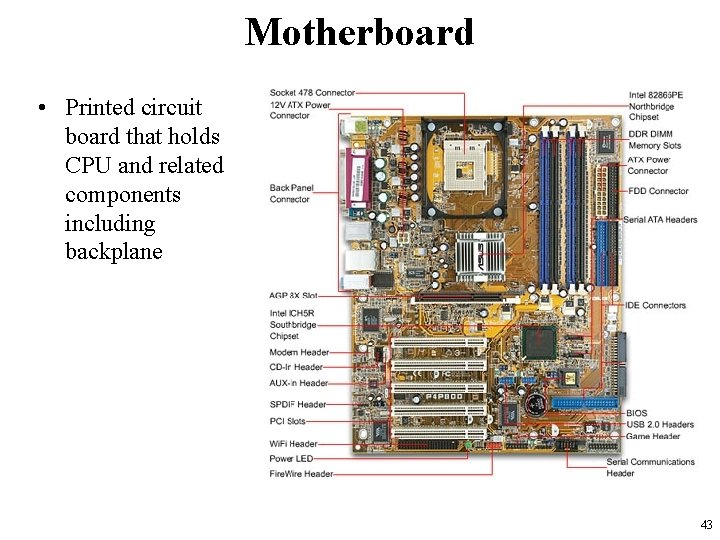

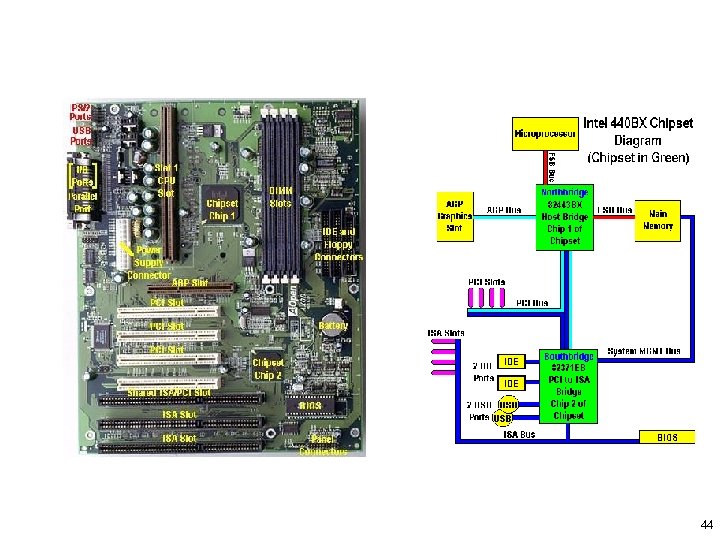

Bus • Connects CPU and Memory • I/O peripherals: on the same bus as CPU/memory or separate bus • Physical packaging commonly called backplane – Also called system bus or external bus – Example of broadcast bus (address bus) – Part of printed circuit board called motherboard that holds CPU and related components 39

Bus Characteristics • Protocol – Documented agreement for communication – Specification that spells out the meaning of each line and each signal on each line • Throughput, i. e. , data transfer rate in bits per second • Data width in bits carried simultaneously 40

Bus types • Data Bus – Carries data – Width is a key determinant of performance • 8, 16, 32, 64 bit • Address bus – Identify the source or destination of data – Bus width determines maximum memory capacity of system • e. g. 8080 has 16 bit address bus giving 64 k address space • Control Bus – Control and timing information • Memory read/write; I/O read/write; Transfer acknowledge; Bus request; Bus grant; Interrupt request; Interrupt acknowledge; Clock; Reset 41

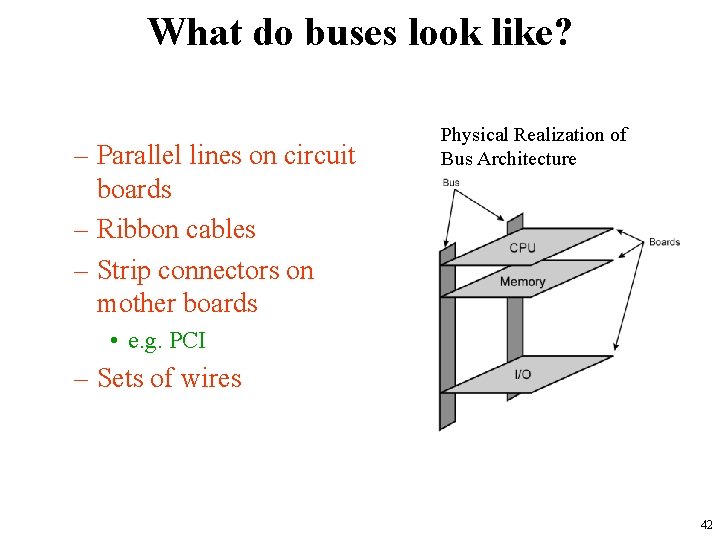

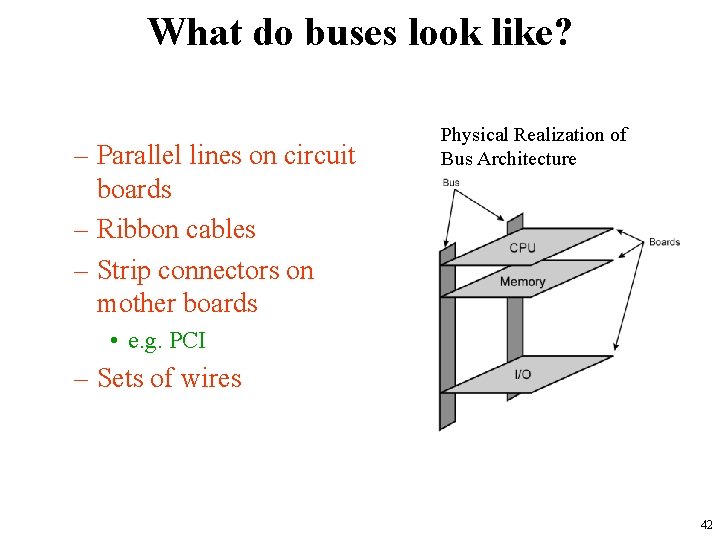

What do buses look like? – Parallel lines on circuit boards – Ribbon cables – Strip connectors on mother boards Physical Realization of Bus Architecture • e. g. PCI – Sets of wires 42

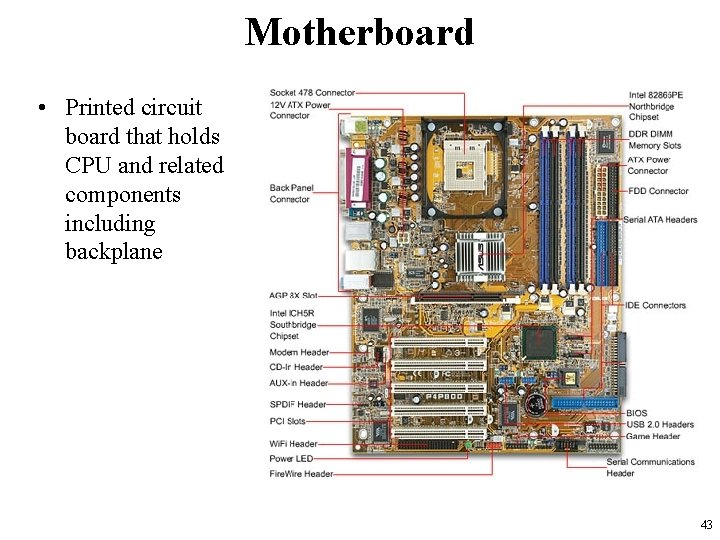

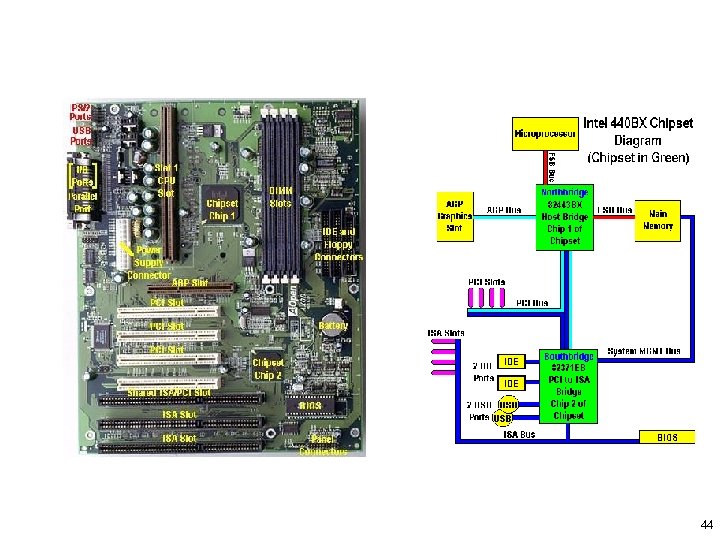

Motherboard • Printed circuit board that holds CPU and related components including backplane 43

44

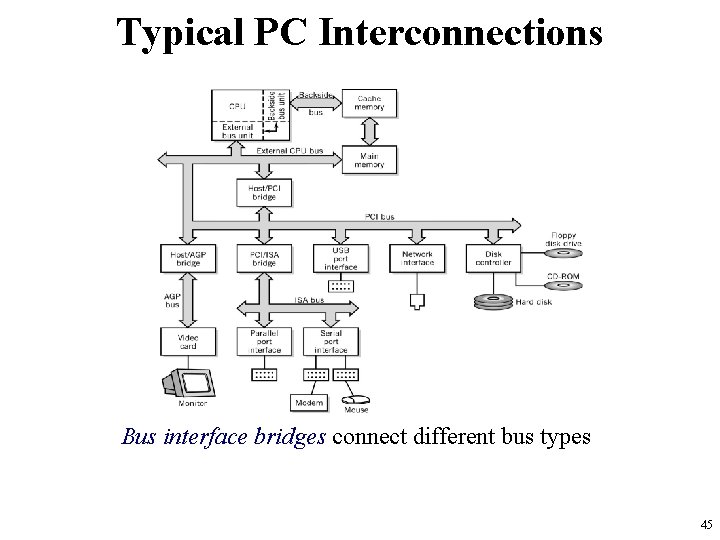

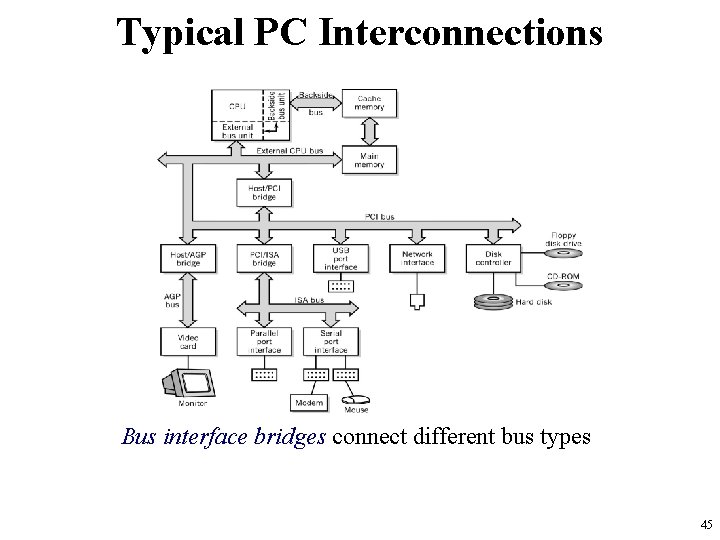

Typical PC Interconnections Bus interface bridges connect different bus types 45

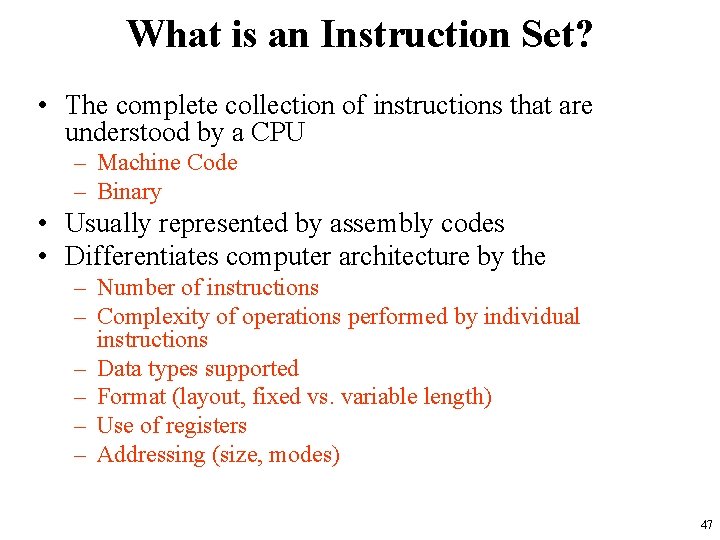

Instructions • Instruction: – Direction given to a computer – Causes electrical signals to be sent through specific circuits for processing • The operation of the processor is determined by the instructions it executes, – which is referrred as machine instructions or computer instructions • The collection of different instructions that the processor execute is referred as the processor’s instruction set. 46

What is an Instruction Set? • The complete collection of instructions that are understood by a CPU – Machine Code – Binary • Usually represented by assembly codes • Differentiates computer architecture by the – Number of instructions – Complexity of operations performed by individual instructions – Data types supported – Format (layout, fixed vs. variable length) – Use of registers – Addressing (size, modes) 47

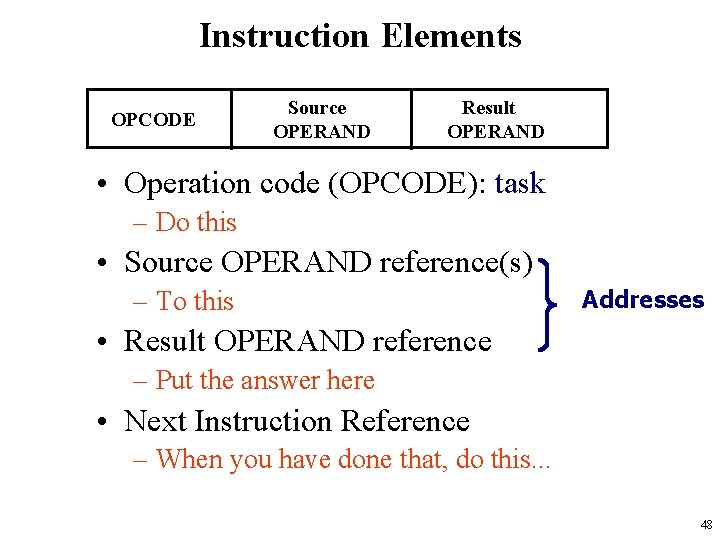

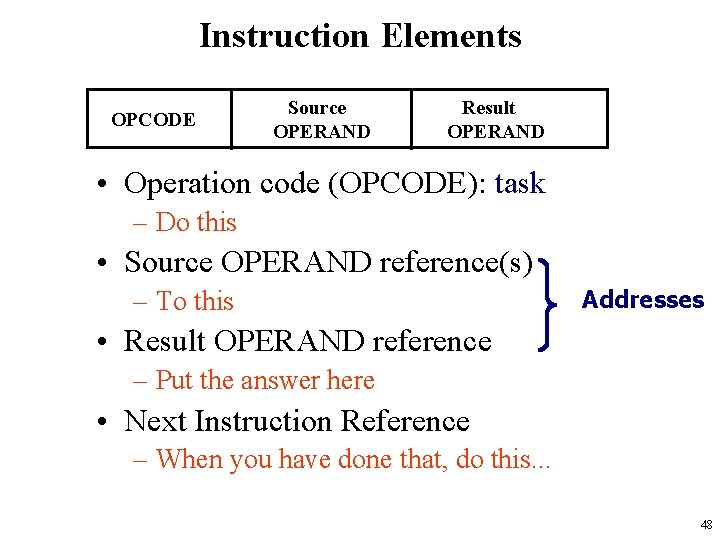

Instruction Elements OPCODE Source OPERAND Result OPERAND • Operation code (OPCODE): task – Do this • Source OPERAND reference(s) – To this Addresses • Result OPERAND reference – Put the answer here • Next Instruction Reference – When you have done that, do this. . . 48

Instruction Elements • Source and Result Operands can be in one of the following areas: – Main memory – Virtual memory – Cache – CPU register – I/O device 49

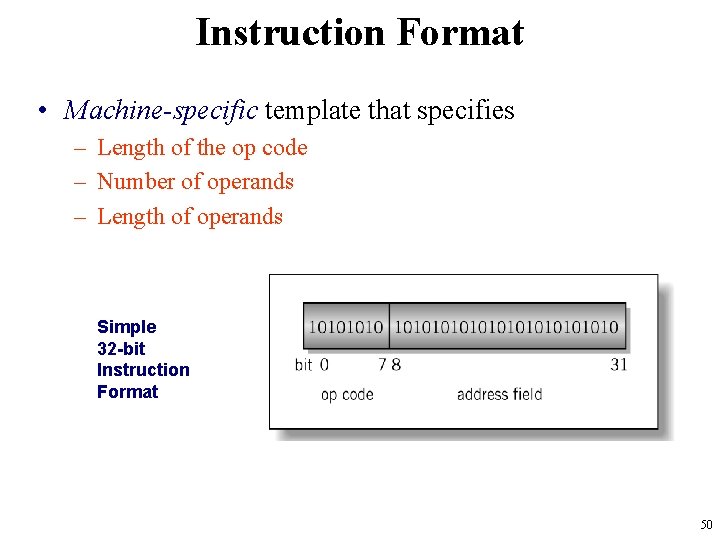

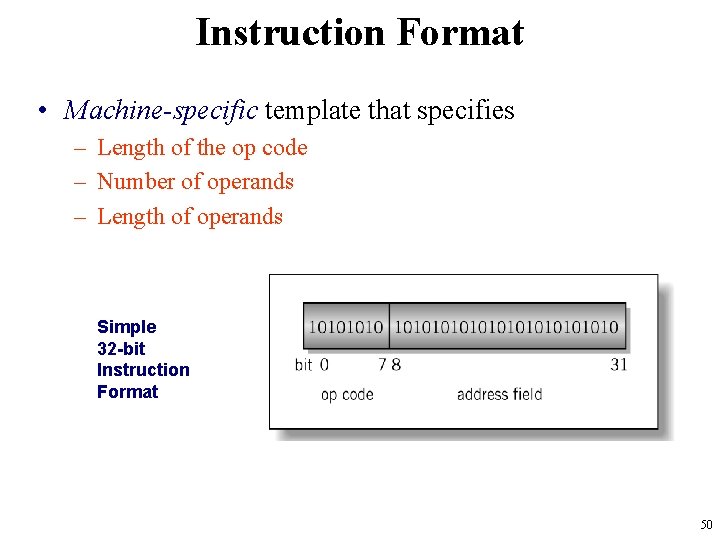

Instruction Format • Machine-specific template that specifies – Length of the op code – Number of operands – Length of operands Simple 32 -bit Instruction Format 50

Instruction Types • Data Transfer (load, store) – Most common, greatest flexibility – Involve memory and registers – What’s a word ? 16? 32? 64 bits? • Arithmetic – Operators + - / * ^ – Integers and floating point • Logical or Boolean – Relational operators: > < = – Boolean operators AND, OR, XOR, NOR, and NOT • Single operand manipulation instructions – Negating, decrementing, incrementing 51

More Instruction Types • Bit manipulation instructions – Flags to test for conditions • • • Shift and rotate Program control Stack instructions Multiple data instructions I/O and machine control 52

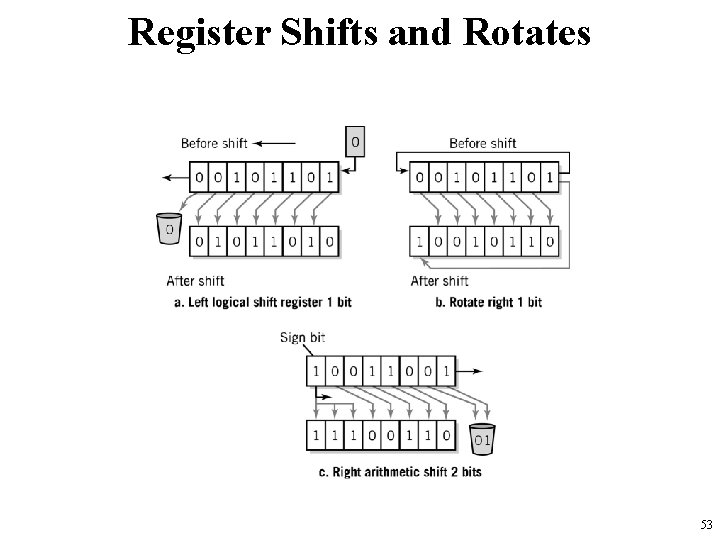

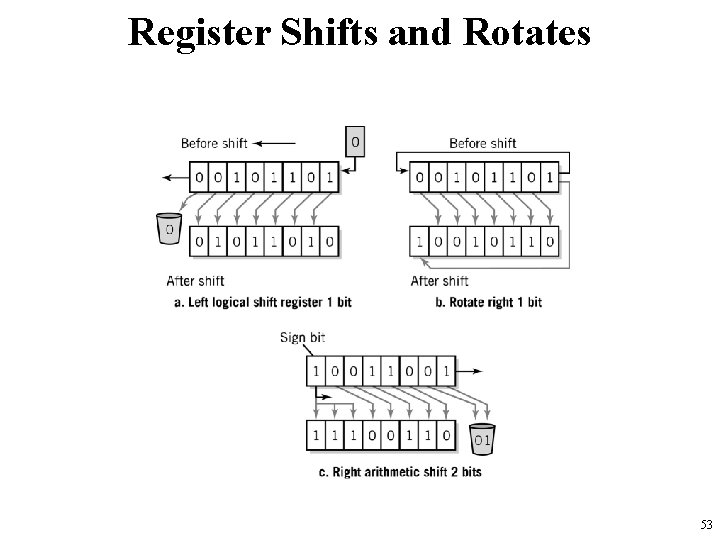

Register Shifts and Rotates 53

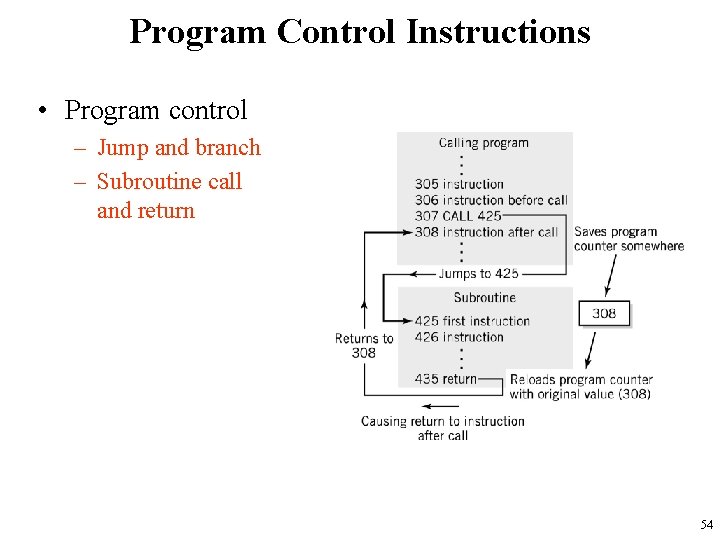

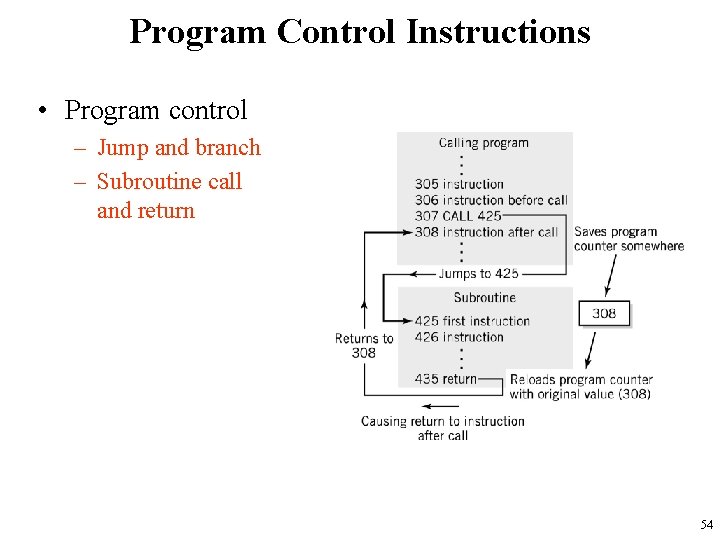

Program Control Instructions • Program control – Jump and branch – Subroutine call and return 54

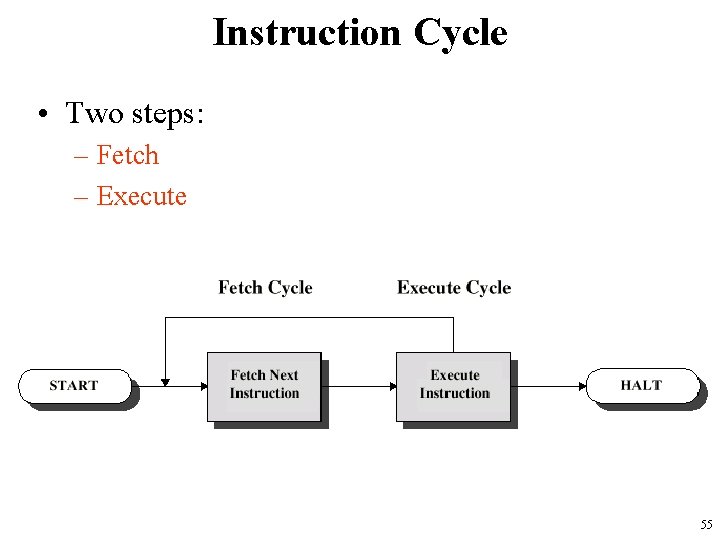

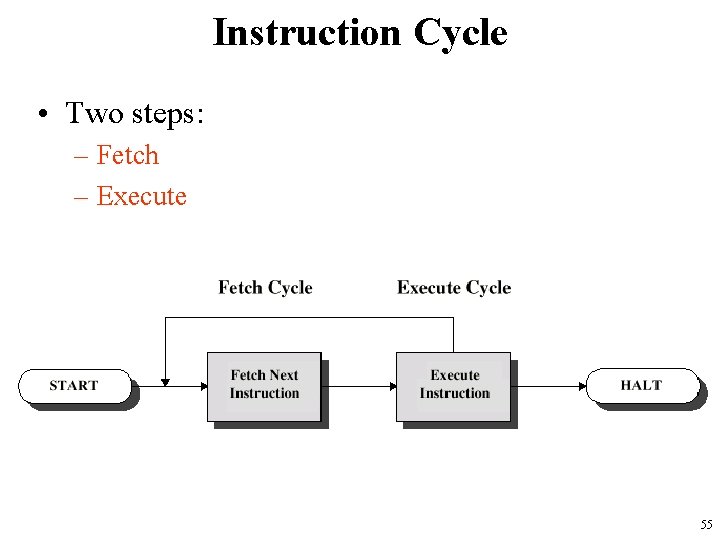

Instruction Cycle • Two steps: – Fetch – Execute 55

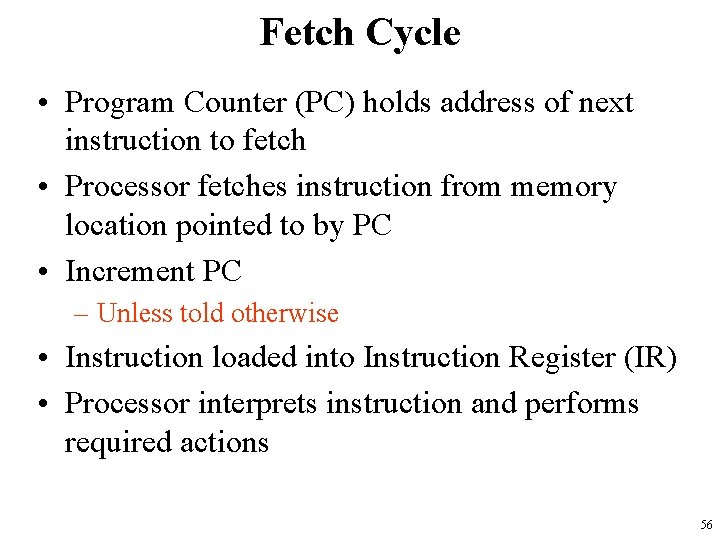

Fetch Cycle • Program Counter (PC) holds address of next instruction to fetch • Processor fetches instruction from memory location pointed to by PC • Increment PC – Unless told otherwise • Instruction loaded into Instruction Register (IR) • Processor interprets instruction and performs required actions 56

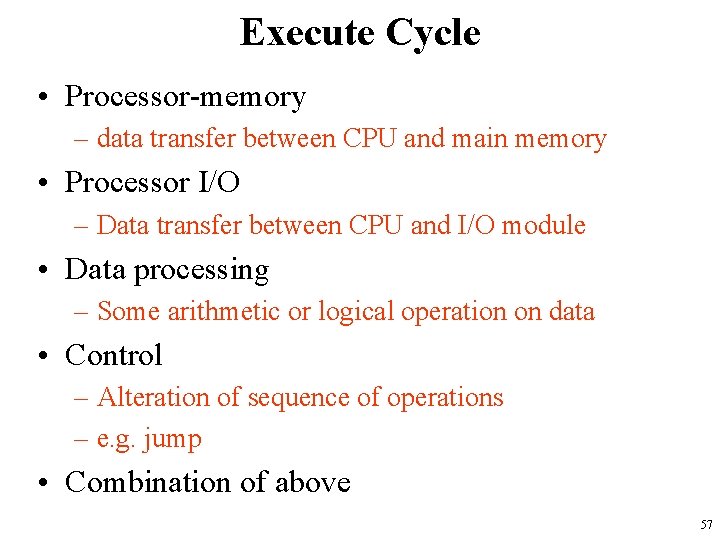

Execute Cycle • Processor-memory – data transfer between CPU and main memory • Processor I/O – Data transfer between CPU and I/O module • Data processing – Some arithmetic or logical operation on data • Control – Alteration of sequence of operations – e. g. jump • Combination of above 57

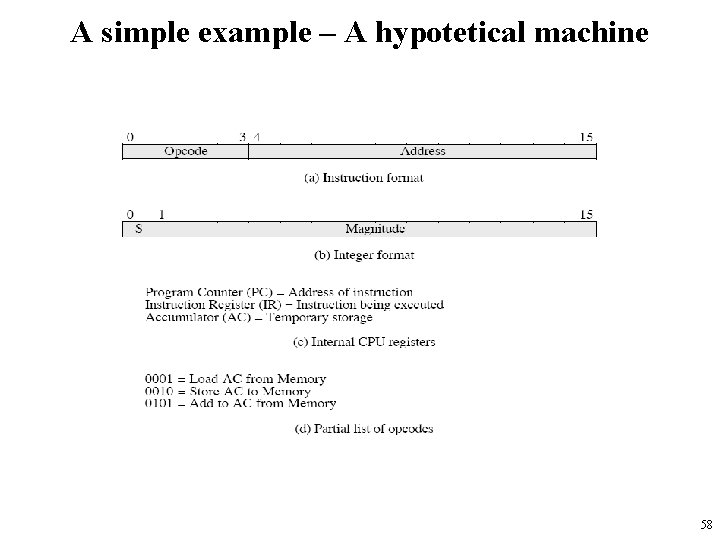

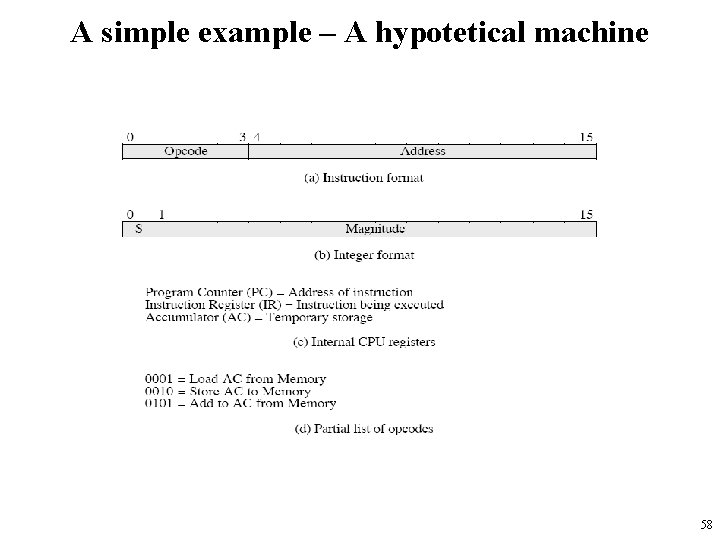

A simple example – A hypotetical machine 58

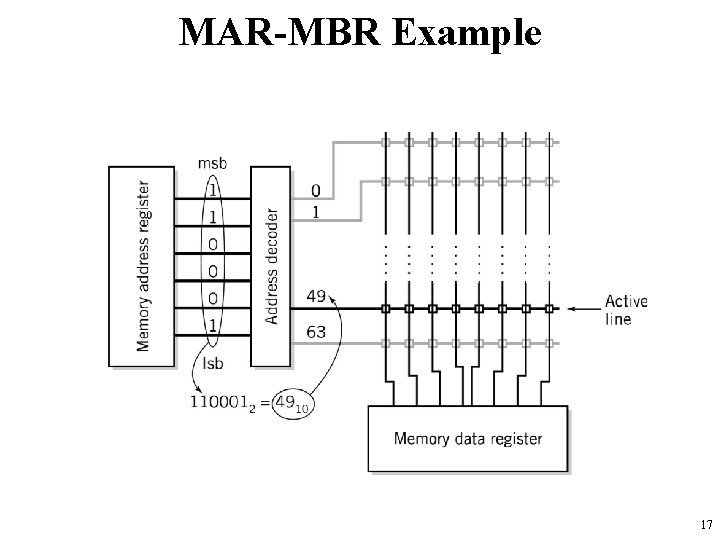

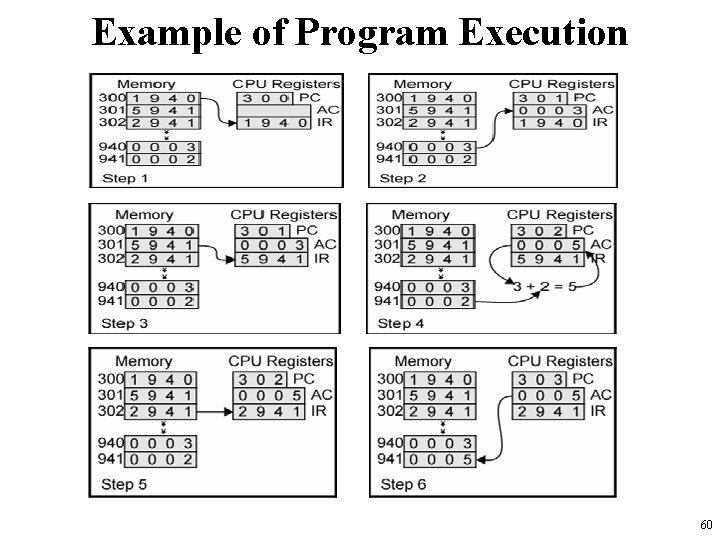

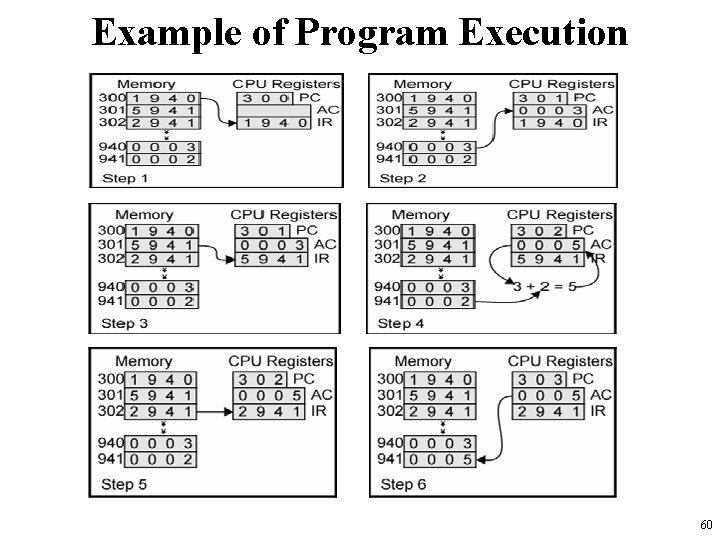

A simple example – • Next figure illustrates a partial program execution. • It adds the contents of the memory word at address 940 to the contents of the memory word at address 941 and stores the result in the address 941. • Here 3 instructions (3 fetch and 3 execute cycles) are required 59

Example of Program Execution 60