COE 202 Introduction to Verilog Computer Engineering Department

![Module and Ports declaration module [module-name] ( [mode] [ d a t a - Module and Ports declaration module [module-name] ( [mode] [ d a t a -](https://slidetodoc.com/presentation_image_h/0055896f3619b53b4ccf8d486acbbdbf/image-7.jpg)

- Slides: 25

COE 202 Introduction to Verilog Computer Engineering Department College of Computer Sciences and Engineering King Fahd University of Petroleum and Minerals

Outline v Introduction v Verilog Syntax v Definition of a Module v Gate Level Modeling v Module Instantiation v Propagation Delay v Boolean Equation-Based Behavioral Models of Combinational Logic v Test Bench Example

Introduction v Verilog is one of the hardware description languages (HDL) available in the industry for hardware modeling, simulation and design. v It allows designers to describe their hardware at different levels of detail (e. g. gate-level, behavioral lavel) v Parallel not serial like programming languages. v Verilog can describe everything from single gate to full computer system.

Verilog v A digital system can be described at several levels of details (more details means more design entry time!): e. g. ² Gate-level Net-list similar to schematic or breadboarding ² Behavioral description: programming-like structures (if-then-else, case, loops …etc) to describe what the circuit does (i. e. behavior) rather than how requires some additional (synthesis) software to actually obtain the logic design v A digital system is described as a set of modules v The module is the basic unit of design

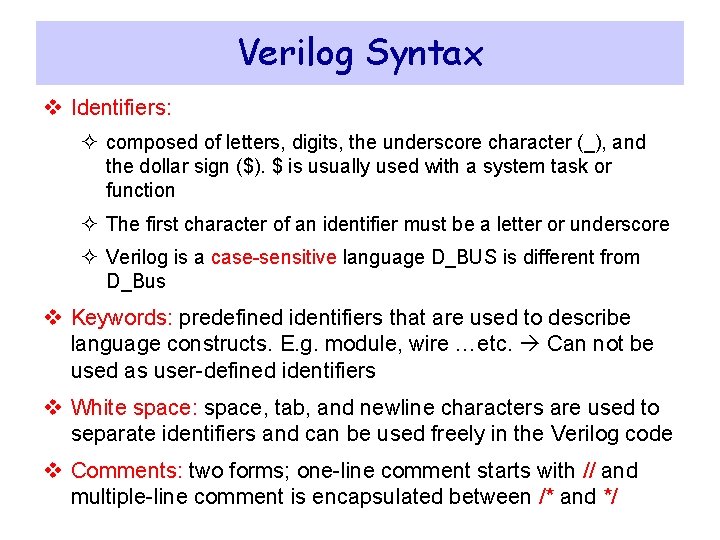

Verilog Syntax v Identifiers: ² composed of letters, digits, the underscore character (_), and the dollar sign ($). $ is usually used with a system task or function ² The first character of an identifier must be a letter or underscore ² Verilog is a case-sensitive language D_BUS is different from D_Bus v Keywords: predefined identifiers that are used to describe language constructs. E. g. module, wire …etc. Can not be used as user-defined identifiers v White space: space, tab, and newline characters are used to separate identifiers and can be used freely in the Verilog code v Comments: two forms; one-line comment starts with // and multiple-line comment is encapsulated between /* and */

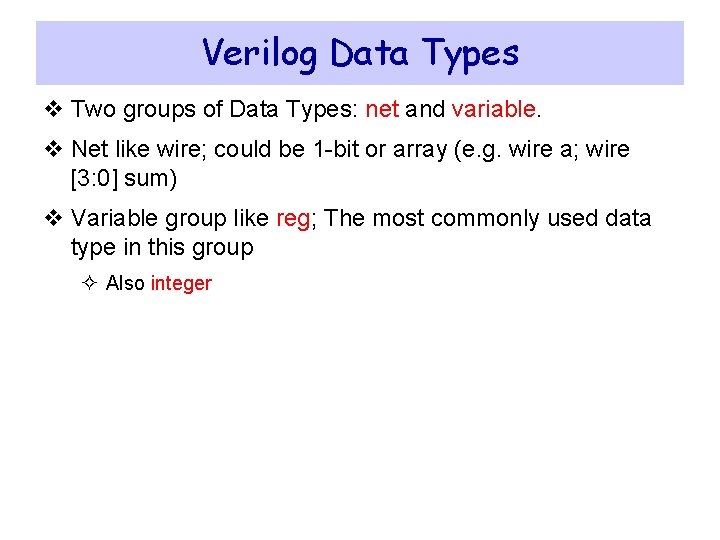

Verilog Data Types v Two groups of Data Types: net and variable. v Net like wire; could be 1 -bit or array (e. g. wire a; wire [3: 0] sum) v Variable group like reg; The most commonly used data type in this group ² Also integer

![Module and Ports declaration module modulename mode d a t a Module and Ports declaration module [module-name] ( [mode] [ d a t a -](https://slidetodoc.com/presentation_image_h/0055896f3619b53b4ccf8d486acbbdbf/image-7.jpg)

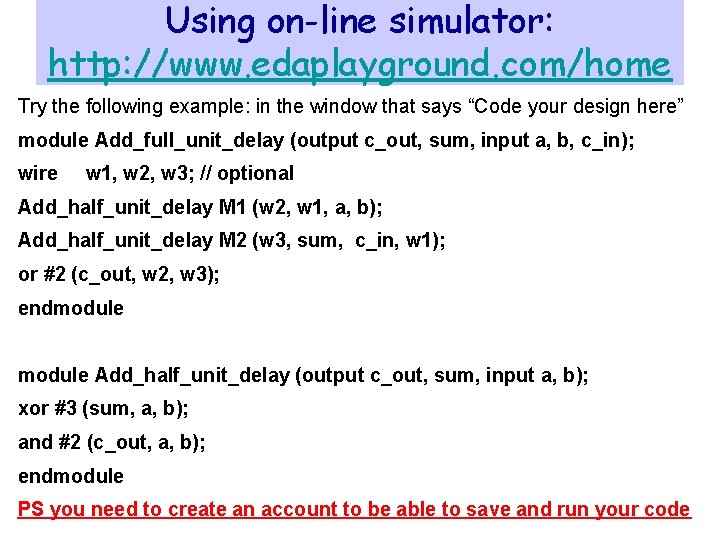

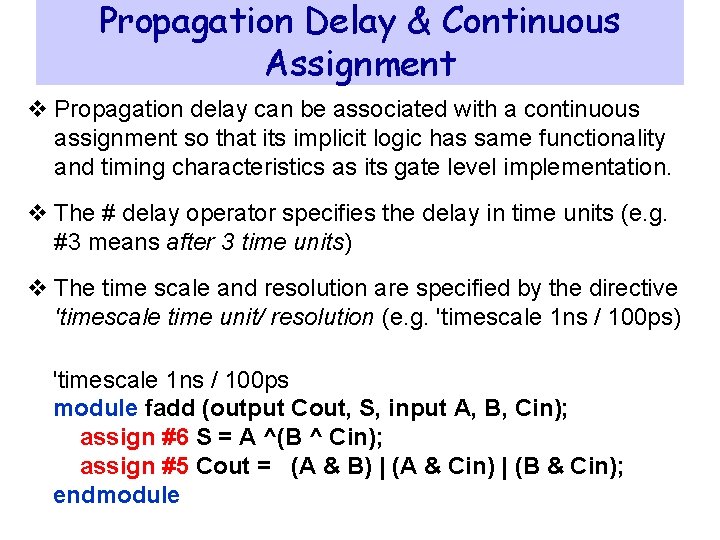

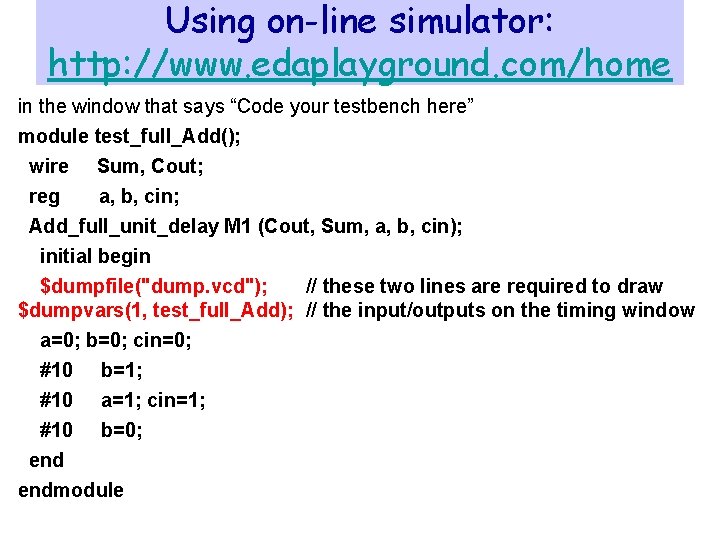

Module and Ports declaration module [module-name] ( [mode] [ d a t a - t y p e ] [ p o r t - n a m e s ] , . . . [mode] [ d a t a - t y p e ] [ p o r t - n a m e s ] ); Ex 1. : module eq 2 ( input wire [1: 0] a , b , output wire aeqb ); Ex 2. : module eq 1( input i 0 , il , // no data type declaration output eq // all will be wires ); v. Data-type could be wire, reg, integer, real …etc.

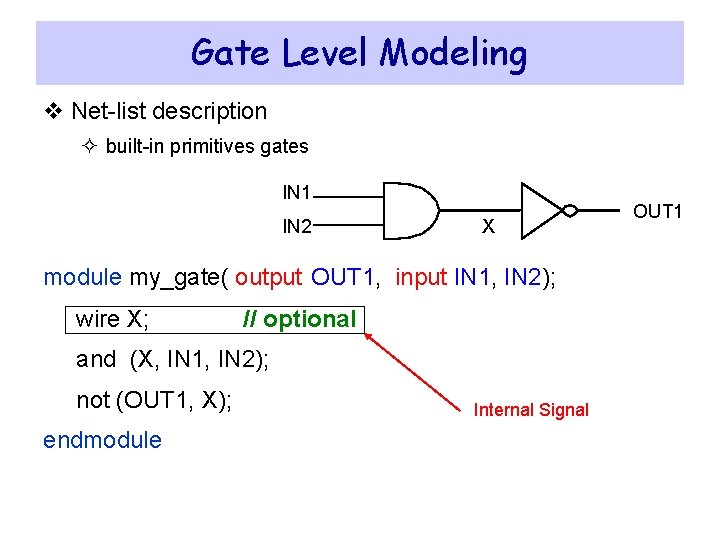

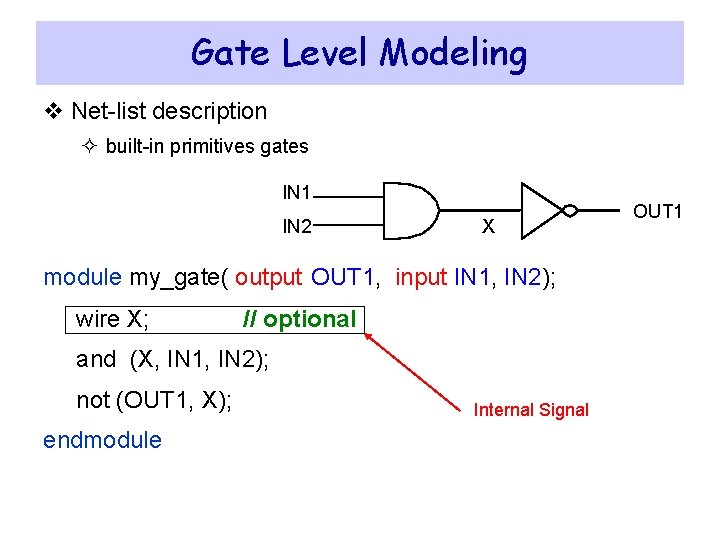

Gate Level Modeling v Net-list description ² built-in primitives gates IN 1 IN 2 X module my_gate( output OUT 1, input IN 1, IN 2); wire X; // optional and (X, IN 1, IN 2); not (OUT 1, X); endmodule Internal Signal OUT 1

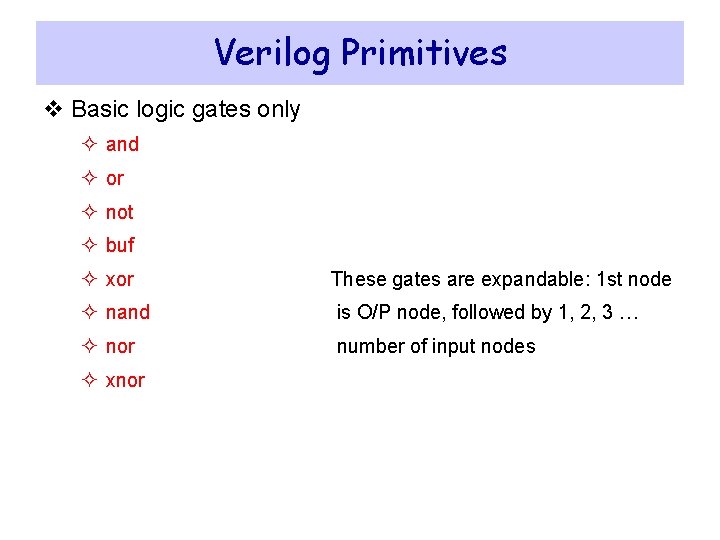

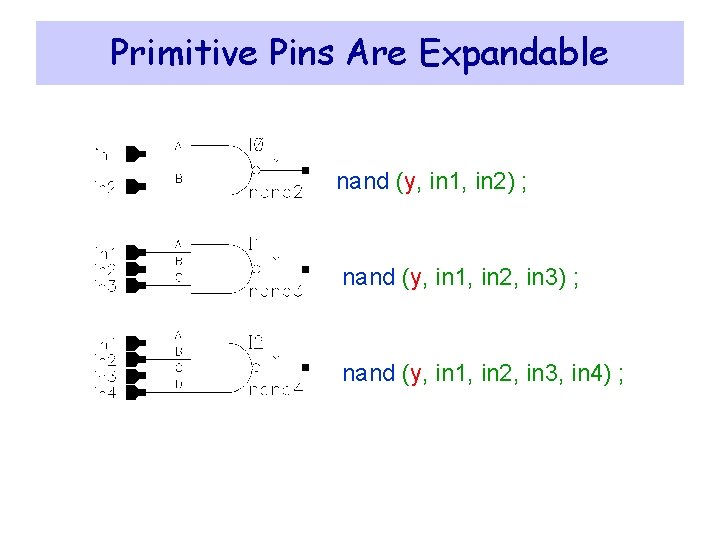

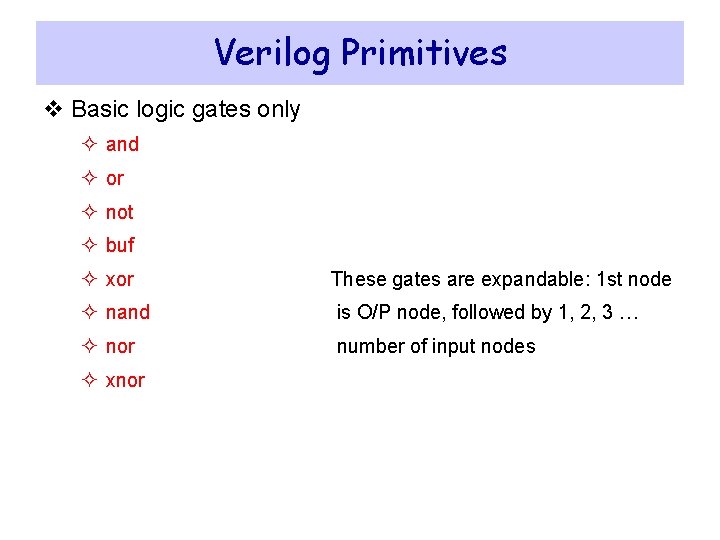

Verilog Primitives v Basic logic gates only ² and ² or ² not ² buf ² xor These gates are expandable: 1 st node ² nand is O/P node, followed by 1, 2, 3 … ² nor number of input nodes ² xnor

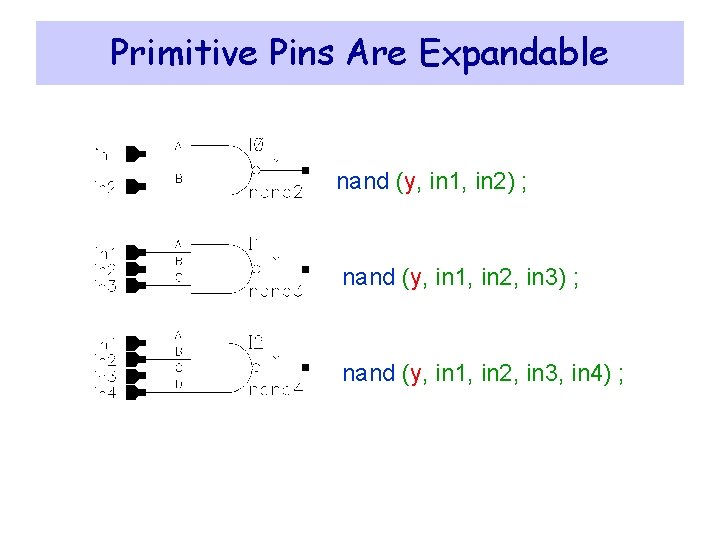

Primitive Pins Are Expandable nand (y, in 1, in 2) ; nand (y, in 1, in 2, in 3, in 4) ;

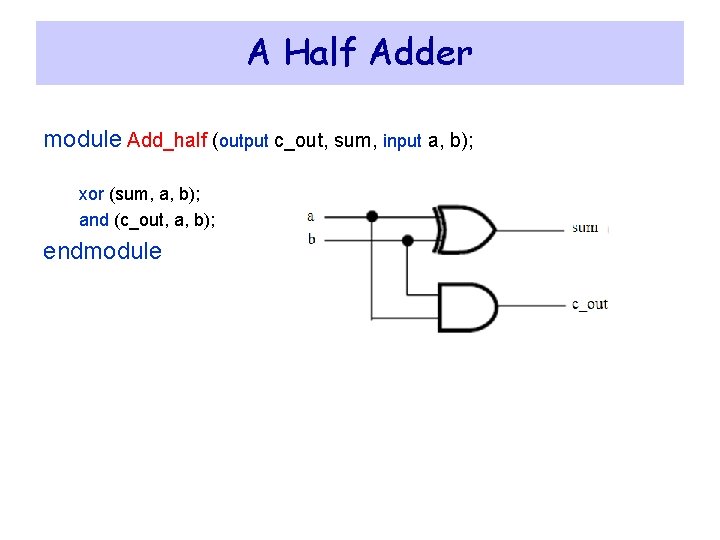

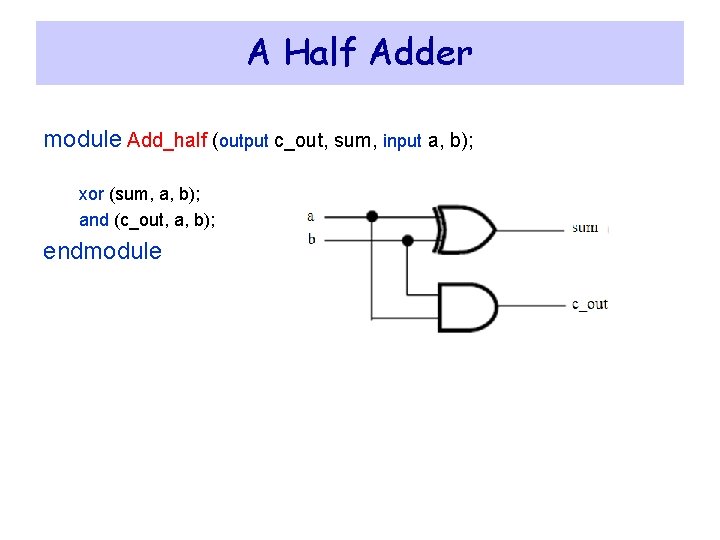

A Half Adder module Add_half (output c_out, sum, input a, b); xor (sum, a, b); and (c_out, a, b); endmodule

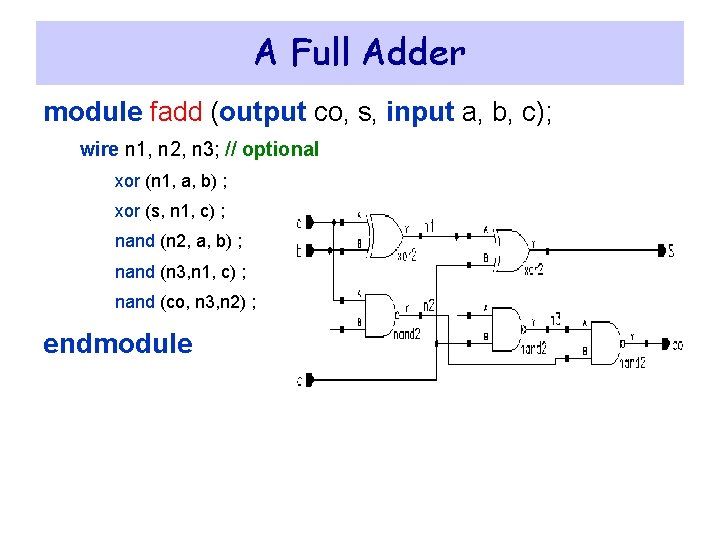

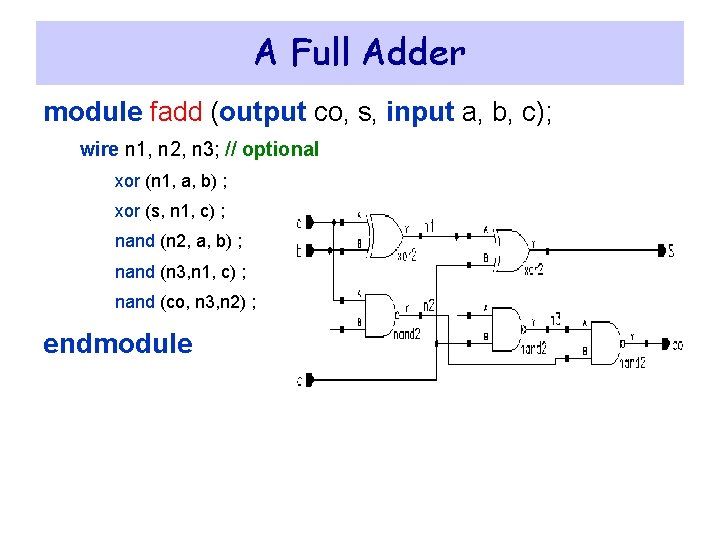

A Full Adder module fadd (output co, s, input a, b, c); wire n 1, n 2, n 3; // optional xor (n 1, a, b) ; xor (s, n 1, c) ; nand (n 2, a, b) ; nand (n 3, n 1, c) ; nand (co, n 3, n 2) ; endmodule

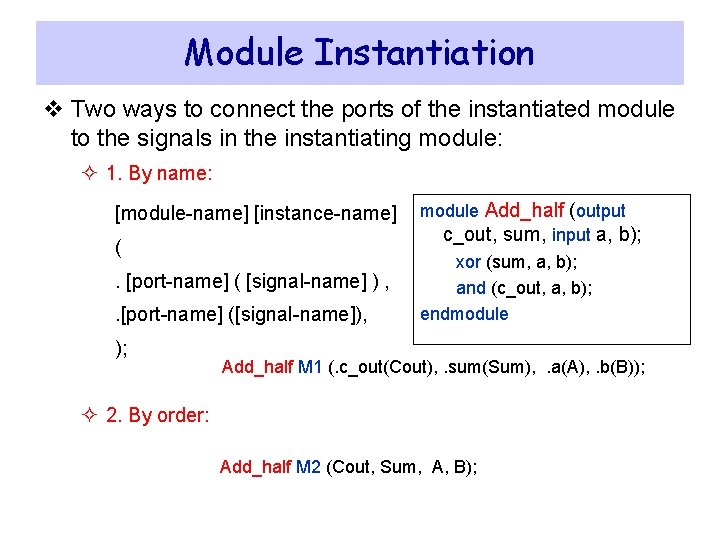

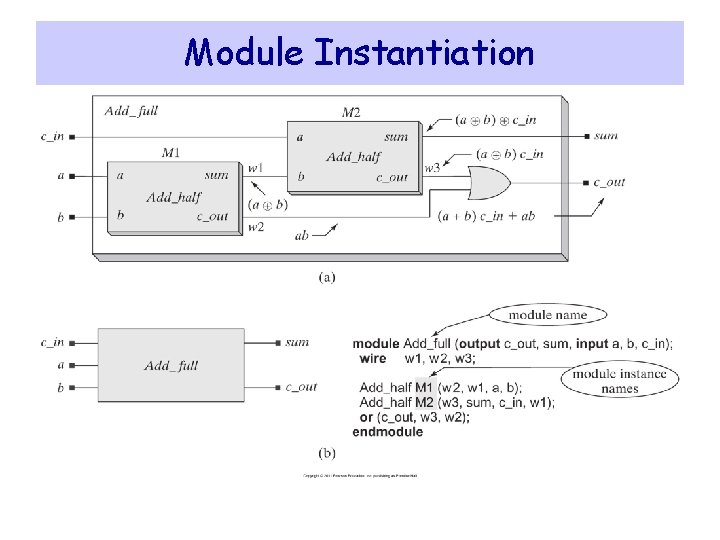

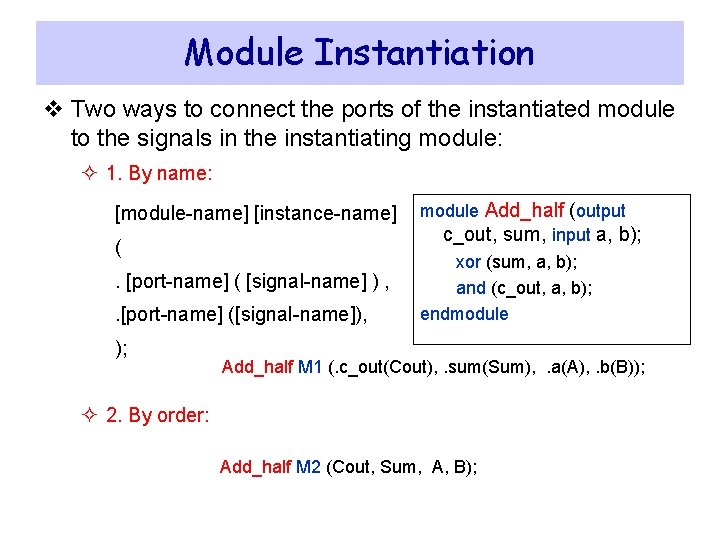

Module Instantiation v Two ways to connect the ports of the instantiated module to the signals in the instantiating module: ² 1. By name: [module-name] [instance-name] (. [port-name] ( [signal-name] ) , . [port-name] ([signal-name]), ); module Add_half (output c_out, sum, input a, b); xor (sum, a, b); and (c_out, a, b); endmodule Add_half M 1 (. c_out(Cout), . sum(Sum), . a(A), . b(B)); ² 2. By order: Add_half M 2 (Cout, Sum, A, B);

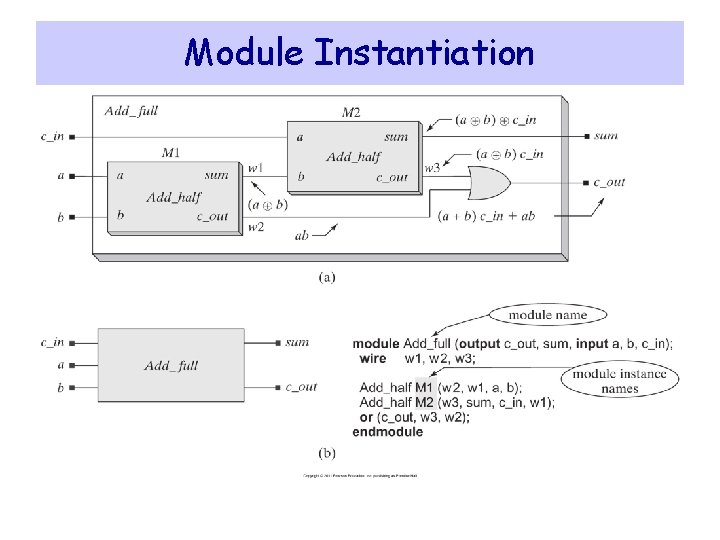

Module Instantiation

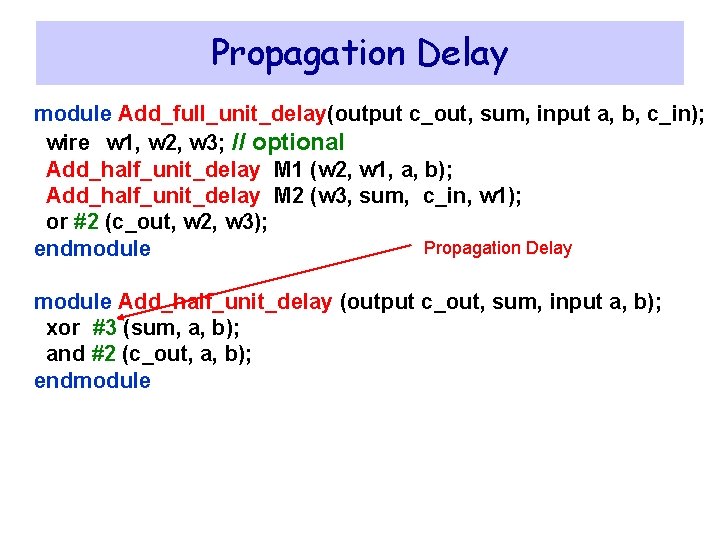

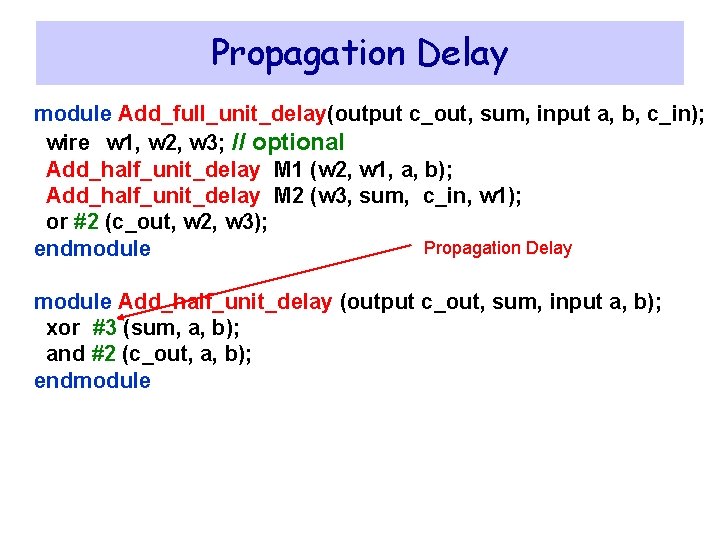

Propagation Delay module Add_full_unit_delay(output c_out, sum, input a, b, c_in); wire w 1, w 2, w 3; // optional Add_half_unit_delay M 1 (w 2, w 1, a, b); Add_half_unit_delay M 2 (w 3, sum, c_in, w 1); or #2 (c_out, w 2, w 3); Propagation Delay endmodule Add_half_unit_delay (output c_out, sum, input a, b); xor #3 (sum, a, b); and #2 (c_out, a, b); endmodule

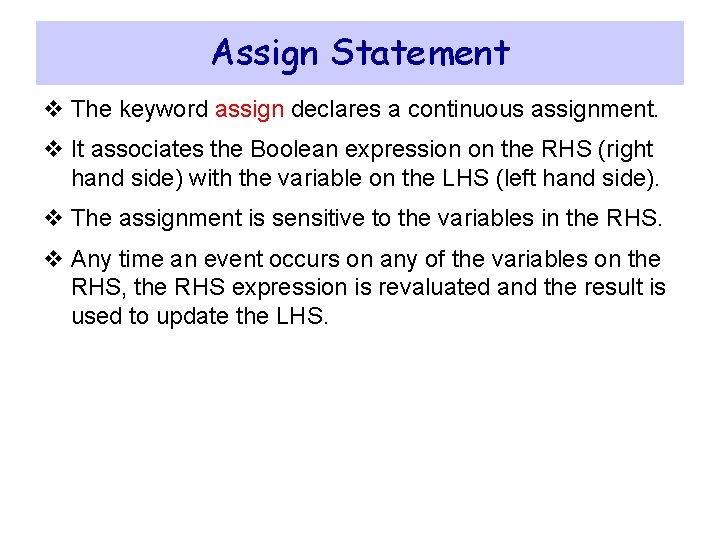

Assign Statement v The keyword assign declares a continuous assignment. v It associates the Boolean expression on the RHS (right hand side) with the variable on the LHS (left hand side). v The assignment is sensitive to the variables in the RHS. v Any time an event occurs on any of the variables on the RHS, the RHS expression is revaluated and the result is used to update the LHS.

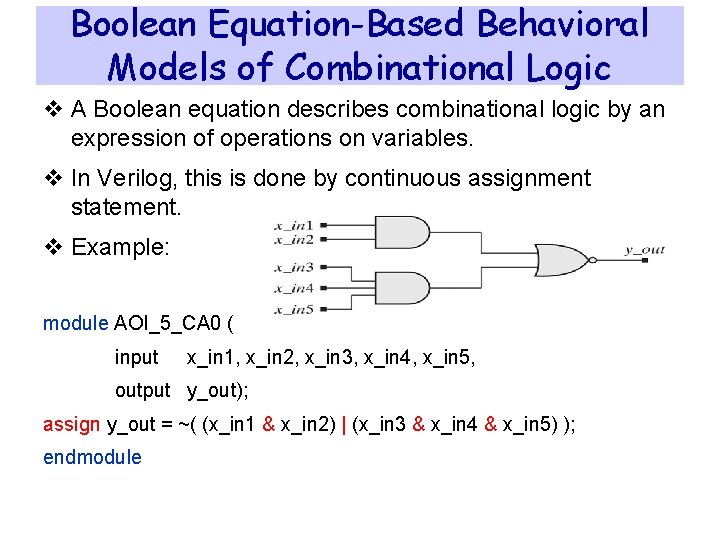

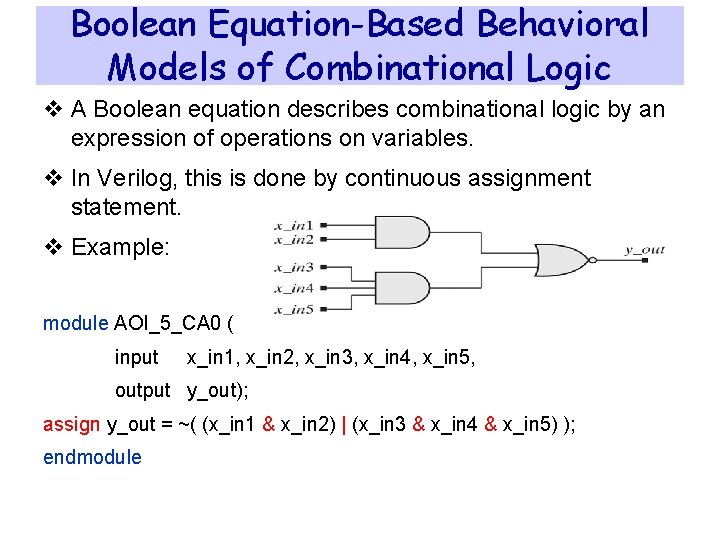

Boolean Equation-Based Behavioral Models of Combinational Logic v A Boolean equation describes combinational logic by an expression of operations on variables. v In Verilog, this is done by continuous assignment statement. v Example: module AOI_5_CA 0 ( input x_in 1, x_in 2, x_in 3, x_in 4, x_in 5, output y_out); assign y_out = ~( (x_in 1 & x_in 2) | (x_in 3 & x_in 4 & x_in 5) ); endmodule

Verilog Operators {} concatenation ~ bit-wise NOT & bit-wise AND % modulus | bit-wise OR > >= < <= relational ^ bit-wise XOR ^~ ~^ bit-wise XNOR & reduction AND | reduction OR ~& reduction NAND ~| reduction NOR ^ reduction XOR ~^ ^~ reduction XNOR << shift left >> shift right ! logical NOT && logical AND || logical OR == logical equality != logical inequality === case equality !== case inequality ? : conditional Used in Boolean functions arithmetic Used in comparing two variables (relational or logic comparisons) + - * / **

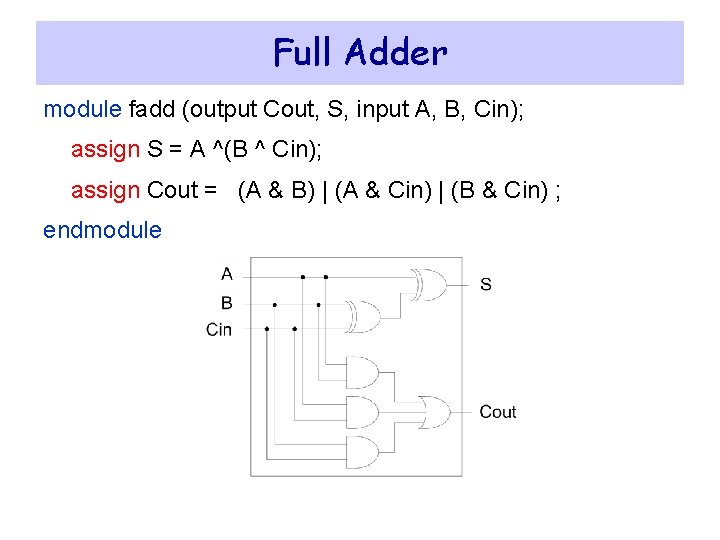

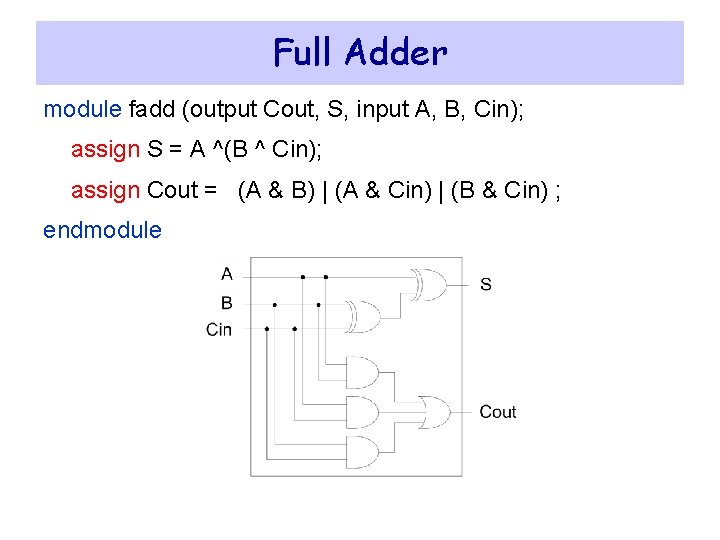

Full Adder module fadd (output Cout, S, input A, B, Cin); assign S = A ^(B ^ Cin); assign Cout = (A & B) | (A & Cin) | (B & Cin) ; endmodule

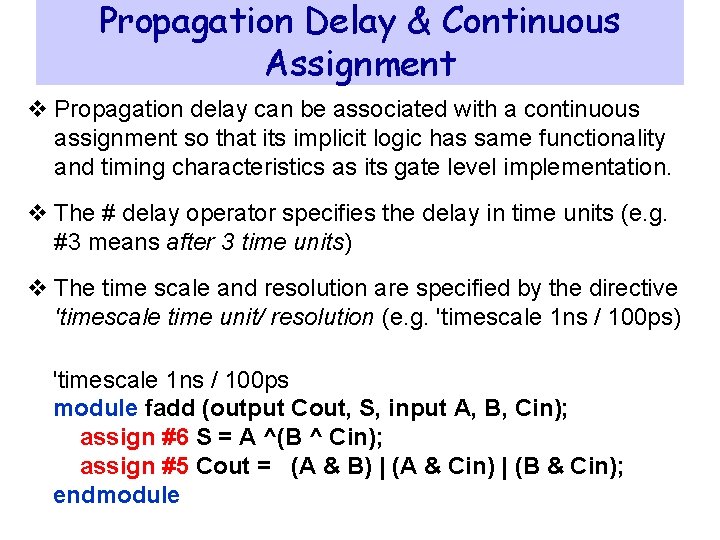

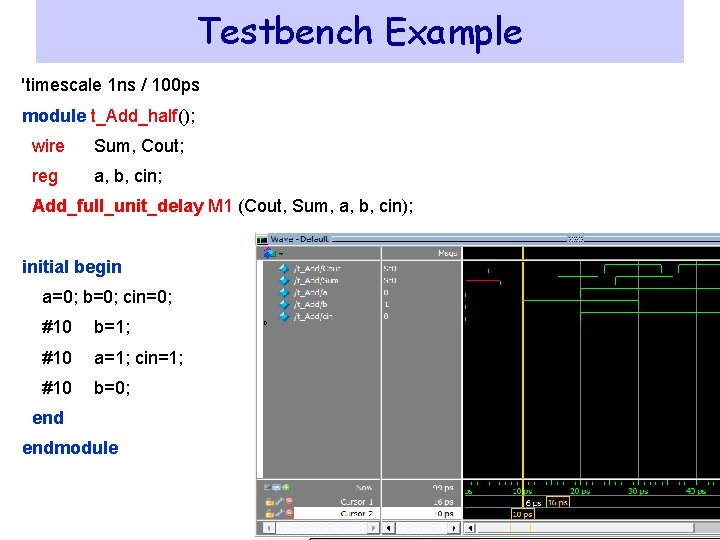

Propagation Delay & Continuous Assignment v Propagation delay can be associated with a continuous assignment so that its implicit logic has same functionality and timing characteristics as its gate level implementation. v The # delay operator specifies the delay in time units (e. g. #3 means after 3 time units) v The time scale and resolution are specified by the directive 'timescale time unit/ resolution (e. g. 'timescale 1 ns / 100 ps) 'timescale 1 ns / 100 ps module fadd (output Cout, S, input A, B, Cin); assign #6 S = A ^(B ^ Cin); assign #5 Cout = (A & B) | (A & Cin) | (B & Cin); endmodule

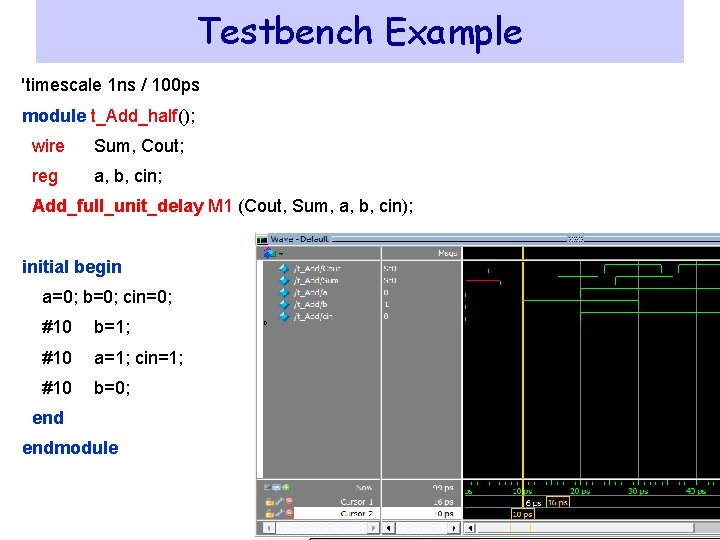

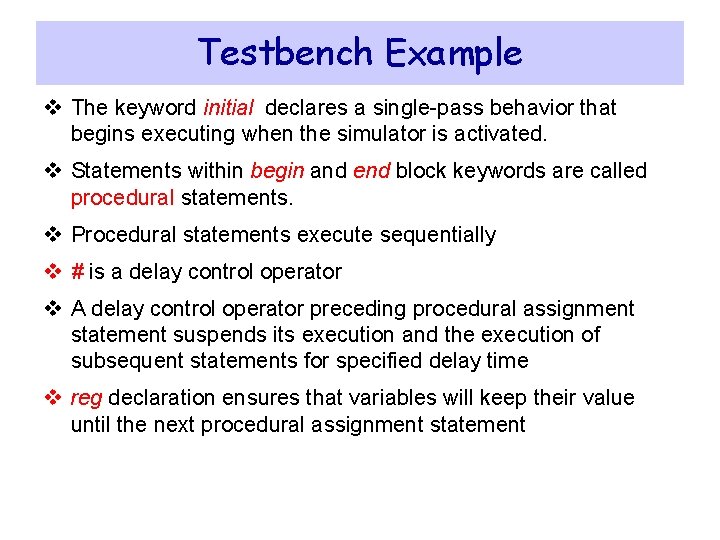

Testbench Example 'timescale 1 ns / 100 ps module t_Add_half(); wire Sum, Cout; reg a, b, cin; Add_full_unit_delay M 1 (Cout, Sum, a, b, cin); initial begin a=0; b=0; cin=0; #10 b=1; #10 a=1; cin=1; #10 b=0; endmodule

Testbench Example v The keyword initial declares a single-pass behavior that begins executing when the simulator is activated. v Statements within begin and end block keywords are called procedural statements. v Procedural statements execute sequentially v # is a delay control operator v A delay control operator preceding procedural assignment statement suspends its execution and the execution of subsequent statements for specified delay time v reg declaration ensures that variables will keep their value until the next procedural assignment statement

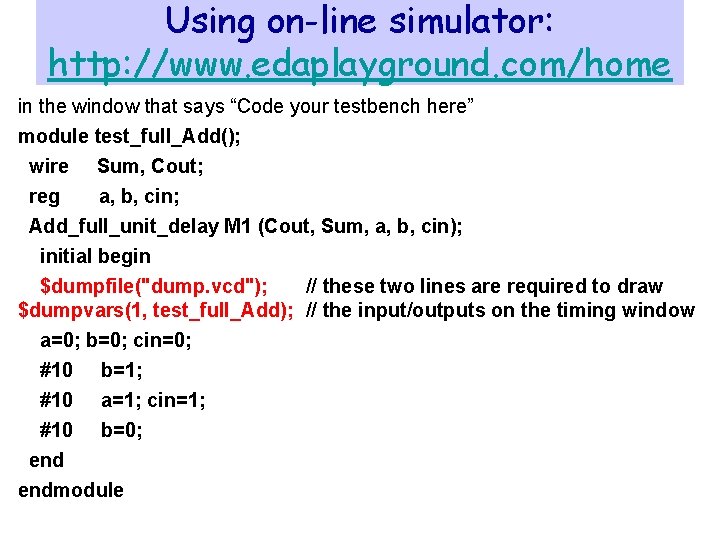

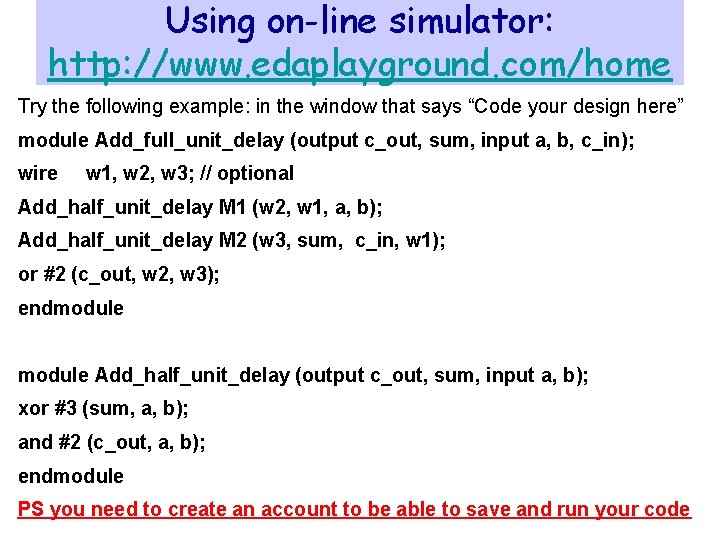

Using on-line simulator: http: //www. edaplayground. com/home Try the following example: in the window that says “Code your design here” module Add_full_unit_delay (output c_out, sum, input a, b, c_in); wire w 1, w 2, w 3; // optional Add_half_unit_delay M 1 (w 2, w 1, a, b); Add_half_unit_delay M 2 (w 3, sum, c_in, w 1); or #2 (c_out, w 2, w 3); endmodule Add_half_unit_delay (output c_out, sum, input a, b); xor #3 (sum, a, b); and #2 (c_out, a, b); endmodule PS you need to create an account to be able to save and run your code

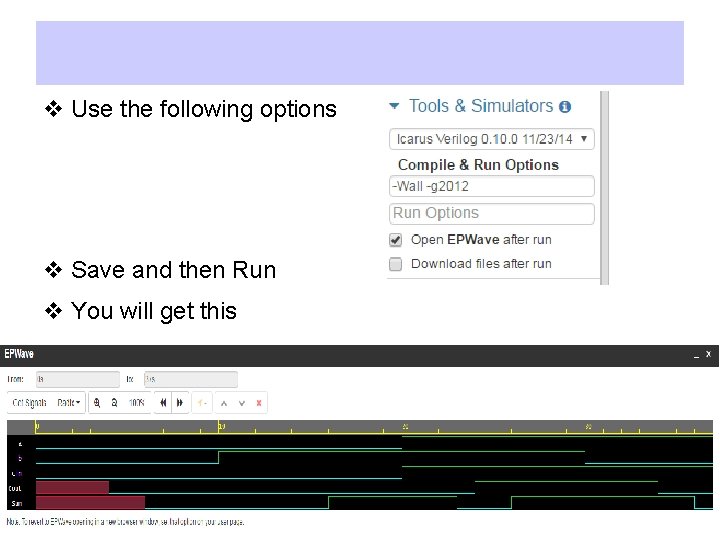

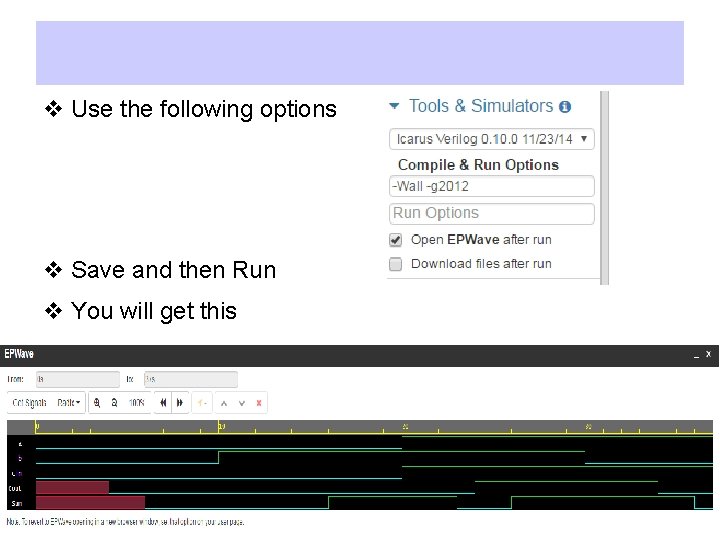

Using on-line simulator: http: //www. edaplayground. com/home in the window that says “Code your testbench here” module test_full_Add(); wire Sum, Cout; reg a, b, cin; Add_full_unit_delay M 1 (Cout, Sum, a, b, cin); initial begin $dumpfile("dump. vcd"); // these two lines are required to draw $dumpvars(1, test_full_Add); // the input/outputs on the timing window a=0; b=0; cin=0; #10 b=1; #10 a=1; cin=1; #10 b=0; endmodule

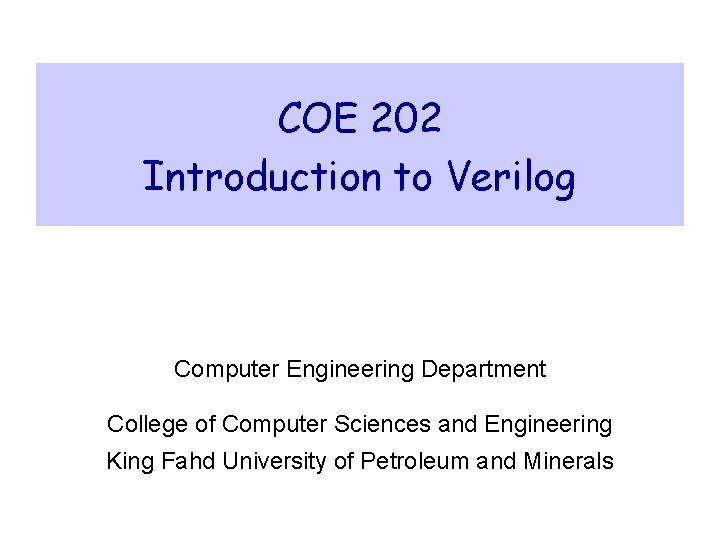

v Use the following options v Save and then Run v You will get this