Verilog AULA 3 Introduo Verilog uma linguagem como

![Características Exemplo de programa: module add (a, b, out); // cabeçalho input [7: 0] Características Exemplo de programa: module add (a, b, out); // cabeçalho input [7: 0]](https://slidetodoc.com/presentation_image/1fdf82d64c257f27b9f3057228e0dad2/image-3.jpg)

![Exemplo de contador module count 4(clk, rst, q); input clk, rst; output [3: 0] Exemplo de contador module count 4(clk, rst, q); input clk, rst; output [3: 0]](https://slidetodoc.com/presentation_image/1fdf82d64c257f27b9f3057228e0dad2/image-22.jpg)

- Slides: 29

Verilog AULA - 3

Introdução Verilog é uma linguagem, como VHDL, largamente usada para descrever sistemas digitais, utilizada universalmente. Histórico: Inicialmente, Verilog era uma linguagem proprietária desenvolvida pela empresa Gateway. Verilog foi desenvolvida nos anos 1980 e foi inicialmente usada para modelar dispositivos ASIC. Em 1990, Verilog caiu no dominio público e agora está sendo padronizado como IEEE 1364.

![Características Exemplo de programa module add a b out cabeçalho input 7 0 Características Exemplo de programa: module add (a, b, out); // cabeçalho input [7: 0]](https://slidetodoc.com/presentation_image/1fdf82d64c257f27b9f3057228e0dad2/image-3.jpg)

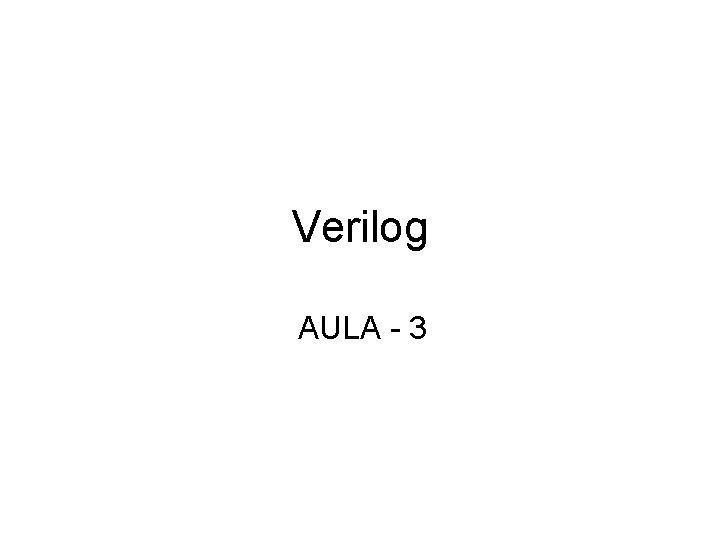

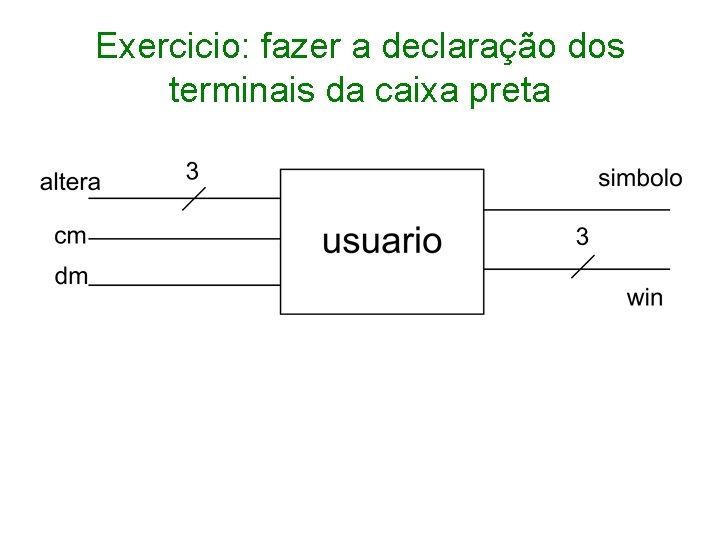

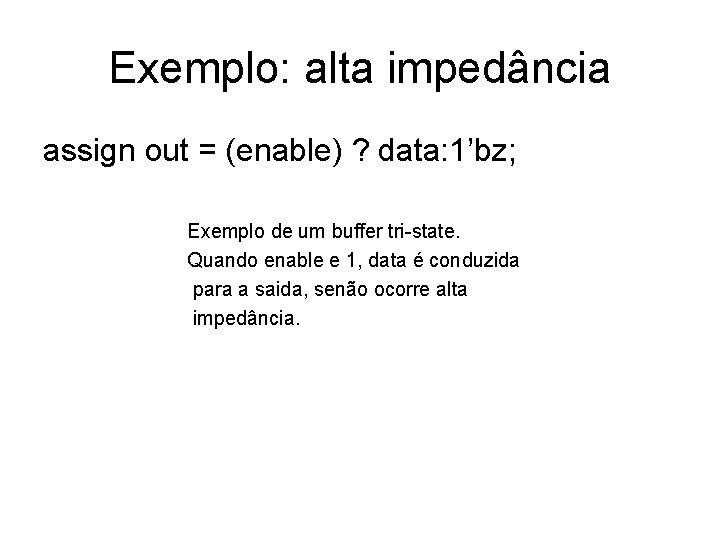

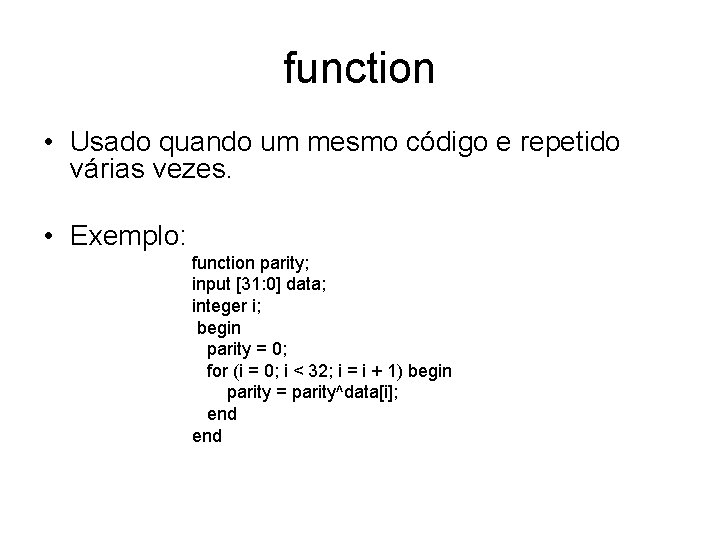

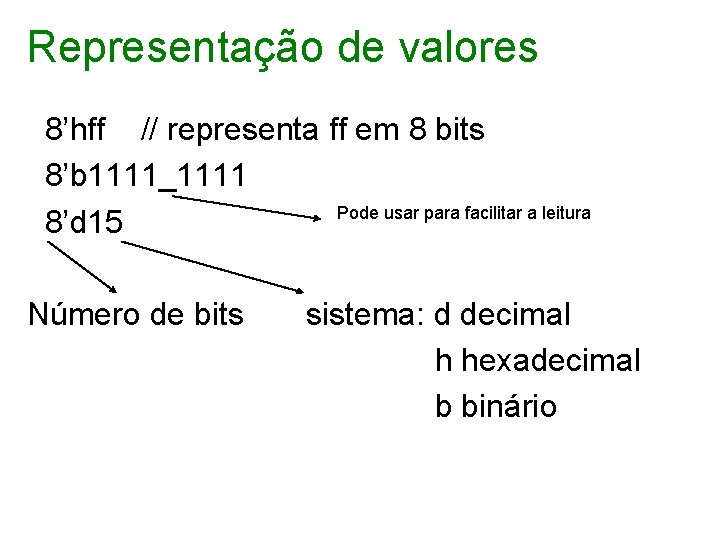

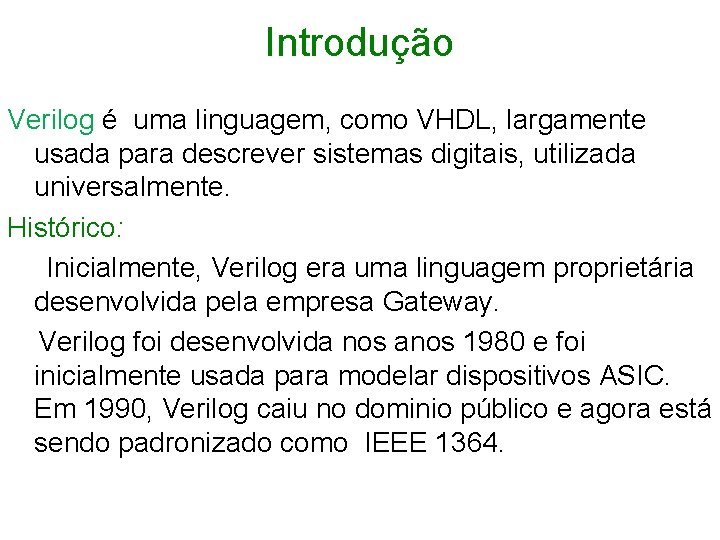

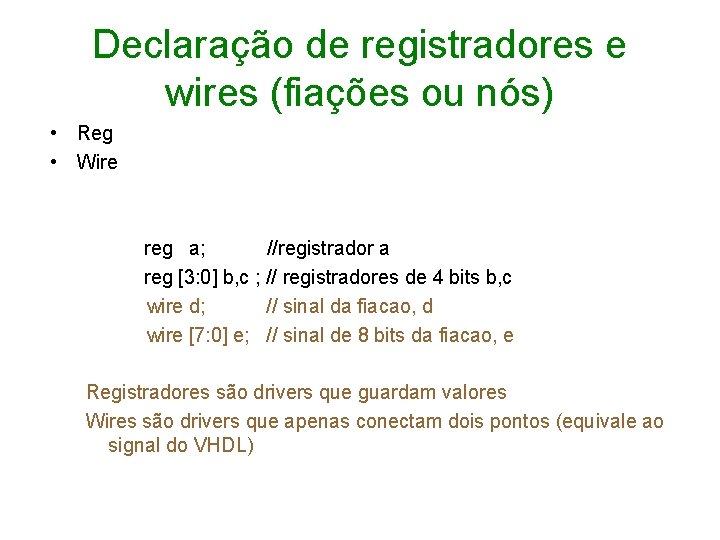

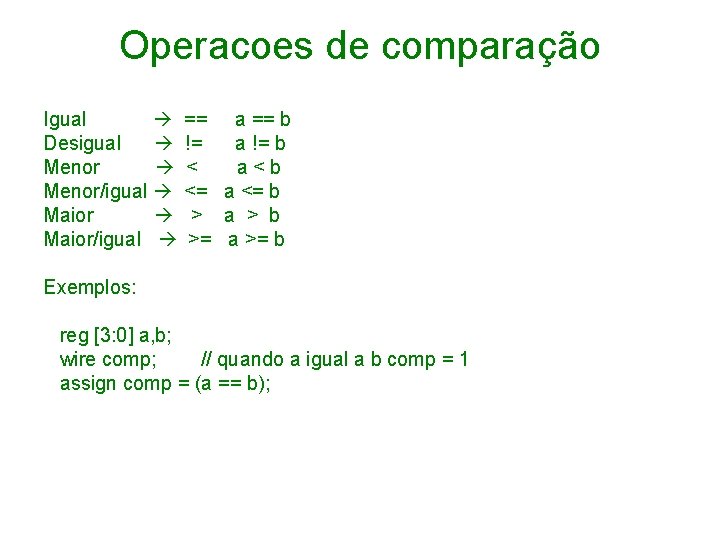

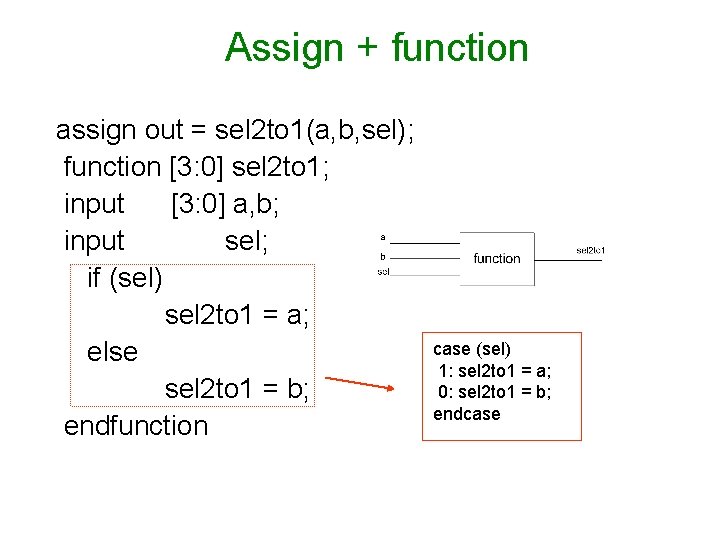

Características Exemplo de programa: module add (a, b, out); // cabeçalho input [7: 0] a, b; // entradas output [7: 0] out; // saidas assign out = a + b; // operação endmodule

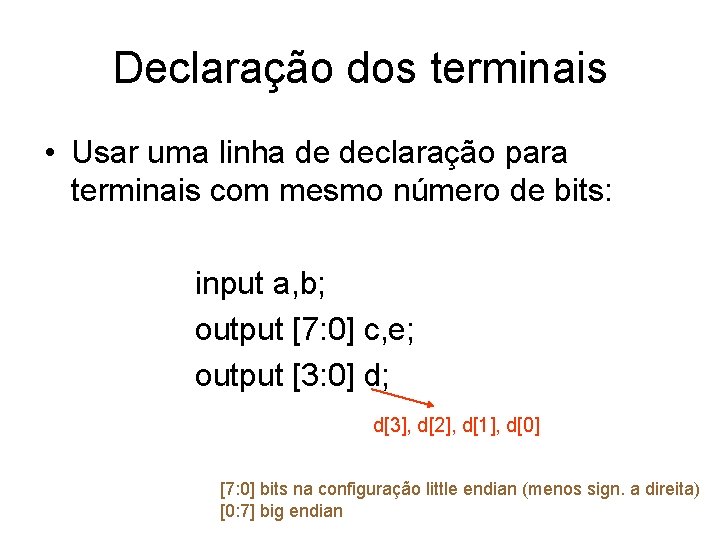

Modulo (conveniente que um arquivo contenha um módulo) module nome_do_modulo ( , , . . , ); lista de terminais declaração { terminais, Terminais são pinos de registradores, wires construção da lógica { assign, function allways endmodule entrada e saída do FPGA registradores e wires são drivers que guardam valores e ligam pontos do circuito, respectiva/.

Declaração dos terminais • Usar uma linha de declaração para terminais com mesmo número de bits: input a, b; output [7: 0] c, e; output [3: 0] d; d[3], d[2], d[1], d[0] [7: 0] bits na configuração little endian (menos sign. a direita) [0: 7] big endian

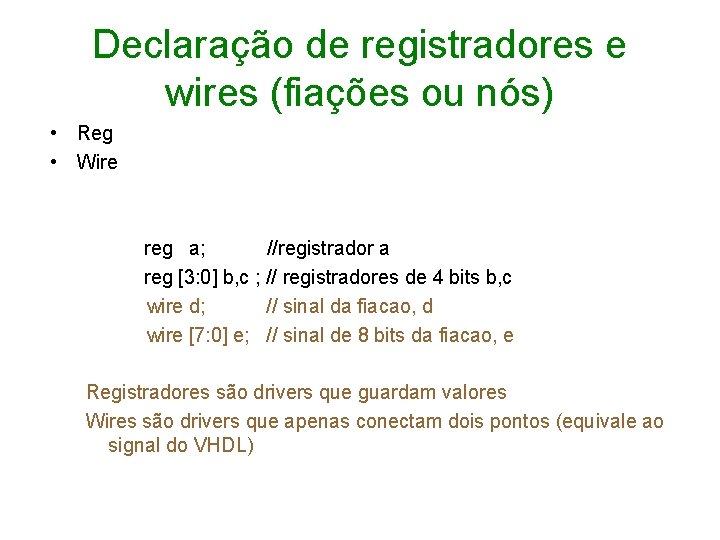

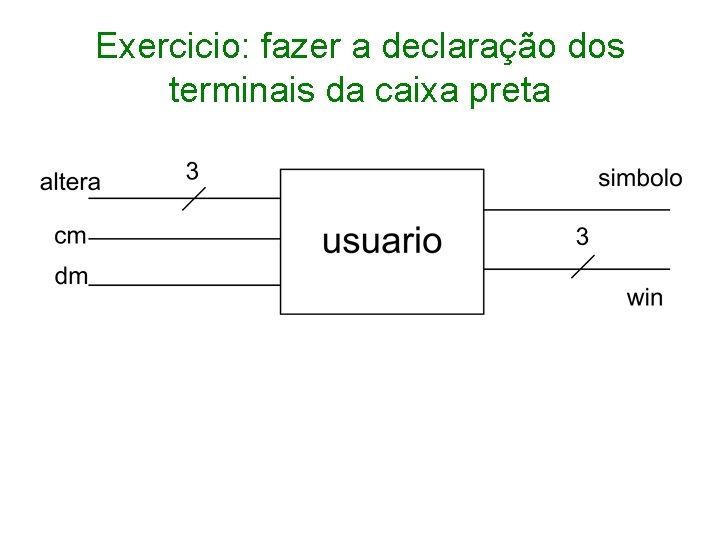

Exercicio: fazer a declaração dos terminais da caixa preta

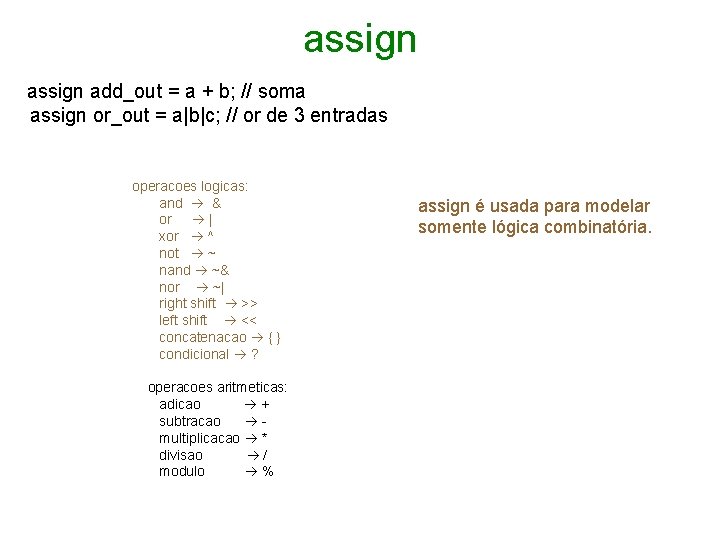

Declaração de registradores e wires (fiações ou nós) • Reg • Wire reg a; //registrador a reg [3: 0] b, c ; // registradores de 4 bits b, c wire d; // sinal da fiacao, d wire [7: 0] e; // sinal de 8 bits da fiacao, e Registradores são drivers que guardam valores Wires são drivers que apenas conectam dois pontos (equivale ao signal do VHDL)

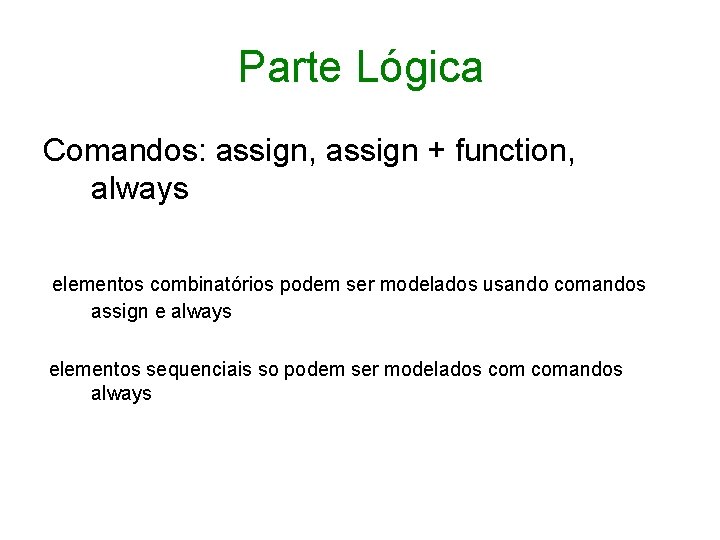

Parte Lógica Comandos: assign, assign + function, always elementos combinatórios podem ser modelados usando comandos assign e always elementos sequenciais so podem ser modelados comandos always

assign add_out = a + b; // soma assign or_out = a|b|c; // or de 3 entradas operacoes logicas: and & or | xor ^ not ~ nand ~& nor ~| right shift >> left shift << concatenacao { } condicional ? operacoes aritmeticas: adicao + subtracao multiplicacao * divisao / modulo % assign é usada para modelar somente lógica combinatória.

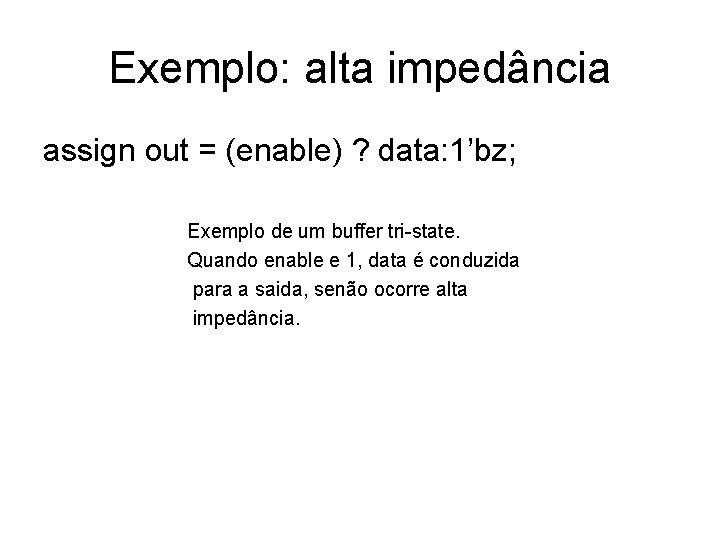

Exemplo: alta impedância assign out = (enable) ? data: 1’bz; Exemplo de um buffer tri-state. Quando enable e 1, data é conduzida para a saida, senão ocorre alta impedância.

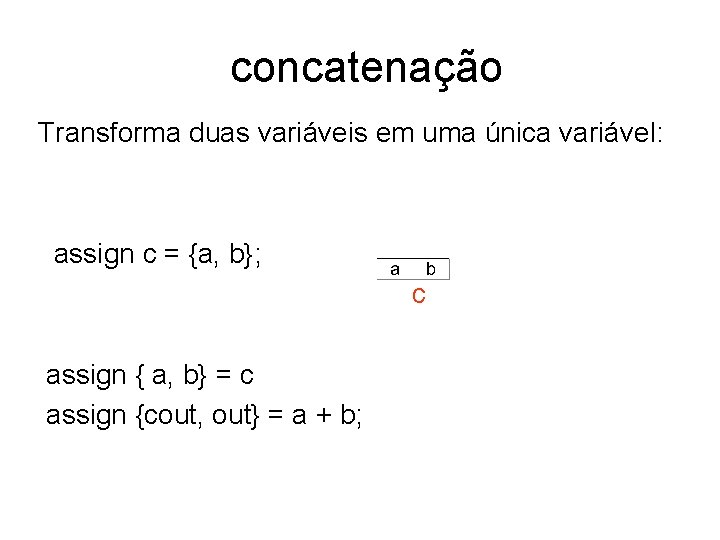

Operacoes de comparação Igual Desigual Menor/igual Maior/igual == a == b != a != b < a<b <= a <= b > a > b >= a >= b Exemplos: reg [3: 0] a, b; wire comp; // quando a igual a b comp = 1 assign comp = (a == b);

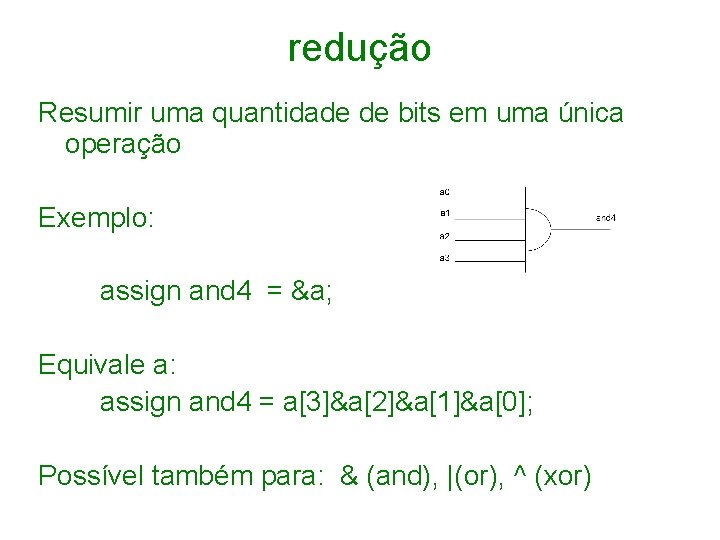

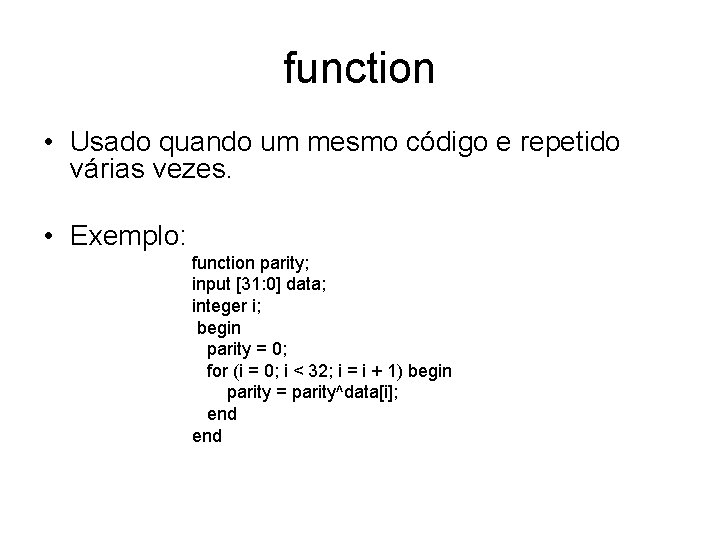

redução Resumir uma quantidade de bits em uma única operação Exemplo: assign and 4 = &a; Equivale a: assign and 4 = a[3]&a[2]&a[1]&a[0]; Possível também para: & (and), |(or), ^ (xor)

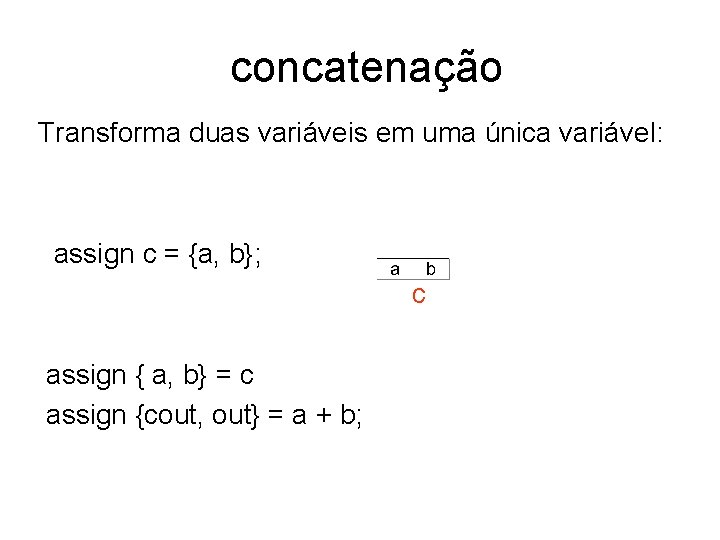

concatenação Transforma duas variáveis em uma única variável: assign c = {a, b}; c assign { a, b} = c assign {cout, out} = a + b;

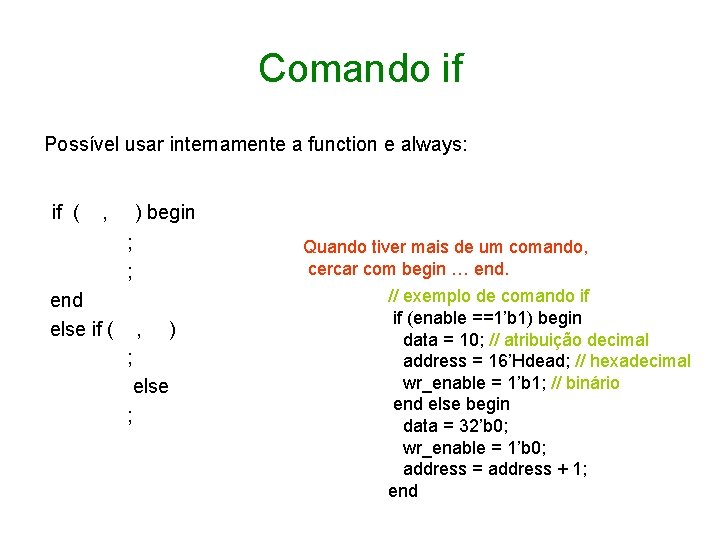

function • Usado quando um mesmo código e repetido várias vezes. • Exemplo: function parity; input [31: 0] data; integer i; begin parity = 0; for (i = 0; i < 32; i = i + 1) begin parity = parity^data[i]; end

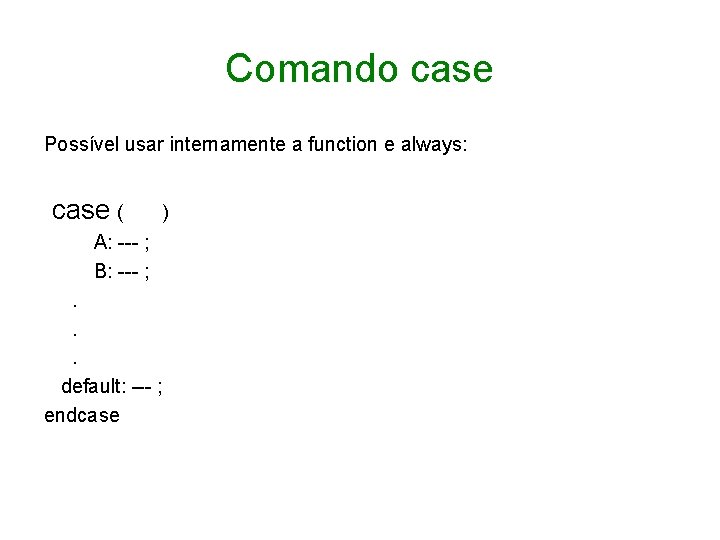

Assign + function assign out = sel 2 to 1(a, b, sel); function [3: 0] sel 2 to 1; input [3: 0] a, b; input sel; if (sel) sel 2 to 1 = a; else sel 2 to 1 = b; endfunction case (sel) 1: sel 2 to 1 = a; 0: sel 2 to 1 = b; endcase

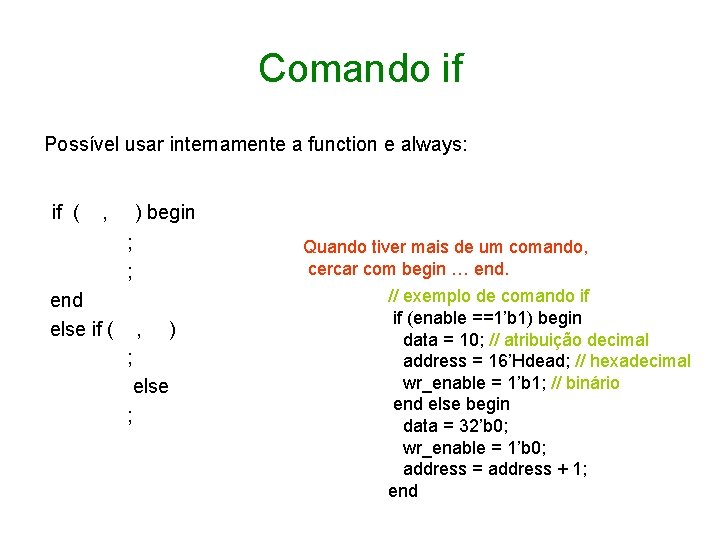

Comando if Possível usar internamente a function e always: if ( , ) begin ; ; end else if ( Quando tiver mais de um comando, cercar com begin … end. , ; else ; ) // exemplo de comando if if (enable ==1’b 1) begin data = 10; // atribuição decimal address = 16’Hdead; // hexadecimal wr_enable = 1’b 1; // binário end else begin data = 32’b 0; wr_enable = 1’b 0; address = address + 1; end

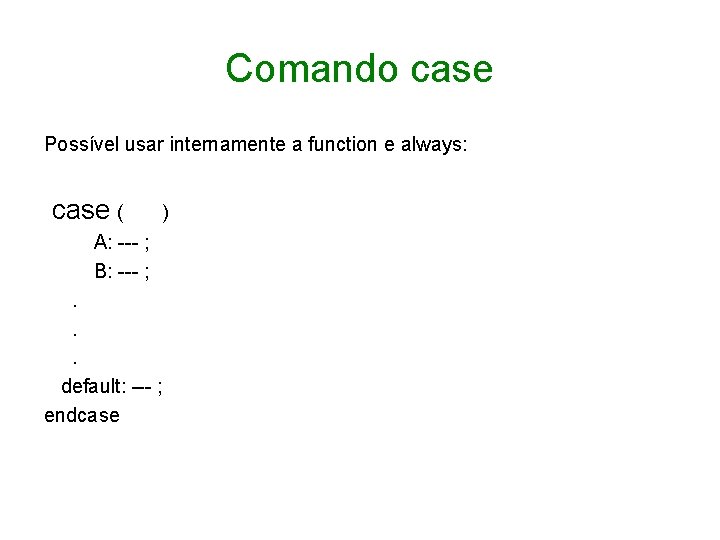

Comando case Possível usar internamente a function e always: case ( ) A: --- ; B: --- ; . . . default: --- ; endcase

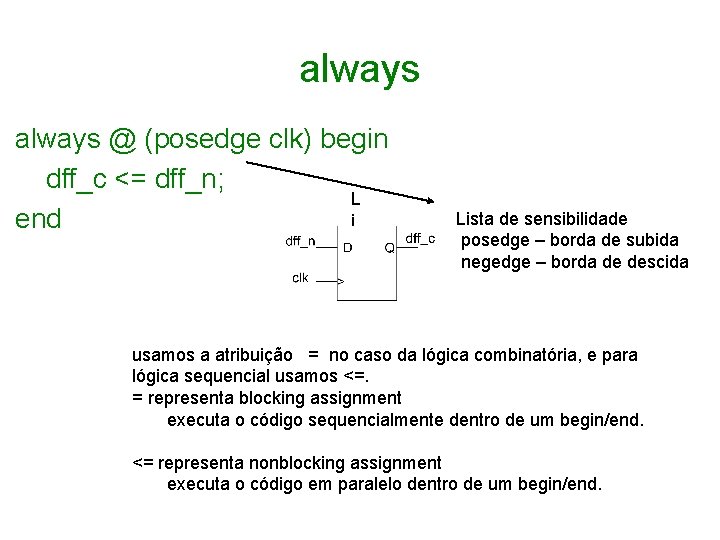

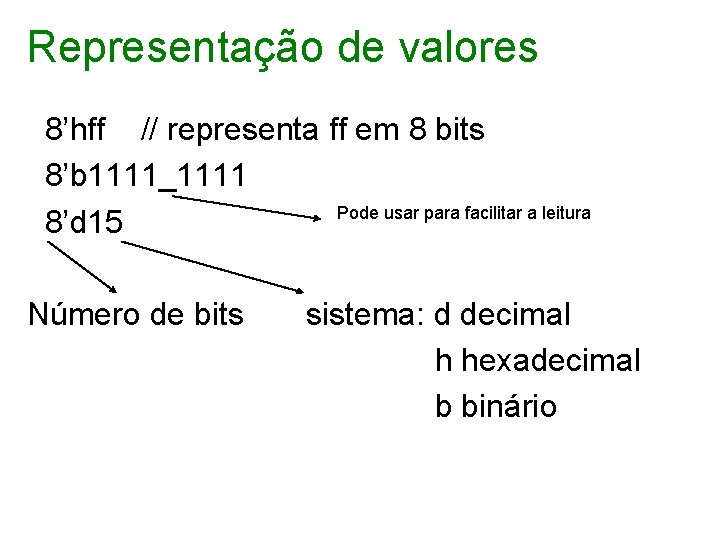

Representação de valores 8’hff // representa ff em 8 bits 8’b 1111_1111 Pode usar para facilitar a leitura 8’d 15 Número de bits sistema: d decimal h hexadecimal b binário

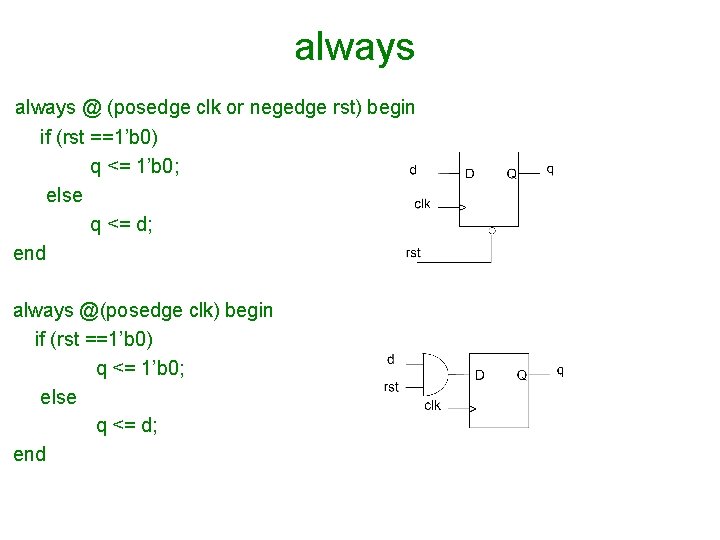

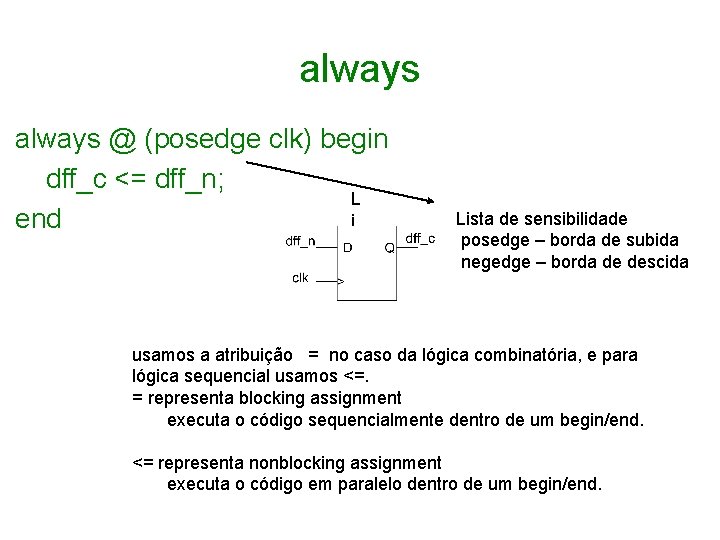

Comando always • O comando always do Verilog é equivalente ao process do VHDL • Todos os comandos always são executados em paralelo, enquanto, internamente a um comando always, os comandos são executados em sequência. always @ (a or b or sel) begin y = 0; if (sel ==0) begin y = a; end else begin y = b; end lista de sensibilidade – diz quando o bloco de código é executado.

always @ (posedge clk) begin dff_c <= dff_n; L i end s t a Lista de sensibilidade posedge – borda de subida negedge – borda de descida usamos a atribuição = no caso da lógica combinatória, e para lógica sequencial usamos <=. = representa blocking assignment executa o código sequencialmente dentro de um begin/end. <= representa nonblocking assignment executa o código em paralelo dentro de um begin/end.

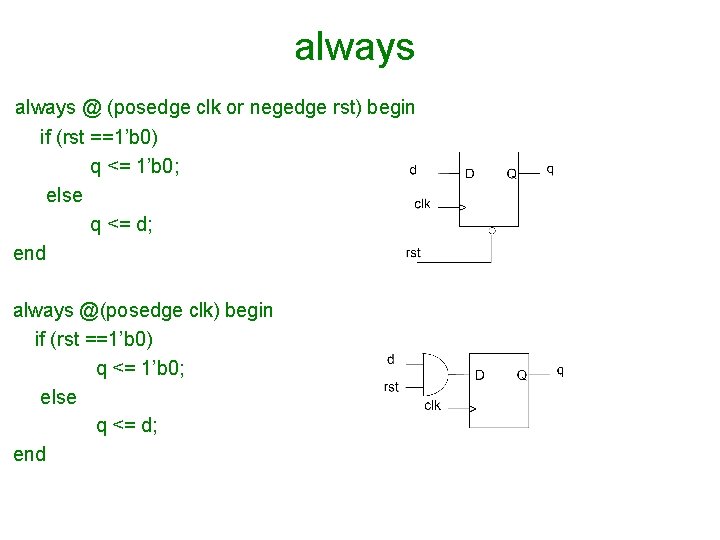

always @ (posedge clk or negedge rst) begin if (rst ==1’b 0) q <= 1’b 0; else q <= d; end always @(posedge clk) begin if (rst ==1’b 0) q <= 1’b 0; else q <= d; end

![Exemplo de contador module count 4clk rst q input clk rst output 3 0 Exemplo de contador module count 4(clk, rst, q); input clk, rst; output [3: 0]](https://slidetodoc.com/presentation_image/1fdf82d64c257f27b9f3057228e0dad2/image-22.jpg)

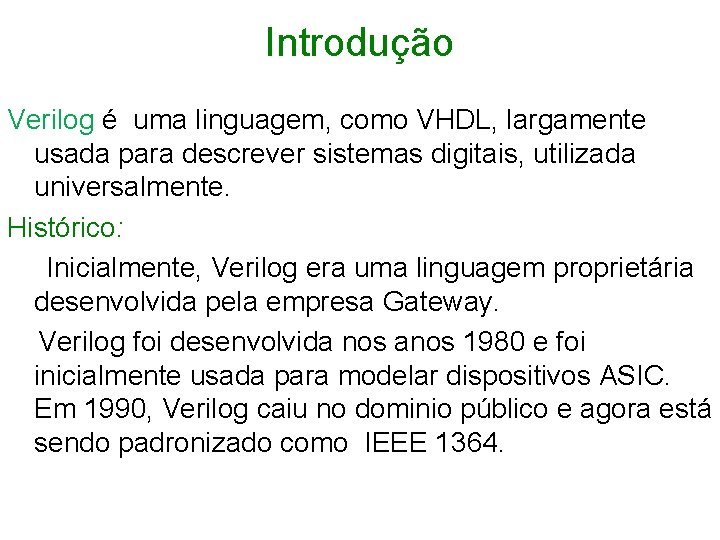

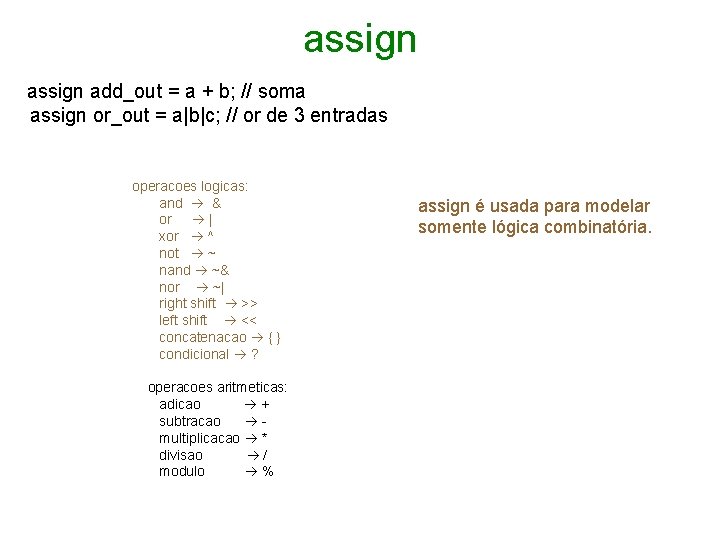

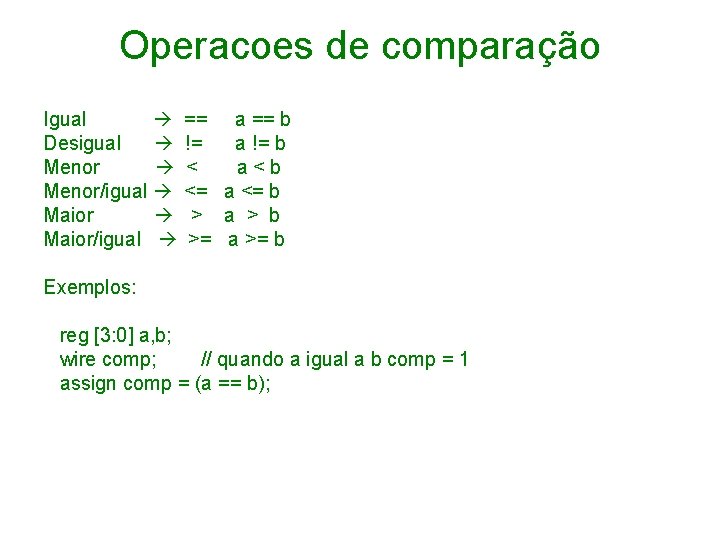

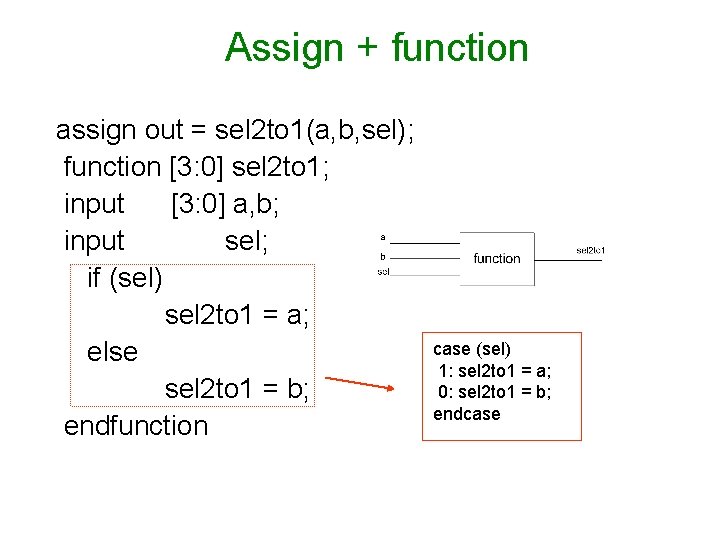

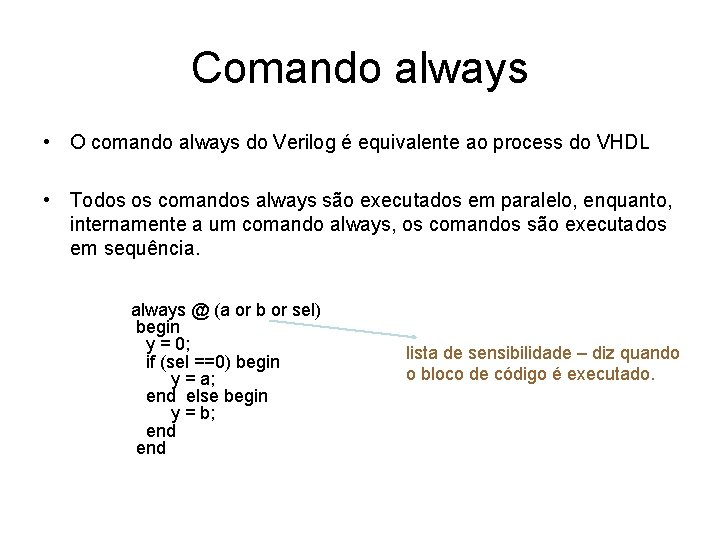

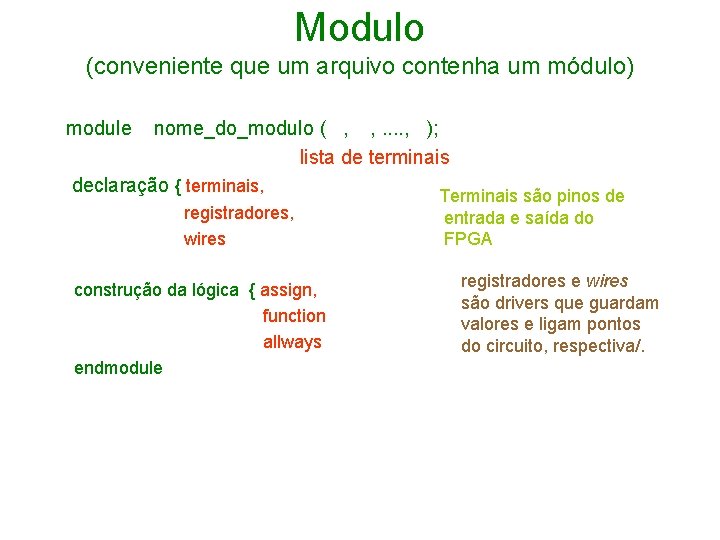

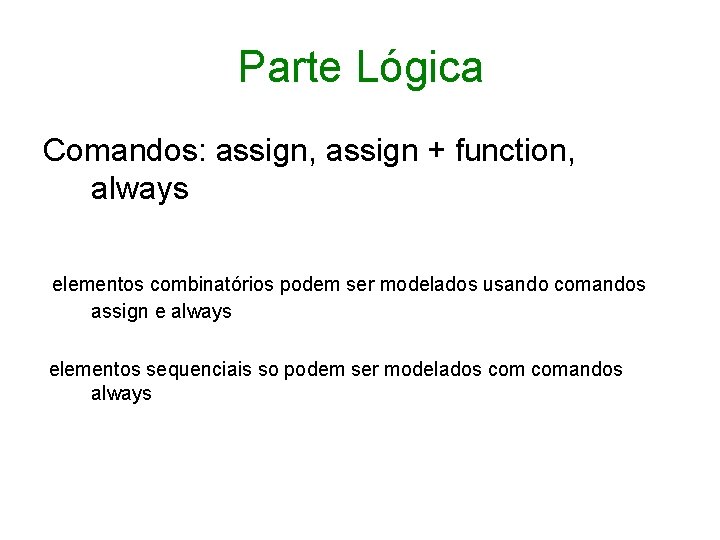

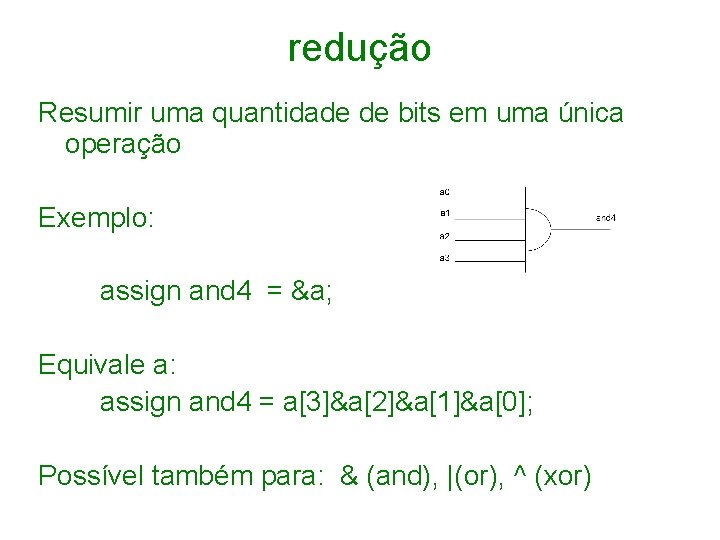

Exemplo de contador module count 4(clk, rst, q); input clk, rst; output [3: 0] q; reg [3: 0] count; always @(posedge clk or negedge rst) begin if (rst == 1’b 0) count <= 4’b 0000; else if (count == 4’b 1110) count <= 4’b 0000; else count <= count + 1; end assign q = count; endmodule

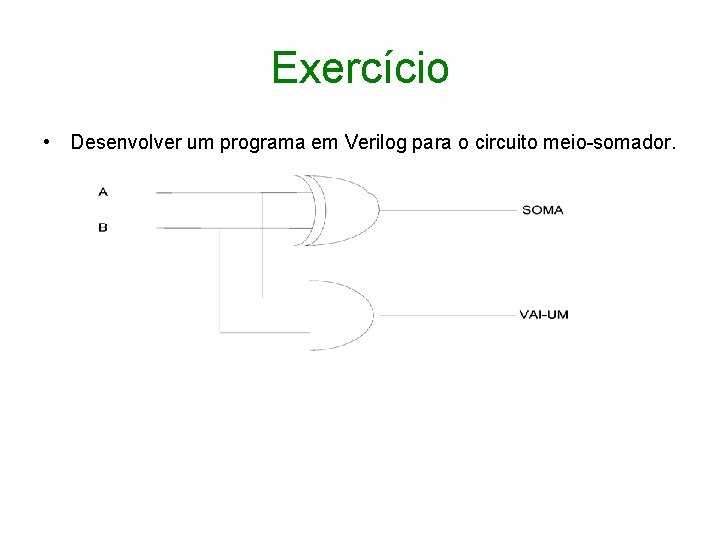

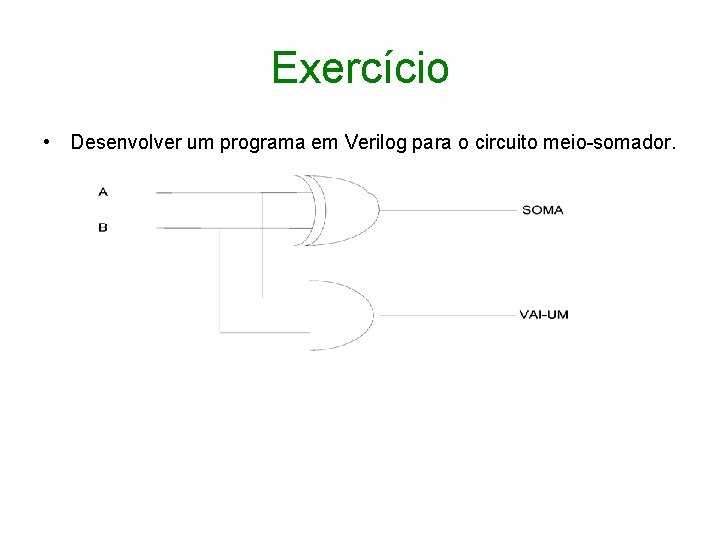

Exercício • Desenvolver um programa em Verilog para o circuito meio-somador.

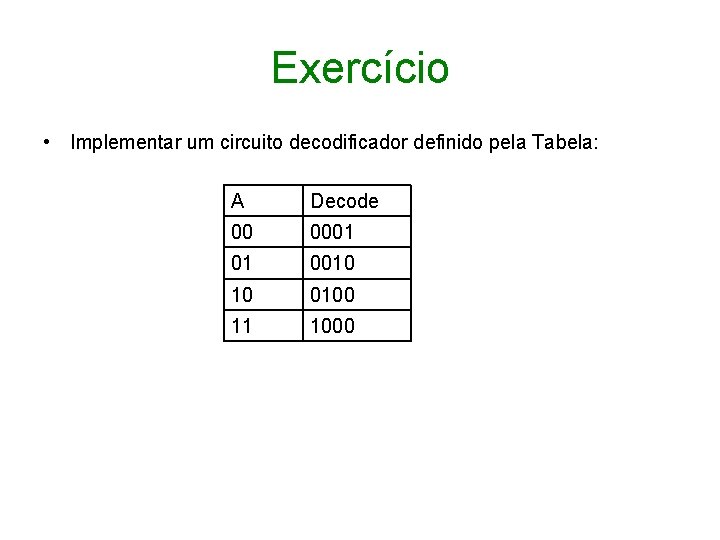

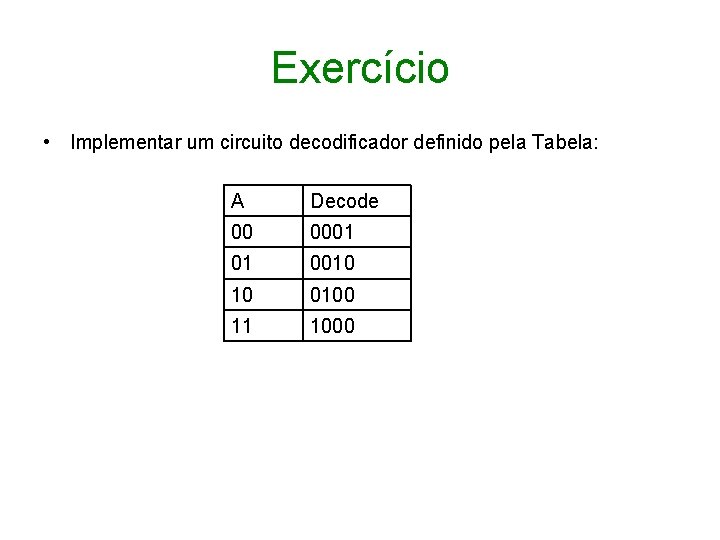

Exercício • Implementar um circuito decodificador definido pela Tabela: A Decode 00 0001 01 0010 10 0100 11 1000

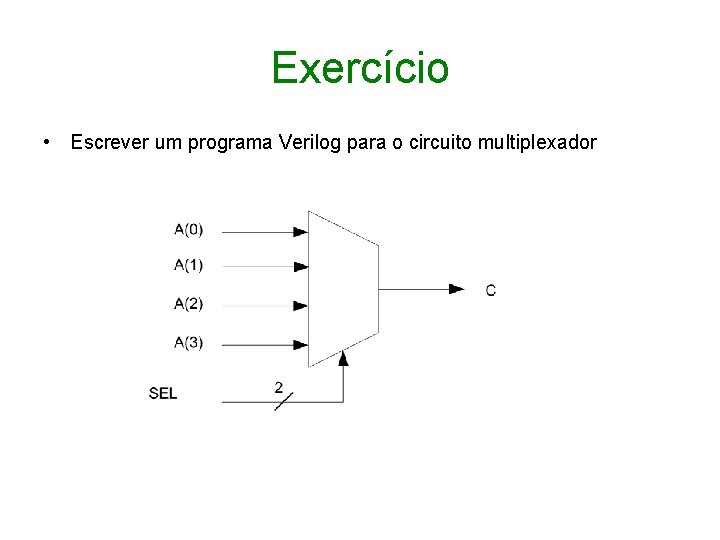

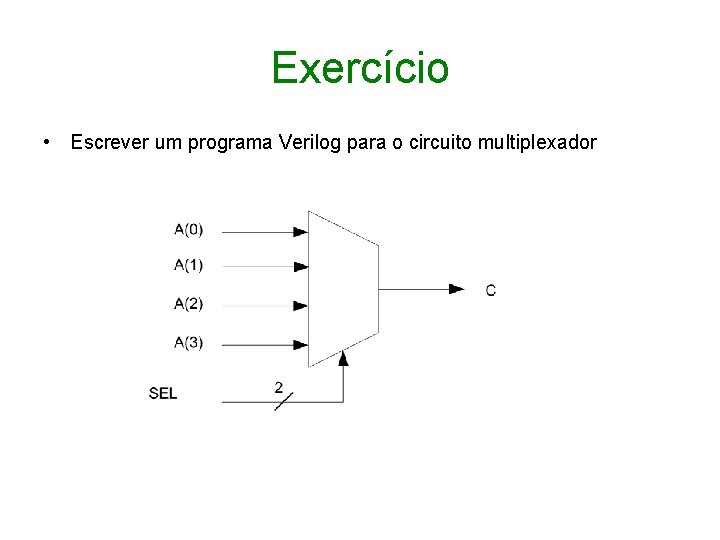

Exercício • Escrever um programa Verilog para o circuito multiplexador

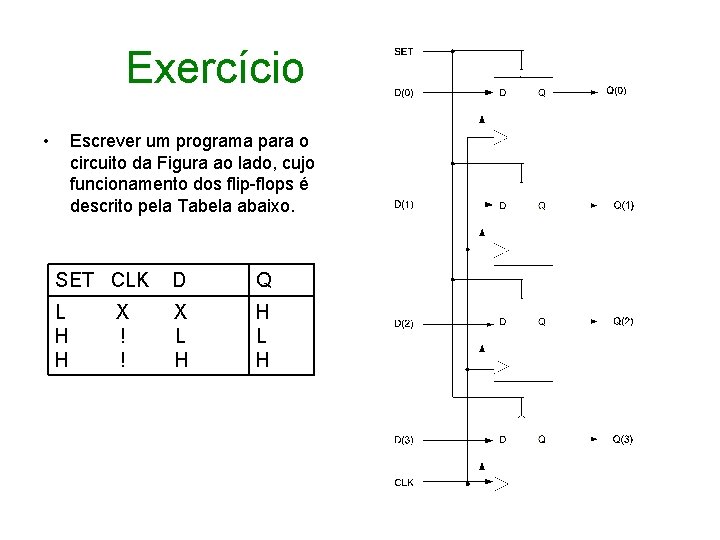

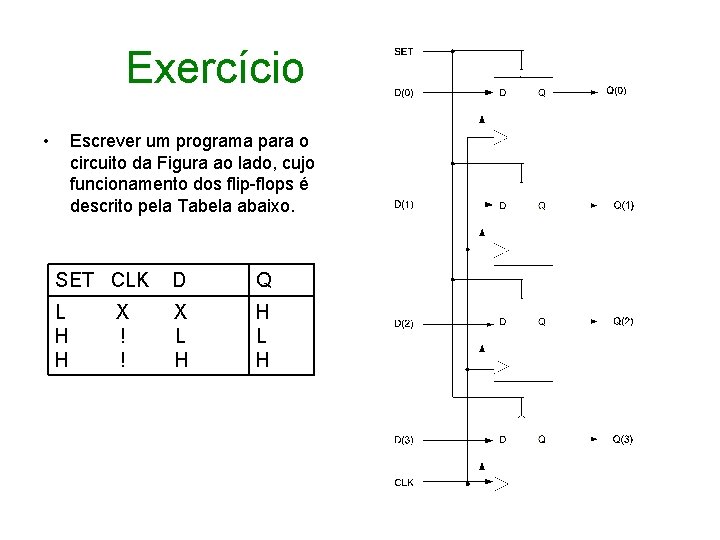

Exercício • Escrever um programa para o circuito da Figura ao lado, cujo funcionamento dos flip-flops é descrito pela Tabela abaixo. SET CLK D Q L H H X L H H L H X ! !

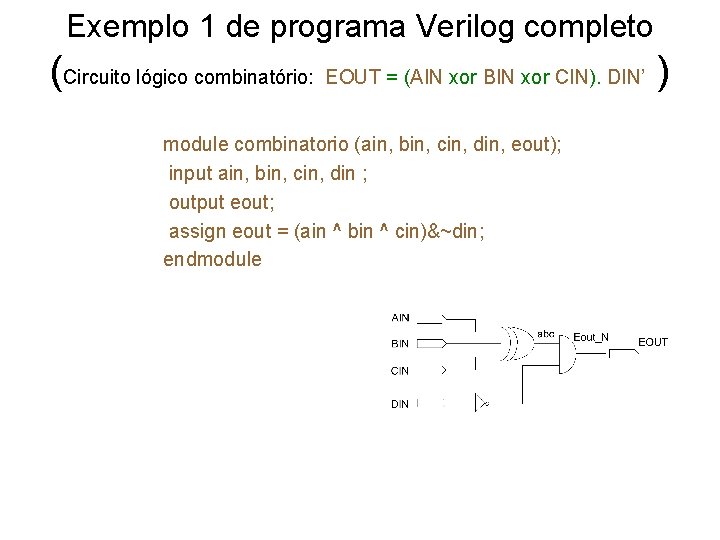

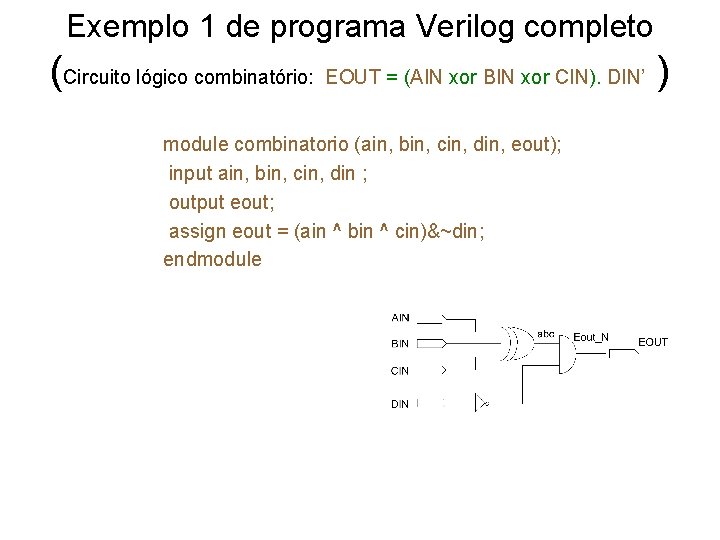

Exemplo 1 de programa Verilog completo (Circuito lógico combinatório: EOUT = (AIN xor BIN xor CIN). DIN’ ) module combinatorio (ain, bin, cin, din, eout); input ain, bin, cin, din ; output eout; assign eout = (ain ^ bin ^ cin)&~din; endmodule

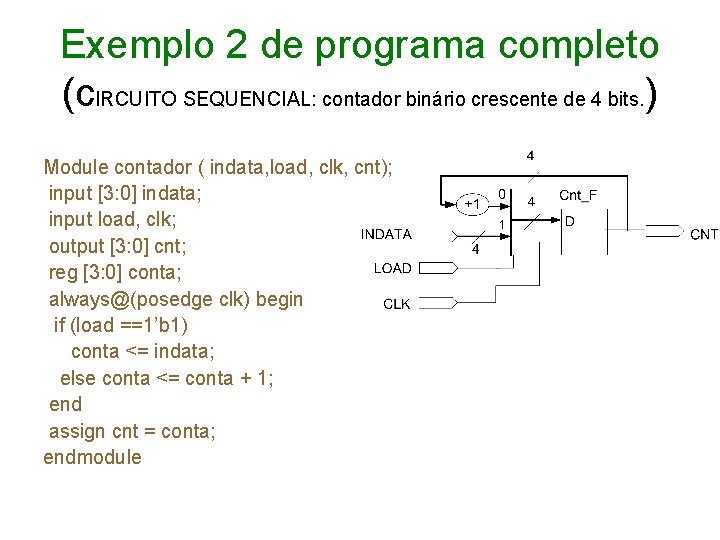

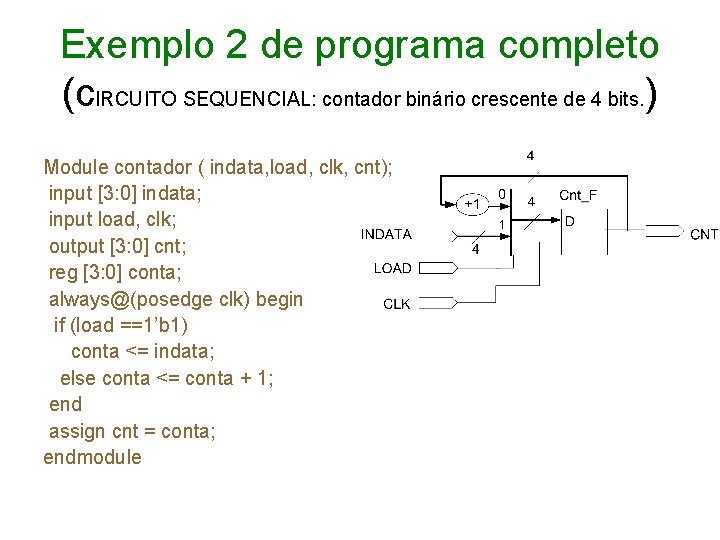

Exemplo 2 de programa completo (c. IRCUITO SEQUENCIAL: contador binário crescente de 4 bits. ) Module contador ( indata, load, clk, cnt); input [3: 0] indata; input load, clk; output [3: 0] cnt; reg [3: 0] conta; always@(posedge clk) begin if (load ==1’b 1) conta <= indata; else conta <= conta + 1; end assign cnt = conta; endmodule

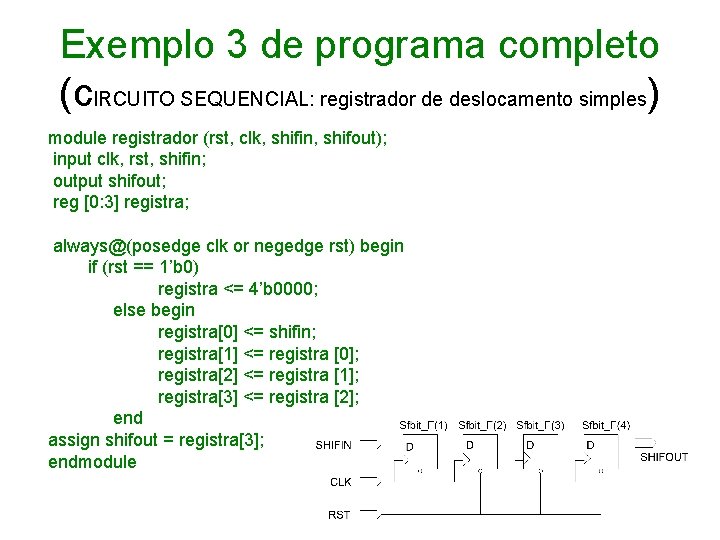

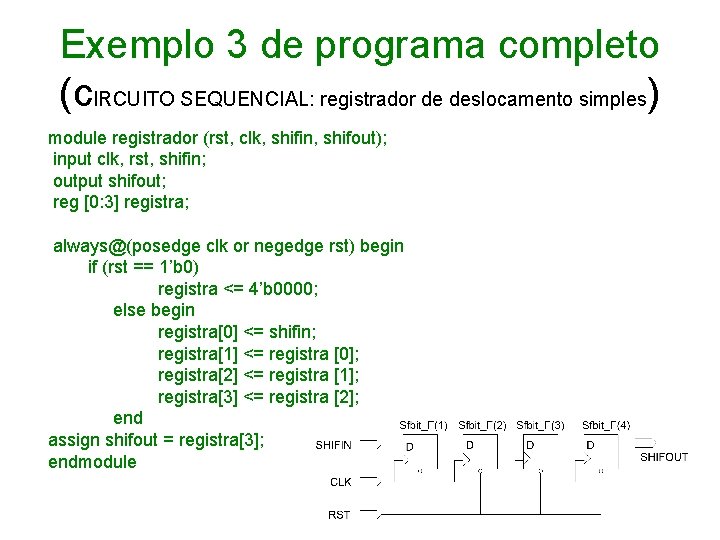

Exemplo 3 de programa completo (c. IRCUITO SEQUENCIAL: registrador de deslocamento simples) module registrador (rst, clk, shifin, shifout); input clk, rst, shifin; output shifout; reg [0: 3] registra; always@(posedge clk or negedge rst) begin if (rst == 1’b 0) registra <= 4’b 0000; else begin registra[0] <= shifin; registra[1] <= registra [0]; registra[2] <= registra [1]; registra[3] <= registra [2]; end assign shifout = registra[3]; endmodule