COE 202 Introduction to Verilog Computer Engineering Department

![Parallel Load Register module Par_load_reg 4 #(parameter word_size=4) ( output reg [word_size-1: 0] Data_out, Parallel Load Register module Par_load_reg 4 #(parameter word_size=4) ( output reg [word_size-1: 0] Data_out,](https://slidetodoc.com/presentation_image_h/28559c925490c7494c77dd76e9352b2d/image-9.jpg)

![Multi. Function Register module MFRegister #(parameter n=3) (output reg [n-1: 0] Q, input [n-1: Multi. Function Register module MFRegister #(parameter n=3) (output reg [n-1: 0] Q, input [n-1:](https://slidetodoc.com/presentation_image_h/28559c925490c7494c77dd76e9352b2d/image-11.jpg)

![Up-Down Counter module Up_Down_Counter 2 ( output reg [2: 0] count, input load, count_up, Up-Down Counter module Up_Down_Counter 2 ( output reg [2: 0] count, input load, count_up,](https://slidetodoc.com/presentation_image_h/28559c925490c7494c77dd76e9352b2d/image-12.jpg)

- Slides: 12

COE 202 Introduction to Verilog Computer Engineering Department College of Computer Sciences and Engineering King Fahd University of Petroleum and Minerals

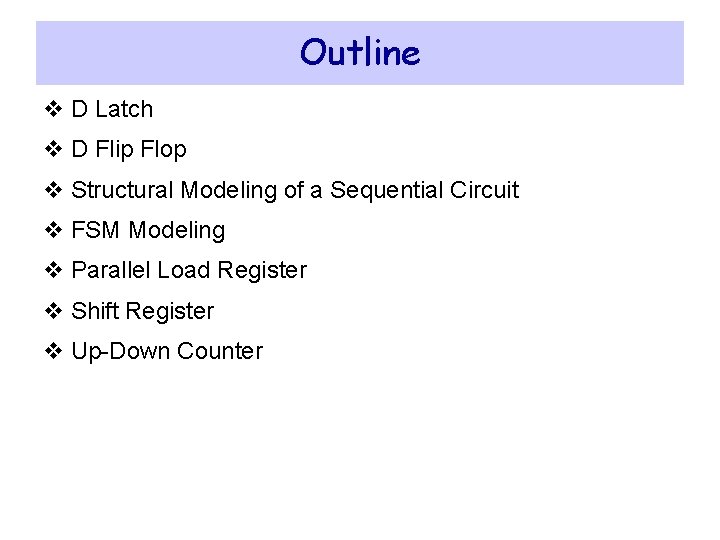

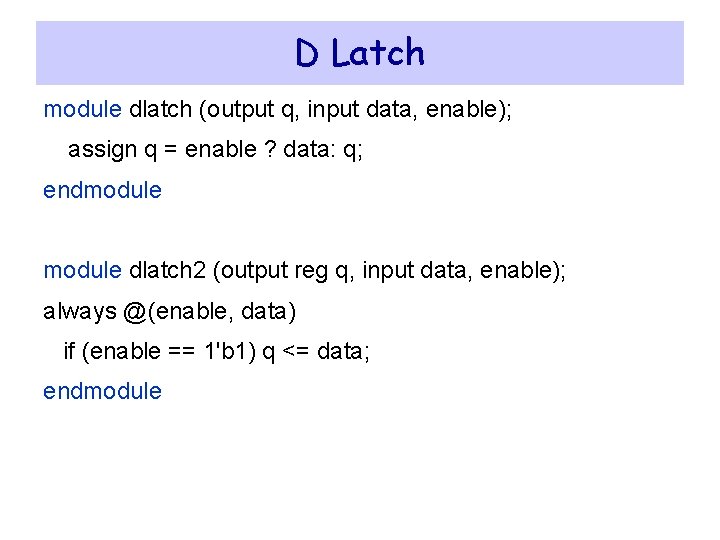

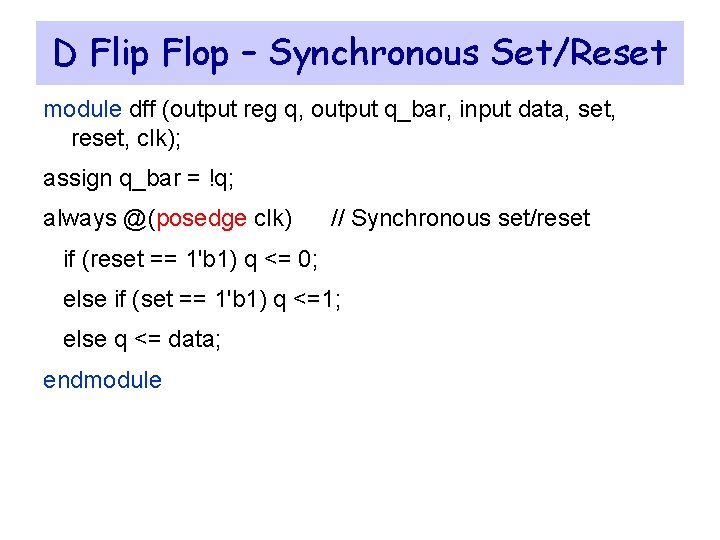

Outline v D Latch v D Flip Flop v Structural Modeling of a Sequential Circuit v FSM Modeling v Parallel Load Register v Shift Register v Up-Down Counter

D Latch module dlatch (output q, input data, enable); assign q = enable ? data: q; endmodule dlatch 2 (output reg q, input data, enable); always @(enable, data) if (enable == 1'b 1) q <= data; endmodule

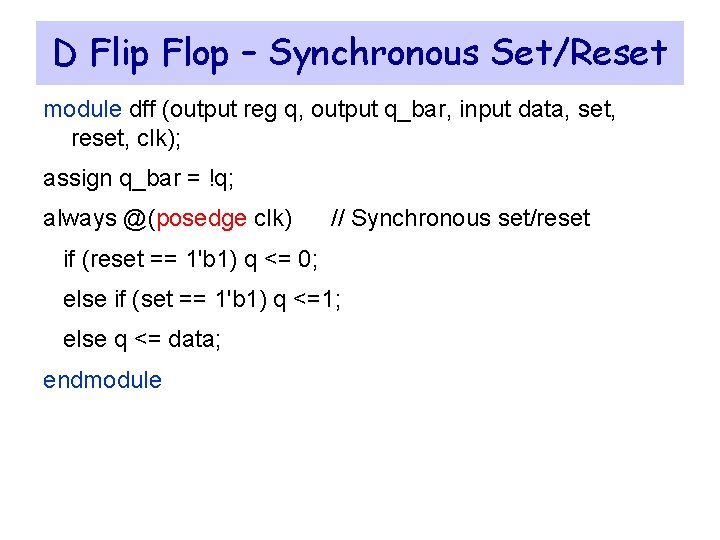

D Flip Flop – Synchronous Set/Reset module dff (output reg q, output q_bar, input data, set, reset, clk); assign q_bar = !q; always @(posedge clk) // Synchronous set/reset if (reset == 1'b 1) q <= 0; else if (set == 1'b 1) q <=1; else q <= data; endmodule

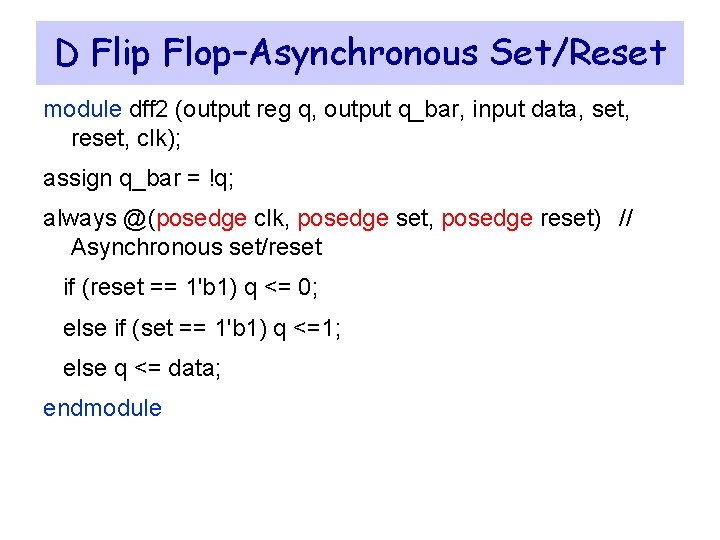

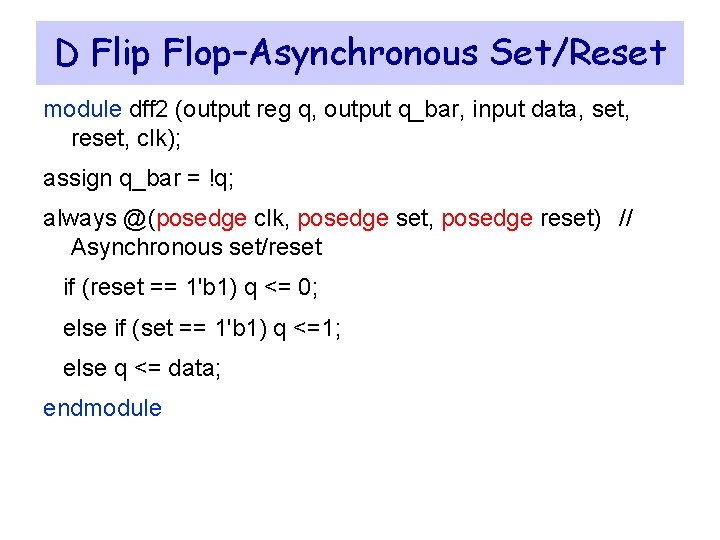

D Flip Flop–Asynchronous Set/Reset module dff 2 (output reg q, output q_bar, input data, set, reset, clk); assign q_bar = !q; always @(posedge clk, posedge set, posedge reset) // Asynchronous set/reset if (reset == 1'b 1) q <= 0; else if (set == 1'b 1) q <=1; else q <= data; endmodule

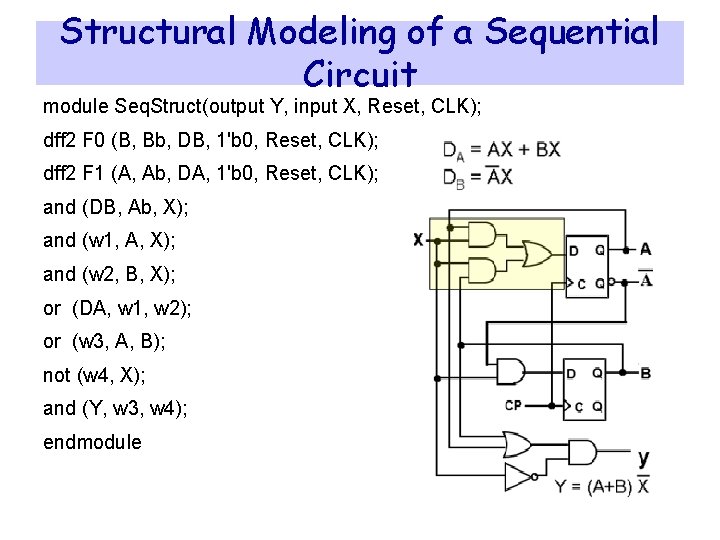

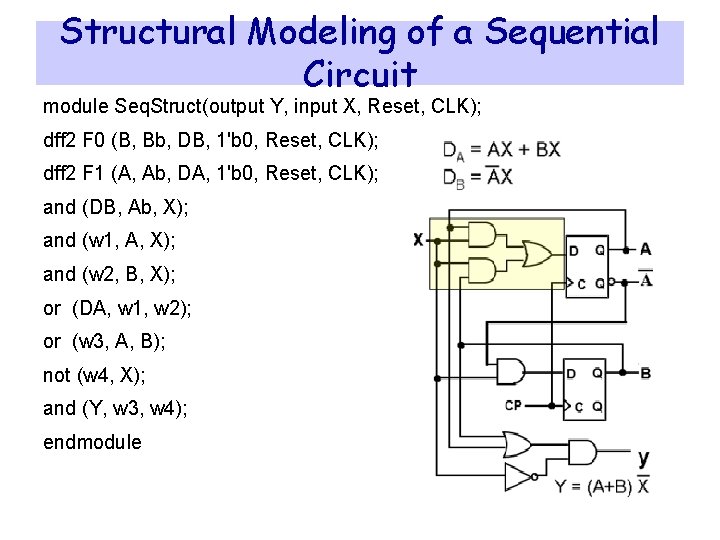

Structural Modeling of a Sequential Circuit module Seq. Struct(output Y, input X, Reset, CLK); dff 2 F 0 (B, Bb, DB, 1'b 0, Reset, CLK); dff 2 F 1 (A, Ab, DA, 1'b 0, Reset, CLK); and (DB, Ab, X); and (w 1, A, X); and (w 2, B, X); or (DA, w 1, w 2); or (w 3, A, B); not (w 4, X); and (Y, w 3, w 4); endmodule

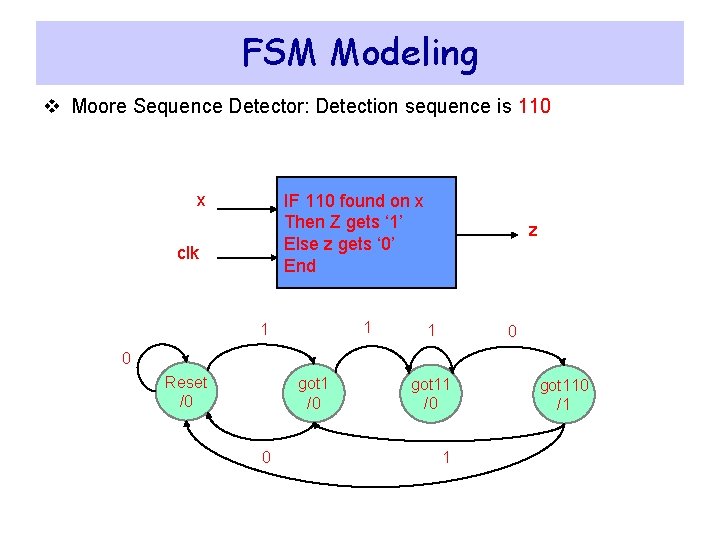

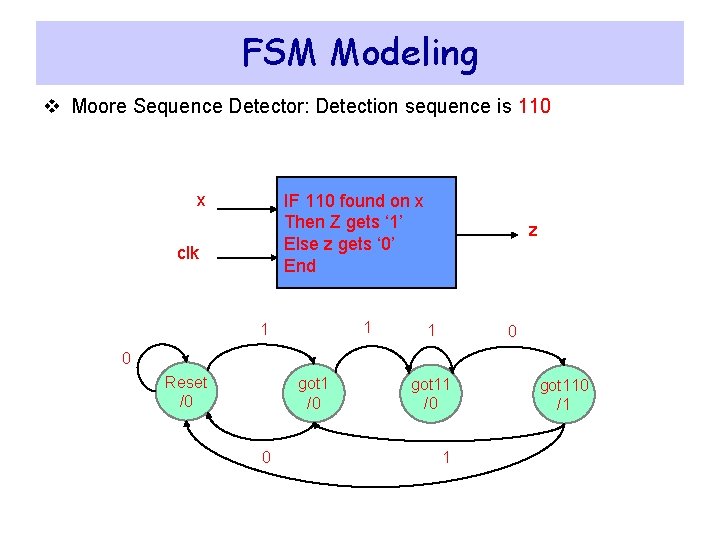

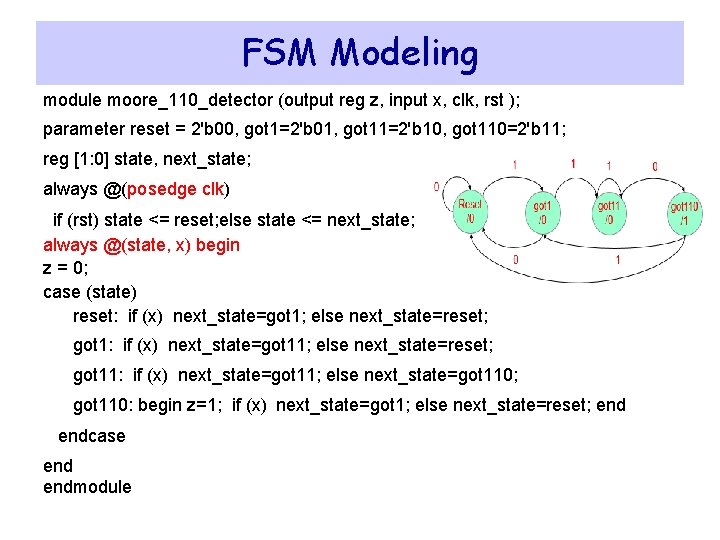

FSM Modeling v Moore Sequence Detector: Detection sequence is 110 x IF 110 found on x Then Z gets ‘ 1’ Else z gets ‘ 0’ End clk 1 1 z 1 0 0 Reset /0 got 1 /0 0 got 11 /0 1 got 110 /1

FSM Modeling module moore_110_detector (output reg z, input x, clk, rst ); parameter reset = 2'b 00, got 1=2'b 01, got 11=2'b 10, got 110=2'b 11; reg [1: 0] state, next_state; always @(posedge clk) if (rst) state <= reset; else state <= next_state; always @(state, x) begin z = 0; case (state) reset: if (x) next_state=got 1; else next_state=reset; got 1: if (x) next_state=got 11; else next_state=reset; got 11: if (x) next_state=got 11; else next_state=got 110; got 110: begin z=1; if (x) next_state=got 1; else next_state=reset; endcase endmodule

![Parallel Load Register module Parloadreg 4 parameter wordsize4 output reg wordsize1 0 Dataout Parallel Load Register module Par_load_reg 4 #(parameter word_size=4) ( output reg [word_size-1: 0] Data_out,](https://slidetodoc.com/presentation_image_h/28559c925490c7494c77dd76e9352b2d/image-9.jpg)

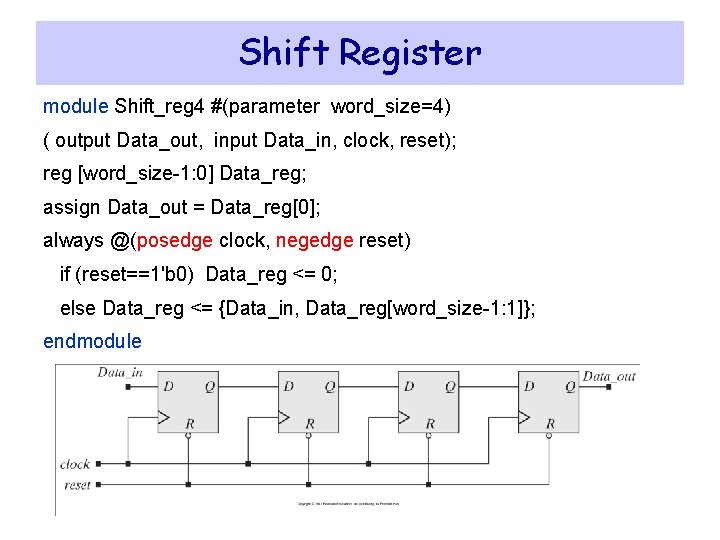

Parallel Load Register module Par_load_reg 4 #(parameter word_size=4) ( output reg [word_size-1: 0] Data_out, input [word_size-1: 0] Data_in, input load, clock, reset); always @(posedge clock, posedge reset) if (reset==1'b 1) Data_out <= 0; else if (load==1'b 1) Data_out <= Data_in; endmodule

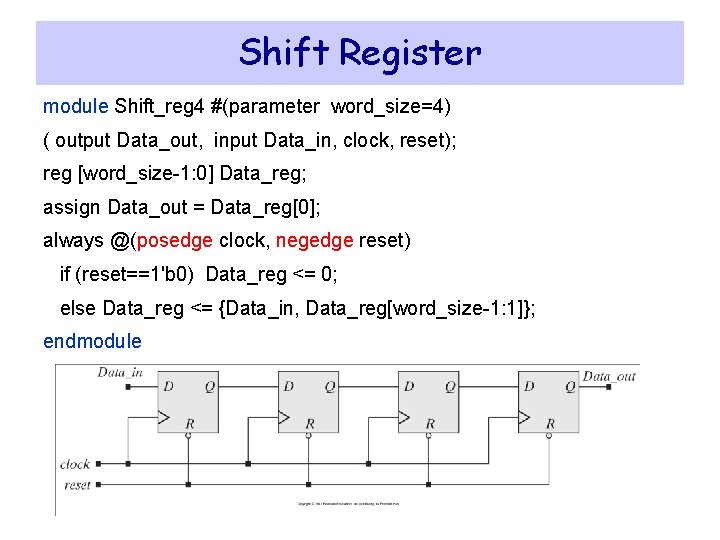

Shift Register module Shift_reg 4 #(parameter word_size=4) ( output Data_out, input Data_in, clock, reset); reg [word_size-1: 0] Data_reg; assign Data_out = Data_reg[0]; always @(posedge clock, negedge reset) if (reset==1'b 0) Data_reg <= 0; else Data_reg <= {Data_in, Data_reg[word_size-1: 1]}; endmodule

![Multi Function Register module MFRegister parameter n3 output reg n1 0 Q input n1 Multi. Function Register module MFRegister #(parameter n=3) (output reg [n-1: 0] Q, input [n-1:](https://slidetodoc.com/presentation_image_h/28559c925490c7494c77dd76e9352b2d/image-11.jpg)

Multi. Function Register module MFRegister #(parameter n=3) (output reg [n-1: 0] Q, input [n-1: 0] I, input s 1, s 0, clk, reset, SI); always @(posedge clk) begin if (reset==1'b 1) Q <= 0; // synchronous reset else case ({s 1, s 0}) 2'b 00: Q <=Q; // no change 2'b 01: Q <= I; // parallel load 2'b 10: Q <= {Q[n-2: 0], SI}; // shift left 2'b 11: Q <= {SI, Q[n-1: 1]}; //shift right endcase endmodule

![UpDown Counter module UpDownCounter 2 output reg 2 0 count input load countup Up-Down Counter module Up_Down_Counter 2 ( output reg [2: 0] count, input load, count_up,](https://slidetodoc.com/presentation_image_h/28559c925490c7494c77dd76e9352b2d/image-12.jpg)

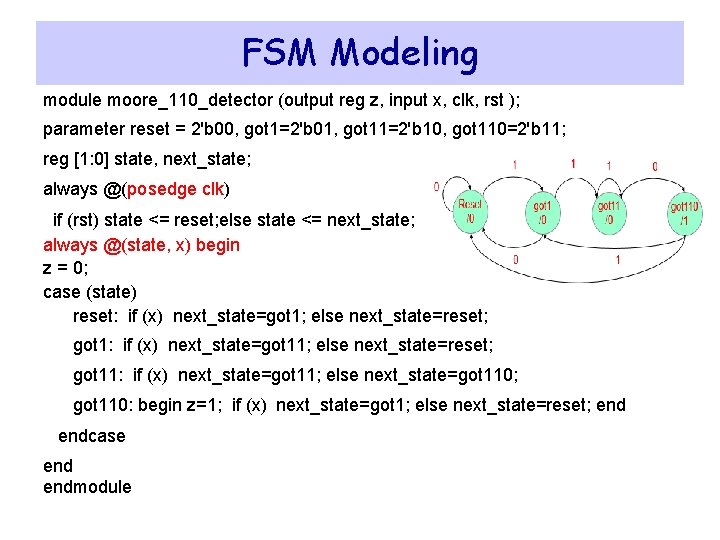

Up-Down Counter module Up_Down_Counter 2 ( output reg [2: 0] count, input load, count_up, counter_on, clock, reset, input [2: 0] Data_in); always @(posedge clock, posedge reset) if (reset==1'b 1) count <= 3'b 0; else if (load == 1'b 1) count <= Data_in; else if (counter_on == 1'b 1) if (count_up == 1'b 1) count<=count+1; else count<=count-1; endmodule