Ch 7 Memory and Programmable Logic Memory and

Ch. 7 Memory and Programmable Logic

Memory and Programmable Logic ¬Random-Access Memory ¬Memory Decoding ¬Error Detection and Correction ¬Read-Only Memory ¬Programmable Logic Array ¬Programmable Array Logic ¬Sequential Programmable Devices

Memory ¬ Memory – A device to which binary information is transferred for storage. ¬ Type of memory – random access memory , RAM – read-only memory, ROM ¬ Write operation – Storing new information into memory ¬ Read operation – Transferring the stored information out of memory

RAM ¬ RAM – The time it takes to transfer information to or from any desired random location is always the same ¬ Storage unit–byte – byte: 8 bits – Length of a word:multiple of 8 bits – word:represent a number, an instruction, alphanumeric character ¬ Capacity of memory–total number of bytes

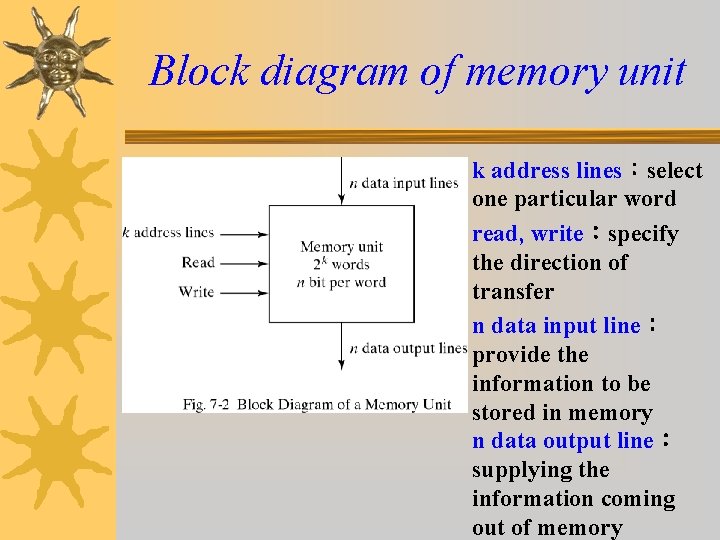

Block diagram of memory unit k address lines:select one particular word read, write:specify the direction of transfer n data input line: provide the information to be stored in memory n data output line: supplying the information coming out of memory

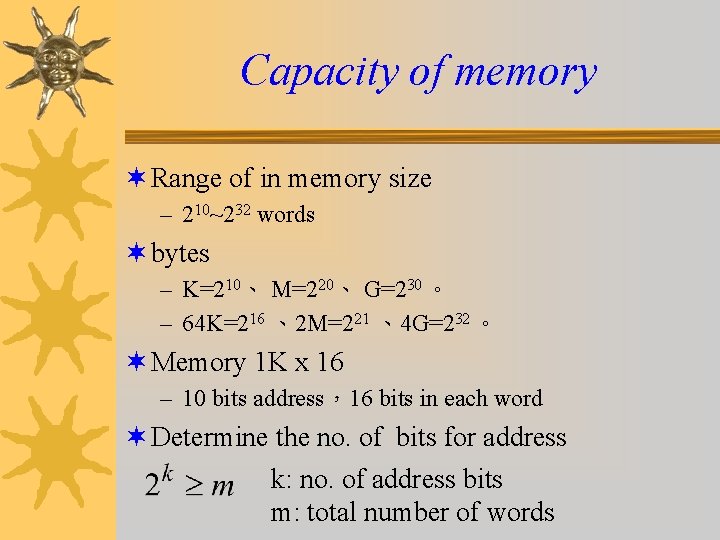

Capacity of memory ¬ Range of in memory size – 210~232 words ¬ bytes – K=210、 M=220、 G=230 。 – 64 K=216 、2 M=221 、4 G=232 。 ¬ Memory 1 K x 16 – 10 bits address,16 bits in each word ¬ Determine the no. of bits for address k: no. of address bits m: total number of words

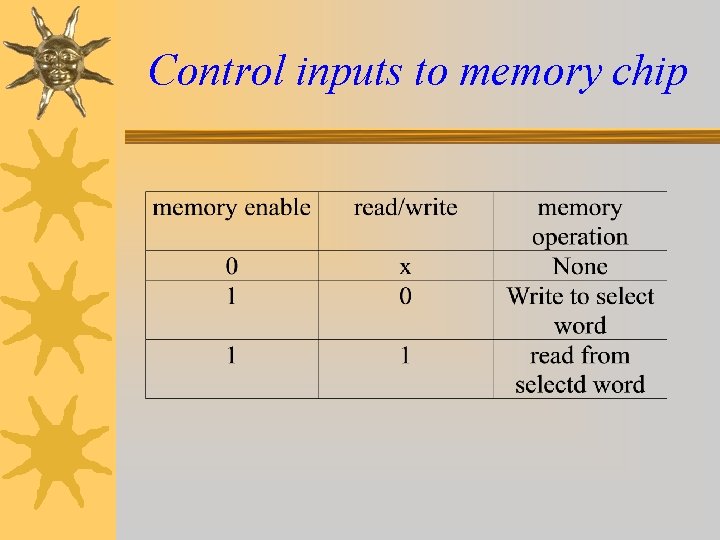

Control inputs to memory chip

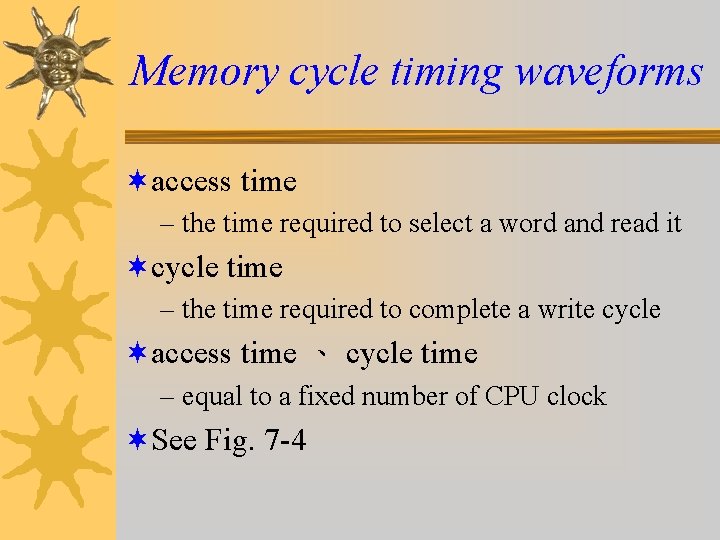

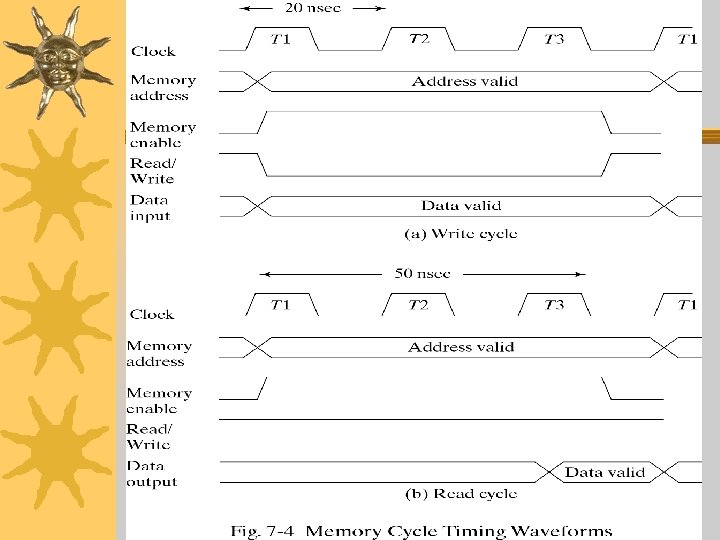

Memory cycle timing waveforms ¬access time – the time required to select a word and read it ¬cycle time – the time required to complete a write cycle ¬access time 、 cycle time – equal to a fixed number of CPU clock ¬See Fig. 7 -4

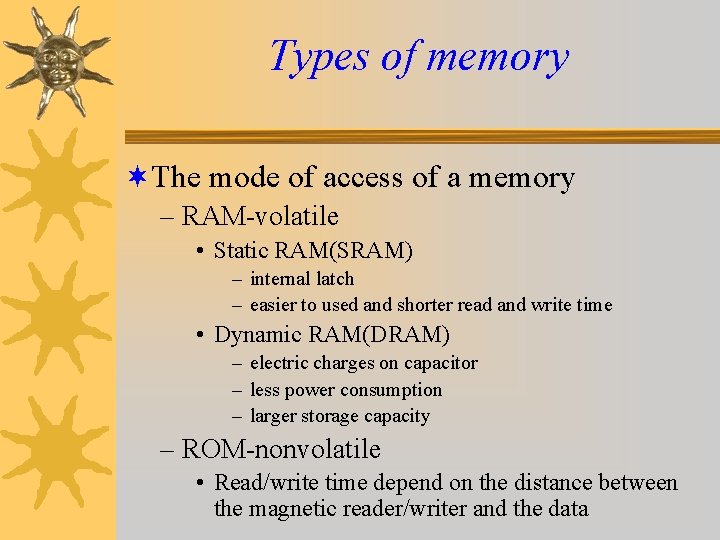

Types of memory ¬The mode of access of a memory – RAM-volatile • Static RAM(SRAM) – internal latch – easier to used and shorter read and write time • Dynamic RAM(DRAM) – electric charges on capacitor – less power consumption – larger storage capacity – ROM-nonvolatile • Read/write time depend on the distance between the magnetic reader/writer and the data

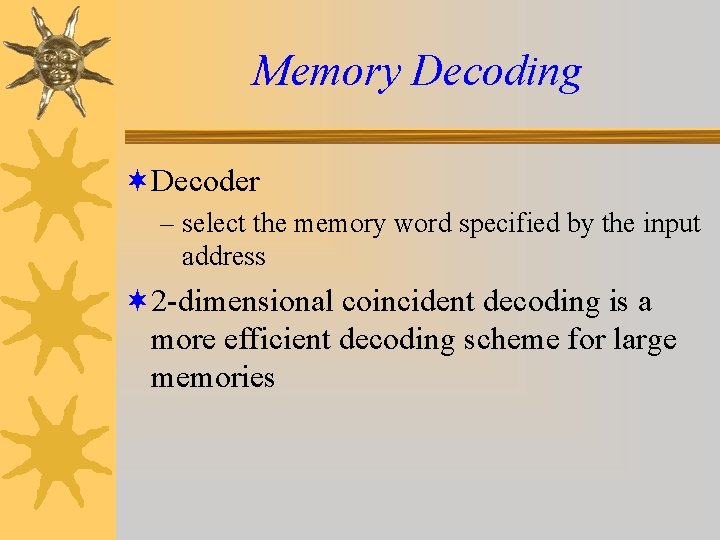

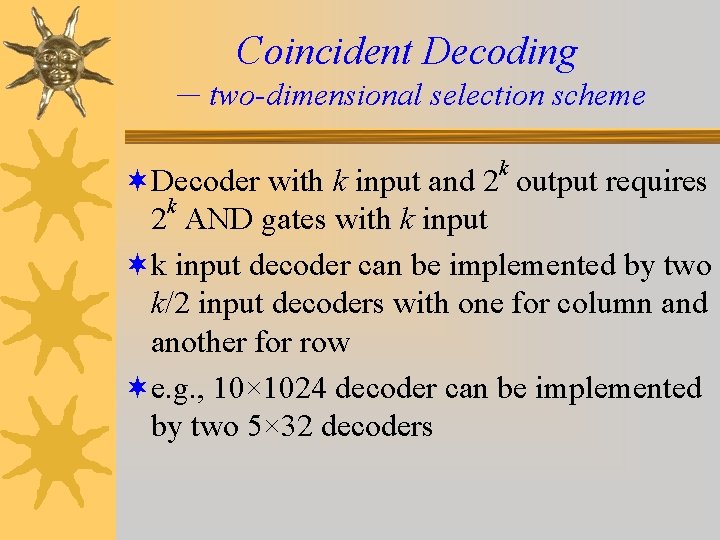

Memory Decoding ¬Decoder – select the memory word specified by the input address ¬ 2 -dimensional coincident decoding is a more efficient decoding scheme for large memories

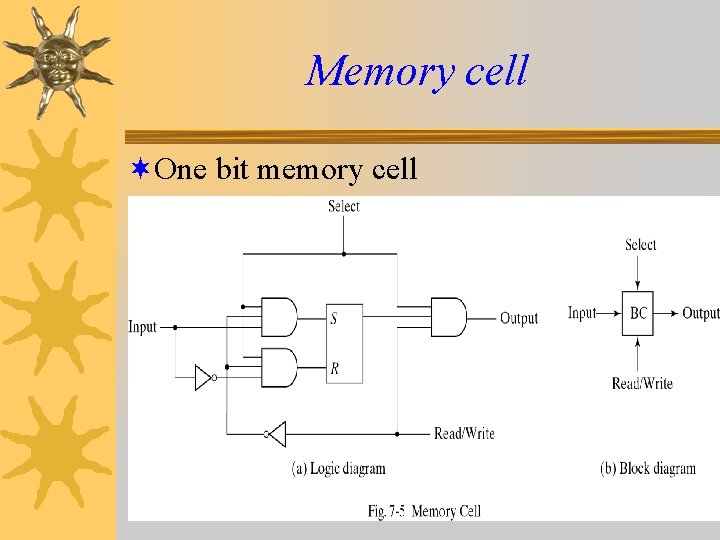

Memory cell ¬One bit memory cell

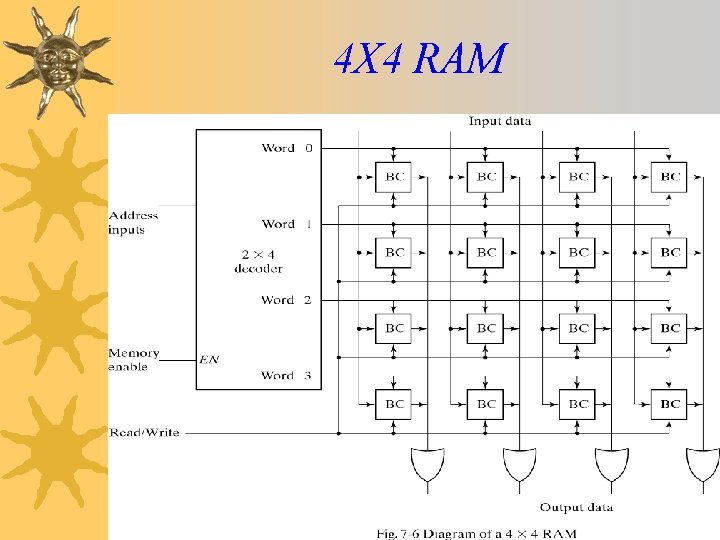

4 X 4 RAM

Coincident Decoding - two-dimensional selection scheme k ¬Decoder with k input and 2 output requires k 2 AND gates with k input ¬k input decoder can be implemented by two k/2 input decoders with one for column and another for row ¬e. g. , 10× 1024 decoder can be implemented by two 5× 32 decoders

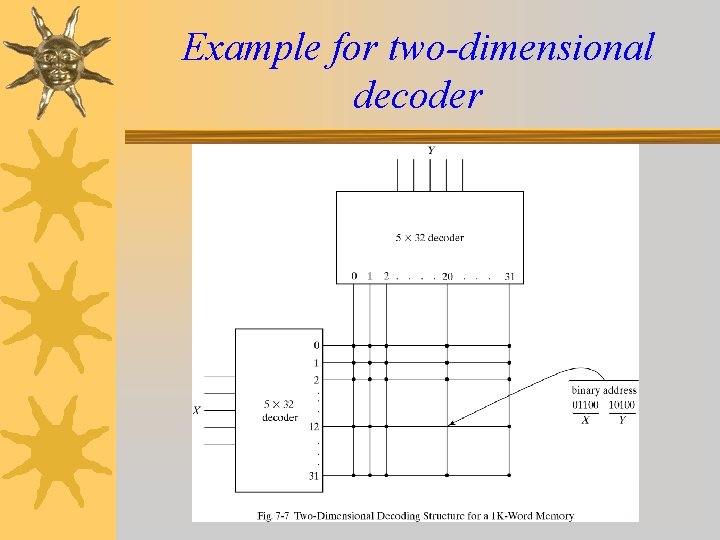

Example for two-dimensional decoder

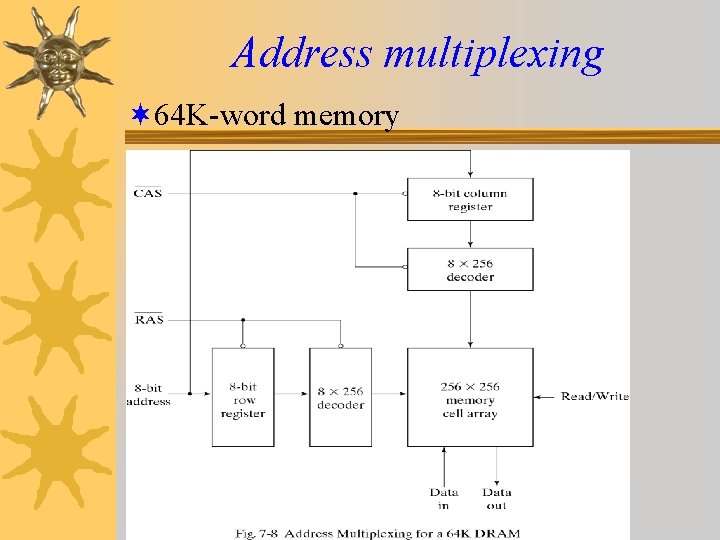

Address multiplexing ¬ 64 K-word memory

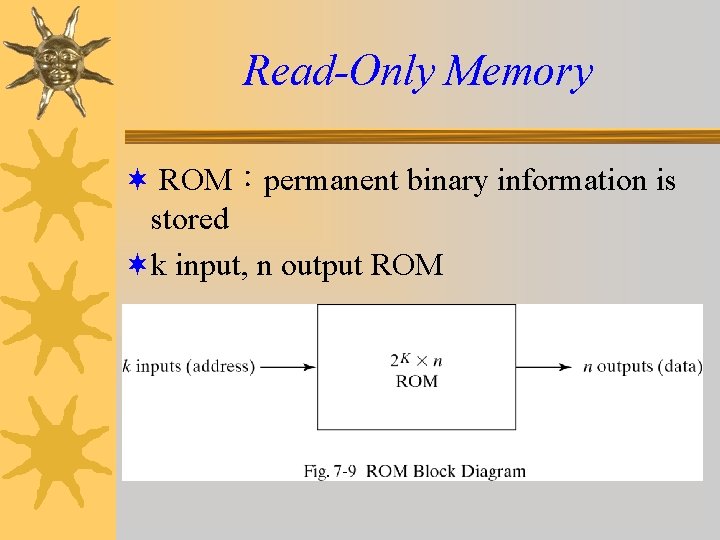

Read-Only Memory ¬ ROM:permanent binary information is stored ¬k input, n output ROM

ROM ¬No data input ¬Integrated circuit ROM have one or more enable input ¬Sometimes come with three-state outputs to facilitate the construction of large arrays of ROM

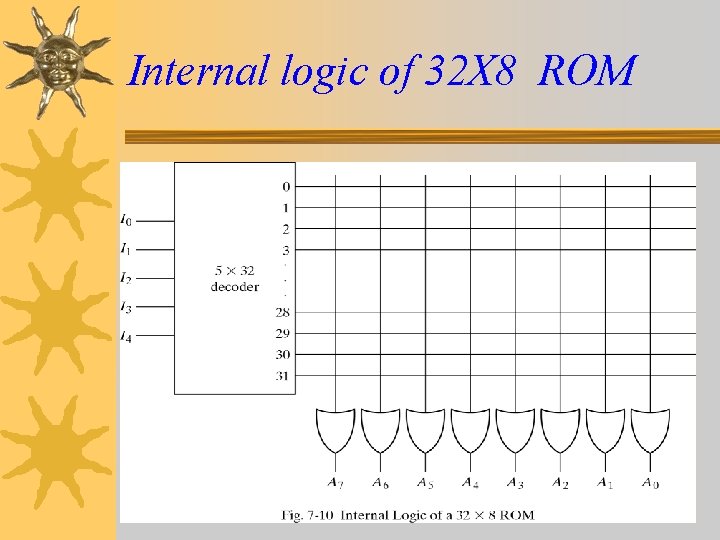

Internal logic of 32 X 8 ROM

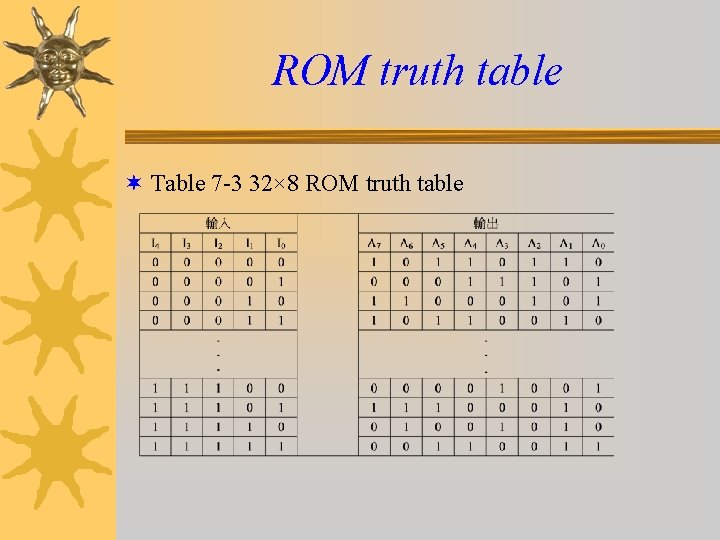

ROM truth table ¬ Table 7 -3 32× 8 ROM truth table

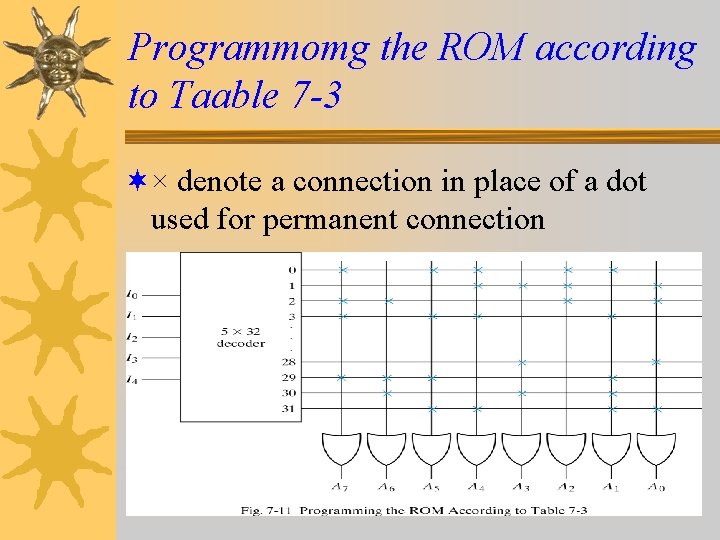

Programmomg the ROM according to Taable 7 -3 ¬× denote a connection in place of a dot used for permanent connection

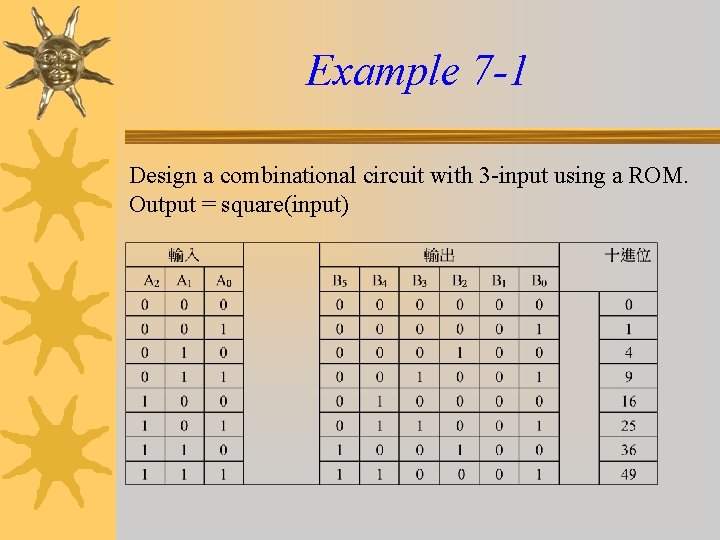

Example 7 -1 Design a combinational circuit with 3 -input using a ROM. Output = square(input)

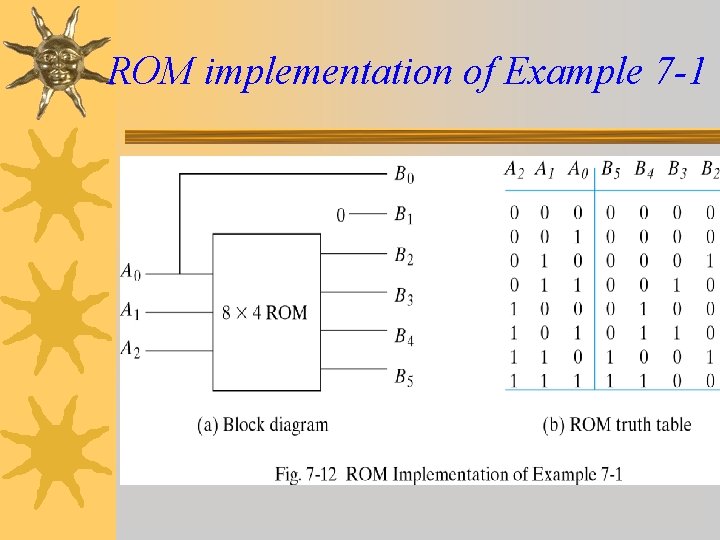

ROM implementation of Example 7 -1

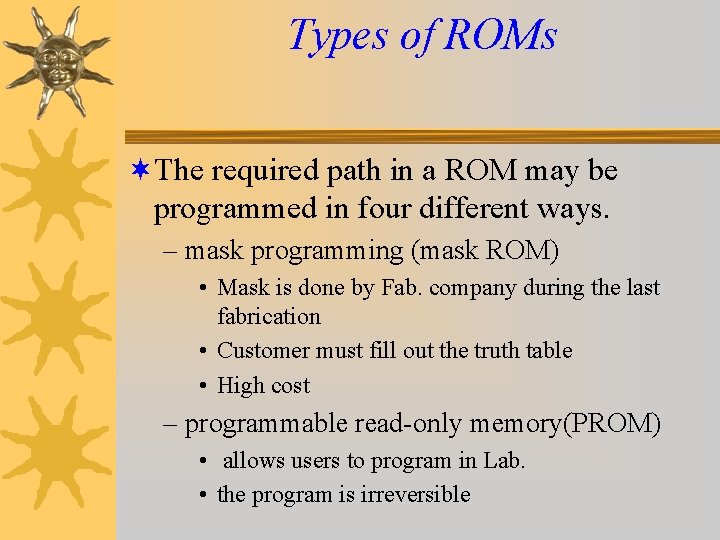

Types of ROMs ¬The required path in a ROM may be programmed in four different ways. – mask programming (mask ROM) • Mask is done by Fab. company during the last fabrication • Customer must fill out the truth table • High cost – programmable read-only memory(PROM) • allows users to program in Lab. • the program is irreversible

Types of ROMs – Erasable PROM(EPROM) • by ultraviolet light – electrically-erasable PROM(EEPROM or E²PROM), • by electrical signal • can be erased without removing it from tis socket

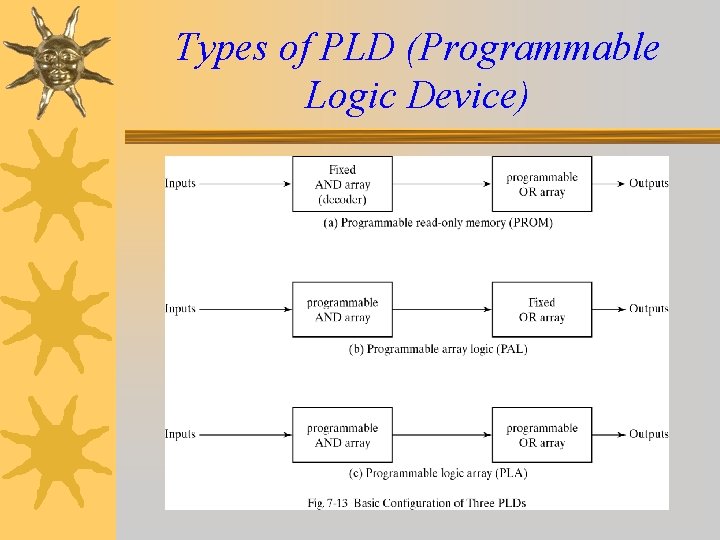

Types of PLD (Programmable Logic Device)

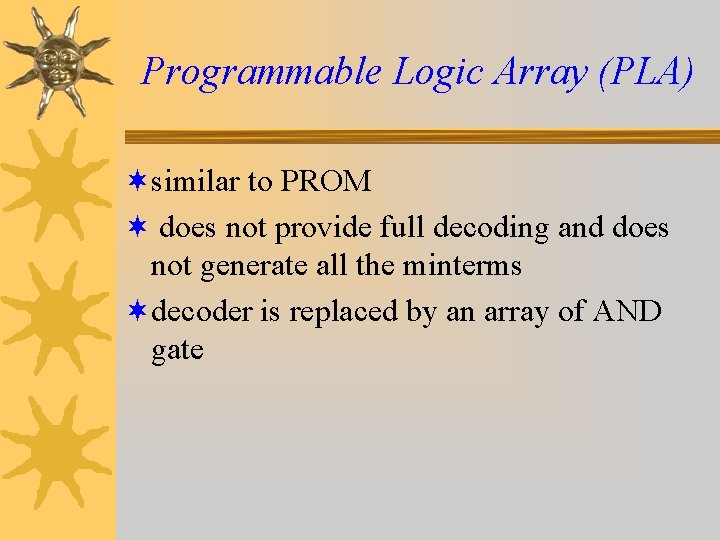

Programmable Logic Array (PLA) ¬similar to PROM ¬ does not provide full decoding and does not generate all the minterms ¬decoder is replaced by an array of AND gate

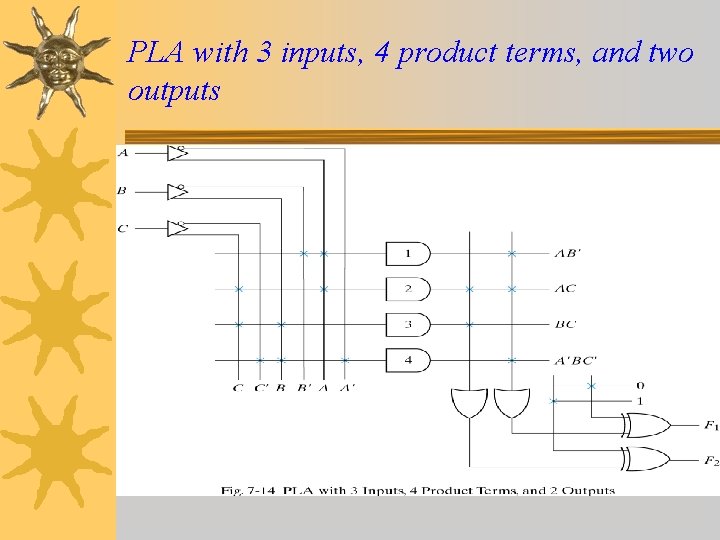

PLA with 3 inputs, 4 product terms, and two outputs

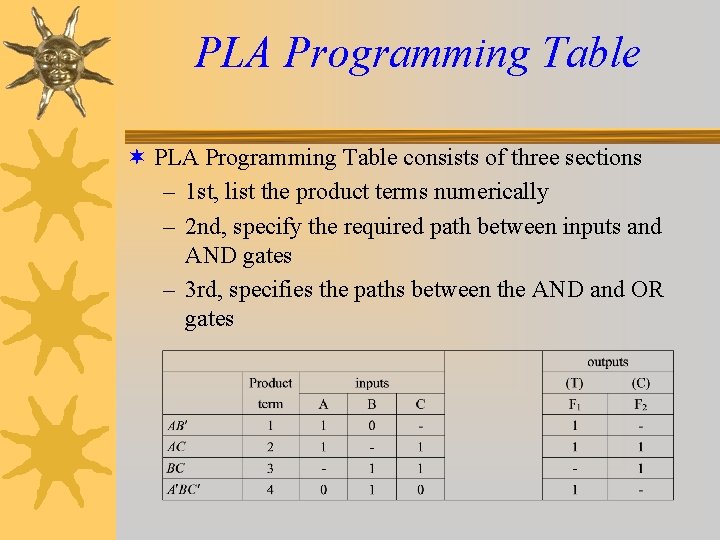

PLA Programming Table ¬ PLA Programming Table consists of three sections – 1 st, list the product terms numerically – 2 nd, specify the required path between inputs and AND gates – 3 rd, specifies the paths between the AND and OR gates

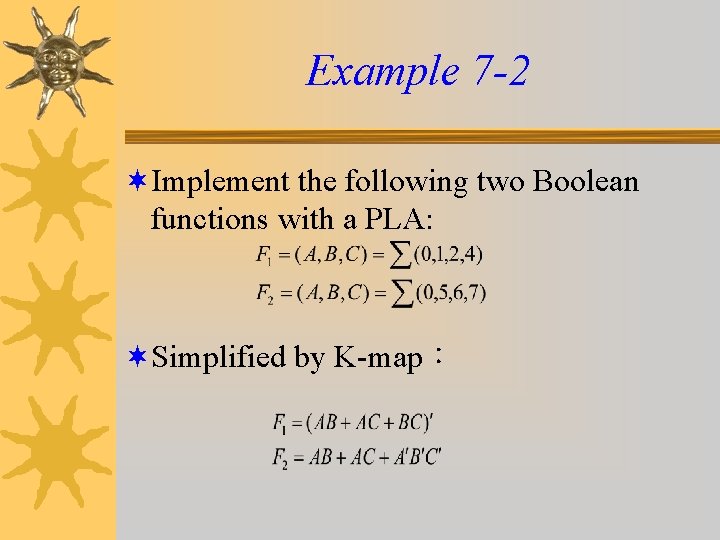

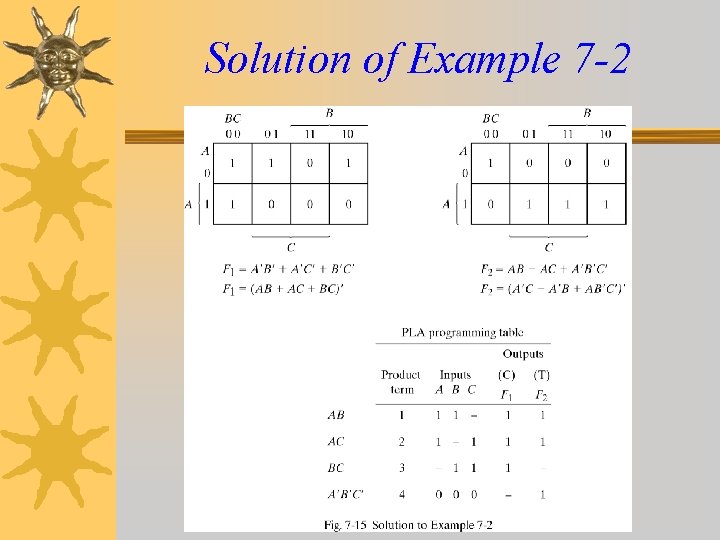

Example 7 -2 ¬Implement the following two Boolean functions with a PLA: ¬Simplified by K-map:

Solution of Example 7 -2

- Slides: 31