Combinational Circuits with Programmable Logic Devices b Programmable

Combinational Circuits with Programmable Logic Devices b. Programmable Logic Arrays (PLA) b. Programmable Read-Only Memory (PROM) 9/9/2021 UHD: CMS: CS 3402: Berrached. A 1

UHD: CMS: CS 3402: Berrached. A Programmable Logic Devices b Any Boolean function can be expressed in a Sum of Product form b SOP form => AND-OR implementation Programmable Logic Devices: b Pre-fabricated building blocks of many AND/OR gates (or NOR, NAND) b Programmed by making or breaking connections among the gates

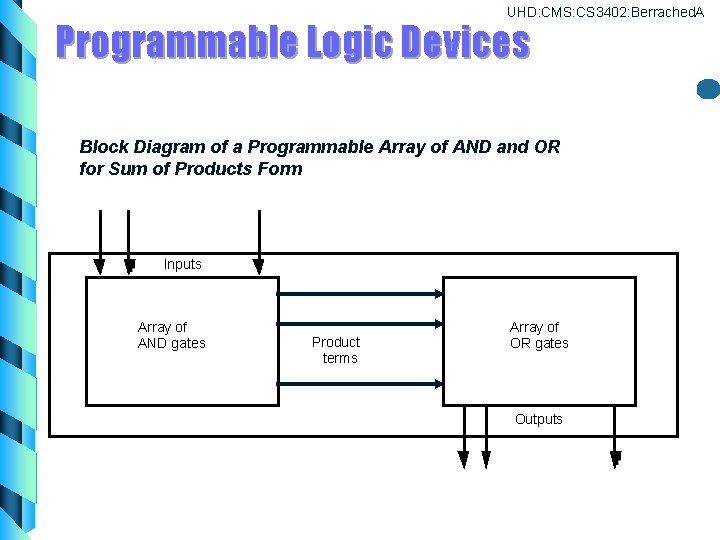

UHD: CMS: CS 3402: Berrached. A Programmable Logic Devices Block Diagram of a Programmable Array of AND and OR for Sum of Products Form Inputs Array of AND gates Product terms Array of OR gates Outputs

UHD: CMS: CS 3402: Berrached. A Programmable Logic Devices b Programmable Logic Array (PLA): The AND array and the OR array are programmable. b Programmable Array Logic (PAL): The AND array is programmable but the OR array is fixed b Programmable Read-Only Memory(PROM): The AND array is fixed and the OR array is programmable.

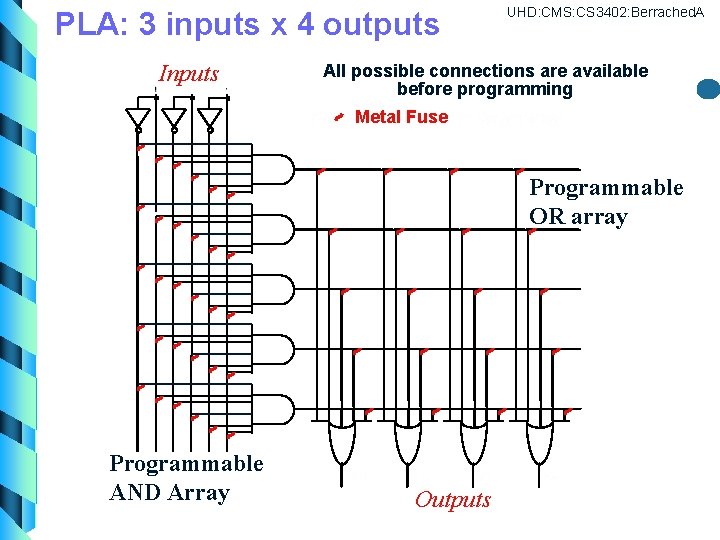

PLA: 3 inputs x 4 outputs Inputs UHD: CMS: CS 3402: Berrached. A All possible connections are available before programming Metal Fuse Programmable OR array Programmable AND Array Outputs

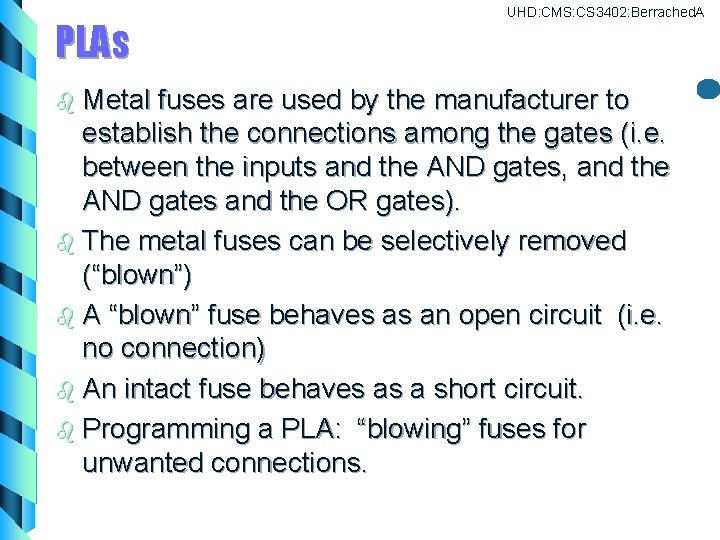

PLAs b Metal UHD: CMS: CS 3402: Berrached. A fuses are used by the manufacturer to establish the connections among the gates (i. e. between the inputs and the AND gates, and the AND gates and the OR gates). b The metal fuses can be selectively removed (“blown”) b A “blown” fuse behaves as an open circuit (i. e. no connection) b An intact fuse behaves as a short circuit. b Programming a PLA: “blowing” fuses for unwanted connections.

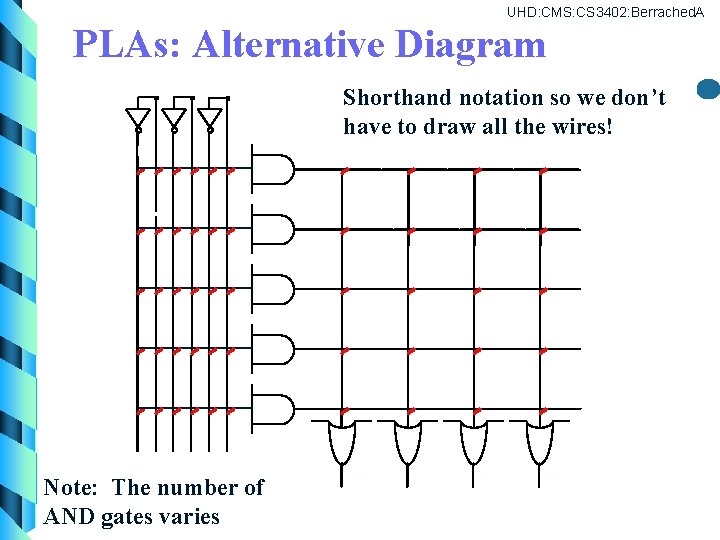

UHD: CMS: CS 3402: Berrached. A PLAs: Alternative Diagram Shorthand notation so we don’t have to draw all the wires! Note: The number of AND gates varies

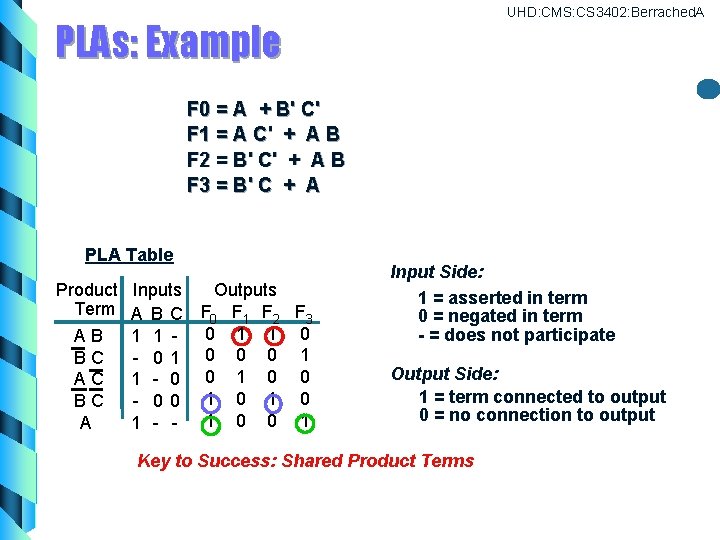

UHD: CMS: CS 3402: Berrached. A PLAs: Example F 0 = A + B' C' F 1 = A C' + A B F 2 = B' C' + A B F 3 = B' C + A PLA Table Product Term AB BC AC BC A Inputs Outputs A B C F 0 F 1 F 2 F 3 0 1 1 - 0 1 0 0 0 1 1 - 0 0 1 0 0 - 0 0 1 0 1 0 0 1 1 - - Input Side: 1 = asserted in term 0 = negated in term - = does not participate Output Side: 1 = term connected to output 0 = no connection to output Key to Success: Shared Product Terms

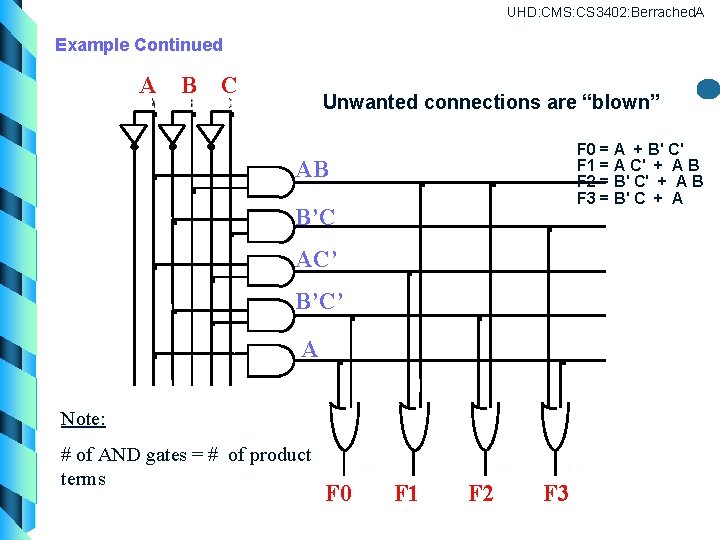

UHD: CMS: CS 3402: Berrached. A Example Continued A B C Unwanted connections are “blown” F 0 = A + B' C' F 1 = A C' + A B F 2 = B' C' + A B F 3 = B' C + A AB B’C AC’ B’C’ A Note: # of AND gates = # of product terms F 0 F 1 F 2 F 3

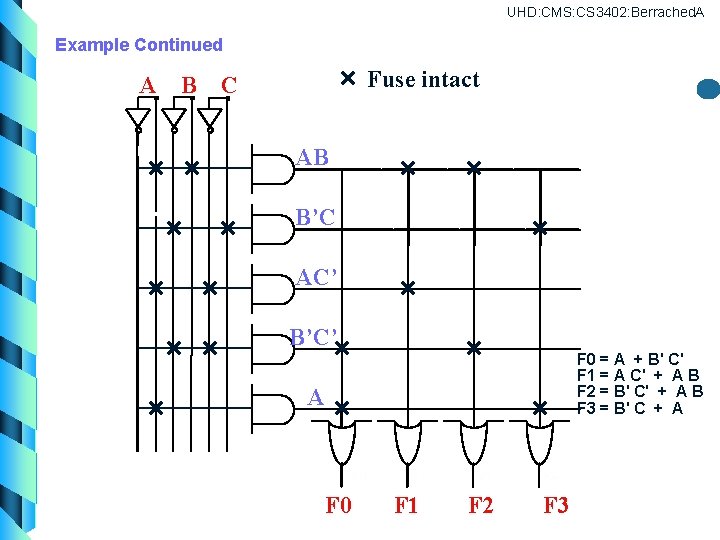

UHD: CMS: CS 3402: Berrached. A Example Continued A B Fuse intact C AB B’C AC’ B’C’ F 0 = A + B' C' F 1 = A C' + A B F 2 = B' C' + A B F 3 = B' C + A A F 0 F 1 F 2 F 3

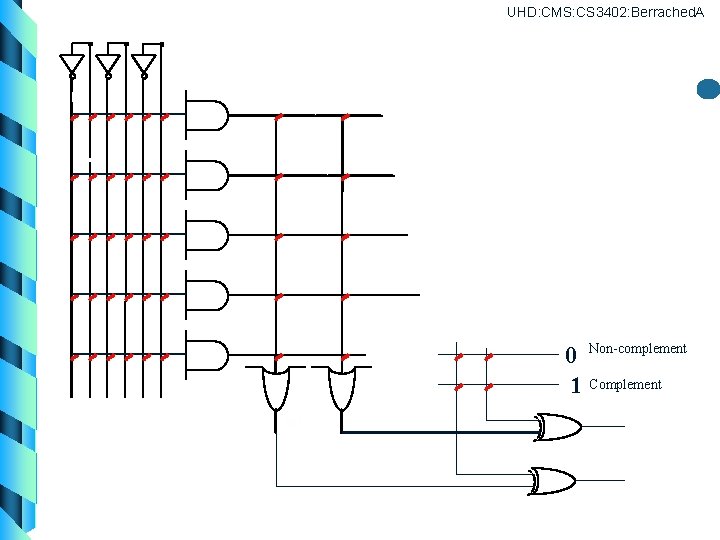

UHD: CMS: CS 3402: Berrached. A 0 Non-complement 1 Complement

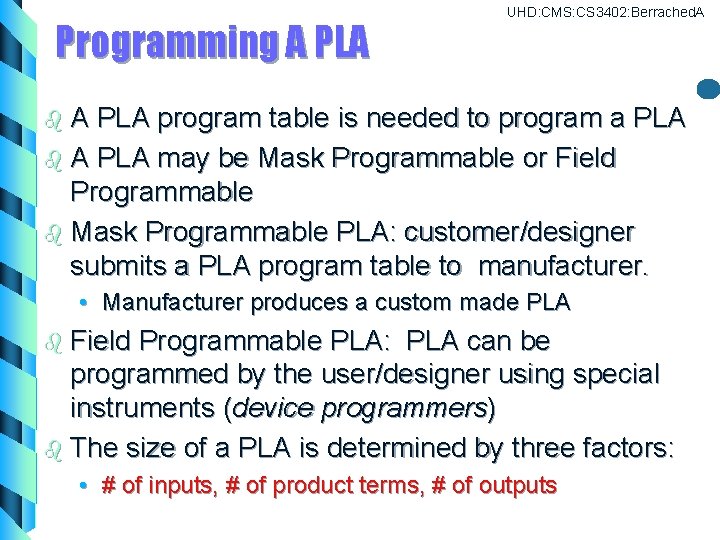

Programming A PLA UHD: CMS: CS 3402: Berrached. A b. A PLA program table is needed to program a PLA b A PLA may be Mask Programmable or Field Programmable b Mask Programmable PLA: customer/designer submits a PLA program table to manufacturer. • Manufacturer produces a custom made PLA b Field Programmable PLA: PLA can be programmed by the user/designer using special instruments (device programmers) b The size of a PLA is determined by three factors: • # of inputs, # of product terms, # of outputs

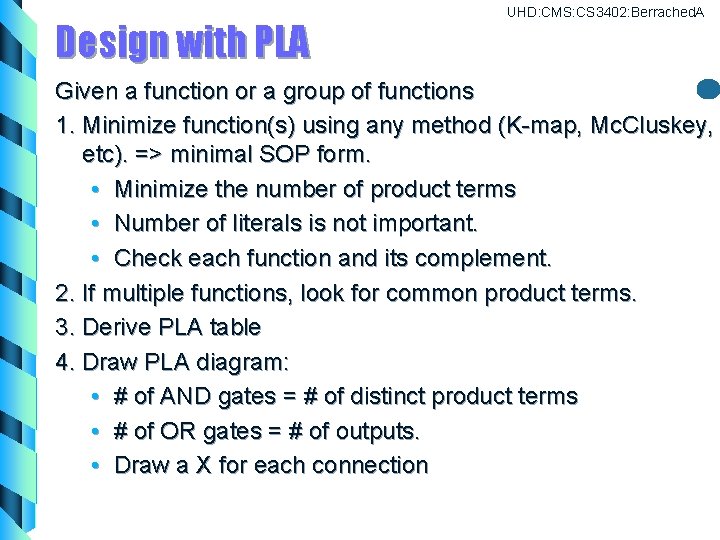

Design with PLA UHD: CMS: CS 3402: Berrached. A Given a function or a group of functions 1. Minimize function(s) using any method (K-map, Mc. Cluskey, etc). => minimal SOP form. • Minimize the number of product terms • Number of literals is not important. • Check each function and its complement. 2. If multiple functions, look for common product terms. 3. Derive PLA table 4. Draw PLA diagram: • # of AND gates = # of distinct product terms • # of OR gates = # of outputs. • Draw a X for each connection

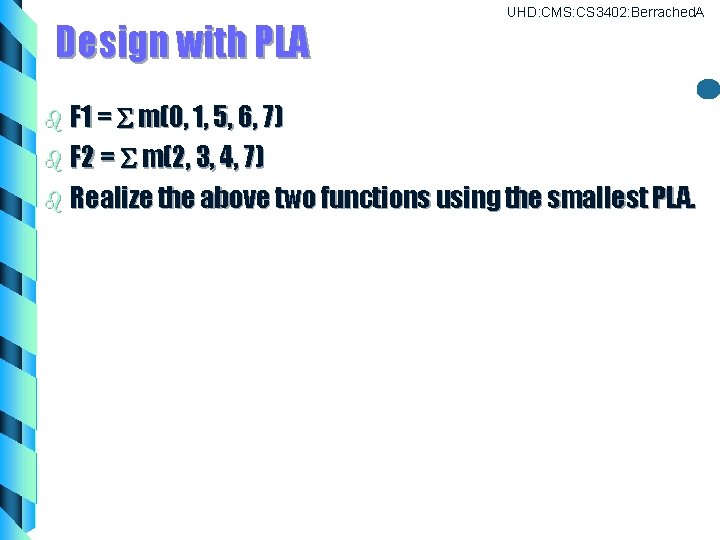

Design with PLA UHD: CMS: CS 3402: Berrached. A b F 1 = m(0, 1, 5, 6, 7) b F 2 = m(2, 3, 4, 7) b Realize the above two functions using the smallest PLA.

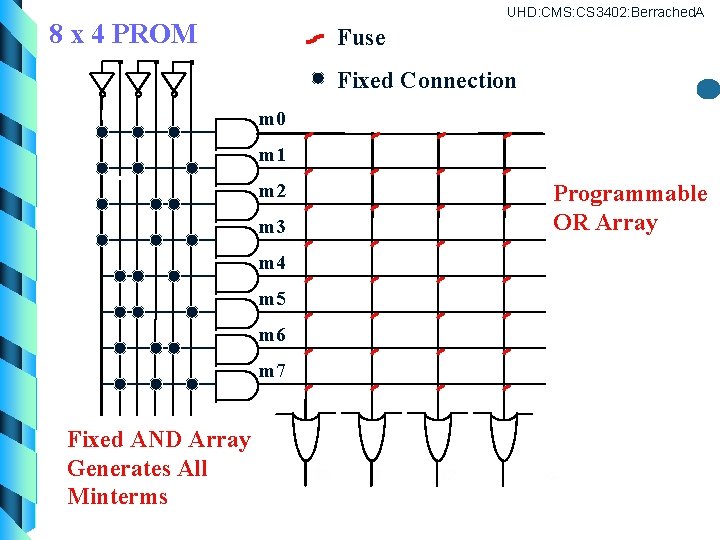

UHD: CMS: CS 3402: Berrached. A 8 x 4 PROM Fuse Fixed Connection m 0 m 1 m 2 m 3 m 4 m 5 m 6 m 7 Fixed AND Array Generates All Minterms Programmable OR Array

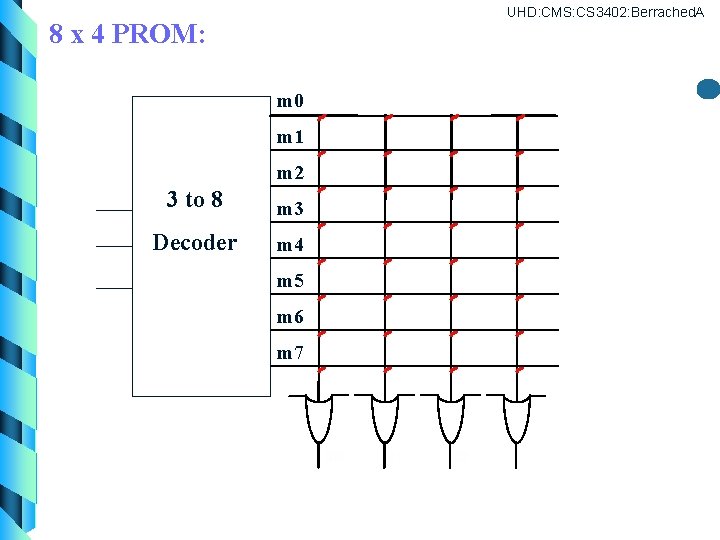

UHD: CMS: CS 3402: Berrached. A 8 x 4 PROM: m 0 m 1 m 2 3 to 8 m 3 Decoder m 4 m 5 m 6 m 7

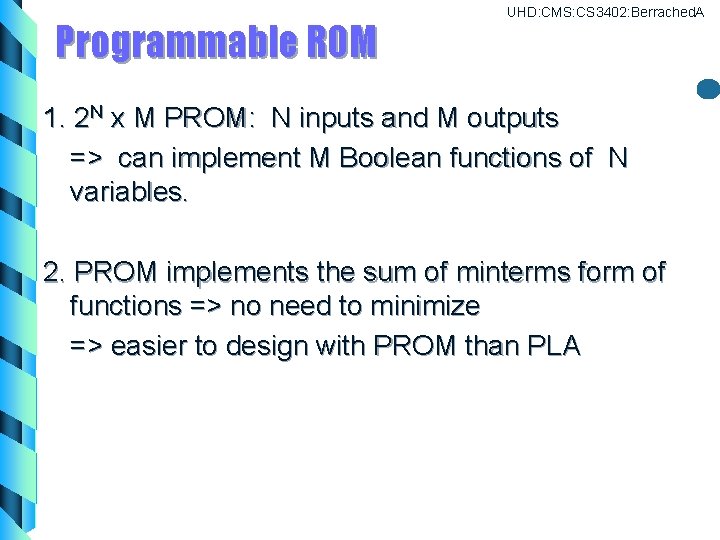

Programmable ROM UHD: CMS: CS 3402: Berrached. A 1. 2 N x M PROM: N inputs and M outputs => can implement M Boolean functions of N variables. 2. PROM implements the sum of minterms form of functions => no need to minimize => easier to design with PROM than PLA

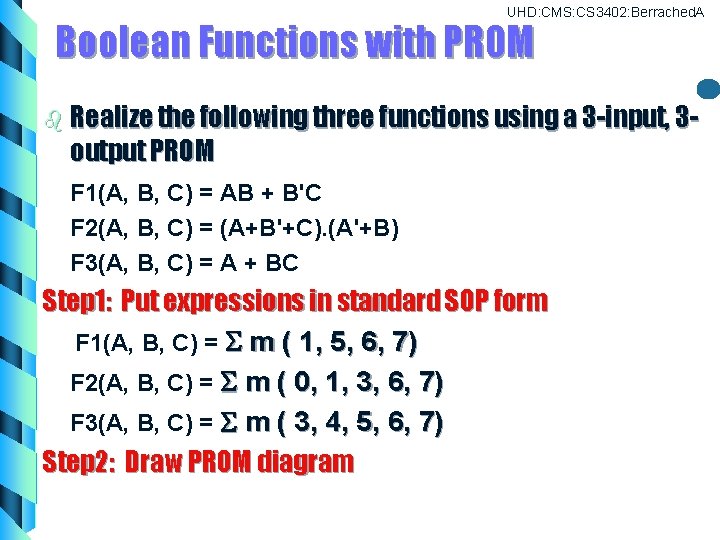

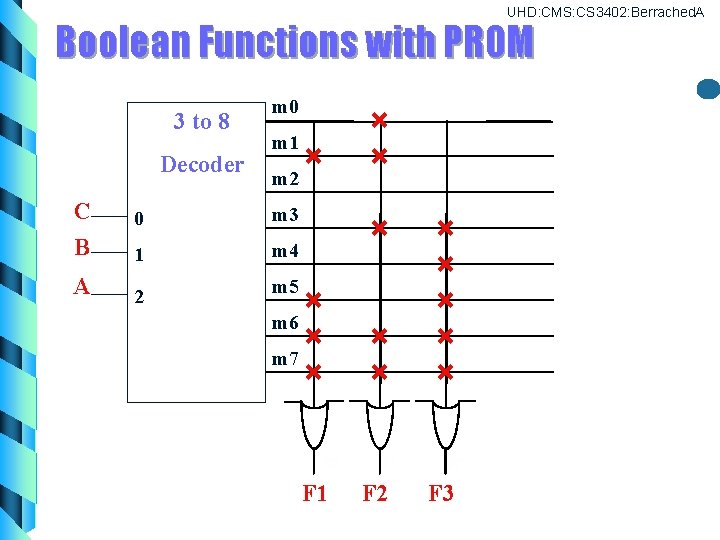

UHD: CMS: CS 3402: Berrached. A Boolean Functions with PROM b Realize the following three functions using a 3 -input, 3 - output PROM F 1(A, B, C) = AB + B'C F 2(A, B, C) = (A+B'+C). (A'+B) F 3(A, B, C) = A + BC Step 1: Put expressions in standard SOP form F 1(A, B, C) = m ( 1, 5, 6, 7) F 2(A, B, C) = m ( 0, 1, 3, 6, 7) F 3(A, B, C) = m ( 3, 4, 5, 6, 7) Step 2: Draw PROM diagram

UHD: CMS: CS 3402: Berrached. A Boolean Functions with PROM 3 to 8 Decoder C B A m 0 m 1 m 2 0 m 3 1 m 4 2 m 5 m 6 m 7 F 1 F 2 F 3

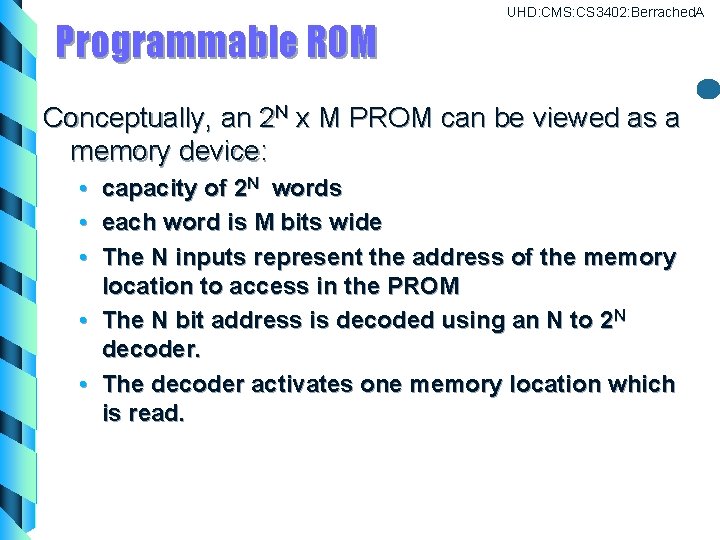

Programmable ROM UHD: CMS: CS 3402: Berrached. A Conceptually, an 2 N x M PROM can be viewed as a memory device: • • • capacity of 2 N words each word is M bits wide The N inputs represent the address of the memory location to access in the PROM • The N bit address is decoded using an N to 2 N decoder. • The decoder activates one memory location which is read.

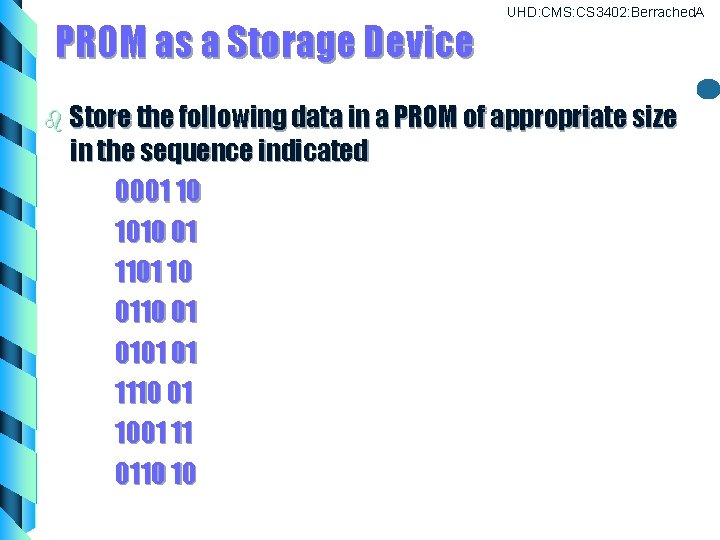

PROM as a Storage Device UHD: CMS: CS 3402: Berrached. A b Store the following data in a PROM of appropriate size in the sequence indicated 0001 10 1010 01 1101 10 01 0101 01 1110 01 1001 11 0110 10

- Slides: 21