Introduction to Programmable Logic Devices and FPGAs Edward

Introduction to Programmable Logic Devices and FPGAs Edward Freeman STFC Technology Department Detector & Electronics Division

Lecture Outline n Introduction u n FPGA Field Programmable Gate Array u n Why Programmable Logic Devices and FPGAs Architecture Design Flow u u Hardware Description Languages Design Tools edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Why Programmable Logic Devices and FPGAs Programmable Logic is a Key Underlying Technology for PP Experiments. n First-Level and High-Level Triggering n Data Transport (Networks) n Computers interacting with Hardware (Networks) n Silicon Trackers (Millions of Data Channels) Commercial Devices. Developments driven by Industry. Telecomms, Gaming, Aerospace, Automotive, Set-top boxes…. edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

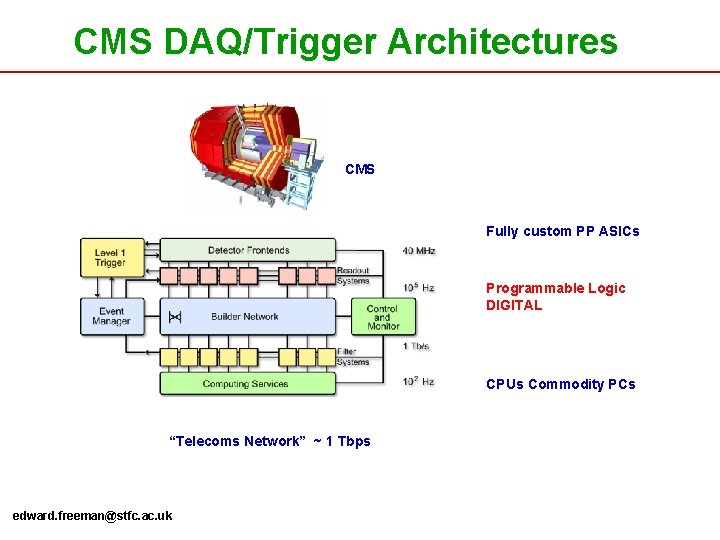

CMS DAQ/Trigger Architectures CMS Fully custom PP ASICs Programmable Logic DIGITAL CPUs Commodity PCs “Telecoms Network” ~ 1 Tbps edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

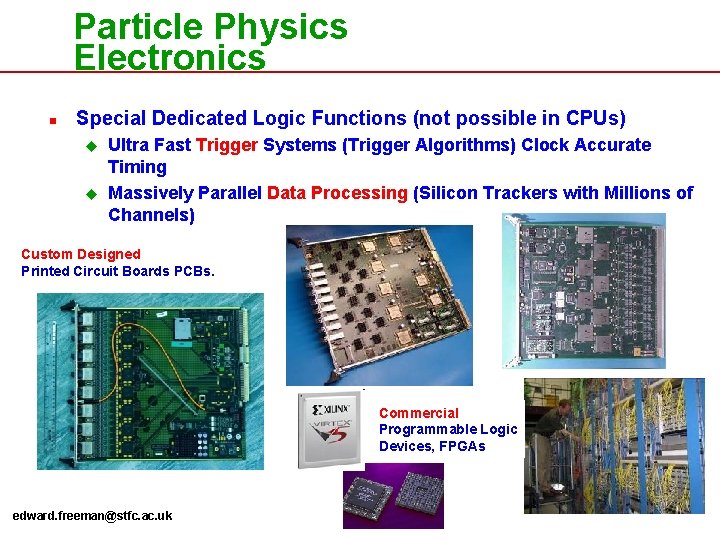

Particle Physics Electronics n Special Dedicated Logic Functions (not possible in CPUs) u u Ultra Fast Trigger Systems (Trigger Algorithms) Clock Accurate Timing Massively Parallel Data Processing (Silicon Trackers with Millions of Channels) Custom Designed Printed Circuit Boards PCBs. Commercial Programmable Logic Devices, FPGAs edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Lecture Outline n Introduction u n FPGA Field Programmable Gate Array u n Why Programmable Logic Devices and FPGAs Architecture Design Flow u u Hardware Description Languages Design Tools edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

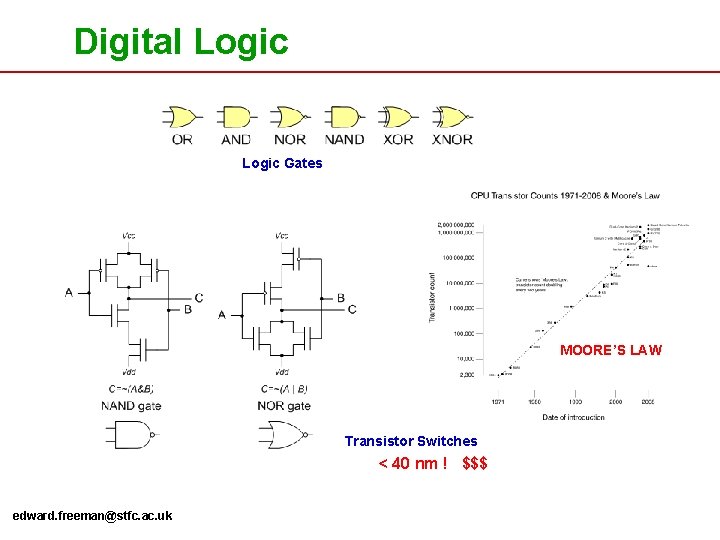

Digital Logic Gates MOORE’S LAW Transistor Switches < 40 nm ! $$$ edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

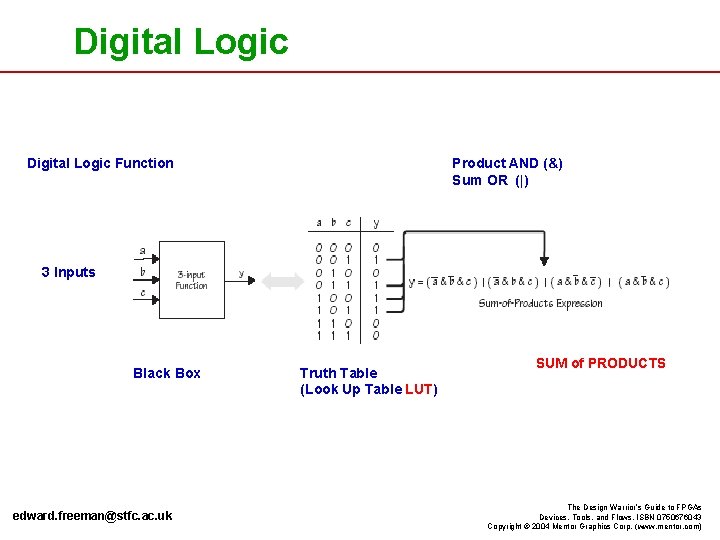

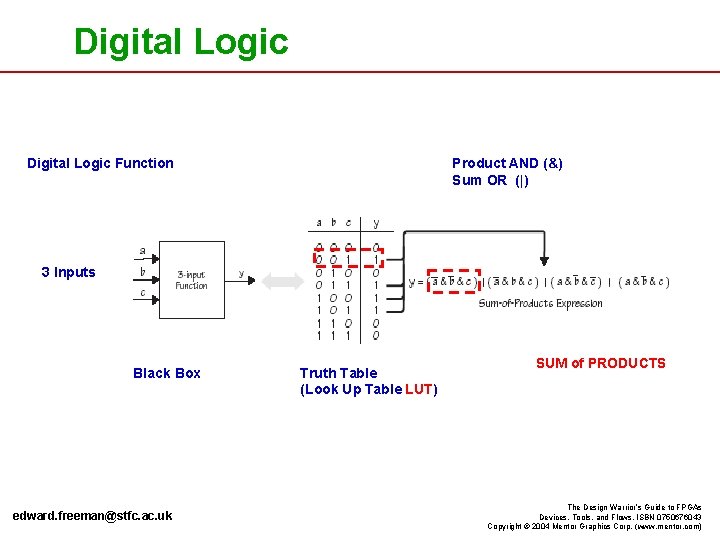

Digital Logic Function Product AND (&) Sum OR (|) 3 Inputs Black Box edward. freeman@stfc. ac. uk Truth Table (Look Up Table LUT) SUM of PRODUCTS The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Digital Logic Function Product AND (&) Sum OR (|) 3 Inputs Black Box edward. freeman@stfc. ac. uk Truth Table (Look Up Table LUT) SUM of PRODUCTS The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

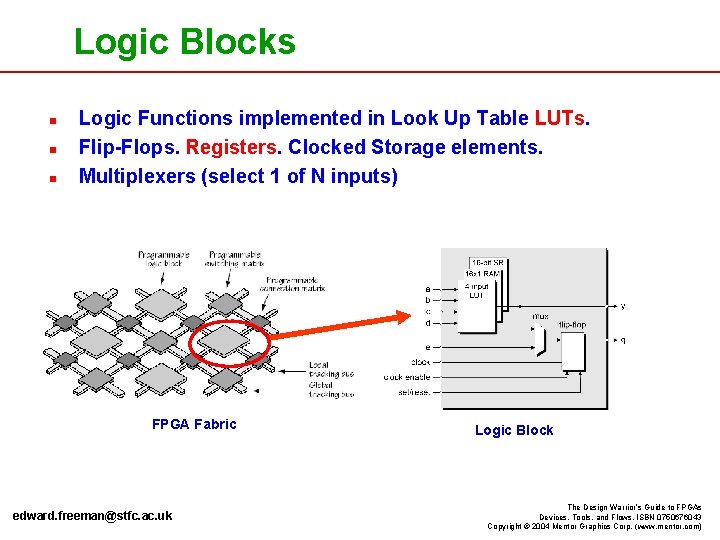

Logic Blocks n n n Logic Functions implemented in Look Up Table LUTs. Flip-Flops. Registers. Clocked Storage elements. Multiplexers (select 1 of N inputs) FPGA Fabric edward. freeman@stfc. ac. uk Logic Block The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

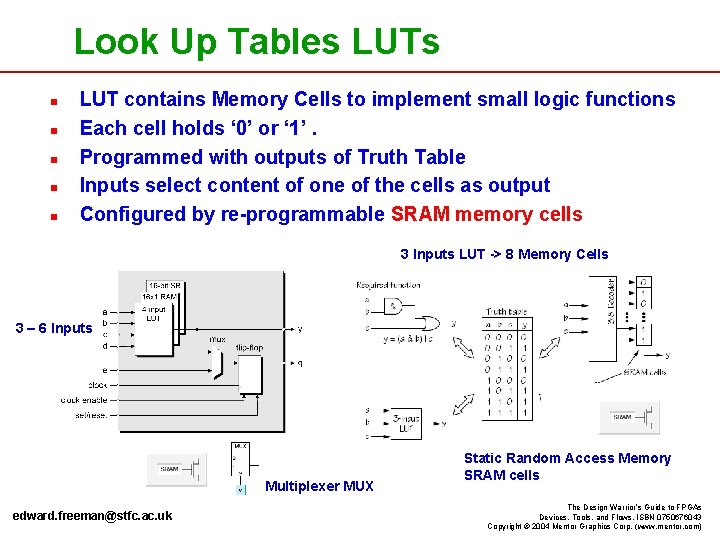

Look Up Tables LUTs n n n LUT contains Memory Cells to implement small logic functions Each cell holds ‘ 0’ or ‘ 1’. Programmed with outputs of Truth Table Inputs select content of one of the cells as output Configured by re-programmable SRAM memory cells 3 Inputs LUT -> 8 Memory Cells 3 – 6 Inputs Multiplexer MUX edward. freeman@stfc. ac. uk Static Random Access Memory SRAM cells The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

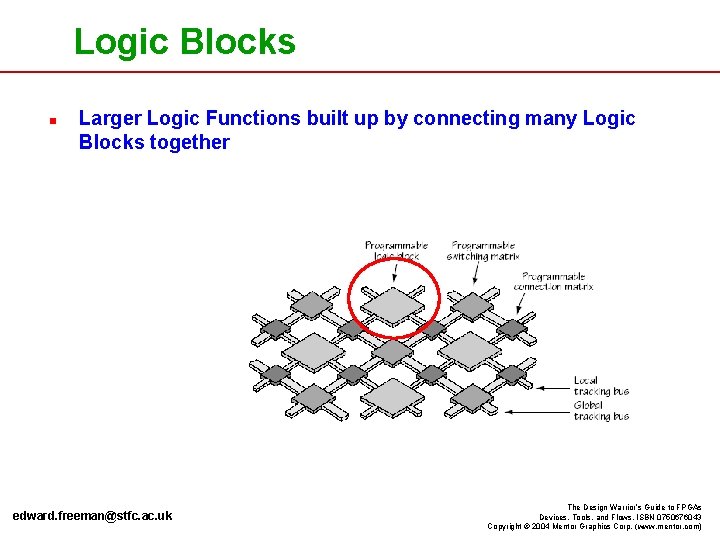

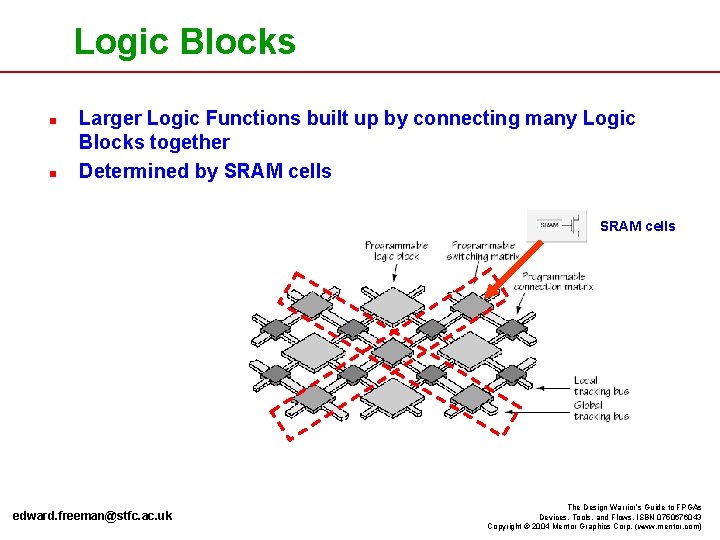

Logic Blocks n Larger Logic Functions built up by connecting many Logic Blocks together edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Logic Blocks n n Larger Logic Functions built up by connecting many Logic Blocks together Determined by SRAM cells edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

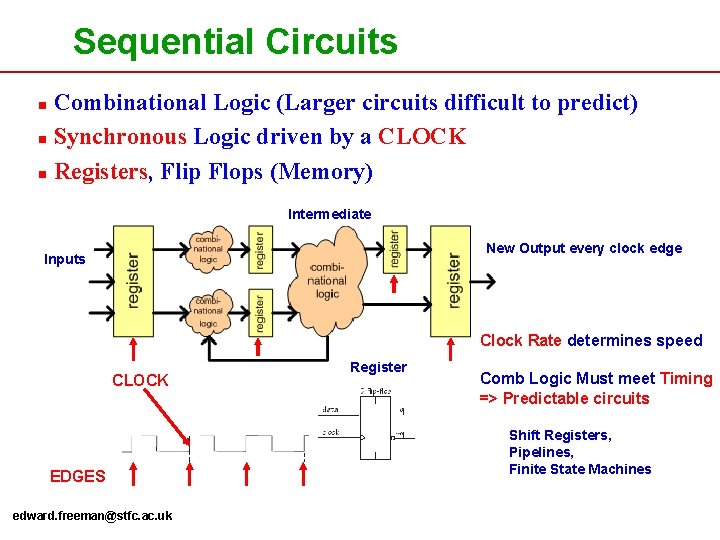

Sequential Circuits Combinational Logic (Larger circuits difficult to predict) n Synchronous Logic driven by a CLOCK n Registers, Flip Flops (Memory) n Intermediate New Output every clock edge Inputs Clock Rate determines speed CLOCK EDGES edward. freeman@stfc. ac. uk Register Comb Logic Must meet Timing => Predictable circuits Shift Registers, Pipelines, Finite State Machines … The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

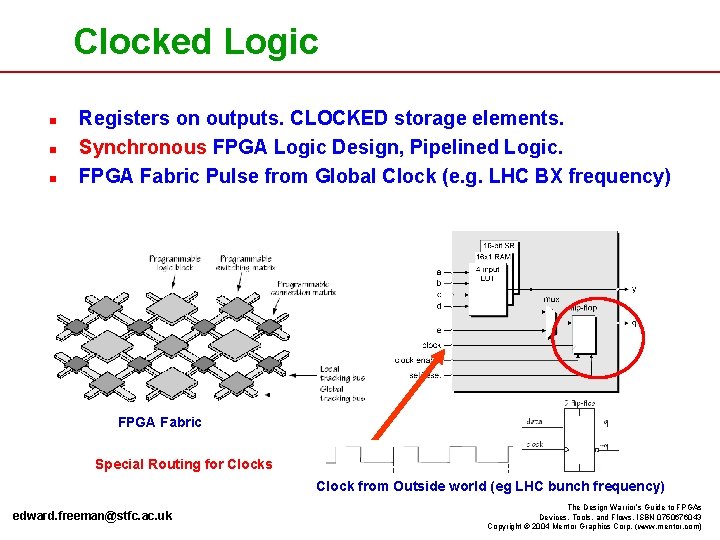

Clocked Logic n n n Registers on outputs. CLOCKED storage elements. Synchronous FPGA Logic Design, Pipelined Logic. FPGA Fabric Pulse from Global Clock (e. g. LHC BX frequency) FPGA Fabric Special Routing for Clocks Clock from Outside world (eg LHC bunch frequency) edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

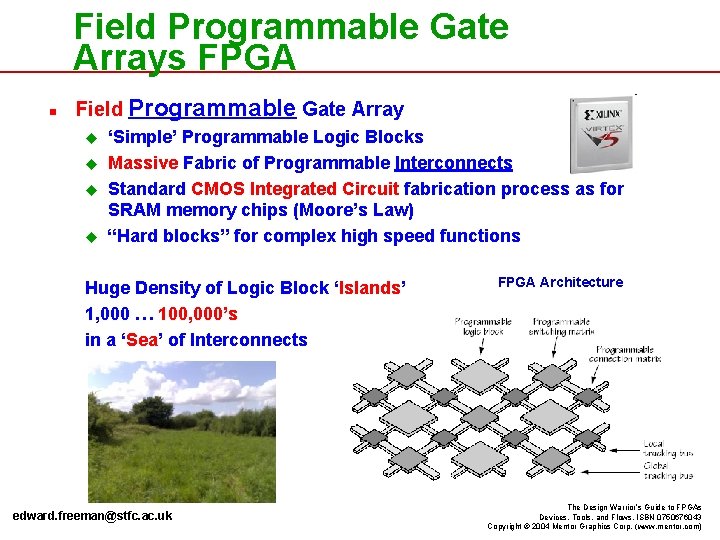

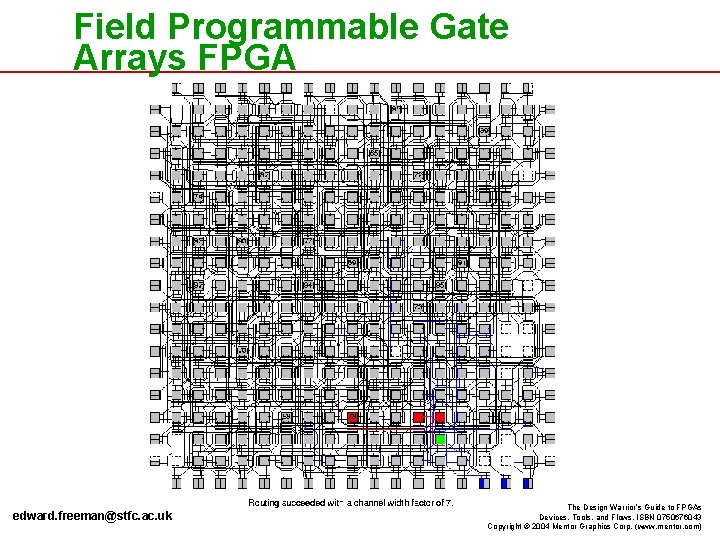

Field Programmable Gate Arrays FPGA n Field Programmable Gate Array u u ‘Simple’ Programmable Logic Blocks Massive Fabric of Programmable Interconnects Standard CMOS Integrated Circuit fabrication process as for SRAM memory chips (Moore’s Law) “Hard blocks” for complex high speed functions Huge Density of Logic Block ‘Islands’ 1, 000 … 100, 000’s in a ‘Sea’ of Interconnects edward. freeman@stfc. ac. uk FPGA Architecture The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Field Programmable Gate Arrays FPGA edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

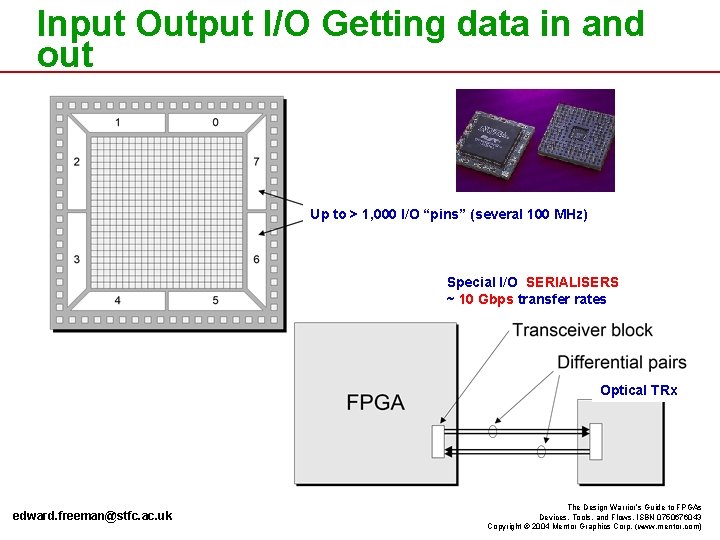

Input Output I/O Getting data in and out Up to > 1, 000 I/O “pins” (several 100 MHz) Special I/O SERIALISERS ~ 10 Gbps transfer rates Optical TRx edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Lecture Outline n Introduction u n FPGA Field Programmable Gate Array u n Why Programmable Logic Devices and FPGAs Architecture Design Flow u u Hardware Description Languages Design Tools edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

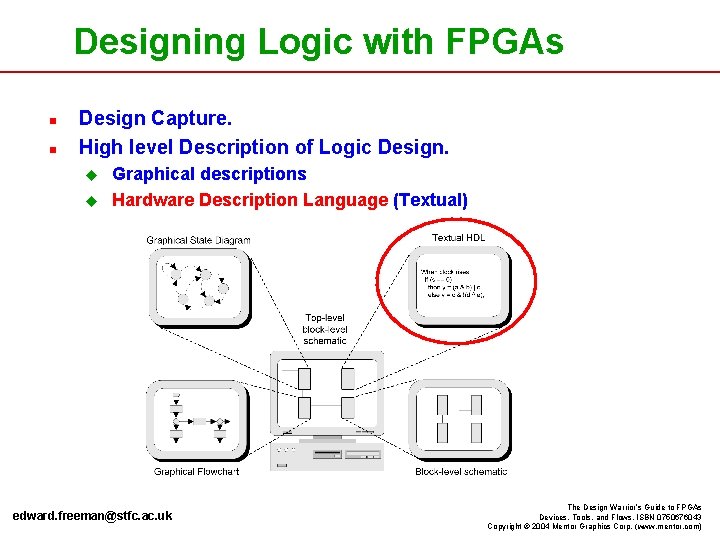

Designing Logic with FPGAs n n Design Capture. High level Description of Logic Design. u u Graphical descriptions Hardware Description Language (Textual) edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

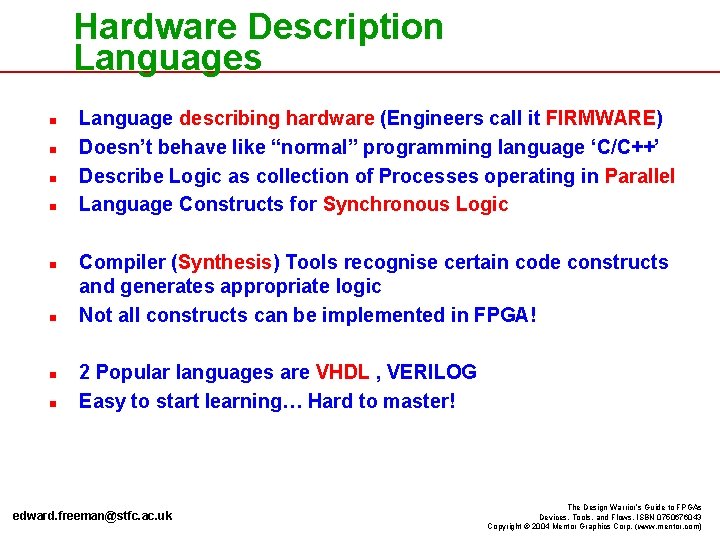

Hardware Description Languages n n n n Language describing hardware (Engineers call it FIRMWARE) Doesn’t behave like “normal” programming language ‘C/C++’ Describe Logic as collection of Processes operating in Parallel Language Constructs for Synchronous Logic Compiler (Synthesis) Tools recognise certain code constructs and generates appropriate logic Not all constructs can be implemented in FPGA! 2 Popular languages are VHDL , VERILOG Easy to start learning… Hard to master! edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

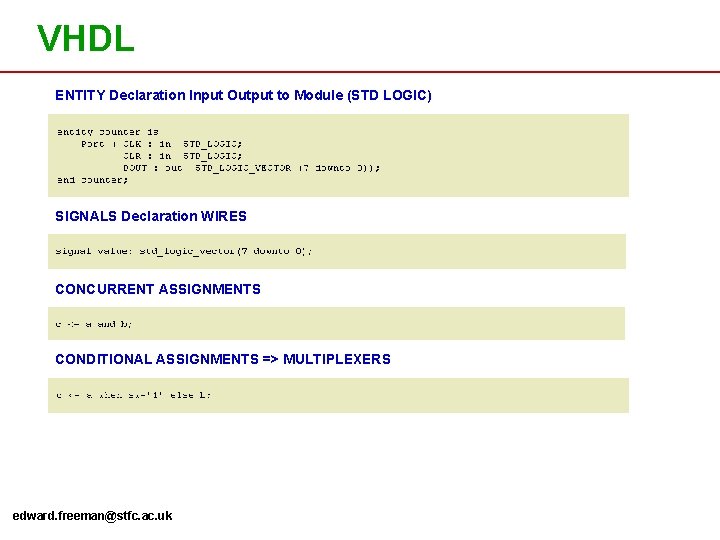

VHDL ENTITY Declaration Input Output to Module (STD LOGIC) SIGNALS Declaration WIRES CONCURRENT ASSIGNMENTS CONDITIONAL ASSIGNMENTS => MULTIPLEXERS edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

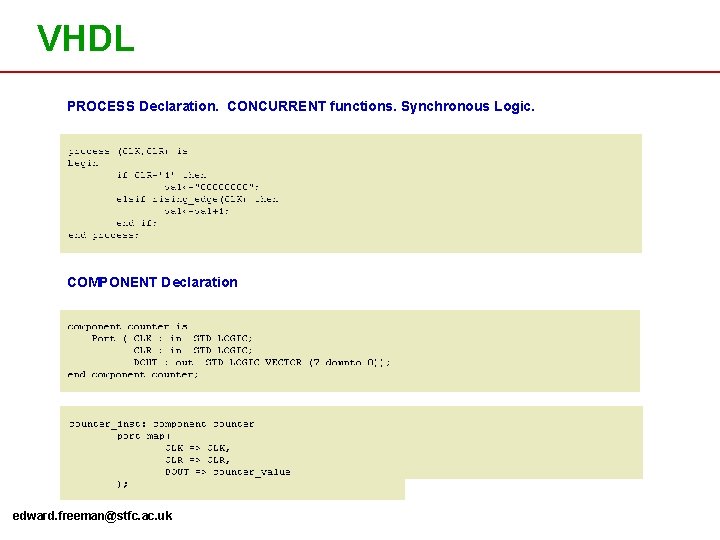

VHDL PROCESS Declaration. CONCURRENT functions. Synchronous Logic. COMPONENT Declaration edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

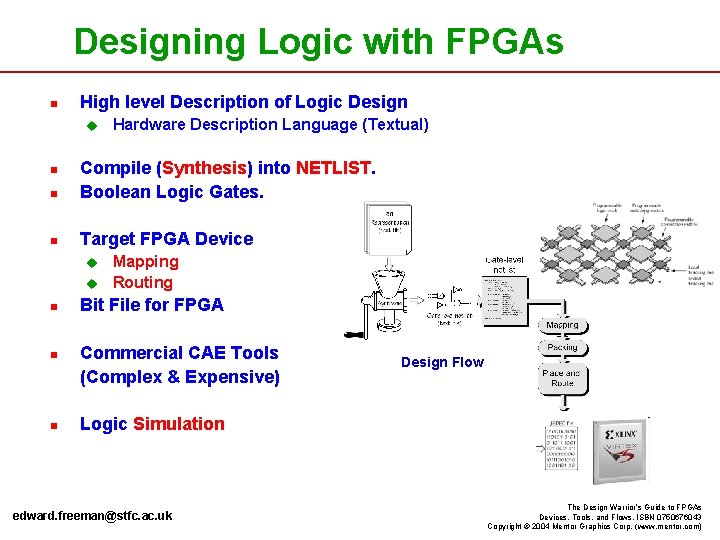

Designing Logic with FPGAs n High level Description of Logic Design u Hardware Description Language (Textual) n Compile (Synthesis) into NETLIST. Boolean Logic Gates. n Target FPGA Device n u u n n n Mapping Routing Bit File for FPGA Commercial CAE Tools (Complex & Expensive) Design Flow Logic Simulation edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

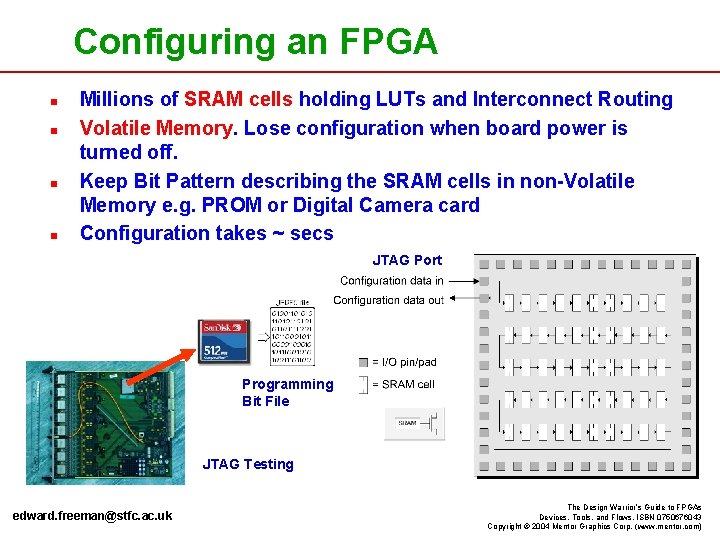

Configuring an FPGA n n Millions of SRAM cells holding LUTs and Interconnect Routing Volatile Memory. Lose configuration when board power is turned off. Keep Bit Pattern describing the SRAM cells in non-Volatile Memory e. g. PROM or Digital Camera card Configuration takes ~ secs JTAG Port Programming Bit File JTAG Testing edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

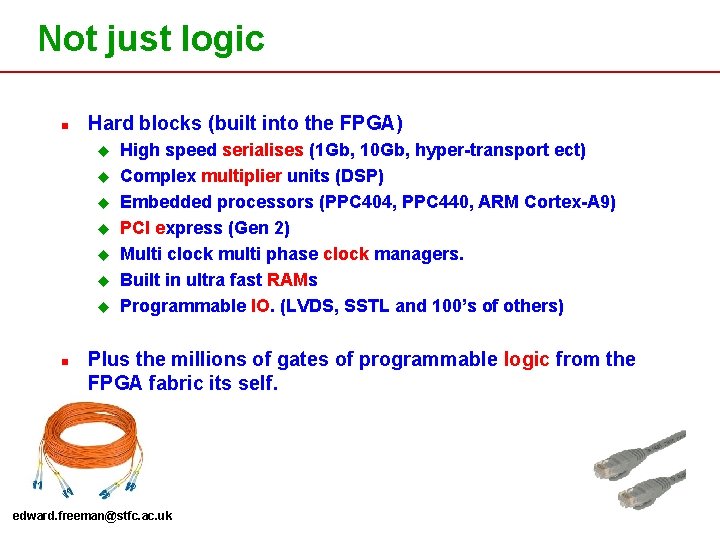

Not just logic n Hard blocks (built into the FPGA) u u u u n High speed serialises (1 Gb, 10 Gb, hyper-transport ect) Complex multiplier units (DSP) Embedded processors (PPC 404, PPC 440, ARM Cortex-A 9) PCI express (Gen 2) Multi clock multi phase clock managers. Built in ultra fast RAMs Programmable IO. (LVDS, SSTL and 100’s of others) Plus the millions of gates of programmable logic from the FPGA fabric its self. edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Serialisers n A number of types and speeds. u u We are currently supporting projects with multi 1 Gb Ethernet readout. 10 Gb is working in the lab and 1 st boards are in testing now PCI express endpoint (Gen 1) Camera link Can use off the self switches to make backend system edward. freeman@stfc. ac. uk PCI express The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Embedded processors and multipliers n Processors u u n Fast image processing and control loop feedback in C code software. (20 KHz image rate) Large ping pong (image) frame buffer System monitoring, house keeping, reporting and logging Can also have an army of small “soft” processor cores Multipliers (DSP blocks) u Complex FFT for machine frequency control. edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Block RAMs and Clock managers n Block RAMs u u u n Small high speed buffers Look up tables and scratch pads. FIFO’s to help adjust data rates between processing blocks. Clock Managers u u u Generate different frequency's from a reference clock. Generate phase shits of the clocks. Distribute the clocks to the different areas of the FPGAs (Not of much interest but nothing works without them) edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Other technology you can add to an FPGA n Memory interfaces u u n Maths functions u u n DRAM, DDR, QDR, SRAM, ZBTRAM ect. Industry standard memory modules DDR 2, DDR 3, Floating point units Complex Multiplier Integer Add, Sub, Multiply, Div Digital signal processing functions FFT, FIR, reed-solomon encoders Or any other digital system that can be described with custom logic. edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

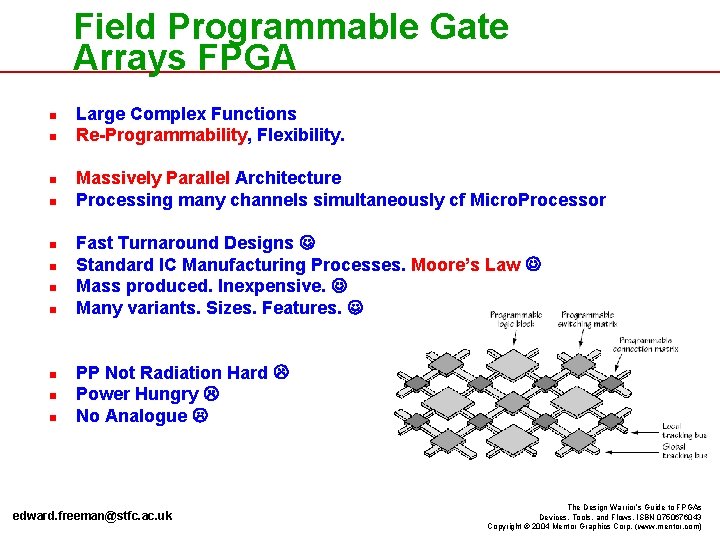

Field Programmable Gate Arrays FPGA n n n Large Complex Functions Re-Programmability, Flexibility. Massively Parallel Architecture Processing many channels simultaneously cf Micro. Processor Fast Turnaround Designs Standard IC Manufacturing Processes. Moore’s Law Mass produced. Inexpensive. Many variants. Sizes. Features. PP Not Radiation Hard Power Hungry No Analogue edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

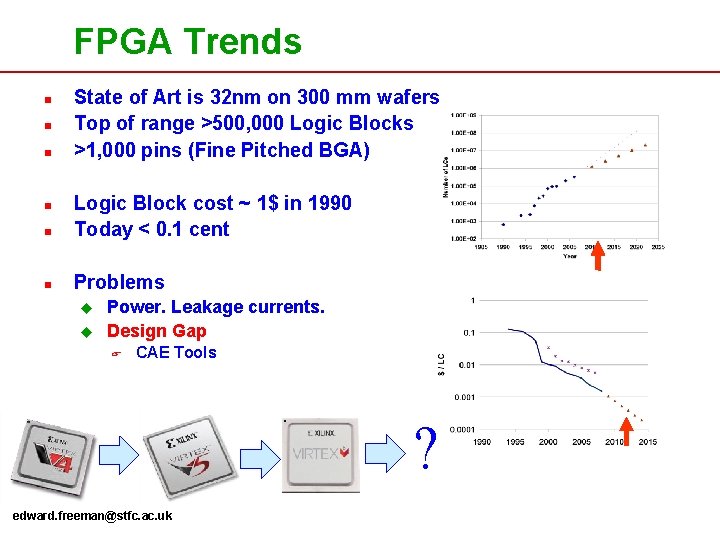

FPGA Trends n n n State of Art is 32 nm on 300 mm wafers Top of range >500, 000 Logic Blocks >1, 000 pins (Fine Pitched BGA) n Logic Block cost ~ 1$ in 1990 Today < 0. 1 cent n Problems n u u Power. Leakage currents. Design Gap F CAE Tools ? edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

Summary n FPGA Field Programmable Gate Arrays u n Architecture Design Flow u u u Hardware Description Languages Design Tools Exploit industry hardware and protocols Importance for Particle Physics Experiments edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

References and contacts n The Design Warrior’s Guide to FPGAs u n FPGA manufacturer web sites u u n www. xilinx. com www. altera. com FPGA Online u u u n Clive Maxfield, Newnes Elsevier www. pldesignline. com www. doulos. com Technology u u Rob Halsall – Rob. Halsall@stfc. ac. uk John Coughlan – John. Coughlan@stfc. ac. uk edward. freeman@stfc. ac. uk The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www. mentor. com)

- Slides: 34