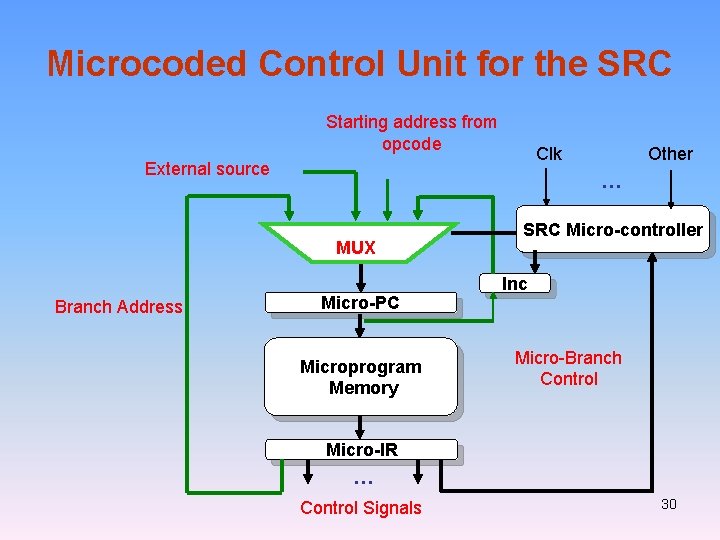

Block diagram of a Microcoded Control unit 4

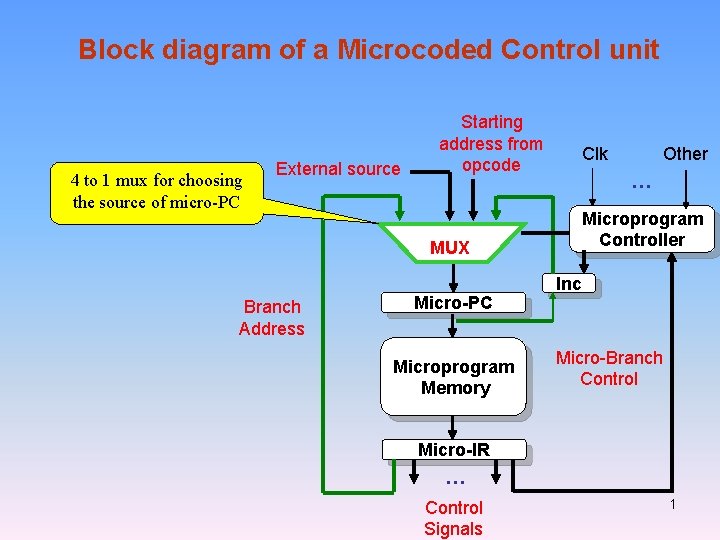

Block diagram of a Microcoded Control unit 4 to 1 mux for choosing the source of micro-PC External source Starting address from opcode MUX Branch Address Micro-PC Microprogram Memory Clk Other … Microprogram Controller Inc Micro-Branch Control Micro-IR … Control Signals 1

Review 2

CS 501 Advanced Computer Architecture Lecture 22 Dr. Noor Muhammad Sheikh 3

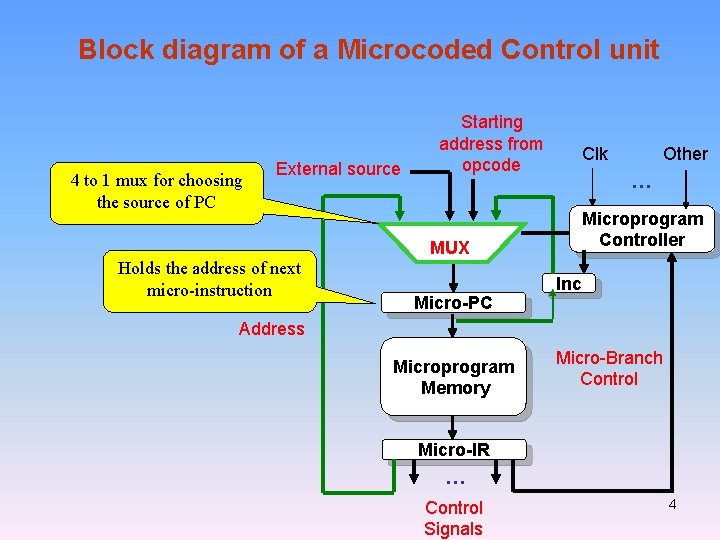

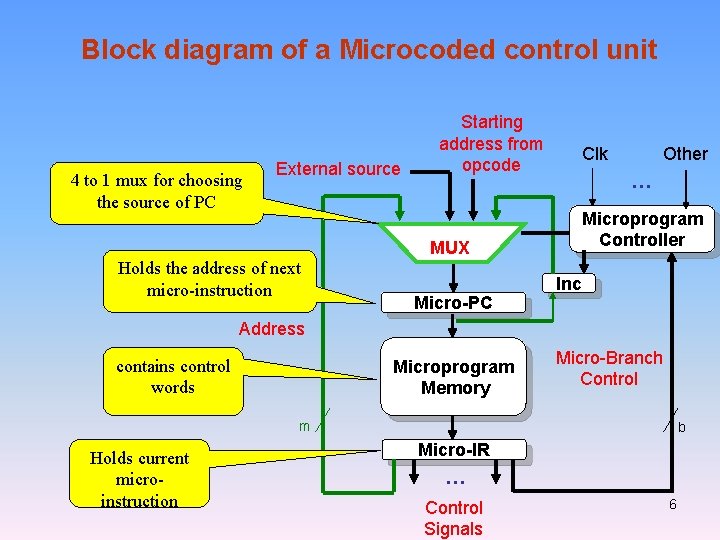

Block diagram of a Microcoded Control unit 4 to 1 mux for choosing the source of PC External source Starting address from opcode MUX Holds the address of next micro-instruction Branch Address Micro-PC Microprogram Memory Clk Other … Microprogram Controller Inc Micro-Branch Control Micro-IR … Control Signals 4

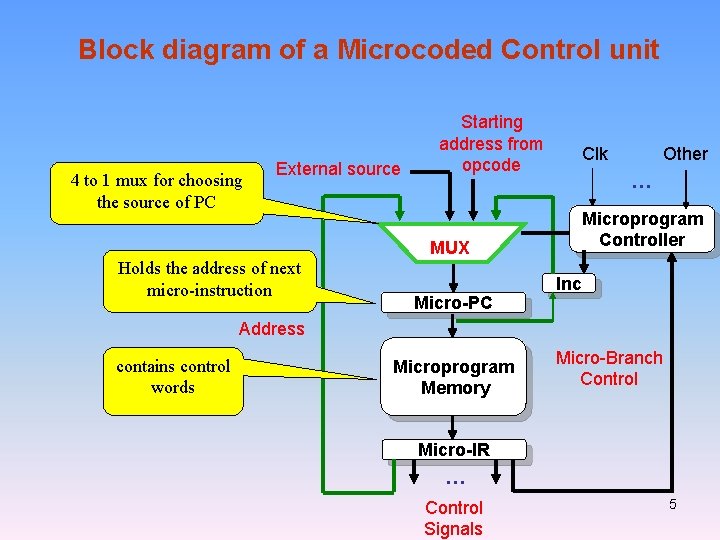

Block diagram of a Microcoded Control unit 4 to 1 mux for choosing the source of PC External source Starting address from opcode MUX Holds the address of next micro-instruction Branch Address contains control words Micro-PC Microprogram Memory Clk Other … Microprogram Controller Inc Micro-Branch Control Micro-IR … Control Signals 5

Block diagram of a Microcoded control unit 4 to 1 mux for choosing the source of PC External source Starting address from opcode MUX Holds the address of next micro-instruction Branch Address contains control words Micro-PC Microprogram Memory Clk Other … Microprogram Controller Inc Micro-Branch Control m Holds current microinstruction b Micro-IR … Control Signals 6

Fields in the micro-instruction Micro-IR 7

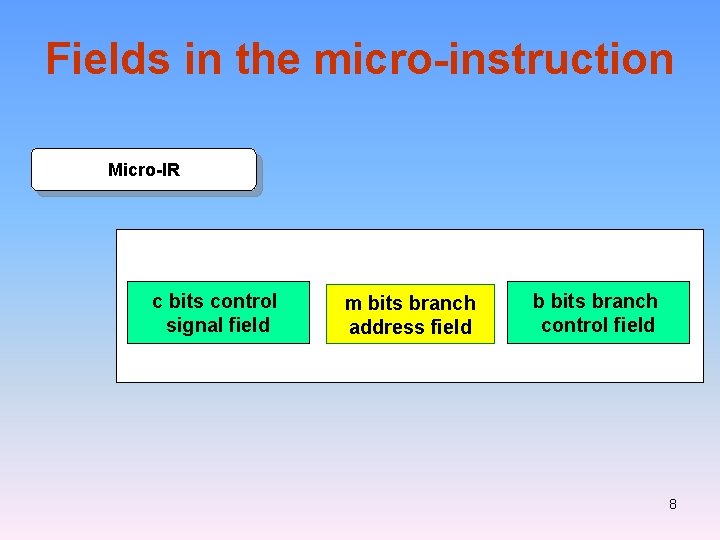

Fields in the micro-instruction Micro-IR c bits control signal field m bits branch address field b bits branch control field 8

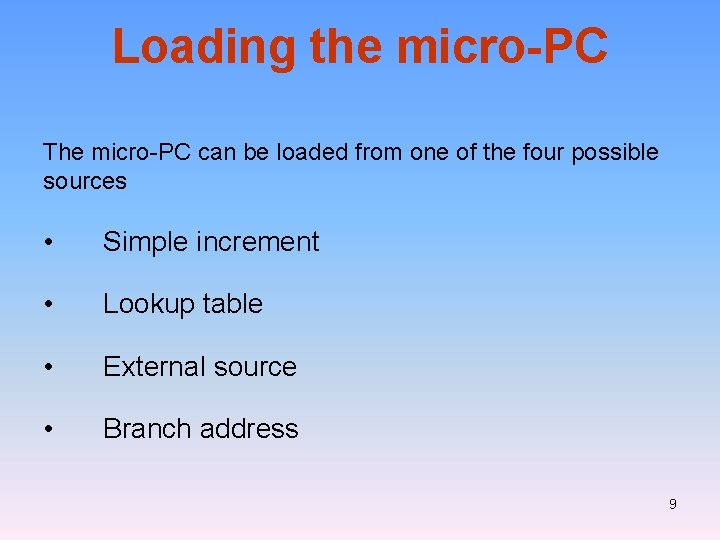

Loading the micro-PC The micro-PC can be loaded from one of the four possible sources • Simple increment • Lookup table • External source • Branch address 9

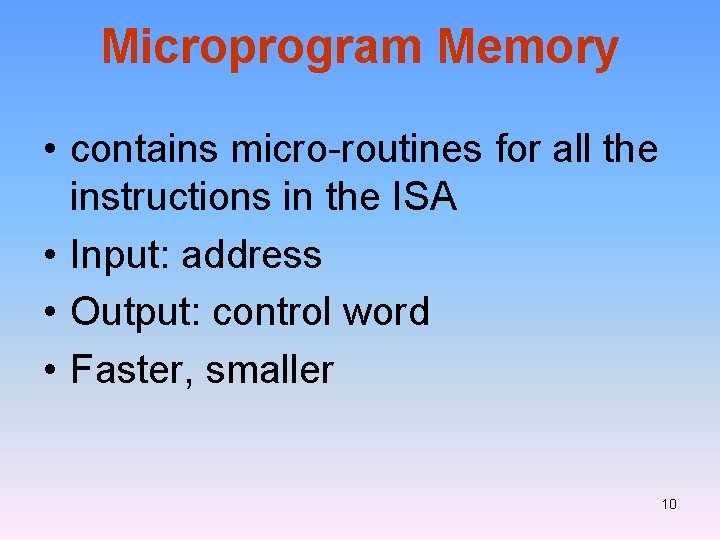

Microprogram Memory • contains micro-routines for all the instructions in the ISA • Input: address • Output: control word • Faster, smaller 10

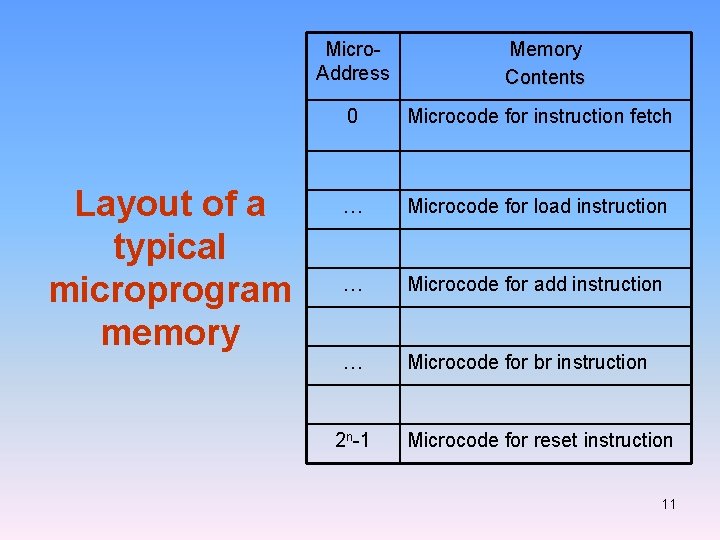

Layout of a typical microprogram memory Micro. Address Memory Contents 0 Microcode for instruction fetch … Microcode for load instruction … Microcode for add instruction … Microcode for br instruction 2 n-1 Microcode for reset instruction 11

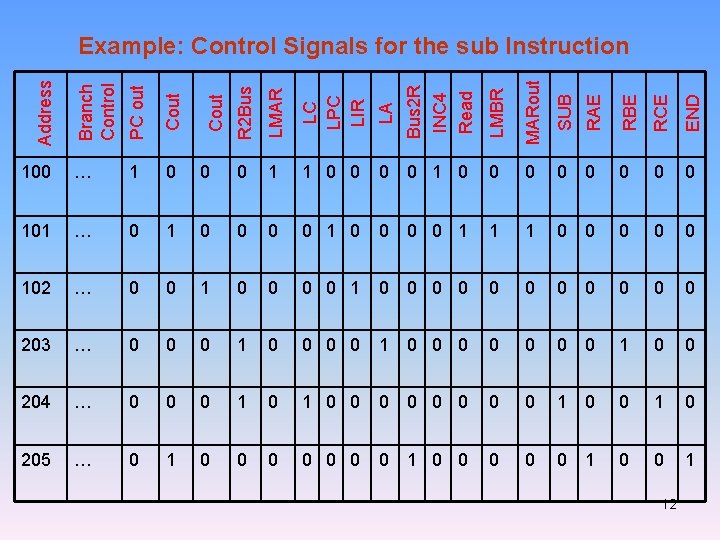

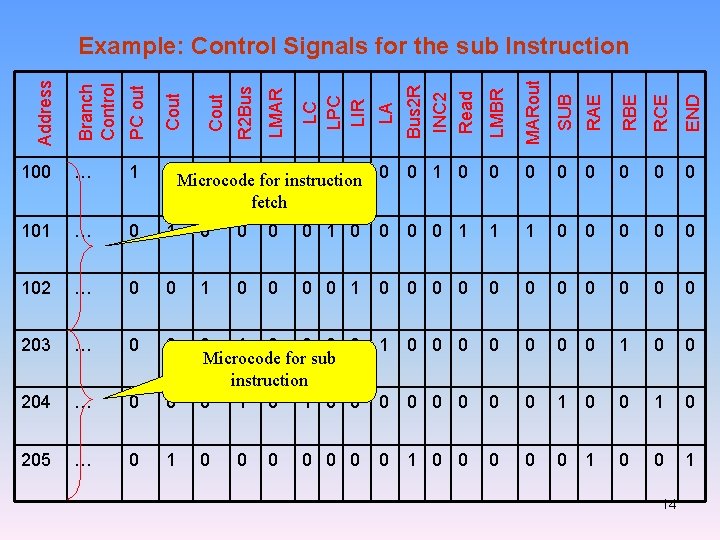

Cout R 2 Bus LMAR LC LPC LIR LA LMBR MARout SUB RAE RBE RCE END … 1 0 0 0 1 1 0 0 0 101 … 0 1 0 0 0 0 1 1 1 0 0 0 102 … 0 0 1 0 0 0 0 203 … 0 0 0 1 0 0 204 … 0 0 0 1 0 0 1 0 205 … 0 1 0 0 0 1 0 0 1 Bus 2 R INC 4 Read PC out 100 Cout Branch Control Address Example: Control Signals for the sub Instruction 12

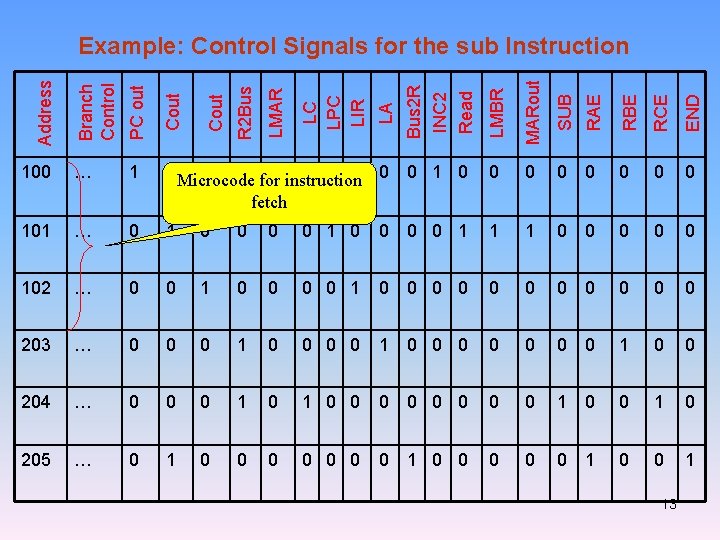

LMBR MARout SUB RAE RBE RCE END Bus 2 R INC 2 Read LA LC LPC LIR 0 Microcode 0 0 for 1 instruction 1 0 0 1 0 LMAR 1 R 2 Bus Cout … Cout PC out 100 Branch Control Address Example: Control Signals for the sub Instruction 0 0 0 0 fetch 101 … 0 1 0 0 0 0 1 1 1 0 0 0 102 … 0 0 1 0 0 0 0 203 … 0 0 0 1 0 0 204 … 0 0 0 1 0 0 1 0 205 … 0 1 0 0 0 1 0 0 1 13

LMBR MARout SUB RAE RBE RCE END Bus 2 R INC 2 Read LA LC LPC LIR 0 Microcode 0 0 for 1 instruction 1 0 0 1 0 LMAR 1 R 2 Bus Cout … Cout PC out 100 Branch Control Address Example: Control Signals for the sub Instruction 0 0 0 0 fetch 101 … 0 1 0 0 0 0 1 1 1 0 0 0 102 … 0 0 1 0 0 0 0 203 … 0 0 1 0 0 204 … 0 0 0 1 0 0 Microcode for sub instruction 0 1 0 0 0 0 1 0 205 … 0 1 0 0 0 0 0 14

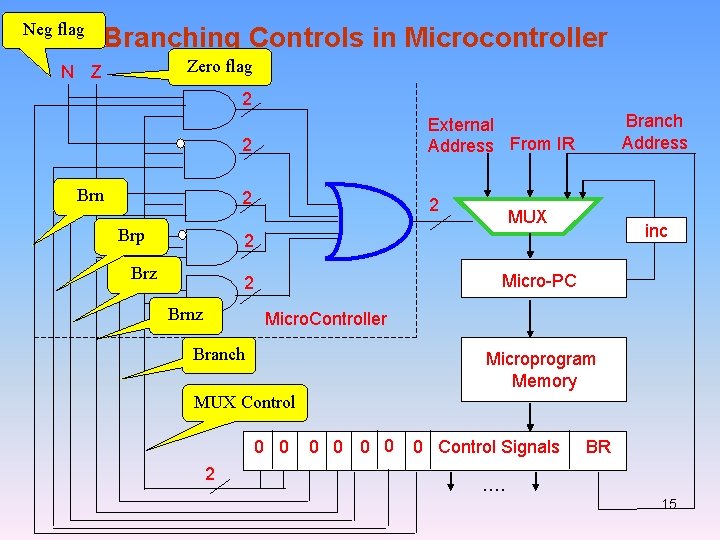

Neg flag Branching Controls in Microcontroller Zero flag N Z 2 Brn Brp 2 External Address From IR 2 2 Branch Address MUX inc 2 Brz Micro-PC 2 Brnz Micro. Controller Branch Microprogram Memory MUX Control 0 0 2 0 0 0 Control Signals BR …. 15

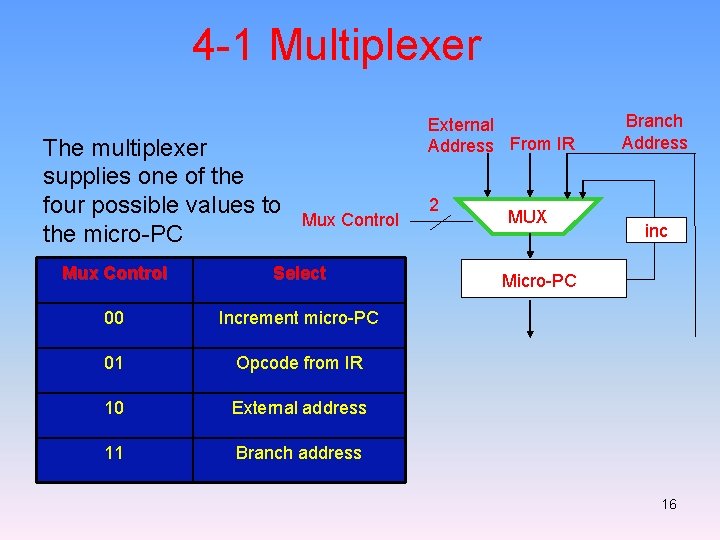

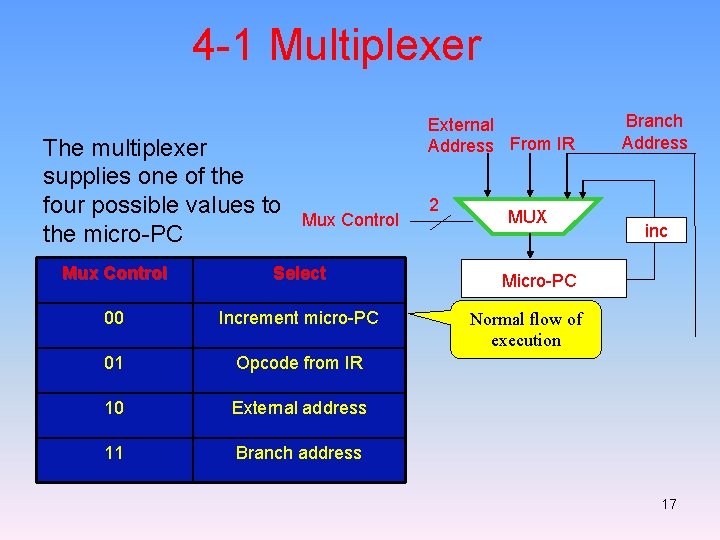

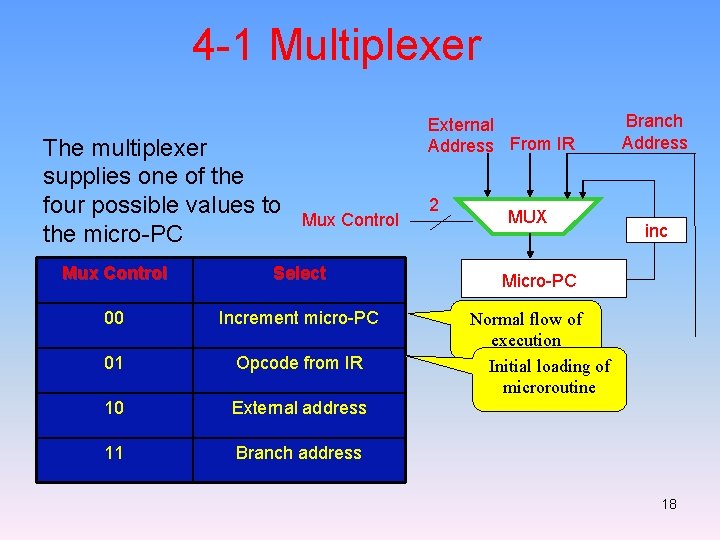

4 -1 Multiplexer The multiplexer supplies one of the four possible values to the micro-PC External Address From IR Mux Control Select 00 Increment micro-PC 01 Opcode from IR 10 External address 11 Branch address 2 MUX Branch Address inc Micro-PC 16

4 -1 Multiplexer The multiplexer supplies one of the four possible values to the micro-PC External Address From IR Mux Control Select 00 Increment micro-PC 01 Opcode from IR 10 External address 11 Branch address 2 MUX Branch Address inc Micro-PC Normal flow of execution 17

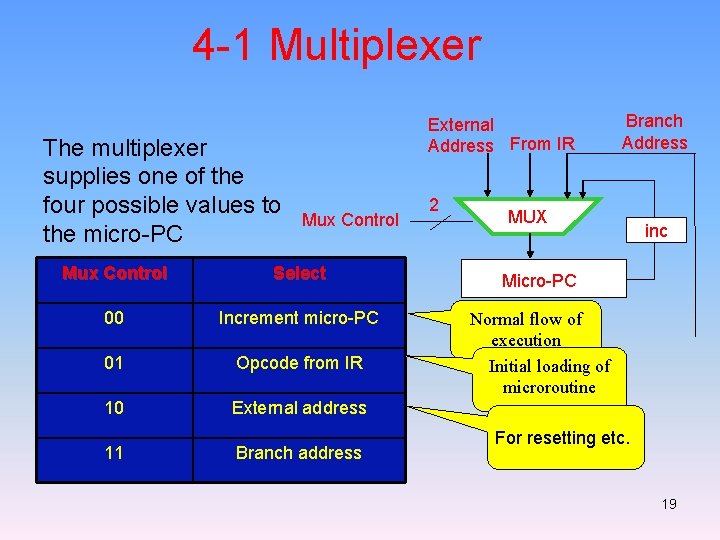

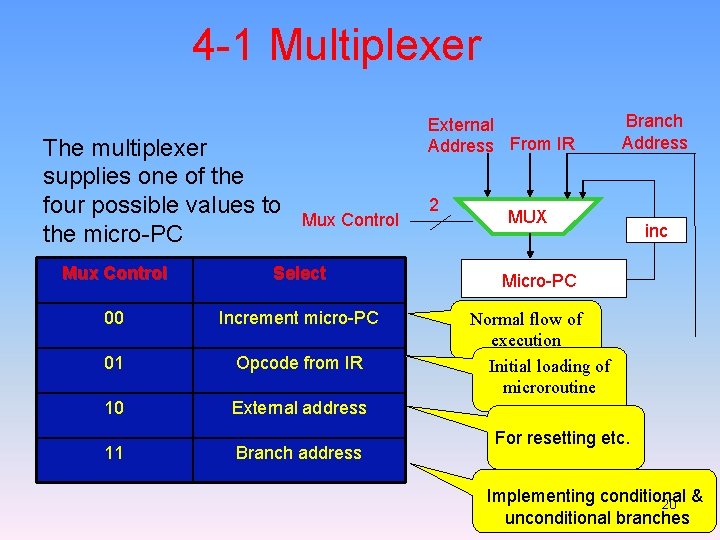

4 -1 Multiplexer The multiplexer supplies one of the four possible values to the micro-PC External Address From IR Mux Control 2 MUX Mux Control Select Micro-PC 00 Increment micro-PC 01 Opcode from IR 10 External address Normal flow of execution Initial loading of microroutine 11 Branch address Branch Address inc 18

4 -1 Multiplexer The multiplexer supplies one of the four possible values to the micro-PC External Address From IR Mux Control 2 Branch Address MUX Mux Control Select Micro-PC 00 Increment micro-PC 01 Opcode from IR 10 External address Normal flow of execution Initial loading of microroutine 11 Branch address inc For resetting etc. 19

4 -1 Multiplexer The multiplexer supplies one of the four possible values to the micro-PC External Address From IR Mux Control 2 Branch Address MUX Mux Control Select Micro-PC 00 Increment micro-PC 01 Opcode from IR 10 External address Normal flow of execution Initial loading of microroutine 11 Branch address inc For resetting etc. Implementing conditional 20 & unconditional branches

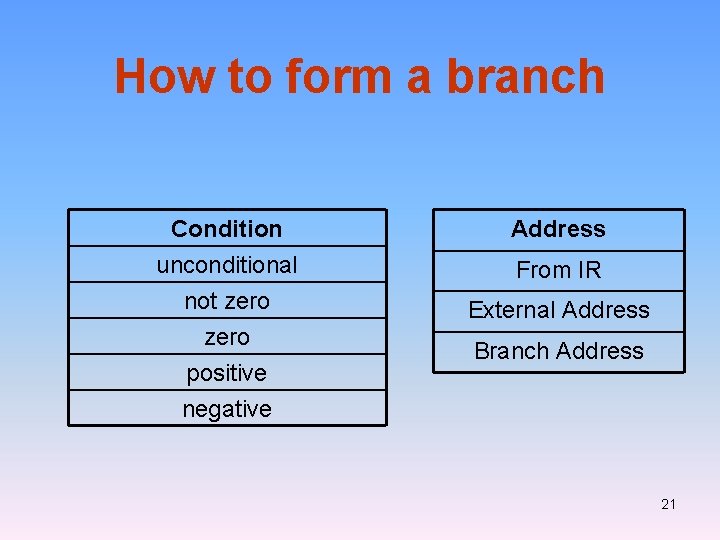

How to form a branch Condition unconditional not zero positive negative Address From IR External Address Branch Address 21

Microcode branching Examples 22

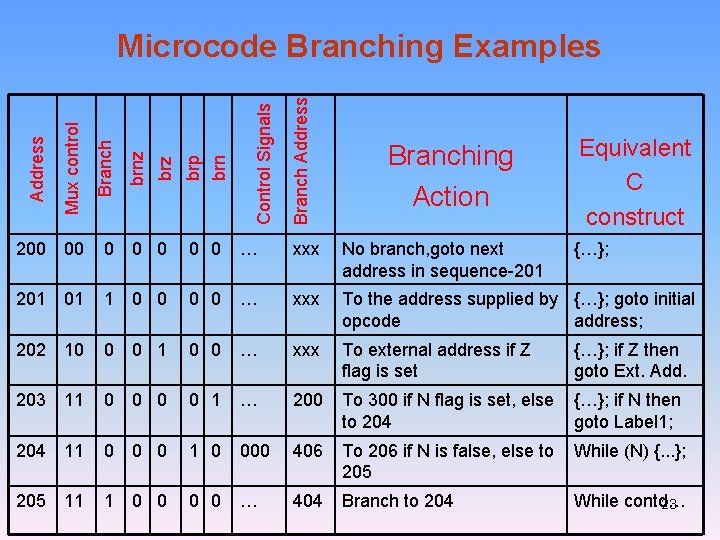

Branch Address 0 0 0 … xxx No branch, goto next address in sequence-201 01 1 0 0 … xxx To the address supplied by {…}; goto initial opcode address; 202 10 0 0 1 0 0 … xxx To external address if Z flag is set {…}; if Z then goto Ext. Add. 203 11 0 0 1 … 200 To 300 if N flag is set, else to 204 {…}; if N then goto Label 1; 204 11 0 0 0 1 0 000 406 To 206 if N is false, else to 205 While (N) {. . . }; 205 11 1 0 0 … 404 Branch to 204 While contd… 23 brp brn Branch 00 brz Mux control 200 brnz Address Control Signals Microcode Branching Examples Branching Action Equivalent C construct {…};

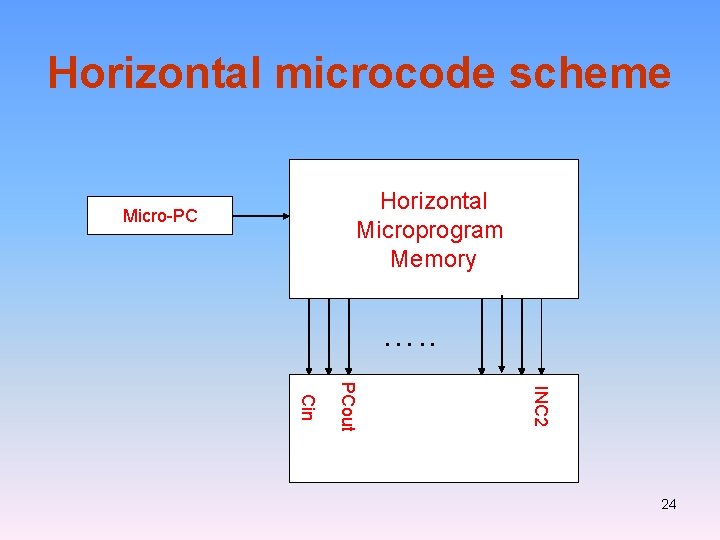

Horizontal microcode scheme Horizontal Microprogram Memory Micro-PC …. . INC 2 PCout Cin 24

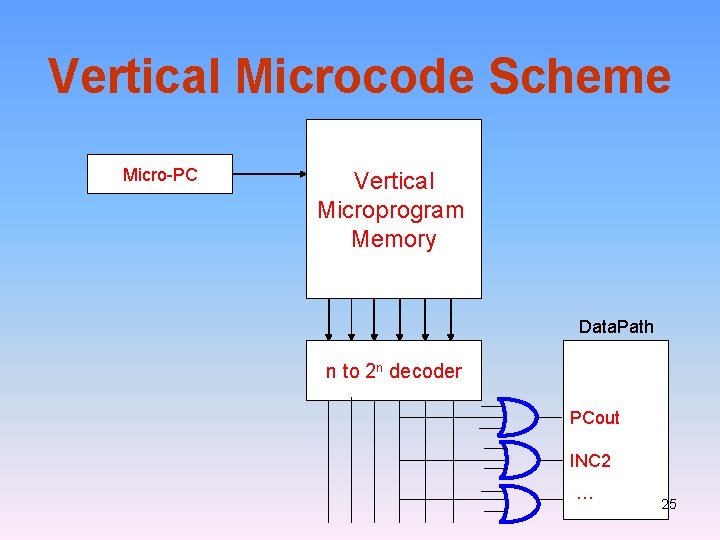

Vertical Microcode Scheme Micro-PC Vertical Microprogram Memory Data. Path n to 2 n decoder PCout INC 2 … 25

Microcoded 1 -bus SRC design 26

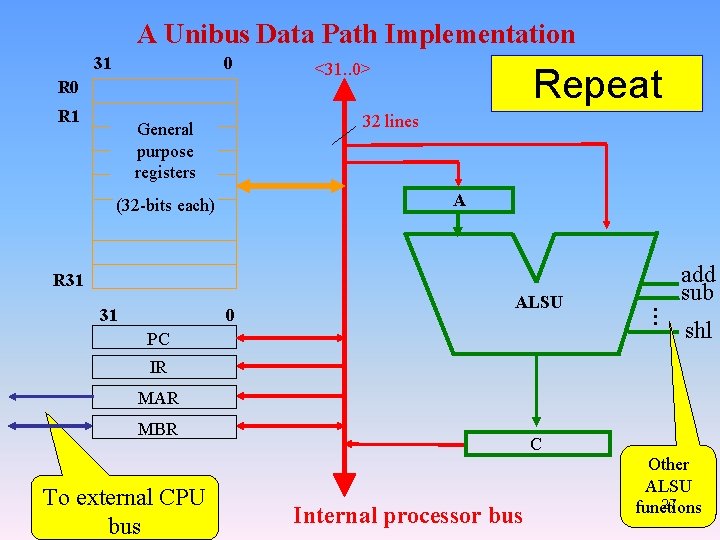

A Unibus Data Path Implementation 31 0 R 1 <31. . 0> Repeat 32 lines General purpose registers A (32 -bits each) add sub R 31 0 PC … 31 ALSU shl IR MAR MBR To external CPU bus C Internal processor bus Other ALSU 27 functions

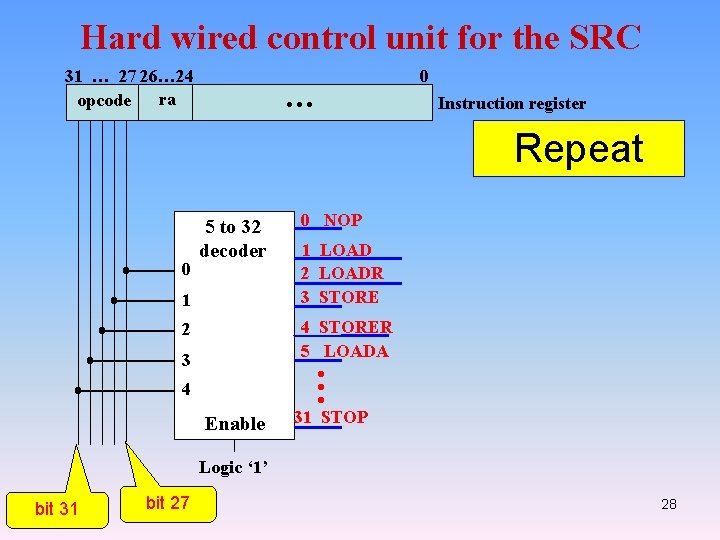

Hard wired control unit for the SRC 31 … 27 26… 24 ra opcode … 0 Instruction register Repeat 0 5 to 32 decoder 1 0 NOP 1 LOAD 2 LOADR 3 STORE 4 STORER 5 LOADA 2 … 3 4 Enable 31 STOP Logic ‘ 1’ bit 31 bit 27 28

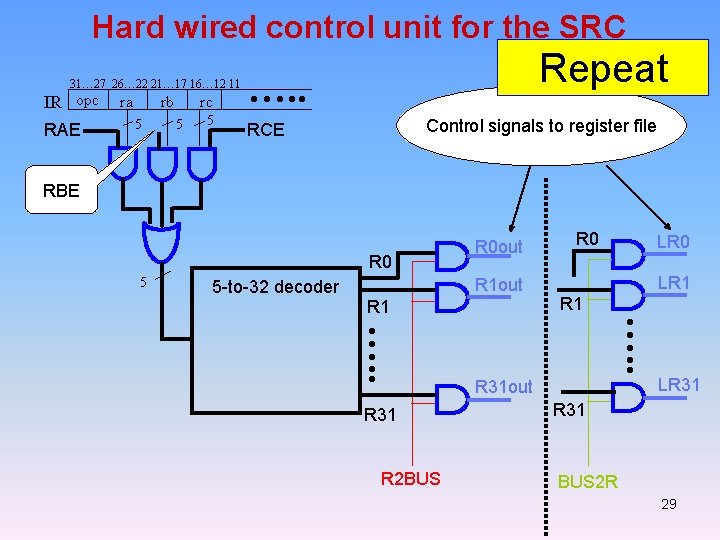

Hard wired control unit for the SRC 31… 27 26… 22 21… 17 16… 12 11 IR opc RAE ra rb 5 rc 5 5 Repeat …. . Control signals to register file RCE RBE R 0 5 R 0 out R 1 out 5 -to-32 decoder …. . R 31 R 2 BUS LR 0 LR 1 …. . R 1 R 0 LR 31 out R 31 BUS 2 R 29

Microcoded Control Unit for the SRC Starting address from opcode Clk External source … MUX Branch Address Other Micro-PC Microprogram Memory SRC Micro-controller Inc Micro-Branch Control Micro-IR … Control Signals 30

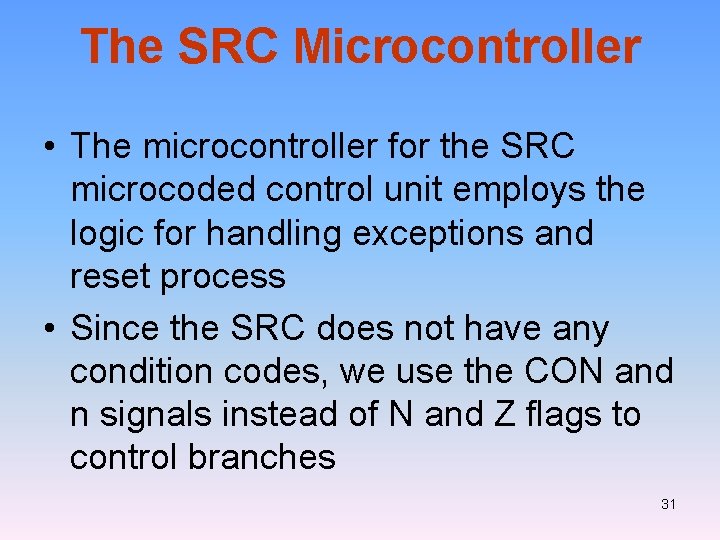

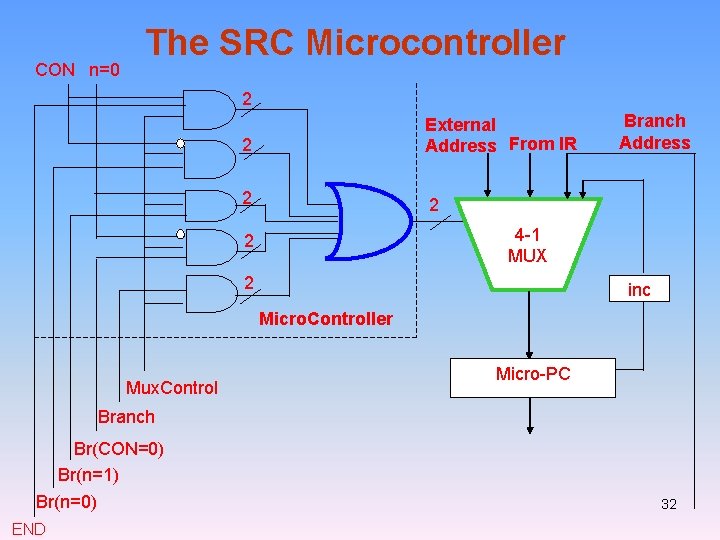

The SRC Microcontroller • The microcontroller for the SRC microcoded control unit employs the logic for handling exceptions and reset process • Since the SRC does not have any condition codes, we use the CON and n signals instead of N and Z flags to control branches 31

CON n=0 The SRC Microcontroller 2 2 External Address From IR 2 2 Branch Address 4 -1 MUX 2 2 inc Micro. Controller Mux. Control Micro-PC Branch Br(CON=0) Br(n=1) Br(n=0) END 32

Microcode for some SRC instructions 33

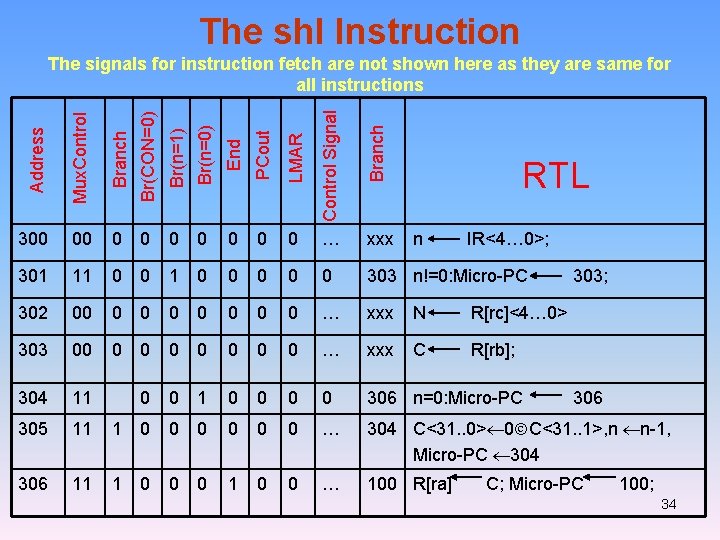

The shl Instruction Mux. Control Branch Br(CON=0) Br(n=1) Br(n=0) End PCout LMAR Control Signal 300 00 0 0 0 … xxx 301 11 0 0 0 0 0 303 n!=0: Micro-PC 302 00 0 0 0 … xxx N R[rc]<4… 0> 303 00 0 0 0 … xxx C R[rb]; 304 11 0 0 0 0 306 n=0: Micro-PC 305 11 1 0 0 0 … 304 C<31. . 0> 0 C<31. . 1>, n n-1, Micro-PC 304 306 11 1 0 0 0 1 0 0 … 100 R[ra] Branch Address The signals for instruction fetch are not shown here as they are same for all instructions RTL n IR<4… 0>; 303; 306 C; Micro-PC 100; 34

Alternative approaches to microcoding • • Bit ORing Nanocoding Writable Microprogram Memory Subroutines in Microprogramming 35

- Slides: 35